# Application Specific Analog-to-Digital Converters (ADCs) for Communication Systems

by

### . Aurangozeb

A thesis submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

in

### Integrated Circuits and Systems

# Department of Electrical and Computer Engineering University of Alberta

© . Aurangozeb, 2019

### Abstract

To compete with the existing products, hardware manufacturers are required to develop their products with a great focus on smaller area and lower power consumption. The trade-offs between power, area, and the speed of operation play a vital role in the field of integrated circuit design. Therefore, an enormous architectural exploration is required to achieve the targeted specification. For the architectural exploration, a significant amount of different hardware architectures needs to be prepared and analyzed to meet the required specifications under the worst-case scenario. It not only involves many steps but is also a very time-consuming and tedious process.

In this dissertation, our architectural exploration was to find the suitable hardware architectures for the given communication systems. More specifically, we tried to minimize the power consumption and area of the most power-hungry block such as analog-to-digital converter (ADC) in the given systems. We designed two ADC prototypes for the given communication systems – one for wireline channel equalization and one for digital beamforming (DBF). The proposed architectures along with the application specific ADCs can successfully achieve lower power and decreases the area, that was verified by the measured results from the implemented prototypes.

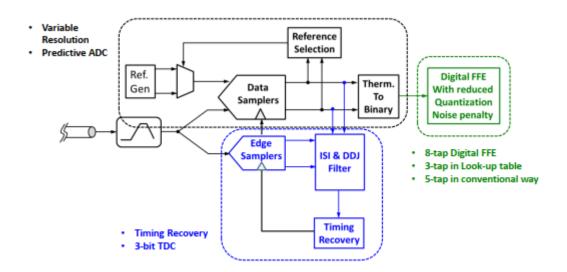

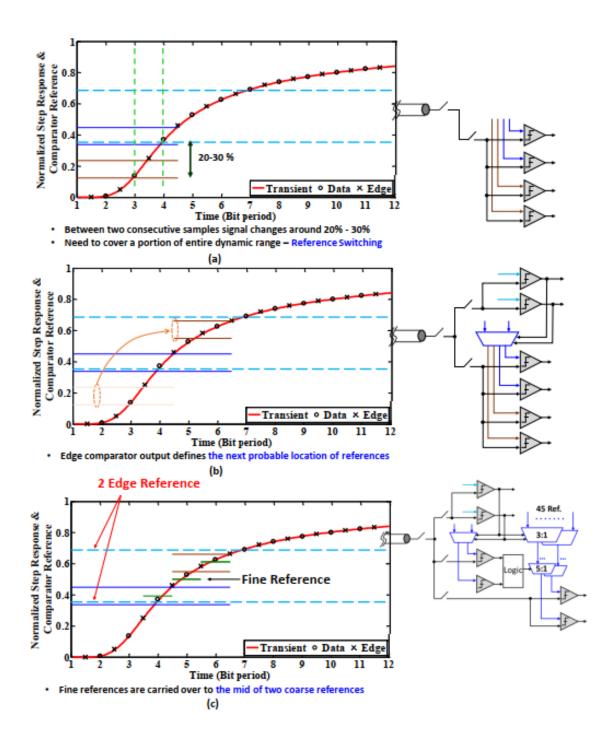

The first prototype is a variable resolution ADC for the wireline transceiver application. In conventional mixed-signal transceivers, most of the equalization is performed in analog domain. As CMOS technologies continues to scale, the linearity requirement for the analog circuitry becomes more stringent. Therefore, porting of conventional mixed-signal transceivers to lower technology nodes becomes challenging. The ADC-based receiver is a viable alternative because it performs the equalization in digital domain. In ADC-based receiver, a digital feedforward equalizer (FFE) along with a decision feedback equalizer (DFE) can be exploited for channel equalization and data recovery. Prior to that, it requires a power-hungry ADC to digitize the received signal, and finally facilitates a high-fidelity recovery of data. Rather than utilizing a general-purpose ADC, an application specific ADC can offer a more power-efficient data recovery. The proof-of-concept is demonstrated by designing and fabricating a low-power channel-adaptive 28 Gb/s PAM-4 receiver in CMOS 65nm technology. It utilizes a predictive ADC, a successive-approximation-register (SAR) time-to-digital converter (TDC), and a feed-

forward equalizer (FFE) in the digital domain. The variable-resolution Flash ADC uses knowledge of the channel inter symbol interference (ISI) characteristics and adjusts the thresholds of the comparators dynamically based on the prediction to cover a significant amount of ADC dynamic range in which the sampled signal can be appeared. As a result, the channel adaptive ADC can cover equivalent dynamic range to a 5.5-bit linear responding ADC utilizing only 16 comparators. By reusing the comparators, the ADC can provide a programmable resolution from 2-bit to 5.5-bit consuming 40 mW to 90 mW respectively. The SAR-TDC generates 5-bit timing information that includes 2-bit ISI and 3-bit timing error to achieve a low-latency, and low-jitter timing recovery. Subsequently, a 3-to-8 programmable tap FFE is used to equalize up to 30 dB loss achieving bit error rate (BER) lower than 10<sup>-8</sup>. FFE is implemented in an FPGA and the first 3 taps are realized in a look-up table (LUT). An offline higher resolution ADC is used to generate the pre-computed values for the LUT. Measured power consumption is 130 mW (excluding DSP) from a 1.2 V power supply with active chip area of 0.2025 mm<sup>2</sup> in 65 nm technology. Due to programmability on the both ADC resolution and the number of FFE taps according to the channel loss, the receiver enables energy efficiency according to loss compensation.

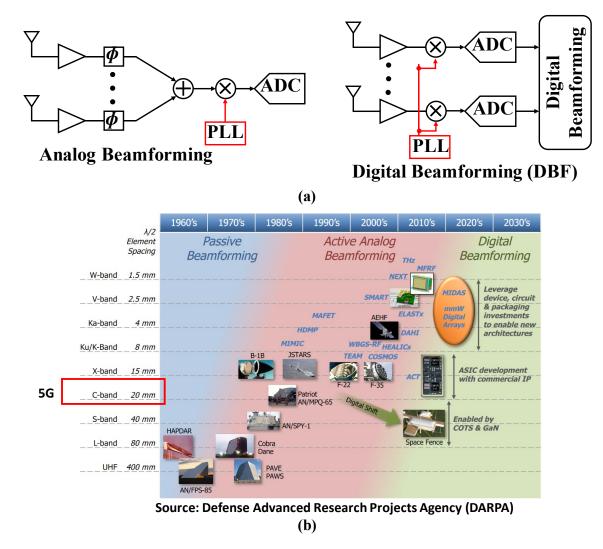

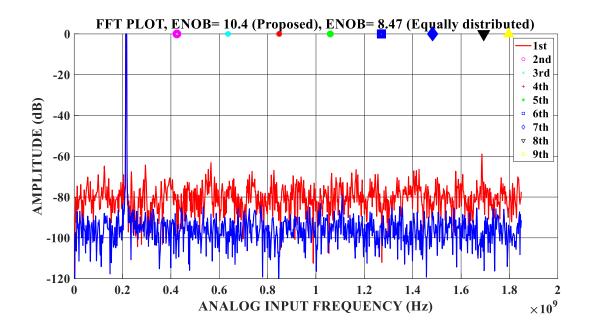

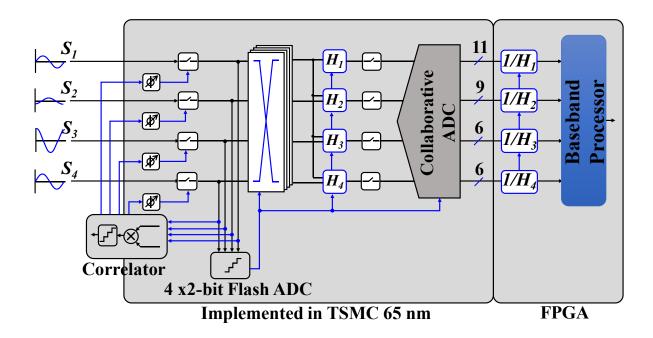

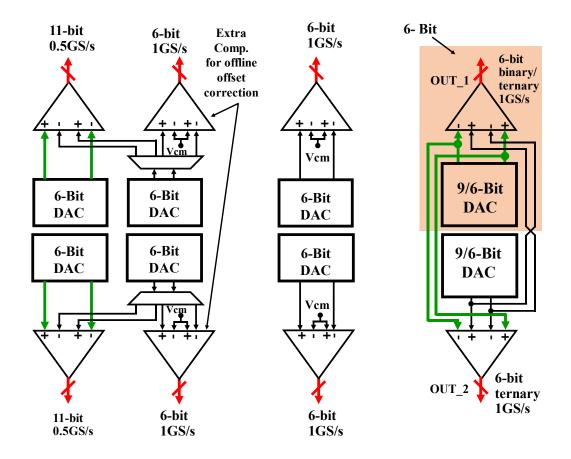

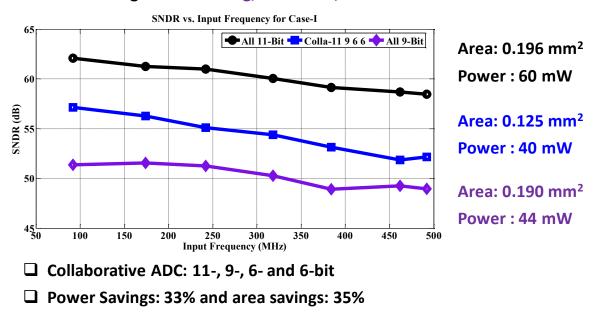

The second prototype is a collaborative ADC for the digital beamforming (DBF) application. In the conventional multiple-input and multiple-output (MIMO) DBF, each channel employs an individual ADC. Therefore, power consumption of these ADCs can easily exceed the transceiver power budget for the portable mobile devices. To resolve this, we introduce a collaborative ADC that digitizes multiple channels together rather than digitizing each channel independently. This technique reduces power consumption by as much as 41% compared to the stand-alone ADCs for a 4-channel MIMO receiver. For the proof-of-concept, a 4x11-bit 1 GS/s 40 mW collaborative ADC is designed in 65nm CMOS. This work extends maximal-ratio-combining (MRC) approach to define ADC resolution in a multi-channel environment to maximize the signal-to-noise ratio (SNR) in a power-constrained application. The ADC takes advantage of the channel diversity by distributing the resolution according to channel SNR. In addition, it utilizes the correlated information between channels to perform energy efficient digitization of received signals. The collaborative ADC is designed with eight successive-approximation-register (SAR) ADC units each having 6-bit resolution. To estimate the relative signal strength and correlation between the channels, a 2-bit Flash ADC is placed in each channel. With the help of the 2-bit flash, the ADC can detect change in channel SNR, and accordingly reconfigure the four ADCs with variable

resolution from 6-bit to 11-bit with less than 1 ns mode switching time. This collaborative ADC performance is compared with 4 channel ADCs with uniform 11 and 9 bits of resolution. It reduces area and power by half and 41% respectively with only 10% degradation of overall signal-to-noise and distortion ratio (SNDR).

### Preface

This dissertation report is an original work by Aurangozeb under the supervision of Prof. Masum Hossain. Our industrial sponsor was Microsemi (acquired by Microchip) Burnaby, British Columbia, Canada. Some parts of the report have already been published or submitted for future publication as follows;

Chapter 3 have been published as

- Aurangozeb, A. K. M. D. Hossain and M. Hossain, "Channel adaptive ADC and TDC for 28 Gb/s PAM-4 digital receiver," 2017 IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, 2017, pp. 1-4.

- Aurangozeb, A. D. Hossain, M. Mohammad and M. Hossain, "Channel-Adaptive ADC and TDC for 28 Gb/s PAM-4 Digital Receiver," in IEEE Journal of Solid-State Circuits, vol. 53, no. 3, pp. 772-788, March 2018.

For the above published works, I was responsible for the system design, measurements, data collection, and analysis as well as the manuscript composition. A. K. M. D. Hossain was responsible in assisting system design. M. Hossain is the supervisory author and was involved with concept formation and manuscript composition. M. Mohammad is the industrial partner from Qualcomm Atheros, San Jose, CA 95110 USA who guided us with testing strategy.

Chapter 4 has been published as

- Aurangozeb, F. Aryanfar and M. Hossain, "A quad channel 11-bit 1 GS/s 40 mW Collaborative ADC based enabling digital beamforming for 5G wireless," 2017 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Honolulu, HI, 2017, pp. 120-123.

- Aurangozeb, F. Aryanfar and M. Hossain, "A quad channel 11-bit 1 GS/s 40 mW Collaborative ADC based enabling digital beamforming for 5G wireless," in IEEE Transactions on Microwave Theory and Techniques, vol. 67, no. 9, pp. 3798-3820, Sept. 2019.

For the above work, I was responsible for the system design, measurements, data collection, and analysis as well as the manuscript composition. M. Hossain is the supervisory author and was

involved with concept formation and manuscript composition. F. Aryanfar is the industrial partner from Straight Path Communications Inc., Glen Allen, VA 23059 USA who helped with antenna design and guideline for measurement.

Other published works:

Aurangozeb, A. D. Hossain, C. Ni, Q. Sharar and M. Hossain, "Time-Domain Arithmetic Logic Unit With Built-In Interconnect," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 25, no. 10, pp. 2828-2841, Oct. 2017.

For this work, I was responsible for the system design, measurements, data collection, and analysis as well as the manuscript composition. M. Hossain is the supervisory author and was involved with concept formation and manuscript composition. A. D. Hossain was involved with initial concept formation. C. Ni, and Q. Sharar was responsible for the system simulation and the manuscript composition.

A. K. M. Delwar Hossain, Aurangozeb and M. Hossain, "Burst mode optical receiver with 10 ns lock time based on concurrent DC offset and timing recovery technique," in IEEE/OSA Journal of Optical Communications and Networking, vol. 10, no. 2, pp. 65-78, Feb. 2018.

For this work, I was responsible for a part of the system design, measurements, data collection, and analysis as well as the manuscript composition. I designed the successive approximation register (SAR) based offset correction for the system. M. Hossain is the supervisory author and was involved with concept formation and manuscript composition. A. K. M. Delwar Hossain was responsible for the complete system design, measurements, data collection, and analysis as well as the manuscript composition.

## ACKNOWLEDGEMENTS

I would like to convey my sincere gratitude and thanks to my advisor professor Dr. Masum Hossain for the tremendous support during my Ph.D. study and showing me the path of my research. His immense knowledge, motivation, and guidance helped me in all the way of my graduate study and writing of my thesis. His kind support and advice on both research and on my career have been invaluable.

I would like to thank my defense committee members, professor Dr. Duncan G Elliott, professor Dr. Kambiz Moez, professor Dr. Vien Van, professor Dr. Mani Vaidyanathan, and Professor Dr. Shahriar Mirabbasi, for serving as my committee members out of your busy schedule. I would like to thank you for making my defense be an enjoyable moment, and for your valuable suggestions and comments.

I would like to convey my gratitude to the Electrical and Computer Engineering (ECE) department and the IT service at the University of Alberta for providing the support for the very-large-scale integration (VLSI) research group at the university.

I would like to thank CMC Microelectronics for providing the computer aided design (CAD) tools for simulation, and fabrication facilities.

In addition, I would like to thank my colleagues Shovon Dey, Carson Dick, AKM Delwar Hossain, Waleed El-Halwagy and Amlan Nag for their valuable discussions.

A special thanks to my parents for all the sacrifices that they made on my behalf and praying for my betterment. I would also like to thank to my beloved wife, Dilfaras Khanam, for supporting me during my studies.

### Table of Contents

|                |                     | ANALOG-TO-DIGITAL<br>S    |   | · / |     |

|----------------|---------------------|---------------------------|---|-----|-----|

| Abstract       |                     |                           |   |     | ii  |

| Preface        |                     |                           |   |     | V   |

| ACKNOWLE       | EDGEMENTS           |                           |   |     | vii |

| List of Figure | s                   |                           |   |     | xi  |

| List of Tables |                     |                           |   |     | XX  |

| Acronyms       |                     |                           |   |     | xxi |

| Chapter 1 An   | alog-to-Digital C   | onverter (ADC)            |   |     | 1   |

| 1 INTRODU      | UCTION              |                           |   |     | 1   |

| 1.1 FLAS       | H ADC               |                           |   |     | 3   |

| 1.1.1          | Decoder             |                           |   |     | 5   |

| 1.2 Two-S      | Step Flash ADC      |                           |   |     | 7   |

| 1.3 Pipelin    | ned ADC             |                           |   |     | 9   |

| 1.4 SAR /      | ADC                 |                           |   |     | 14  |

| 1.4.1          | Comparator          |                           |   |     | 19  |

| 1.4.2          | SAR Control L       | ogic                      |   |     | 22  |

| 1.4.3          | Capacitive DA       | C Switching Power         |   |     | 23  |

| 1.4.4          |                     | son between Flash and SA  |   |     |     |

| 1.5 Hybrid     | d-ADC               |                           |   |     | 28  |

| 1.6 Contri     | bution              |                           |   |     | 30  |

| 1.6.1          | ADC designed        | for Channel Equalization. |   |     | 32  |

| 1.6.2          | ADCs designed       | for Digital Beamforming   | 5 |     | 32  |

| Chapter 2 Cas  | ses for Application | on Specific ADCs          |   |     |     |

| 2 | Nee   | ed for A | Application Specific Hardware                                                     | 36  |

|---|-------|----------|-----------------------------------------------------------------------------------|-----|

|   | 2.1   | ADCs     | for Channel Equalization                                                          | 36  |

|   | 2.2   | ADCs     | for Digital Beamforming                                                           | 46  |

| C | hapte | er 3 Cha | annel-Adaptive ADC and TDC for 28 Gb/s PAM-4 Digital receiver                     | 51  |

| 3 | Intr  | oductic  | on                                                                                | 51  |

|   | 3.1   | ADC-     | TDC-based Receiver Architecture                                                   | 54  |

|   | 3.2   | ISI AV   | WARE VARIABLE RESOLUTION ADC                                                      | 56  |

|   |       | 3.2.1    | Timing Budget for Reference Selection                                             | 62  |

|   |       | 3.2.2    | Modes of operation                                                                | 65  |

|   | 3.3   | Timin    | g Recovery                                                                        | 65  |

|   | 3.4   | Scalab   | le Digital Equalization                                                           | 74  |

|   | 3.5   | Implei   | mentation & Measurement                                                           | 80  |

|   | 3.6   | Conclu   | usion                                                                             | 89  |

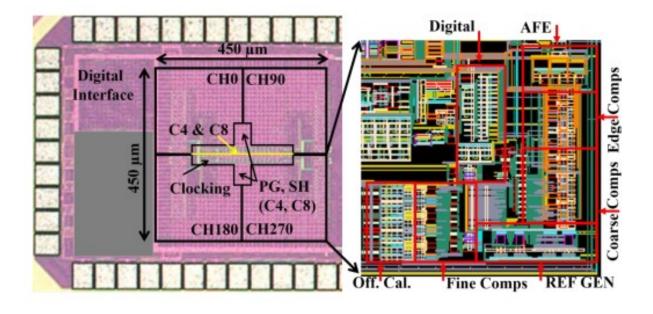

| C |       |          | Quad Channel 11-bit 1 GS/s 40 mW Collaborative ADC Enabling D ing for 5G Wireless |     |

| 4 | INT   | RODU     | JCTION                                                                            | 90  |

|   | 4.1   | Power    | -Aware SQNR Optimization                                                          | 95  |

|   | 4.2   | Distril  | oution of ADC Resolution Based on Interference                                    | 97  |

|   | 4.3   | Analo    | g Front End (AFE) for Collaborative ADC                                           | 102 |

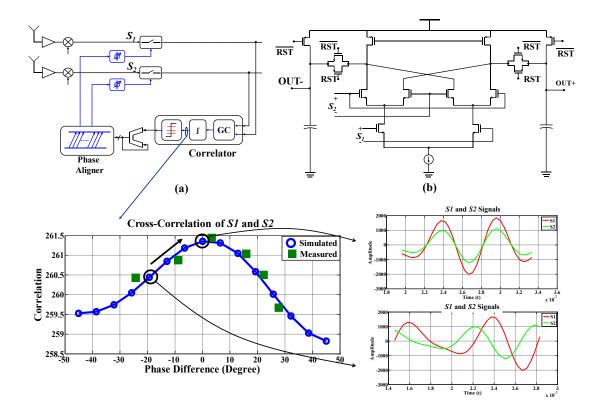

|   |       | 4.3.1    | Phase Alignment                                                                   | 104 |

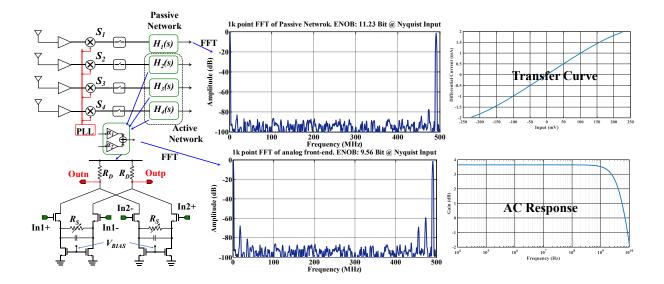

|   |       | 4.3.2    | Analog Pre-Processing                                                             | 106 |

|   | 4.4   | Recon    | figurable ADC                                                                     | 111 |

|   |       | 4.4.1    | Clock Generation                                                                  | 113 |

|   |       | 4.4.2    | A 6-bit Asynchronous conventional SAR ADC                                         | 113 |

|   |       | 4.4.3    | A 9-bit Ternary Asynchronous SAR ADC                                              | 118 |

|   |       | 4.4.4    | A 11-bit 2-way Time-Interleaved (TI) Asynchronous SAR ADC                         | 121 |

|    |       | 4.4.5    | Calibration123                                             | 8 |

|----|-------|----------|------------------------------------------------------------|---|

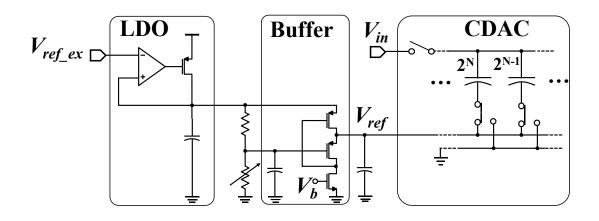

|    |       | 4.4.6    | Reference Voltage Generation                               | 9 |

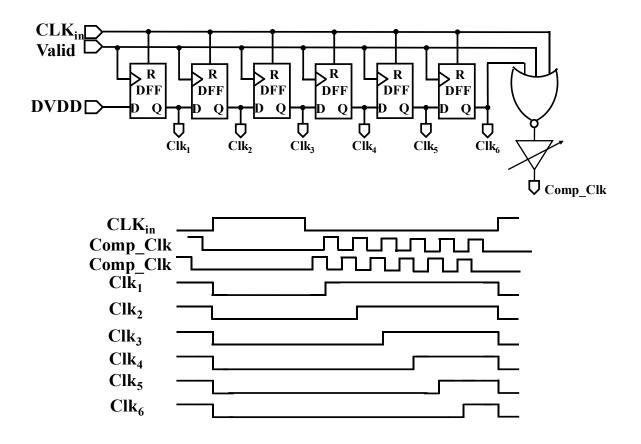

|    |       | 4.4.7    | Asynchronous Clock Generation                              | 1 |

|    | 4.5   | Impler   | nentation and Measured Results134                          | 4 |

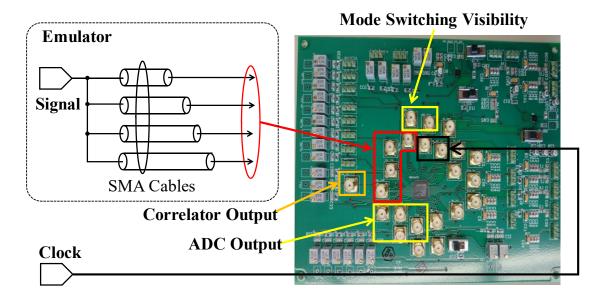

|    |       | 4.5.1    | Test Setup and Measurement                                 | 5 |

|    |       | 4.5.2    | Testing of Phase Alignment                                 | 5 |

|    |       | 4.5.3    | Testing of individual ADC                                  | 6 |

|    |       | 4.5.4    | Mode switching                                             | 8 |

|    |       | 4.5.5    | Collaborative performance                                  | 2 |

|    | 4.6   | Conclu   | 14.                                                        | 5 |

| Cł | napte | er 5 Cor | clusion and Future Works14                                 | 6 |

| 5  | INT   | RODU     | CTION14                                                    | 6 |

|    | 5.1   | Summ     | ary of the dissertation14                                  | 6 |

|    | 5.2   | Thesis   | Contribution                                               | 7 |

|    | 5.3   | Future   | Work                                                       | 9 |

|    |       | 5.3.1    | Analog-to-Sequence Converter (ASC) for channel equalizer14 | 9 |

|    |       | 5.3.2    | Collaborative ADC for 8- or more channel MIMO receiver     | 9 |

| Re | efere | nces     |                                                            | 1 |

## List of Figures

| Figure 1-1 : The concept of analog-to-digital conversion                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1-2 : Block diagram and operation of ADC                                                                                                                                                                                             |

| Figure 1-3 : ADC quantization levels and quantization error                                                                                                                                                                                 |

| Figure 1-4 : (a) Architecture of the Flash ADC, (b) Timing diagram of the Flash ADC operation.                                                                                                                                              |

| Figure 1-5 : Different types of encoders for Flash ADC, (a) ROM-based, (b) Fat tree, (c) Wallace Tree, and (d) MUX-based                                                                                                                    |

| Figure 1-6 : Two-step Flash ADC                                                                                                                                                                                                             |

| Figure 1-7 : Two-step Flash ADC working principle. (a) When residue is multiplied by $2^{M}$ , (b) when residue is multiplied by 1                                                                                                          |

| Figure 1-8 : Pipelined ADC architecture                                                                                                                                                                                                     |

| Figure 1-9 : (a) Architecture of a multiply-by-two switched-capacitor circuit used as a MDAC in pipelined ADC state, (b) Timing diagram of the operation, (c) the operation of the sampling, and (d) the operation of residue-amplification |

| Figure 1-10 : (a) A residue plot considering ideal behavior, (b) A residue plot considering capacitor mismatch, and (c) A residue plot considering finite op-amp gain and comparator offset                                                 |

| Figure 1-11 : (a) A residue plot considering comparator offset for a differential system, (b) A residue plot that avoids comparator offset , and (c) A 1.5-bit/stage implementation                                                         |

| Figure 1-12 : The operation of the binary search algorithm                                                                                                                                                                                  |

| Figure 1-13 : (a) The architecture of a SAR ADC, (b) timing diagram of the SAR ADC operation                                                                                                                                                |

| Figure 1-14 : SAR ADC operation                                                                                                                                                                                                             |

| Figure 1-15 : Schematic Diagram of a strong-ARM latch comparator                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1-16 : Comparator operation phases, (a) precharge, (b) amplification, (c) turn-on cross-<br>coupled NMOS pair, and (d) turn-on back-to-back inverter                                                                                              |

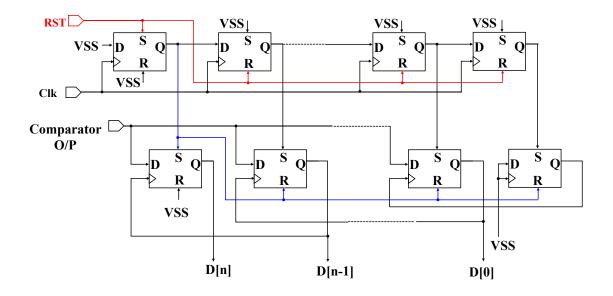

| Figure 1-17 : Conventional design of SAR Logic                                                                                                                                                                                                           |

| Figure 1-18 : Schematic of DFF with set and reset                                                                                                                                                                                                        |

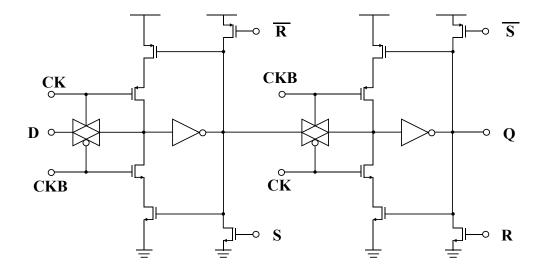

| Figure 1-19 : Time interleaved ADC architecture                                                                                                                                                                                                          |

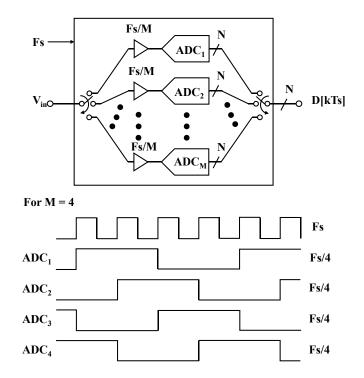

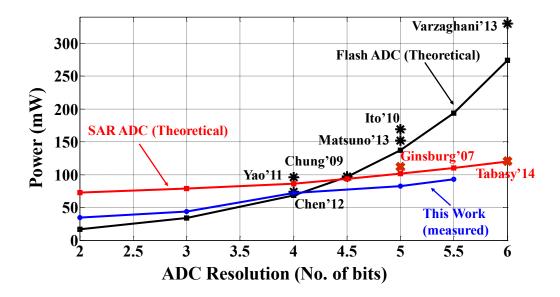

| Figure 1-20 : ADC resolution vs. power @ 14 GS/s in 65nm CMOS for flash and SAR architecture.                                                                                                                                                            |

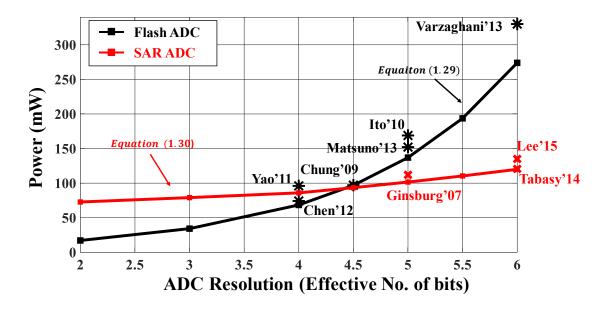

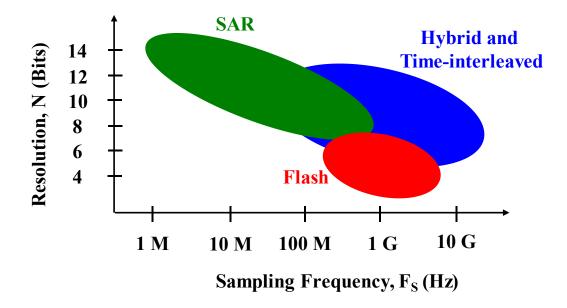

| Figure 1-21 : ADC scenario for Flash, SAR, and hybrid & TI architectures in terms of resolution and sampling frequency                                                                                                                                   |

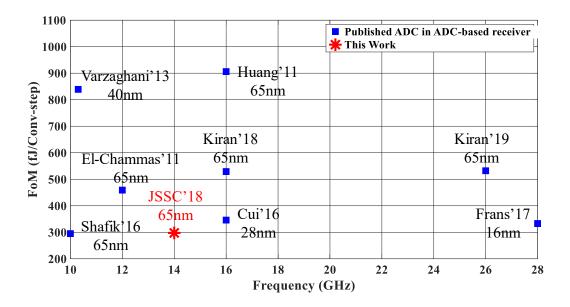

| Figure 1-22 : Walden FoM of different types of ADCs used in ADC-based receiver having sampling frequency greater than or equal to 10 GS/s                                                                                                                |

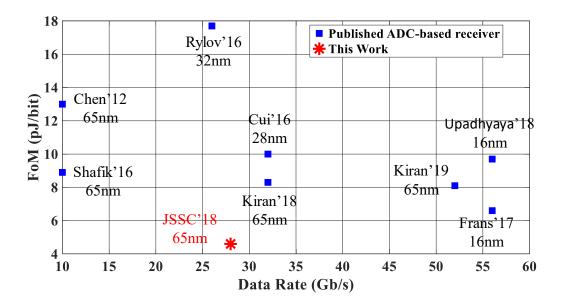

| Figure 1-23 : Comparison of the receiver FoM of the ADC-based receivers                                                                                                                                                                                  |

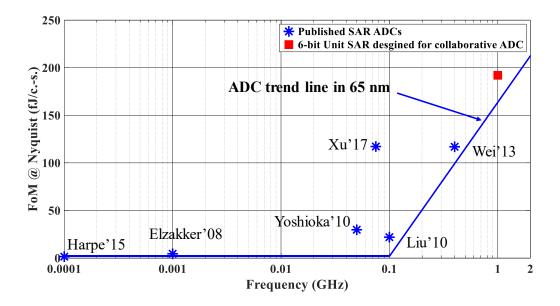

| Figure 1-24 : Walden FoM of the SAR ADCs published in ISSCC and VLSI from 2005 using 65nm technology                                                                                                                                                     |

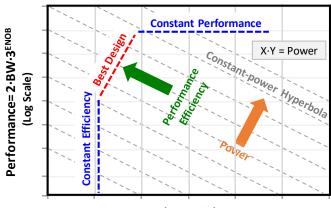

| Figure 1-25 : (a) Performance vs. energy efficiency plot for the ADCs to find the optimum design point for the ADCs to achieve low power and consistent performance, and (b) Comparison of the proposed 4x collaborative ADC with the published SAR ADCs |

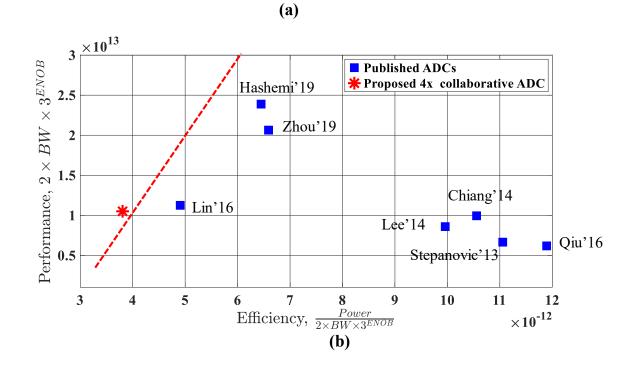

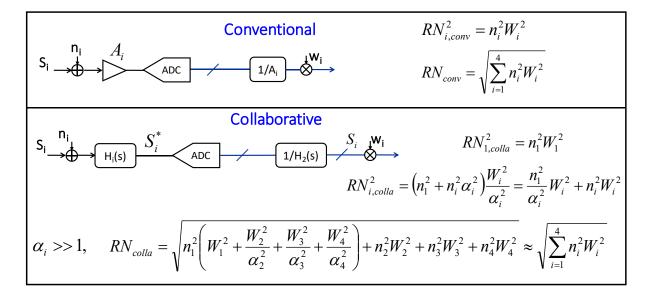

| Figure 2-1: (a) A backplane system with transmitter, connectors, PCB traces, and receiver, (b) The                                                                                                                                                       |

| loss profile of the backplane system, (c) PAM – 2 data transmission at different losses, and (d)<br>Impulse response of a channel                                                                                                                        |

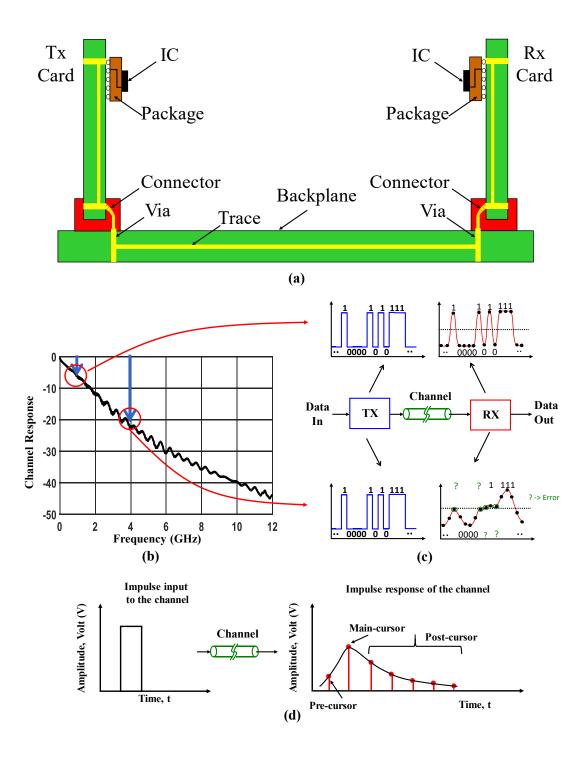

| Figure 2-2: Architecture of a conventional mixed-signal transceiver                                                                                                                                                                                      |

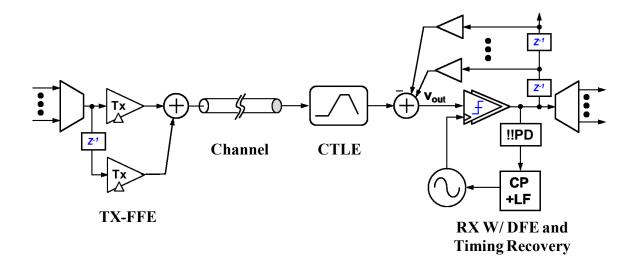

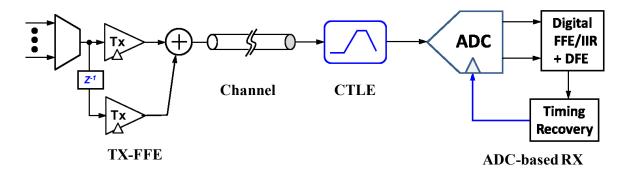

| Figure 2-3: Architecture of an ADC-based receiver                                                                                                                                                                                                        |

| Figure 2-4: Proposed ADC-based receiver to overcome the design challenges associated with the ADC-based receiver                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-5: Variable resolution ADC takes the advantage of the channel ISI. For the low-loss channel case, the signal variation is almost entire dynamic range of the ADC within a single unit interval (UI). Therefore, for a 12 dB loss channel, four comparators are sufficient to perform the equalization. In this case, most of the equalization is performed by the front-end linear equalizer, so the ADC only performs the symbol detection |

| Figure 2-6: Scenario of the selection of ADC resolution for a 25 dB loss channel. Step response at ADC input for a long-reach channel with 30 dB loss. In both cases LEQ boost is set to 8 dB.44                                                                                                                                                                                                                                                     |

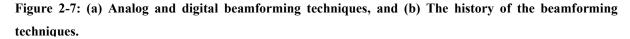

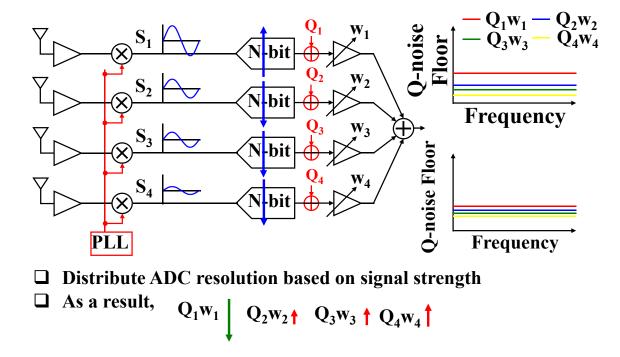

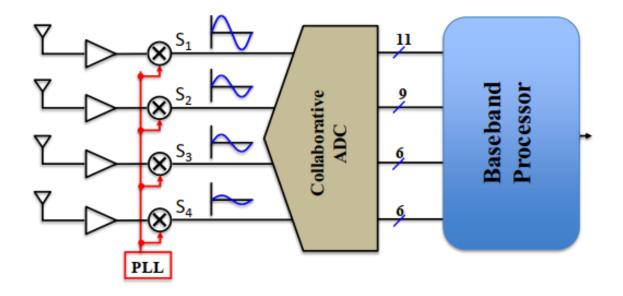

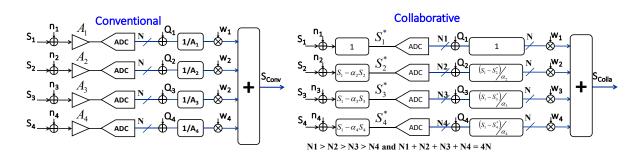

| Figure 2-7: (a) Analog and digital beamforming techniques, and (b) The history of the beamforming techniques                                                                                                                                                                                                                                                                                                                                         |

| Figure 2-8: Distribution of the total ADC resolution based on signal strength in digital beamforming                                                                                                                                                                                                                                                                                                                                                 |

| Figure 2-9: A collaborative ADC concept for a 4-cahnnel MIMO receiver                                                                                                                                                                                                                                                                                                                                                                                |

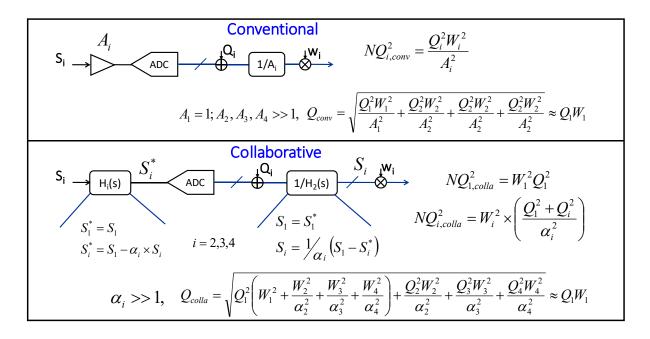

| Figure 2-10 : Noise source modeling of conventional and collaborative ADC                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 2-11: Comparison of the quantization noises at the outputs                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 2-12: Comparison of the thermal noises at the outputs                                                                                                                                                                                                                                                                                                                                                                                         |

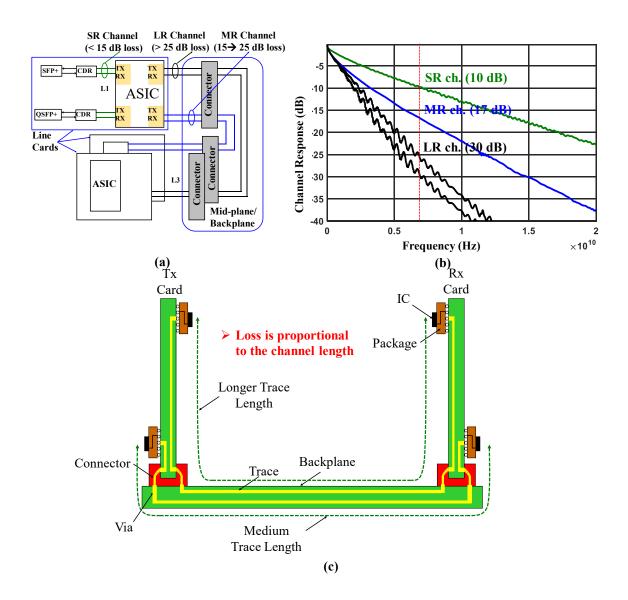

| Figure 3-1 : (a) ASICs with transceivers supporting long-reach (LR), medium-reach (MR) and short-reach (SR) channels, (b) Their frequency responses, and (c) The detailed connections about a medium-reach channel and a long-reach channel                                                                                                                                                                                                          |

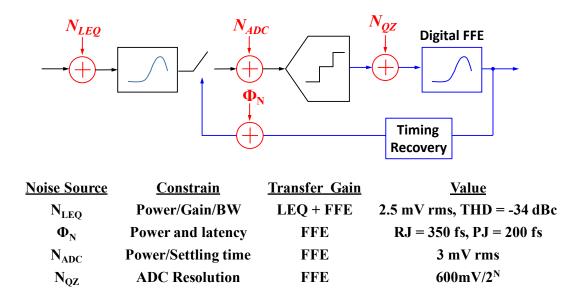

| Figure 3-2 : ADC-based digital receiver with noise sources                                                                                                                                                                                                                                                                                                                                                                                           |

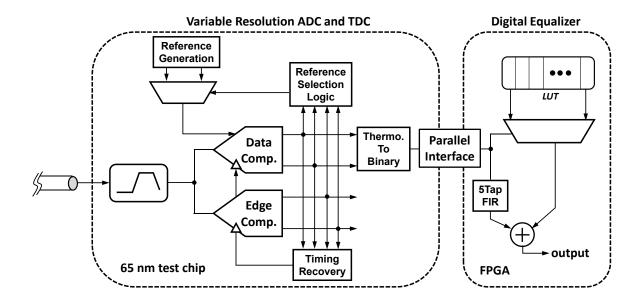

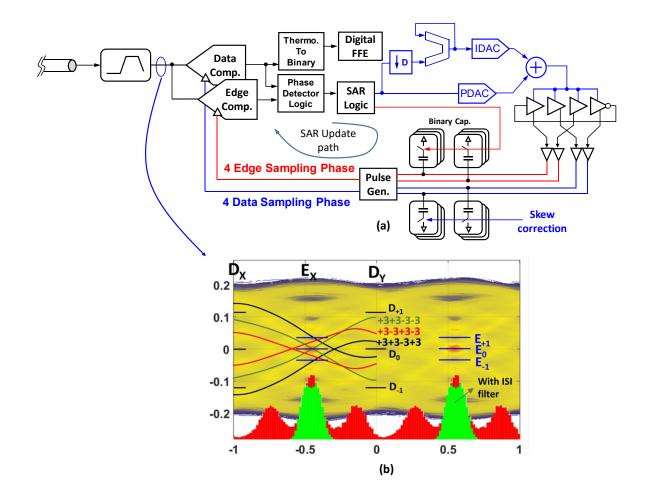

| Figure 3-3 : The overall architecture of the proposed ADC-based digital receiver                                                                                                                                                                                                                                                                                                                                                                     |

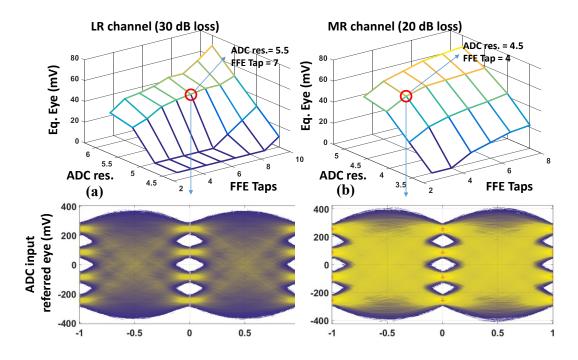

| needed resolution and taps to achieve $40+$ mV opening for BER $< 10^{-6}$                          |

|-----------------------------------------------------------------------------------------------------|

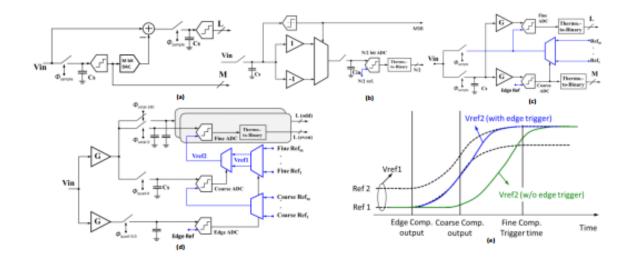

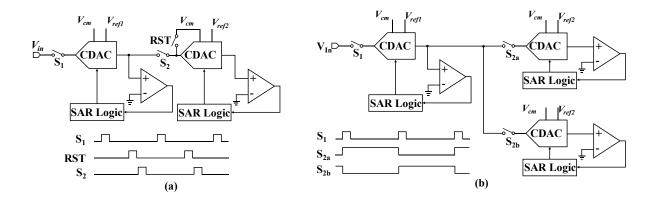

| Figure 3-5 : Different architecture of two-step flash ADC (a) subtraction of coarse reference from  |

| input and residue amplification [95], (b) Rectification, resampling and sharing the resampled value |

| [96], (c) Sharing sampled value between coarse and fine ADC [99], (d) Proposed ISI aware            |

| variable resolution ADC where Edge S/H pulse appears 0.5 UI earlier than data S/H pulse, and (e)    |

| Reference passing with and without edge trigger                                                     |

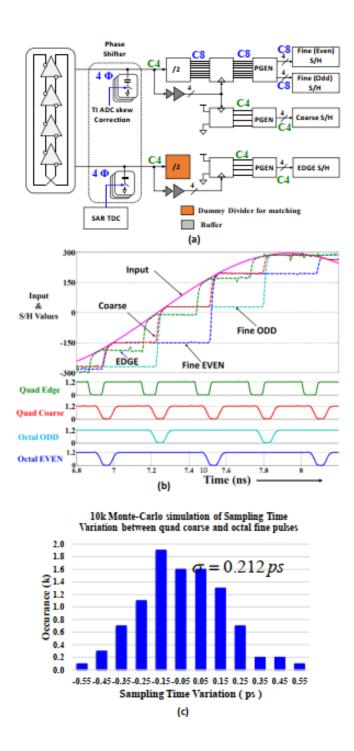

| Figure 3-6 : S/H pulse generation (a) Block diagram, (b) simulation, and (c) 10k run Monte-Carlo    |

| simulation of sampling timing variation between quad coarse and octal fine pulses                   |

| Figure 3-7 : ADC resolution vs power @ 14 GS/s in 65nm CMOS 60                                      |

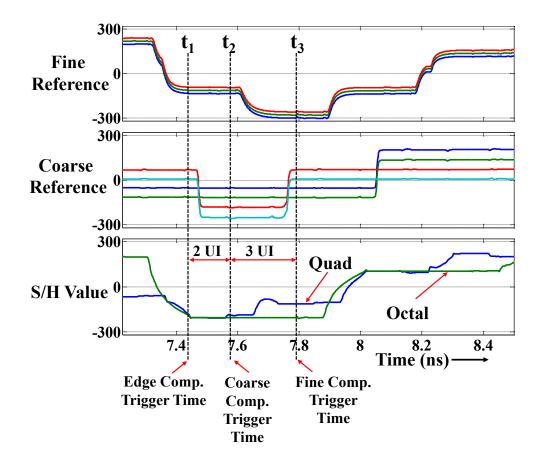

| Figure 3-8 : Simulation results of reference settling for coarse and fine comparators               |

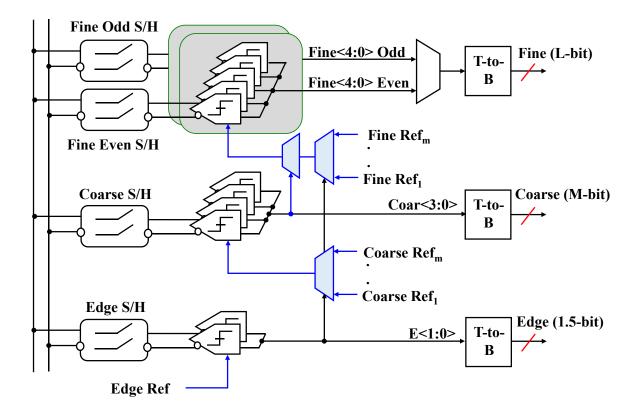

| Figure 3-9 : ADC block diagram showing S/H, comparators, reference passing mux, and                 |

| thermometer-to-binary (T-to-B) decoder only                                                         |

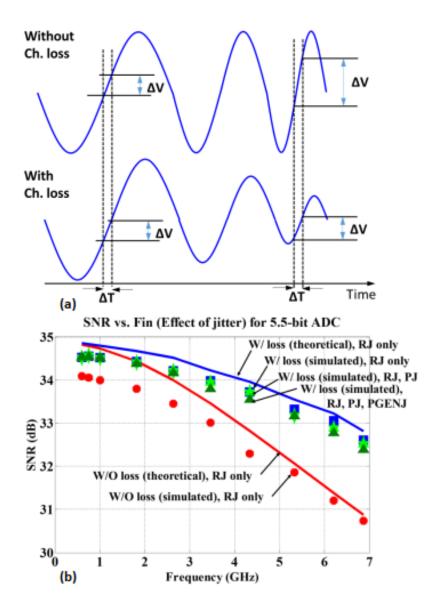

| Figure 3-10 : (a)Effect of timing noise in W/O and W/ loss channels (b) SNR penalty as a function   |

| of input frequency in the presence of jitter                                                        |

| Figure 3-11 : (a) TDC based timing recovery loop, (b) PAM 4 in the presence of ISI with edge        |

| distribution with and without ISI filter                                                            |

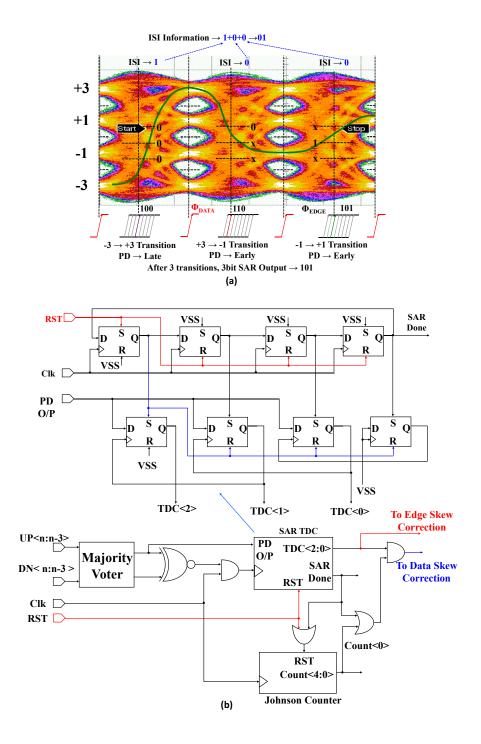

| Figure 3-12 : (a) SAR TDC operation in three consecutive cycles, and (b) Block diagram of SAR       |

| TDC                                                                                                 |

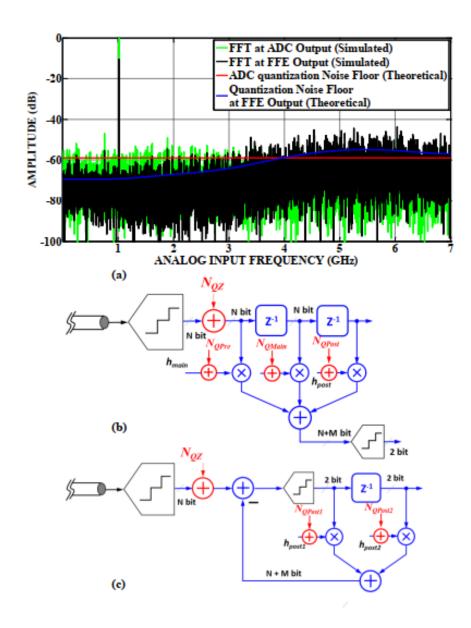

| Figure 3-13 : (a) Shaping of ADC quantization noise by FFE (theoretical & simulation), (b) ADC      |

| followed by FFE, and (c) ADC followed by DFE architecture                                           |

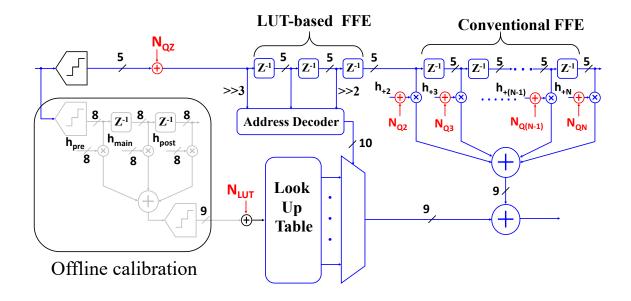

| Figure 3-14 : Proposed ADC-based digital receiver where first 3 taps are implemented using LUT      |

| and rest taps in conventional way. An offline higher resolution ADC and higher resolution FFE       |

| are used to prepare the LUT74                                                                       |

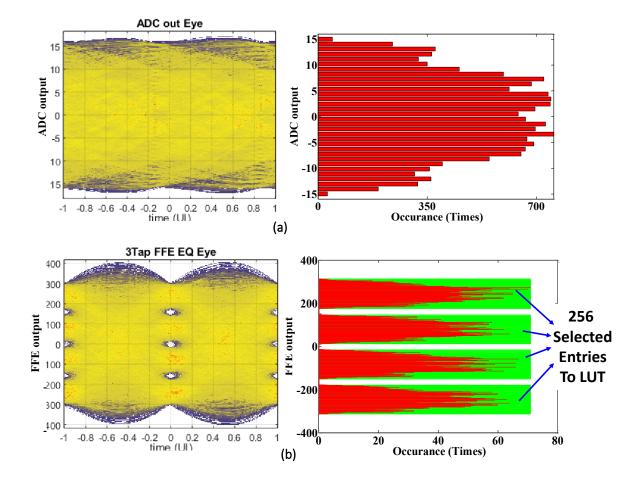

| Figure 3-15: (a) ADC output eye and distribution, (b) 3-tap digital FFE output eye and distribution. |

|------------------------------------------------------------------------------------------------------|

|                                                                                                      |

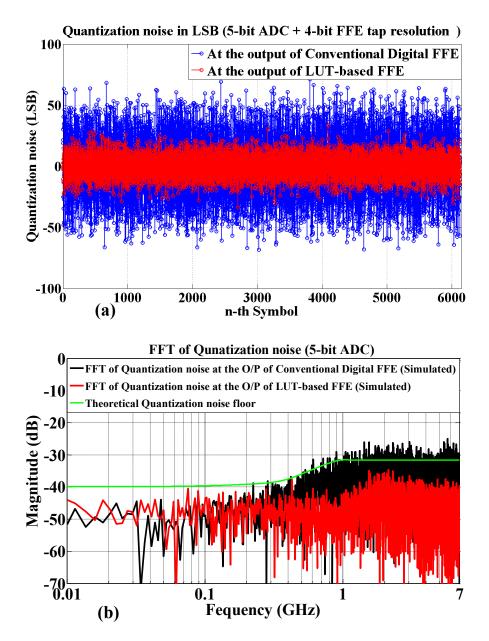

| Figure 3-16 : Performance comparison in terms of quantization noise between 3-tap conventional       |

| digital FFE and LUT-based FFE (a) Quantization noise transient, and (b) FFT of quantization noise    |

| at the output of the FFE with theoretical quantization noise floor. Here, ADC resolution is 5-bit.   |

|                                                                                                      |

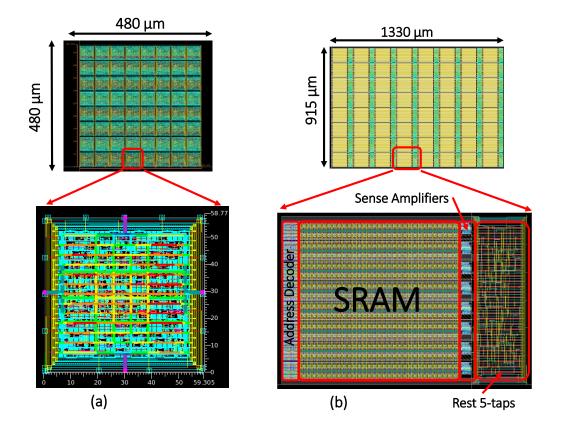

| Figure 3-17: Synthesized digital equalizer core for (a) conventional 8-tap FIR, and (b) 3-tap LUT-   |

| based followed by 5-tap conventional FIR                                                             |

| Figure 3-18 : Implemented prototype in 65nm CMOS 79                                                  |

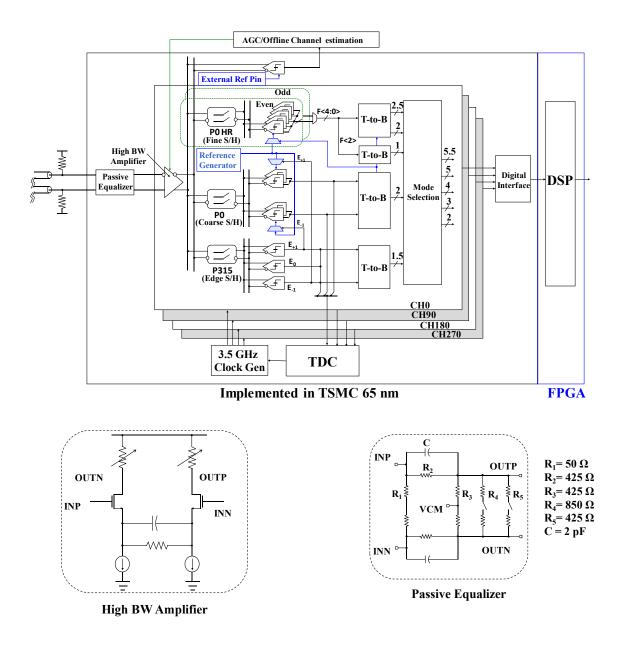

| Figure 3-19 : Block diagram of implemented digital receiver                                          |

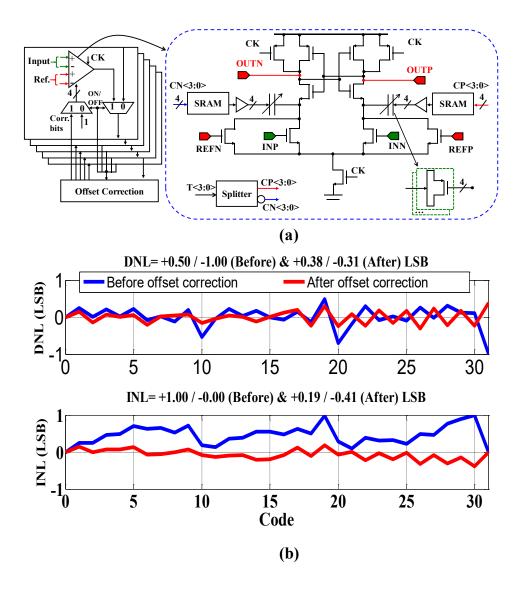

| Figure 3-20 : (a) Comparator with offset Correction, (b) measured INL/DNL of the ADC for 5-bit       |

| resolution                                                                                           |

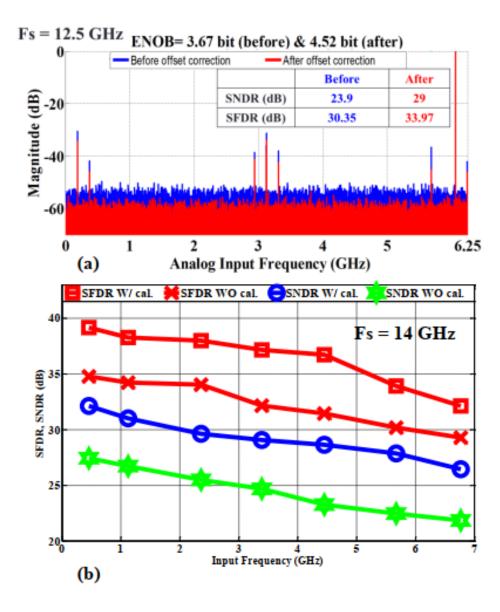

| Figure 3-21 : ADC Performance, (a) FFT at the ADC output w/ and wo offset correction @Fs=12.5        |

| GS/s, (b) SNDR & SFDR vs. input frequency $@$ Fs = 14 GS/s                                           |

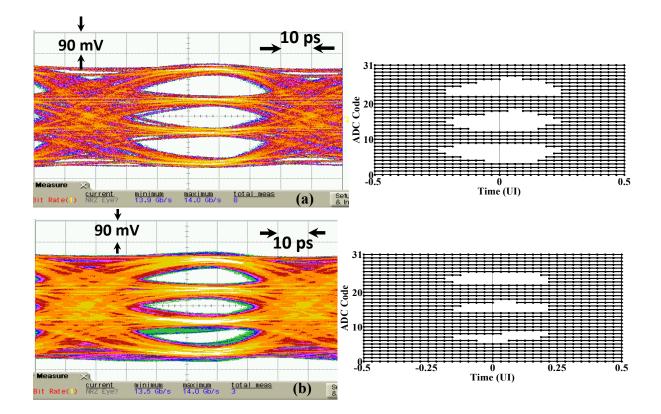

| Figure 3-22 : Input eye and digitally reconstructed eye generated from ADC output for (a) an open    |

| eye, and (b) a semi-open eye                                                                         |

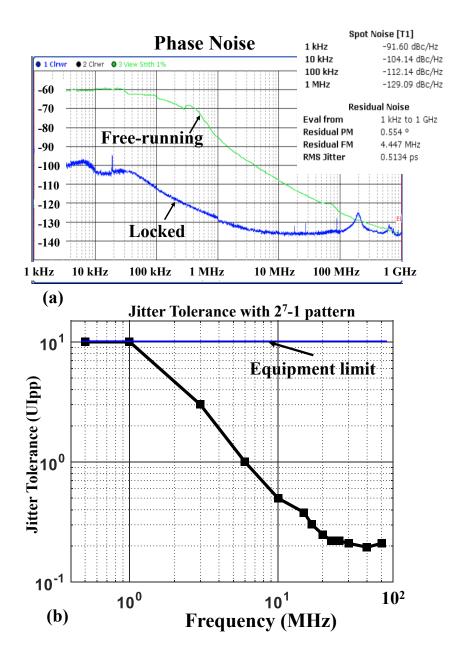

| Figure 3-23 : (a) Phase noise plot of recovered clock, and (b) Jitter tolerance @ 28 Gb/s with       |

| BER< 10 <sup>-9</sup>                                                                                |

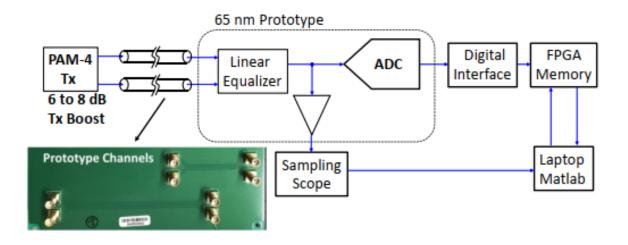

| Figure 3-24 : Test setup for receiver characterization. The channels are the PCB traces of different |

| lengths                                                                                              |

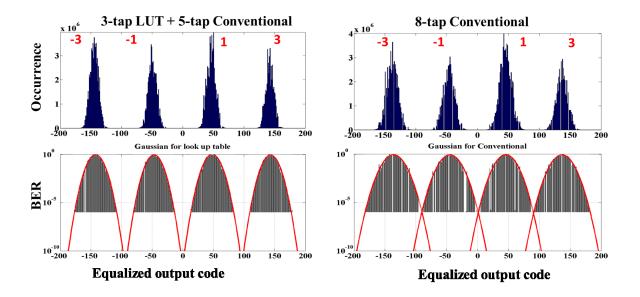

| Figure 3-25 : Link margin test at 28Gb/s for a 30 dB Channel where FFE is realized as (a) 3-tap      |

| LUT + 5-tap conventional, and (b) 8-tap conventional                                                 |

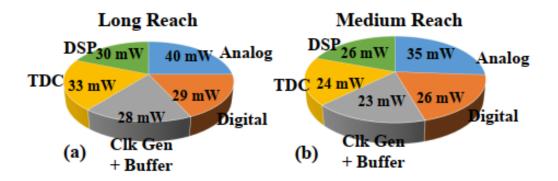

| Figure 3-26 : Power breakdown for (a) Long-reach channel, and (2) Medium-reach channel 87            |

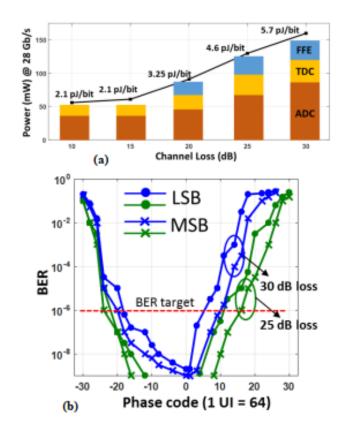

| Figure 3-27 : (a) Power consumption of the receiver for different channel losses, and (b) measured                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------|

| receiver BER for 25 dB and 30 dB loss channels                                                                                               |

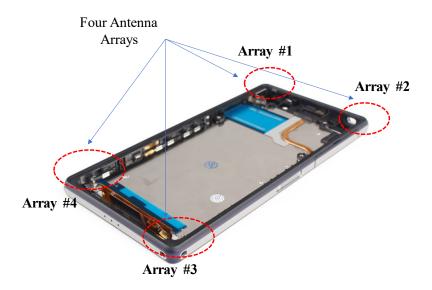

| Figure 4-1 : Placement of four antenna arrays in a mobile phone. Each antenna array consists of multiple individual antennas                 |

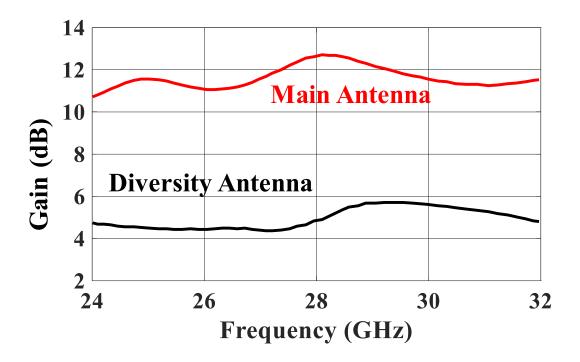

| Figure 4-2 : An antenna array gain plot                                                                                                      |

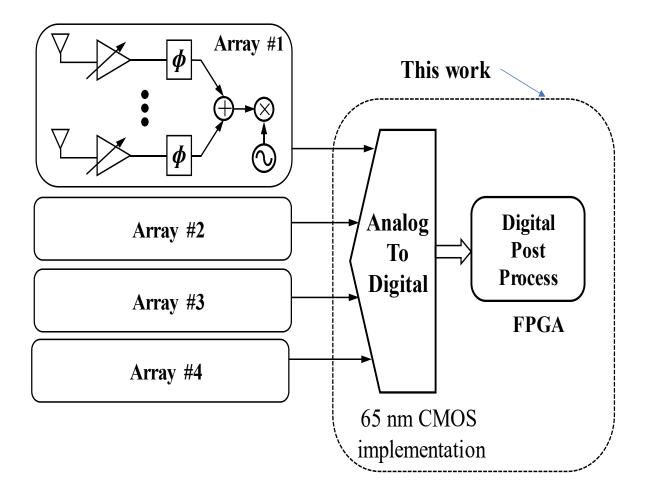

| Figure 4-3 : Hybrid beamforming technique and proposed solution for collaborative digitization of down converted signal                      |

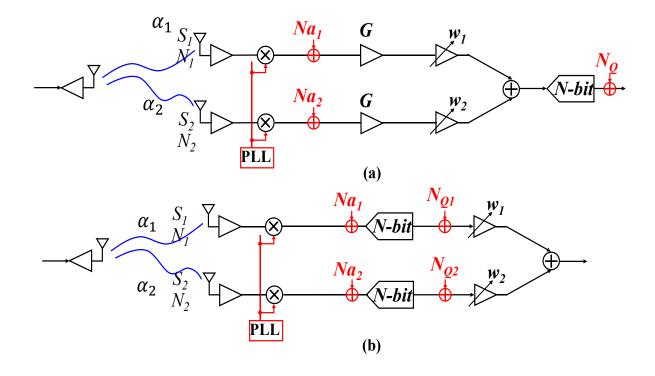

| Figure 4-4 : Architecture of a 2-channel (a) Analog, and (b) Digital beamforming with noise sources                                          |

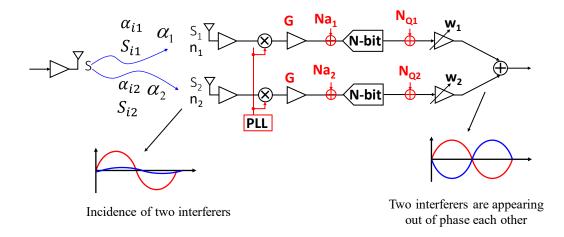

| Figure 4-5: Two channel with the presence of interferences                                                                                   |

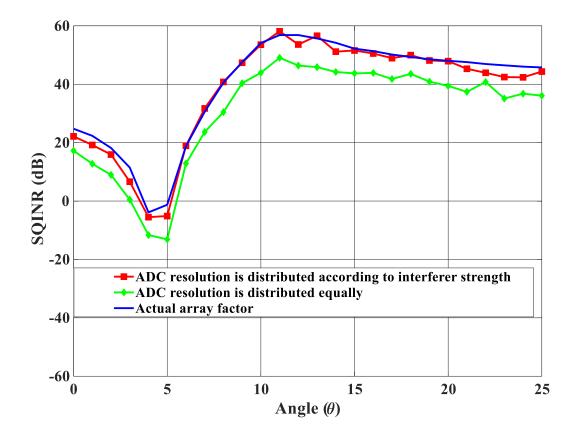

| Figure 4-6: SQINR vs. interference appearing angle                                                                                           |

| Figure 4-7: FFT at the output for the two cases                                                                                              |

| Figure 4-8 : A 4x11-bit 1 GS/s 40mW collaborative ADC in 65nm CMOS for a 4-cahnnel MIMO receiver                                             |

| Figure 4-9 : (a) Architecture of the phase alignment technique, and (b) Schematic diagram of the Gilbert Cell (GC) followed by an integrator |

| Figure 4-10 : Block diagram of the analog pre-processing with FFT simulation results, transfer curve, and AC response                        |

| Figure 4-11 :Noise model for (a) Conventional, and (b) Proposed front-end and the comparison with signal amplification using gain block      |

| Figure 4-12 :Test bench for comparator decision time simulation and decision time vs. input difference plot                                  |

| Figure 4-13 :Architecture of (a) Conventional switching SAR ADC, and (b) Monotonic switching SAR ADC                                         |

| Figure 4-14 :Block diagram of clock generation and Monte Carlo simulation 110                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

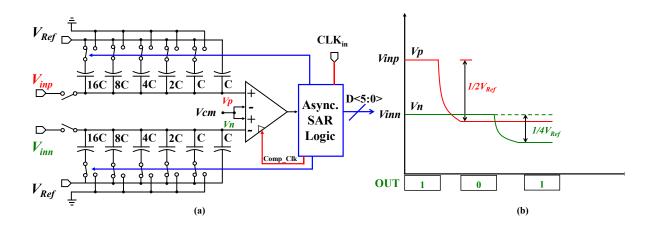

| Figure 4-15 : (a) Complete architecture of the implemented 6-bit monotonic SAR ADC, and (b)                                                                                                                                                  |

| Change of DAC voltage during SAR operation                                                                                                                                                                                                   |

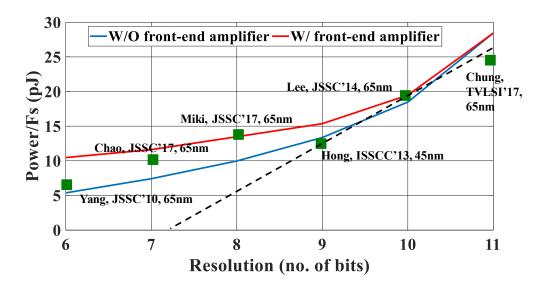

| Figure 4-16 : Power/Fs vs. resolution plot for a monotonic single-channel SAR ADC 115                                                                                                                                                        |

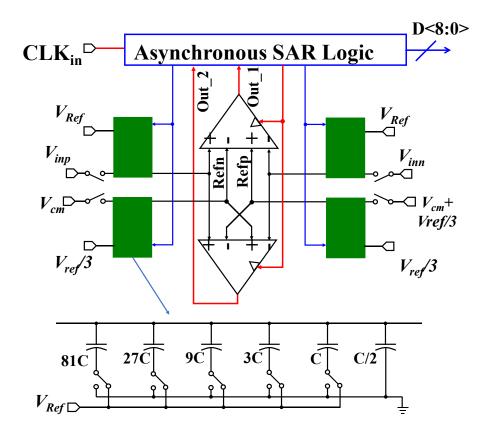

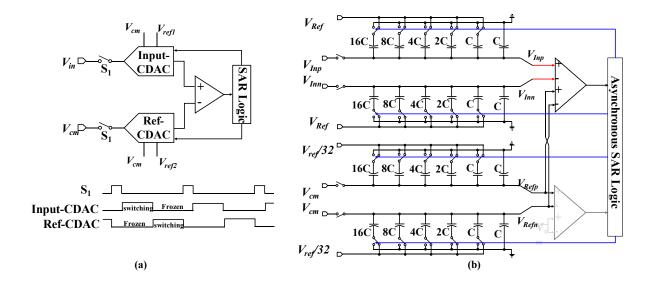

| Figure 4-17 : Architecture of the proposed 9-Bit ADC. The schematic of the capacitive DAC is symbolized as a green box                                                                                                                       |

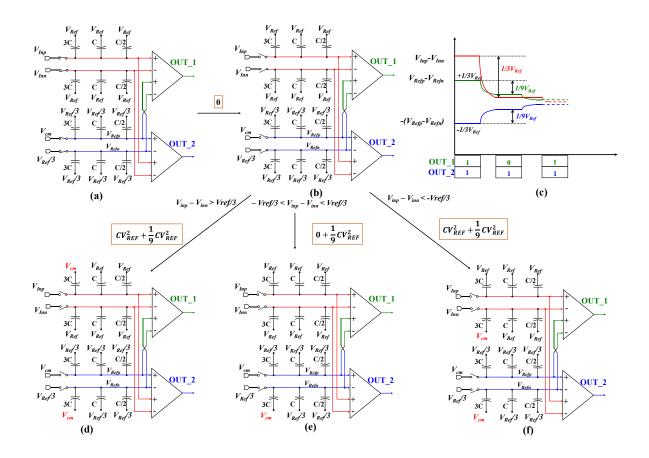

| Figure 4-18 : Switching operation of the proposed 9-bit ternary SAR ADC. (a) Input and reference sampling, (b) First stage comparison that utilizes the sampled references (no capacitor switching),                                         |

| (c) The change of DAC voltage during SAR operation, (d) Switching procedure when input is                                                                                                                                                    |

| greater that $V_{REF}/3$ at the first stage, (e) Switching procedure when input is between $-V_{REF}/3$ and $V_{REF}/3$ , and (f) Switching procedure when input is less that $-V_{REF}/3$                                                   |

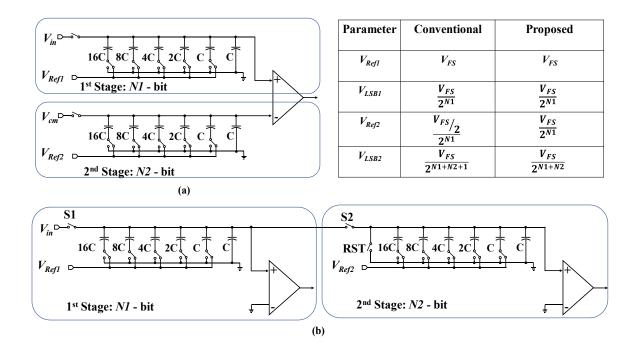

| Figure 4-19 : (a) Schematic and timing diagram of passive residue transfer that requires both RST and residue transfer pulse [147], [148], and (b) Omission of RST pulse by introducing ping-pong technique in the second stage [149], [150] |

| Figure 4-20 : (a) Proposed two-step SAR ADC that is exempt from both RST and residue transfer                                                                                                                                                |

| pulse, and (b) Schematic diagram of the differential implementation of the proposed 11-bit two-<br>step SAR ADC                                                                                                                              |

| Figure 4-21 : Residue transfer in two-step SAR ADC architecture (a) Proposed, and (b)<br>Conventional                                                                                                                                        |

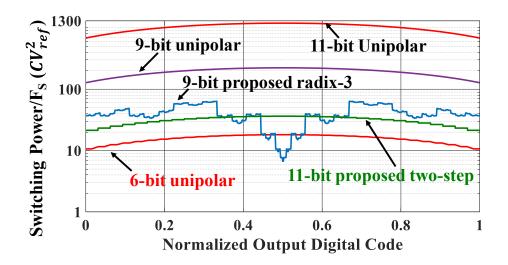

| Figure 4-22 : Comparison of the switching energy vs. normalized digital code for the different resolution of conventional monotonic SAR ADCs and the proposed ADCs                                                                           |

| Figure 4-23 : Reconfigurablity of 8 6-bit SAR ADCs to achieve variable resolution ADC 127                                                                                                                                                    |

| Figure 4-24 : Reference voltage is applied externally, and low output impedance reference buffer is used to drive the CDAC load                                                                                                              |

| Figure 4-25 : Test setup. Here, scenario of the diversity in the received signals is emulated 130                                                                                                                                            |

| Figure 4-26 : Asynchronous clock generation and timing diagram 130                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|

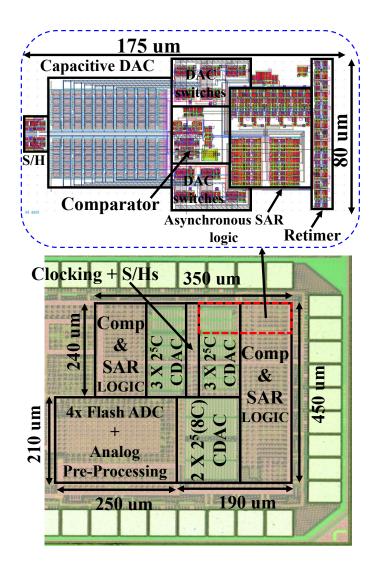

| Figure 4-27 : Implemented prototype in TSMC 65nm 131                                                                                                       |

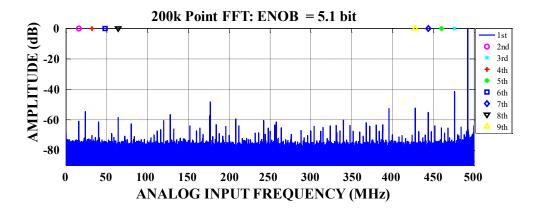

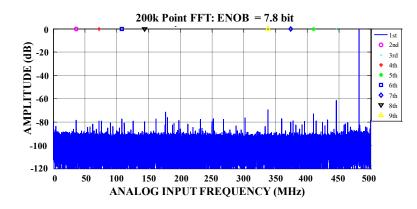

| Figure 4-28 : Measured 6-bit ADC spectra at 1GS/s with a Nyquist input                                                                                     |

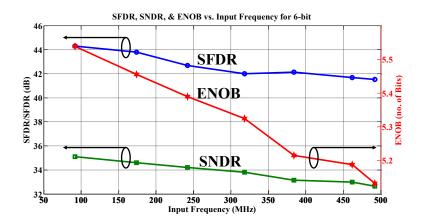

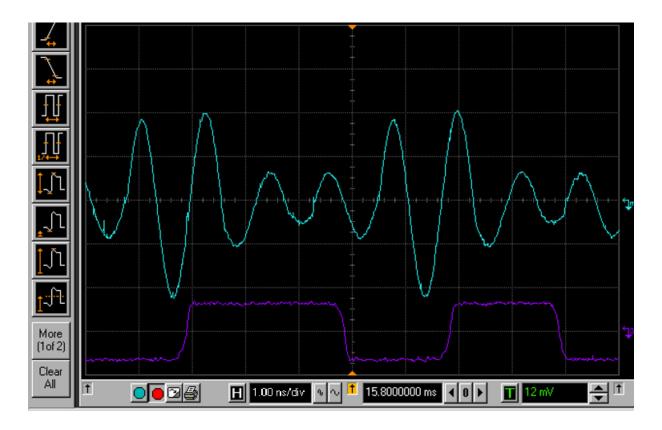

| Figure 4-29 : Measured 6-bit SNDR/SFDR, and ENOB vs. input frequency at 1GS/s 132                                                                          |

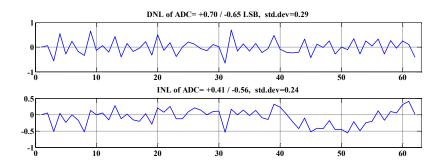

| Figure 4-30 : Measured 6-bit ADC DNL/INL profiles                                                                                                          |

| Figure 4-31 : Measured 9-bit ADC spectra at 1GS/s with a Nyquist input                                                                                     |

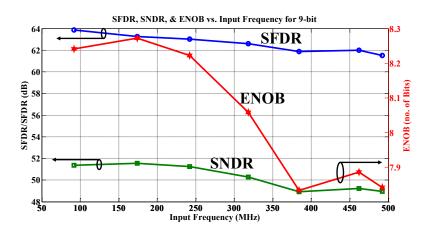

| Figure 4-32 : Measured 9-bit SNDR/SFDR, and ENOB vs. input frequency at 1GS/s 133                                                                          |

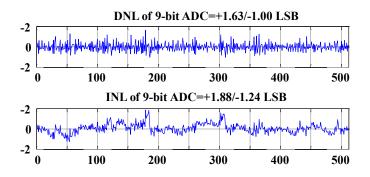

| Figure 4-33 : Measured 9-bit DNL/INL profiles                                                                                                              |

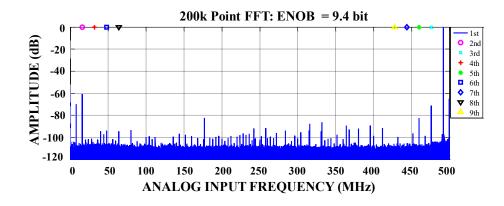

| Figure 4-34 : Measured 11-bit ADC spectra at 1GS/s with a Nyquist input                                                                                    |

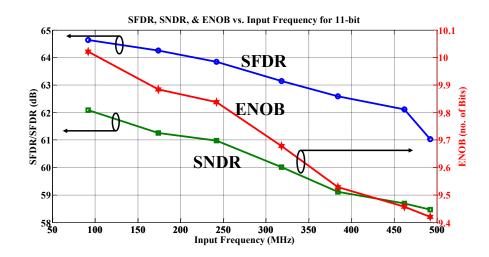

| Figure 4-35 : Measured 11-bit SNDR/SFDR, and ENOB vs. input frequency at 1GS/s                                                                             |

| Figure 4-36 : Measured 11-bit DNL/INL profiles                                                                                                             |

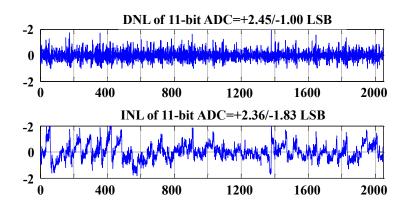

| Figure 4-37 : (a) Schematic of 6/9-Bit ADC and (b) Simulation of 6-bit to 9-bit switching (decided by the first stage flash ADC)                           |

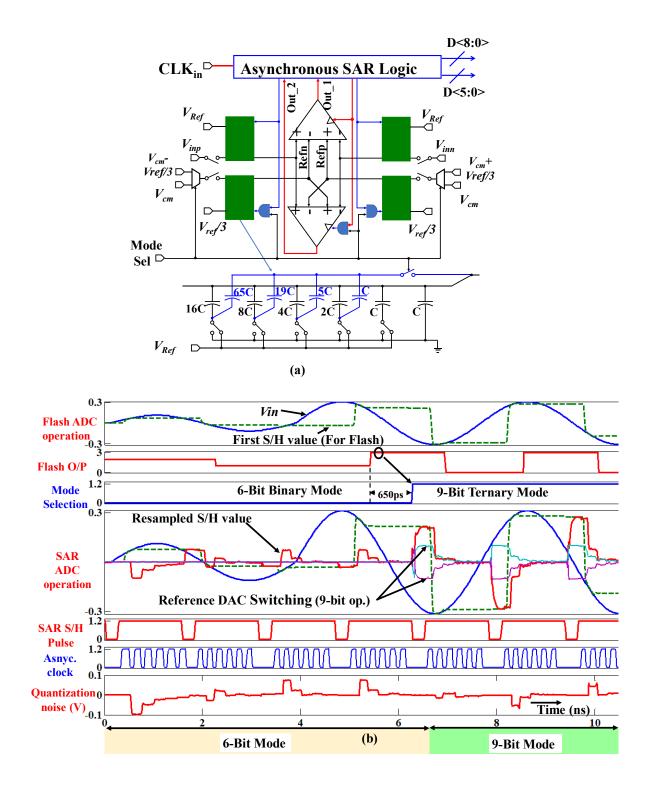

| Figure 4-38 : Measured mode switching output 140                                                                                                           |

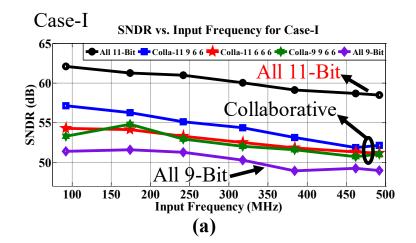

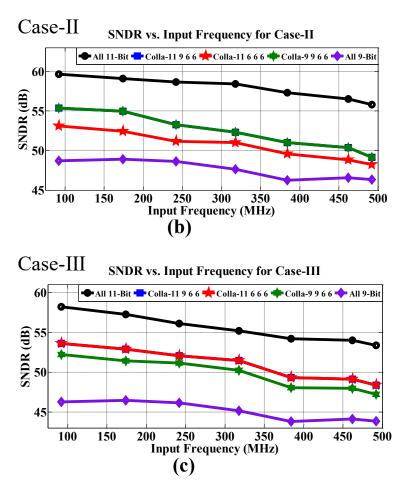

| Figure 4-39 : Measured SNDR vs. input frequency and comparison with all 11-bit and all 9-bit implementations for (a) CASE I, (b) CASE II, and (c) CASE III |

| Figure 4-40 : Measured combined ADC spectra at 1GS/s with a Nyquist input for CASE I 142                                                                   |

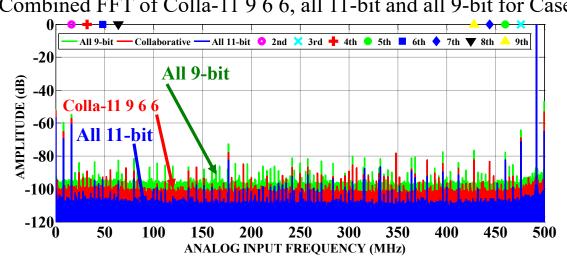

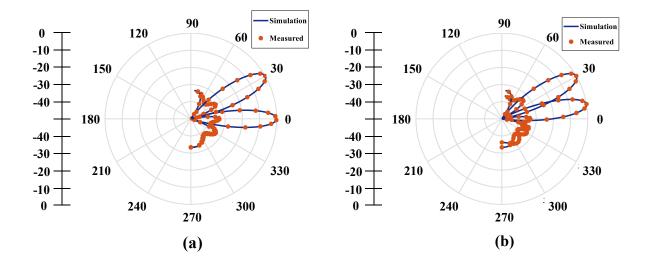

| Figure 4-41 : Measured beamforming for a single lobe at 00 (a) and 450 (b), respectively 143                                                               |

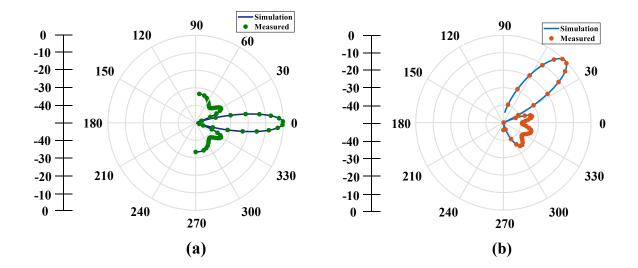

| Figure 4-42 : Measured beamforming for two lobes at $(0^{\circ} \& 30^{\circ})$ (a) and $(15^{\circ} \& 30^{\circ})$ (b), respectively.                    |

## List of Tables

| Table 1-1: Comparison table for different kind of encoder used in Flash ADC                     |

|-------------------------------------------------------------------------------------------------|

| Table 1-2: Power efficiency comparison of the different architectures of Nyquist ADCs           |

| Table 3-1 : Coarse Comparator Reference Selection budget                                        |

| Table 3-2 : Fine Comparator Reference Selection budget                                          |

| Table 3-3 : Resources allocation based on resolution                                            |

| Table 3-4 : Summary of PD Logic and ISI Filtering    71                                         |

| Table 3-5 : DSP comparison    77                                                                |

| Table 3-6 : COMPARISON WITH STATE-OF-ART    88                                                  |

| Table 4-1 : Average Switching Energy Associated With Different Resolution Of Conventional       |

| Monotonic SAR ADCs And Compares With The Proposed ADCs 124                                      |

| Table 4-2 : Reconfigurability Options And The Power Savings For Each Case 126                   |

| Table 4-3 : Performance comparison of 6-bit ADC                                                 |

| Table 4-4 : Performance comparison of 9-bit ADC                                                 |

| Table 4-5 : Performance comparison of 11-bit ADC                                                |

| Table 4-6 : Performance summary and comparison with all 11-bit & all 9-bit implementation 144   |

| Table 4-7 : Comparison of proposed architecture with 4×11-bit and 4x8-bit architecture in terms |

| of area, power, and SNDR 144                                                                    |

| Table 5-1 : Comparison of the proposed ADC with the state-of-the-art ADCs designed for ADC-     |

| based receiver                                                                                  |

## Acronyms

| ADC  | Analog-to-Digital Converter    |  |

|------|--------------------------------|--|

| AWG  | Arbitrary Waveform Generator   |  |

| BBPD | Bang-Bang Phase Detector       |  |

| BER  | Bit Error Rate                 |  |

| CDR  | Clock and Data Recovery        |  |

| DAC  | Digital-to-Analog Converter    |  |

| DDJ  | Data-dependent Jitter          |  |

| DFE  | Decision Feedback Equalizer    |  |

| DFS  | Dynamic FullScale              |  |

| DNL  | Differential Non-linearity     |  |

| DSP  | Digital Signal Processing      |  |

| ENOB | Effective Number of Bits       |  |

| ERBW | Effective Resolution Bandwidth |  |

| FFE  | Feed-Forward Equalizer         |  |

| FIR  | Finite Impulse Response        |  |

| FPGA | Field Programmable Gate Arrays |  |

| IC   | Integrated Circuits            |  |

| ISI  | Inter-Symbol Inteference       |  |

| INL  | Integral Non-Linearity         |  |

| LEQ    | Linear Equalizer                      |  |

|--------|---------------------------------------|--|

| LUT    | Look-up Table                         |  |

| MIMO   | Multiple-Input Multiple-Output        |  |

| MRC    | Maximal Ratio Combining               |  |

| PAM    | Pulse Amplitude Modulation            |  |

| PD     | Phase Detector                        |  |

| SAR    | Successive Approximation Register     |  |

| SFDR   | Spurious-Free Dynamic Range           |  |

| SNDR   | Signal-to- Noise-and-Distortion ratio |  |

| SNR    | Signal-to-Noise Ratio                 |  |

| TDC    | Time-to-Digital Converter             |  |

| T-to-B | Thermometer-to-Binary                 |  |

| VCO    | Voltage Controlled Oscillator         |  |

# Chapter 1 Analog-to-Digital Converter (ADC)

### 1 INTRODUCTION

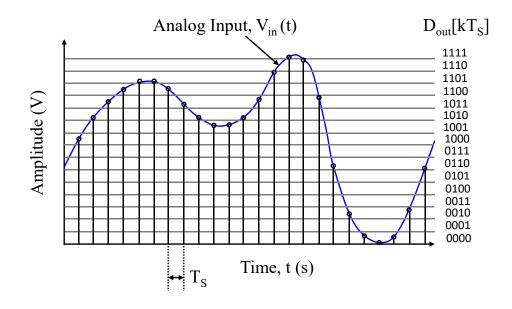

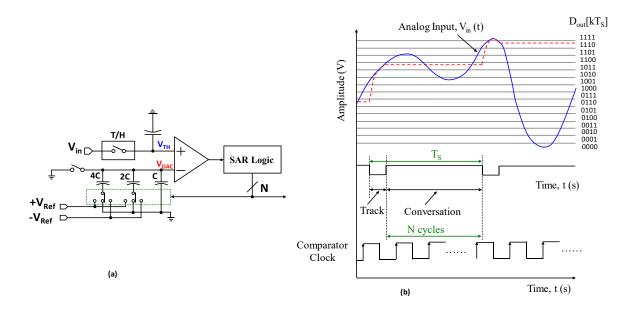

Analog-to-digital converters (ADCs) are the circuits that sample continuous-time signals or analog signals and convert them into digital codes. They provide the means of interfacing between the analog and digital domains. They divide the analog input range into a finite number of discrete levels (quantization levels) as illustrated in Figure 1-1. For a 4-bit digitization, the total number of intervals is  $2^4 = 16$ . When an analog input exceeds a quantization level, it returns the corresponding digital code. Therefore, the input of the converter is a real-valued continuous-time signal,  $V_{in}(t)$ , and the output is a discrete-time digital code,  $D_{out}[kT_S]$ , where  $T_S$  is the sampling period and k is the index of the sample.

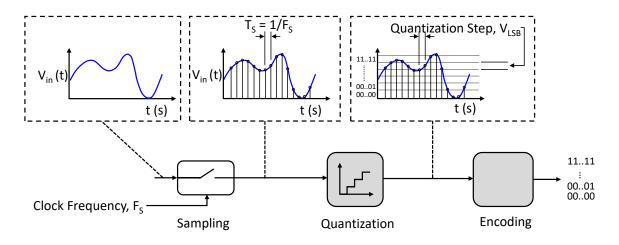

The operating principle of ADCs is illustrated in Figure 1-2 [1]. At first, the analog input signal is sampled by a sample-and-hold (S/H) circuit at a sampling frequency of  $F_S$  (=1/ $T_S$ ) Hz. The sampled value is a discrete-time signal which is then quantized by the quantizer. The output of the quantizer represents the approximate quantization level of the sampled value. Finally, the encoder transforms the quantization level into a digital code. For a N-bit ADC, the digital output is ranging from 0 to  $2^{N}$ -1, and each digital code is a vector of N dimension with the entries '0' and '1'.

The S/H operates at a clock frequency of  $F_S$  Hz, and it requires two phases. It tracks the analog input in the first phase and holds the sampled value in the second phase. According to the Nyquist theorem, as long as the input frequency is less than  $F_S/2$  Hz, the input signal can be recovered without any loss of information in it [2].

Based on the sampling frequency, ADCs can be categorized into two groups: the Nyquist rate and the oversampling converters. Nyquist rate converters consider that the maximum frequencies of the input signals are slightly less than the Nyquist frequency,  $F_{NYQUIST} = F_S/2$  Hz. When the maximum frequency of input signals is more than the Nyquist frequency, the Nyquist converter cannot convert the signals properly due to signal distortion or aliasing. So, the frequencies above the Nyquist frequency must be attenuated by using a low-pass anti-aliasing filter. For the

Figure 1-1 : The concept of analog-to-digital conversion.

Figure 1-2 : Block diagram and operation of ADC.

oversampling converters, the maximum frequency of the input signals is much lower than the Nyquist frequency.

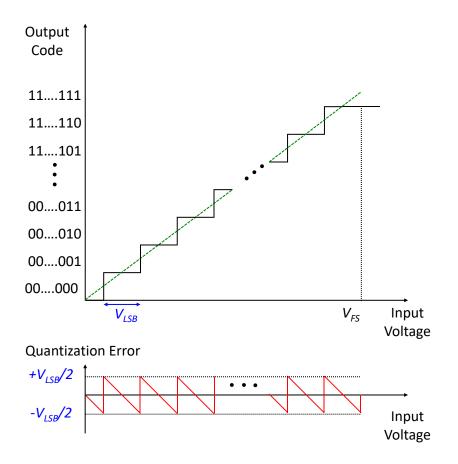

An N-bit ADC divides the full-scale input into  $2^{N}$  discrete levels (Figure 1-3), where the step size between two consecutive levels is equal to  $V_{LSB} = V_{FS}/2^{N}$ . When the analog sampled value is between  $n \cdot V_{LSB}$  and  $(n+1) \cdot V_{LSB}$ , it is mapped to a digital code, n, where  $0 \le n \le 2^{N}$ -1. Therefore, it is obvious that there is an irreversible error—a quantization error—which prohibits the signal

Figure 1-3 : ADC quantization levels and quantization error.

from being exactly reconstructed. The maximum quantization error is  $|e_q| = V_{LSB}/2$  as illustrated by the transfer curve of the quantization error in Figure 1-3.

### 1.1 FLASH ADC

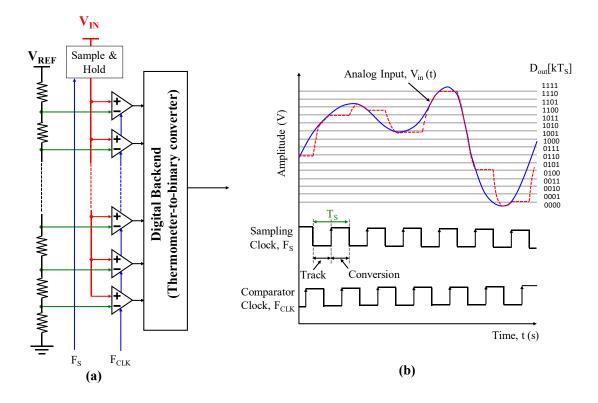

Flash ADCs are the highest speed ADC [3], [4]. Figure 1-4(a) shows the architecture of a flash ADC. The flash ADC digitizes the analog input by placing a comparator for each quantization level. Therefore, for an N-bit flash ADC, it requires a resistor ladder of  $2^{N}$  equal resistors, a  $2^{N}$  - 1 number of comparators, and a backend digital decoder. The comparator array provides a thermometric output that is proportional to the analog input, and the decoder converts the output to a binary code.

Figure 1-4 : (a) Architecture of the Flash ADC, (b) Timing diagram of the Flash ADC operation.

Figure 1-4(b) shows the operational timing diagram of the Flash ADC. Here, the frequencies of the sampling clock (Fs) and the comparator clock ( $F_{CLK}$ ) are the same. However, the comparator clock is delayed by a significant amount to allow proper settling for the sample-and-hold (S/H) operation. During the low level of the sampling clock, the S/H circuit is closed. At that time, the output of the S/H circuit tries to follow the input signal, and this time duration is known as the tracking phase. At the rising edge of the sampling clock, the S/H opens and holds the sampled value for the next half cycle. Therefore, during the high level of the sampling clock, the S/H circuit holds the sampled value, and this time duration is known as the hold phase. Rising edge of the comparator clock appears after a significant time of the sampling clock, and the comparator starts to resolve the sampled input. The outputs of the comparator array are thermometric, and a thermometric-to-binary decoder is used to generate the binary code.

Since, all the comparators are fired at the same time, the digitization of the sampled value is performed in one cycle. Therefore, the Flash ADC becomes the fastest ADC.

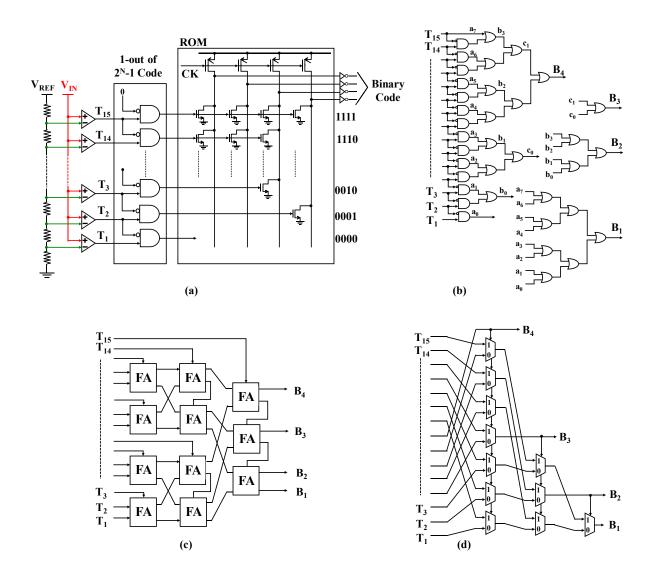

Figure 1-5 : Different types of encoders for Flash ADC, (a) ROM-based, (b) Fat tree, (c) Wallace Tree, and (d) MUX-based.

#### 1.1.1 Decoder

For high-speed application, flash architecture is often used [5], [6]. However, it requires  $2^{N}$ -1 number of comparators, where N indicates the resolution of the ADC. Here, one input of each comparator is connected to the input and another to a unique reference voltage. Therefore, it requires  $2^{N}$ -1 number of reference levels which is usually generated by a resistive ladder. When the input voltage is greater than the reference voltage of a comparator, the output is high, otherwise, the output is low. As a result, for a given analog input, the outputs of the comparators having

|              | Unit Components | Count                                                          |

|--------------|-----------------|----------------------------------------------------------------|

| Wallace Tree | Full Adder      | $\sum_{q=1}^{N} (q-1) \cdot 2^{N-q}$                           |

| MUX-based    | 2:1 MUX         | $\sum_{q=1}^{N-1} (2^{N-q} - 1)$                               |

| Fat-Tree     | AND, OR         | AND: $2^{N-1} *$<br>OR: $2 \cdot \sum_{q=1}^{N-1} 2^{N-q} - 1$ |

| ROM-based    | AND, NMOS, PMOS | AND: $2^{N-1}$ *<br>NMOS: N · $2^{N-2}$<br>PMOS: N             |

Table 1-1: Comparison table for different kind of encoder used in Flash ADC

\* Actual number of AND gates is  $2^{N-2}$ . However, for equal loading to each comparator, the number of AND gates is made equal to the number of comparators.

reference levels lower than the input are high and others are low, which is a thermometric representation of input. A Thermometer-to-Binary (T-to-B) decoder is required to convert the 2<sup>N</sup>-1 thermometer codes into an N-bit binary code. Several techniques have been presented for thermometer to binary conversion such as Wallace tree-based decoder [7], [8], gray or binary ROM-based decoder [9], [10], Fat tree-based decoder [11]–[13], and MUX-based decoder [14], [15]. Figure 1-5 shows the implementation of different types of encoders for Flash ADC. Table 1-1 summarizes the key blocks for the implementation of each encoder and the respective hardware count.

The total power of a single channel flash ADC includes the comparator power, comparator clocking power and the Thermometer-to-binary(T-to-B) encoder logic power. If a Wallace tree encoder is used, it requires  $2^{N} - N - 1$  number of full-adder cells [16]. Thus, the total power associated with an N-bit single channel flash ADC is the following:

$$P_{FLASH,u} = (2^{N} - 1) \cdot (P_{C,u} + P_{CK,u}) + (2^{N} - N - 1) \cdot P_{LG,u}$$

(1.1)

where  $P_{C,u}$  is the unit comparator power,  $P_{CK,u}$  is the unit clocking power for each comparator, and  $P_{LG,u}$  is the full-adder power.

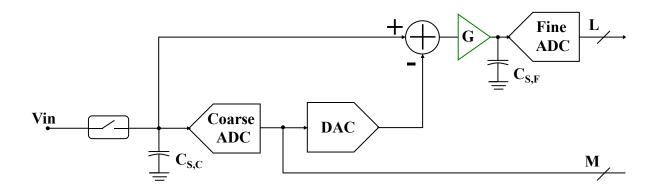

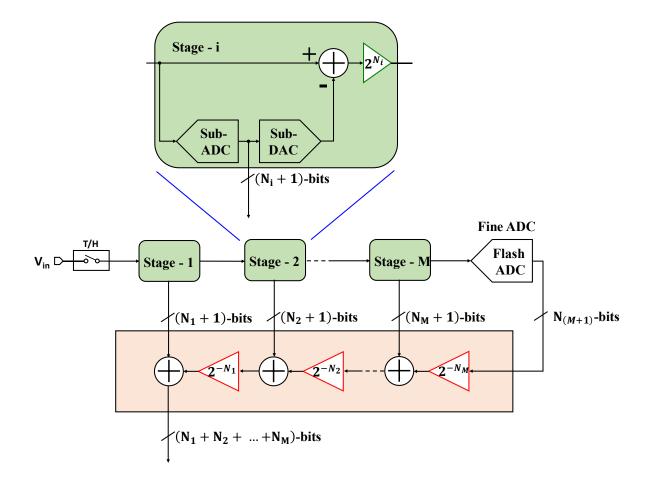

### 1.2 Two-Step Flash ADC

In the flash ADC architectures, it achieves the highest operating speed; however, its power dissipation, area, and input capacitance grow exponentially with the resolution [17]. Because the total number of comparators in the FLASH ADCs exponentially increases with the number of bits. To alleviate the exponential trade-off relationship between the power and the number of bits, two-step FLASH ADC can be introduced.

Figure 1-6 shows the architecture of a two-step Flash ADC [18]. It consists of a coarse flash ADC stage to resolve the M-bit MSBs and a fine flash ADC stage to resolve the remaining L-bit LSBs. A DAC converts the coarse flash ADC output to an equivalent analog value and a subtractor is used to subtract the equivalent analog value from the sampled input signal and transfer the residue to the fine ADC. Moreover, an inter-stage gain amplifier between the subtractor and the fine flash ADC is necessary.

Figure 1-7a and Figure 1-7b shows the working principle of a 4-bit two-step flash ADC. Here, 2bit MSBs are resolved by the coarse ADC, and 2-bit LSBs by the fine ADC. At the coarse ADC, it requires three comparators ( $2^2$ -1) to resolve the 2-bit MSBs. Since the input is between first and second comparator, the output of the coarse ADC is 01. After generating the residue and multiplied by  $2^{M}$  (=4), the residue is transferred to the fine ADC. At the fine ADC, the residue resides between second and third comparator and the fine ADC resolves it as 10. Thus, the 4-bit output of the input signal is 0110. By amplifying the residue by  $2^{M}$ , the dynamic range for the fine ADC becomes equal to the dynamic range of the coarse ADC. However, a precise gain controller is required for the inter-stage gain amplifier. We can get rid of the gain amplifier by placing the fine flash ADC at the interval of coarse ADC where the input signal resides. In that case, it is known as a subrange ADC where residue is amplified by 1.

Although two-step and subranging ADCs provide a low power solution to implement high-speed ADCs, there are some disadvantages to them. There is an unavoidable delay to the final digital output due to the two-step operation. On top of this, it is mandatory to have a front-end S/H circuit

Figure 1-6 : Two-step Flash ADC.

Figure 1-7 : Two-step Flash ADC working principle. (a) When residue is multiplied by  $2^{M}$ , (b) when residue is multiplied by 1.

for both subranging and two-step ADCs to assist transferring the residue to the fine stage. The gain of the residue amplifier needs to be precise, otherwise the generated residue voltage might not fit or surpass the dynamic range of the fine ADC. As a result, the residue voltage will be erroneous and there will be severe linearity issues such as non-monotonicity or missing-codes for the overall transfer curve of the ADC. Several techniques such as digital background calibration of the ADC output by applying inverse of the gain error [19] or provide additional resolution to the fine ADC (known as redundancy) can mitigate the range-mismatch issue. The DAC non-ideality can also cause errors for the LSBs in the fine ADC conversion.

The benefit of the two-step ADC is that it largely reduces the number of comparators. The total number of comparators used in a two-step flash is only  $2^{M} + 2^{L}-2$  instead of  $2^{M+L}-1$  comparators in a straightforward flash ADC.

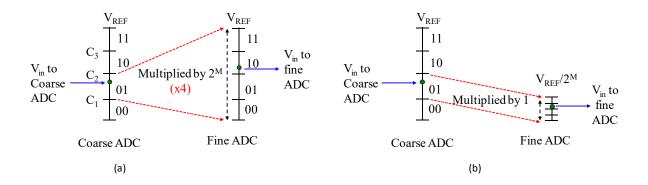

### 1.3 Pipelined ADC

Figure 1-8 : Pipelined ADC architecture.

A pipelined ADC is an extended version of the two-step ADC, where a high-resolution conversion is achieved by breaking into multiple steps with the smaller resolution. As a result, the pipelined ADCs can perform high-resolution operation at higher conversion rates. The architecture of a pipelined ADC is shown in Figure 1-8 that includes a S/H circuit, a series of M coarse converters, followed by a fine converter. The coarse converters are similar in structurally, which consists of a  $(N_i+1)$ -bit sub-ADC, a  $(N_i+1)$ -bit sub-DAC, a subtractor, and an amplifier with a gain factor of  $2^{N_i}$ . Each stage performs a coarse converter. Since the analog signal and generates a residue signal which is an amplified version of the quantization error. At the end, there is a  $N_{(M+1)}$ -bit flash ADC which works as the fine converter. Since the analog input signal gets amplified along the coarse converter stages, the digital output is de-scaled accordingly to generate the final digital code.

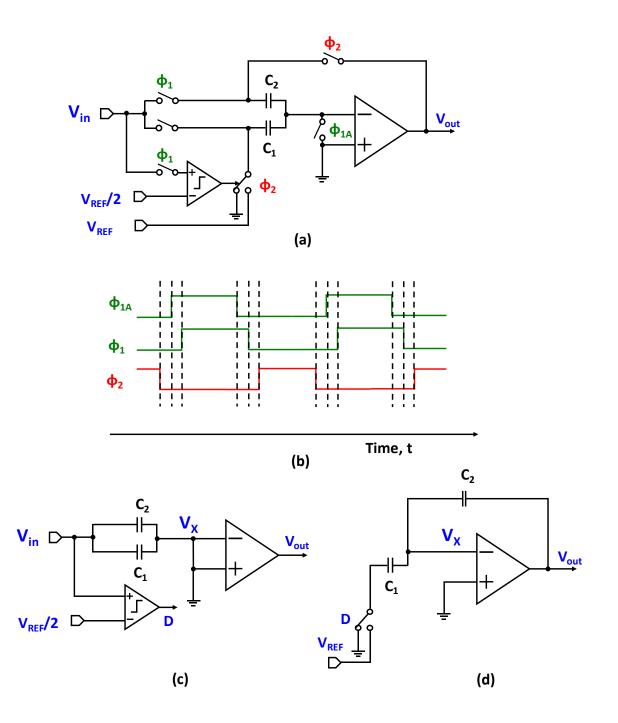

Figure 1-9 : (a) Architecture of a multiply-by-two switched-capacitor circuit used as a MDAC in pipelined ADC state, (b) Timing diagram of the operation, (c) the operation of the sampling, and (d) the operation of residue-amplification.

The building block of the n<sup>th</sup>-stage of the pipelined ADC includes a S/H, a sub-ADC, a sub-DAC,

a subtraction circuit and a residue amplifier as shown in Figure 1-8. The operations of DAC, subtraction and residue amplification are usually realized using a multiplying DAC (MDAC) which is a single switched-capacitor circuit [20]. Typically, the sub-ADC is realized using a flash ADC, but not limited to.

The single ended implementation of an 1-bit/stage (1 bit is resolved per stage) MDAC is shown in Figure 1-9a. The MDAC is a switched-capacitor circuit and it requires two phases of operation: a sampling phase ( $\phi_1$ ) and a residue-amplification phase ( $\phi_2$ ). Figure 1-9b shows the timing diagram associated with the two phases of operation. In the sampling phase (Figure 1-9c), the analog input is sampled on the input capacitors, C<sub>1</sub> and C<sub>2</sub>. At the same time, the sub-ADC samples the analog input on the comparator's input to perform the 1-bit digitization. Note that a single comparator is required to perform the 1-bit digitization. At the end of the sampling phase, the 1-bit output, denoted by D, is readily available. If the sampled input is greater than the half of the *V<sub>REF</sub>*, *Vin* > *V<sub>REF</sub>/2*, the output of the comparator, D, is 1, otherwise, the output is 0. After sampling the input, the total charge associated with the capacitors, C<sub>1</sub> and C<sub>2</sub>, is defined as:

$$Q_1 = V_{in} \cdot (C_1 + C_2) \tag{1.2}$$

In the residue-amplification phase (Figure 1-9d), one of the capacitors,  $C_1$ , is either connected to the ground (when D = 0) or the  $V_{REF}$  (when D = 1) and the other capacitor,  $C_2$ , is connected to the output. At this phase, the total charge associated with the capacitors,  $C_1$  and  $C_2$ , is defines as:

$$Q_2 = V_{out} \cdot C_2 + D \cdot V_{REF} \cdot C_1 \tag{1.3}$$

According to the conservation of the charge, we can write  $Q_1 = Q_2$ . Therefore, by equating, eq. (1.2) and eq. (1.3), the output of the MDAC becomes:

$$V_{out} = V_{in} \cdot \frac{C_1 + C_2}{C_2} - D \cdot V_{REF} \cdot \frac{C_1}{C_2}$$

(1.4)

For the 1-bit/stage pipelined ADC, the gain of the residue amplifier needs to be  $2^1 = 2$ . To achieve the such gain requirement, the both capacitors should be equal, i.e.,  $C_1 = C_2 = C$ . As a result, the eq. (1.4) becomes

Figure 1-10 : (a) A residue plot considering ideal behavior, (b) A residue plot considering capacitor mismatch, and (c) A residue plot considering finite op-amp gain and comparator offset.

$$V_{out} = 2 \cdot V_{in} - D \cdot V_{REF} \tag{1.5}$$

The output of the n<sup>th</sup>-stage,  $V_{out}$ , is a function of the output of the previous stage,  $V_{in}$ , and the reference voltage,  $V_{REF}$ . Based on the comparator decision, D, the relationship can be expanded as

$$V_{out} = f(V_{in}, V_{REF}) = V_{RES} = \begin{cases} 2 \cdot V_{in} & \text{, when } V_{in} < V_{REF}/2 \\ 2 \cdot V_{in} - V_{REF} & \text{, when } V_{in} > V_{REF}/2 \end{cases}$$

(1.6)

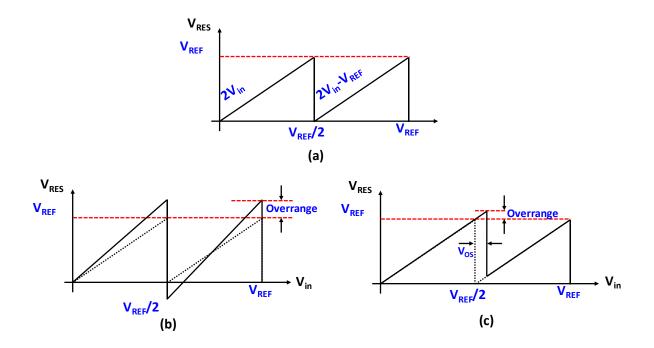

Figure 1-10a shows the plot for the  $f(V_{in}, V_{REF}) = V_{RES}$ . When  $V_{in} < V_{REF}/2$ , the comparator output is 0. In this case, the residue,  $V_{RES}$ , is the twice the input voltage,  $V_{RES} = 2 \cdot V_{in}$ . When  $V_{in} > V_{REF}/2$ , the comparator output is 1. In this case, the residue,  $V_{RES}$ , is the subtraction of the twice the input voltage and the reference voltage,  $V_{RES} = 2 \cdot V_{in} - V_{REF}$ .

Let's consider the MDAC performance under the sources of error. The slope of the residue plot will be changed under the presence of capacitor mismatch (Figure 1-10b), and finite gain of the

op-amp (Figure 1-10c). In the presence of the comparator offset,  $V_{OS}$ , the decision point shifts away from  $V_{in} = V_{REF}/2$  (Figure 1-10c). For both capacitor mismatch, and finite op-amp errors, the residue might go beyond the input dynamic range of the next stage which is known as "residue over-range". By shifting the decision point from  $V_{in} = V_{REF}/2$  due to the comparator offset also exhibit the "residue over-range", sometimes even more.

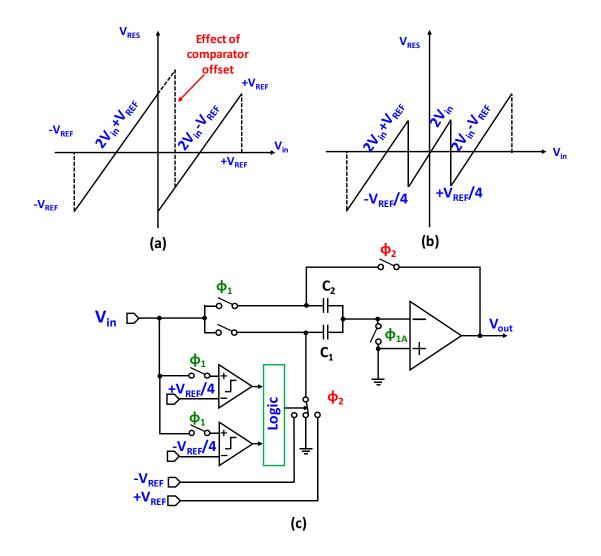

For the better explanation of the effect of the comparator offset in the MDAC, a residue plot for the differential implementation is shown in Figure 1-11a. In this case, the comparator's threshold is set to 0 V. Therefore, the relationship between  $V_{RES}$  and  $V_{in}$  can be revised as:

$$V_{out} = f(V_{in}, V_{REF}) = V_{RES} = \begin{cases} 2 \cdot V_{in} + V_{REF} , when V_{in} < 0 \\ 2 \cdot V_{in} - V_{REF} , when V_{in} > 0 \end{cases}$$

(1.7)

It is noticed that the comparator's threshold is set such a point where the residue voltage reaches the maximum values,  $\pm V_{REF}$ . Therefore, any deviation of the comparator's threshold due to the offset causes the residue falls below the  $\pm V_{REF}$  (under-range), or go beyond the  $\pm V_{REF}$  (overrange) as shown in Figure 1-11a. A solution to this problem is to set the comparator's threshold such a point, so that the residue does not reach the maximum values,  $\pm V_{REF}$ , at that point (Figure 1-11b). That leads us to introduce two comparators, one of the thresholds is at  $-V_{REF}/4$ , and another threshold is at  $+V_{REF}/4$  [21]. Therefore, the relationship between  $V_{RES}$  and  $V_{in}$  can be revised as:

$$V_{out} = f(V_{in}, V_{REF}) = V_{RES} = \begin{cases} 2 \cdot V_{in} + V_{REF}, when V_{in} < -V_{REF}/4 \\ 2 \cdot V_{in}, when -V_{REF}/4 < V_{in} < +V_{REF}/4 \\ 2 \cdot V_{in} - V_{REF}, when V_{in} > +V_{REF}/4 \end{cases}$$

(1.8)

Figure 1-11c shows the architecture of the such implementation to overcome the comparator offset issue in the MDAC. This topology utilizes two comparators to perform the digitization with a residue amplification gain of 2 in each stage and is known as "1.5/stage" architecture. It is notice that the maximum values of the residue voltage reach now to  $\pm V_{REF}/2$ . It means there is a  $\pm V_{REF}/2$  voltage margin to the residue voltage to reach the values  $\pm V_{REF}$ . Therefore, this topology can tolerate the comparator offset upto  $\pm V_{REF}/4$  (due to 2× gain in the residue, the tolerable input offset is the half of the residue voltage margin).

Figure 1-11 : (a) A residue plot considering comparator offset for a differential system, (b) A residue plot that avoids comparator offset , and (c) A 1.5-bit/stage implementation.

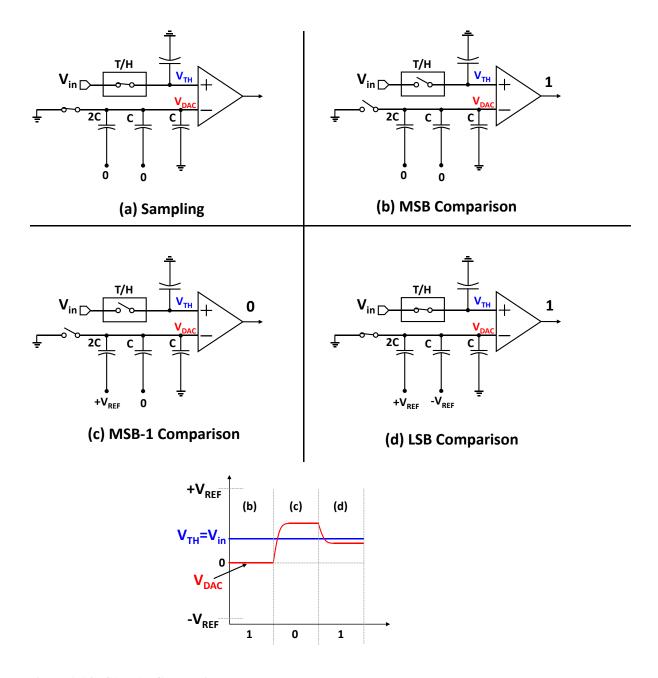

#### 1.4 SAR ADC

SAR ADC digitizes the analog input by following a binary search algorithm. In the pipelined ADC, the MDAC stages digitize the analog input by following a concurrent operation where each stage receives the input, then digitizes it, and finally transfers the residue to the next stage with a gain. However, in the SAR ADC a single stage is employed to perform the digitization where the

Figure 1-12 : The operation of the binary search algorithm.

Figure 1-13 : (a) The architecture of a SAR ADC, (b) timing diagram of the SAR ADC operation.

reference of the comparator is updated after each decision. Therefore, an N-bit SAR ADC requires exactly N comparison cycles to digitize an analog input to an N-bit digital output. Figure 1-12

Figure 1-14 : SAR ADC operation.

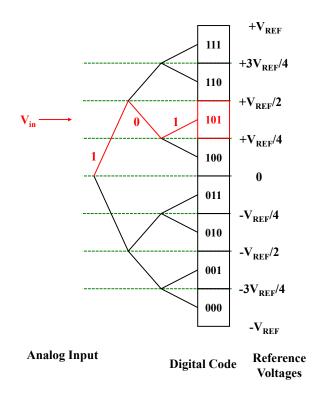

shows an example of a binary search algorithm to digitize an analog input to a 3-bit binary code [18], where the full-scale analog input range is between  $-V_{REF}$  and  $+V_{REF}$ . In the first comparison, input voltage ( $V_{in}$ ) is compared with the middle voltage of the full-range (i.e., in this case it is 0 V). Since the input is greater than 0 V, the first bit is resolved as 1. It also shows that the input lies somewhere between 0 to  $+V_{REF}$ . Therefore, in the second comparison, the new reference is set to the middle of the probable input range (i.e., in this case it is  $+V_{REF}/2$  V). At this time, the input is

Figure 1-15 : Schematic Diagram of a strong-ARM latch comparator.

less than  $+V_{REF}/2$ , and so, the second bit is resolved as 0. After two comparisons, it indicates that the input lies somewhere between 0 to  $+V_{REF}/2$ . Therefore, in the third comparison, the new reference is set to the middle of the probable input range (i.e., in this case it is  $+V_{REF}/4$  V). Since the input is greater than  $+V_{REF}/4$ , the third bit is resolved as 1. So, the 3-bit representation of this sampled input is 101.

As we can see, there are three components involved in each comparison (Figure 1-13a). The first one is that the digital-to-analog (DAC) converter generates the corresponding reference level to compare the input with and the reference level gets updated depending on the resolved bit decisions. The second one is the analog comparator that compares the sampled input with the reference level generated by the DAC. The final component is the SAR logic that receives the comparator output and updates the DAC code to generate the next reference level for comparison. In addition to these, a sample and hold (S/H) circuit is required that samples the analog input on a sampling capacitor,  $C_S$ . Figure 1-13b shows the timing diagram of the SAR ADC. Similar to the Flash ADC, at the low level of the sampling clock, the output of the S/H circuits follows the input and the input is sampled at the rising edge of the sampling clock. In this case, the hold time is longer than the Flash ADC due to successive comparison. For an N-bit SAR ADC, there should

Figure 1-16 : Comparator operation phases, (a) precharge, (b) amplification, (c) turn-on cross-coupled NMOS pair, and (d) turn-on back-to-back inverter.

be N clock cycles during the conversion phase. Therefore, SAR ADC seems to be the lowest speed ADC. To achieve similar speed of a Flash ADC for a given resolution, a number of SAR ADCs should be operated in a time-interleaved way [22].

Figure 1-14 shows the operation of the SAR ADC. At first, the input ( $V_{SH} = V_{in}$ ) is sampled on the sampling capacitor and the capacitive DAC is reset to the middle of the input dynamic range ( $V_{DAC} = 0$  V). After that, the sampled input is compared with 0 V and the comparator resolves the MSBbit. In this case,  $V_{in} > 0$  V, therefore, the comparator output is 1. Now, the capacitive DAC needs to generate reference voltage for the next comparison. Since the  $V_{in} > 0$ , the next probable range of the input is 0 to + $V_{REF}$  and the capacitive DAC generates the reference voltage which is in the middle of the probable range (i.e., in this case it is  $V_{REF}/2$ ) by switching the MSB Capacitor (2C) from 0V to  $V_{REF}$ . In this comparison, the  $V_{in} < V_{REF}/2$ , therefore, the comparator output is 0 and the next probable range for the input becomes 0 to  $V_{REF}/2$ . To generate the middle of probable range (i.e.,  $V_{REF}/4$ ), the next capacitor is switched from 0V to  $-V_{REF}$ . In this case, the input  $V_{in} > V_{REF}/4$ , therefore, the comparator output is 1. After three successive comparisons, the 3-bit digital code for the sampled input is 101.

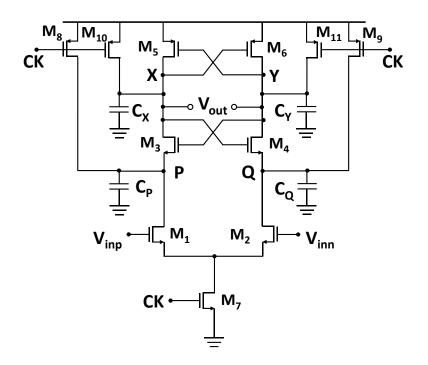

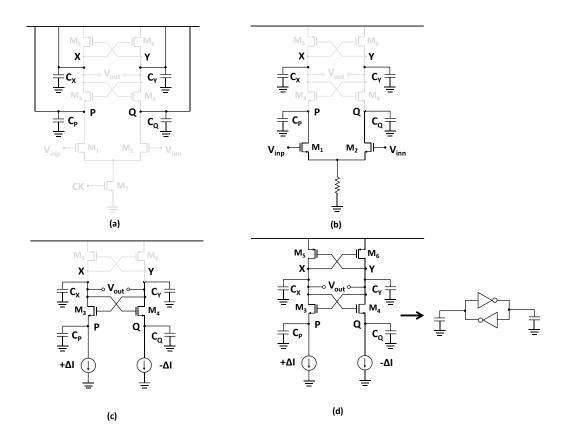

#### 1.4.1 Comparator

Figure 1-15 shows the schematic of a Strong-ARM latch [23] with parasitic associated with each node. It consists of a clocked differential pair,  $M_1$ - $M_2$ , two inverters connected in back-to-back, and four precharge switches,  $M_8$ - $M_{11}$ . The ground pins of the two inverters are connected to the output of the differential pair to transfer the input information into the back-to-back inverters. Finally, the back-to-back inverters amplify the information and provide rail-to-rail outputs at X and Y. These outputs are the function of polarity of  $V_{inp}$  -  $V_{inn}$ . The whole operation is completed in four phases.

In the first phase, which is known as the precharge phase, nodes X, Y, P, and Q are precharged to  $V_{DD}$  through their respective switches, keeping the CK signal low. At that time, the differential input pair, M<sub>1</sub>-M<sub>2</sub>, is off. The circuit associated with this phase is shown in Figure 1-16a.

In the next phase, CK goes HIGH, thereby the precharge switches are turning off, and the clocked differential pair is turning on. Since, the back-to-back inverters are still turned off (due to  $V_{DD}$  at input, output, and ground pin), the nodes P and Q start to discharge through the differential pair. The differential current associated with the discharging operation (Figure 1-16b) is proportional to the input difference,  $V_{inp}$  -  $V_{inn}$ . The output of the differential pair,  $|V_P - V_Q|$ , allows to grow (amplification) according to following relation:

$$\left|V_{P} - V_{Q}\right| \approx \frac{g_{m1,2} \left|V_{inp} - V_{inn}\right|}{C_{P,Q}} \cdot t$$

(1.9)

where,  $g_{m1,2}$  is the transconductance of the differential pair, and  $C_{P,Q} = C_P = C_Q$ . During this time, it is considered that the tail current is almost constant. When the V<sub>P</sub> and V<sub>Q</sub> fall to V<sub>DD</sub> -V<sub>THN</sub>, it turns on the cross-coupled NMOS transistors of the back-to-back inverters (third phase). It allows the nodes X and Y to discharge along with the nodes P and Q through the differential pair. Therefore, the duration of the amplification phase is approximately

$$t_0 \approx \frac{C_{P,Q}}{I_{CM}} \cdot V_{THN}$$

(1.10)

where,  $I_{CM}$  is the common mode (CM) current, which is drawn from each capacitor. By combing eq. (1.9) and eq. (1.10), the voltage gain in this operation can be written as

$$A_V \approx \frac{g_{m1,2}V_{THN}}{I_{CM}} \tag{1.11}$$

In the third phase, the cross-coupled NMOS transistors start to regenerate the voltage difference that appeared at the output of the differential pair,  $V_P - V_Q$ . The operation is similar to a back-to-back latch. The differential equation associated with this phase (Figure 1-16c) is the following:

$$C_{X,Y} \frac{d}{dt} (V_X - V_Y) - g_{m3,4} \left( 1 - \frac{C_{X,Y}}{C_{P,Q}} \right) (V_X - V_Y) = 0$$

(1.12)

The output voltage difference is  $V_{out} = V_X - V_Y$ , and solving for  $V_{out}$ , we get the following:

$$V_{out} = V_X - V_Y = V_{latch-initial} e^{\frac{t}{\tau_{regen}}}$$

(1.13)

where,  $V_{latch-initital}$  is the initial voltage of the back-to-back latch which is equal to the final output voltage at the end of the amplification phase, and  $\tau_{regen}$  is the regeneration time constant of the latch. By substituting

$$\frac{V_{latch-initial}}{\tau_{regen}}C_{X,Y}e^{\frac{t}{\tau_{regen}}} - g_{m3,4}\left(1 - \frac{C_{X,Y}}{C_{P,Q}}\right)V_{latch-initial}e^{\frac{t}{\tau_{regen}}} = 0$$

(1.14)

After solving the equation, the  $\tau_{regen}$  becomes

$$\tau_{regen} = \frac{C_{X,Y}}{g_{m3,4} \left( 1 - \frac{C_{X,Y}}{C_{P,Q}} \right)}$$

(1.15)

It shows that the regeneration time constant is scaled by a factor of  $1 - \frac{C_{X,Y}}{C_{P,Q}}$ . Since  $C_{X,Y} > C_{P,Q}$ , the cross-coupled NMOS transistors do not provide significant regeneration.

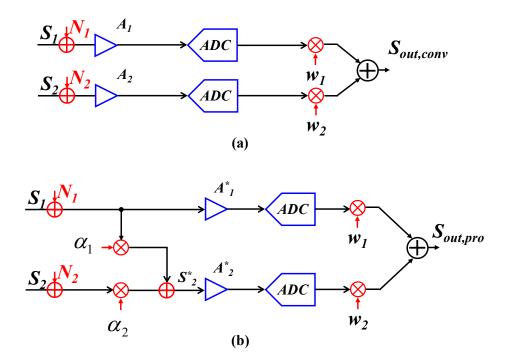

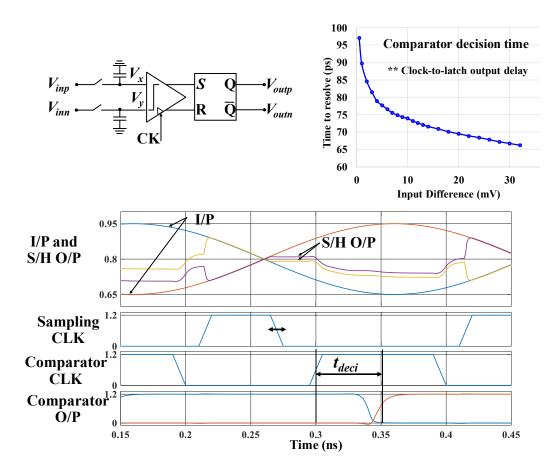

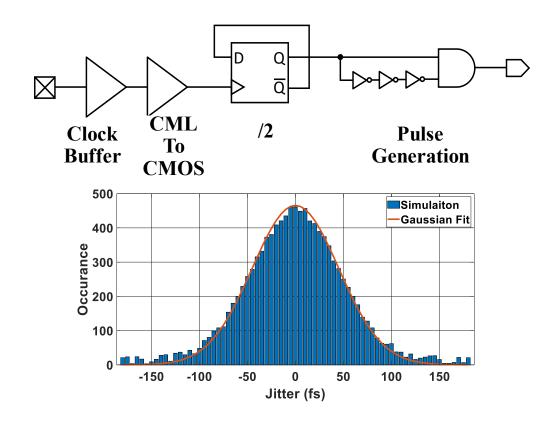

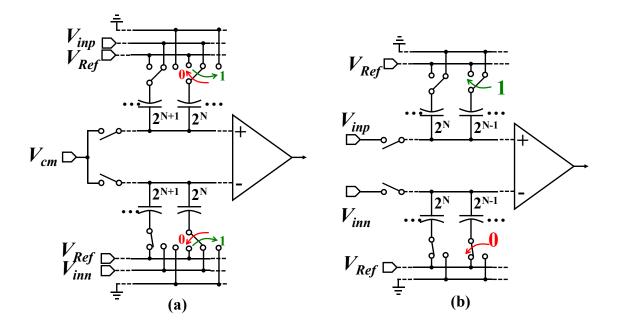

The degeneration through cross-coupled NMOS transistors continues till the output voltages  $V_X$  and  $V_Y$  fall to  $V_{DD}$  - $V_{THN}$ . At this point,  $M_5$  and  $M_6$  turn on and the circuit enters the positive-feedback phase through the back-to-back inverters (Figure 1-16d). As a result, one of the outputs eventually reaches back to  $V_{DD}$  and the other falls to the ground.