Bibliothèque nationale du Canada

Canadian Theses Service

Services des thèses canadiennes

Ottawa, Canada K1 A 0N4

CANADIAN THESES

THÈSES CANADIENNES

#### NOTICE

The quality of this microfiche is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Previously copyrighted materials (journal articles, published tests, etc.) are not filmed.

Reproduction in full or in part of this film is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30.

#### **AVIS**

La qualité de cette microfiche dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

Les documents qui font déjà l'objet d'un droit d'auteur (articles de revue, examens publiés, etc.) ne sont pas microfilmés.

La reproduction, même partielle, de ce microfilm est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30.

THIS DISSERTATION

HAS BEEN MICROFILMED

EXACTLY AS RECEIVED

LA THÈSE A ÉTÉ MICROFILMÉE TELLE QUE NOUS L'AVONS REÇUE

Canada

THE UNIVERSITY OF ALBERTA

CMOS SQUARE-WAVE OSCILLATORS

, BY

IAN A. McKAY

#### A THESIS

SUBMITTED TO THE FACULTY OF GRADUATE STUDIES AND RESEARCHIN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE

OF MASTER OF SCIENCE

DEPARTMENT OF ELECTRICAL ENGINEERING

EDMONTON, ALBERTA

FALL, 1986

Permission has been granted to the National Library of Canada to microfilm this thesis and to lend or sell copies of the film.

The author (copyright owner) has reserved other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without his/her written permission.

L'autorisation a été accordée à la Bibliothèque nationale du Canada de microfilmer cette thèse et de prêter ou de vendre des exemplaires du film.

L'auteur (titulaire du droit d'auteur) se réservé les autres droits de publication; ni là thèse ni de longs extraits de celle-ci ne doivent être imprimés ou autrement réproduits sans son autorisation écrite.

## THE UNIVERSITY OF ALBERTA RELEASE FORM

NAME OF AUTHOR:

IAN A. McKAY

TITLE OF THESIS:

CMOS SQUARE-WAVE OSCILLATORS

DEGREE:

MASTER OF SCIENCE

YEAR THIS DEGREE GRANTED: FALL 1986

Permission is hereby granted to THE UNIVERSITY OF ALBERTA LIBRARY to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly or scientific research purposes only.

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reporduced without the author's written permission.

(Student's signature)

PERMANENT ADDRESS:

Box 2

Cowley, Alberta TOK OPO

DATED: September 16, 1986

# THE UNIVERSITY OF ALBERTA FACULTY OF GRADUATE STUDIES AND RESEARCH

The undersigned certify that they have read, and recommend to the Faculty of Graduate studies and Research for acceptance, a thesis entitled CMOS SQUARE-WAVE OSCILLATORS submitted by IAN McKAY in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE.

. . . . . . . . .

Supervisor

W allegrette

Date . 6. Soft. P.G.

#### ABSTRACT

This is a thesis on the design and application of CMOS square-wave oscillators. It is divided into three studies, the first of which is an examination of eleven simple multivibrators. The goal is to gain a basic understanding how square-wave oscillators work and to provide a series of recommendations for their design. Next is a description of a magnetically-controlled bscillator which was fabricated in 5 micrometer CMOS. This circuit combines an oscillator with a magnetic sensor. It is sensitive to field components perpendicular to the chip surface and immune to parallel ones. The final topic considers the application of square-wave oscillators to phase-locked loops. The voltage-controlled oscillator found in the feedback path of any PLL must be designed carefully for the overall system to be linear.

#### **ACKNOWISEDGEMENTS**

I would like to thank the following for making this less painful:

- Mr. Stan Nasland who sparked my interest in electronics;

- the Canadian Microelectronics Corporation for arranging the fabrication of the integrated circuits;

- Drs. Henry Baltes and Keith Stromsmoe and the Alberta

Microelectronic Centre for giving me money;

- June Swanson for bugging me until I finished the manuscript and then typing it when I did;

- Arokia Nathan and Lundy Taylor for listening to my ideas and waiting

whil I was out of earshot before starting to laugh;

- and, of course, Igor Filanovsky, without whom this entire venture would have been absolutely impossible.

## TABLE OF CONTENTS

| Chapter                               | Pa                                                    | ge |

|---------------------------------------|-------------------------------------------------------|----|

| 1                                     | Introduction                                          | 1  |

| 2                                     | Square-Wave Oscillators: Theory and Design Problems . | 5  |

| 4                                     | 2.2 Analysis of Ideal Multivibrators                  | 6  |

| a de                                  | 2.2.1 Usual Technique                                 | 5  |

| 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 2.2.2 Exceptions to the Usual Technique 1             | 0  |

|                                       | 2.3 Analysis of Real Multivibrators                   | 3  |

| , ,                                   | 2.3.1 Practical Restrictions 1                        | 3  |

| 9                                     | 2.3.1.1 Buffer Slew Rate 1                            | 4  |

|                                       | 2.3.1.2 Comparator and Switch Time Delay 1            | 5  |

| •                                     | 2.3.1.3 Other Problems                                | 7  |

| •                                     | 2.3.2 Charge Injection                                | 8  |

|                                       | 2.3.2.1 The Effect of Charge Injection on Oscillators | 8  |

|                                       | 2.3.2.2 Modeling Charge Injection 2                   | 0  |

|                                       | 2.3.3 What Was Not Studied                            | 2  |

|                                       | 2.4 Summary                                           | 3  |

| 3                                     | A Magnetically-Controlled Oscillator                  | 4  |

|                                       | 3.1 Introduction                                      | 4  |

|                                       | 3.2 Design Considerations                             | 6  |

|                                       | 3.2.1 Biasing                                         | 7  |

|                                       | 3.2.2 Circuit Design                                  | .7 |

|                                       | 3.2.3 Circuit Immunity to Magnetic Field 2            | 8  |

| •                                     | 3.3 MCO Description                                   | 9  |

|                                       | 3 / Pasults and Discussion                            | 1  |

| Chapter * |                                                  | Page |

|-----------|--------------------------------------------------|------|

|           | 3.5 A Proposed MCO Integrated Circuit 4          | 34 . |

| •         | 3.6 Conclusion and Outlook                       | 36   |

| 4 .       | Phase-Locked Loops                               | 37   |

|           | 4.1 Introduction to Phase-Locked Loops           | 37   |

|           | 4.2 Basic PLL Building Blocks                    | 38   |

| ļ         | 4.3 Common Circuit Implementations of PLL Blocks | 39   |

|           | 4.3.1 Phase Detectors                            | 39   |

| •         | 4.3.1.1 Multiplier-Type                          | 39   |

|           | 4.3.1.1 Exclusive-OR Gate                        | 41   |

| *         | 4.3.2 Voltage-Controlled Oscillators             | ,42  |

|           | 4.3.3 Loop Filters                               | 43   |

|           | 4.4 Theory of the Linear Phase-Locked Loop       | 44   |

|           | 4.4.1 Linear Analysis                            | 44,  |

|           | 4.4.2 Nonlinear Analysis                         | 47   |

|           | 4.5 PLL Applications                             | 49   |

| :         | 4.5.1 FM Modulation and Demodulation             | 49   |

|           | 4.5.2 AM Demodulation                            | 49   |

|           | 4.5.3 Clock Signal Recovery                      | 49   |

|           | 4.5.4 Frequency Synthesis                        | 49   |

| •         | 4.6 A CMOS PLL Integrated Circuit                | 52   |

|           | 4.6.1 Phase Detector                             | 52   |

|           | 4.6.2 Voltage-Controlled Oscillator              | 53   |

|           | 4.6.3 Operation Amplifier                        | 55   |

|           | 4.6.3.1 Basic Circuit                            | 55   |

|           | 4.6.3.2 Power Amplifier                          | 57   |

|           | 4.6.3.3 Biasing                                  | 57   |

| Chapter   | u<br>u     | •      | <b>\</b> |          |        |     | <b>\</b> |       | •• | Page |

|-----------|------------|--------|----------|----------|--------|-----|----------|-------|----|------|

|           | 4.6.4      | Fabric | ation    | and T    | esting | • • | .)       |       |    | 59   |

| 5         | Conclusion |        | ,        | <b>\</b> |        |     |          |       | _  |      |

| 9         | 6 .        |        |          |          |        |     |          | •     |    | 100  |

| REFERENCE | :s         |        |          | • • /•   | . 19   | • • | • • •    | • • • |    | 108  |

#### LIST OF TABLES

| Table | Description          | Page |

|-------|----------------------|------|

| 4.1   | PLL design formulae. | 62   |

| 4.2   | PLL, specifications. | . 63 |

## LIST OF FIGURES

| Figure | Description                                                                                             | Page        |

|--------|---------------------------------------------------------------------------------------------------------|-------------|

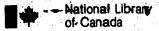

| 1.1    | Block diagram of a general square-wave oscillator.                                                      | 64          |

| 2.1    | Oscillator #1.                                                                                          | 65 -        |

| 2-2    | Oscillator #2.                                                                                          | 66          |

| 2.3    | Oscillator #3.                                                                                          | 67          |

| 2.4    | Oscillator #4.                                                                                          | 68          |

| 2.5    | Oscillator #5.                                                                                          | <b>69</b> . |

| 2.6    | Oscillator #6.                                                                                          | 70          |

| 2.7    | Oscillator #7.                                                                                          | . 71        |

| 2.8    | Oscillator #8.                                                                                          | 72          |

| 2.9    | Oscillator #9.                                                                                          | 73          |

| ′ 2.10 | Oscillator #10.                                                                                         | <b>.74</b>  |

| 2.11   | Oscillator #11.                                                                                         | 75          |

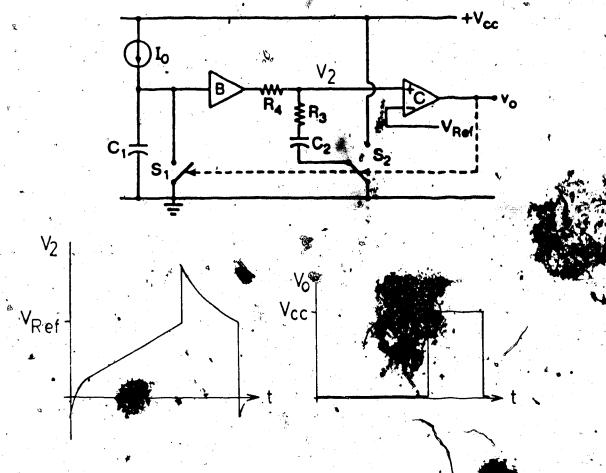

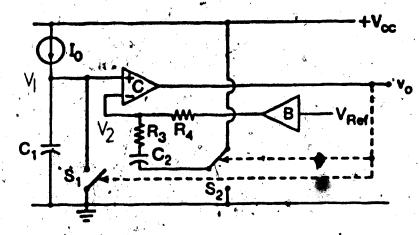

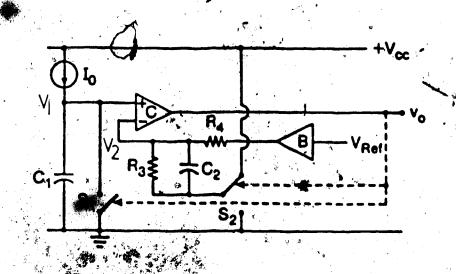

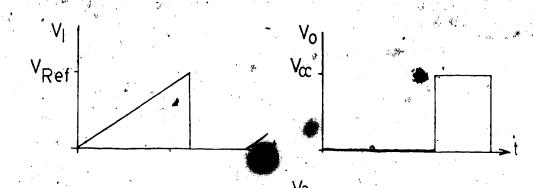

| 2.12   | Fig. 2.6 with switch and comparator time delay.                                                         | 76          |

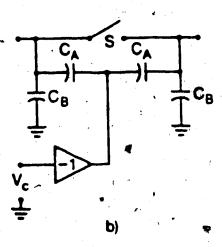

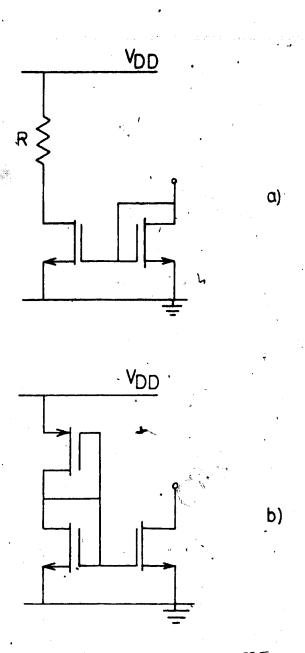

| 2.13   | Analog switch models: a) positive switch, and b) negative switch.                                       | 77 A        |

| 2.14   | Fig. 2.2 with switch model.                                                                             | 78          |

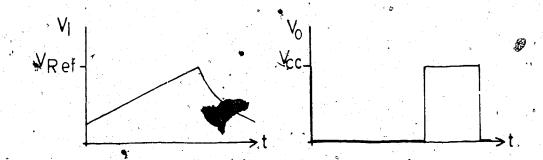

| 2.15   | a) Switch circuit; b) and c) input and output waveforms.                                                | 79          |

| 2.16   | Modeled high frequency oscillations.                                                                    | 80          |

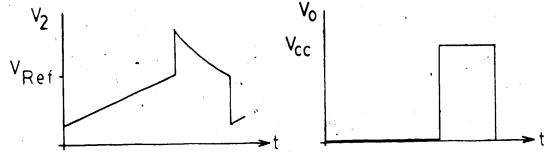

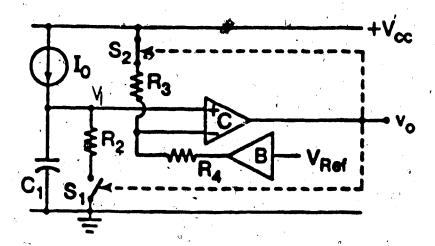

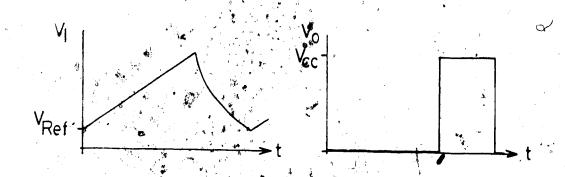

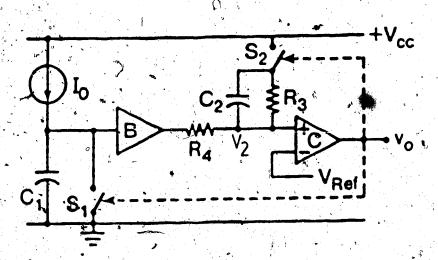

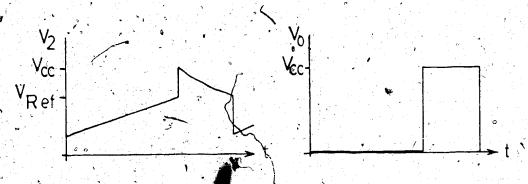

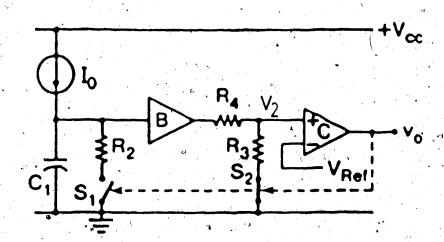

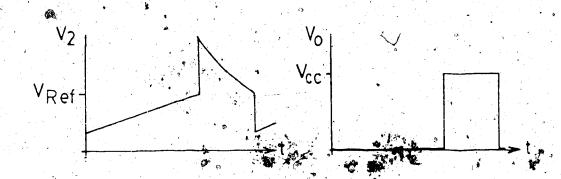

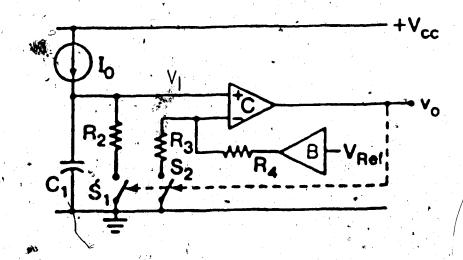

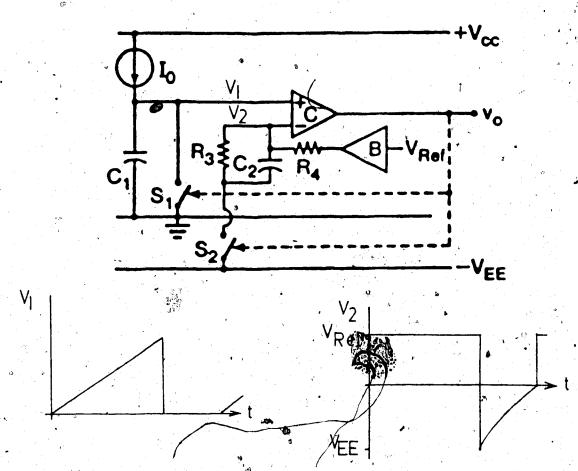

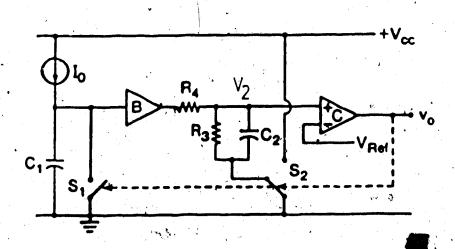

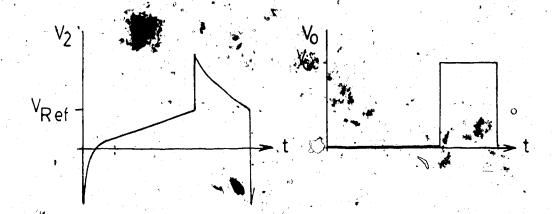

| 2.17   | $V_0$ and $V_2$ using negative switches in a positive switch circuit (a and b) and in a negative switch |             |

| •      | circuit (c).                                                                                            | 81          |

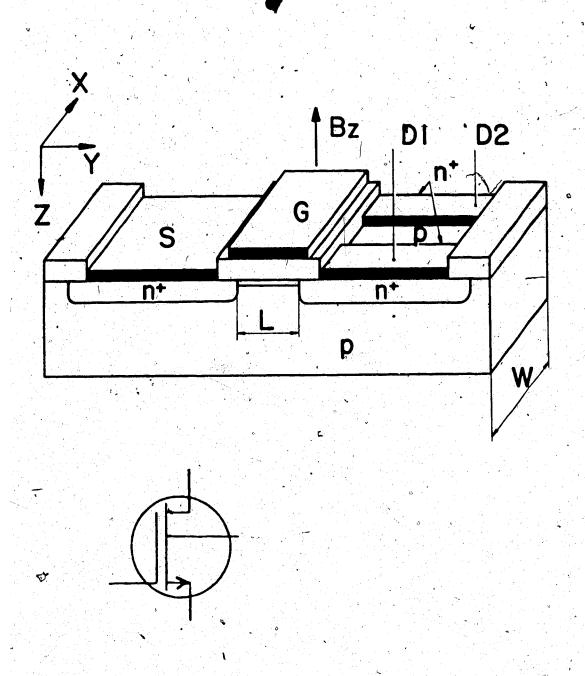

| 3.1    | Three-dimensional view of an N-channel split-drain MAGFET and its circuit symbol.                       | ·82         |

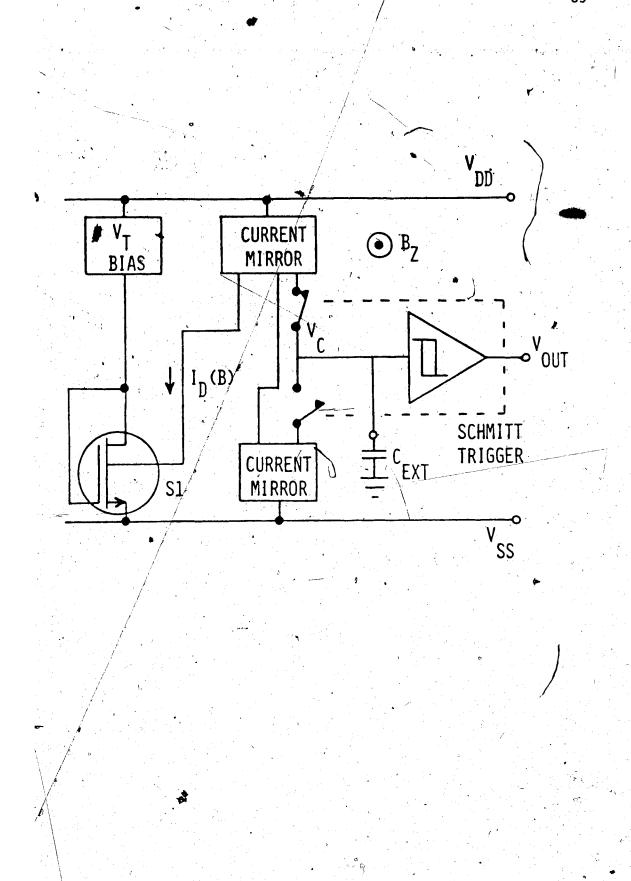

| 3.2    | Block diagram of the MCO.                                                                               | 83          |

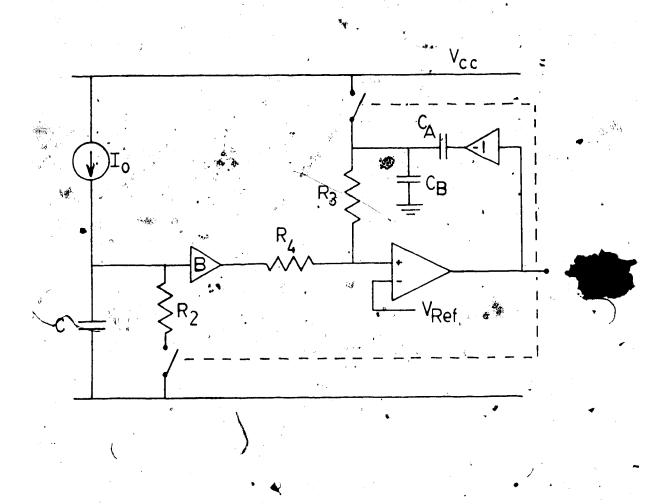

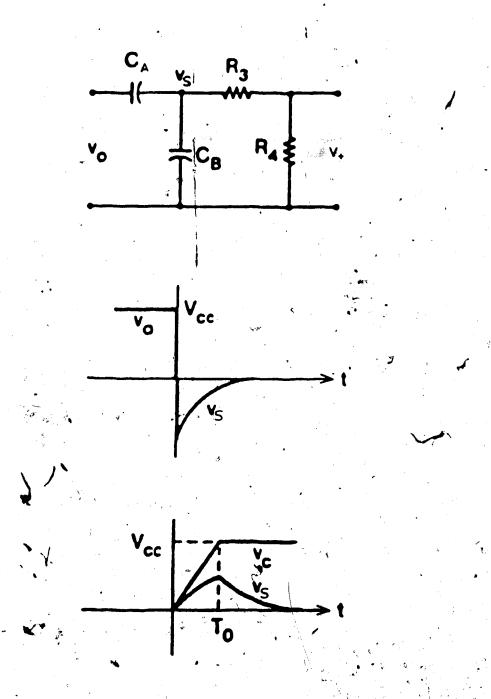

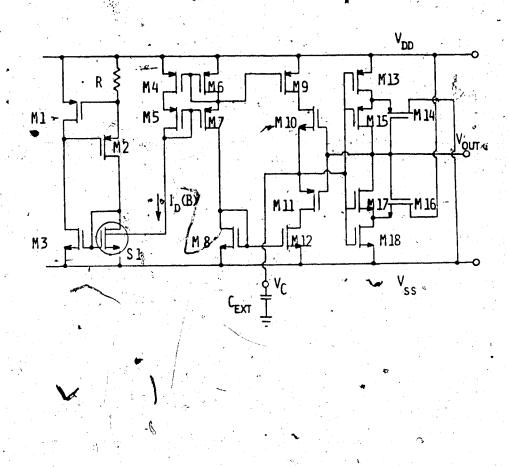

| 2 2    | Circuit cohometic                                                                                       | 84          |

Qc

| Figure       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Page       |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

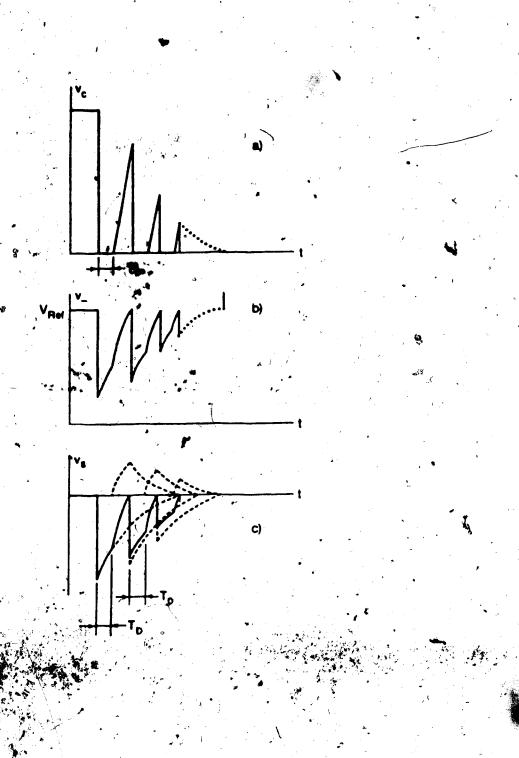

| <b>3.4</b> . | V <sub>OUT</sub> and V <sub>c</sub> for: a) B = 1 T; b) B = 0 T;<br>c) B = -1 T.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 85         |

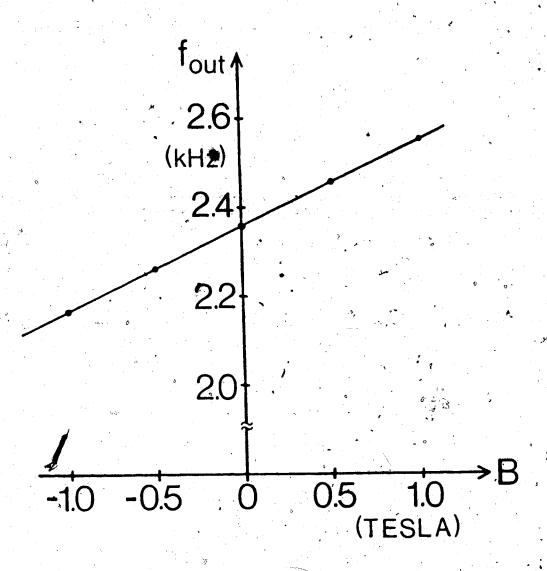

| 3.5          | Output frequency four as a function of B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 86         |

| 3.6          | Photomicrograph of the MCO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 87         |

| .3.7         | Proposed MCO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 88       |

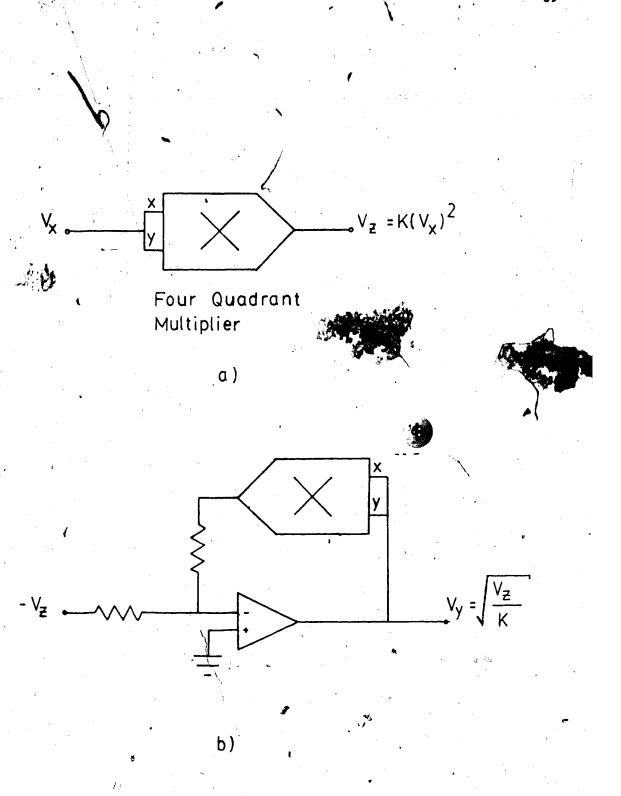

| 4.1          | a) Squaring circuit; b) square-root circuit; the gain of the multiplier, usually K = 0.1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | K is 89    |

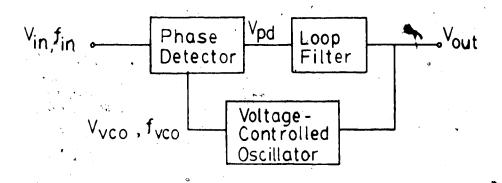

| 4.2          | Black diagram of the basic PLL system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 90         |

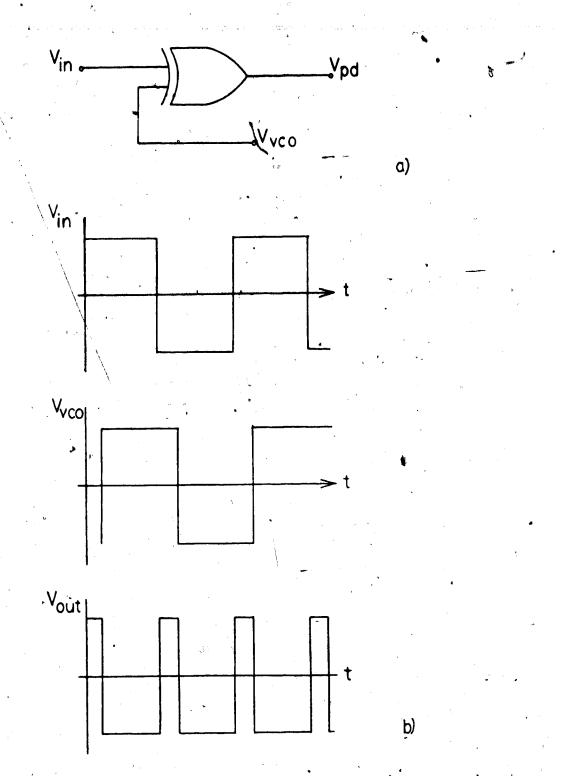

| 4.3          | Exclusive OR gate as a phase detector: a) sy b) input and output waveforms.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ymbol;     |

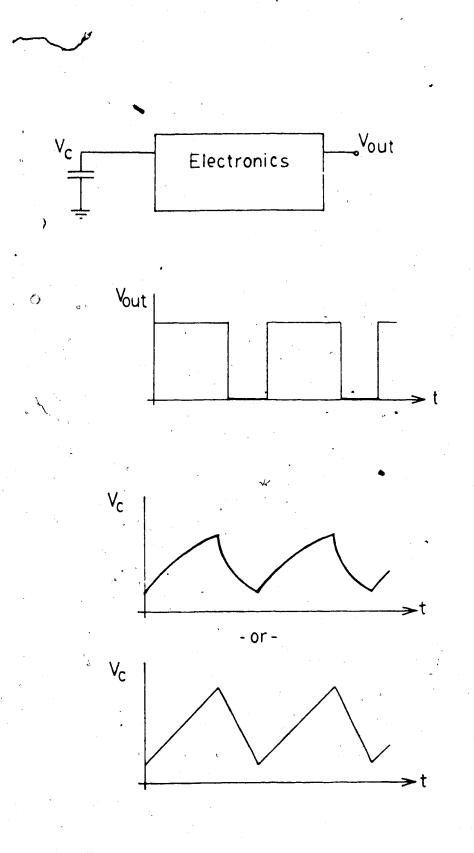

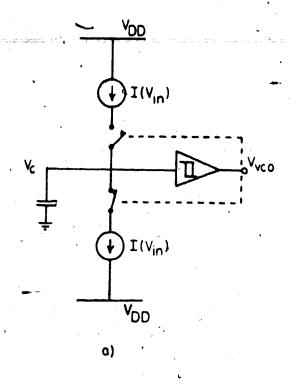

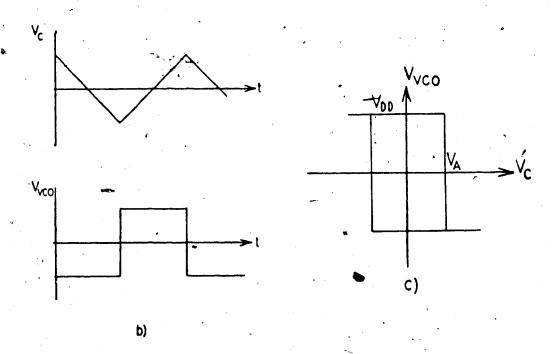

| 4.4          | Voltage-controlled oscillator: a) block diagonal |            |

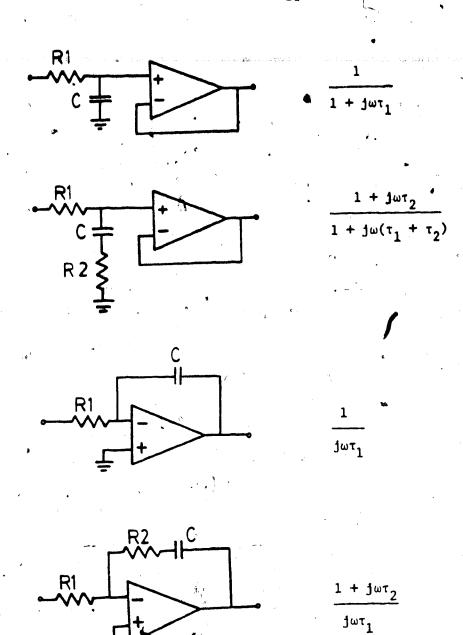

| 4.5          | Loop filters: a) passive (with buffer); b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | active. 93 |

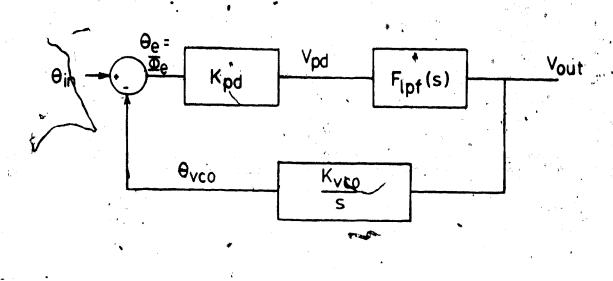

| 4.6 .        | Block diagram of a phase-locked loop system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 94         |

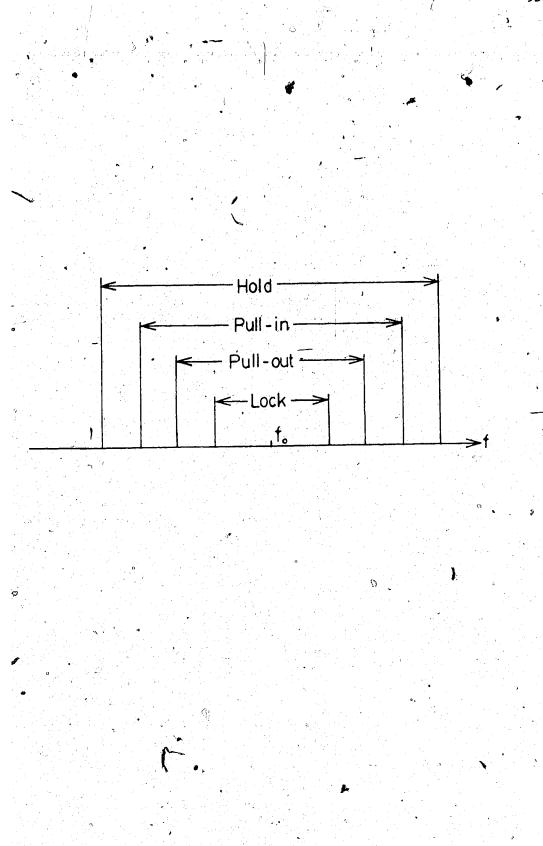

| 4.7          | PLL ranges.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 95         |

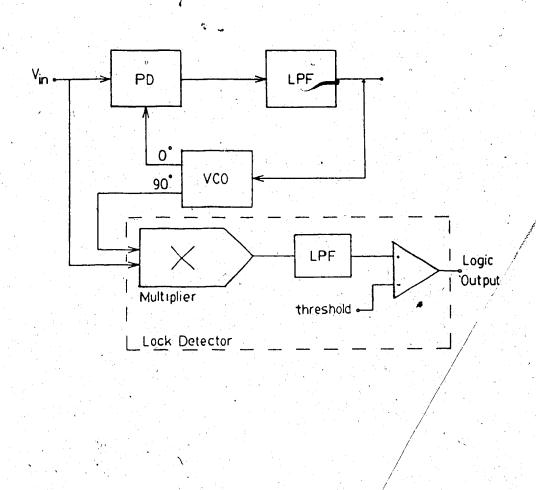

| 4.8°         | Tone decoder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 96         |

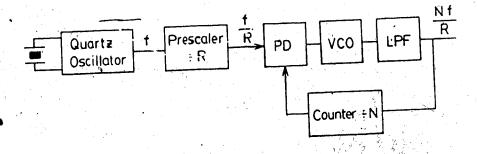

| 4.9          | Frequency synthesizer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 97         |

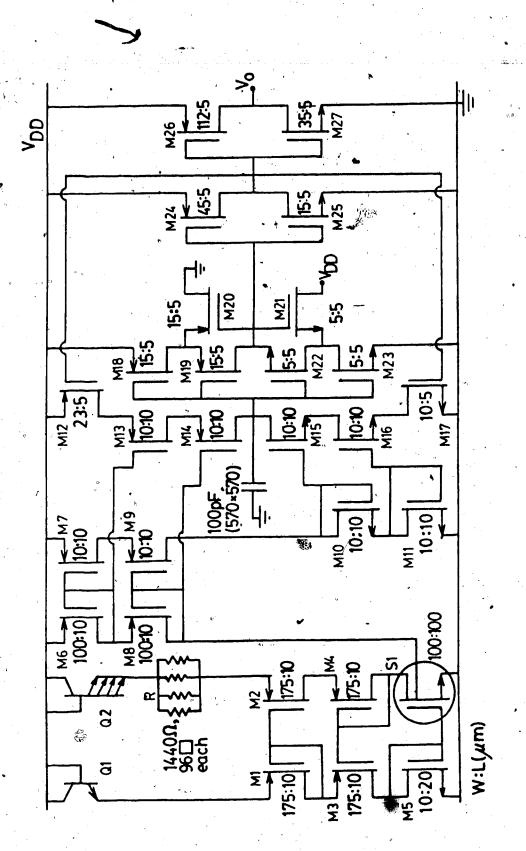

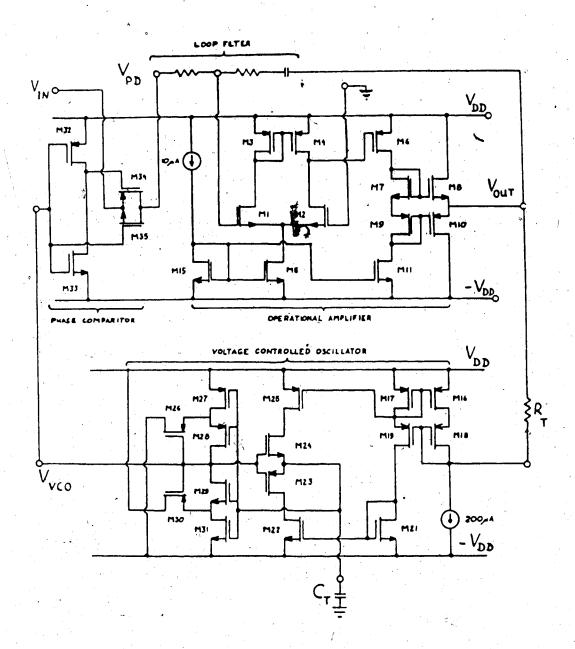

| 4.10         | Schematic of the CMOS PLL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 98         |

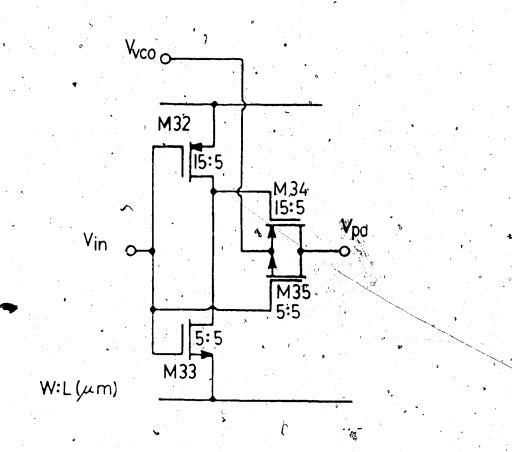

| 4.11         | Phase comparitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 99         |

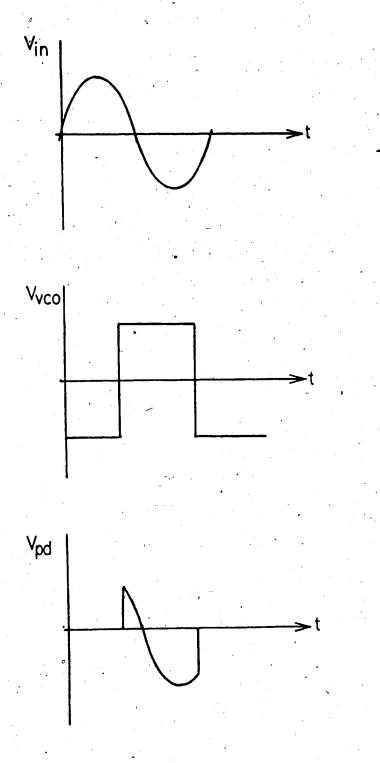

| 4.12         | Phase detector waveforms.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 100        |

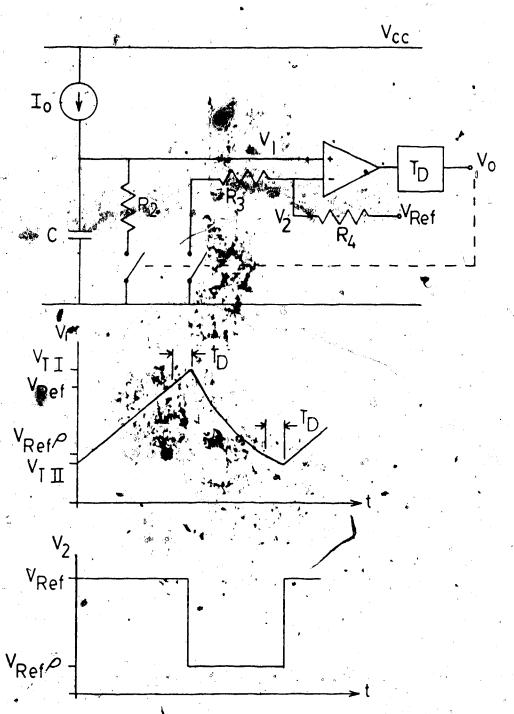

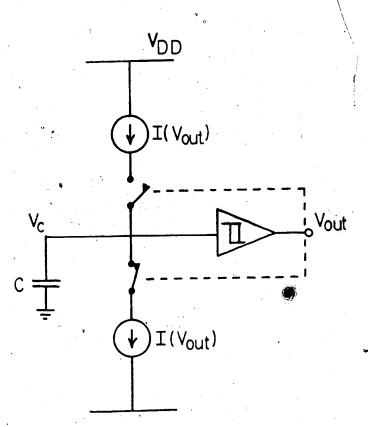

| 4.13         | Block diagram of the VCO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 101        |

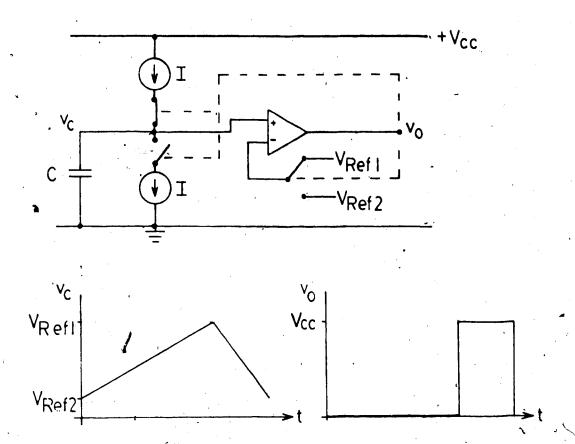

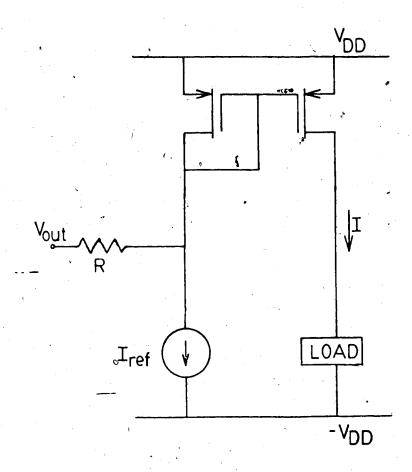

| 4.14         | Detail of the VCO input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 102        |

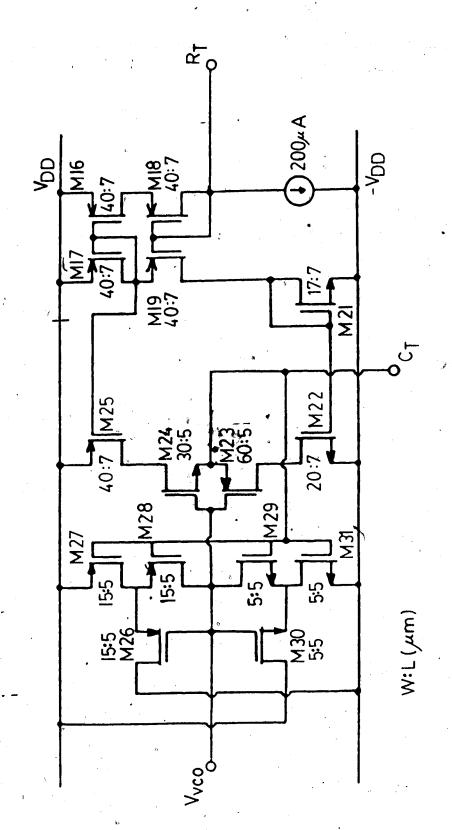

| 4.15         | Voltage-controlled oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 193        |

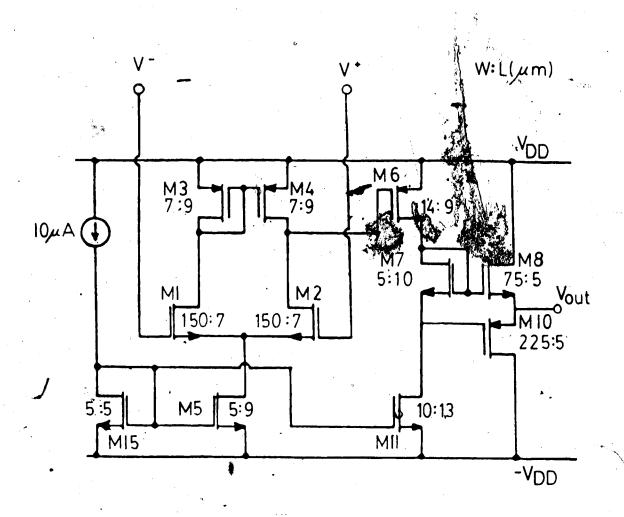

| 4.16         | Operational amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 104        |

| 4.17         | Commonly used bias sources.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 105        |

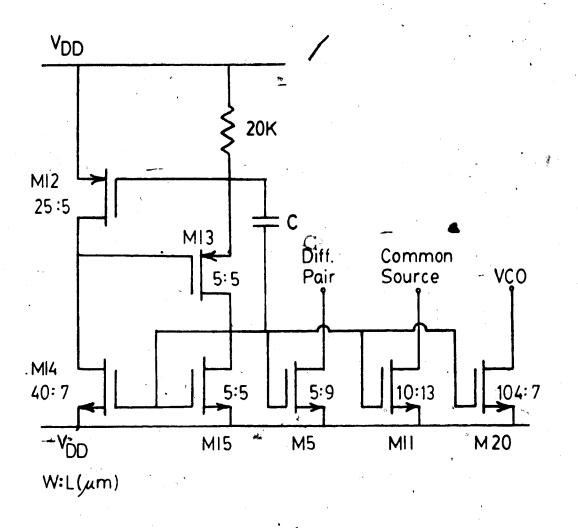

| 4.18         | Bias circuit of the PLL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>106</b> |

| 4.19         | Photomicrograph of the PLL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 107        |

|              | xi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •          |

|                                         | LIST OF SYMBOLS                    |

|-----------------------------------------|------------------------------------|

| Symbol Symbol                           | Description                        |

| A.                                      | Voltage gain                       |

| <b>B</b>                                | Magnetic induction                 |

| c                                       | Capacitance                        |

| $\mathbf{r}$                            | Loop filter transfer function      |

|                                         | Frequency                          |

| <b>f</b> .                              | Certer frequency                   |

| 8_                                      | Transconductance                   |

| 8°                                      | Output conductance                 |

| H <sub>PHASE</sub> , H <sub>ERROR</sub> | PLL transfer functions             |

| PHASE ERROR                             | Current                            |

| . ID                                    | Drain current                      |

|                                         | Current density                    |

| K <sub>PD</sub>                         | Phase detector gain                |

| K <sub>VCO</sub>                        | Voltage-controlled oscillator gain |

| VCO                                     | Gate length                        |

|                                         | Counter input                      |

| Q                                       | Charge                             |

|                                         | Resistance                         |

| 1                                       | . MCO sensitivity                  |

| SR **                                   | . Slew rate                        |

| T R                                     | Pulse duration                     |

|                                         | Delay time                         |

| $T_{\mathbf{D}}$                        |                                    |

|                                         | Voltage                            |

|                                         |                                    |

| Symbol -                                            | Description               |

|-----------------------------------------------------|---------------------------|

| $v_{\mathbf{A}}$                                    | Schmitt trigger threshold |

| V <sub>BE</sub>                                     | Base-emitter voltage      |

| V <sub>CC</sub> , V <sub>EE</sub> , V <sub>DD</sub> | Supply voltage            |

| V <sub>f</sub>                                      | Final voltage             |

| V <sub>GS</sub>                                     | Gate-source voltage       |

| V                                                   | Initial voltage           |

| V <sub>IN</sub>                                     | Input voltage             |

| V <sub>OUT</sub>                                    | Output voltage            |

| $v_{ m PD}$                                         | PD output voltage         |

| ${\sf V}_{\sf Ref}$                                 | Reference voltage         |

| V <sub>SB</sub>                                     | Source-substrate voltage  |

| V <sub>ss</sub>                                     | Steady-state voltage      |

| V <sub>ST</sub> , V <sub>H</sub>                    | Hysteresis voltage        |

| $V_{T}$ , $V_{Tn}$ , $V_{Tp}$                       | Threshold voltage         |

| v <sub>t</sub>                                      | Thermal voltage           |

| v <sub>vco</sub>                                    | VCO output voltage        |

|                                                     | Gate width                |

| β β p                                               | Process gain              |

| <b>.</b>                                            | Damping factor            |

| 8                                                   | Transform of θ            |

| 0                                                   | Phase                     |

| $\mu_{\mathbf{n}}, \mu_{\mathbf{p}}$                | Mobility ,                |

| μ <mark>*, μ</mark> *, μ                            | Hall mobility             |

| <b>p</b>                                            | Resistivity               |

|                                                     |                           |

Time constant

| Symbol                | Description           |  |  |

|-----------------------|-----------------------|--|--|

| Ø                     | Phase angle           |  |  |

| Ω                     | Transform of $\omega$ |  |  |

| ω                     | Radian frequency      |  |  |

| $\omega_{\mathbf{n}}$ | Natural frequency     |  |  |

#### Chapter 1

#### Introduction

This thesis deals with some topics within the broader area of CMOS square-wave oscillator design.

A square-wave oscillator is any circuit whose output is a square-wave. A square-wave is a voltage waveform which spends practically all of its time at one of two distinct voltages. That is to say, the output voltage of the oscillator is always at one or the other of the two levels and periodically switches between them. The output need not spend the same amount of time in one state as it does in the other but, from period to period, the durations of the two states are constant,

The timing of all oscillators is controlled by an energy storage element (quartz crystal, capacitor, inductor, etc.). All of the circuits considered here will use one of the following: a capacitor-resistor combination (and thereby rely on an exponential time constant); a capacitor, charged and discharged with a constant current source; or some combination of the two, as a basis for timing. Fig. 1.1 shows a block diagram of a general square-wave oscillator.

The literature contains a great deal about bipolar integrated oscillators as well as ICs which use them as the building blocks of a larger system. The same cannot be said for CMOS. CMOS integrated circuits which use oscillators do exist but, for the most part, the designs have been copied from those already used in bipolar technology. This is unfortunate because CMOS, which uses MOSFETs, provides

oscillator circuits. This happens simply because bipolar transistors and MOSFETs work differently. It is therefore not necessary, and perhaps not even wise, to substitute n-channel for npn and p-channel for pnp in one of the old designs to create a CMOS oscillator. On the contrary, it is prudent to redesign oscillators given the devices at hand. This thesis attempts to fill some of the void in the literature and to study design problems which are peculiar to CMOS.

Square-wave oscilla@ors find application everywhere. All micro-processors use crystal oscillators to synchronize the various components in the computer system. Integrated circuit timers, which are general purpose circuits that perform timing functions, are used in hundreds of different situations [Jung]. Communication also relies on square-waves in the form of the pulse-coded modulation and pulse-width modulation transmission schemes.

In addition to the theory and basic design problems found in Chapter 2 of this thesis, Chapters 3 and 4 discuss two specific applications of square-wave oscillators: a magnetically-controlled oscillator and a phase-locked loop. The following is an introduction to the three substantive chapters of the thesis.

Chapter 2 attempts to do two things. The first is to gain a basic understanding of how square-wave oscillators work and to provide a series of recommendations for their design. The focus of this study is not on CMOS as such, but is general enough to apply to CMOS, bipolar or whatever. The second goal of the chapter is to fill part of the void in the literature regarding nonsymmetric square-wave oscillators.

These problems will be addressed by considering eleven basic circuits. Analysis techniques are demonstrated first under the assumption that the active components, which form part of the circuit, operate perfectly. Then, the effects of real active devices on the circuit's operation is discussed. This will lead to recommendations for avoiding the pitfalls of oscillator design which these devices can cause. In particular, the switches used for changing the oscillator from one state to the next exhibit something called "charge injection," the effects of which may be devastating to the circuit's operation. An analysis and a method for combating the effects of charge injection is included in the last part of the chapter:

The third chapter contains a description of the first of two integrated circuits covered by this thesis. It is a square-wave oscillator whose output frequency varies linearly with the magnetic field perpendicular to the surface of the chip. This circuit is called a "magnetically-controlled" oscillator (MCO). This project was undertaken primarily as a design exercise; to gain experience at preparing a circuit for submission to a silicon foundry (layout, rule checking, etc.); and to determine the practicality of combining a magnetic sensor and a square-wave oscillator on the same chip.

The integrated circuit consists of a split-drain magnetic field sensor (a sensor which provides an output current which is proportional to the incident magnetic field) connected to the input of a current-controlled oscillator (an oscillator whose output frequency varies with input current).

In addition, to a description of the MCOs design, this chapter provides a general discussion of the problems involved in combining

magnetic sensors and circuitry on the same chip. Results of the fabricated integrated circuit are included and, based on those, an improved design for the MCO is proposed.

The third and final topic examined in this thesis (found in Chapter 4) is the application of square-wave oscillators to phase-locked loops (PLL). Without going into the details, a phase-locked loop is a feedback control system whose primary function is to convert frequency signals to voltages. (It can, therefore, take the output of the MCO and convert it into a voltage which is proportional to the magnetic field incident on the MCO.) On the surface, a phase-locked loop may seem like an unlikely candidate for this thesis but, as it turns out, that portion of a PLL which relies on a square-wave oscillator is critical. The voltage-controlled oscillator (its output frequency is proportional to an input voltage) which is found in the feedback path of every PLL system, must be designed carefully, particularly with regard to linearity, if the system is to be linear.

The chapter details the design of an integrated PLL intended for fabrication in CMOS. In addition, a treatment of what PLLs are, what they do, how they are constructed in technologies other than CMOS and the basics of PLL theory are included. Assorted PLL applications are also described.

To summarize, this thesis discusses three aspects of square-wave oscillators, the material includes both the theory of their operation and some of their applications.

#### Chapter 2

#### Square-Wave Oscillators: Theory and Design Problems

#### 2.1 Introduction

A great deal is already known about square-wave oscillators, particularly symmetric ones. There is extensive literature concerning the generation of square waves using bipolar technology. What is missing from this body of knowledge is a treatment of nonsymmetric square-wave oscillators and the problems with oscillator design which are peculiar to CMOS. This chapter will attempt to fill part of that gap. (

The following is a discussion of eleven basic nonsymmetric square-wave oscillators (or multivibrators, as they are sometimes called). They will be studied on the building block level. That is to say, the actual details of the active devices are not considered but rather are left as individual blocks with generalized characteristics. This means that the statements made about these circuits are valid regardless of whether they are integrated or discrete, bipolar or CMOS.

First, this chapter will discuss the analysis of these circuits assuming that all of the active components operate ideally. Then, the effect of the active circuit blocks have on the circuit's function will be considered. The material concludes with a treatment of a subtle but important problem: the effect of charge injection.