### Radio-Frequency Linearity of Carbon-Based Nanoscale Field-Effect Transistors

by

Ahsan Ul Alam

A thesis submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Solid State Electronics

Department of Electrical and Computer Engineering University of Alberta

© Ahsan Ul Alam, 2015

## Abstract

This Ph.D. thesis focuses on the radio-frequency (RF) linearity of carbon-nanotube field-effect transistors (CNFETs) and graphene field-effect transistors (GFETs). The thesis can be categorized into three stages.

In the first stage, the RF linearity potential of CNFETs has been investigated by considering an array-based device structure under the first approximation of ballistic transport. A nonlinear equivalent circuit for ballistic field-effect transistors is used to compare the linearity of CNFETs to conventional MOSFETs. It is shown that nanotube devices working at high frequencies are not inherently linear, as recently suggested in the literature, and that CNFETs exhibit overall linearity that is comparable to their MOSFET counterparts. The nonlinear quantum capacitance is identified to be a major source of high-frequency nonlinearity in CNFETs. The impact of device parameters such as oxide capacitance, channel width, and tube pitch are also investigated.

In the second stage, a modified top-of-the-barrier model (MTBM) capable of simulating ballistic transport in GFETs is developed. The model captures band-to-band (Klein-Zener) tunneling, which is important in zero-bandgap materials, and it accounts for variations in the densities of states between the channel and the source and drain regions. The model is benchmarked against a sophisticated solver (based on the non-equilibrium Green's function approach) and is shown to have very good quantitative agreement. The utility of the modified TBM is demonstrated by investigating and comparing the RF linearity of GFETs to that of CNFETs and conventional MOSFETs.

In the third stage, the RF linearity potential of short-channel GFETs is assessed by using the modified top-of-the-barrier approach developed in stage 2, again under the first approximation of ballistic transport. An intrinsic GFET is examined to reveal the key features of GFET linearity, and extrinsic parasitics are then included to assess the overall RF linearity. It is shown that short-channel GFETs can be expected to have a signature behavior versus gate bias that includes a constant-linearity region at low gate bias, sweet spots of high linearity before and after the gate bias for peak unity-current-gain frequency, and poor linearity at the gate bias corresponding to the peak unity-current-gain frequency. It is otherwise found that a GFET offers overall linearity that is comparable to a conventional MOSFET and a CNFET, with the exception that the amount of intermodulation distortion in a GFET is dominated by the drain-injected carriers, a unique outcome of graphene's lack of a bandgap.

То

The three most special ladies of my life,

My mother, my wife, and my daughter

And

My life-long role model

My father

## Acknowledgements

I would like to begin my acknowledgement by thanking the Almighty for giving me the opportunity, will, and provisions to pursue and complete this Ph.D.

I would like to express my heartfelt gratitude to my supervisor, Dr. Mani Vaidyanathan. He has not only been a remarkable supervisor to me but also a wonderful role model. In the span of these last six years, he has helped me grow as a self-sufficient, confident, and detail-oriented professional. His passion for quality work and his ever-positive approach to solve problems has guided me through the ups and downs of my Ph.D.

I would also like to take this opportunity to thank Dr. Diego Kienle of Universität Bayreuth, Germany, for being a wonderful mentor and friend throughout my Ph.D. I am deeply indebted to him for his guidance and especially for all those long emails, beautifully explaining the answers to my endless queries. Special thanks to Dr. Prasad Gudem of Qualcomm Inc. for his valuable feedback on my work on GFET linearity.

I am grateful to the members of my supervisory and Ph.D. examination committee, Dr. Sandipan Pramanik, Dr. Masum Hossain, Dr. Ray DeCorby, Dr. Dileepan Joseph, and Dr. Xihua Wang for their comments and suggestions that were invaluable in elevating the quality of this thesis.

I am thankful to my past and present colleagues of the Nanoelectronics Research Laboratory, Dr. Navid Paydavosi, Dr. Sabbir Ahmed, Kyle Holland, and Michael Wong. I will always cherish all our enlightening and passionate discussions at the whiteboard.

I am deeply indebted to Rezu Kaka, Salima Chachi, Sakin, and Lamisa, who have become my family away from home throughout the course of my Ph.D. I would also like to thank my dear friend Saif and Afsana for always being there for me. I can only offer my deepest gratitude and regards to my loving parents Nusrat Sultana and Md. Badrul Alam. Their affection, dedication, and endless sacrifice have made me the person I am today.

Finally, I would like to acknowledge the immeasurable support of my loving wife Rezwana. For the last 6 years, she has singlehandedly taken care of me, my daughter Areeba, the whole household, and her own graduate research, which has enabled me to focus on my work. This Ph.D. would not have been possible without her sacrifice and tremendous support.

Special thanks to the F.S. Chia Ph.D. Scholarship, Queen Elizabeth II Graduate Scholarship, the Natural Sciences and Engineering Research Council (NSERC) of Canada, and AWR Corp. for the wonderful financial and technical support during this work.

# **Table of Contents**

|    | Table of    | of Contents                                                   | vii          |  |  |  |

|----|-------------|---------------------------------------------------------------|--------------|--|--|--|

|    | List of     | Figures                                                       | ix           |  |  |  |

|    | List of     | Tables                                                        | XV           |  |  |  |

| 1. | Introduct   | tion                                                          | 1            |  |  |  |

|    | 1.1.        | Motivation                                                    | 1            |  |  |  |

|    | 1.2.        | This Work                                                     |              |  |  |  |

|    | 1.3.        | Stages of Work                                                | 4            |  |  |  |

|    | 1.4.        | Summary of Contributions                                      |              |  |  |  |

| 2. | RF Linea    | arity Potential of Carbon-Nanotube Transistors Versus MOSFE   | Гs24         |  |  |  |

|    | 2.1.        | Introduction                                                  |              |  |  |  |

|    | 2.2.        | Approach                                                      |              |  |  |  |

|    | 2.2.1.      | Device Structure                                              |              |  |  |  |

|    | 2.2.2.      | Intrinsic Equivalent Circuit                                  |              |  |  |  |

|    | 2.2.3.      | Extrinsic Equivalent Circuit                                  |              |  |  |  |

|    | 2.3.        | Results and discussion                                        |              |  |  |  |

|    | 2.3.1.      | Condition for "Inherent Linearity"                            | 33           |  |  |  |

|    | 2.3.2.      | CNFET vs. CMOS Transistor                                     | 33           |  |  |  |

|    | 2.3.3.      | Linearity of Array-Based CNFETs                               |              |  |  |  |

|    | 2.4.        | Conclusions                                                   | 51           |  |  |  |

| 3. | A Modif     | ied Top-of-the-Barrier Solver for Graphene and Its Applicatio | n to Predict |  |  |  |

|    | RF Linea    | arity                                                         | 53           |  |  |  |

|    | 3.1.        | Introduction                                                  | 53           |  |  |  |

|    | 3.2.        | Theory                                                        | 54           |  |  |  |

|    | 3.2.1.      | Effective Density of States                                   | 57           |  |  |  |

|    | 3.2.2.      | Band-to-Band Tunneling                                        | 59           |  |  |  |

|    | 3.3.        | Results and Discussion                                        | 60           |  |  |  |

|    | 3.4.        | Conclusions                                                   | 66           |  |  |  |

| 4. | RF Line     | earity Performance Potential of Short-Channel Graphene        | Field-Effect |  |  |  |

|    | Transistors |                                                               |              |  |  |  |

|    | 4.1.     | Introduction                                                                        |     |

|----|----------|-------------------------------------------------------------------------------------|-----|

|    | 4.2.     | Approach                                                                            |     |

|    | 4.2.1.   | Device Structure                                                                    |     |

|    | 4.2.2.   | Intrinsic Equivalent Circuit                                                        |     |

|    | 4.2.3.   | Extrinsic Equivalent Circuit                                                        |     |

|    | 4.3.     | Results and Discussion                                                              |     |

|    | 4.3.1.   | Key Features of GFET Linearity                                                      | 74  |

|    | 4.3.2.   | Drain Dominance in GFET Linearity                                                   |     |

|    | 4.3.3.   | Linearity of a GFET versus a MOSFET and a CNFET                                     |     |

|    | 4.3.4.   | Extrinsic Linearity of GFET                                                         |     |

|    | 4.4.     | Qualitative Comparison with Experimental Results                                    |     |

|    | 4.5.     | Conclusions                                                                         |     |

| 5. | Conclusi | ions and Future Work                                                                |     |

|    | 5.1.     | Summary of Contributions                                                            | 101 |

|    | 5.1.1.   | Stage 1 (Chapter 2)                                                                 |     |

|    | 5.1.2.   | Stage 2 (Chapter 3)                                                                 |     |

|    | 5.1.3.   | Stage 3 (Chapter 4)                                                                 |     |

|    | 5.2.     | Future Projects                                                                     |     |

|    | 5.2.1.   | Project A: Effect of Bandgap on RF Linearity of MoS <sub>2</sub> Versus GFETs       |     |

|    | 5.2.2.   | Project B: Compact Nonlinear Modeling of Scattering in GF<br>Effect on RF Linearity |     |

| 6. | Appendi  | x A: Top-of-the-Barrier Model                                                       |     |

| 7. | Appendi  | x B: Derivation of the Condition for "Inherent Linearity"                           | 112 |

# **List of Figures**

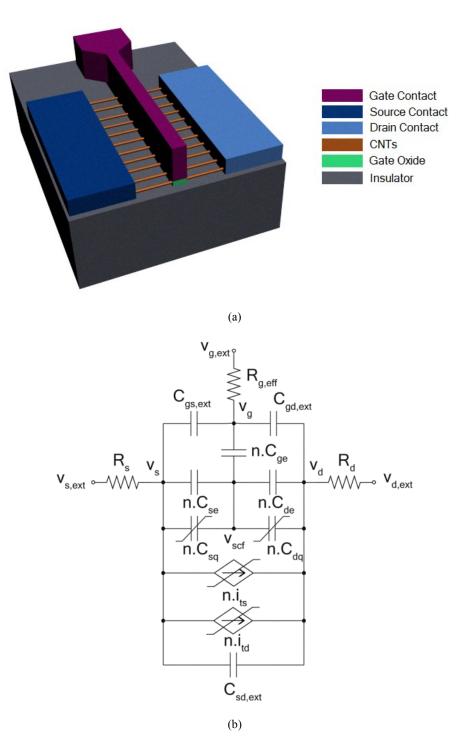

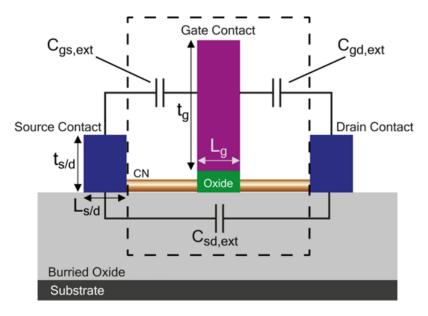

| Fig. 1.1. (a) Schematic of the array-based CNFET used in stage 2 of the Ph.D. (b)<br>Extrinsic nonlinear, small-signal equivalent circuit of an array-based CNFET. 5                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

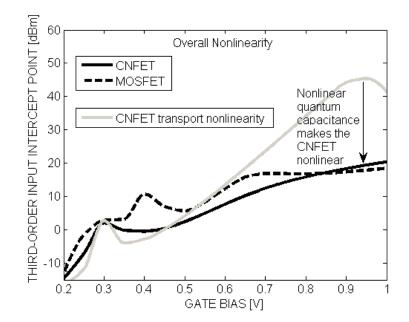

| Fig. 1.2. Intrinsic (neglecting parasitics) IIP3 vs. gate bias for a 20-nm ballistic array-<br>based CNFET and a 20-nm ballistic conventional MOSFET                                                                                       |

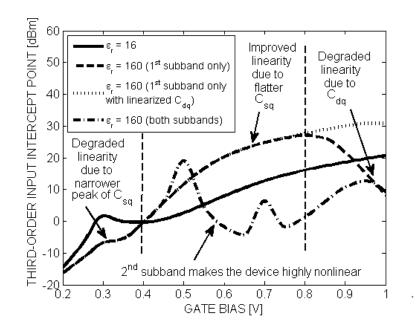

| Fig. 1.3. Extrinsic (including parasitics) IIP3 vs. gate bias for a 20-nm ballistic array-<br>based CNFET with different gate oxides                                                                                                       |

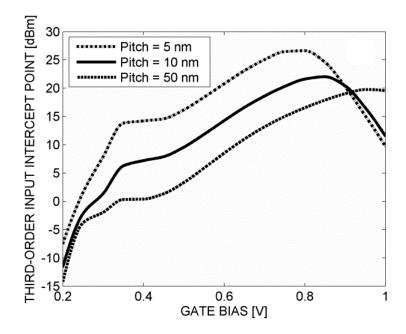

| Fig. 1.4. Extrinsic (including parasitics) IIP3 vs. gate bias for a 30-µm wide ballistic array-based CNFET for different tube pitches                                                                                                      |

| Fig. 1.5. Schematic of the simulated GFET [10]. (b) Current-voltage characteristics of the GFET from NEGF and the modified top-of-the-barrier model                                                                                        |

| Fig. 1.6. (a) Transconductance, output conductance (inset), and (b) first derivative of transconductance with respect to gate voltage of the GFET from NEGF, conventional top-of-the-barrier model, and modified top-of-the-barrier model. |

| Fig. 1.7. IIP3 versus gate bias, with the drain bias held fixed at (a) 0.5 V and (b) 0.8 V, of                                                                                                                                             |

| the GFET compared to its CNFET and MOSFET counterparts 12                                                                                                                                                                                  |

| Fig. 1.8: Complete nonlinear small-signal equivalent circuit of a ballistic GFET                                                                                                                                                           |

| Fig. 1.9: Intrinsic IIP3 and unity-current-gain frequency $f_T$ versus gate bias for the GFET under investigation                                                                                                                          |

| Fig. 1.10: Effect of distortion from the source and drain on IIP317                                                                                                                                                                        |

| Fig. 1.11: IIP3 versus gate bias, at a few different values of drain bias                                                                                                                                                                  |

| Fig. 1.12: Effect of load resistance $R_L$ on GFET IIP3                                                                                                                                                                                    |

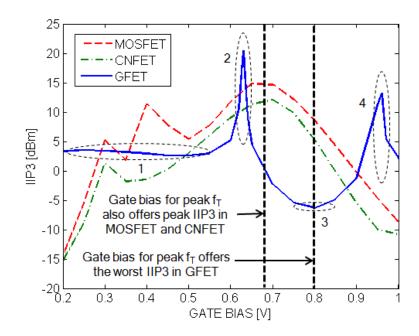

| Fig. 1.13: Intrinsic linearity performance comparison of a GFET with its MOSFET and CNFET counterparts. The peak IIP3 for a CNFET and MOSFET occur at the                                                                                  |

| same gate bias as peak $f_T$ whereas for a GFET the minimum IIP3 occurs at the                                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gate bias for peak $f_T$                                                                                                                                                                                                                                                                                         |

| Fig. 1.14: Intrinsic and extrinsic IIP3 versus gate bias                                                                                                                                                                                                                                                         |

| Fig. 1.15: Effect of load resistance $R_L$ on GFET extrinsic IIP3. The improvement in IIP3<br>with a reduction in $R_L$ is less pronounced than in the intrinsic case shown in<br>Fig. 1.12                                                                                                                      |

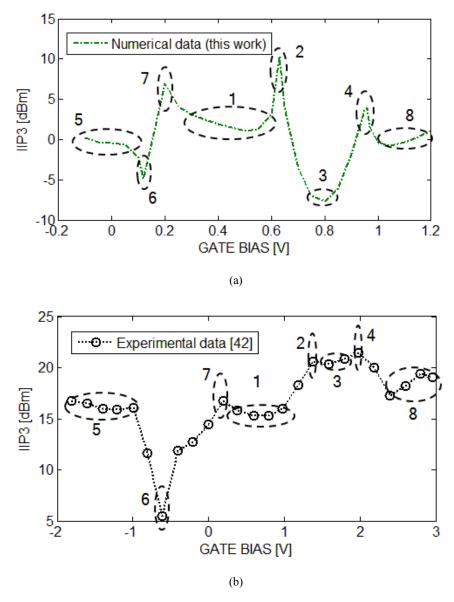

| Fig. 1.16: Qualitative comparison of (a) numerical (extrinsic) IIP3 values of the GFET under investigation with (b) experimental data [42]21                                                                                                                                                                     |

| <ul> <li>Fig. 2.1. Schematics of (a) the array-based CNFET structure, (b) a portion of the transistor consisting of a single tube that can be considered as a single-tube CNFET, and (c) the conventional MOSFET counterpart. The figures are not drawn to scale.</li> <li>27</li> </ul>                         |

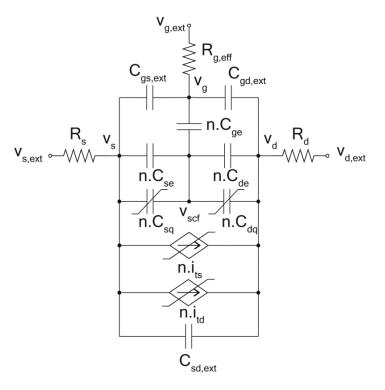

| Fig. 2.2. Nonlinear equivalent circuit for a single-tube ballistic CNFET based on the purely linear topology developed in [14]                                                                                                                                                                                   |

| Fig. 2.3. (a) Family of current vs. bias voltage curves and (b) unity-current-gain frequency $f_T$ vs. gate bias for a 20-nm single-tube CNFET. The solid lines represent the values from the top-of-the-barrier approach [12-14] and the black dots represent data from the BTE-Poisson solver reported in [61] |

| Fig. 2.4. Cross-section of the array-based CNFET structure used in this work                                                                                                                                                                                                                                     |

| Fig. 2.5. Complete nonlinear small-signal equivalent circuit for an array-based CNFET.                                                                                                                                                                                                                           |

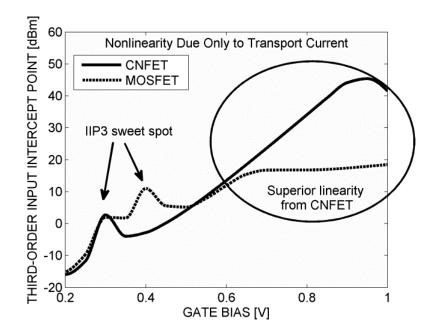

| Fig. 2.6. Intrinsic IIP3 vs. gate bias for a 20-nm ballistic array-based CNFET and ballistic MOSFET, considering only nonlinear transport current                                                                                                                                                                |

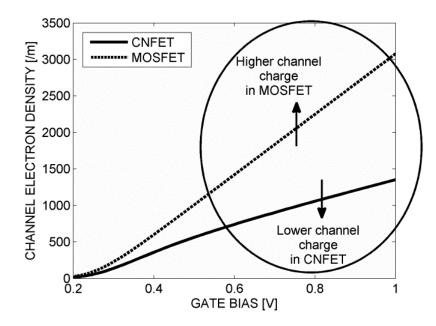

| Fig. 2.7. Channel charge (electron) density of the 20-nm ballistic array-based CNFET and ballistic MOSFET                                                                                                                                                                                                        |

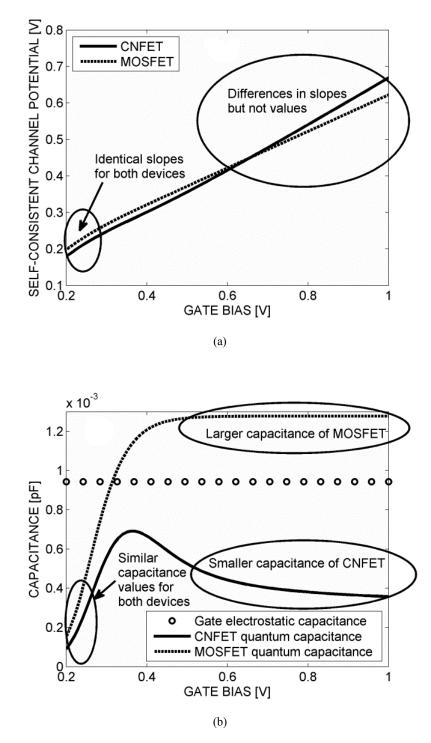

| Fig. 2.8. (a) Self-consistent channel potential and (b) electrostatic and quantum capacitances ( $C_{ge}$ and $C_{sq}$ ) vs. gate bias for a 20-nm ballistic array-based                                                                                                                                         |

| CNFET and ballistic MOSFET                                                                                                                                                                                                                                                                                       |

- Fig. 4.4. Intrinsic IIP3 and unity-current-gain frequency  $f_T$  versus gate bias for the GFET under investigation. 75

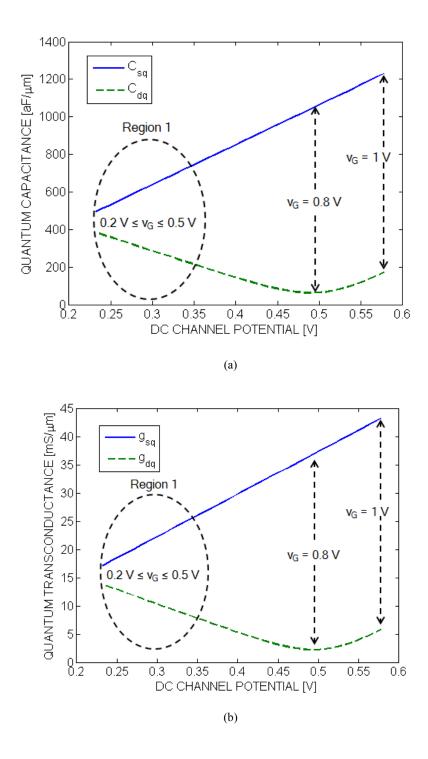

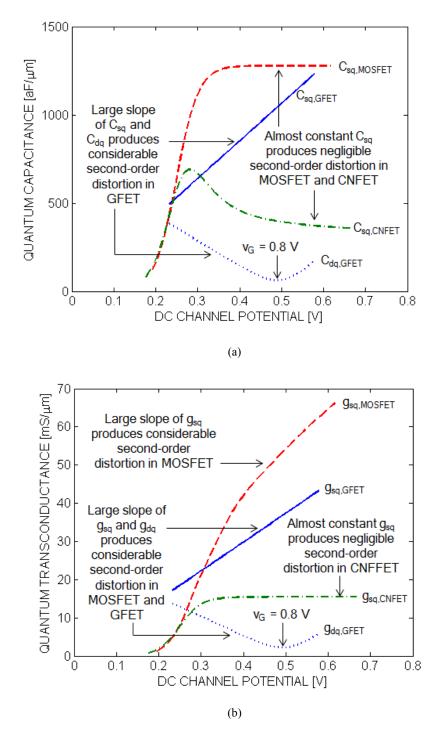

| Fig. 4.5. | (a) Quantum capacitance and (b) transconductance versus the dc part of the                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | channel potential for the GFET under investigation. The gate bias voltages for                                                                                                                                                                                                                                                                                                                                                                                            |

|           | a few points are indicated for reference                                                                                                                                                                                                                                                                                                                                                                                                                                  |

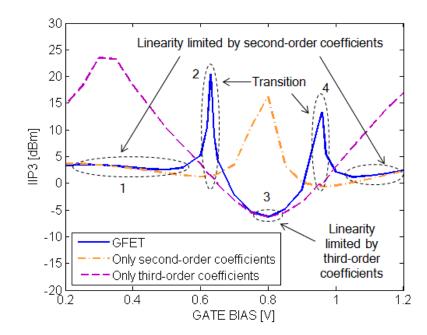

| Fig. 4.6. | Effects of the second- and third-order coefficients on the overall linearity of the GFET                                                                                                                                                                                                                                                                                                                                                                                  |

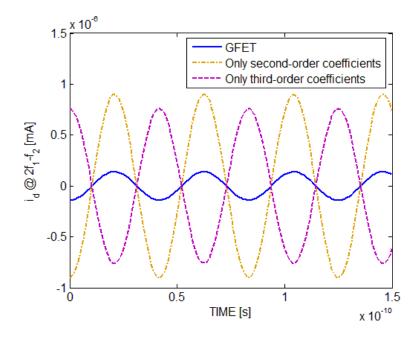

| Fig. 4.7. | Distortion components at $2f_1 - f_2$ in $i_d$ at a gate bias of 0.63 V (point 2 in Fig. 4.6). A destructive combination of the distortion from the two types of sources results in a diminished overall distortion                                                                                                                                                                                                                                                       |

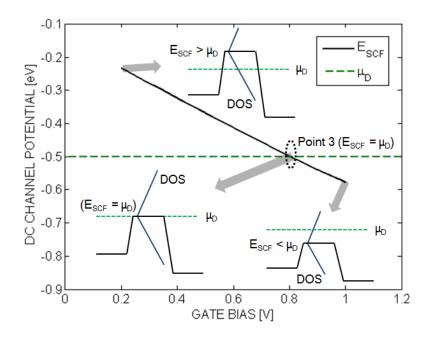

| Fig. 4.8. | The dc part of the channel potential $E_{SCF} = -qv_{SCF}$ versus gate bias. The drain<br>Fermi level $\mu_D$ (fixed by the constant drain voltage of 0.5 V) is also shown.<br>The source Fermi level $\mu_S$ (not shown) is taken to be the reference ( $\mu_S = 0$<br>eV)                                                                                                                                                                                               |

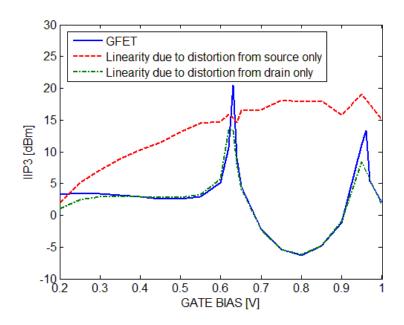

| Fig. 4.9. | Effect of distortion from the source and drain on IIP3. Linearity due only to the source was found by setting the higher-order coefficients in (4.2) and (4.4) to zero; similarly, linearity due only to the drain was found by setting the higher-order coefficients in (4.1) and (4.3) to zero                                                                                                                                                                          |

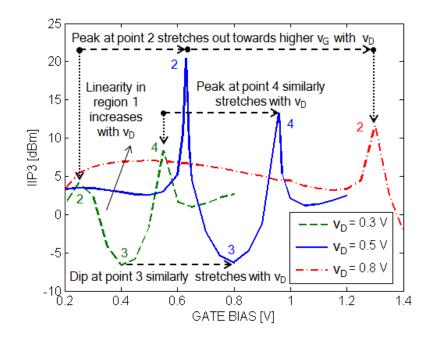

| Fig. 4.10 | . IIP3 versus gate bias, at a few different values of drain bias                                                                                                                                                                                                                                                                                                                                                                                                          |

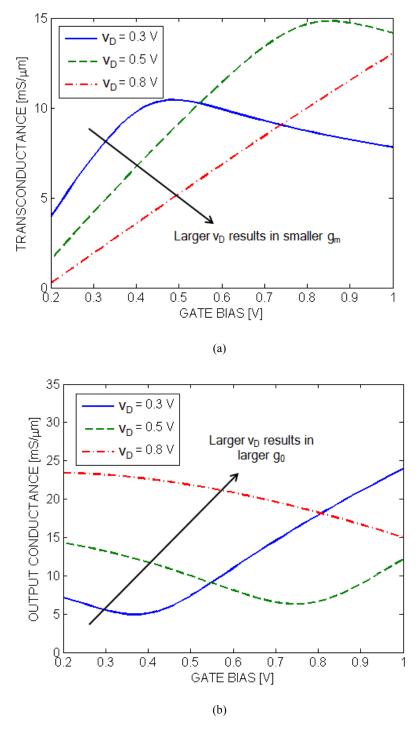

| Fig. 4.11 | . (a) Transconductance and (b) output conductance versus gate bias for varying drain bias                                                                                                                                                                                                                                                                                                                                                                                 |

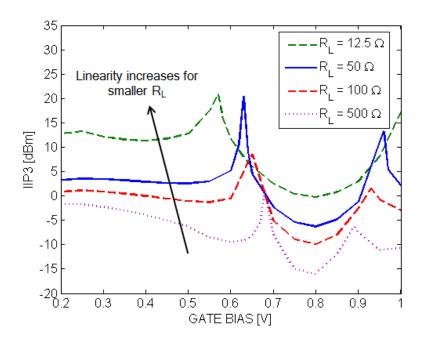

| Fig. 4.12 | . Effect of load resistance <i>R<sub>L</sub></i> on GFET IIP3                                                                                                                                                                                                                                                                                                                                                                                                             |

|           | B. Intrinsic linearity performance potential comparison of a GFET with its MOSFET and CNFET counterparts. The region 1 and points 2-4 from Fig. 4.4 for the GFET curve are marked. We have also indicated that the peak IIP3 for a CNFET and MOSFET occur at the same gate bias as peak $f_T$ whereas for a GFET the minimum IIP3 occurs at the gate bias for peak $f_T$ . The GFET $f_T$ curve is available in Fig. 4.4; the MOSFET and CNFET $f_T$ curves are not shown |

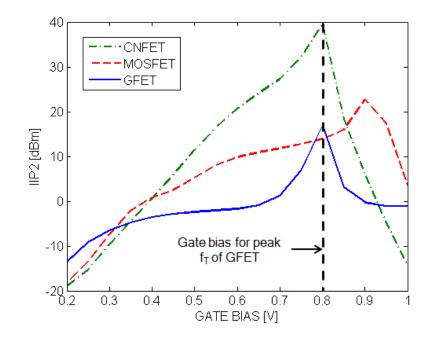

| Fig. 4.14 | . Intrinsic IIP2 versus gate bias of a GFET compared with its MOSFET and                                                                                                                                                                                                                                                                                                                                                                                                  |

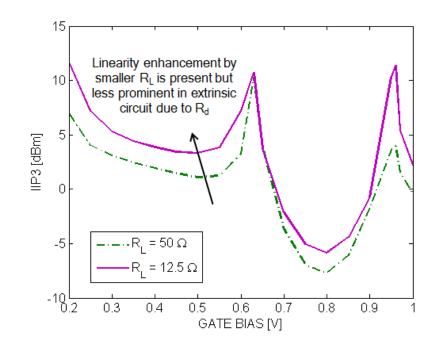

- Fig. 4.17. Effect of  $R_L$  on GFET extrinsic IIP3. The improvement in IIP3 with a reduction in  $R_L$  is less pronounced than in the intrinsic case shown in Fig. 4.12.

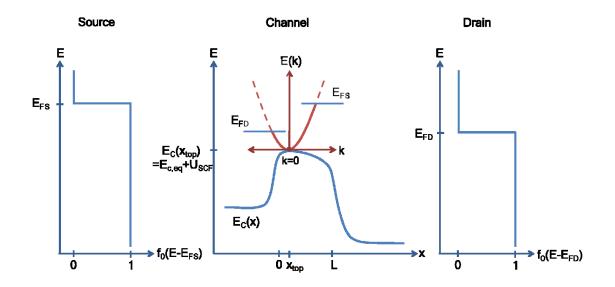

- Fig. A.1. An illustration of the conduction-band edge  $E_c(x)$  versus transport direction x in a MOSFET. The *E*-*k* relation at  $x = x_{top}$ , the location of the top of the source-to-drain energy barrier, is also shown. At 0 K, the positive- and negative-going *k*-states get filled up to the source and drain Fermi levels, respectively, as indicated by the solid portions of the dispersion curve. ...... 106

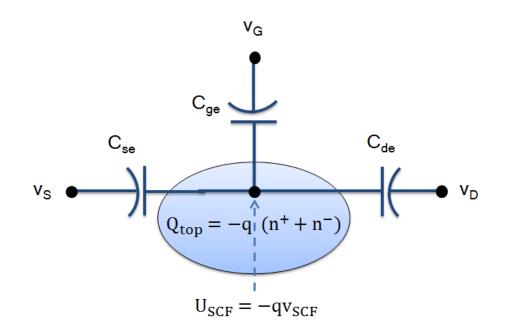

- Fig. A.2. Simple circuit model for the electrostatic behavior of a ballistic MOSFET. The electrostatic potential at the top of the barrier  $U_{SCF}$  is controlled by the voltages applied to the gate, drain, and source through the three illustrated capacitors.

# List of Tables

| Table 2.1. Intrinsic and extrinsic circuit components of the array-based CNFET     | 44  |

|------------------------------------------------------------------------------------|-----|

| Table 4.1. Effect of channel width and load impedance on linearity and gain @ 24 G | Ghz |

| and 0.5 V of gate and drain bias                                                   | 87  |

| Table 4.2. Intrinsic and extrinsic circuit components of the GFET                  | 92  |

## Chapter 1

## Introduction

#### 1.1. Motivation

For more than half a century, Moore's law has ruled the development of electronics. However, as we approach the year 2020, the exponential growth promised by Moore's law is about to come to an end [1-4]. This realization has started a massive search for alternatives to current silicon technology. The hope is that a new material with better electrical properties will continue to provide improved performance, or that a new material will provide a path to new applications, even if the desired (exponential) scaling of silicon is no longer possible.

An array of exotic carbon-based materials, including one-dimensional (1D) carbon nanotubes and two-dimensional (2D) graphene, have shown great promise in replacing or augmenting silicon for future electronics. The advantages of these 1D and 2D forms of carbon over conventional silicon are multifold. First, the reported carrier mobility in both carbon nanotubes and graphene are much higher than in state-of-the-art silicon [5, 6], suggesting the possibility of generally improved device behavior even at long channel lengths (where mobility is a valid figure of merit for transport). Second, consistent with the first point, the electron mean-free paths in both nanotubes and graphene are much larger than in silicon (100 nm in nanotubes and graphene [7] vs. 40 nm in silicon [8]), which means that scattering will not have as deleterious an effect on device performance at short channel lengths. Third, the 1D and 2D nature of these materials facilitate excellent electrostatics for superior gate control at smaller technology nodes.

Consistent with the above observations, both carbon-nanotube field-effect transistors (CNFETs) and graphene field-effect transistors (GFETs) have been reported to offer the potential for excellent high-frequency figures of merit that could meet or exceed the specifications of the International Technology Roadmap for Semiconductors (ITRS) [9], including unity-current-gain frequencies ( $f_T$ ) and unity-power-gain frequencies ( $f_{max}$ ) in the range of THz for channel lengths in the 20-nm range [10, 11]. Given the potential for such high cutoff frequencies, combined with their unique electrical properties, carbon nanotubes and graphene have garnered particular attention as promising candidates for *analog* high-frequency, or radio-frequency<sup>1</sup> (RF), electronics.

One of the key figures-of-merit for RF applications is linearity<sup>2</sup>, which measures the degree of distortion generated by the nonlinear mixing of an input signal with jammers. High linearity is desirable in wireless communication systems, where signals can get distorted due to interference and intermodulation from nearby communication bands and channels (the so-called "jammers"). Advantages in linearity would hence provide a specific motivation to further pursue new materials for RF applications, over and above simply trying to extend Moore's law.

Linearity is difficult to ascertain *directly* from first-principles physical descriptions, such as a non-equilibrium Green's functions (NEGF) approach or the Boltzmann transport equation (BTE). Rather, a compact circuit model is needed. In this thesis, we use such a model, based on the "top-of-the-barrier" approach<sup>3</sup> [12-14]. We calibrate the

<sup>&</sup>lt;sup>1</sup> The terms "radio-frequency" and "high-frequency" are used interchangeably in this thesis.

<sup>&</sup>lt;sup>2</sup> Ideally, we desire a small ac input signal to be *linearly* amplified by a transistor, without interference from jamming signals that are nearby in frequency. However, the nonlinear nature of a transistor's currentand charge-voltage behavior will cause the output signal to be a *distorted* version of the input, due to the nonlinear mixing of a desired input with nearby jammers. *Linearity* is the property --- defined formally by a figure of merit known as the "third-order input-intercept point (IIP3)" --- that characterizes the extent of such distortion.

<sup>&</sup>lt;sup>3</sup> The "top-of-the-barrier" model is a method of describing charge and current in any ballistic (collisionless) transistor. Historically, it is based on an original formulation by Natori [12] that was refined by Rahman *et al.* [13] and which was then used to create an equivalent circuit (for purely linear operation) according to Hasan *et al.* [14]. The key elements of the model are provided in Appendix A. Unfamiliar readers may wish to review Appendix A prior to reading Chapters 2 and 3. For the discussion in this introductory

model with NEGF or BTE results, and employ it to study the RF linearity offered by emerging channel materials, particularly those based on carbon.

#### **1.2.** This Work

Many studies have been conducted on the dc (static) and *linear* high-frequency behavior of carbon-based transistors, while their *nonlinear* high-frequency behavior remains relatively unexplored. This work is thus concerned with the *nonlinear* high-frequency performance of emerging carbon-based, field-effect transistors (FETs). The aim of the research was to accomplish the following tasks:

- Use a nonlinear circuit model for carbon-nanotube field-effect transistors, based on the top-of-the-barrier approach [12-14] and calibrated with BTE simulations, to shed insight into their RF linearity.

- (2) Develop a nonlinear circuit model for graphene field-effect transistors based on an extended top-of-the-barrier approach to include effects arising from the positional variation of the density of states and band-to-band tunneling, both of which arise from graphene's unique lack of a bandgap.

- (3) Use the developed nonlinear circuit model of GFETs from (2) to shed insight into their RF linearity.

To accomplish the above tasks, the Ph.D. research can be categorized into three stages. All three stages are complete, and have led to a significant journal paper in the *IEEE Transactions on Nanotechnology* [15] and a conference paper at the *IEEE SISPAD* conference held in Glasgow, Scotland in September, 2013 [16]. A third manuscript has been submitted to the *IEEE Transactions on Microwave Theory and Techniques* in August, 2014 [17].

chapter, it suffices to note that under the assumption that the electrons traveling from the source to the drain experience *no* collisions, the charge and current in the transistor can be known by keeping track of what happens at a *single point* in the channel, *i.e.*, the point at which the conduction band reaches its highest energy, the so-called *top of the* source-to-drain energy *barrier*.

1.3 Stages of Work

#### **1.3. Stages of Work**

A summary and a description of the key points of each stage of the Ph.D. are provided below; interested readers can find more details in Chapters 2, 3, and 4.

#### 1. RF Linearity Potential of Carbon-Nanotube Transistors Versus MOSFETs

#### Summary:

CNFETs are one of the most promising alternatives to conventional silicon MOSFETs, and their RF figures of merit show great potential for applications in high-frequency electronics [18-21]. To date, there has been a limited amount of theoretical and experimental work done on the nonlinear RF performance of CNFETs [22-24]. In the first stage of the Ph.D., we hence use a compact, nonlinear, small-signal equivalent circuit for array-based CNFETs based on the top-of-thebarrier approach [12-14] to investigate CNFET linearity. With this model, the linearity of CNFETs is shown to be comparable to --- not better than, as previously reported [22] --- their conventional MOSFET counterparts. Key mechanisms defining the nonlinear behavior of both CNFETs and MOSFETs are identified. Our work also reveals that a smaller pitch in CNFET arrays yields not only greater drive current but also better linearity (provided that the devices are sufficiently wide). Our published work [15] on this stage of the Ph.D. was reviewed as being "an excellent paper," with the study described as "systematic" and "very well-organized," and the conclusions deemed to be "of great interests [sic] to researchers working on carbon nanotube electronics."

#### Key Points:

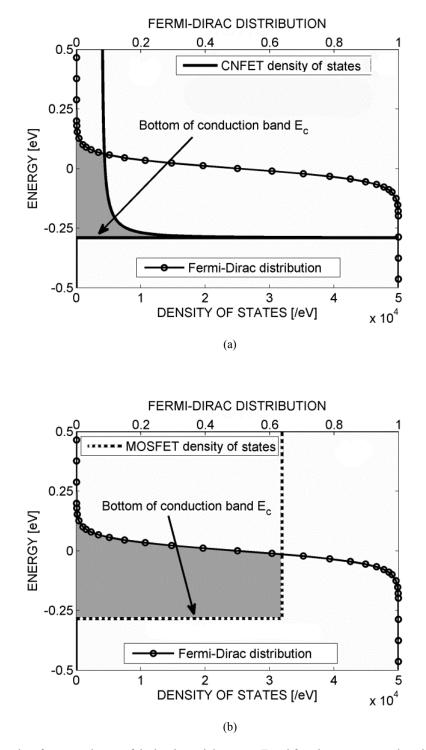

Linearity is an extremely important figure of merit in RF electronics because it dictates the ability of an analog amplifier to faithfully amplify a small ac input signal. In 2007, Baumgardner *et al.* [22] claimed that CNFETs have the potential to achieve "inherent linearity," *i.e.*, *perfectly* distortionless amplification. Although the study only considered distortion arising from the nonlinear current-voltage relationship (transport nonlinearity) of a CNFET, and neglected distortion arising from the nonlinear capacitance, the promise of "inherent linearity" was intriguing.

Hence, to probe the claim further, we investigated the impact of the nonlinear capacitance.

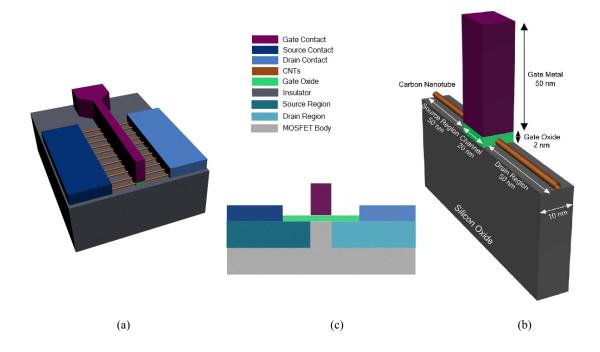

Fig. 1.1. (a) Schematic of the array-based CNFET used in stage 2 of the Ph.D. (b) Extrinsic nonlinear, smallsignal equivalent circuit of an array-based CNFET.

The array-based CNFET used in the study is reproduced here in Fig. 1.1(a), and Fig. 1.1(b) shows the nonlinear, small-signal equivalent circuit based on the top-of-the-barrier approach, assuming the CNFET contains n tubes. Details on the circuit are available in Chapter 2, where it is presented in Fig. 2.1.

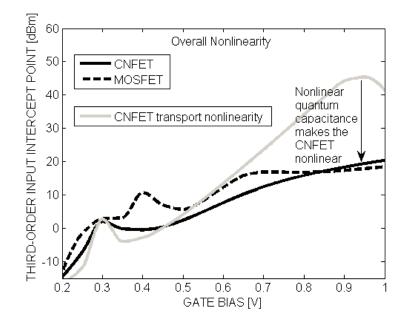

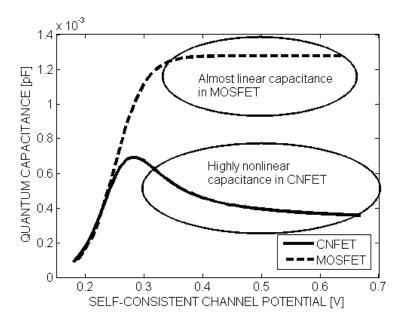

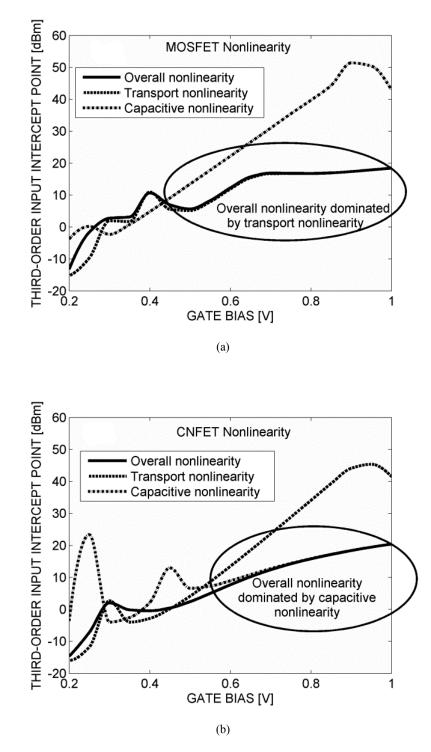

Our work reveals that although the linearity of a CNFET such as that in Fig. 1.1(a) seems to be superior to its MOSFET counterpart when only transport nonlinearity is considered, the nonlinear quantum capacitance makes the *overall* linearity of a CNFET comparable to that of a conventional MOSFET; this outcome is evident from the results displayed in Fig. 1.2. The nonlinear quantum capacitance is identified as the factor that degrades the linearity of CNFETs. The nonlinear 1D density of states of a CNFET yields a highly nonlinear quantum capacitance [the element  $n \cdot C_{sq}$  in Fig. 1.1(b)], which is to be contrasted with the essentially linear quantum capacitance arising from the essentially linear 2D density of states of a MOSFET.

Fig. 1.2. Intrinsic (neglecting parasitics) IIP3 vs. gate bias for a 20-nm ballistic array-based CNFET and a 20-nm ballistic conventional MOSFET.

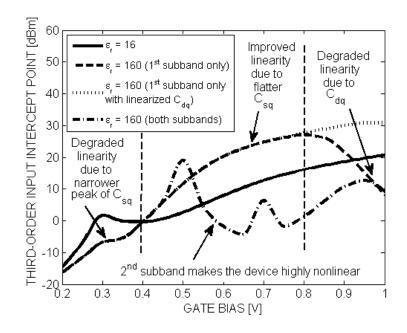

Ahsan UI Alam

It was also claimed in [22] that CNFETs can be made "inherently linear" in the limit of infinite gate-oxide capacitance. However, our work reveals the opposite to occur, *i.e.*, that the device becomes *less linear* under the influence of a large gate-oxide capacitance. The basic result can be discerned from the results in Fig. 1.3; the details of this figure (which is the same as Fig. 2.13) are discussed in Chapter 2, and here the essence can be noted by focusing on the solid, dotted, and stippled curves. The solid curve shows the linearity with a typical gate-oxide capacitance, achieved with a gate dielectric constant  $\varepsilon_r$  set to 16 (corresponding to hafnium oxide); increasing  $\varepsilon_r$  to 160 seems to improve the linearity, but *only* if we restrict our attention to the impact of the first conduction subband in the nanotube, as shown by the dotted curve; if we additionally account for the impact of the second conduction subband, the linearity degrades, as shown by the stippled curve. A more detailed explanation, including a connection of the behavior in Fig. 1.3 to the quantum-capacitance elements in Fig. 1.1(b), is provided in Section 2.3.3(b).

Fig. 1.3. Extrinsic (including parasitics) IIP3 vs. gate bias for a 20-nm ballistic array-based CNFET with different gate oxides.

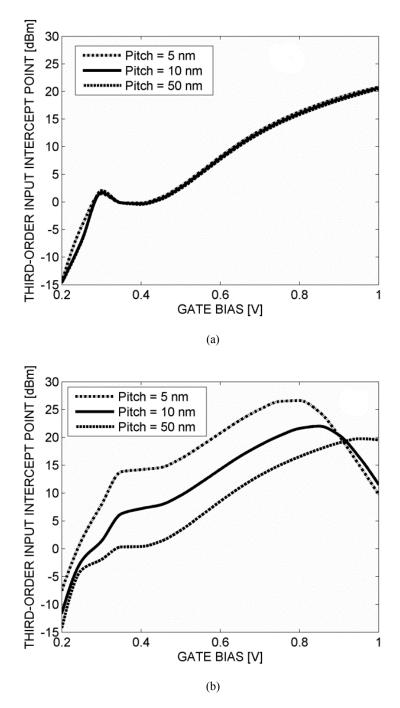

Fig. 1.4. Extrinsic (including parasitics) IIP3 vs. gate bias for a 30-µm wide ballistic array-based CNFET for different tube pitches.

Finally, in our work, we show that the extrinsic (including parasitics) linearity of an array-based CNFET depends on the tube pitch, provided that the device is sufficiently wide ( $\geq 30 \ \mu m$ ). The key results are shown in Fig. 1.4. Here, for a device having a channel width of 30  $\mu m$ , it is shown that the device becomes more linear as the tube pitch is decreased. This is a very favorable observation, as a smaller tube pitch also means a higher drive current and consequently a larger gain.

### 2. A Modified Top-of-the-Barrier Solver for Graphene and its Application to Predict RF Linearity

#### Summary:

Due to its unique electrical properties, graphene has recently been the center of attraction for new devices. Although the zero bandgap of graphene makes it difficult to employ in digital applications, the RF properties of graphene show great promise for high-frequency electronics [25, 26]. While GFETs have been analyzed and assessed using top-of-the-barrier models [27, 28], the accuracy of these approaches

suffer when nonidealities such as the positional variation of the density of states and band-to-band tunneling become prominent. In this stage of work, we have thus modified the conventional top-of-the-barrier model to account for these nonidealities, and we have developed a compact, nonlinear, circuit model that agrees with a highly sophisticated numerical solver based on NEGF [10]. Nonlinear analysis of the circuit showed that the linearity of GFETs is very sensitive to the drain bias, unlike with conventional transistors. Our initial findings were presented at the *IEEE Simulation of Semiconductor Processes and Devices (SISPAD) 2013* [16]. Detailed analysis of the developed nonlinear model was later conducted (in the third stage of the Ph.D. discussed below) to gain further insight into the physics behind the nonlinear operation of GFETs.

#### Key points:

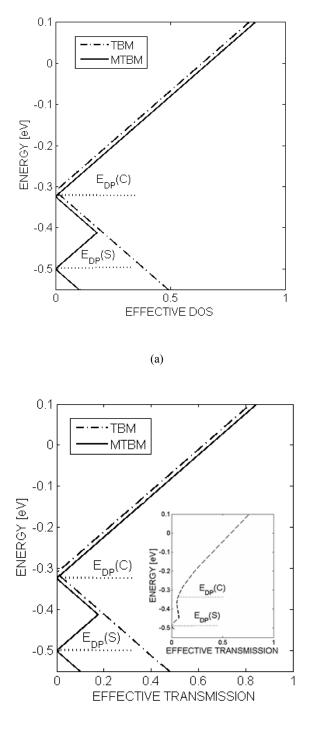

The modified top-of-the-barrier model developed in this stage captures the mentioned nonidealities through the following steps. First, we account for the fact that the densities of states in the heavily doped source and drain regions differ from the density of states (DOS) in the channel region; specifically, we construct an "effective DOS" that accounts for the fact that the DOS in the source and drain contacts vanish at the local Dirac points, precluding transmission at these energies. Second, since graphene has no bandgap, a major portion of the source-to-drain transport is mediated via band-to-band tunneling, which we include into the amended top-of-the-barrier model within the WKB approximation [29].

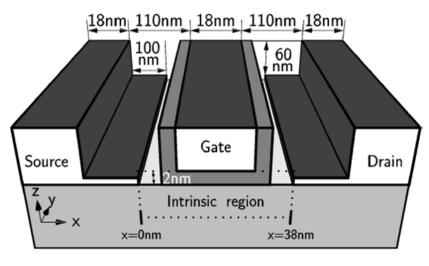

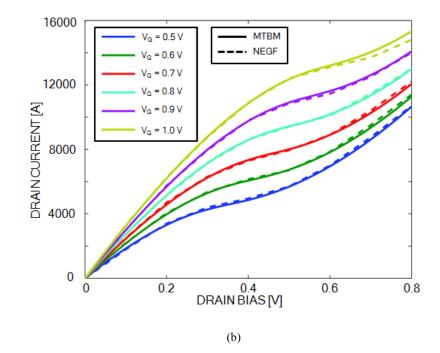

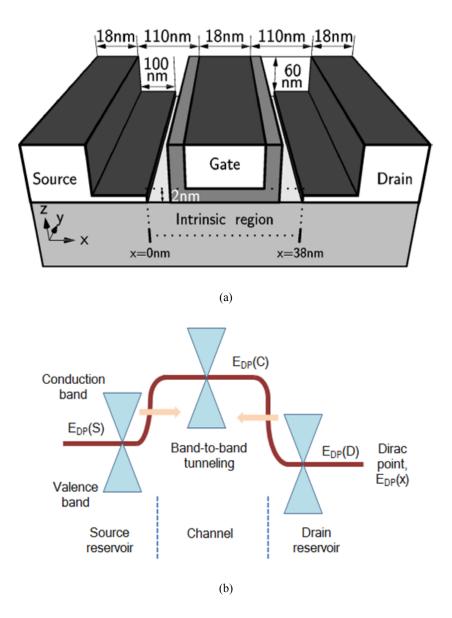

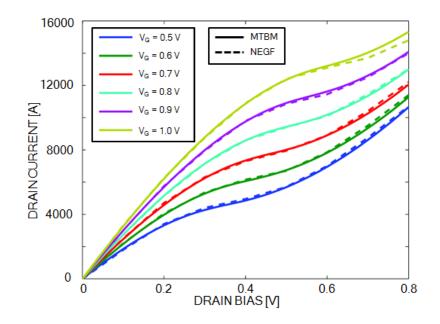

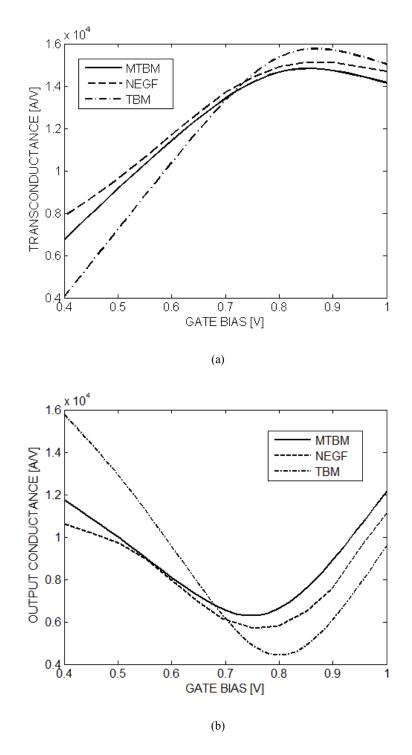

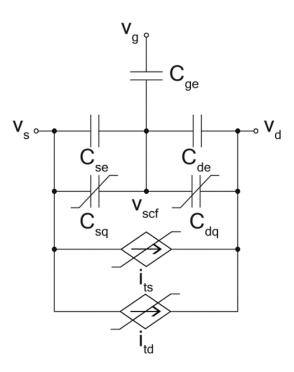

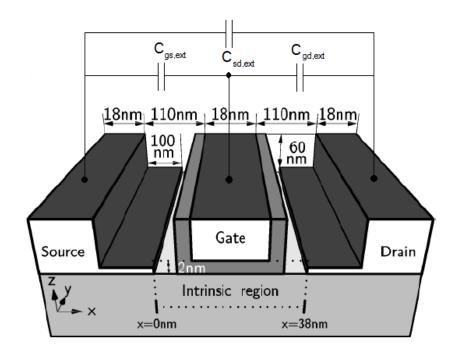

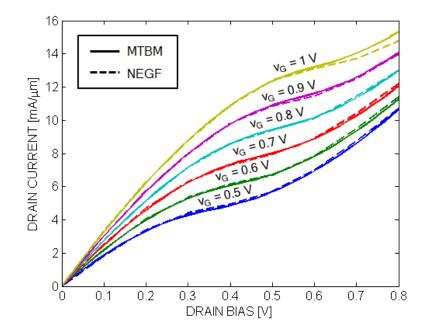

Fig 1.5(a) shows the structure of the GFET investigated. The structure is identical to the one used in [10]. Fig. 1.5(b) shows the current-voltage characteristics of the GFET from our amended top-of-the-barrier model and a self-consistent NEGF solver [10]. Considering the simplicity of our amended top-of-the-barrier approach, the agreement is quite remarkable. The developed model not only quantitatively matches the  $i_D - v_G$  output characteristics, but also is in good agreement with more sensitive quantities involving derivatives, such as the transconductance  $g_m$  and output conductance  $g_d$ , as demonstrated in Fig. 1.6(a). The second derivatives of the current with respect to gate voltage  $v_G$  are plotted in Fig. 1.6(b), which shows an

even better improvement over the conventional model. Such improved agreement is important for an accurate prediction of the RF properties, such as linearity, which requires a proper modeling of the slope and curvature of the transistor characteristics versus voltage.

Fig. 1.5. Schematic of the simulated GFET [10]. (b) Current-voltage characteristics of the GFET from NEGF and the modified top-of-the-barrier model.

Fig. 1.6. (a) Transconductance, output conductance (inset), and (b) first derivative of transconductance with respect to gate voltage of the GFET from NEGF, conventional top-of-the-barrier model, and modified top-of-the-barrier model.

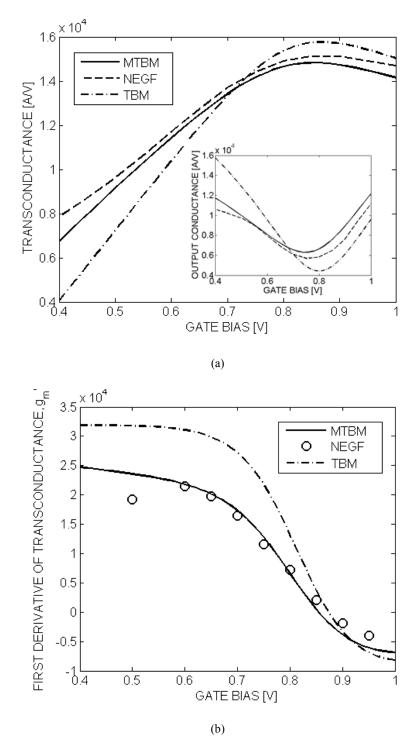

Fig. 1.7. IIP3 versus gate bias, with the drain bias held fixed at (a) 0.5 V and (b) 0.8 V, of the GFET compared to its CNFET and MOSFET counterparts.

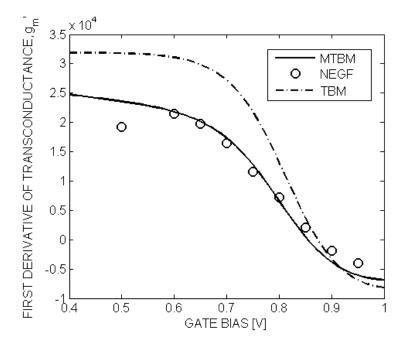

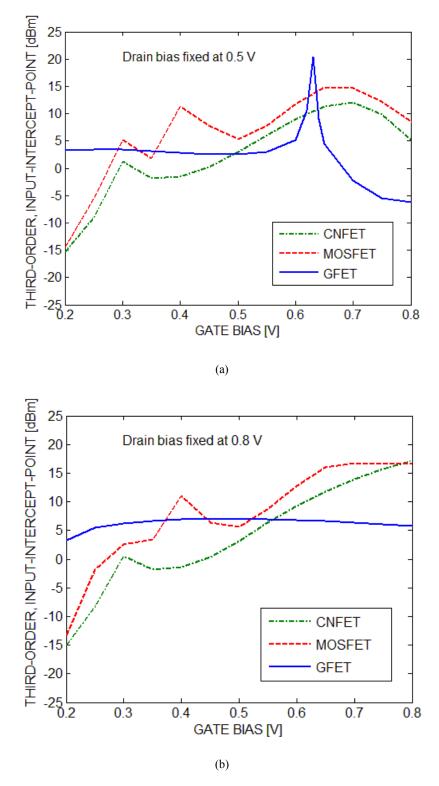

The modified top-of-the-barrier model allows us to predict the circuit properties of a GFET including all key physical effects, something that would be very difficult to do directly from first-principles formalisms such as NEGF. For example, we used the modified top-of-the-barrier approach to determine the element values for a GFET's equivalent circuit, which has the form in Fig. 1.8 [similar to that in Fig. 1.1(b)]. We then used the harmonic balance (HB) solver in Microwave Office [30] to determine the GFET's IIP3.<sup>4</sup> Fig. 1.7(a) shows that for a drain bias of 0.5 V, the IIP3 of the GFET is comparable to its CNFET and MOSFET counterparts, where the latter have dimensions and oxide capacitances identical to the GFET. Increasing the drain bias to 0.8 V slightly improves the GFET linearity but the overall IIP3 remains comparable to that of the CNFET and the MOSFET, as shown in Fig. 1.7(b). However, unlike a CNFET and a MOSFET, where the drain biasing has a minimum effect on the characteristics of the IIP3 curve, our results show that the shape of the IIP3 curve of GFETs is quite sensitive to the drain bias.

### 3. RF Linearity Performance Potential of Short-Channel Graphene Field-Effect Transistors

Summary:

This stage of work exploits the amended top-of-the-barrier model developed in the second stage of the Ph.D. (discussed above) to explore GFET linearity in greater detail.

To date, there have been only a few modeling studies that explore GFET linearity [31-33], and none of them accounted for all the sources of nonlinearity relevant for RF performance, and in particular, transport *and* capacitive nonlinearities, both of which can be expected to play a role [15]. In this final stage of work, we thus provide a more detailed and comprehensive study of the RF linearity mechanisms of an 18-nm GFET, chosen for demonstration purposes and consistent with current CMOS technology nodes [9]. Based on an examination of IIP3 values for

<sup>&</sup>lt;sup>4</sup> Please see footnote 2 on p. 2 for a definition of IIP3 that is sufficient for the present discussion.

intermodulation distortion under a two-tone input, our study reveals that a GFET's linearity has a *signature behavior* versus gate bias that includes a constant-linearity region at low gate bias, sweet spots of high linearity before and after the gate bias for peak  $f_T$ , and poor linearity at the gate bias corresponding to the peak  $f_T$ . We otherwise find that a GFET offers overall linearity that is comparable to a MOSFET and a CNFET, with the exception that the amount of intermodulation distortion in a GFET is dominated by the drain-injected carriers, a unique outcome of graphene's lack of a bandgap. We also examine the effects of drain bias, load resistance, and external parasitics.

#### Key Points:

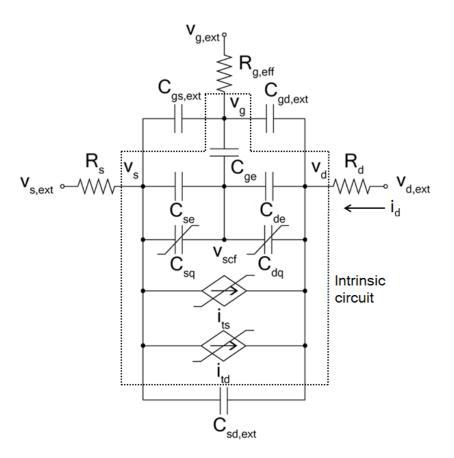

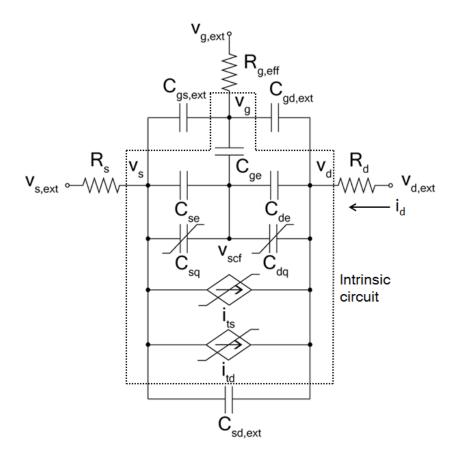

We start our analysis by using the nonlinear small-signal circuit of Fig. 1.8 [16]. The intrinsic components of the circuit are extracted based on the modified top-of-the-barrier model (MTBM) developed in the second stage [16]. The external parasitics are then calculated with the aid of COMSOL [34] and added to obtain the complete extrinsic nonlinear circuit, an approach that was already shown [16] in the second stage to capture the nonlinear voltage dependencies of key device parameters determined from a more detailed simulator [10]. The HB solver in Microwave Office (MWO) [30] is then used to simulate the nonlinear circuit.

Fig 1.5(a) show the structure of the GFET under investigation, identical to the one used in the second stage. Fig. 1.5(b) shows the current-voltage characteristics of the GFET from our modified top-of-the-barrier model and a self-consistent NEGF solver [10]. As in the earlier stages, we assume ballistic transport, a reasonable first approximation for graphene at small channel lengths ( $\leq 20$  nm) for the purposes of assessing performance potential, especially since the reported electron mean-free path in graphene is much larger ( $\geq 100$  nm) [7]. We also consider a doped MOSFET-like device, as done in recent studies to assess the performance potential of carbon-based electronics [14, 27]; short-channel MOSFET-like devices can be expected to outperform the long-channel Schottky-barrier devices prevalent today [35] and are a suitable choice to gauge performance potential.

Fig. 1.8: Complete nonlinear small-signal equivalent circuit of a ballistic GFET.

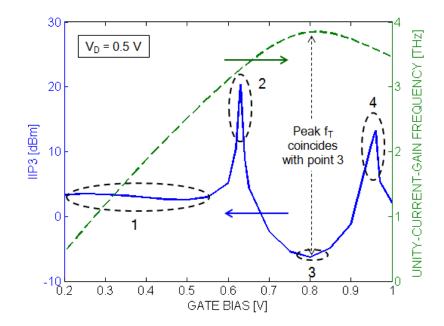

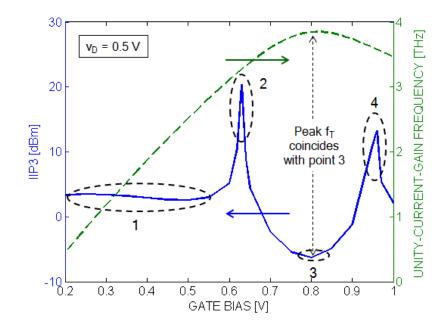

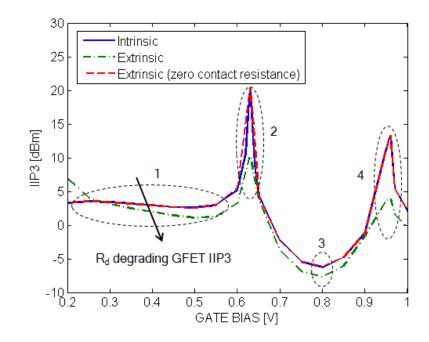

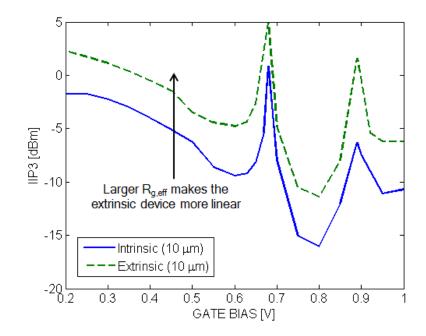

To reveal the key features of GFET linearity, we first investigated the intrinsic RF linearity of a GFET, *i.e.*, the linearity determined by the dotted portion of Fig. 1.8 and excluding external parasitics. The resulting IIP3 was plotted against variations in gate bias and is shown in Fig. 1.9. The IIP3 curve has a very distinct shape (signature), with a constant linearity region (region 1), two sharp peaks at points 2 and 4, and a large dip around point 3. The presence of the peaks at points 2 and 4 means that bias sweet spots may exist where a GFET will behave very linearly. Fig. 1.9 also shows the unity-current-gain frequency  $f_T$  versus gate bias. Note that the peak  $f_T$  coincides with point 3, which means the GFET is most nonlinear at peak  $f_T$ . A detailed discussion on the mechanism behind this signature behavior of GFET IIP3 is available in Chapter 4.

Fig. 1.9: Intrinsic IIP3 and unity-current-gain frequency  $f_T$  versus gate bias for the GFET under investigation.

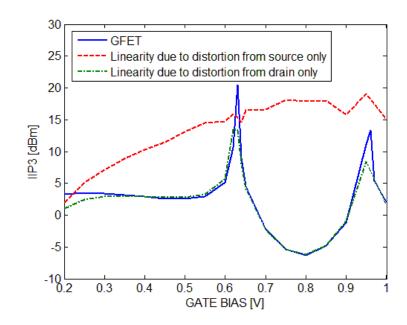

A closer look at the GFET linearity mechanism reveals that the zero bandgap of graphene results in a strong drain dependence in GFET linearity. By selectively turning on and off the distortion from the components in the circuit of Fig. 1.8, it is possible to isolate the distortion originating from the source and drain. The results are shown in Fig. 1.10, which plots the GFET IIP3 due to distortion coming only from the source and drain, respectively, and compares it with the overall IIP3. For all gate biases, the linearity of the device is found to be dominated by distortion coming from the drain. This result is significantly different from a conventional field-effect transistor in which the channel material has a finite bandgap (MOSFET or CNFET), where the distortion primarily comes from the source components [15].

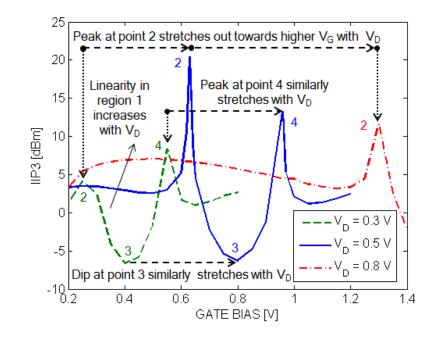

One obvious outcome of the drain dominance on GFET linearity is a drain-bias dependence of the overall linearity. For example, Fig. 1.11 (which is the same as Fig. 4.10) shows that in region 1 (constant linearity), a larger drain bias makes the device more linear; other aspects of the figure are discussed in Chapter 4.

Fig. 1.10: Effect of distortion from the source and drain on IIP3.

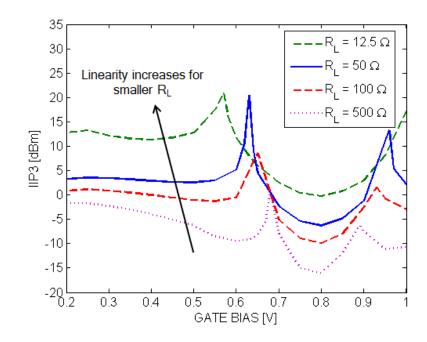

Another outcome of the drain dominance on GFET linearity is the effect of the load resistance  $R_L$ . A larger  $R_L$  enhances the distortion from the drain components and makes the device more nonlinear whereas a smaller  $R_L$  makes the device more linear by reducing the distortion generated by the drain components. Fig. 1.12 shows the effect of  $R_L$  on IIP3, while the source resistance is held at 50  $\Omega$ . As expected, reducing the load from 50  $\Omega$  to 12.5  $\Omega$  dramatically increases the GFET IIP3 by almost 10 dB. Similarly, increasing the value of  $R_L$  degrades linearity. The unique zero bandgap of graphene (the reason behind the drain dominance) thus makes it possible to improve the linearity by reducing the load resistance. However, before reducing  $R_L$  to improve the linearity, one must consider its implications on the voltage and power gains of the device, two desirable properties of any FET operating at RF frequencies. Such considerations, along with a more detailed discussion on the drain dependence of GFET linearity and its outcomes, are provided in Chapter 4.

Fig. 1.11: IIP3 versus gate bias, at a few different values of drain bias.

Fig. 1.12: Effect of load resistance  $R_L$  on GFET IIP3.

In order to determine if a GFET holds any promise in RF electronics in terms of linearity, we compare its linearity performance against that of a silicon MOSFET and an array-based CNFET with identical channel length (L = 18 nm), channel width

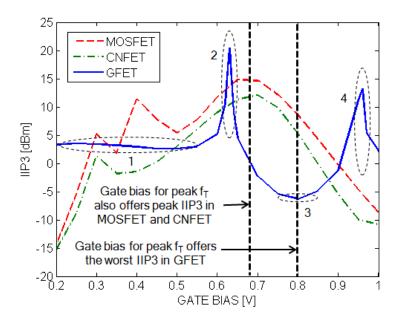

$(W = 1 \ \mu\text{m})$ , and gate capacitance. Fig. 1.13 shows that the GFET offers linearity that is, overall, comparable to its MOSFET and CNFET counterparts under this scenario. However, two differences can be flagged. First, as already discussed, the drain dependence of the GFET offers us with an opportunity to enhance its linearity by increasing the drain bias  $v_D$  or by lowering  $R_L$ , which is not possible in the other devices. Second, the GFET's linearity offers a sweet spot prior to and after peak  $f_T$ ; these are the points 2 and 4 discussed earlier in conjunction with Fig. 1.9. In fact, the GFET offers its worst IIP3 at peak  $f_T$ .

Fig. 1.13: Intrinsic linearity performance comparison of a GFET with its MOSFET and CNFET counterparts. The peak IIP3 for a CNFET and MOSFET occur at the same gate bias as peak  $f_T$  whereas for a GFET the minimum IIP3 occurs at the gate bias for peak  $f_T$ .

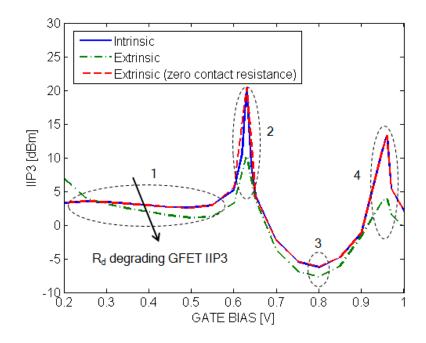

Simulation of the entire circuit in Fig. 1.8 reveals that the external parasitics slightly degrade the device linearity, but the signature shape identified from the intrinsic device remains, as demonstrated in Fig. 1.14. The drain contact resistance is shown to be primarily responsible for degrading the overall RF linearity of the GFET. Additionally, the presence of the drain contact resistance makes it impossible to reduce the distortion from the drain components by using a smaller  $R_L$ .

Fig. 1.14: Intrinsic and extrinsic IIP3 versus gate bias.

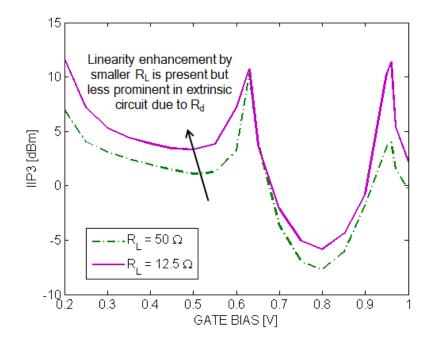

Fig. 1.15: Effect of load resistance  $R_L$  on GFET extrinsic IIP3. The improvement in IIP3 with a reduction in  $R_L$  is less pronounced than in the intrinsic case shown in Fig. 1.12.

Fig. 1.15 shows the effect of variation in  $R_L$  on linearity for the extrinsic GFET. The reduction in  $R_L$  that improved the linearity by almost 10 dB in the intrinsic circuit, as illustrated in Fig. 1.12, only improves the linearity by 2.2 dB in the extrinsic circuit. Keeping the drain contact resistance low is hence also important to allow for potential linearity improvement by adjusting  $R_L$ .

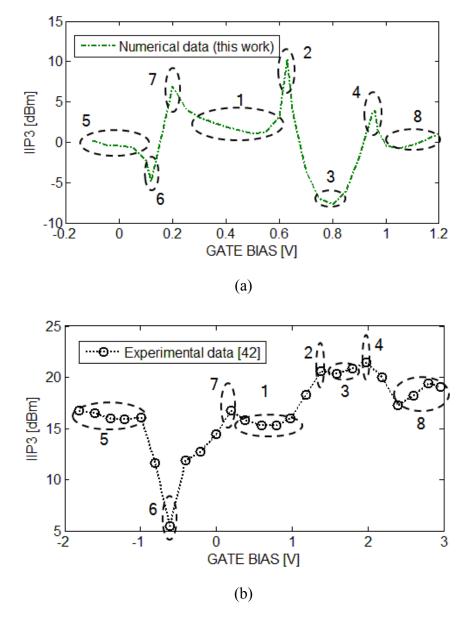

Fig. 1.16: Qualitative comparison of (a) numerical (extrinsic) IIP3 values of the GFET under investigation with (b) experimental data [42].

Finally, we compare our IIP3 values with experimental results. To date, there has been a significant amount of experimental work done on the RF linearity of graphene transistors [36-42]. However, all of these studies were done on long-channel devices  $(L \ge 250 \text{ nm})$ , which makes a *direct* comparison with our simulation results

impossible. Nonetheless, we can make a *qualitative* comparison to the reported IIP3 values in [42]. Fig. 1.16 shows that the key signature of the GFET IIP3 (regions 1 to 4), as identified in this work, is present even in the long-channel (L = 700 nm) device considered in [42]. Furthermore, by extending the gate bias values beyond the 0.2 V to 1 V range used for most of the simulations in our study,<sup>5</sup> we see that our model also captures the features in regions 5, 6, 7, and 8 seen in the fabricated device. For the purpose of this thesis, this comparison provides a striking qualitative validation of our modeling approach and our resulting observations on the linearity of GFETs. A more detailed discussion on the mismatch between the numerical and experimental results, and the mechanism behind the new features (regions 5 to 8), is included in Chapter 4. An even more detailed comparison and discussion will be presented in future work that is to be published separately from the work done directly for this thesis; the work done for this thesis, as summarized in this chapter and as laid out in full in Chapter 4, including the qualitative comparison to experiment, has been submitted to the IEEE Transactions on Microwave Theory and Techniques [17].

# 1.4. Summary of Contributions

The unique electrical properties of carbon-based materials have attracted a lot of attention from the semiconductor industry, and the promises of ultra-fast operation and near-ballistic transport have made carbon-based nanoscale transistors serious contenders in future RF electronics. This thesis has examined their linearity, a key RF property.

By revealing the key physical mechanisms, we have shown that the RF linearity of CNFETs and GFETs is comparable to their conventional silicon MOSFET counterpart. However, each of these devices offers unique opportunities for linearity enhancement that could potentially make them favorites in future RF applications.

<sup>&</sup>lt;sup>5</sup> In comparing the numerical and experimental data in parts (a) and (b) of Fig. 1.16, the *actual* gate bias and IIP3 values are not important; these will not overlap, as the two devices involved have different channel lengths. Of relevance is the *relative* positions of the identified regions and points with respect to gate bias, and the resulting *signature* in the IIP3 behavior.

In the case of CNFETs, the low 1D density of states of the nanotubes results in a very linear transport in the device. The same 1D density of states also results in a very nonlinear capacitance, which can ultimately limit the overall linearity to be on par with conventional silicon MOSFETs. However, our work also reveals that a practical array-based CNFET can potentially offer superior RF linearity by increasing the number of tubes in the channel and thereby enhancing the linearizing feedback [p.101, 43] provided by the extrinsic circuit components.

In the case of GFETs, the RF linearity is found to be dictated by graphene's 2D density of states and its zero bandgap. The zero bandgap introduces additional distortion from drain-injected carriers, which ultimately restricts the overall RF linearity of these devices and makes them comparable to conventional silicon MOSFETs. However, the unique 2D density of states combined with the zero bandgap creates linearity sweet spots, where highly linear behavior can be expected. In addition, the zero bandgap makes the GFET linearity sensitive to the load, which offers the potential for linearity enhancement by load manipulation.

Overall, our work in this Ph.D. shows that although the RF linearity of CNFETs and GFETs are comparable to conventional MOSFETs, both offer unique opportunities for linearity enhancements. This potential for enhanced linearity combined with their superior electrical characteristics continues to make these carbon-based nanoscale transistors very promising candidates for future RF electronics.

# **Chapter 2**

# **RF Linearity Potential of Carbon-Nanotube Transistors Versus MOSFETs<sup>6</sup>**

## 2.1. Introduction

CNFETs are promising candidates for emerging RF electronics [18], and they have recently been predicted to offer "inherent linearity" [22]. Linearity is an extremely desirable property for transistors operating at high frequencies, particularly for wireless communications [18]; for example, a small advantage in linearity could simplify the design and implementation of low-noise amplifiers (LNAs) used in wireless receivers and hence reduce the overall production cost. Given the potentially high values of unitycurrent-gain frequency ( $f_T$ ) [19, 21] and unity-power-gain frequency ( $f_{max}$ ) [20, 21] attainable by CNFETs, their potential for linear behavior merits further investigation.

To date, the study of CNFET linearity has been limited. In 2007, Baumgardner *et al.* [22] analytically showed that the current-voltage relationship of a ballistic CNFET can become "inherently linear" under certain conditions; while their approach considered only the transport current as a source of nonlinearity within the device, the claim of "inherent linearity" was nevertheless intriguing. In 2008, Curutchet *et al.* [23] measured the nonlinear behavior of a CNFET at a fundamental frequency of 600 MHz and suggested a simple model to predict the third-order intermodulation distortion. More

<sup>&</sup>lt;sup>6</sup> A version of this chapter has been published [15].

recently, in 2011, Wang *et al.* [24] reported promising linearity figures of merit for a nanotube transistor working at 1 GHz. As far as we know, no further studies of the linearity of CNFETs have emerged, and a more comprehensive investigation is thus warranted.

When it comes to classifying CNFETs based on their operation, there are mainly two types: the "MOSFET-like" [44-52] and the "zero-Schottky-barrier" [51-56] structure. From an experimental viewpoint, the fabrication of the latter is easier; however, MOSFET-like structures have been predicted to outperform their zero-Schottky-barrier counterparts in both digital [57, 58] and RF [59, 60] applications. In addition, for practical implementations, it is now well-known that array-based CNFETs (vs. single tubes) must be used [18, 61]. This work thus concentrates on the linearity of array-based, MOSFET-like CNFETs.

The starting point of our analysis is to develop a simplified model for the nonlinear behavior of a ballistic single-tube CNFET based on a "top-of-the-barrier" approach [12-14]; the assumption of ballistic transport can be justified by the ongoing scaling of device size and by the aim of performing a best-case assessment. Despite being simple in nature, the model is shown to be capable of capturing the nonlinear voltage dependencies of key device properties determined from a more detailed simulator [62], such as the voltage dependencies of the drain current and the  $f_T$ . Once the intrinsic nonlinear components of the single-tube transistor are extracted, they are used to generate the intrinsic components of an array-based CNFET. The external parasitics of the array-based structure are then calculated with the aid of COMSOL [34] and are appropriately added to get the complete extrinsic nonlinear model.

The HB simulator "Microwave Office (MWO)" [30] from AWR Corp. is used to simulate the developed nonlinear model (equivalent circuit). The simulator is used to measure the third-order input-intercept point (IIP3) [63] for a two-tone input, a widely accepted linearity figure of merit. With this approach, the linearity of an array-based CNFET is investigated for both typical and limiting structures, such as a structure in which the gate electrostatic capacitance is much larger than the quantum capacitance, a

scenario that might substantially enhance the device linearity, as predicted by Baumgardner *et al.* [22].

The main contribution of this work is a comparative study of the linearity of CNFETs vs. their MOSFET counterparts. Our work reveals that CNFETs are unlikely to offer a major advantage over conventional MOSFETs in terms of RF linearity, owing to the distortion arising from the nonlinear quantum capacitance in CNFETs. We also examine the channel-width and tube-pitch dependency of CNFET linearity.

Section 2.2 presents the device structure and the development of the nonlinear equivalent circuit based on the top-of-the-barrier approach. Section 2.3 compares the linearity of CNFETs with conventional CMOS transistors of similar specifications and also probes the overall high-frequency linearity of array-based CNFETs in terms of device parameters. The conclusions of this work are summarized in Section 2.4.

# 2.2. Approach

#### 2.2.1. Device Structure

Fig. 2.1(a) shows the structure of the top-gated, array-based CNFET used in this work, and Fig. 2.1(b) shows a portion of the transistor consisting of a single tube that can be considered as a single-tube CNFET. The tubes in the structure are all zigzag (16,0) carbon nanotubes with the following characteristics: a diameter of 1.25 nm; doped source and drain regions (outside the gate) that each have a background *n*-type doping level of  $10^9 \text{ m}^{-1}$  and a length of 50 nm; and an undoped *i* region (underneath the gate) of length 20 nm. The gate (or channel) length of 20 nm was chosen purely for demonstration purposes; the results will apply to any gate length for which the transport can be considered ballistic or simply as a best-case assessment. The planar gate oxide has a thickness of 2 nm and a relative dielectric constant of 16 (*i.e.*, hafnium oxide), and the gate metal has a thickness of 50 nm and a work function of 4.5 eV (*e.g.*, chrome or tungsten). The tubes sit on a thick (100-nm) layer of silicon oxide, and the total channel width is taken to be 1  $\mu$ m for demonstration purposes. Fig. 2.1(c) shows the conventional n-channel, Si MOSFET used for comparison. The gate/channel length is 20 nm and the oxide thickness is 3 nm with a relative dielectric constant of 16 (*i.e.*, hafnium oxide). The heavily doped source and drain regions have a doping density of  $10^{20}$  cm<sup>-3</sup>. The body is considered to be large enough to neglect the effect of the substrate for the sake of simplicity.

The CNFET gate capacitance is matched to that of its MOSFET counterpart by taking the number of tubes per  $\mu$ m to be 100, yielding a tube pitch of 10 nm. Existing literature shows that this is the maximum achievable density for CNFET arrays without significant tube-to-tube screening [64]. It is worth mentioning that a structure similar to that in Fig. 2.1(a) (but with a longer channel length and wider tube pitch) has been experimentally demonstrated [49].

Fig. 2.1. Schematics of (a) the array-based CNFET structure, (b) a portion of the transistor consisting of a single tube that can be considered as a single-tube CNFET, and (c) the conventional MOSFET counterpart. The figures are not drawn to scale.

#### 2.2.2. Intrinsic Equivalent Circuit

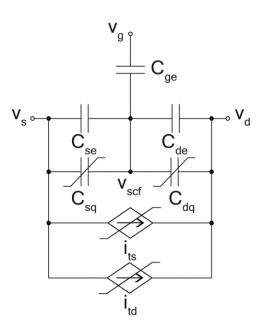

Fig. 2.2. Nonlinear equivalent circuit for a single-tube ballistic CNFET based on the purely linear topology developed in [14].

In this work, we focus on *small-signal* nonlinear operation, *i.e.*, of interest is the nonlinear behavior of small signals superimposed on dc bias values; we hence use Taylor-series expansions for all components in the small-signal equivalent circuit, where the coefficients of the series are specified by appropriate derivatives [evaluated at the bias (operating) point] of the corresponding large-signal device equations. Fig. 2.2 shows the topology of such a circuit for a single-tube CNFET, adapted from a purely linear small-signal equivalent circuit [14] based on the top-of-the-barrier model of Rahman *et al.* [13].

The elements in Fig. 2.2 are as follows:  $C_{ge}$ ,  $C_{se}$ , and  $C_{de}$  are the electrostatic capacitances of the CNFET and are presumed linear, an assumption justified further below;  $C_{sq}$  and  $C_{dq}$  are the nonlinear source and drain quantum capacitances, respectively; and  $i_{ts}$  and  $i_{td}$  are nonlinear sources that model the quasi-static transport

currents<sup>7</sup> of the device. Based on the small-signal assumption and the relationships discussed in [13, 14], the charge-voltage or current-voltage behavior of each nonlinear element is represented by a Taylor-series expansion up to third order:

$$q_{\rm sq} = C_{\rm sq1}(v_s - v_{\rm scf}) + C_{\rm sq2}(v_s - v_{\rm scf})^2 + C_{\rm sq3}(v_s - v_{\rm scf})^3$$

(2.1)

$$q_{\rm dq} = C_{\rm dq1}(v_d - v_{\rm scf}) + C_{\rm dq2}(v_d - v_{\rm scf})^2 + C_{\rm dq3}(v_d - v_{\rm scf})^3$$

(2.2)

$$i_{\rm ts} = g_{\rm sq1}(v_s - v_{\rm scf}) + g_{\rm sq2}(v_s - v_{\rm scf})^2 + g_{\rm sq3}(v_s - v_{\rm scf})^3$$

(2.3)

$$i_{\rm td} = g_{\rm dq1}(v_d - v_{\rm scf}) + g_{\rm dq2}(v_d - v_{\rm scf})^2 + g_{\rm dq3}(v_d - v_{\rm scf})^3$$

(2.4)

where  $q_{sq}$  and  $q_{dq}$  are the small-signal charges held by the quantum capacitances  $C_{sq}$  and  $C_{dq}$ , respectively,  $v_s$  and  $v_d$  are the small-signal source and drain voltages, respectively, and  $v_{scf}$  is the small-signal channel potential.

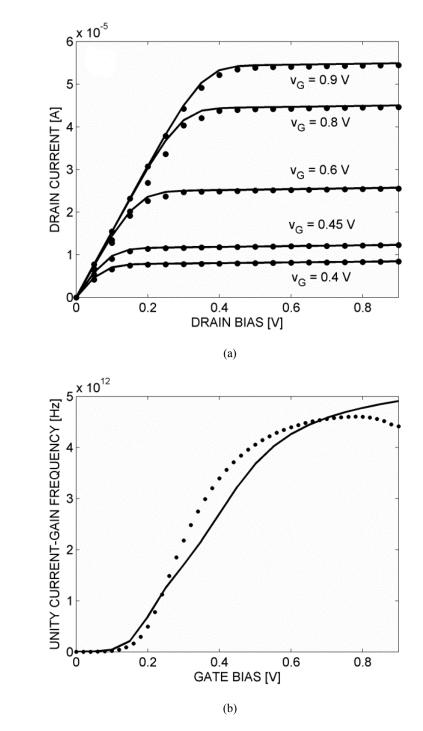

To extract the values of the coefficients in equations (2.1) - (2.4), the *large-signal* topof-the-barrier equations of [13, 14] were first solved and fitted to the output of the more detailed BTE-Poisson solver reported in [62]; with the recipe provided in [13], the values of the relevant fitting parameters from this process were  $E_F = -0.25$  eV,  $C_{ge}/C_e = 0.87$ , and  $C_{de}/C_e = 0.01$ , where  $C_e \equiv C_{ge} + C_{se} + C_{de}$  is the total electrostatic capacitance. Figs. 2.3(a) and 2.3(b) show the resulting agreement between the large-signal equations and the numerical solver [62]. With this agreement established, the coefficients in (2.1) – (2.4) could easily be obtained from the large-signal equations at any operating point of interest. The agreement in Fig. 2.3(a) shows that the nonlinear current-voltage behavior will be properly modeled by this procedure. Similarly, the agreement in Fig. 2.3(b), while more crude, shows that the overall nonlinear charge-voltage behavior of the device will be properly modeled [65] to an extent sufficient for the purposes of this work, *i.e.*, for a preliminary linearity assessment; it also shows that the agreement can be obtained under the assumption of linear electrostatic capacitances.

<sup>&</sup>lt;sup>7</sup> In this thesis, we use the following convention: small-signal voltages and currents are denoted by lowercase letters with lowercase subscripts whereas total (large-signal) voltages and currents are denoted by lowercase letters with uppercase subscripts. For convenience, bias (dc) voltages and currents, which are equal to the large-signal values at the operating point, are referenced by the same notation as the large-signal quantities, with the meaning clear from the context.

Fig. 2.3. (a) Family of current vs. bias voltage curves and (b) unity-current-gain frequency  $f_T$  vs. gate bias for a 20-nm single-tube CNFET. The solid lines represent the values from the top-of-the-barrier approach [12-14] and the black dots represent data from the BTE-Poisson solver reported in [62].

#### 2.2.3. Extrinsic Equivalent Circuit

#### a) Array-Based Structure

To model the behavior of an array-based structure (as opposed to a single tube), we assume all the individual single-tube CNFETs of an array have identical bias points; this can be justified by the negligible dc voltage drop on the metal gate (since the dc gate current is zero) and by the assumption that the source and drain biases are applied to all the tubes from the sides [from the left and right in Fig. 2.1(a)]. Since the tubes of an array are hence essentially in parallel, the intrinsic equivalent circuit for an *n*-tube array can be obtained simply by multiplying the power-series coefficients for each of the elements in Fig. 2.2 by n.

#### b) Parasitics

In practical CNFETs, the extrinsic (parasitic) circuit elements due to the metallic contacts are the main reason for the degradation of the cutoff frequencies ( $f_T$  and  $f_{max}$ ) from the theoretically predicted values. The impact of these parasitics on the linearity should also be assessed. Fig. 2.4 shows a cross-section of an array-based structure with the extrinsic capacitances marked, along with the dimensions of the gate and source/drain regions. The dashed portion of the figure (excluding the labeled extrinsic capacitances) can be modeled by the circuit of Fig. 2.2 with the element values multiplied by n, as already discussed. To such a circuit, we then add the labeled extrinsic capacitances, along with the contact resistances  $R_{g,eff}$ ,  $R_s$ , and  $R_d$  of the gate, drain, and source, respectively; all these parasitics were found as described in [21] with the aid of COMSOL [34] and by using the contact dimensions specified further below in Section 2.3.3(a). The final circuit is shown in Fig. 2.5, where  $v_s$ ,  $v_d$ , and  $v_g$  are the internal node voltages on the CNTs of an array and  $v_{s,ext}$ ,  $v_{d,ext}$ , and  $v_{g,ext}$  represent the external terminal voltages of the overall device. Table 2.1 in Section 2.3.3(a) lists all the component values (both intrinsic and extrinsic) for the device.

Fig. 2.4. Cross-section of the array-based CNFET structure used in this work.

Fig. 2.5. Complete nonlinear small-signal equivalent circuit for an array-based CNFET.

# 2.3. Results and discussion

#### 2.3.1. Condition for "Inherent Linearity"

In order to investigate the potential for "inherent linearity" in CNFETs, we need to establish the condition under which the *large-signal* transport current  $i_T \equiv i_{TS} + i_{TD}$ becomes a linear function of the gate voltage  $v_G$ , where  $i_{TS}$  and  $i_{TD}$  refer to the sourceand drain-injected components of the current, respectively, and where the source is taken as the reference ( $v_S \equiv 0$  V). As shown in Appendix B, under the assumption of a high drain voltage, where  $i_T \approx i_{TS}$ , the condition of Baumgardner *et al.* [22] for inherent linearity is equivalent to requiring that the ratio of channel charge to gate-oxide capacitance be much smaller than the gate voltage:

$$\left|\frac{\lambda}{C_{\rm ge}}\right| \ll v_G \tag{2.5}$$

where  $\lambda$  represents the channel charge. Based on condition (2.5), a MOSFET-like CNFET might hold promise for highly linear behavior, since the one-dimensional (1-D) density of states of a nanotube will tend to keep the channel charge  $\lambda$  small for a given  $v_G$ , while the use of high-k dielectrics can result in a large gate-oxide capacitance  $C_{\text{ge}}$ . However, (2.5) is derived while considering only the nonlinearity due to the transport current  $i_T \approx i_{\text{TS}}$ , *i.e.*, it neglects distortion arising from the quantum capacitances  $C_{\text{sq}}$  and  $C_{\text{dq}}$ ; this is equivalent to retaining the nonlinear small-signal current source  $i_{\text{ts}}$  in Fig. 2.2 (with  $i_{\text{td}} \approx 0$ ), while neglecting all distortion due to  $C_{\text{sq}}$  and  $C_{\text{dq}}$ . Hence, the *overall* nonlinearity of CNFETs, even if (2.5) is well satisfied, remains unclear, and it must be tested and compared to other devices.

#### 2.3.2. CNFET vs. CMOS Transistor

#### a) Basis and Method for Comparison

In order to determine whether a CNFET offers any advantage over its conventional MOSFET counterpart in terms of RF linearity, we also investigate the linearity of the MOSFET shown in Fig. 2.1(c) using the same top-of-the-barrier [12-14] approach used

for the CNFET. Besides having identical gate capacitances, the MOSFET is also assumed to have identical dimensions to the CNFET, including the channel length and width, and the size and orientation of the gate, source, and drain contacts. The barrier height at the top-of-the-barrier under equilibrium is kept identical to the CNFET at 0.25 eV.

MWO was used to simulate the nonlinear circuits of the CNFET and MOSFET using the harmonic-balance (HB) technique; the circuit of Fig. 2.2 was used for both devices, with the component values replaced by total values in the case of the MOSFET and single-tube values multiplied by the number of tubes n in the case of the CNFET. The load impedance was set to 50  $\Omega$ , the usual characteristic impedance for RF applications. A two-tone source with an impedance of 50  $\Omega$  and an operating frequency of 24 GHz ---which is an application frequency of interest as identified by the 2012 ITRS [9] --- and a difference of 100 kHz between the tones were used. The source was grounded, the drain bias  $v_D$  was fixed at 0.8 V, and the gate bias  $v_G$  was varied from 0.2 to 1.0 V.

#### b) Nonlinearity Due Only to Transport Current

To investigate the effect of the nonlinear transport current, both transistors were simulated with the nonlinear current sources  $i_{ts}$  and  $i_{td}$  in Fig. 2.2 fully active but with linearized quantum capacitances  $C_{sq}$  and  $C_{dq}$ , *i.e.*, with all the coefficients in (2.3) and (2.4) retained but with the higher order coefficients in (2.1) and (2.2) set to zero. The third-order input-intercept point (IIP3) at different gate biases is shown in Fig. 2.6.

The basic shape of the IIP3 vs. gate bias is comparable for the two devices, including the presence of an IIP3 sweet-spot in the low-bias region and an improvement in IIP3 with increasing bias; more importantly, as shown, with only the transport-current nonlinearity, the CNFET has a significantly higher IIP3 at high bias.

Fig. 2.6. Intrinsic IIP3 vs. gate bias for a 20-nm ballistic array-based CNFET and ballistic MOSFET, considering only nonlinear transport current.

Fig. 2.7. Channel charge (electron) density of the 20-nm ballistic array-based CNFET and ballistic MOSFET.

The reason for the better linearity of the CNFET at high bias in Fig. 2.6 can be discerned from the curves in Fig. 2.7, where it is shown that the CNFET has a

significantly lower channel charge at high gate bias ( $v_G \ge 0.5$  V), causing (2.5) to be better satisfied. To examine this outcome in greater detail, we first compare the bias dependence of the self-consistent channel potential of the two devices, and then use the result of that comparison to show how the difference in the densities of states in the two materials results in the variation in channel charge depicted in Fig. 2.7 and hence in the linearity according to (2.5).

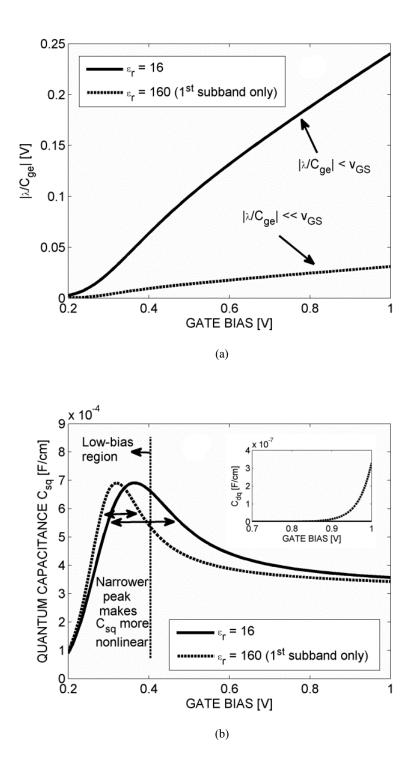

#### i) Bias Dependence of Self-Consistent Channel Potential

Fig. 2.8(a) shows the result for the self-consistent channel potential  $v_{SCF}$  as a function of the gate bias voltage  $v_G$ ; as shown, the values of  $v_{SCF}$  at each  $v_G$  are approximately equal in the two devices. To understand this result, which is not entirely obvious, we first note that for typical structures and for sufficiently large drain bias, the large-signal input equivalent circuit looking into the gate consists primarily of the series combination of  $C_{ge}$ and  $C_{sq}$ , with the latter being a nonlinear function of the voltage v across it. The stored charge on each of these two capacitors must be equal and represents the channel charge  $\lambda$ :

$$C_{\rm ge}(v_G - v_{\rm SCF}) = \lambda = \int_0^{v_{\rm SCF}} C_{\rm sq}(v) \, dv \tag{2.6}$$

where  $C_{sq}$  is written as  $C_{sq}(v)$  to emphasize its dependence on v. By differentiating both sides of (2.6) with respect to  $v_{SCF}$  and rearranging the result, we can find an expression for the rate of change of  $v_{SCF}$  with respect to  $v_G$ :

$$\frac{dv_{\rm SCF}}{dv_G} = \frac{C_{\rm ge}}{\left[C_{\rm ge} + C_{\rm sq}(v_{\rm SCF})\right]}$$

(2.7)

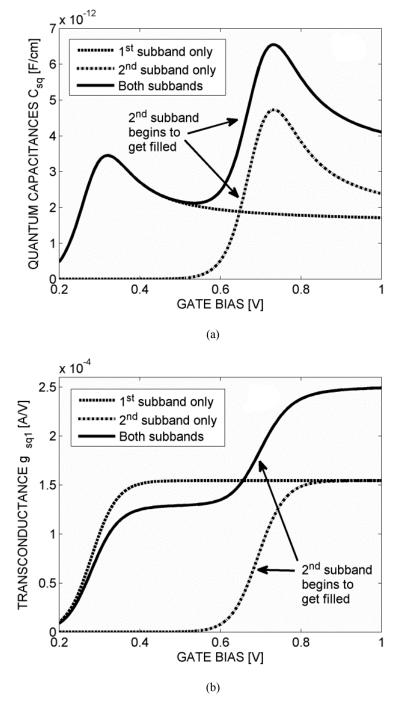

Fig. 2.8. (a) Self-consistent channel potential and (b) electrostatic and quantum capacitances ( $C_{ge}$  and  $C_{sq}$ ) vs. gate bias for a 20-nm ballistic array-based CNFET and ballistic MOSFET.