### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand comer and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

| • |  |  |

|---|--|--|

|   |  |  |

### University of Alberta

Design, Construction, and Control of a Teleoperated Mobile Robot Test-bed

by

L. M. Wyard-Scott

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Master of Science

Department of Electrical and Computer Engineering Edmonton, Alberta Fall 1999

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre reference

Our file Notre reference

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-47119-5

#### UNIVERSITY OF ALBERTA

#### RELEASE FORM

NAME OF AUTHOR: L. M. Wvard-Scott

TITLE OF THESIS: Design. Construction. and Control of a Teleoperated Mo-

bile Robot Test-bed

**DEGREE**: Master of Science

YEAR THIS DEGREE GRANTED: 1999

Permission is hereby granted to the UNIVERSITY OF ALBERTA LIBRARY to reproduce single copies of this thesis and to lend or sell such copies for private. scholarly or scientific research purposes only.

The author reserves all other publication rights and other rights in association with the copyright of the thesis, and except as hereinbefore provided neither the thesis nor any substantial portion thereof may be printed or otherwise reproduced in any material form whatever without the author's prior written permission.

(Signed) 1. Wyork South

Permanent Address: 24. 2204-118 Street

Edmonton, Alberta

CANADA

24 September 1999 Date:

### UNIVERSITY OF ALBERTA

### FACULTY OF GRADUATE STUDIES AND RESEARCH

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies and Research for acceptance, a thesis entitled **Design**, **Construction**, and **Control** of a **Teleoperated Mobile Robot Test-bed** submitted by **L**. **M**. **Wyard-Scott** in partial fulfillment of the requirements for the degree of Master of Science.

Q.-H. M. Meng (Supervisor)

Prof. R. P. W. Lawson

Prof. H. Zhang

Date: 23 Sept 1999

### Abstract

This thesis presents and applies design models for a teleoperated mobile robot test platform. Two models are used. The first is applied to hardware design and is derived from a test-bed's paramount requirement: flexibility. Flexibility manifests itself through modularity of the electronics, standardized connectors, and cross-platform technology selection.

The second design model, applied to software, is referred to as the Robotic Internet Platform (RIP) design paradigm. As with the hardware design model, modularity and flexibility are of utmost importance. This is achieved through selection of a platform-independent workcell software interface implemented using string data types. Code, modularly written, promotes recycling and thereby minimizes development time for research of a selected topic.

The requirements of the test-bed designed here are outlined in terms of active research areas. The reader is lead through the design process which adheres to the design models. A complete, functional, flexible, teleoperated mobile-robot system is presented.

# Acknowledgements

I owe gratitude to many people for helping me complete this document and the work associated with it. Dr. Q.-H. (Max) Meng has provided me with the intellectual environment that has made the experience pleasurable. C. Ronald Kube has given me guidance and advice that coerced me into focusing and breaking the daunting task before me into achievable, logical steps. Mike Lepatski has given me unfaltering friendship for many years, and has allowed me to bend his ear many times. This is something that I don't think I could have done without, and I look forward to bending his ear many more times in the future. Keith Lo's occasionally sardonic composure has lead me to many laughs which have made the difficult times easier. Kees den Hartigh, Norman Janz, and Shaju Zacharia, system administrators for the Department of Electrical and Computer Engineering are thanked for putting up with my occasionally uninformed questions, and providing a second-to-none computing environment in which this work was done. Rod Johnson has provided me with a lot of guidance in the workings of the University machine, and on many technical aspects which I needed to conquer. Michelle Lock has helped me through friendship and thorough knowledge of requirements of a graduate student. Glen Walker has made his vast knowledge of C and TCL available to which end the software design became easier. Hien Dang, Fraser Murch. Christy Dolynchuk have all spurred me onward to completion by assisting in tasks which I considered to be unrewarding. Thanks to Jonathan Baldwin whose generosity made my task a little easier. Mike Chen, James Smith, and Rod Frey have provided guidance and occasional pep-talks under the guise of friendship. I am very grateful to Dr. R.P.W. Lawson who never hesitated to share his sensibility and wisdom. Loretta Ludwig has spurred me onward by looking after everyday mundane tasks which the work load occasionally forced me to neglect. She has also helped me realize why this work is so important to me. More satisfaction is drawn from the process by this realization. Last, but not least. is my entire family. Without their support, the entire process would not have been possible.

# Contents

| 1 Introduction |      |             |                                              | j              |

|----------------|------|-------------|----------------------------------------------|----------------|

|                | 1.1  | Organizat   | ion                                          | <br>•          |

| 2              | Tele | operation S | Systems                                      | 3              |

|                | 2.1  | Introducti  | ion                                          | <br>3          |

|                | 2.2  | A Typical   | Teleoperation Platform                       | <br>4          |

|                | 2.3  | Teleroboti  | ics Research Areas                           |                |

|                |      | 2.3.1 Co    | ontrol                                       | <br>$\epsilon$ |

|                |      | 2.3.2 Co    | ommunication                                 | <br>7          |

|                |      | 2.3.3 Te    | lerobotic System Software                    | <br>7          |

|                |      | 2.3.4 Sy    | stem Architecture                            | <br>8          |

|                |      | 2.3.5 Us    | er-Interface Functionality and Human Factors | <br>g          |

|                |      | 2.3.6 Ser   | nsing Techniques                             | <br>10         |

|                | 2.4  | Summary     |                                              | <br>11         |

| 3              | Obj  | ectives and | System Design Models                         | 12             |

|                | 3.1  | Introducti  | on                                           | <br>12         |

|                | 3.2  | Functiona   | l Specifications                             | <br>13         |

|   | 3.3  | Electronic Hardware Design: The Test-Bed Model           | 14 |

|---|------|----------------------------------------------------------|----|

|   | 3.4  | Software Interface Design Model: The RIP Paradigm        | 16 |

|   |      | 3.4.1 Selection of the Operating System                  | 18 |

|   |      | 3.4.2 Design Implications                                | 18 |

|   |      | 3.4.3 User Interface Development Considerations          | 19 |

|   |      | 3.4.4 Workcell Control Engine Design Implications        | 20 |

|   | 3.5  | Summary                                                  | 21 |

| 4 | Syst | tem Overview                                             | 22 |

|   | 4.1  | Introduction                                             | 22 |

|   | 4.2  | The Control Station                                      | 23 |

|   |      | 4.2.1 Control Station Operating System                   | 25 |

|   | 4.3  | The Workcell PC Motherboard                              | 26 |

|   |      | 4.3.1 Workcell PC Operating System                       | 27 |

|   | 4.4  | Communication Technology                                 | 27 |

|   | 4.5  | The Client-Server Model                                  | 28 |

|   | 4.6  | Summary                                                  | 28 |

| 5 | Мос  | lular Workcell Hardware Design                           | 30 |

|   | 5.1  | Introduction                                             | 30 |

|   | 5.2  | Module Overview                                          | 31 |

|   |      | 5.2.1 Serial Level Conversion PCB                        | 33 |

|   |      | 5.2.2 Parallel-Port Expansion PCB                        | 34 |

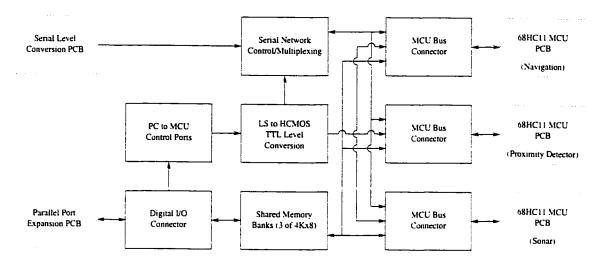

|   |      | 5.2.3 PC-to-MCU Shared Memory/Serial Network Control PCB | 34 |

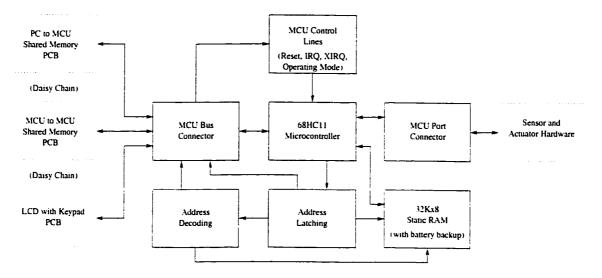

|   |      | 5.2.4 MC6HC11 Microcontroller (MCU) PCB                  | 35 |

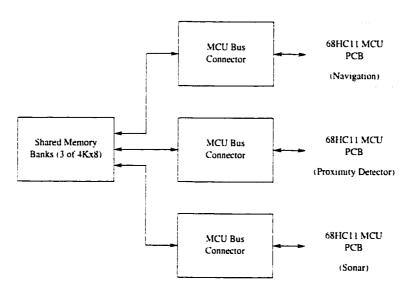

|   |      | 5.2.5 MCU-to-MCU Shared Memory PCB                       | 38 |

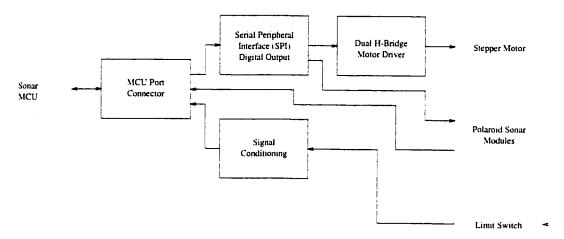

|   |     | 5.2.6    | SONAR Module Interface PCB                    | 39 |

|---|-----|----------|-----------------------------------------------|----|

|   |     | 5.2.7    | Near-Range IR Proximity Sensor PCB            | 40 |

|   |     | 5.2.8    | Bump Sensor PCB                               | 41 |

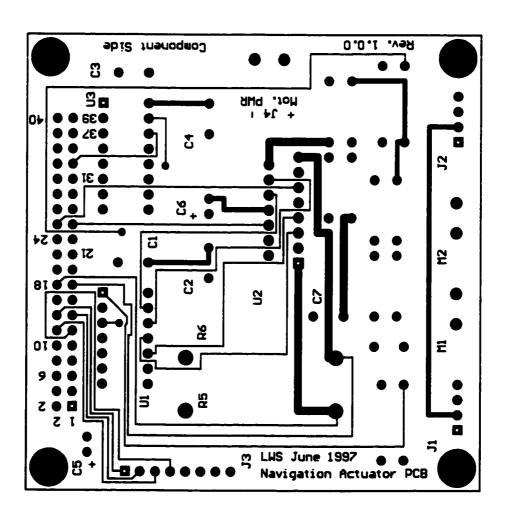

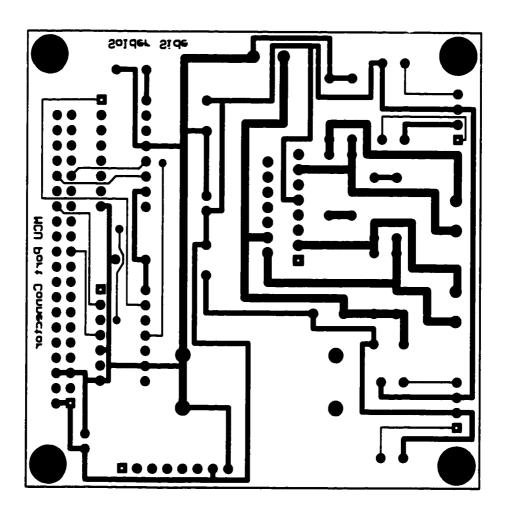

|   |     | 5.2.9    | Navigation Hardware PCB                       | 42 |

|   | 5.3 | Mecha    | anical Structure Overview                     | 42 |

|   |     | 5.3.1    | Structure                                     | 43 |

|   |     | 5.3.2    | Sensor Placement                              | 44 |

|   | 5.4 | Summ     | nary                                          | 46 |

| 6 | Mod | lular Sc | oftware Design                                | 48 |

|   | 6.1 | Introd   | uction                                        | 48 |

|   | 6.2 | Micro    | controller Layer Software                     | 49 |

|   |     | 6.2.1    | Development Platform: Interactive-C           | 49 |

|   |     | 6.2.2    | Software Operation                            | 51 |

|   | 6.3 | Server   | (Workcell Control Engine) Software            | 56 |

|   |     | 6.3.1    | Development Platform: Tool Command Language   | 57 |

|   |     | 6.3.2    | Software Operation                            | 58 |

|   |     | 6.3.3    | Programming Interface                         | 63 |

|   | 6.4 | Client   | (Control-Station) Software and User Interface | 64 |

|   |     | 6.4.1    | Development Platform: TCL/TK and C            | 64 |

|   |     | 6.4.2    | Socket Control Module                         | 65 |

|   |     | 6.4.3    | Navigation Console Module                     | 66 |

|   |     | 6.4.4    | Message Module                                | 67 |

|   |     | 6.4.5    | Sensor Status Display Module                  | 69 |

|   |     | 646      | Mapper Module                                 | 71 |

|   | 6.5      | Summary                                       | 72         |

|---|----------|-----------------------------------------------|------------|

| 7 | Resi     | ults and Demonstrations                       | 75         |

|   | 7.1      | Introduction                                  | <b>7</b> 5 |

|   | 7.2      | Setpoint Movement Test                        | 75         |

|   | 7.3      | Bump Sensor Test                              | 78         |

|   | 7.4      | Infrared Sensor Test                          | 78         |

|   | 7.5      | SONAR Sensor Test                             | 78         |

|   | 7.6      | Summary                                       | 82         |

| 6 | <b>C</b> |                                               |            |

| 8 | Con      |                                               | 83         |

|   | 8.1      | Summary of Contribution                       | 83         |

|   | 8.2      | Evaluation of the Design and Design Technique | 84         |

|   |          |                                               |            |

| E | Biblio   | ography                                       | 85         |

|   |          |                                               |            |

| A | ppe      | ndix                                          |            |

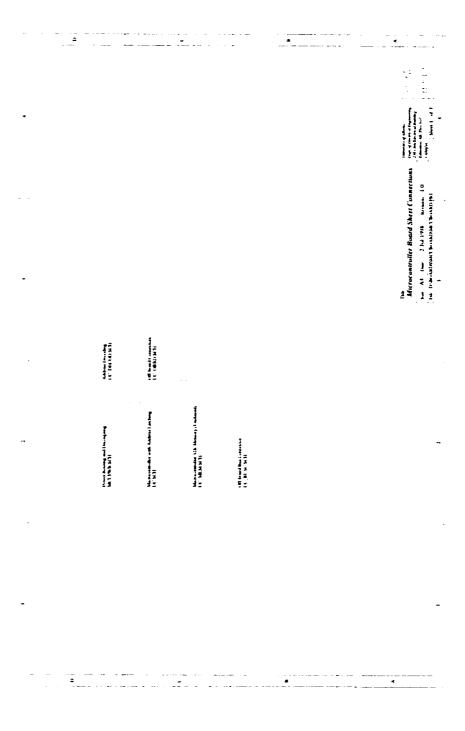

| A | МС       | 68HC11 Microcontroller PCB                    | 90         |

|   | A.1      | Introduction                                  | 90         |

|   |          |                                               | 90         |

|   |          |                                               | 91         |

|   |          |                                               |            |

|   |          | A.2.2 Control-Line Circuitry                  | 91         |

|   |          | A.2.3 Address Latching                        | 92         |

|   |          | A.2.4 Static RAM                              | 92         |

|   |          | A.2.5 Address Decoding                        | 93         |

|   | A.3         | User-settable Options               | 93 |

|---|-------------|-------------------------------------|----|

|   |             | A.3.1 Reset Switch: SW1             | 93 |

|   |             | A.3.2 CPU Mode Control: J2          | 94 |

|   |             | A.3.3 Power Select: JP1             | 94 |

|   | A.4         | Connector Descriptions              | 94 |

|   |             | A.4.1 Bus Connector: J1             | 94 |

|   |             | A.4.2 Power Connector: J3           | 97 |

|   |             | A.4.3 Port Connector: J4            | 97 |

|   |             | A.4.4 Piezo Buzzer Connector: J5    | 98 |

|   |             | A.4.5 Serial Data Connector: J6     | 99 |

|   | A.5         | Future Improvements                 | 99 |

|   | A.6         | Schematic Diagrams and Board Layout | 00 |

|   |             | A.6.1 Part List                     | 00 |

| В | Seria       | al-Level Conversion PCB             | 11 |

|   | B.1         | Introduction                        | 11 |

|   | B.2         | Connector Descriptions              | 11 |

|   |             | B.2.1 PC RS-232 Connector: J1       | 11 |

|   |             | B.2.2 HC11 TTL Serial Connector: J2 | 12 |

|   | B.3         | Future Improvements                 | 12 |

|   | B.4         | Schematic Diagrams and Board Layout | 13 |

|   |             | B.4.1 Part List                     | 13 |

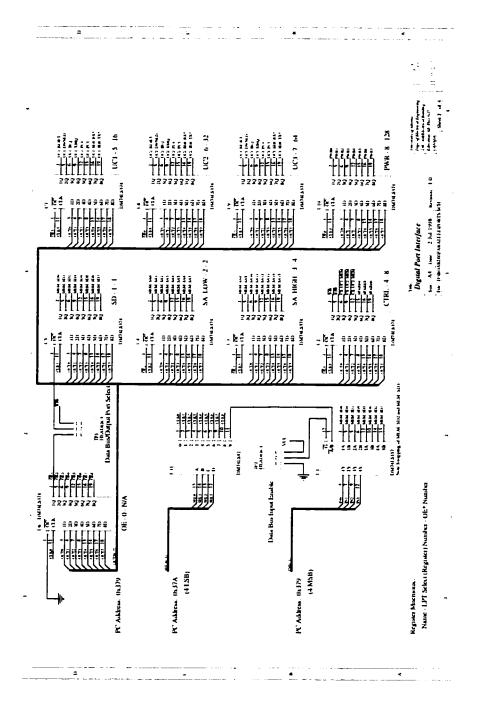

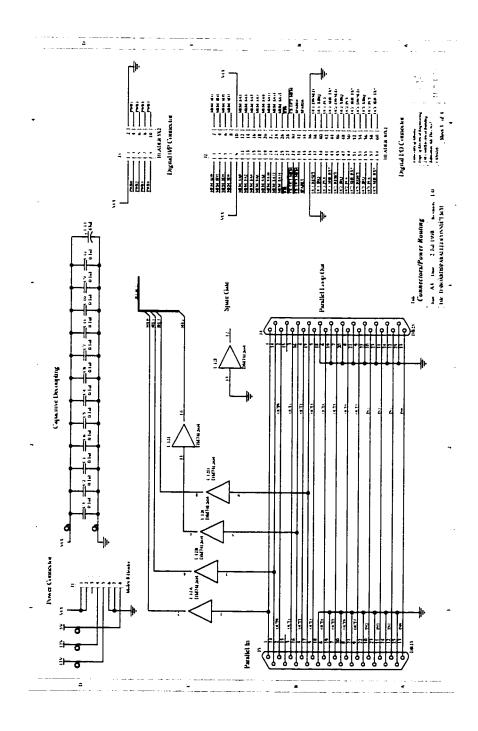

| С | Para        | allel Port Expansion PCB            | 17 |

|   | C.1         | Introduction                        | 17 |

|   | <b>C</b> .2 | Operation                           | 18 |

|   |            | C.2.1                                                     | Register Descriptions              | 118                                           |

|---|------------|-----------------------------------------------------------|------------------------------------|-----------------------------------------------|

|   | C.3        | User-se                                                   | ettable Options                    | 121                                           |

|   |            | C.3.1                                                     | Data Bus/Output Port Select: JP1   | 121                                           |

|   |            | C.3.2                                                     | Data Bus Input Enable: JP2         | 121                                           |

|   | C.4        | Connec                                                    | ctor Descriptions                  | 122                                           |

|   |            | C.4.1                                                     | Power Connector: J1                | 122                                           |

|   |            | C.4.2                                                     | Digital I/O Connector: J2          | 122                                           |

|   |            | C.4.3                                                     | Digital O/P Connector: J3          | 124                                           |

|   |            | C.4.4                                                     | Parallel Port Connector: J4 and J5 | 124                                           |

|   | C.5        | Design                                                    | Limitations                        | 125                                           |

|   | C.6        | Future                                                    | Improvements                       | 126                                           |

|   | C.7        | Schema                                                    | atic Diagrams and Board Layout     | 127                                           |

|   |            |                                                           |                                    |                                               |

|   |            | C.7.1                                                     | Part List                          | 127                                           |

| D | PC-t       |                                                           | Part List                          | 127<br>135                                    |

| D |            | o-MCU                                                     |                                    |                                               |

| D | D.1        | o-MCU<br>Introdu                                          | Shared Memory PCB                  | 135                                           |

| D | D.1        | o-MCU<br>Introdu<br>Operat                                | Shared Memory PCB                  | 135<br>135                                    |

| D | D.1        | o-MCU<br>Introdu<br>Operat<br>D.2.1                       | Shared Memory PCB  iction          | 135<br>135<br>135<br>136                      |

| D | D.1        | o-MCU<br>Introdu<br>Operat<br>D.2.1<br>D.2.2              | Shared Memory PCB  iction          | 135<br>135<br>135<br>136                      |

| D | D.1<br>D.2 | o-MCU<br>Introdu<br>Operat<br>D.2.1<br>D.2.2<br>D.2.3     | Shared Memory PCB  iction          | 135<br>135<br>135<br>136                      |

| D | D.1<br>D.2 | o-MCU Introdu Operat D.2.1 D.2.2 D.2.3 Connec             | Shared Memory PCB  iction          | 135<br>135<br>135<br>136<br>136               |

| D | D.1<br>D.2 | o-MCU Introdu Operat D.2.1 D.2.2 D.2.3 Connec D.3.1       | Shared Memory PCB  Iction          | 135<br>135<br>135<br>136<br>136<br>137        |

| D | D.1<br>D.2 | o-MCU Introdu Operat D.2.1 D.2.2 D.2.3 Connec D.3.1 D.3.2 | Shared Memory PCB  Iction          | 135<br>135<br>135<br>136<br>136<br>137<br>137 |

|   | D.5  | Future Improvements                       | 38 |  |

|---|------|-------------------------------------------|----|--|

|   | D.6  | Schematic Diagrams and Board Layout       | 39 |  |

|   |      | D.6.1 Part List                           | 39 |  |

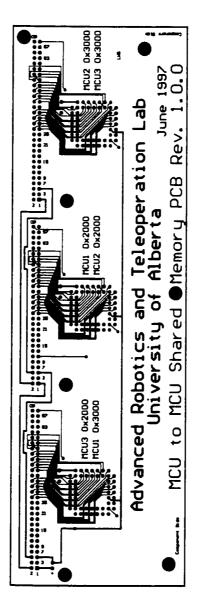

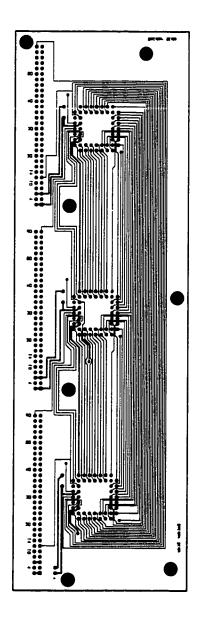

| E | мс   | U-to-MCU Shared Memory PCB                | 49 |  |

|   | E.1  | Introduction                              | 49 |  |

|   | E.2  | Operation                                 | 49 |  |

|   | E.3  | Connector Descriptions                    | 50 |  |

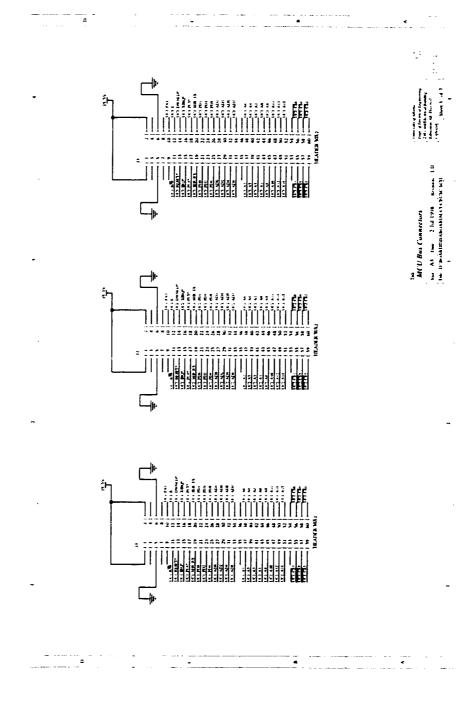

|   |      | E.3.1 MCU Bus Connectors: J2-J4           | 50 |  |

|   | E.4  | Design Limitations                        | 50 |  |

|   | E.5  | Future Improvements                       | 50 |  |

|   | E.6  | Schematic Diagrams and Board Layout       | 51 |  |

|   |      | E.6.1 Part List                           | 51 |  |

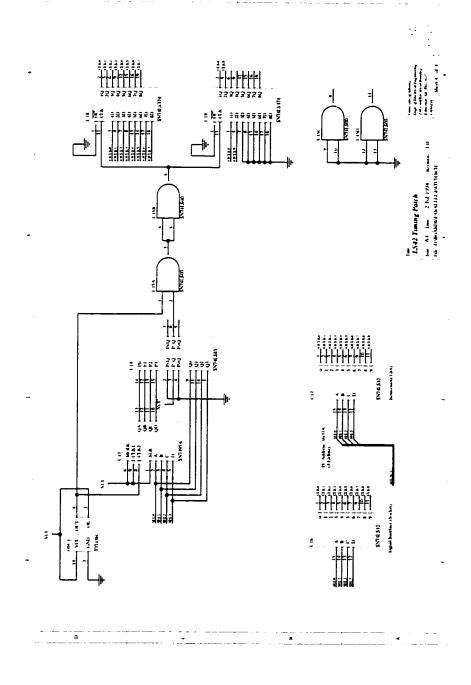

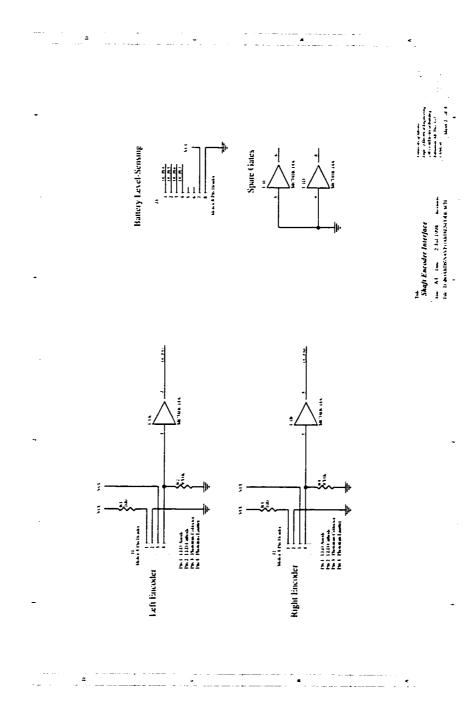

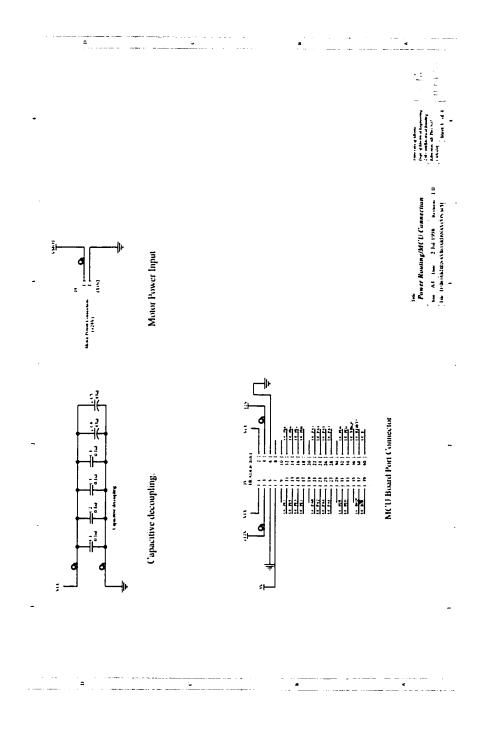

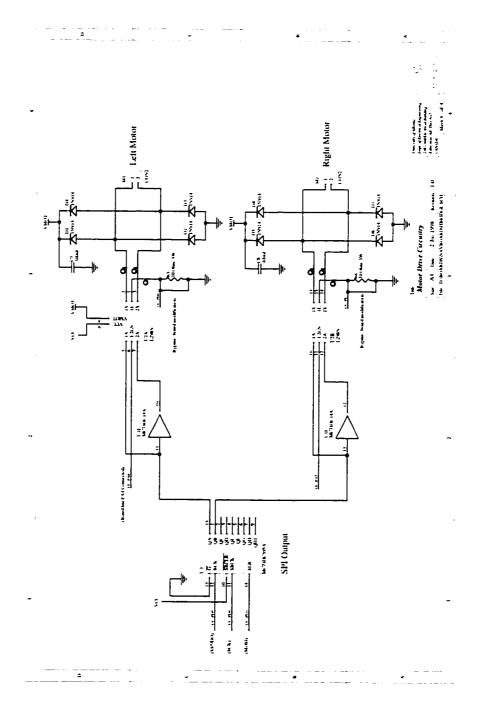

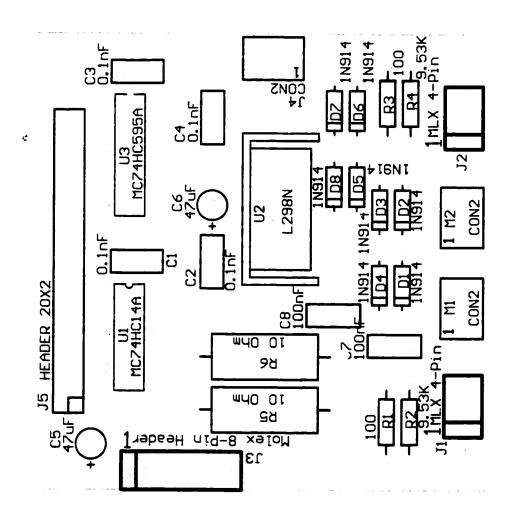

| F | Navi | gation Hardware PCB                       | 59 |  |

|   | F.1  | Introduction                              | 59 |  |

|   | F.2  | Operation                                 | 60 |  |

|   | F.3  | Connector Descriptions                    | 61 |  |

|   |      | F.3.1 Encoder Connectors: J1. J2          | 61 |  |

|   |      | F.3.2 Battery-level Sensing Connector: J3 | 61 |  |

|   |      | F.3.3 Motor Power Connector: J4           | 62 |  |

|   |      | F.3.4 Port Connector: J5                  | 62 |  |

|   | F.4  | Future Improvements                       | 62 |  |

|   | F.5  | Schematic Diagrams and Board Layout       | 62 |  |

|   |      | F.5.1 Part List                           | 63 |  |

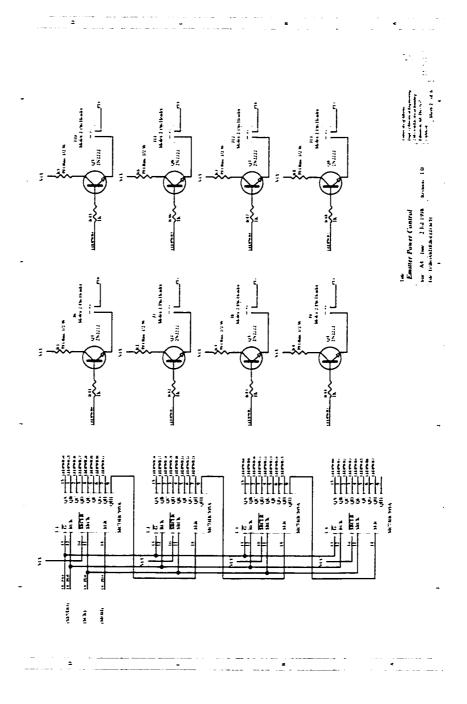

| G | Near | r-Range IR Proximity Sensor PCB         | 171 |  |  |

|---|------|-----------------------------------------|-----|--|--|

|   | G.1  | Introduction                            |     |  |  |

|   | G.2  | Operation                               |     |  |  |

|   |      | G.2.1 Digital Output (Emitter Control)  | 172 |  |  |

|   |      | G.2.2 Analog Input (Detector Reading)   | 172 |  |  |

|   | G.3  | Connector Descriptions                  | 174 |  |  |

|   |      | G.3.1 Port Connector: J1                | 174 |  |  |

|   |      | G.3.2 IR Pair Power Connectors: J2-J5   | 174 |  |  |

|   |      | G.3.3 J5-J37: IR Pair Signal Connectors | 174 |  |  |

|   | G.4  | Design Limitations                      | 175 |  |  |

|   | G.5  | Future Improvements                     | 175 |  |  |

|   | G.6  | Schematic Diagrams and Board Layout     | 175 |  |  |

|   |      | G.6.1 Part List                         | 175 |  |  |

| Н | Bum  | ap Sensor PCB                           | 185 |  |  |

|   | H.1  | Introduction                            | 185 |  |  |

|   | H.2  | Operation                               | 185 |  |  |

|   | H.3  | Connector Descriptions                  | 186 |  |  |

|   |      | H.3.1 Port Connector: J1                | 186 |  |  |

|   |      | H.3.2 Bump Sensor Connectors: J2-J17    | 187 |  |  |

|   | H.4  | Design Limitations                      | 187 |  |  |

|   | H.5  | Future Improvements                     | 187 |  |  |

|   | H.6  | Schematic Diagrams and Board Layout     | 188 |  |  |

|   |      | H.6.1 Part List                         | 188 |  |  |

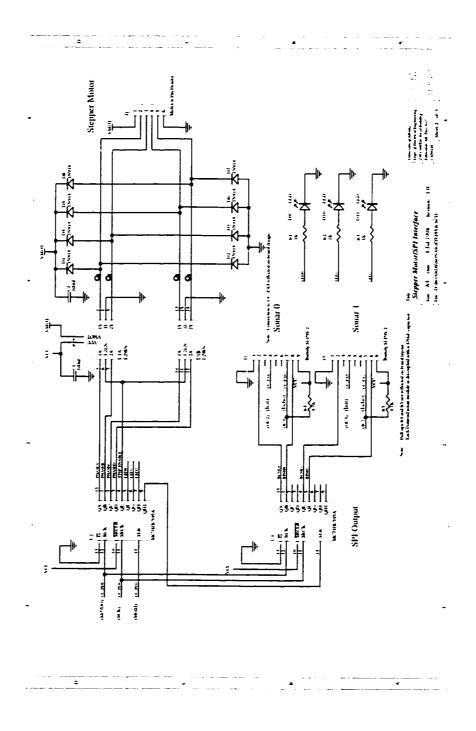

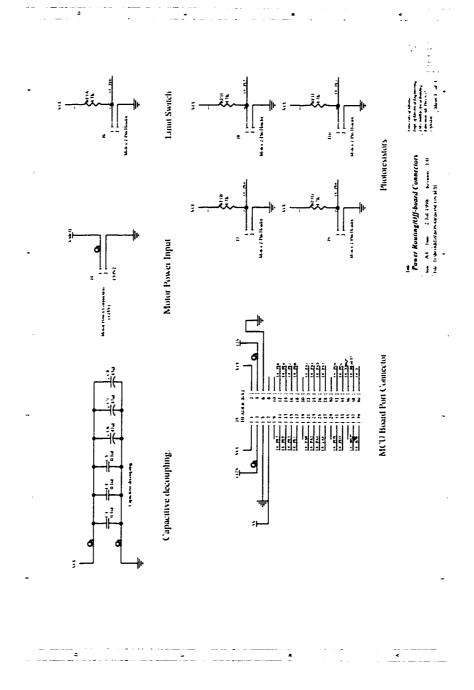

| I | Sona | nar Module Interface PCB |                                   |     |  |  |

|---|------|--------------------------|-----------------------------------|-----|--|--|

|   | I.1  | Introd                   | luction                           | 195 |  |  |

|   | I.2  | Opera                    | tion                              | 195 |  |  |

|   | I.3  | Conne                    | ector Descriptions                | 197 |  |  |

|   |      | I.3.1                    | Stepper Motor Connector: J1       | 197 |  |  |

|   |      | I.3.2                    | Polaroid Module Connector: J2, J3 | 197 |  |  |

|   |      | I.3.3                    | Motor Power Connector: J4         | 199 |  |  |

|   |      | I.3.4                    | MCU Port Connector: J5            | 199 |  |  |

|   |      | I.3.5                    | Limit-Switch Connector: J6        | 199 |  |  |

|   |      | I.3.6                    | Photoresistor Connectors: J7-J10  | 199 |  |  |

|   | I.4  | Future                   | e Improvements                    | 200 |  |  |

|   | 1.5  | Schem                    | atic Diagrams and Board Layout    | 200 |  |  |

|   |      | I.5.1                    | Part List                         | 200 |  |  |

| J | Code | e Docui                  | mentation                         | 208 |  |  |

|   | J.1  | Micro                    | controller Code                   | 208 |  |  |

|   |      | J.1.1                    | File message.c                    | 208 |  |  |

|   |      | J.1.2                    | File memory.c                     | 209 |  |  |

|   |      | J.1.3                    | File spi.c                        | 209 |  |  |

|   |      | J.1.4                    | Navigation MCU Code               | 210 |  |  |

|   |      | J.1.5                    | Proximity Detector MCU Code       | 213 |  |  |

|   |      | J.1.6                    | SONAR MCU Code                    | 213 |  |  |

|   | J.2  | Server                   | (Workcell Control Engine) Code    | 215 |  |  |

|   |      | J.2.1                    | ANSI C Mapping Code               | 215 |  |  |

|   |      | J.2.2                    | TCL Mapping Code                  | 218 |  |  |

|    |       | J.2.3   | ANSI C Parallel Port I/O Code     | 220 |

|----|-------|---------|-----------------------------------|-----|

|    |       | J.2.4   | TCL Shared Memory Interface Code  | 223 |

|    |       | J.2.5   | Server Module Code                | 224 |

|    | J.3   | Client  | (Control Station) Code            | 225 |

|    |       | J.3.1   | Socket Control Module Code        | 226 |

|    |       | J.3.2   | Navigation Console Module Code    | 226 |

|    |       | J.3.3   | Message Module Code               | 227 |

|    |       | J.3.4   | Sensor Status Display Module Code | 227 |

|    |       | J.3.5   | Mapper Module Code                | 228 |

|    |       | J.3.6   | Functions                         | 228 |

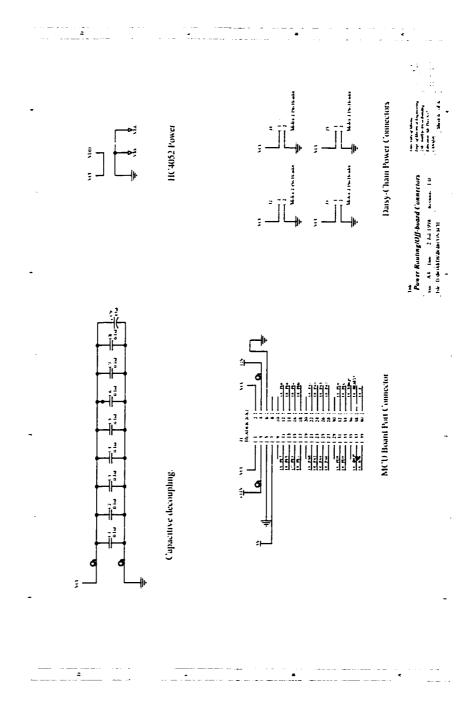

| K  | Pow   | er-Up S | teps                              | 233 |

|    | K.1   | PPP C   | Connection to the Workcell        | 233 |

|    | K.2   | Downl   | oading the MCU Layer Code         | 234 |

|    | K.3   | Startin | ng the Workcell Server            | 235 |

|    | K.4   | Startin | ng the Control Station Client     | 236 |

| Gl | ossai | ry      |                                   | 237 |

# List of Tables

### Table

| 6.1 | Allocation of the shared memory.                 | 53  |

|-----|--------------------------------------------------|-----|

| A.1 | Address decoding ('HC138) ranges                 | 93  |

| A.2 | MCU board J2 jumper position definitions         | 94  |

| A.3 | MCU board JP1 jumper position definitions        | 94  |

| A.4 | MCU Board bus connector pinouts (J1)             | 96  |

| A.5 | MCU Board power connector pinouts (J3)           | 97  |

| A.6 | MCU Board port connector pinouts (J4)            | 98  |

| A.7 | MCU Board piezo buzzer connector pinouts (J5)    | 99  |

| A.8 | MCU Board serial data connector pinouts (J6)     | 99  |

| A.9 | Microcontroller board parts list (3 constructed) | 100 |

| B.1 | Serial-level Conversion PCB connector J1 pinouts | 112 |

| B.2 | Serial-level Conversion PCB connector J1 pinouts | 112 |

| B.3 | Serial-Level Conversion board parts list         | 113 |

| C.1 | Parallel port address definitions                | 118 |

| C.2 | Parallel port expansion PCB register definitions | 119 |

| C.3 | Parallel port expansion PCB CTRL register (register 4) bit definitions.   | 120 |

|-----|---------------------------------------------------------------------------|-----|

| C.4 | Parallel port expansion PCB UCx register (registers 5-7) bit definitions. | 120 |

| C.5 | Parallel port expansion PCB connector J1 pinouts                          | 122 |

| C.6 | Parallel port expansion PCB connector J2 pinouts                          | 124 |

| C.7 | Parallel port expansion PCB connector J3 pinouts                          | 124 |

| C.8 | Parallel port expansion PCB connector J4 and J5 pinouts                   | 125 |

| C.9 | Parallel port expansion board parts list                                  | 127 |

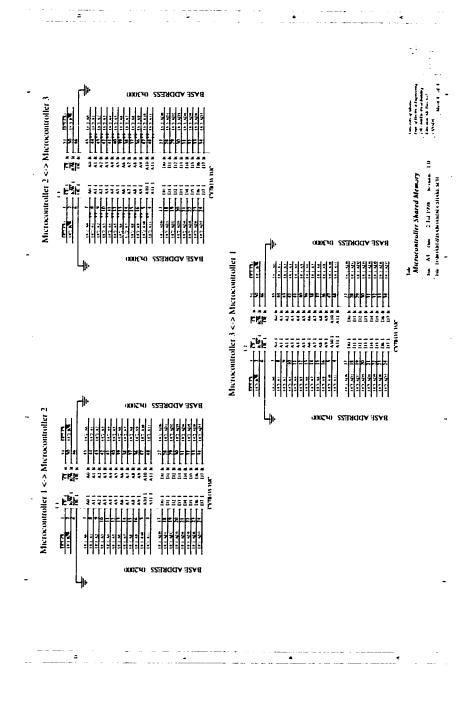

| D.1 | PC-to-MCU Shared Memory PCB MCU memory base locations and                 |     |

|     | PC selection signal mnemonics.                                            | 136 |

| D.2 | PC-to-MCU Shared Memory PCB MCU memory base locations and                 |     |

|     | PC selection signal mnemonics.                                            | 137 |

| D.3 | PC-to-MCU Shared Memory PCB connector J1 pinouts                          | 138 |

| D.4 | PC-to-MCU Shared Memory board parts list                                  | 139 |

| E.1 | MCU-to-MCU Shared Memory PCB Memory address bases                         | 150 |

| E.2 | MCU-to-MCU shared memory board parts list                                 | 151 |

| F.1 | Motor control signals                                                     | 160 |

| F.2 | Navigation Control Hardware PCB connector J1. J2 pinouts                  | 161 |

| F.3 | Navigation Control Hardware PCB connector J3 pinouts                      | 161 |

| F.4 | Navigation Control Hardware PCB connector J4 pinouts                      | 162 |

| F.5 | Navigation Control Hardware board parts list                              | 163 |

| G.1 | IR Pair input connector-to-bit correspondence and analog input            | 173 |

| G.2 | Near-Range Proximity PCB connectors J2-J5: sensor power connections.      | 174 |

| G.3 | Near-Range Proximity PCB connectors J5-J37: sensor signal connec- |     |

|-----|-------------------------------------------------------------------|-----|

|     | tions                                                             | 174 |

| G.4 | Near-range Proximity Detector board parts list                    | 175 |

| H.1 | Digital input connector-to-bit correspondence                     | 186 |

| H.2 | Bump Sensor PCB connectors (J2-J17)                               | 187 |

| H.3 | Bump Sensor board parts list                                      | 188 |

| I.1 | Sonar Module Interface PCB SPI bit definitions                    | 196 |

| I.2 | Sonar Module Interface PCB stepper motor connector J1 pinouts     | 197 |

| I.3 | Sonar Module Interface PCB Polaroid Module 0 connector J2         | 198 |

| I.4 | Sonar Module Interface PCB Polaroid Module 1 connector J3         | 198 |

| I.5 | Sonar Module Interface PCB motor power connector J4 pinouts       | 199 |

| I.6 | Sonar Module Interface PCB Limit-Switch connector J6 pinouts      | 199 |

| I.7 | Sonar Module Interface PCB CdS Cell connector pinouts: J7-J10     | 200 |

| I.8 | Sonar Module Interface board parts list.                          | 201 |

# List of Figures

### Figure

| 2.1 | A top-level block diagram of a typical teleoperation system            | 4  |

|-----|------------------------------------------------------------------------|----|

| 3.1 | A block diagram of a system under the Robotic Internet Platform        |    |

|     | design paradigm                                                        | 16 |

| 4.1 | A block diagram of the test platform with some details filled in under |    |

|     | the guidance of the two design models described in Chapter 3           | 23 |

| 4.2 | The telerobotic system layout                                          | 24 |

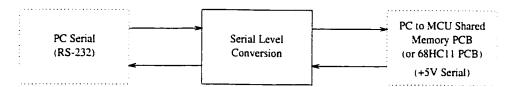

| 5.1 | Location of the Serial Conversion PCB in the test-bed                  | 33 |

| 5.2 | Block diagram of the Serial Conversion board electronics               | 34 |

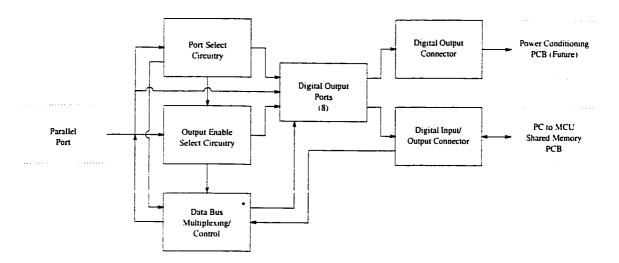

| 5.3 | Block diagram of the Parallel-Port Expansion board electronics         | 35 |

| 5.4 | Block diagram of the PC-to-MCU Shared Memory/Serial Conversion         |    |

|     | board                                                                  | 36 |

| 5.5 | Location of the HC11 microcontroller PCBs in the test-bed              | 37 |

| 5.6 | Block diagram of the MCU board electronics                             | 38 |

| 5.7 | Block diagram of the MCU-to-MCU Shared Memory board electronics.       | 39 |

| 5.8 | Block diagram of the SONAR Module Interface board electronics          | 40 |

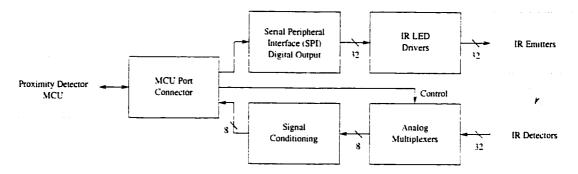

| 5.9              | Block diagram of the Near-Range Proximity Sensor board electronics. | 41  |

|------------------|---------------------------------------------------------------------|-----|

| 5.10             | Block diagram of the Bump Sensor board electronics                  | 42  |

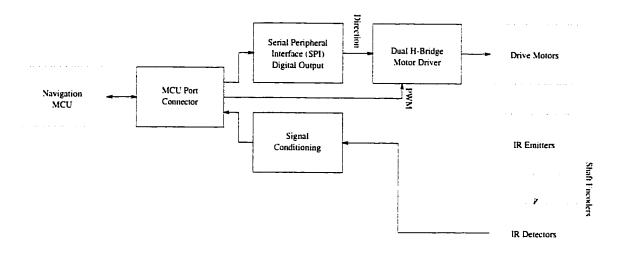

| 5.11             | Block diagram of the Navigation Hardware PCB electronics            | 43  |

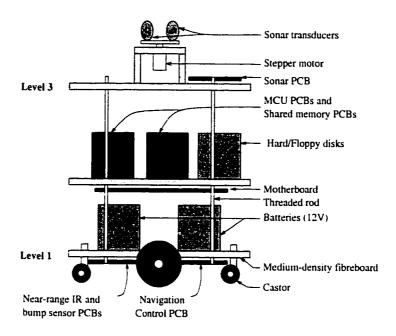

| 5.12             | Side view of the mobile robot workcell                              | 44  |

| 5.13             | Photograph of the mobile robot workcell                             | 45  |

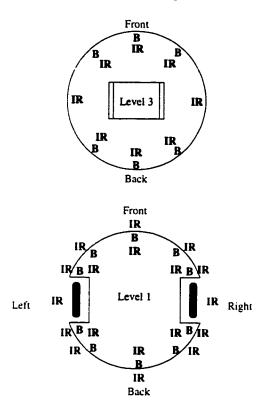

| 5.14             | Positions of the workcell sensors.                                  | 46  |

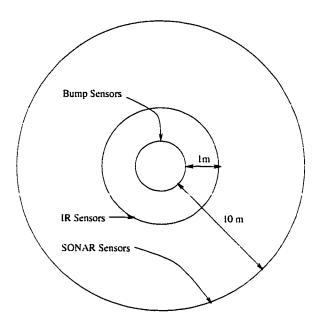

| 5.15             | Graphical depiction of sensing distances                            | 47  |

| 6.1              | Graphical depiction of the test bed development platforms           | 49  |

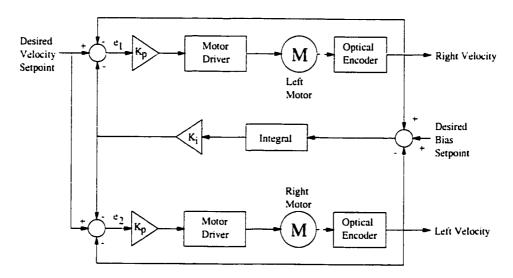

| 6.2              | The slaved-PI velocity control loop for the drive motors            | 55  |

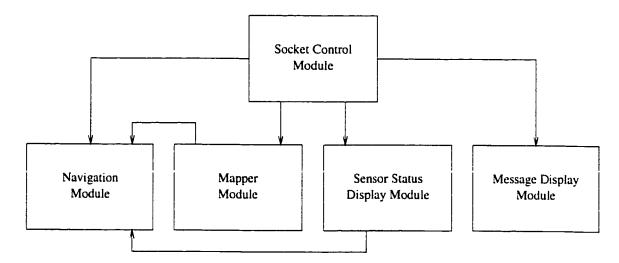

| 6.3              | Graphical depiction of the five user interface modules              | 66  |

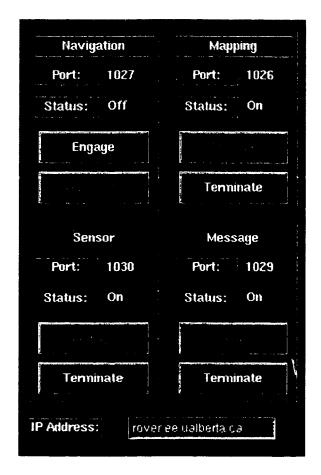

| 6.4              | Screenshot of the Socket Control module UI                          | 67  |

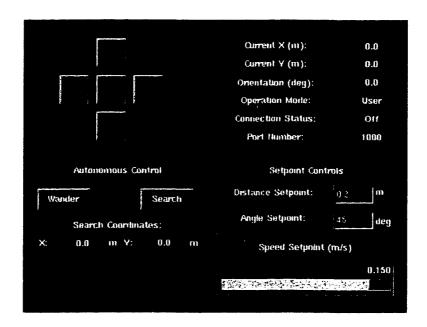

| $6.\overline{5}$ | Screenshot of the Navigation Console module UI                      | 68  |

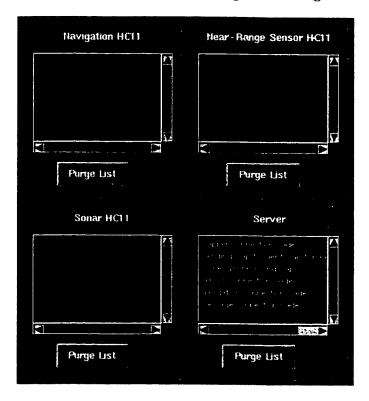

| 6.6              | Screenshot of the Message module UI                                 | 69  |

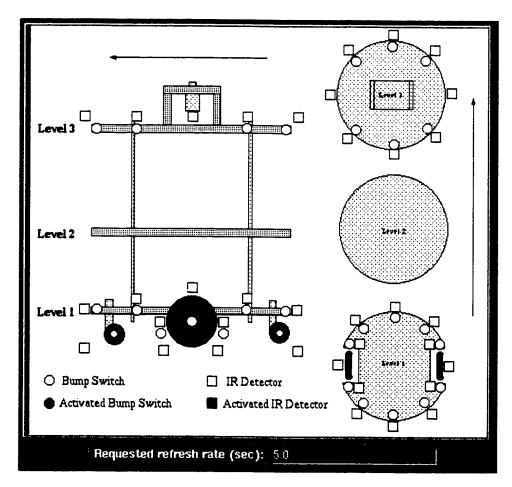

| 6.7              | Screenshot of the Sensor Status Display module UI                   | 70  |

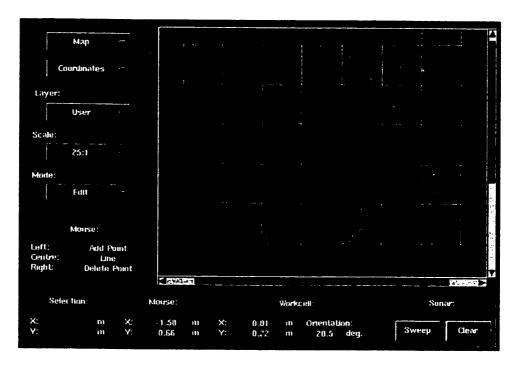

| 6.8              | Screenshot of the Mapper module UI                                  | 73  |

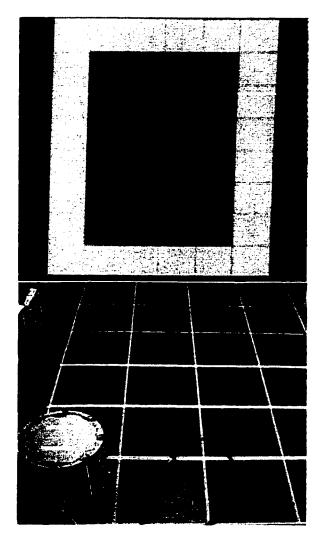

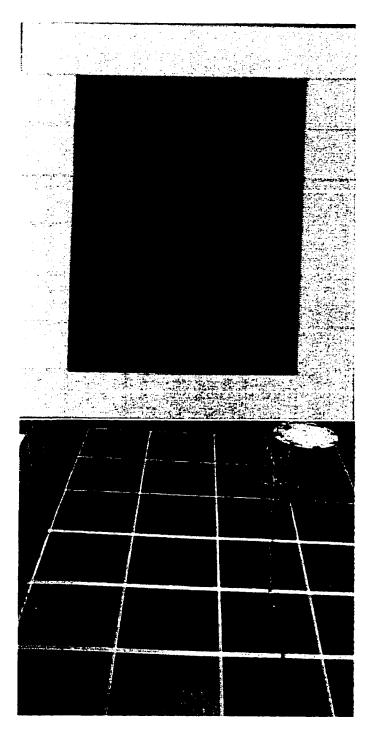

| 7.1              | The setpoint search algorithm in action (1 of 2)                    | 76  |

| 7.2              | The setpoint search algorithm in action (1 of 2)                    | 77  |

| 7.3              | Bump sensor test actual and mapped environments                     | 79  |

| 7.4              | IR sensor test actual and mapped environments                       | 80  |

| 7.5              | SONAR sensor test actual and mapped environments                    | 81  |

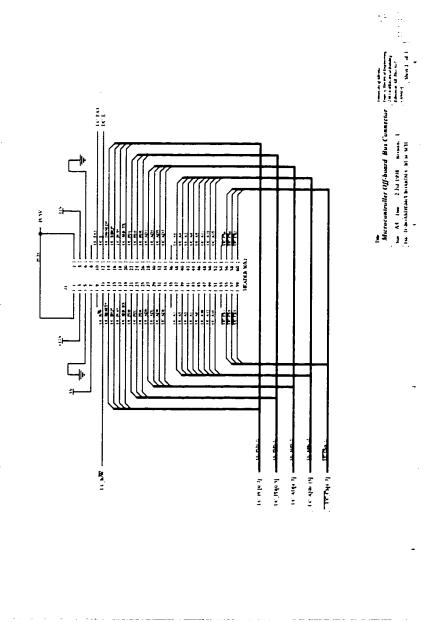

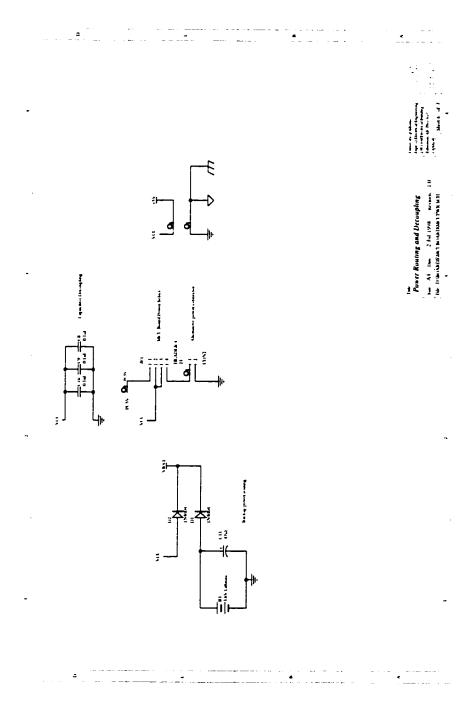

| A.1              | Microcontroller board schematic (1 of 7)                            | 101 |

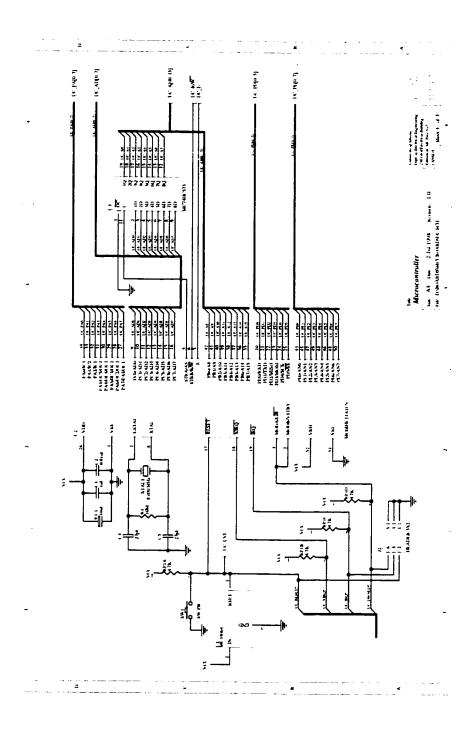

| A.2              | Microcontroller board schematic (2 of 7)                            | 102 |

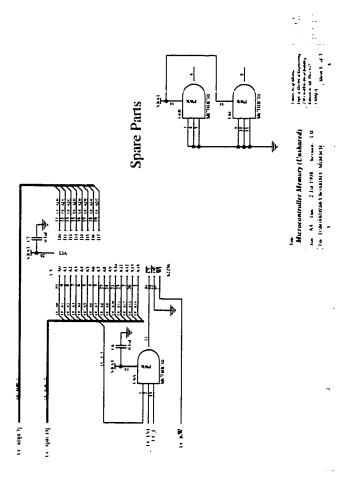

| A.3              | Microcontroller board schematic (3 of 7)                            | 103 |

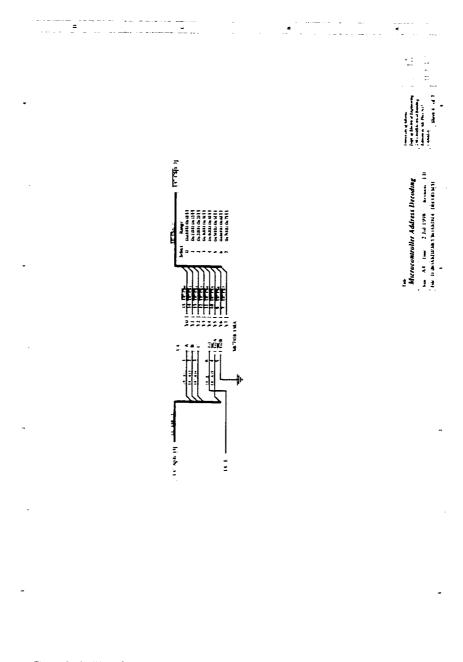

| A.4              | Microcontroller board schematic (4 of 7)                            | 104 |

| A.5  | Microcontroller board schematic (5 of 7)                                  | 105 |

|------|---------------------------------------------------------------------------|-----|

| A.6  | Microcontroller board schematic (6 of 7)                                  | 106 |

| A.7  | Microcontroller board schematic (7 of 7)                                  | 107 |

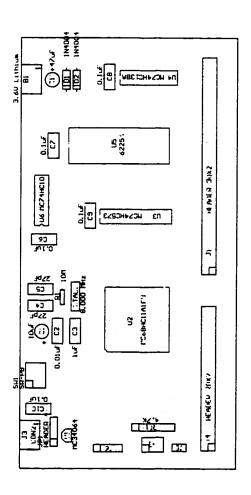

| A.8  | Microcontroller board part placement diagram                              | 108 |

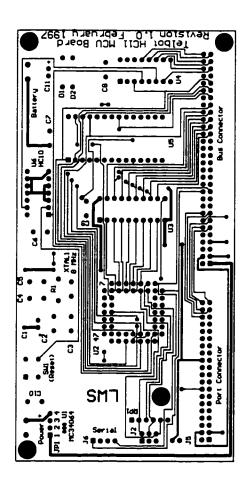

| A.9  | Microcontroller board top-layer copper foil pattern. Not to scale         | 109 |

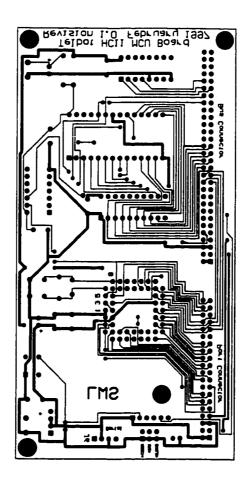

| A.10 | Microcontroller bottom-layer copper foil pattern (through-board view).    |     |

|      | Not to scale                                                              | 110 |

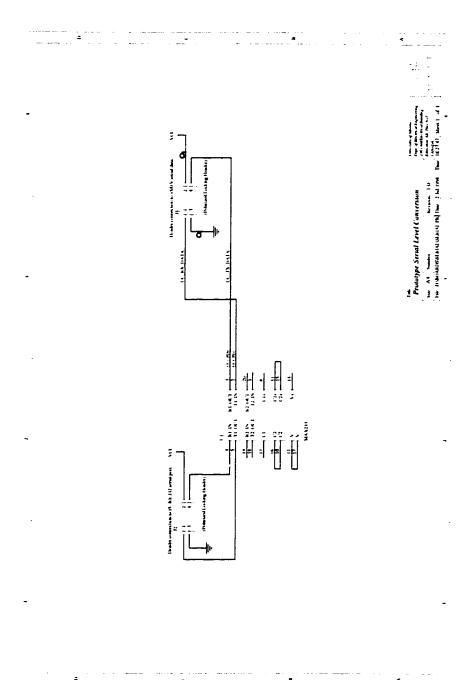

| B.1  | Serial-Level Conversion schematic (1 of 1)                                | 114 |

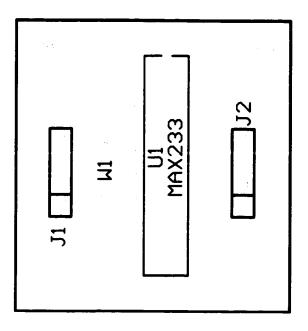

| B.2  | Serial-Level Conversion part placement diagram                            | 115 |

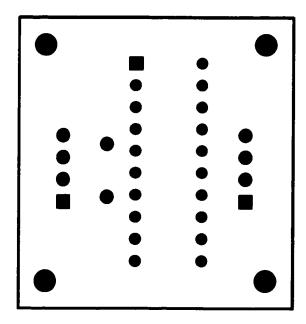

| B.3  | Serial-Level Conversion top-layer copper foil pattern. Not to scale       | 115 |

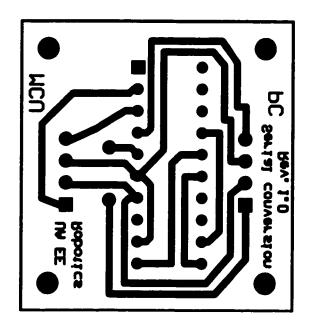

| B.4  | Serial-Level Conversion bottom-layer copper foil pattern (through-board   |     |

|      | view). Not to scale                                                       | 116 |

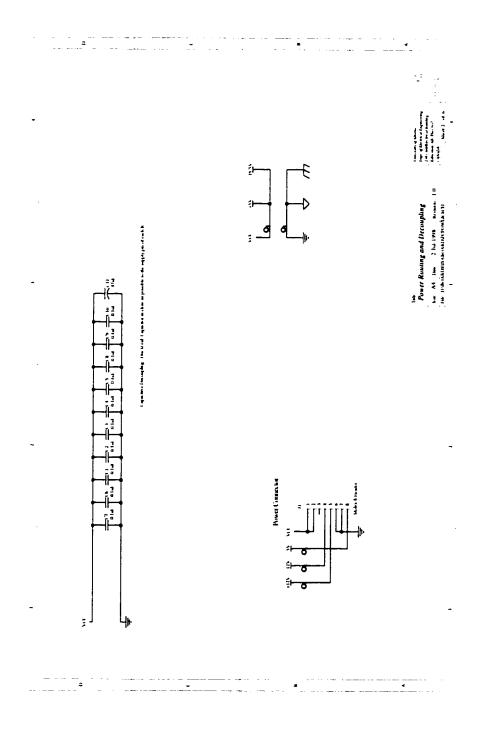

| C.1  | Parallel port interface card schematic (1 of 4)                           | 128 |

| C.2  | Parallel port interface card schematic (2 of 4)                           | 129 |

| C.3  | Parallel port interface card schematic (3 of 4)                           | 130 |

| C.4  | Parallel port interface card schematic (4 of 4)                           | 131 |

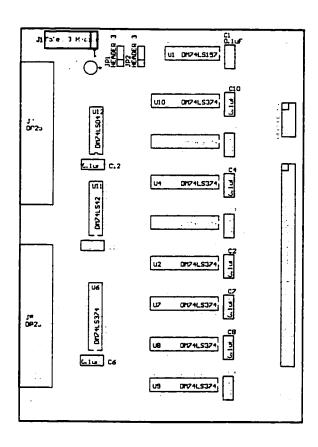

| C.5  | Parallel port interface card part placement diagram                       | 132 |

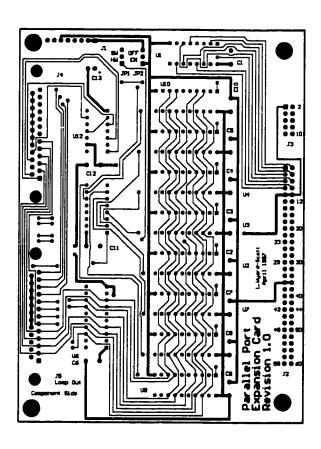

| C.6  | Parallel port interface card top-layer copper foil pattern. Not to scale. | 133 |

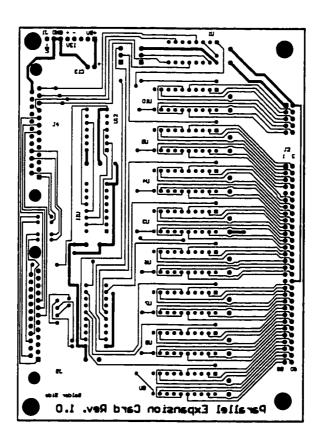

| C.7  | Parallel port interface card bottom-layer copper foil pattern (through-   |     |

|      | board view). Not to scale                                                 | 134 |

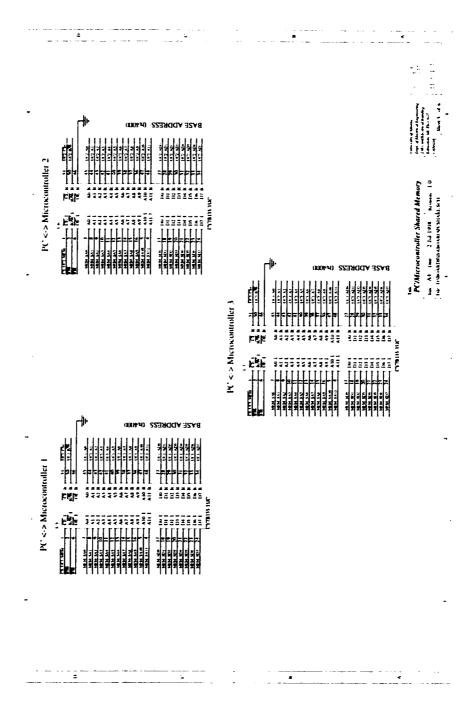

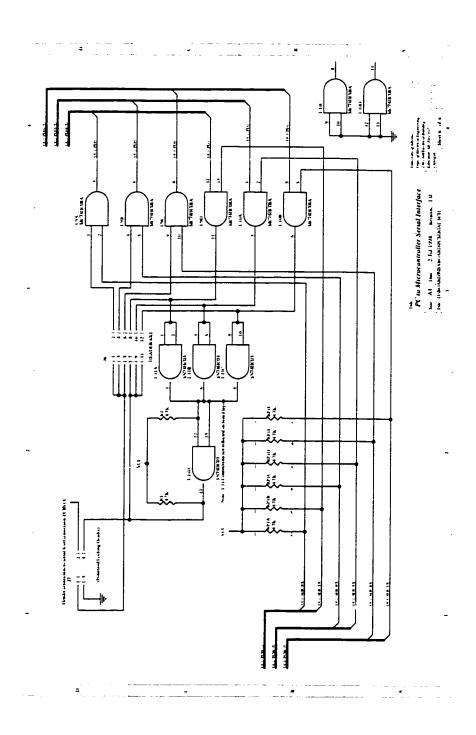

| D.1  | PC-to-MCU Shared Memory PCB schematic (1 of 6)                            | 140 |

| D.2  | PC-to-MCU Shared Memory PCB schematic (2 of 6)                            | 141 |

| D.3  | PC-to-MCU Shared Memory PCB schematic (3 of 6)                            | 142 |

| D.4  | PC-to-MCU Shared Memory PCB schematic (4 of 6)                            | 143 |

|      |                                                                           |     |

| D.5 | PC-to-MCU Shared Memory PCB schematic (5 of 6)                          | 144  |

|-----|-------------------------------------------------------------------------|------|

| D.6 | PC-to-MCU Shared Memory PCB schematic (6 of 6)                          | 145  |

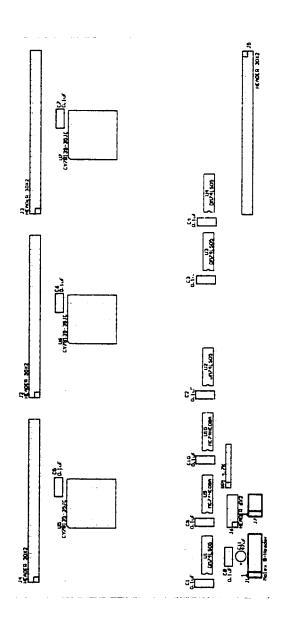

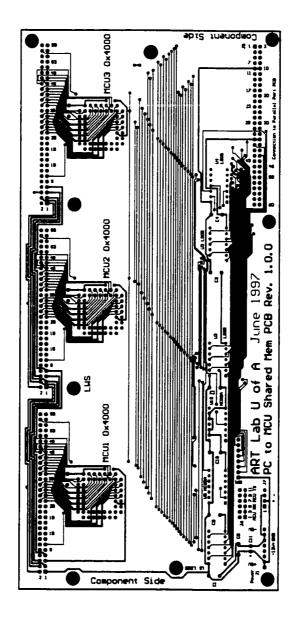

| D.7 | PC-to-MCU Shared Memory PCB part placement diagram                      | 146  |

| D.8 | PC-to-MCU Shared Memory PCB top-layer copper foil pattern. Not          |      |

|     | to scale.                                                               | 147  |

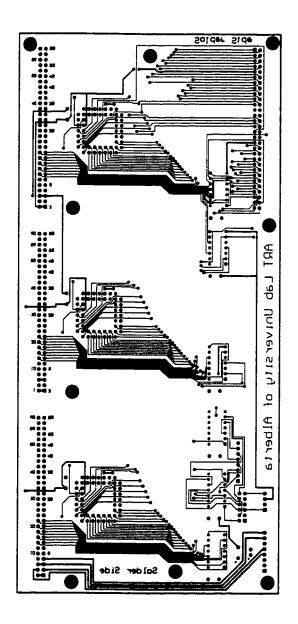

| D.9 | PC-to-MCU Shared Memory PCB bottom-layer copper foil pattern            |      |

|     | (through-board view). Not to scale                                      | 148  |

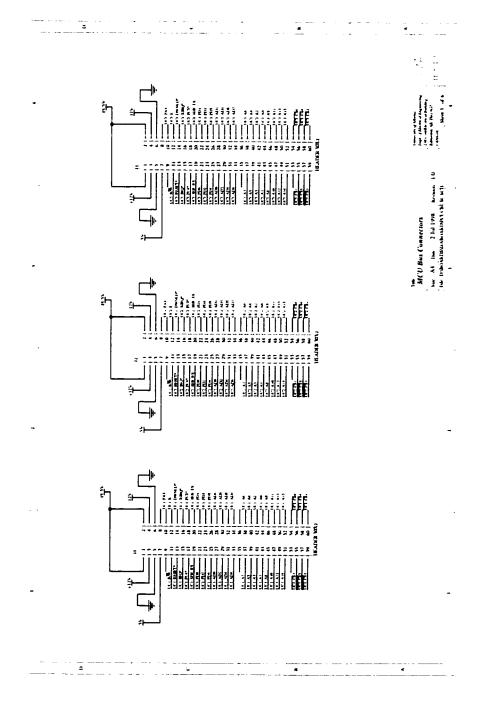

| E.1 | MCU-to-MCU Shared Memory PCB schematic (1 of 4)                         | 152  |

| E.2 | MCU-to-MCU Shared Memory PCB schematic (2 of 4)                         | 153  |

| E.3 | MCU-to-MCU Shared Memory PCB schematic (3 of 4)                         | 154  |

| E.4 | MCU-to-MCU Shared Memory PCB schematic (4 of 4)                         | 155  |

| E.5 | MCU-to-MCU Shared Memory PCB part placement diagram                     | 156  |

| E.6 | MCU-to-MCU Shared Memory PCB top-layer copper foil pattern. Not         |      |

|     | to scale                                                                | 157  |

| E.7 | MCU-to-MCU Shared Memory PCB bottom-layer copper foil pattern           |      |

|     | (through-board view). Not to scale                                      | 158  |

| F.1 | Navigation Control Hardware schematic (1 of 4)                          | 164  |

| F.2 | Navigation Control Hardware schematic (2 of 4)                          | 165  |

| F.3 | Navigation Control Hardware schematic (3 of 4)                          | 166  |

| F.4 | Navigation Control Hardware schematic (4 of 4)                          | 167  |

| F.5 | Navigation Control Hardware part placement diagram                      | 168  |

| F.6 | Navigation Control Hardware top-layer copper foil pattern. Not to scale | .169 |

| F.7 | Navigation Control Hardware bottom-layer copper foil pattern (through-  |      |

|     | board view). Not to scale                                               | 170  |

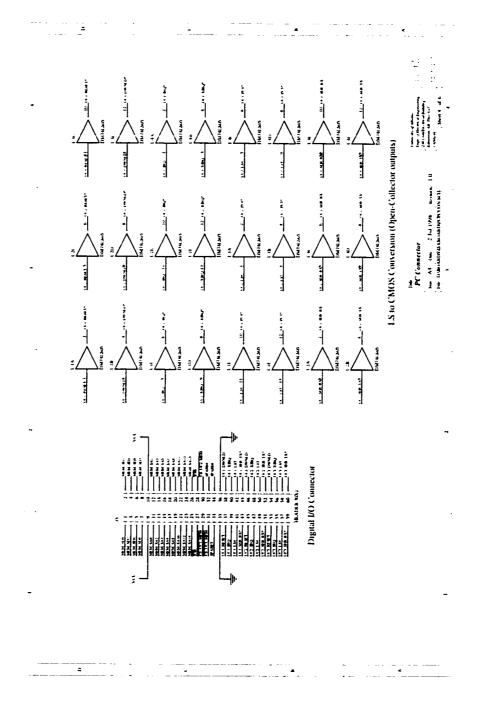

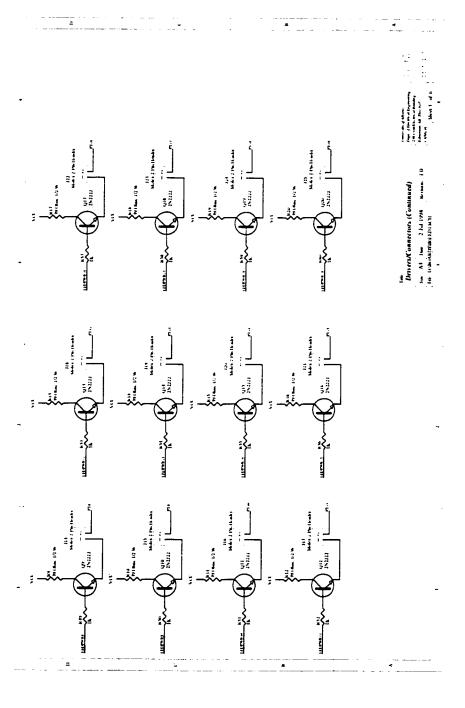

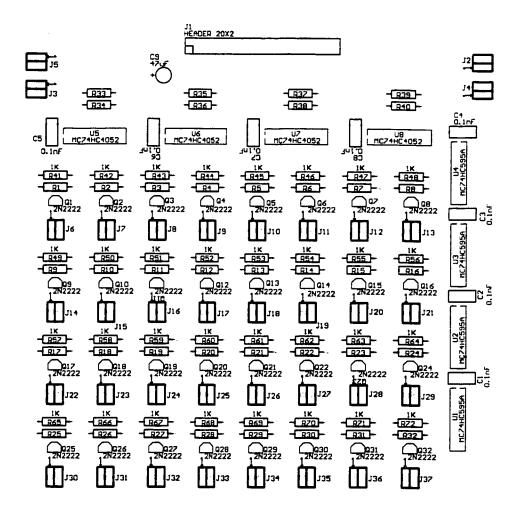

| G.1 | Near-Range Proximity PCB schematic (1 of 6)                              | 176 |

|-----|--------------------------------------------------------------------------|-----|

| G.2 | Near-Range Proximity PCB schematic (2 of 6)                              | 177 |

| G.3 | Near-Range Proximity PCB schematic (3 of 6)                              | 178 |

| G.4 | Near-Range Proximity PCB schematic (4 of 6)                              | 179 |

| G.5 | Near-Range Proximity PCB schematic (5 of 6)                              | 180 |

| G.6 | Near-Range Proximity PCB schematic (6 of 6)                              | 181 |

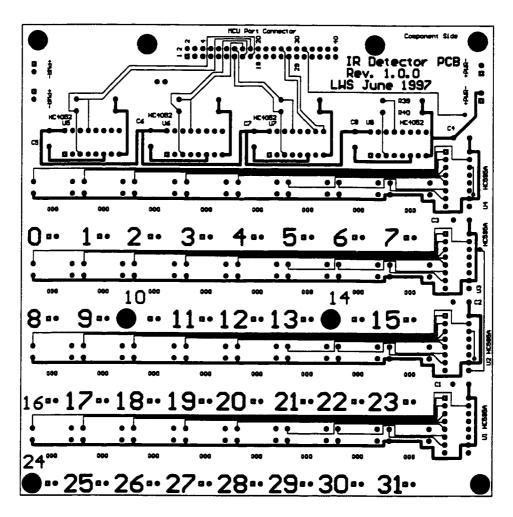

| G.7 | Near-Range Proximity PCB part placement diagram                          | 182 |

| G.8 | Near-Range Proximity PCB top-layer copper foil pattern. Not to scale.    | 183 |

| G.9 | Near-Range Proximity PCB bottom-layer copper foil pattern (through-      |     |

|     | board view). Not to scale.                                               | 184 |

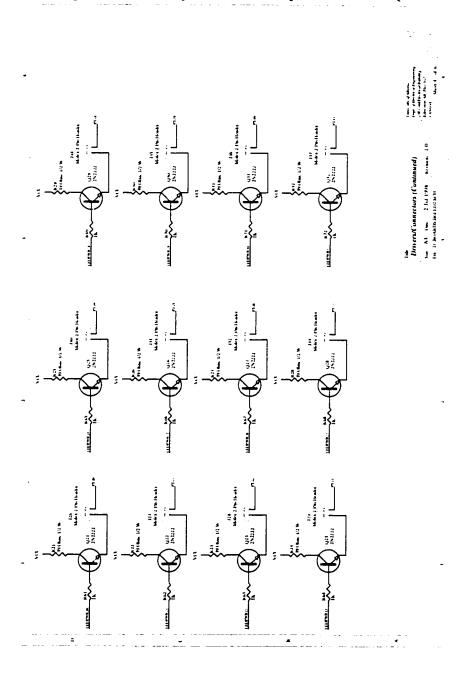

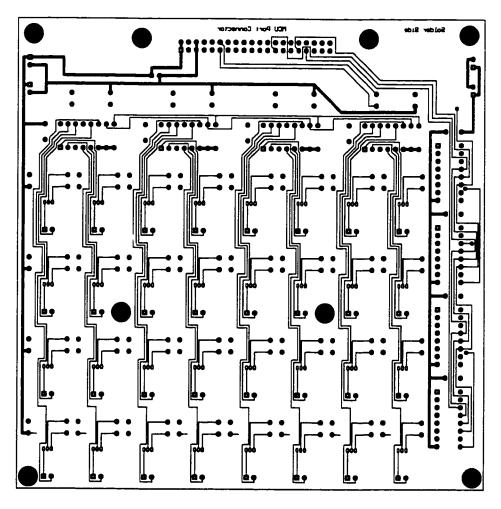

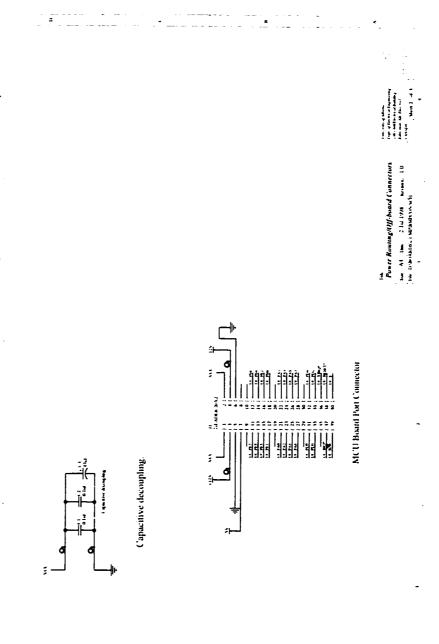

| H.1 | Bump Sensor PCB schematic (1 of 3)                                       | 189 |

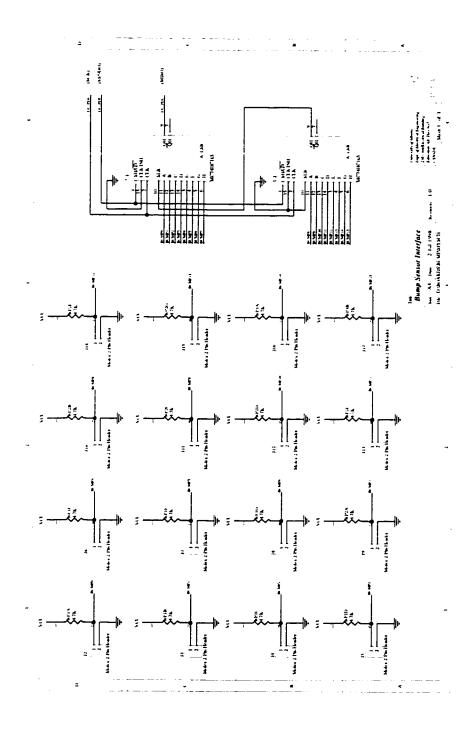

| H.2 | Bump Sensor PCB schematic (2 of 3)                                       | 190 |

| H.3 | Bump Sensor PCB schematic (3 of 3)                                       | 191 |

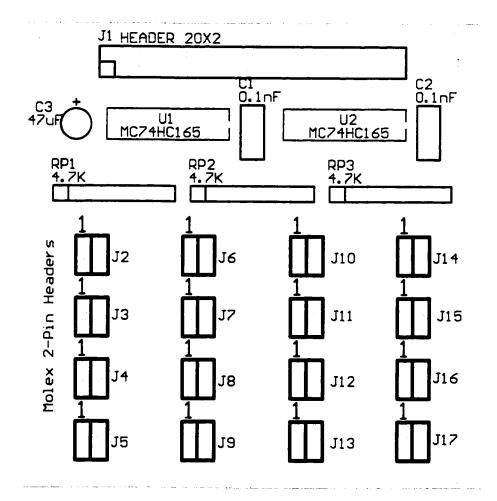

| H.4 | Bump Sensor PCB part placement diagram                                   | 192 |

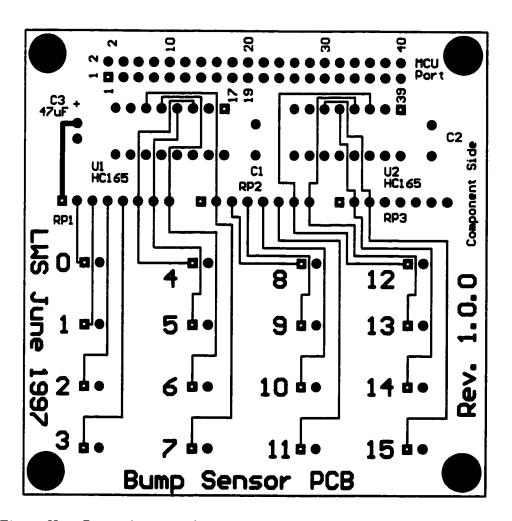

| H.5 | Bump Sensor PCB top-layer copper foil pattern. Not to scale              | 193 |

| H.6 | Bump Sensor PCB bottom-layer copper foil pattern (through-board          |     |

|     | view). Not to scale                                                      | 194 |

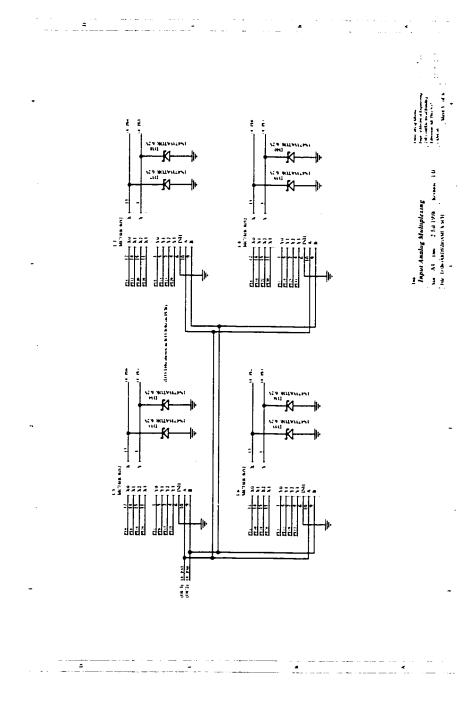

| I.1 | Sonar Module Interface board schematic (1 of 3)                          | 202 |

| I.2 | Sonar Module Interface board schematic (2 of 3)                          | 203 |

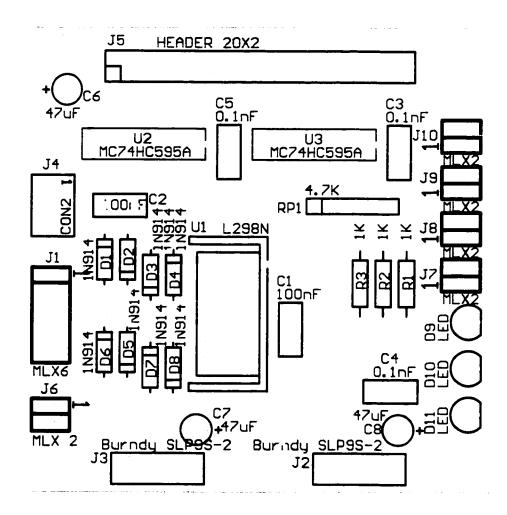

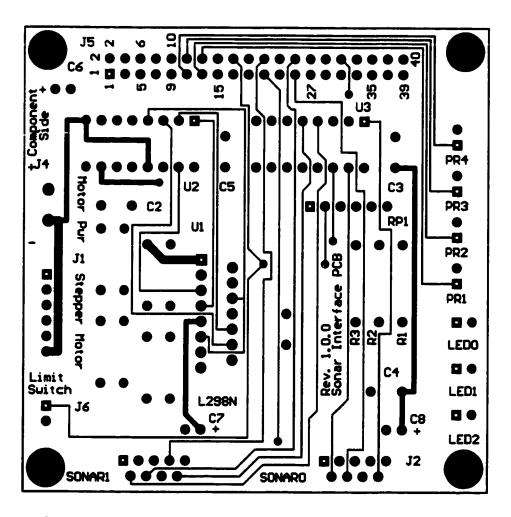

| I.3 | Sonar Module Interface board schematic (3 of 3)                          | 204 |

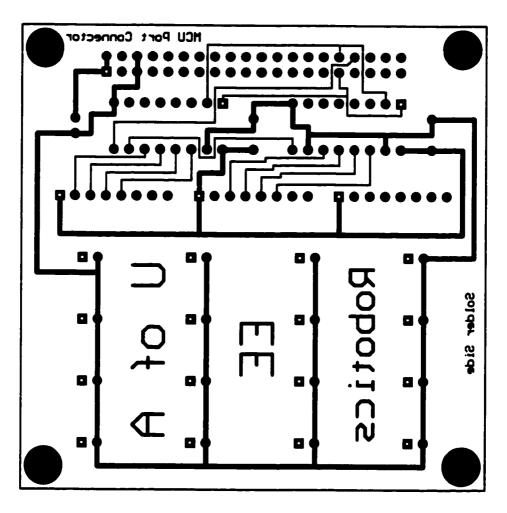

| I.4 | Sonar Module Interface board part placement diagram                      | 205 |

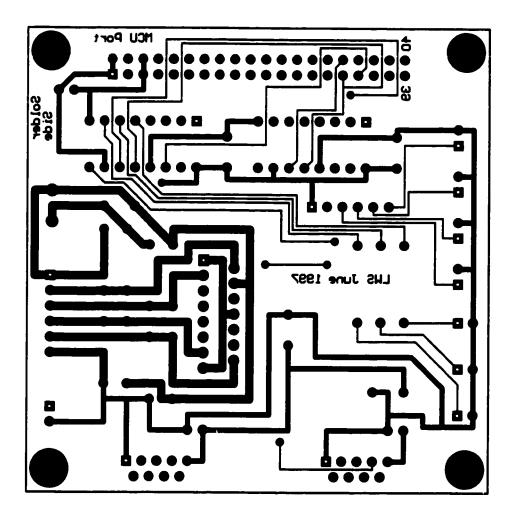

| I.5 | Sonar Module Interface board top-layer copper foil pattern. Not to scale | 206 |

| I.6 | Sonar Module Interface board bottom-layer copper foil pattern (through-  |     |

|     | board view). Not to scale.                                               | 207 |

# Chapter 1

### Introduction

The objective of the research presented here is to develop a complete, modifiable teleoperated mobile robot platform for the purpose of control algorithm and interface testing.

The design is carried out under the guidelines of two models: one which outlines necessities for a test-bed, and another (the Robotic Internet Platform (RIP) design paradigm) which dictates the form of software interfaces between the layers of the system.

A comprehensive library of software routines are developed to minimize system development time for future researchers. This software implements the robust, extensible interfaces between the abstract layers of the system in accordance to the second of the two design models.

As a test of the resulting systems capabilities, a complete, functional system is developed: from user-interface to remote workcell actuators. The reader is led through the development of the design models and application of them.

### 1.1 Organization

The organization of this thesis is as follows. Chapter 2. Teleoperation Systems. is an overview of existing teleoperation platforms and active research areas in teleoperation. This chapter is used to derive the design objectives and system design models of Chapter 3. The next three chapters contain the design of the teleoperation system resulting from the design models: Chapter 4. System Overview, is a top-level description of the system. Chapter 5. Modular Workcell Hardware Design, describes the workcell hardware and the motivation used to achieve it, and Chapter 6. Modular Software Design, is an overview of the system software and the workcell software interface. Upon completion of the system design, Chapter 7. Results and Demonstrations, the test-bed's functionality is demonstrated. Lastly, Chapter 8 evaluates the success of the design models and the system yielded from them.

A set of appendices describe the modular workcell hardware in detail. These are presented to aid future researchers in reconfiguration of the platform. An appendix with software documentation is also presented to aid the discussion in Chapter 6. These appendices, though verbose, are a necessity for an effective test bed platform.

# Chapter 2

# **Teleoperation Systems**

### 2.1 Introduction

In this chapter, the structure of a typical teleoperated system is presented along with the definitions of several terms that are encountered in this very active area of research. There are several specific facets of teleoperation systems that are of paramount interest. These are discussed using a survey of several existing teleoperation systems. There are also many active areas of research in **mobile** robotics. These include Artificial Intelligence (AI) topics, such as subsumption architecture and neural networks, and topics to do with navigation, such as path-planning and localization techniques. Although it is desirable to create a test-bed that will be able to research these topics, they are not covered here.

The next chapter utilizes the information derived here to develop two design models and design objectives for a test-bed system used for research.

### 2.2 A Typical Teleoperation Platform

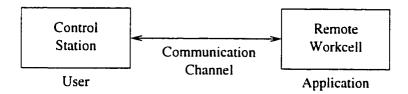

Fig. 2.1 shows typical division of a teleoperation system into Control Station and Remote Workcell blocks. The Control Station is where the user interacts through a User Interface (UI) to take control over the Remote Workcell. Communication between the control station and the workcell occurs through a bidirectional channel. Directives are issued from the control station to the workcell (left-to-right data flow), and feedback about the state of the workcell and information about its surrounding environment is related from the workcell back to the control station (right-to-left data flow).

Figure 2.1: A top-level block diagram of a typical teleoperation system. The system is physically divided into a Control Station and a Workcell, operating remotely. Communication between the two occurs through some sort of channel.

The following definitions are commonly encountered in this field of study. The definitions are expressed in terms of a top-level view of the system, shown in Fig. 2.1.

Teleoperation is the process by which control station initiated directives are executed on a remote workcell. The amount of feedback that is returned to the control station from the can vary from nothing (open-loop) to comprehensive (detailed). This definition is apparently context-sensitive. If used when referring to a telepresence system, teleoperation may mean that the user actually performs the task that the workcell is to execute.

**Telepresence** is the discipline where feedback from the workcell to the control station is comprehensive. The feedback is so thorough that the user "feels" that they are physically located at the remote workcell's location. The actions that the user takes at the control station are somehow mimicked by the workcell.

Telerobotics has varying definitions. For instance, [PPA94] states that a telerobotics system is one wherein the user at the control station actually performs the action taken by the workcell. Other literature, such as [JP94] or [LMR94] assume that telerobotics is the field of study which is a superset of teleoperation, telepresence, and teleprogramming; any system which has a control station, communication link, and a remote workcell. This second definition is the one used throughout this document.

**Teleprogramming** is the act of changing the operation of a workcell from the control station through transmission of a program. Programming may occur at runtime, or when the workcell is in an idle mode. However the programming is performed, the syntax that the program is defined with is referred to as the teleprogramming language.

Distinction between the terms is difficult and depends upon the specific research area or system being addressed.

### 2.3 Telerobotics Research Areas

This section is an overview of telerobotic research areas. The goal is to be able to design a test-bed that can be used for research in any of these areas. This analysis of existing work will be used to develop the system design models and functional objectives presented in the next chapter.

Dividing the research into these areas is synthetic since they are all intertwined. For instance, the form of a user interface could be classified as control research.

#### 2.3.1 Control

A workcell is often given reflexive behaviours to preserve itself. For instance, a mobile workcell is typically not given the option to drive over a cliff, even if the user (via the control station) tells it to do so. This area addresses the topic of where control-loops are closed: within the workcell itself (local control), or through the control-station (remote control).

Certain applications may require that control be transferred from the controlstation (remote) to the workcell (local), or vice versa. This type of transfer is not necessarily trivial. Often, cases will arise where the workcell may behave unpredictably when control is transferred.

If a workcell is performing an application-critical task under control from the control station and the communication link is lost, some technique needs to be in place to rationalize the workcell's actions. Since the control-loop incorporating the control station is effectively broken, the workcell could become unstable.

Teleautonomous guidance [BK90] is a scheme in which the workcell has collision-avoidance (or similar) control loops closed on the workcell and an external loop closed by the user's perception and action at the control station. When activated, the collision-avoidance loop is closed, otherwise remaining open. This approach can also be seen in [TBGX94], [HM94a] (approached through a teleprogramming paradigm), and [BAXTJ96]. "Shared autonomy" [MA94] is a similar method, but assumes that both control loops are closed simultaneously. The sharing of autonomy with the

workcell makes the system safer, dependable, and reduces interaction required of the user at the control station [SJ94].

#### 2.3.2 Communication

Research focusing on communication examines the operation of a system when there is transmission delay between the control station and the workcell.

Communication between the control station and the workcell can be achieved in several different ways: umbilical, wireless modem, wireless Ethernet, infrared, microwave, and satellite, among others. Establishing such a link may be simple, or involve multiple "hops" as in [Leo95] or [BFKS94].

Control-loops behave poorly under delay. The more accurate the control needs to be, the higher the required bandwidth. If a control-loop is closed via the control station, the bandwidth and transmission delay of the communication channel are of interest.

To compensate for a communication delay, predictive models can be used as in [HM94b], [Say96], [HLF94] and [BBZ98].

#### 2.3.3 Telerobotic System Software

Communication between control station and workcell must follow a protocol. The structure of the "language" that is used to communicate between the two components of the system is referred to as a **teleoperation language**. This language can be embedded into an operating system, such as CHIMERA, developed at Carnegie-Mellon and utilized by [NX94] to control a manipulator used in Space Station Freedom. The syntax of the communication may also be implemented in another language. See, for instance, Steele and Backes [SB94].

It can be argued that a teleoperation language is simply a teleprogramming language in its most basic form. Teleprogramming typically involves specifying a task or a mission that the workcell is to complete.

In task-level teleprogramming [PPA94], in addition to a description of the task that the workcell is to perform, a program can be written to include information that the workcell is unable to obtain itself (perhaps a-priori knowledge of the workcell's environment).

Programming and Interpreted Languages Of actions for Telerobotics (PILOT) [LMR94], is a high-level interpreted visual language which is able to accommodate event-driven actions. Its object-oriented design links three software layers (mission, control-task, and servo-control) using standard language primitives (sequential, iterative, conditional, and parallel). PILOT is not intended to process data from sensors: operations (other than comparisons) are not supported. This would be a disadvantage for a test bed application since research into areas such as sensor fusion would not be supported.

#### 2.3.4 System Architecture

Telerobotic system architecture refers to how the software is written, or how the hardware is designed. Since hardware and software are co-dependent, descriptions typically address both.

Typically, there is a physical distinction between a telerobotic system's control station and workcell. However, from a software perspective a division between the two is not so obvious. For instance, all of the system software could be implemented on the workcell; only the UI is displayed on the "empty" control station, perhaps using a web-browser or X-window display commands. Where the software division is

made depends not only upon the application, but also upon the other technologies (such as the communication medium) that the system employs.

The NASA/NIST Standard Reference Model (NASREM) [Lum94] suggests that a telerobot system should have a parallel-processing structure to meet real-time performance requirements. The software architecture consists of six levels which range from a synchronous servo level to an asynchronous mission-defining level. NASREM does not provide a methodology for designing the system hardware.

Another architecture project in [JP94] outlines the need for a standard for industrial remanufacturing telerobotic systems. Backes et al. [BBL+94] implement a work-cell controller system entitled Modular Telerobot Task Execution System (MOTES). It is an interpreted language which offers concurrent control over control modules. A three-layer structure is used in [Cro89]: the top layer is an interpreter which handles asynchronous commands, the middle layer is a "virtual" workcell, and the bottom layer is the interface to the actual vehicle. The European Space Agency follows the guidelines of a unified control architecture for planetary rovers. Two projects which make use of this system are [RVR98] and [SLMV98].

Regardless of the architectures, there is one undeniable fact: there is movement towards decoupling and modularizing of telerobotic system hardware and software to increase flexibility and promote re-use of code and hardware.

### 2.3.5 User-Interface Functionality and Human Factors

For effective control over the remote workcell, the interface to the user at the control station will need to be effective. Poor interfaces will lead to poor control. This research explores the design of effective UIs and the methods used to evaluate them.

UIs are not only used to provide a means for the user to control the workcell. but also to provide a medium for the feedback from the workcell to be delivered to the user. Effectiveness of the UI can be evaluated by the number of successful task completions [CRKW96] or even through the EMG signals of the system user [RCMT94].

To help a user maintain control of the workcell, the UI can present the feedback in varying manners. Lloyd et al. [LBPL97] and McMaster et al. [MNBF94] present the workcell and its environment as a computer-generated graphical image. This approach is useful in situations where the communication bandwidth is insufficient to transmit, or the environmental conditions are too poor to capture, quality video signals. Another approach is to super-impose computer-generated graphics over a potentially low-quality video stream as in [BFKS94] or [MCC92].

Another possibility is to have the feedback to the UI completely simulated. Although this is no longer a telerobotic system, it may be useful for operator training [MS94]. To this end, unrealistic worlds could be shown to research perception and how it applies to teleoperation systems [RKSG94].

UIs can be delivered on different platforms: through a WWW browser, applicationlevel programs in a Windowing environment, or perhaps even a text-only shell environment.

#### 2.3.6 Sensing Techniques

How a workcell senses the environment around it is important for effective control. In telepresence applications, sensing is important as it is through it that the remote world is represented to the user at the control station.

Even to implement autonomous behaviours (to close the workcell control loop on the workcell itself), there is need for sensors to relay information about the environment back to the control architecture. This sensing can be as simple as a bump switch or as complex as a multi-camera video system.

One may be inclined to think that more sensor information is better. However, the limitations of the CPU's speed or the communication channel's bandwidth will quickly become apparent. The process of sensor fusion [LK89] [DW87] can help the system reduce the amount of data to process by by algorithmically isolating the relevant portions of sensor data by linking together data from more than one (or more than one type) of sensor. The algorithms may involve simple modeling of sensor response [WSM96] or involve the operator in the process [YMP+94].

## 2.4 Summary

There is a lot of activity in the field of telerobotics research. This chapter has outlined basic terms found in, and examined research directions in the field of telerobotics. Control techniques, communication, system software (teleprogramming and teleoperation languages), system (software) architecture, user interfaces, and sensing techniques are all areas that a test bed should be able to research. The next chapter presents design models which emphasize the flexibility and modularity that are required of a system in order to achieve this goal.

# Chapter 3

# Objectives and System Design Models

### 3.1 Introduction

This chapter provides a "specification" for the desired operation of the test-bed. In order to meet these specifications and to obtain a system that can successfully be used to research the areas outlined in the last chapter, it is necessary to concentrate on the fact that the system is a test-bed. Since it is impossible to predict with certainty the areas in which a test-bed will be applied, flexibility becomes the key issue.

Flexibility is required not only in the hardware design but also in the software. The model used for this design has been coined the Robotic Internet Platform (RIP) design paradigm and is presented in Section 3.4.

# 3.2 Functional Specifications

The teleoperated mobile-robot test-bed is to have the ability to research the areas outlined in Chapter 2. These areas are restated here in terms of high-level specifications. The resulting system is to have the following features:

- (1) Ability to implement autonomous or reflexive behaviours on the workcell (control level research):

- (2) Ability to transfer control between the workcell (autonomous control) and the control station (user-initiated control) (control transfer research):

- (3) Interruptable communication channel (communication research):

- (4) Delayable communication channel (communication research):

- (5) Changeable communication medium (communication research):

- (6) Flexible languages for UI implementation (UI functionality and human factors research):

- (7) Multiple UI delivery mechanisms (web- or application-based UI implementation) (UI interface research):

- (8) Support for teleoperation languages of different structures and syntax (teleoperation language research);

- (9) Flexible teleprogramming interface (teleprogramming research):

- (10) Ability to move the workcell/control station division easily (system software research): and

(11) Workcell sensors (sensor fusion and sensing technique research).

Two design models, loosely categorized by hardware and software, are used to achieve these design goals. The remainder of this chapter outlines these models.

# 3.3 Electronic Hardware Design: The Test-Bed

# Model

Telerobotic systems have been developed for use in submarine [LB94a] [LMR94]. outer space [WL94] [BBL+94], and hazardous environments [BHW+94]. This thesis documents the design of a teleoperated mobile robot system intended for **research** in the areas outlined in the last section and Chapter 2. Unlike the projects mentioned above, the development of a test bed requires a great deal of flexibility to accommodate future research directions.

In typical modern systems, some flexibility is offered through software modifications. This concept is pursued in this project. In addition, flexibility with regard to electronic hardware structure is required. This requirement is approached by designing the electronic systems with a high degree of **modularity** to accommodate future changes. Fortunately, modularity also accommodates the most restrictive design constraint: financial limitations. Without a modular approach, cost would increase with the effort to accommodate new research areas.

Therefore, in addition to the features outlined in the last section, the following test bed features are required: design:

- modularity;

- flexibility; and

• safety of operation.

Modularity promotes the reuse of individual software and hardware blocks, and reduces system set-up time. Wherever possible, each module should be made as a stand-alone device, which aids in debugging and expands its usefulness. When designing hardware modules, the technology used should be consistent. For instance, a single type of microcontroller should be used throughout the system, or connector types should be standardized. Again, this promotes recycling, not only of code, but also of schematic libraries. Additionally, when researchers use the test-bed, the amount of information they need to know to reconfigure the setup is minimized.

The design is to be **flexible** so that both hardware and software can be reconfigured to suit an area of research. Reconfiguration may involve leaving a specific module entirely out of the system.

Safe operation requires the system to be reliable. If a CPU crashes the workcell should not behave unpredictably. In order to achieve this, it is suggested that a distributed-processor model be used to give the system some redundancy.

Start-up of systems typically present transient operation which needs to be accounted for. Bus contention needs to be avoided by ensuring that devices are disabled on power-up.

Since the test-bed is intended for use in a wide range of research applications, several requirements need to be accommodated:

- Multiple users will need access to the system, perhaps simultaneously:

- Development time of software needs to be minimized:

- Operation needs to be straightforward, as the researchers may receive minimal training on the test-bed; and

• Documentation needs to be concise and comprehensive.

In short, the more familiar the technology used in the system, the more effective the system will be from the researchers' perspective.

# 3.4 Software Interface Design Model: The RIP Paradigm

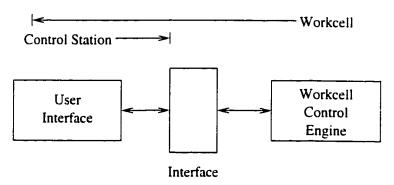

Design of telerobotic system software can be a daunting task. Design approaches can quickly become cluttered as more detail is established. To make the system software design process achievable, an alternate view of the system is required. This view is represented in Fig. 3.1, differing slightly from Fig. 2.1.

Figure 3.1: A top-level block diagram of a telerobotic application under the Robotic Internet Platform design paradigm. The User Interface is the component that the operator interacts with. The Workcell Control Engine, typically running on the workcell itself, is software responsible for control of the workcell movement. The software interface between the two needs to be well documented, flexible, and based upon the string data type.

This view is referred to as the "Robotic Internet Platform" (RIP) paradigm. Under the RIP paradigm, it is assumed that the communication channel (referring to Fig. 2.1) consists of an Internet connection and both the control station and the

workcell are Internet machines capable of utilizing this connection. Inherent to the design paradigm is the ability to develop telerobotic systems that have more than one user and/or more than one workcell.

Essentially, the remote workcell can be viewed as an Internet server that has the ability to move, whether in respect to some global coordinate frame, or through movement of manipulators, etc. The addition of motion to an Internet server (or conversely, Internet connectivity added to a robot) opens up an area that is just starting to be explored.

A primary goal of this model is to separate the user interface (UI) from the workcell control engine, a separation which manifests itself in the telerobotic system software. The separation of the control station and the workcell is no longer solidly defined: the bounds of where specific features of the system are implemented depends upon:

- the method chosen to implement the UI; and

- the required nature of the workcell control engine.

The workcell control engine is responsible for low-level I/O with sensors and actuators. Depending upon the application, it may also be responsible for control algorithms requiring reasonably fast execution speed. It is assumed here that the workcell control engine will be entirely implemented on the physical workcell.

The primary goal of the RIP design model is to develop a standardized workcell control engine that can be utilized by any telerobotic system UI. Conversely, this will allow any UI developer to access the features of the workcell through a standardized interface; something which is essential in a multi-user environment. Such a separation will minimize development time for researchers and developers.

#### 3.4.1 Selection of the Operating System

The operating system (OS) upon which the user interface is implemented can be different than that selected for the workstation control engine.

For quick development time it is suggested that the selected operating systems on the workcell and the control station(s) be identical. This allows direct porting of code common to the control station and the workcell.<sup>1</sup> However, depending upon the application being addressed, common OSs may not be possible. For instance, in design of a system which is intended to be accessed by a wide range of users, it may not be possible to specify a consistent control station OS.

As time progresses and the difference in capabilities of operating systems becomes smaller (reflecting the apparent trend in OS development), this stage of the design process will become simpler. In essence, the choice of the operating system will depend upon the selected user interface and workstation control methods, outlined shortly.

#### 3.4.2 Design Implications

Changing how a telerobotic system is viewed as is suggested under the RIP paradigm changes the design process. A great deal of the design effort needs to be spent on creation of the software interface between the UI and the workcell control engine.

The fact that the Internet is utilized as the communication medium between the control station and the workcell makes this software interface a necessity. To make the telerobotic system usable by the widest range of users it will be necessary to

<sup>&</sup>lt;sup>1</sup> Code porting can also be addressed by the development language. The selection of the development language is addressed in Chapter 6.

accommodate various UIs written on various development platforms: thus, the need for a strictly defined (yet flexible) software interface arises. The fact that multiple users may be in communication with the robot simultaneously also requires a great deal of planning in order to maintain system integrity.

The interface should receive and issue nothing but ASCII characters. The primary reason for this is that strings can encapsulate other data types (by use of their string representations) and thereby offer a sense of global portability. Almost all programming languages deal with strings in an identical way.

In essence, the RIP paradigm emphasizes the need for modularity of the two major system software components – the UI and the workcell control engine. This decoupling is commonplace in software design, and it is suggested that the lessons learned there should be applied to telerobotic systems. When decoupled, telerobotic systems used for research and development may be adopted by institutions with few, if any, changes to the workcell control engine.

### 3.4.3 User Interface Development Considerations

UIs can be developed in many different programming languages. Bearing in mind the telerobotic application and its test-bed nature, the following factors are of interest in selection of the UI development platform:

- hardware independence/portability;

- ease and speed of development; and

- bandwidth/hardware requirements.

Hardware independence describes the ability to quickly port software to new workcell configurations as well as the ability to run the same user-end software on multiple workstation types. Ease and speed of development is especially important in the experimental phase when the developer needs to make rapid changes to the software and quickly simulate various environmental conditions. Bandwidth and hardware requirements may be an issue when power or circuit real estate is at a premium, such as in small mobile robots.

### 3.4.4 Workcell Control Engine Design Implications

The workcell control engine has several roles:

- (1) to provide access to the robot sensors and actuators (low-level I/O):

- (2) to provide feedback control of the actuators (if required by the application): and

- (3) to provide the software interface to the UI.

The typical method of providing low-level I/O to the robot sensors and actuators is through routines written in C or Assembler. The interface to the workcell control engine needs to conform to one major restriction: the data that is initiated by, and destined for, the UI needs to be compatible with data types supported by the control engine development platform. Since one of the major motivations of the RIP paradigm is to allow development of a UI on almost any platform, this interface needs to cover as many bases as possible. This requirement points to the use of ASCII characters (or sequences of characters) as the data type of choice, outlined earlier.

Certain levels of autonomous operation, survival reflexes, etc., may be implemented within the workcell control engine, depending upon the application being addressed. The issue of how complex (how high-level) the workcell control engine should be is still a topic of discussion (see, for instance, [Lum94] or [LMR94]).

The manner in which this is addressed indirectly points to the syntax of the teleoperation language.

The implementation and type of control-loops that are embedded into the work-cell control engine may place requirements on where it is implemented. For instance, a servo-loop that requires a fast sampling rate would be best implemented directly on the workcell in order to avoid any delay presented by the communication medium.

# 3.5 Summary

This chapter has outlined two models which should govern the design process of a teleoperation system. These models are a hardware design model (the test-bed design model) and a software design model (the RIP paradigm), although there is a certain amount of interplay between the roles of the models.

The test-bed model dictates that the design process should be modular and flexible to minimize reconfiguration for research in a specific area of telerobotics.

The RIP paradigm suggests that the workcell, viewed from a software perspective, be considered an Internet server that has the ability to move. The interface between the UI and the workcell control engine should be string-oriented to allow for development of either component in any language. However, the UI and the workcell control engine should be written with portability in mind, allowing for implementation on an arbitrary operating system.

# Chapter 4

# System Overview

### 4.1 Introduction

This chapter contains a high-level description of the system. The discussion of the design is presented in light of the models presented in Chapter 3.

The following components of the design receive attention here:

- (1) the control station hardware:

- (2) the control station operating system:

- (3) the workcell PC hardware (motherboard);

- (4) the workcell PC operating system;

- (5) the communication technology; and

- (6) the client-server relationship.

Chapter 5 details the workcell hardware. Chapter 6 describes the software (and the development platforms) for the components of the system residing on the

microcontroller (sensor/actuator) layer, the workcell (server) layer, and the control-station (client) layer.

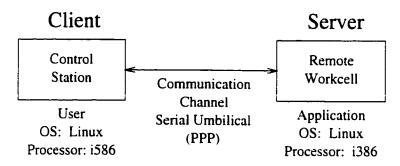

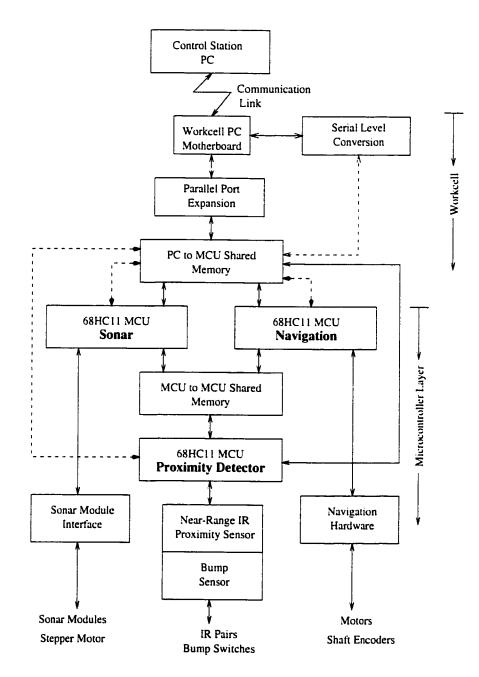

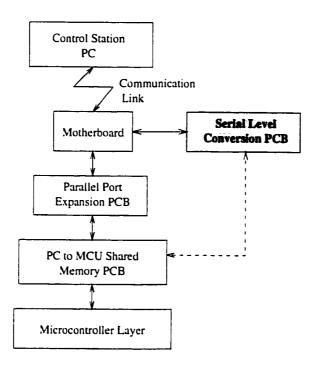

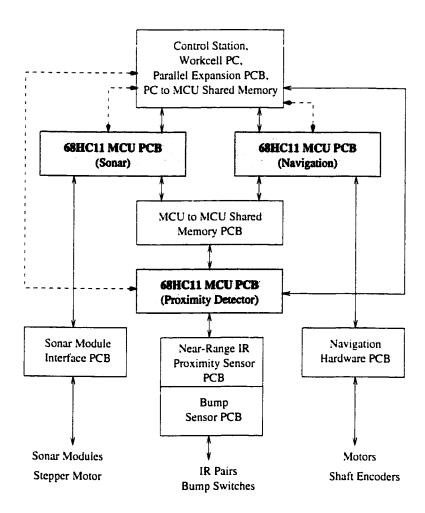

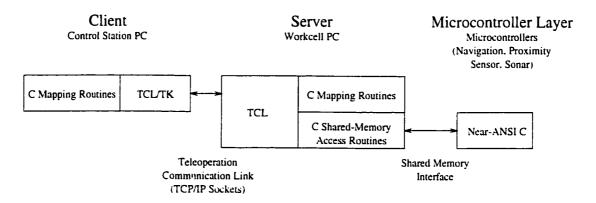

Figure 4.1: A block diagram of the test platform with some details filled in under the guidance of the two design models described in Chapter 3.

Fig. 4.1 is the typical view of a telerobotic system with some details of the design filled-in. Fig. 4.2 shows the system at a more detailed level than Fig. 4.1.

## 4.2 The Control Station

The Control Station is the component of the system upon which the User Interface runs. Commands are sent to, and feedback is received from, the workcell PC motherboard through the communication link.

In the system presented here, the entire workcell control engine is implemented directly on the workcell. Conversely, the UI is implemented on a dedicated PC. This Cyrix 586 motherboard has sufficient computational ability to present UIs to the different users of the system:

- The programmer.

- The user.

- The builder (designer).

Figure 4.2: A block diagram of the system layout. Dashed lines indicate serial communication. The system is divided into three "layers": the control station layer, consisting of the Control Station PC, the workcell PC layer, consisting of the Workcell PC Motherboard, the Serial Level Conversion, Parallel Port Expansion and PC to MCU Shared Memory blocks, and the microcontroller layer.

• The maintainer.

A PC platform was selected due to the wide range of communication peripherals that are available for it: wireless Ethernet, wireless modems, etc.

In addition to the motherboard, the control station PC contains storage devices. external Ethernet connection to the Internet. a 17" monitor, and mouse.

#### 4.2.1 Control Station Operating System

The operating system on the Control Station PC is Linux, a PC derivative of the UNIX operating system. The Linux (RedHat 6.0) platform was selected for a number of reasons:

- It is free:

- It is a truly pre-emptive multitasking operating system:

- The kernel is open-source and modifications can be made to the operating system:

- It is well documented:

- There is a large knowledge-base in the Internet community which freely communicates regarding Linux issues:

- It offers a comprehensive set of development tools, such as C-compilers, debuggers, and text editors;

- It offers the X-windows interface, ideal for GUI development and presentation: and

- It has full TCP/IP support.