#### PWM and Control Strategies for Modular CSC based High Power Application

by

Li Ding

A thesis submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in

Energy Systems

Department of Electrical and Computer Engineering University of Alberta

©Li Ding, 2020

#### Abstract

Current source converter (CSC) enjoys the features such as four quadrant operation, low dv/dt outputs, inherent short circuit protection as well as voltage boost capacity, which made it widely adopted in high voltage direct current (HVDC) system, industry high power medium voltage (MV) motor drives and sustainable energy conversations such as photovoltaic (PV) and wind turbine. Modular CSC has the benefits of improved reliability, extended power range as well as better harmonic performance, which attracted increased attentions these years. The parallel CSC topologies can be divided into two categories: independent DC-link and shared DC-link. One of the major concerns for CSC-fed MV drives is the common-mode voltage (CMV), which can cause motor winding isolation failure. To suppress the CMV, transformerless configuration with integrated common-mode (CM) and differential choke can effectively reduce the system size and cost compared with the bulky isolation transformer. Improved modulation strategies with CMV reduction is desired to further reduce the CM choke size. Another essential issue is the circulating current (CC) flowing through the parallel modules. Moreover, the DC current balance is the priority task for shared DC-link structure since only the total DC current can be regulated. For series CSC, the DC voltages of each module are added up and DC voltage quality improvement is the main target. Therefore, the modulation strategies should be designed specifically for different modular structures. Meanwhile, the low

switching frequency of CSC based high power application puts great challenge for the controller and observer design.

The purposes of this research work are to develop the improved modulation strategies as well as the control methods to deal with these challenges. The space vector modulation (SVM) based CMV average value reduction (AVR) methods are proposed for independent DC-link parallel configuration to suppress the CMV and CC while achieving multilevel output. A multilevel SVM based DC current balance and CMV reduction method is proposed for shared DC-link parallel structure to simultaneously balance the DC current and suppress CMV. To achieve easy-implement for N-CSC (N≥3) system, an interleaved carrier-based sinusoidal pulse-width modulation (SPWM) is proposed and it can be further extended into mixed series-parallel CSC system, where better AC current and DC voltage can be achieved simultaneously. Besides, a typical CSC-fed drive application with long cable application: electrical submersible pump (ESP) is also studied. A multi-loop controller is developed to improve the system dynamic performance and attenuate the LC resonance. Moreover, an adaptive discrete-time sliding mode observer (SMO) based sensorless method is proposed to estimate the rotor speed and position. Such modulation and control development can effectively overcome the aforementioned challenges and guarantee good performance for practical applications.

### Acknowledgements

First and foremost, I would like to thank my Ph. D. supervisor, Professor Yunwei (Ryan) Li for his continuous support and guidance through these years. His insightful advices and encouragement helped me a lot to overcome different challenges and enrich my research experience. It is always my great honor to join in Prof. Li's group and I pretty enjoy this journey.

Besides, I would like to express my appreciation to Dr. Kai Sun, who provided me an opportunity to visit Tsinghua University. I would also like to thank Dr. Ye (Eric) Zhang, Dr. Zhongyi (Alex) Quan, Dr. Hao Tian and Dr. Dehong Zhou for their helps on hardware. Also, the peer support from all other lab members means a lot for me, thanks for their kind help during my Ph. D.

I would also like to thank Alberta Innovates Graduate Student Scholarship program for their financial support during my Ph. D.

Finally, I would like to sincerely thank my girlfriend Miss. Mei Hu for her great support and company during the past years, I really enjoys the daily stories we had made and looking forward the future life we planned together.

### **Table of Contents**

| СН  | CHAPTER 1 INTRODUCTION1 |                                                          |     |  |

|-----|-------------------------|----------------------------------------------------------|-----|--|

| 1.1 | Ct                      | JRRENT SOURCE CONVERTERS AND APPLICATIONS                | 2   |  |

|     | 1.1.1                   | High Voltage Direct Current System                       | 2   |  |

|     | 1.1.2                   | High Power Medium Voltage Drives                         | 4   |  |

|     | 1.1.3                   | Low Power High Switching Frequency Application           | 6   |  |

| 1.2 | PA                      | RALLEL CSC-FED SYSTEM AND MODULATION STRATEGIES          | 8   |  |

|     | 1.2.1                   | Parallel CSC Topology                                    | 9   |  |

|     | 1.2.2                   | Modulation Strategies                                    | 11  |  |

|     | 1.2.3                   | Comparison of CSC Modulation                             | 19  |  |

|     | 1.2.4                   | Modulation Strategies for Parallel CSC System            | 21  |  |

| 1.3 | SE                      | ENSORLESS CSC-FED HIGH POWER DRIVES                      | 24  |  |

|     | 1.3.1                   | Sensorless Control Strategies                            | 25  |  |

|     | 1.3.2                   | Discrete-time Modeling                                   |     |  |

|     | 1.3.3                   | High-speed Electrical Submersible Pump System            |     |  |

| 1.4 | Ri                      | ESEARCH OBJECTIVES AND CONTRIBUTIONS                     | 27  |  |

| СН  | APTE                    | <b>R 2</b> CMV RESONANCE AND CIRCULATING CURRE           | NT  |  |

| SU  | PPRES                   | SION WITH INDEPENDENT DC-LINK                            | 30  |  |

| 2.1 | Сс                      | DMMON-MODE LOOP CIRCUIT ANALYSIS                         | 31  |  |

| 2.2 | SV                      | /M BASED CMV REDUCTION METHOD                            | 37  |  |

|     | 2.2.1                   | Interleaved SVM based CMV Reduction                      | 37  |  |

|     | 2.2.2                   | Multilevel SVM based CMV Reduction                       | 40  |  |

| 2.3 | V                       | VERIFICATION RESULTS                                     | 45  |  |

| 2.4 | St                      | JMMARY                                                   | 52  |  |

| СН  | APTE                    | <b>R 3</b> SIMULTANEOUS DC CURRENT BALANCE AND           | CMV |  |

| RE  | DUCTI                   | ON WITH SHARED DC-LINK                                   | 53  |  |

| 3.1 | D                       | C-LINK AND COMMON-MODE LOOP CIRCUIT ANALYSIS             | 55  |  |

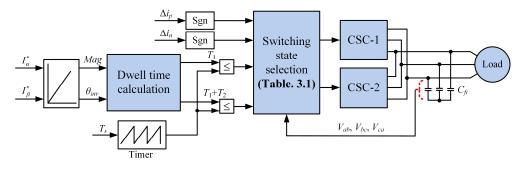

| 3.2 | SI                      | MULTANEOUS DC CURRENT BALANCE AND CMV REDUCTION STRATEGY | 59  |  |

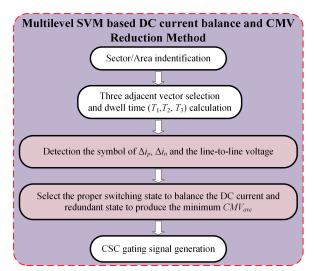

|     | 3.2.1                   | Multilevel SVM based Method                              | 60  |  |

|     | 3.2.2                   | Interleaved SPWM based Method                            | 63  |  |

| 3.3 | VI                      | ERIFICATION RESULTS                                      | 66  |  |

| 3.4 | Su                      | JMMARY                                                   | 75  |  |

| СН  | APTE                    | <b>R 4 MIXED SERIES-PARALLEL CSC SYSTEM AND</b>          |     |  |

| OP  | TIMIZ                   | ED CARRIER-BASED SPWM                                    | 76  |  |

| 4.1 | OI    | PTIMIZED CARRIER-BASED SPWM WITH REDUCED CMV          | 78  |

|-----|-------|-------------------------------------------------------|-----|

|     | 4.1.1 | Optimized Bi-tri logic SPWM                           | 79  |

|     | 4.1.2 | PWM Sequence and CMV Comparison                       | 85  |

| 4.2 | М     | IXED SERIES-PARALLEL CSC SYSTEM WITH INTERLEAVED SPWM |     |

|     | 4.2.1 | DC-link Voltage Analysis                              |     |

|     | 4.2.2 | Optimized Interleaving Angle Design                   |     |

| 4.3 | VI    | ERIFICATION RESULTS                                   | 93  |

| 4.4 | St    | JMMARY                                                | 102 |

| СН  | IAPTE | <b>R 5 DISCRETE-TIME SMO BASED SENSORLE</b>           | SS  |

| CO  | NTRO  | L FOR CSC-FED PMSM DRIVES                             | 103 |

| 5.1 | М     | ULTI-LOOP FIELD-ORIENTED CONTROL                      | 106 |

|     | 5.1.1 | CSC-fed PMSM Model                                    |     |

|     | 5.1.2 | Multi-loop Current Controller Design                  |     |

| 5.2 | AI    | DAPTIVE DISCRETE-TIME SMO                             | 109 |

|     | 5.2.1 | Conventional SMO                                      |     |

|     | 5.2.2 | Discrete-time SMO Design                              | 111 |

|     | 5.2.3 | Adaptive Back-EMF Filter Design                       | 112 |

|     | 5.2.4 | High-speed Drive with Long Cable Application          | 115 |

| 5.3 | VI    | ERIFICATION RESULTS                                   | 117 |

| 5.4 | Su    | JMMARY                                                | 126 |

| СН  | IAPTE | <b>R 6 CONCLUSIONS AND FUTURE WORK</b>                | 127 |

| 6.1 | Сс    | DNCLUSION                                             | 127 |

| 6.2 | Tł    | IESIS CONTRIBUTION                                    | 129 |

| 6.3 | Fu    | JTURE WORK                                            | 131 |

| RE  | FEREN | NCES 133                                              |     |

## **List of Figures**

| Fig. 1.1. Hybrid current source HVDC system for offshore wind power generation                                      | 2      |

|---------------------------------------------------------------------------------------------------------------------|--------|

| Fig. 1.2. Series connected PWM CSC for HVDC application.                                                            | 3      |

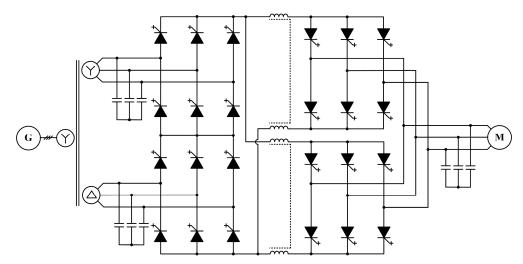

| Fig. 1.3. PWM CSC-fed MV drive with isolation transformer.                                                          | 4      |

| Fig. 1.4. PWM CSC-fed MV drive with dual-bridge rectifier                                                           | 5      |

| Fig. 1.5. Transformerless PWM CSC-fed MV drive                                                                      | 5      |

| Fig. 1.6. Single stage three-phase boost CSI-interfaced PV application.                                             | 7      |

| Fig. 1.7. System diagram of CSI-fed drives for EV application                                                       | 7      |

| Fig. 1.8. Parallel CSC system with independent DC source                                                            | 10     |

| Fig. 1.9. Parallel CSC system with shared DC source                                                                 | 10     |

| Fig. 1.10. Modulation strategies of CSC.                                                                            | 11     |

| Fig. 1.11. Space vector modulation of CSC, (a) CSC diagram, (b) space vector diagram                                | 13     |

| Fig. 1.12. Selective harmonic elimination modulation                                                                | 13     |

| Fig. 1.13. Trapezoidal pulse-width modulation                                                                       | 14     |

| Fig. 1.14. Space vector diagram, (a) VSC, (b) CSC.                                                                  | 15     |

| Fig. 1.15. Bi-tri logic SPWM, (a) bi-tri logic translation, (b) gating signals                                      | 16     |

| Fig. 1.16. SS-DPWM principle, (a) modulation waveforms, (b) digital implement                                       | 17     |

| Fig. 1.17. DDPWM principle, (a) <i>I<sub>max</sub></i> and <i>I<sub>min</sub></i> waveforms, (b) digital implement. | 18     |

| Fig. 1.18. PWM waveforms and harmonic distribution with different modulations                                       | 20     |

| Fig. 1.19. THD and switching time comparison with different CSC modulations                                         | 21     |

| Fig. 1.20. Interleaved SVM for 2-CSC parallel system.                                                               | 22     |

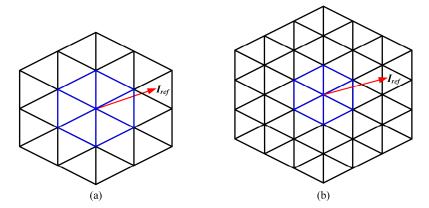

| Fig. 1.21. Space vector diagram, (a) 2-CSC parallel system, (b) 3-CSC parallel system                               | 23     |

| Fig. 1.22. Interleaved carrier-based SPWM for 2-CSC parallel system.                                                | 24     |

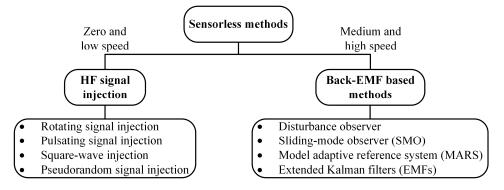

| Fig. 1.23. Sensorless control strategies                                                                            | 25     |

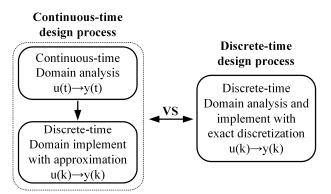

| Fig. 1.24. Continuous and discrete-time design process                                                              | 26     |

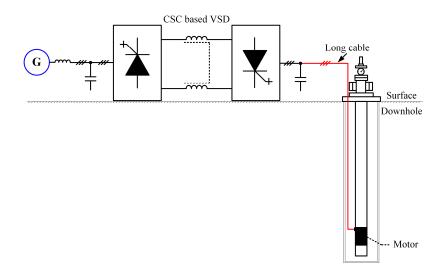

| Fig. 1.25. CSC-fed ESP system                                                                                       | 27     |

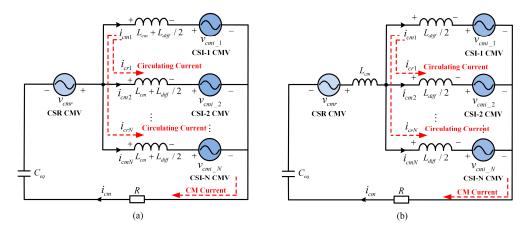

| Fig. 2.1. Parallel connected CSC-fed motor drive system with independent DC-link                                    | 30     |

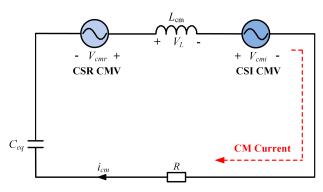

| Fig. 2.2. Common-mode loop circuit for single CSC                                                                   | 32     |

| Fig. 2.3. Equivalent common-mode loop circuit of single CSC                                                         | 33     |

| Fig. 2.4. Space vector diagram of 2-CSC parallel system.                                                            | 34     |

| Fig. 2.5. Equivalent common-mode loop circuit of parallel CSC system.                                               | 35     |

| Fig. 2.6. Interleaved SVM based CMV reduction.                                                                      | 37     |

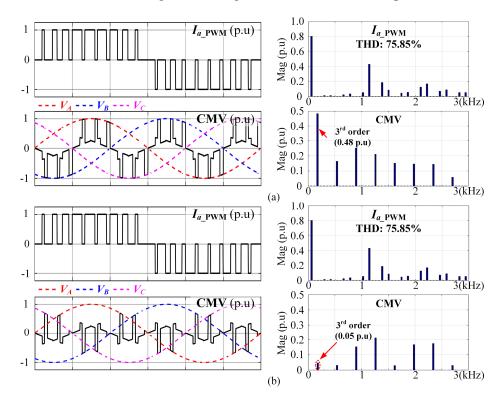

| Fig. 2.7. Output current PWM and CMV waveforms of single CSC ( $m_a=0.8, f_0=60$ Hz, $f_s=10$                       | 80Hz), |

| (a) conventional 3-segment SVM, (b) 3-segment AVR SVM                                                               | 38     |

| Fig. 2.8. Output current PWM and CMV waveforms of parallel CSC ( $m_a$ =0.8, $f_{0}$ =                              | =60Hz, |

| f <sub>3</sub> =1080Hz), (a) conventional 3-segment SVM, (b) 3-segment AVR SVM                                      | 39     |

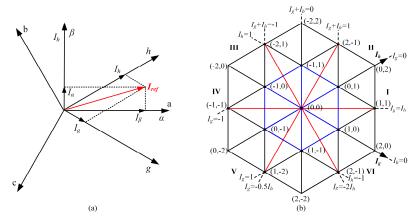

| Fig. 2.9. <i>g</i> - <i>h</i> frame transform, (a) $\alpha$ - $\beta$ frame to <i>g</i> - <i>h</i> frame, (b) space vector   |

|------------------------------------------------------------------------------------------------------------------------------|

| Fig. 2.10. Multilevel SVM based CMV reduction                                                                                |

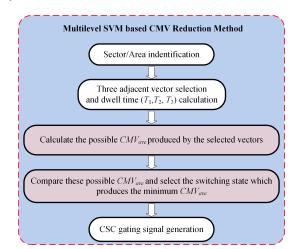

| Fig. 2.11. Flowchart of multilevel SVM based CMV reduction                                                                   |

| Fig. 2.12. Third-order CMV component, (a) interleaved conventional 3-segemnt SVM, (b)                                        |

| interleaved 3-segment AVR SVM, (c) conventional 5-level SVM, (d) 5-level AVR SVM                                             |

| Fig. 2.13. Simulation results of CMV, CMC and CC waveform of 2-CSC parallel system under                                     |

| 10Hz output frequency (a) 3-level AVR SVM, (b) conventional 5-level SVM, (c) 5-level AVR                                     |

| SVM                                                                                                                          |

| Fig. 2.14. Simulation results of CMV, CMC and CC waveform of 2-CSC parallel system under                                     |

| 13Hz output frequency (a) 3-level AVR SVM, (b) conventional 5-level SVM, (c) 5-level AVR                                     |

| SVM                                                                                                                          |

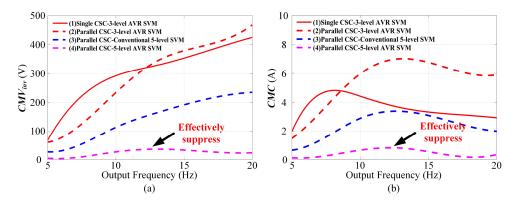

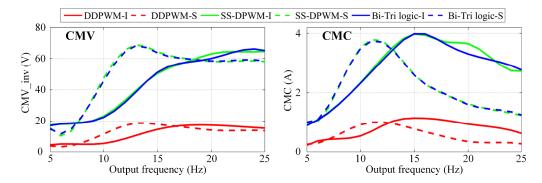

| Fig. 2.15. Simulation results of different modulation strategies under variable output frequency,                            |

| third-order component of (a) inverter-side CMV, (b) CMC                                                                      |

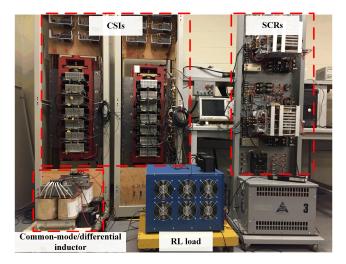

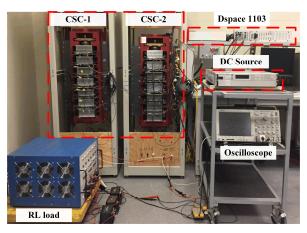

| Fig. 2.16. Experiment setup of 2-CSC parallel system                                                                         |

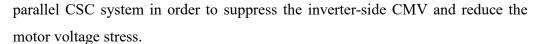

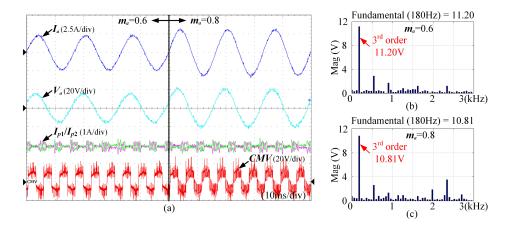

| Fig. 2.17. Single and parallel CSC operation, (a) output waveforms, (b) CMV FFT results of single                            |

| CSC operation, (c) CMV FFT results of parallel CSC operation                                                                 |

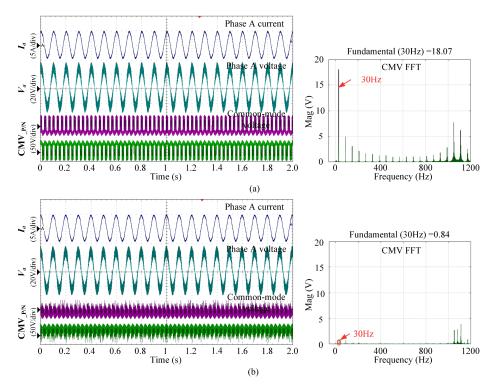

| Fig. 2.18. Experimental results of 2-CSC parallel system with 10Hz output frequency, (a)                                     |

| conventional 3-level SVM, (b) 5-level AVR SVM                                                                                |

| Fig. 2.19. Experimental results of 2-CSC parallel system with 15Hz output frequency, (a)                                     |

| conventional 3-level SVM, (b) 5-level AVR SVM                                                                                |

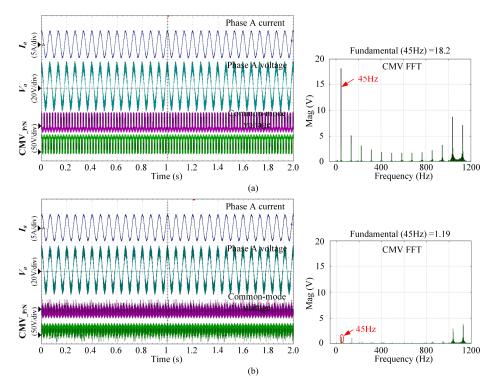

| Fig. 3.1. Parallel CSC system with shared DC-link (a) independent CM choke, (b) shared CM                                    |

| choke                                                                                                                        |

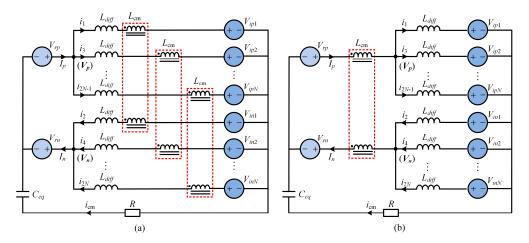

| Fig. 3.2. Equivalent DC-link circuit of N-CSC parallel system with shared DC-link, (a) independent                           |

| CM choke, (b) shared CM choke                                                                                                |

| Fig. 3.3. Equivalent common-mode loop circuit of N-CSC parallel system with shared DC-link, (a)                              |

| independent CM choke, (b) shared CM choke                                                                                    |

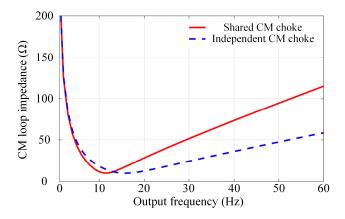

| Fig. 3.4. CM loop impedance with shared and independent CM choke                                                             |

| Fig. 3.5. Multilevel based DC current balance strategy                                                                       |

| Fig. 3.6. Space vector sequence and DC current influence in sector 1 area 3                                                  |

| Fig. 3.7. Flowchart of multilevel SVM based DC current balance and CMV reduction method 62                                   |

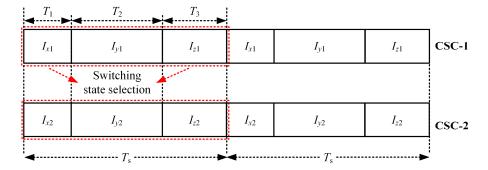

| Fig. 3.8. PWM sequence of interleaved DDPWM                                                                                  |

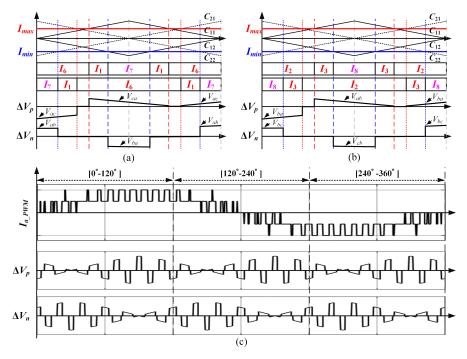

| Fig. 3.9. PWM sequence and voltage difference of interleaved DDPWM, (a) $\omega t=15^{\circ}$ , (b) $\omega t=135^{\circ}$ , |

| (c) one fundamental cycle                                                                                                    |

| Fig. 3.10. Active DC current balance with interleaved DDPWM                                                                  |

| Fig. 3.11. CMV, CC and CMC waveforms at 20Hz (a) independent CM choke (b) shared CM                                          |

| choke                                                                                                                        |

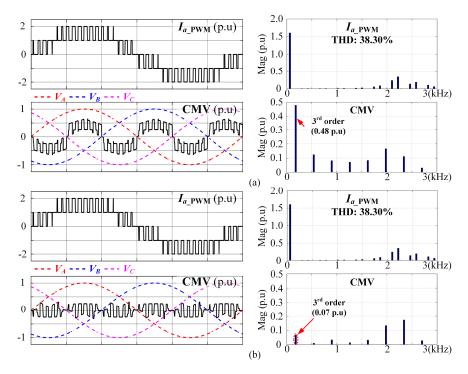

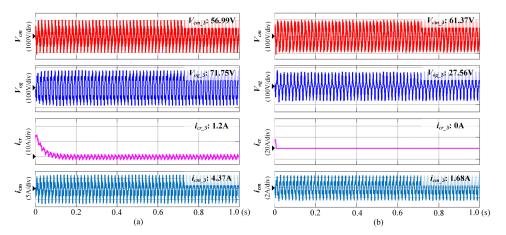

| Fig. 3.12. Simulation results of multilevel SVM with 10Hz output frequency, (a) DC-link current                          |

|--------------------------------------------------------------------------------------------------------------------------|

| and CMV waveforms, CMV FFT results of (b) DC current balance method, (c) DC current                                      |

| balance with CMV reduction method                                                                                        |

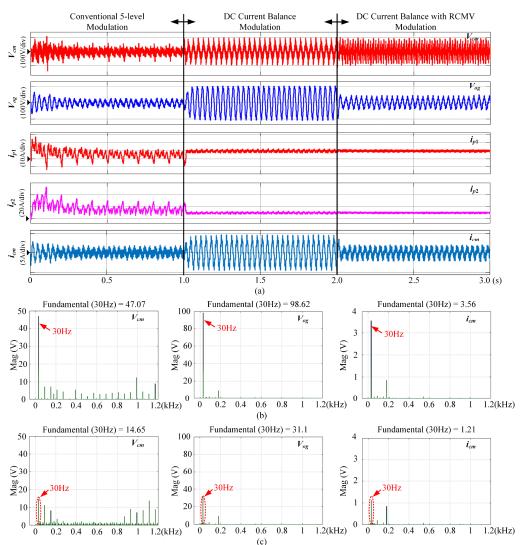

| Fig. 3.13. Simulation results of different interleaved SPWMs with independent CM choke                                   |

| structure, (a) DC-link current and CMV waveforms, CMV FFT results of (b) BTSPWM, (c)                                     |

| SS-DPWM, (d) DDPWM                                                                                                       |

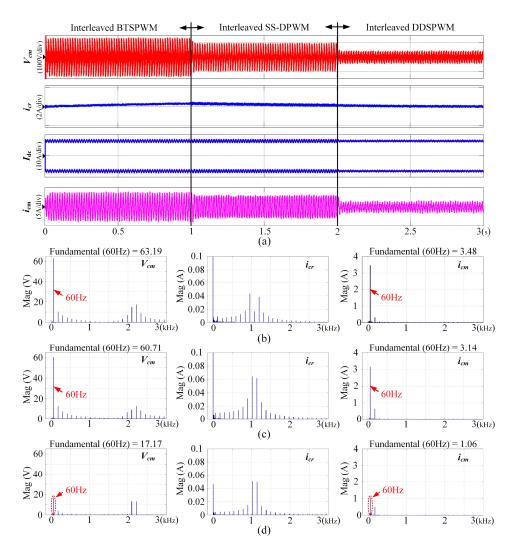

| Fig. 3.14. Simulation results of different interleaved SPWMs with shared CM choke structure, (a)                         |

| DC-link current and CMV waveforms, CMV FFT results of (b) BTSPWM, (c) SS-DPWM, (d)                                       |

| DDPWM                                                                                                                    |

| Fig. 3.15. Simulation results of independent and shared CM choke parallel structure with different                       |

| interleaved SPWMs                                                                                                        |

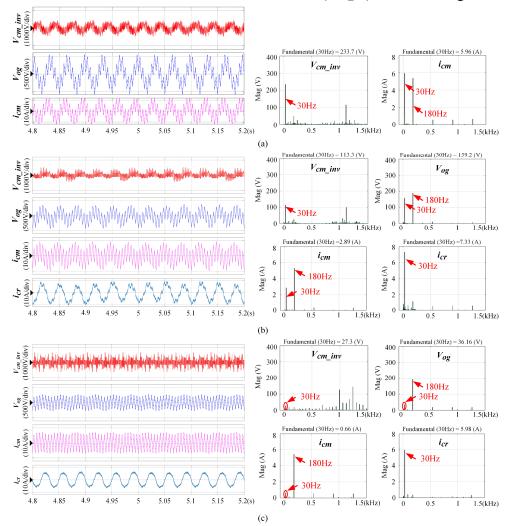

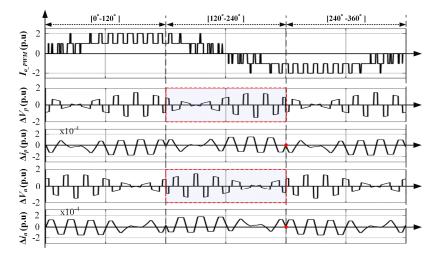

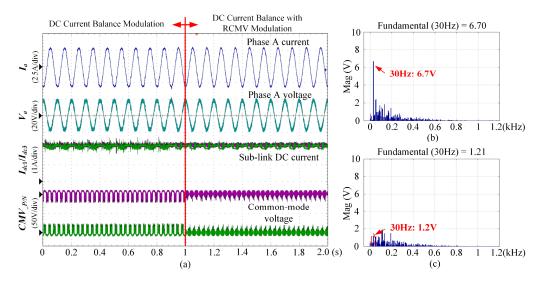

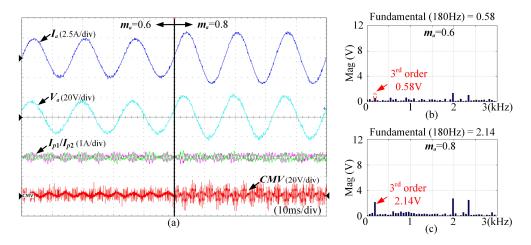

| Fig. 3.16. Experimental results of multilevel SVM with 10Hz output frequency, (a) DC-link                                |

| current and CMV waveforms, CMV FFT results of (b) DC current balance method, (c) DC current                              |

| balance with RCMV method                                                                                                 |

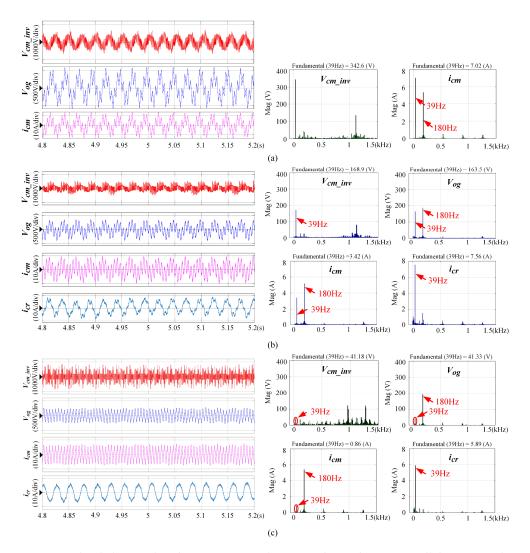

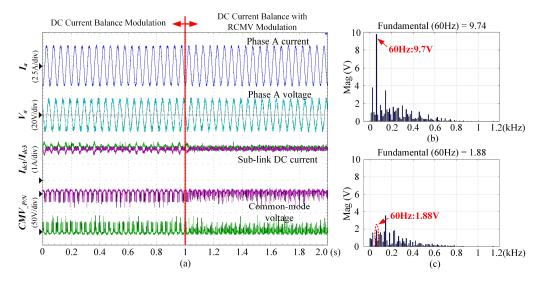

| Fig. 3.17. Experimental results of multilevel SVM with 20Hz output frequency, (a) DC-link                                |

| current and CMV waveforms, CMV FFT results of (b) DC current balance method, (c) DC current                              |

| balance with RCMV method                                                                                                 |

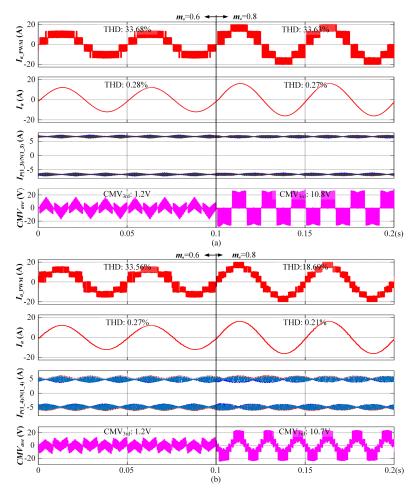

| Fig. 3.18. Experimental results of SS-DPWM with 60Hz output frequency, (a) DC-link current and                           |

| CMV waveforms, CMV FFT results of (b) $m_a=0.6$ , (c) $m_a=0.8$                                                          |

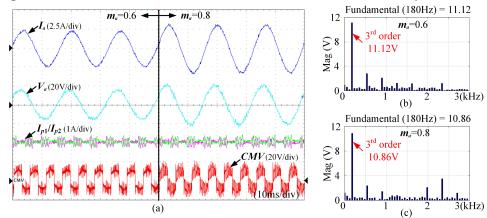

| Fig. 3.19. Experimental results of discontinuous BTSPWM with 60Hz output frequency, (a)                                  |

| DC-link current and CMV waveforms, CMV FFT results of (b) $m_a=0.6$ , (c) $m_a=0.8$                                      |

| Fig. 3.20. Experimental results of DDPWM with 60Hz output frequency, (a) DC-link current and                             |

| CMV waveforms, CMV FFT results of (b) $m_a=0.6$ , (c) $m_a=0.8$                                                          |

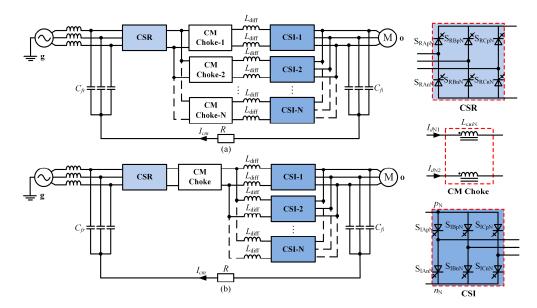

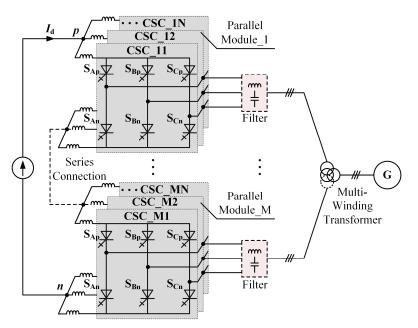

| Fig. 4.1. Mixed series-parallel CSC system                                                                               |

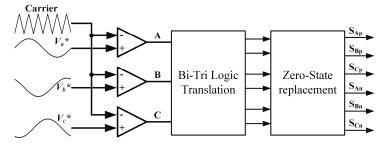

| Fig. 4.2. Bi-tri logic SPWM principle                                                                                    |

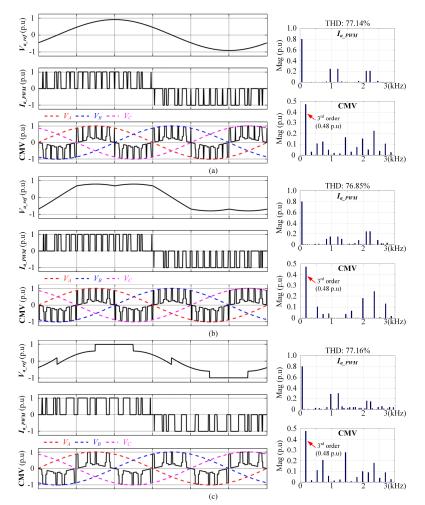

| Fig. 4.3. Current PWM and CMV waveforms with BTSPWM, (a) case 1, (b) case 2, (c) case 3 80                               |

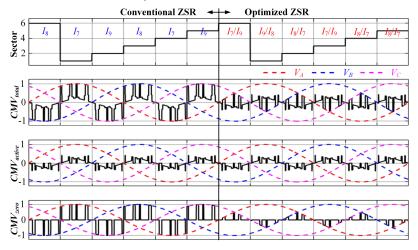

| Fig. 4.4. PWM sequence and CMV waveforms of discontinuous BTSPWM ( $m_a=0.8, \varphi=0^\circ$ ), (a)                     |

| PWM sequence, (b) CMV waveforms                                                                                          |

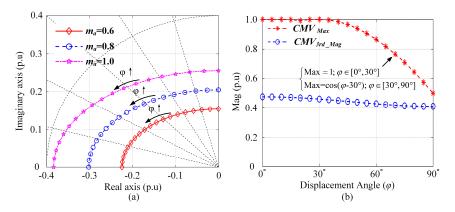

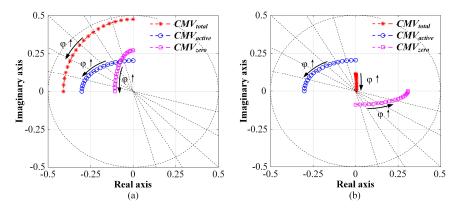

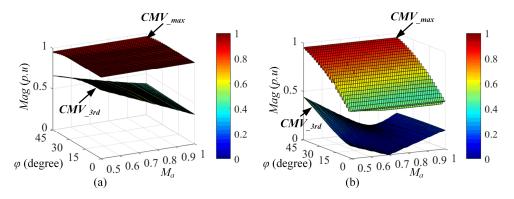

| Fig. 4.5. CMV features of discontinuous BTSPWM, (a) third-order CMVactive, (b) maximum value                             |

| and third-order CMV <sub>total</sub> (m <sub>a</sub> =0.8)                                                               |

| Fig. 4.6. CMV third-order component changing with displacement angle ( $m_a=0.8$ , $\varphi=0^{\circ}-90^{\circ}$ ), (a) |

| conventional ZSR, (b) optimized ZSR                                                                                      |

| Fig. 4.7. CMV waveforms ( $m_a=0.8$ , $\varphi=0^\circ$ ) of discontinuous BTSPWM, (a) conventional ZSR, (b)             |

| optimized ZSR                                                                                                            |

| Fig. 4.8. CMV maximum value and third-order component, (a) conventional ZSR, (b) optimized                               |

| ZSR                                                                                                                      |

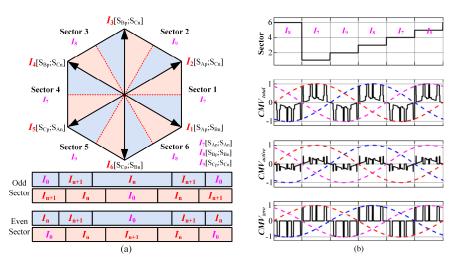

| Fig. 4.9. PWM sequence of carrier based SPWMs, (a) space vector diagram, (b) discontinuous          |

|-----------------------------------------------------------------------------------------------------|

| Bi-tri logic SPWM, (c) SS-DPWM, (d) DDPWM                                                           |

| Fig. 4.10. Interleaved DDPWM for N-CSC parallel system                                              |

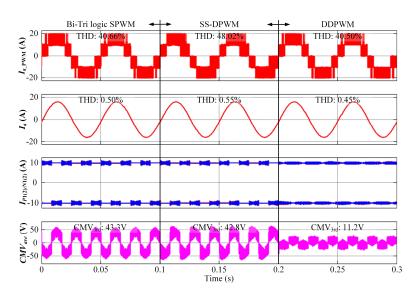

| Fig. 4.11. Current PWM and CMV waveforms of interleaved carrier-based SPWMs (fo=60Hz,               |

| $f_s$ =1080Hz, $m_a$ =0.8), (a) discontinuous BTSPWM, (b) SS-DPWM, (c) DDPWM                        |

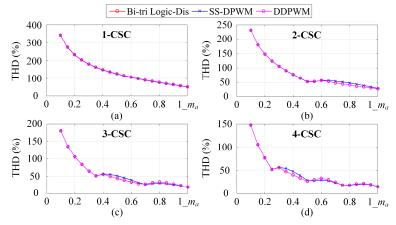

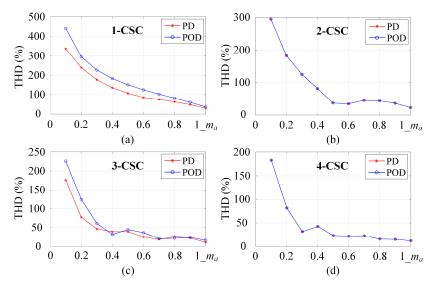

| Fig. 4.12. THD performance of carrier-based SPWMs, (a) single CSC, (b) 2 parallel CSC, (b) 3        |

| parallel CSC, (c) 4 parallel CSC                                                                    |

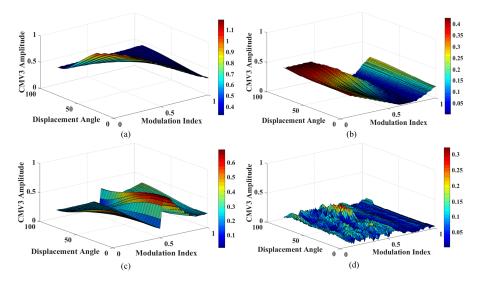

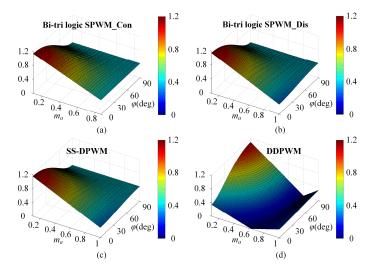

| Fig. 4.13. Third-order CMV (p.u), (a) Bi-tri logic SPWM_ case 1, (b) Bi-tri logic SPWM_ case 3      |

| (c) SS-DPWM, (d) DDPWM                                                                              |

| Fig. 4.14. Series CSC structure                                                                     |

| Fig. 4.15. DC-link voltage analysis for series CSC system, (a) system diagram, (b) POD              |

| Fig. 4.16. DC voltage and harmonic distribution of POD with series connection ( $m_a=0.8$ ,         |

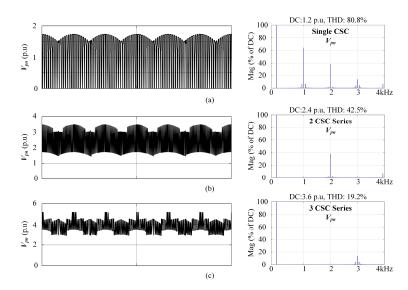

| interleaving angle 360°/M), (a) single CSC (b) 2 CSCs, (c) 3 CSCs                                   |

| Fig. 4.17. THD of DC voltage with series connection, (a) single CSC (b) 2 CSCs, (c) 3 CSCs, (d) 4   |

| CSCs                                                                                                |

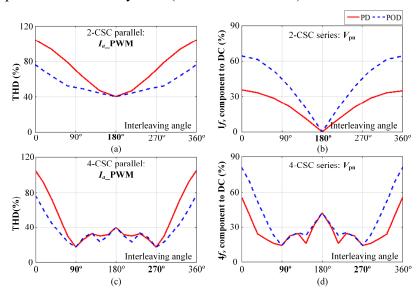

| Fig. 4.18. THD of AC current and DC voltage ( $m_a=0.8$ ) (a) 2-CSC parallel, (b) 2-CSC series, (c) |

| 4-CSC parallel, (d) 4-CSC series                                                                    |

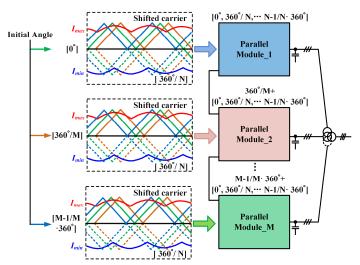

| Fig. 4.19. Carrier-shift SPWM for modular series-parallel connected CSC system                      |

| Fig. 4.20. Simulation results with different carrier based SPWMs                                    |

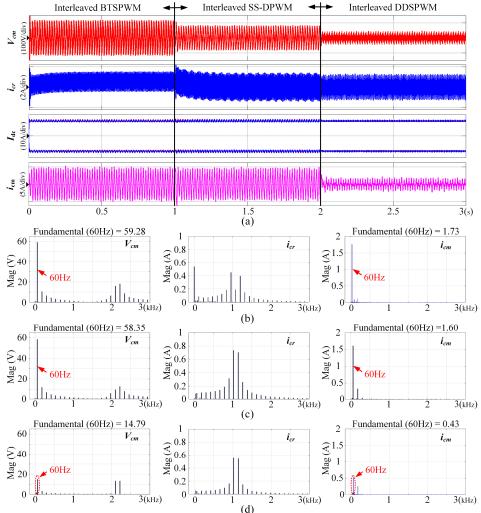

| Fig. 4.21. Simulation results of N-CSC parallel with interleaved DDPWM, (a) N=3, (b) N=495          |

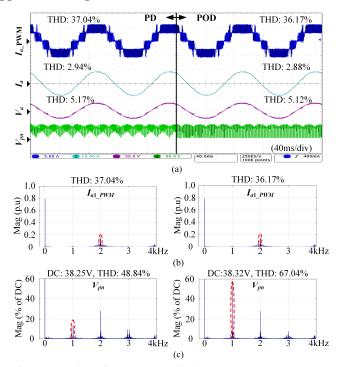

| Fig. 4.22. Simulation results of 2-parallel 3-series CSC system, (a) output waveforms, harmonic     |

| distribution of (b) AC outputs, (c) DC voltage                                                      |

| Fig. 4.23. Simulation results of 3-parallel 2-series CSC system, (a) output waveforms, harmonic     |

| distribution of (b) AC outputs, (c) DC voltage                                                      |

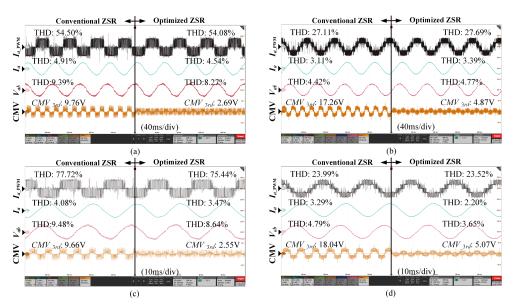

| Fig. 4.24. Experiment setup for series or parallel CSC system                                       |

| Fig. 4.25. Experiment results with conventional and optimized ZSR, single CSC (a) 20Hz, (c)         |

| 50Hz, parallel CSC (b) 20Hz, (d) 50Hz                                                               |

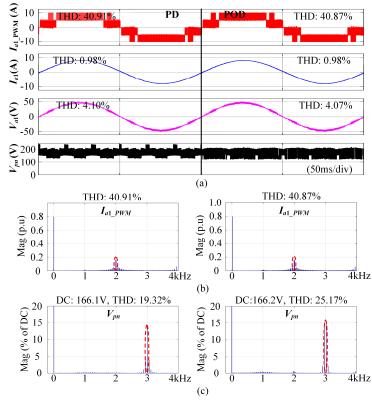

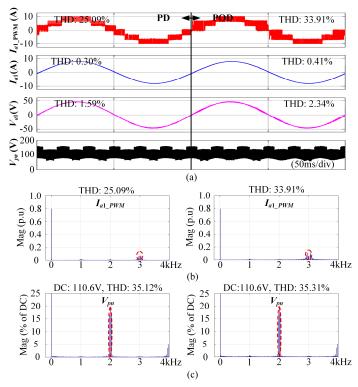

| Fig. 4.26. Experiment results of 2-CSC parallel system (a) AC output and DC voltage, harmonic       |

| distribution of (b) AC outputs, (c) DC voltage                                                      |

| Fig. 4.27. Experiment results of 2-CSC series system (a) AC output and DC voltage, harmonic         |

| distribution of (b) AC outputs, (c) DC voltage                                                      |

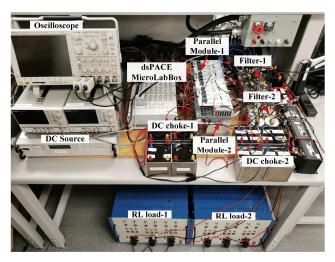

| Fig. 4.28. Experiment setup for mixed series and parallel CSC system                                |

| Fig. 4.29. Experiment results of mixed 2 series and 2 parallel CSC (a) PD, (b) POD 101              |

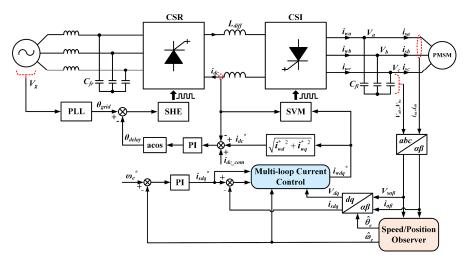

| Fig. 5.1. Sensorless control diagram of CSC-fed PMSM drives 104                                     |

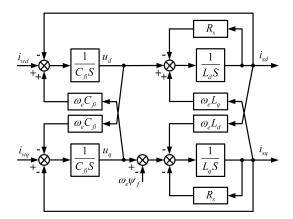

| Fig. 5.2. Capacitor filter and PMSM model in synchronous frame 107                                  |

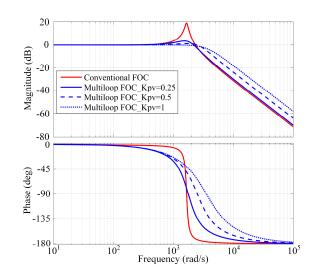

| Fig. 5.3. Multi-loop current controller, (a) capacitor voltage loop, (b) current loop 107           |

| Fig. 5.4. Bode diagram of current loop of CSC-fed PMSM drives 109                                   |

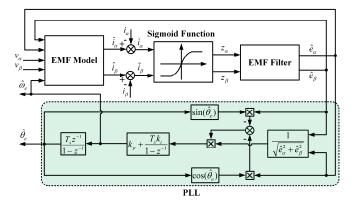

| Fig. 5.5. Basic structure of SMO with quadrature PLL                                                  |

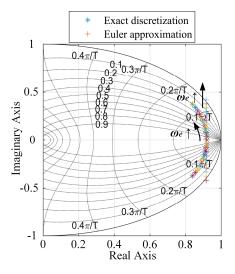

|-------------------------------------------------------------------------------------------------------|

| Fig. 5.6. Pole migration of conventional and discrete-time SMO under actual parameters 112            |

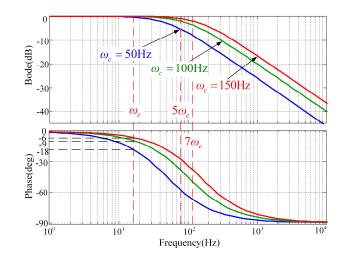

| Fig. 5.7. Bode diagram of LPF                                                                         |

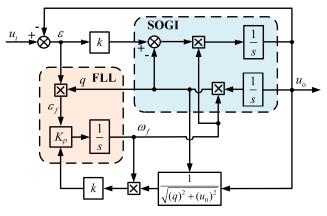

| Fig. 5.8. Basic structure of SOGI and FLL                                                             |

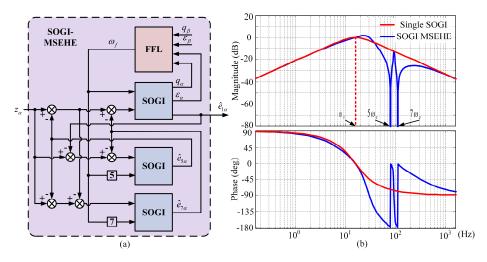

| Fig. 5.9. Multiple SOGI-MSEHE, (a) block diagram, (b) bode diagram of single SOGI and                 |

| SOGI-MSEHE                                                                                            |

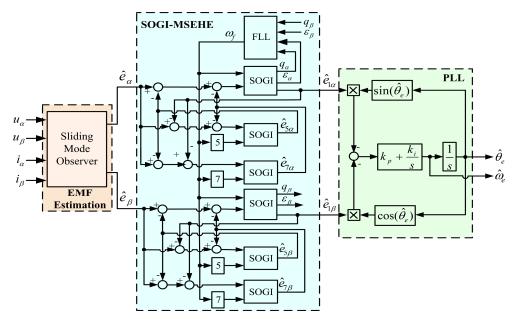

| Fig. 5.10. Sliding mode observer combined with SOGI-MSEHE 115                                         |

| Fig. 5.11. CSC-fed ESP system with long cable connection                                              |

| Fig. 5.12. Pole migration of conventional and discrete-time SMO under 50% $L_q$ mismatch 116          |

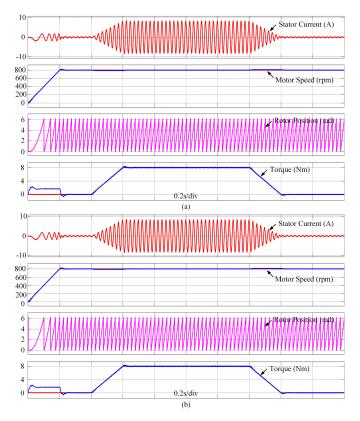

| Fig. 5.13. Simulation results of speed and position estimation errors with step speed change, (a)     |

| conventional SMO with LPF, (b) discrete-time SMO with LPF, (c) discrete-time SMO with                 |

| SOGI-MSEHE                                                                                            |

| Fig. 5.14. Simulation results of speed and position estimation errors with step load change, (a)      |

| conventional SMO with LPF, (b) discrete-time SMO with LPF, (c) discrete-time SMO with                 |

| SOGI-MSEHE                                                                                            |

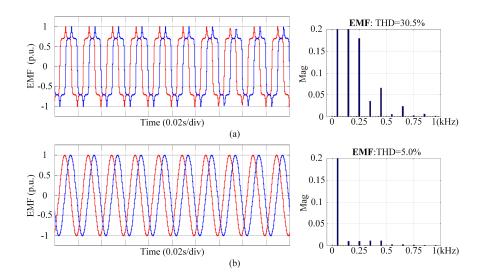

| Fig. 5.15. EMF waveform and harmonic distribution, (a) LPF, (b) SOGI-MSEHE 120                        |

| Fig. 5.16. Simulation results of CSC-fed PMSM with long cable application, (a) 0 km, (b) 5 km.        |

|                                                                                                       |

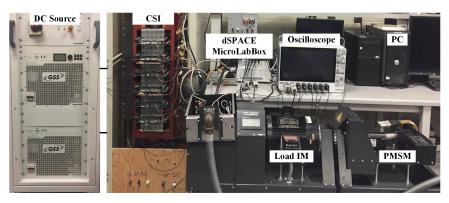

| Fig. 5.17. Experiment Setup 121                                                                       |

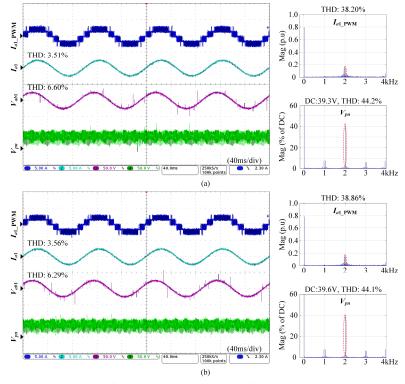

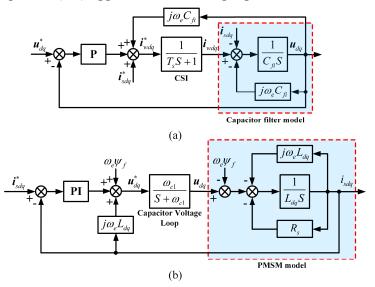

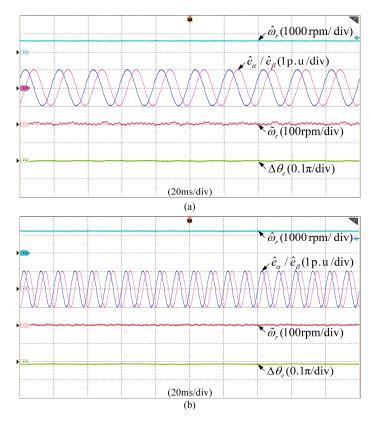

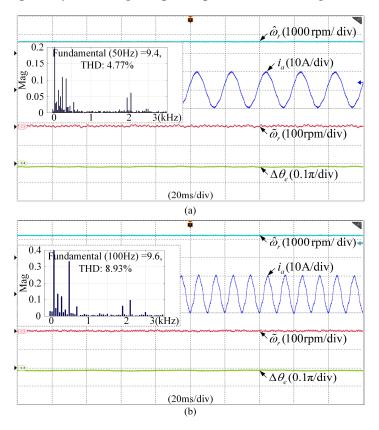

| Fig. 5.18. Steady-state experimental results of speed and position estimation error with no load, (a) |

| 600 rpm, (b) 1200 rpm                                                                                 |

| Fig. 5.19. Steady-state results of position estimation error with 8 Nm load, (a) 600 rpm, (b) 1200    |

| rpm                                                                                                   |

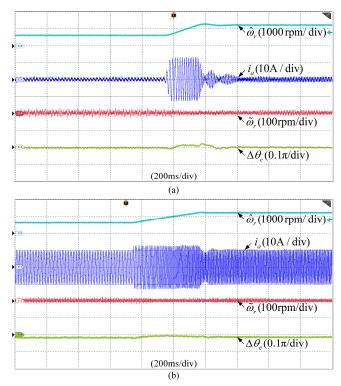

| Fig. 5.20. Experimental results step load change from 0 Nm to 8 Nm, (a) 600 rpm, (b) 1200 rpm.        |

|                                                                                                       |

| Fig. 5.21. Experimental results of step speed change from 600 rpm to 1200 rpm, (a) no load, (b) 8     |

| Nm load                                                                                               |

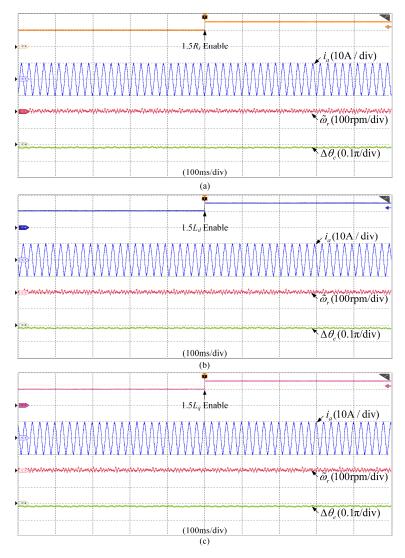

| Fig. 5.22. Experimental results with parameter mismatch under 600rpm and 4Nm load, (a) 1.5 $R_s$ ,    |

| (b) $1.5L_d$ , (c) $1.5L_q$                                                                           |

### List of Tables

| Table 1.1. Bi-tri logic translation                             | 15  |

|-----------------------------------------------------------------|-----|

| Table 1.2. Switching sequence with different modulations        | 19  |

| Table 2.1 Common-mode voltage of single CSC                     | 33  |

| Table 2.2. Common-mode voltage of 2-CSC parallel system         |     |

| Table 2.3. Sector and area identification                       | 41  |

| Table 2.4. Three adjacent vector selection                      | 42  |

| Table 2.5. Dwell time in Sector I                               | 42  |

| Table 2.6. Simulation and experiment parameters                 | 45  |

| Table 3.1. DC current influence with different switching states | 60  |

| Table 3.2. DC current influence with interleaved DDPWM          | 64  |

| Table 3.3. Simulation and experiment parameters                 | 67  |

| Table 4.1. Switching Sequence of discontinuous BTSPWM and DDPWM | 85  |

| Table 4.2. Simulation and experiment results                    |     |

| Table 5.1. Simulation and experiment parameters                 | 117 |

| Table 5.2. THD of phase current with long cable application     | 121 |

### List of Abbreviations

| AC               | Alternating current                                                   |

|------------------|-----------------------------------------------------------------------|

| AVR              | Average value reduction                                               |

| BTSPWM           | Bi-tri logic SPWM                                                     |

| CC               | Circulating current                                                   |

| CM               | Common-mode                                                           |

| CMC              | Common-mode current                                                   |

| CMV              | Common-mode voltage                                                   |

| CSC              | Current source converter                                              |

| CSI              | Current source inverter                                               |

| CSR              | Current source rectifier                                              |

| DC               | Direct current                                                        |

| DDPWM            | Direct duty-ratio PWM                                                 |

| ESP              | Electrical submersible pump                                           |

| EV               | Electric vehicle                                                      |

| FFT              | Fast Fourier Transform                                                |

| FOC              | Field oriented control                                                |

| FACT             | Flexible alternative current transmission system                      |

| GTO              | Gate turn-off thyristor                                               |

| HF               | High frequency                                                        |

| HVDC             | High voltage direct current                                           |

| IGBT             | Insulated-gate bipolar transistor                                     |

| IGCT             | Integrated gate-commutated thyristor                                  |

| IM               | Induction machine                                                     |

| LCC              | Line communicated converter                                           |

| LPF              | Low pass filter                                                       |

| MARS             | Model reference adaptive system                                       |

| MFT              | Medium-frequency transformer                                          |

| MSEHE            | Multiple selective EMF harmonic elimination                           |

| MV               | Medium voltage                                                        |

| PD<br>PMSM       | Phase disposition                                                     |

|                  | Permanent magnet synchronous machine                                  |

| POD<br>PWM       | Phase opposite disposition<br>Pulse-width modulation                  |

| r www<br>PV      | Photovoltaic                                                          |

| r v<br>RCMV      |                                                                       |

| SCR              | Reduced common-mode voltage<br>Silicon controlled rectifier           |

| SCK<br>SGCT      |                                                                       |

| SGCT             | Symmetric gate-commutated thyristor<br>Selective harmonic elimination |

| SHE<br>SMO       | Sliding-mode observer                                                 |

| SMO              | Stidling-mode observer<br>Second order generalized integrator         |

| SOGI             | Sinusoidal pulse-width modulation                                     |

| SF WW<br>SS-DPWM | Six-step direct PWM                                                   |

| <b>33-DL M M</b> |                                                                       |

| SVM  | Space vector modulation            |

|------|------------------------------------|

| THD  | Total harmonic distortion          |

| TPWM | Trapezoidal pulse-width modulation |

| VSC  | Voltage source converter           |

| WBG  | Wide bandgap                       |

| ZSR  | Zero state replacement             |

## List of Symbols

| $I_1, I_2, I_3, I_4, I_5, I_6$ | Six active vectors for single CSC                                  |

|--------------------------------|--------------------------------------------------------------------|

| $I_{7}, I_{8}, I_{9}$          | Three zero vectors for single CSC                                  |

| $I_S$                          | Small vector for 2-CSC parallel system                             |

| $I_M$                          | Medium vector for 2-CSC parallel system                            |

| $I_L$                          | Large vector for 2-CSC parallel system                             |

| i <sub>crN</sub>               | Circulating current                                                |

| $i_{cmN}$                      | Common-mode current                                                |

| $V_{cm}$                       | Common-mode voltage                                                |

| $V_{og}$                       | Common-mode voltage stress of the motor                            |

| V <sub>cm_rec</sub>            | Rectifier-side common-mode voltage                                 |

| $V_{cm\_inv}$                  | Inverter-side common-mode voltage                                  |

| V <sub>cm_3</sub>              | Third-order component of common-mode voltage                       |

| CMV <sub>ave</sub>             | Average value of common-mode voltage                               |

| $CMV_{act1}, CMV_{act2}$       | Common-mode voltage excited by the two active vectors              |

| $CMV_{total}$                  | Total common-mode voltage                                          |

| $CMV_{active}$                 | Common-mode voltage excited by active vectors                      |

| CMVzero                        | Common-mode voltage excited by zero vector                         |

| $m_a$                          | Modulation index                                                   |

| $F_r$                          | Resonance frequency                                                |

| L <sub>diff</sub>              | Differential inductance                                            |

| $L_{cm}$                       | Common-mode inductance                                             |

| $L_{cm\_eq}$                   | Equivalent common-mode inductance                                  |

| $C_{eq}$                       | Equivalent capacitance                                             |

| R                              | Damping resistance in the common-mode loop                         |

| $Z_I$                          | Total impedance of parallel CSC with independent common-mode choke |

| $Z_S$                          | Total impedance of parallel CSC with common-mode choke             |

| arphi                          | Displacement angle between voltage and current                     |

| $i_lpha$ , $i_eta$             | Inverter output currents in $\alpha$ - $\beta$ frame               |

| $V_{lphaeta}$ , $I_{lphaeta}$  | Voltage and current vector in $\alpha$ - $\beta$ frame             |

| $\boldsymbol{e}_{lphaeta}$        | EMF vector in $\alpha$ - $\beta$ frame                           |

|-----------------------------------|------------------------------------------------------------------|

| $i_g$ , $i_h$                     | Inverter output currents in g-h frame                            |

| $u_d, u_q$                        | Capacitor voltage in <i>d-q</i> frame                            |

| i <sub>wd</sub> , i <sub>wq</sub> | Inverter output currents in <i>d-q</i> frame                     |

| i <sub>sd</sub> , i <sub>sq</sub> | Stator currents in <i>d-q</i> frame                              |

| $\Delta V_p$                      | Voltage difference between the positive DC bus                   |

| $\Delta V_n$                      | Voltage difference between the negative DC bus                   |

| $\Delta i_p$                      | Current difference between the positive DC bus                   |

| $\Delta i_n$                      | Current difference between the negative DC bus                   |

| K <sub>s</sub>                    | Gain of sliding-mode observer                                    |

| $K_{pd}$ , $K_{pq}$               | Proportionality coefficient of current loop controller           |

| K <sub>id</sub> , K <sub>iq</sub> | Integral coefficient of current loop controller                  |

| $K_{pv}$                          | Proportionality coefficient of capacitor voltage loop controller |

# **Chapter 1**

### Introduction

There are mainly three types of current source converters (CSCs), such as current source DC-DC converter, current source rectifier (CSR) and current source inverter (CSI), which had been studied for decades. Compared to the voltage source converter (VSC) which holds a constant voltage on the DC-link, the CSC is fed by a constant DC current and the AC-side currents are pulse-width modulation (PWM) waveforms. A capacitor filter is required in CSC output side for the commutation of devices and a DC inductor is needed to support the constant DC current. Among which, line communicated converter (LCC) by adopting silicon controlled rectifier (SCR) thyristors whose commutation is assisted by the load with a leading power factor and PWM CSC by using integrated gate-commutated thyristor (IGCT) or gate turn-off thyristor (GTO) are commonly used for high power applications, such as high-voltage direct current (HVDC) systems and medium-voltage (MV) drives. Moreover, PWM CSR and CSI can also be adopted in low power application such as photovoltaic (PV) and electrical vehicle (EV) with the development of commercialized reverse-blocking devices. On the other hand, the current source DC-DC converters have been widely used for DC voltage boost circuit and multiple-stage voltage conversation, such as data center.

This chapter mainly focus on the PWM CSC by introducing the typical topologies, modulation strategies and control method for CSC-fed drives. The common applications are reviewed in the first section. To specific, the transformerless PWM CSC-fed drive and its parallel structure will be investigated to address the essential issues such as common-mode voltage (CMV) and common-mode (CM) resonance excited by CMV. Various types of modulation strategies such as space vector modulation (SVM), selective harmonic elimination (SHE), carrier-based PWM and their extension to parallel CSC system will be

discussed in the second section. At last, the motor control strategy and challenges for high power CSC based drives will be addressed in the last section.

### **1.1 Current Source Converters and Applications**

The CSC had been widely adopted in industry for decades and the trends changed with the development of CSC semiconductors. Typical application examples mainly involved in high power sites such as HVDC systems and high power MV drives. Nowadays, more and more PWM CSC-based high switching applications such as renewable energy conversation, data center power supply and wide bandgap (WBG) device-based boost converter for electrical vehicles (EVs) had been investigated due to the development of devices, control and modulation strategies. This section will briefly review the state-of-art CSC applications in industry and foresee the possible trends.

#### 1.1.1 High Voltage Direct Current System

Nowadays the offshore wind farms are planned far away from the onshore grid connection, which made HVDC transmission a feasible solution for distant wind power generation [1-5]. Traditionally, LCC based HVDC (LCC-HVDC) had dominated the HVDC market due to it high power rating, reliability and efficiency [1]. Apart from the conventional LCC-HVDC, two main topologies include VSC based HVDC (VSC-HVDC) and PWM CSC based HVDC (PWM CSC-HVDC) had been well investigated in literatures [2], [3]. CSC based HVDC systems achieve reverse power flow through alternating the DC voltage polarity while maintaining fixed-directional current, which enjoys high reliability and low

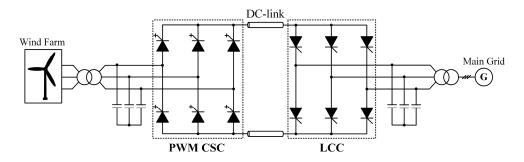

Fig. 1.1. Hybrid current source HVDC system for offshore wind power generation.

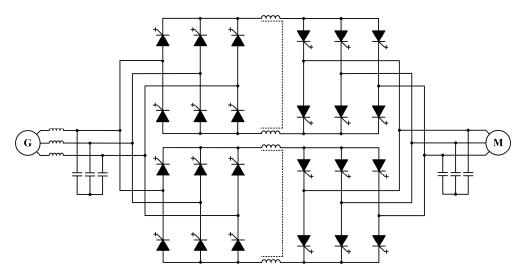

maintenance requirement compared with other VSC-based topologies. To utilize the features of PWM CSC such as reactive power control, operation without commutation voltage and relative small footprint with improved harmonic performance over the LCC schemes, a hybrid CSC-HVDC system was proposed in [4], which adopted a PWM CSC on the offshore wide turbine side to reduce the footprint and connected to onshore grid though DC cable and LCC as shown in Fig. 1.1. Such topology can combine the advantages of both PWM CSC and LCC techniques in offshore wind application. To further eliminate the costly and bulky offshore step-up transformer, some literature studied the series connected PWM CSC system to increase the power rating for high voltage application, where each CSC can be regard as a module. A cascaded GTO-based CSR system was introduced in [5], which can improve the quality of supply current though symmetrical phase angle control. A multi-phase wind turbine generator connected by a multi-winding transformer though cascaded PWM CSCs was introduced in [6]. Series connected PWM CSC employed on both offshore generator side and onshore grid side was introduced in [7], [8] as shown in Fig. 1.2. On the offshore generator side, the DC voltage in the range of 100 to 150kV can be easily be achieved by cascading appropriate numbers of MV wind generators through the

Fig. 1.2. Series connected PWM CSC for HVDC application.

PWM CSCs and consequently eliminate the costly and bulky step-up transformer. Moreover, multiple series-connected converters instead of single converter with series connected devices on the grid side can eliminate the challenge of voltage sharing on each series device. Above on this, a modular medium-frequency transformer (MFT) [9] and series/parallel connection [10] based configurations had been researched recently, which can further improve the system performance.

#### **1.1.2 High Power Medium Voltage Drives**

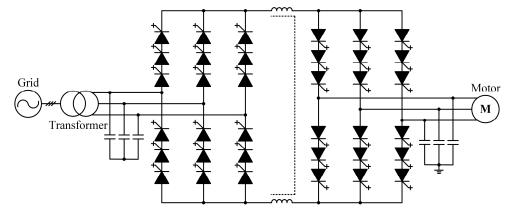

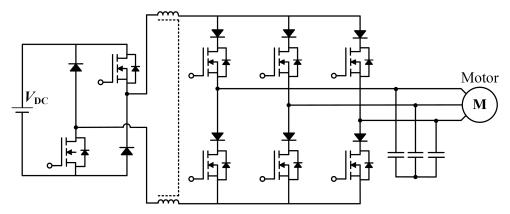

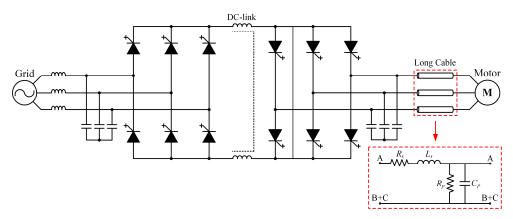

CSC-fed drive configurations had been widely adapted in industry for high power (>1MW) MV applications, such as pumps, fans, compressors, etc. [1]. Among which, load communicated inverter (LCI) topology is particularly suitable for very large synchronous motor drives with power rating up from tens of MW to 100 MW due to low manufacturing cost and high power rating of SCR devices [11]. On the other hand, PWM CSI-fed drive can easily filter out the low order harmonics which results in small torque ripples. The grid-side line quality and power factor can be improved through PWM CSR with power factor compensation (PFC) and PWM techniques. As a result, it is a preferred choice for most MV drives with the power rating from 1 to 10 MW [12]. The synchronous gate-commutated thyristor (SGCT) [13] can be connected in series manner to increase the power capacity. The typical configuration of back-to-back PWM CSC-fed MV drives for 6.6 kV application is shown as Fig. 1.3, which consists CSR, DC-link inductor, CSI and input/output filters.

Fig. 1.3. PWM CSC-fed MV drive with isolation transformer.

Fig. 1.4. PWM CSC-fed MV drive with dual-bridge rectifier.

To further reduce the line current distortion, a CSI-fed drive topology with dual-bridge PWM rectifier for 4160V application is shown as Fig. 1.4, the rectifier using SHE scheme can eliminate the 11<sup>th</sup> and 13<sup>th</sup> harmonics and the phase-shifting transformer can cancel the 5<sup>th</sup>, 7<sup>th</sup>, 17<sup>th</sup> and 19<sup>th</sup> harmonics. Other remaining high-order harmonics can be filtered by the input capacitor. Thus, this topology is suitable for applications that have a strict standard of line current distortion. Moreover, the DC-link voltage quality with dual-bridge rectifier can be potentially improved with enhanced modulation strategies.

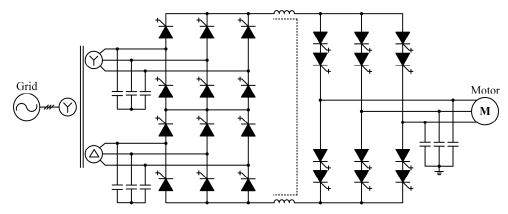

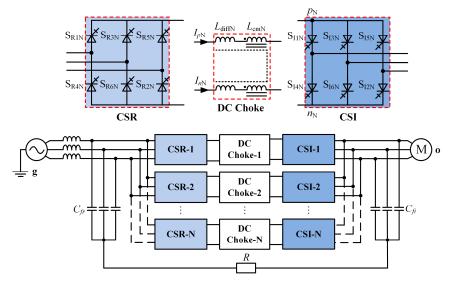

A transformerless CSC-fed drive configuration is shown as Fig. 1.5, where the isolation or phase-shifting transformer is replaced with a three-phase reactor. Therefore, the system power losses, cost and size caused by the bulky transformer can be effectively reduced. However, one of the major concerns in transformerless CSC-fed drive is the CMV, which is excited by the switching actions of the

Fig. 1.5. Transformerless PWM CSC-fed MV drive.

semiconductor devices. Such CMV can cause motor shaft voltage, bearing current, which would cause premature failure of the motor winding isolations if not mitigated [14], [15]. One solution is to use a custom-made drive with an increased insulation level, but it is not practical for those applications which the standard motors are already in use. Another way is to adopt a large common-mode (CM) choke either on AC or DC side, which can provide high impedance to withstand the CMV while enjoying higher efficiency and lower cost compared with the isolation transformer [1].

The integrated DC choke structure as shown in Fig. 1.5, which combines the differential and CM inductances with a single core, as a result, the size can be reduced. The neutral points of input and output filter are connected through a small damping resistor to create a CM loop and suppress the potential CM resonance due to the series connection of CM choke and the capacitor filters. However, the size and cost of the CM choke strongly depend on the magnitude of CMV and CMC, which are heavily dependent on the modulation strategies. As a result, it is always desirable to suppress the CMV, thus, several control and modulation strategies had been investigated in literates [42]-[46] to further address the CMV issues actively.

#### 1.1.3 Low Power High Switching Frequency Application

The typically applications of CSC are mainly involved in high power fields where the switching frequency is limited to hundreds of hertz to reduce the switching losses. Besides on these high power applications introduced earlier, CSC can also be adopted in low power applications with high switching frequency, such as grid-interfacing PV converter, EV application and data center power supplies with higher switching frequency.

Fig. 1.6 shows a typical single stage boost CSI-interfaced PV application, where the boost DC/DC converter can be eliminated compared with the two-stage DC/DC plus DC/AC voltage source inverter (VSI) based PV system. Therefore, higher efficiency and simpler control scheme can be achieved [16], [17]. Meanwhile, the CSC-based PV system enjoys better reliability due to the inherent

short circuit protection and elimination of unreliable DC capacitor in VSI. Typically, the maximum power point tracking (MPPT) technique is applied to regulate the DC current, power control can be achieved by adjusting the current references. Some novel topologies based on CSC, such as CH5 [18] and CH7 [19] had been proposed to supress the leakage current. Improved space vector modulation (SVM) was investigated in [20] to reduce the CMV and leakage current.

Fig. 1.6. Single stage three-phase boost CSI-interfaced PV application.

The voltage boost capacity of CSI was investigated in [21] for EV application as shown in Fig. 1.7. The DC/DC converter was used to regulate the DC-link current and the charge the battery during dynamic breaking to fulfil bidirectional power flow. The DC-link current can be controlled to a desired value according to the motor speed and load condition. The output voltage can be easily boosted to a high value with relatively small DC source, which can guarantee a high ratio of constant power speed range and therefore very suitable for EV applications.

Fig. 1.7. System diagram of CSI-fed drives for EV application.

Meanwhile, the near sinusoidal output voltage and current can reduce the dv/dt related electromagnetic noises, the copper and iron losses of the motor as well as the bearing current [22].

Other high frequency CSC applications such as data center power supply by utilizing the buck CSR feature [23]-[25]. Reverse blocking insulated-gate bipolar transistor (RB-IGBT) based CSI had been developed in [26], [27] with boost capacity. WBG devices such as all Silicon carbide (SiC) diode series connected with MOSFET [25], SiC JFET [28], GaN-HEMT-based reverse blocking switches adopted for CSC [29] had been studied for efficiency enhancement with much higher switching frequency operation. The newly developed dual-gate monolithic bidirectional GaN e-FET [30] had been well investigated in literatures, where the power density and efficiency could be significant increased and competitive with the VSC counterparts. Due to these breakthroughs of CSC semiconductors, the CSC will be involved more and more potential applications in the future.

#### **1.2 Parallel CSC-fed System and Modulation Strategies**

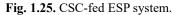

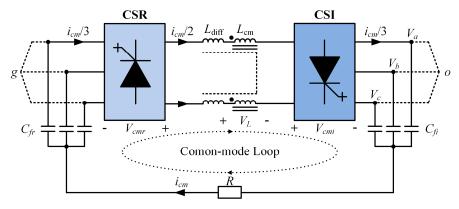

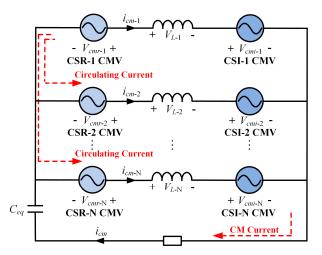

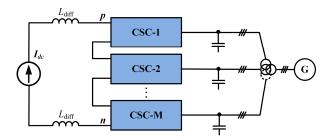

To increase the system power range and improve current quality with multilevel output, multilevel converters (MLCs) had been persistently researched for decades which can be classified into three categories: embedded, two stage, and parallel structures [31]-[33]. Among them, parallel operation is a practical and easy implement way and it enjoys the benefits of modularity, simple structure, improved fault tolerance and reliability, extended power range beyond semiconductor limits as well as better harmonic performance, which attracted increased attentions in recent years. There are mainly two types of parallel CSC configurations: independent DC-link [34]-[36] and shared DC-link [37]-[39]. For independent DC-link structure, the DC-link currents for each CSC module can be controlled independently, thus most of the modulation or control methods adopted in independent DC-link structure are mainly developed to improve the PWM sequence, AC output quality, suppress the CM resonance and reduce circulating current (CC) by reducing the CMV.

On the other hand, with shared DC-link parallel structure, the DC current balance is the main concern, as the sub DC-link currents may not be balanced mainly due to the following reasons:

- 1) tolerance in the DC-link inductances and winding resistances,

- 2) differences of on-state voltages of devices,

- 3) variations in time delay of the gating signals of the two inverters [39].

The unbalanced DC current can degrade the AC output quality, make the system unstable, and even destroy the devices due to over current [40]. Since only the total DC-link current can be controlled, most of the current balance schemes were investigated in literatures by choosing or adjusting proper dwell time of small and medium vectors. In this section, the two main parallel CSC structure and their main concerns for MV drive application was introduced firstly. Then several popular CSC modulation strategies developed for CSC system were introduced and compared. At last, the introduced PWMs were extended for parallel CSC application.

#### **1.2.1 Parallel CSC Topology**

Series or parallel connected devices to increase the voltage/current rating for much higher power application had widely adopted in industry, where the series of parallel connected devices can be simply treated as a single device but with increased power rating. Typically, these devices are driven with synchronous gating signals to achieve desired power sharing performance. Therefore, the system output features in terms of PWM sequence, average switching frequency and harmonic distortion almost stays the same but increased rating. On the contrary, series or parallel connection based on the converter perspective can also easily increase the system power rating. More importantly, the series/parallel converters can bring other advantages such as improved output quality, reliability as well as superior control strategy design. A dual bridge shown in Fig. 1.4 was a typical series CSC connection case which can potentially improve the line currents with proper modulation scheme development. On the other hand, parallel CSC connection was also popular in industry motor drive application.

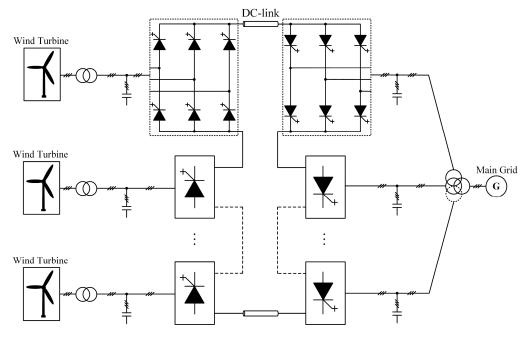

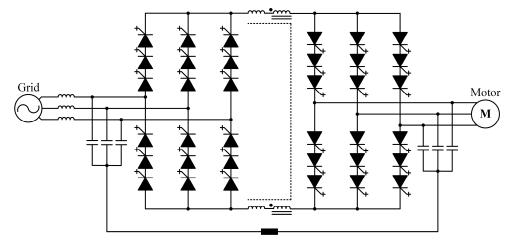

Fig. 1.8. Parallel CSC system with independent DC source.

Fig. 1.8 shows the two paralleled back-to-back PWM CSCs with shared input and output filters, where each CSC can be regarded as a standard module with independent DC-link. Each module has its own DC inductor to support their sub DC-link current, which can be controlled through the CSR independently. The number of the paralleled modules can be easily determined by the wanted system power rating. Since the DC current balance is not a big issue for each module, most of the modulation and control strategies were developed to achieve better output waveforms and smaller CMV.

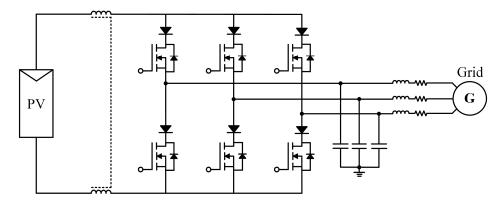

Besides the independent DC-link parallel structure, a shared DC-link parallel CSC was also investigated in literatures where paralleled PWM CSRs or

Fig. 1.9. Parallel CSC system with shared DC source.

CSIs shared the common DC-link. A typical shared DC-link case is shown as Fig. 1.9, the total DC-link current is provided by a dual bridge CSR and each sub DC-link current should be balanced through proper switching sequence design. Otherwise, the imbalanced currents could result in large CC, deteriorate the output currents and lead to overcurrent issue which would damage the semiconductor. Therefore, DC current balance strategy development was the priority task for this parallel structure.

To address the emerging challenges such as the motor-side CMV stress, CC and DC current balance along with the parallel structures, the parallel CSC modulation scheme development had raised increased attention in the recent years. A general review is conducted to introduce the existing CSC modulation methods and the features are simply compared.

#### **1.2.2 Modulation Strategies**

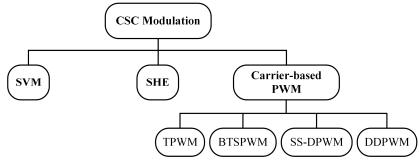

The performance of CSC is strictly dependent on the modulation strategies. There are three major CSC PWM methods had been developed as listed in Fig. 1.10. They are 1) SVM [41]-[46], 2) selective harmonic elimination (SHE) [47]-[52], and 3) carrier-based PWM, such as trapezoidal PWM (TPWM) [53], Bi-tri logical SPWM (BTSPWM) [54]-[58], six-step direct PWM (SS-DPWM) [59], direct duty-ratio PWM (DDPWM) [60], [61].

Both SVM and SHE are difficult to design for parallel CSC system with multilevel output mainly due to the large number of redundant switching states. For example, 729 switching states are available for 3-CSC parallel system with SVM, the switching patterns are numerous for multilevel SHE [62]. Therefore,

Fig. 1.10. Modulation strategies of CSC.

both methods are hard to be generalized for N-CSC (N≥3) parallel system and most of the relevant research was focused on 2-CSC parallel system. On the other hand, the TPWM adopts trapezoidal references and triangular carriers had been applied in 3-level and 5-level CSC system. However, the small DC current utilization range and poor harmonic performance by adopting trapezoidal references limited its application. The BTSPWM was derived from well developed VSC PWM through logic translation [54], [55]. The line-to-line output voltage of VSC is dual to line current of CSC, which causes three-phase line currents lead to their references by 30° and the linear DC current utilization range is 0-0.866. The switching frequency with continuous sinusoidal voltage reference is same as the carrier frequency. By adopting specific discontinuous voltage references, the switching frequency can be reduced to 2/3 of carrier frequency and the DC current utilization range can be increase to 0-1[57], [58]. However, it generates a switching state where all switches are turned off and this state needs to be replaced by zero states, which increase the complexity, especially for N-CSC parallel system. The SS-DPWM was proposed in [59], which can directly generate CSC gating signals by proper selecting voltage references and carriers. The DDPWM was more straightforward by adopting current references directly [60].

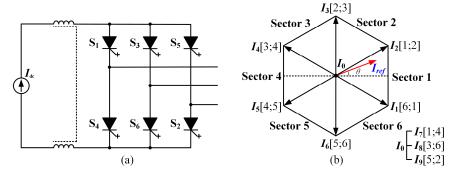

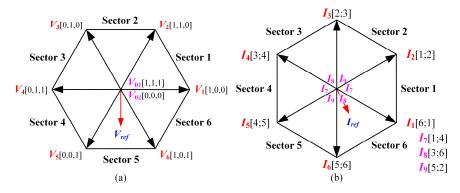

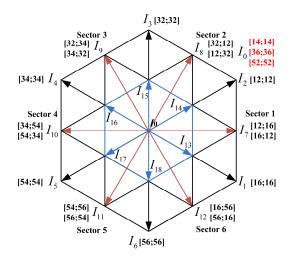

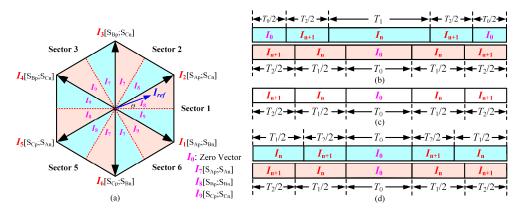

#### A. Space Vector Modulation

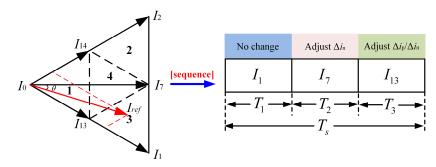

Based on the conduction constraint introduced before, only two switches in the converter conduct at any time instant, one in the top half of the CSC bridge and the other in the bottom half. Under this constraint, the three-phase inverter has a total of nine switching states. These switching states can be classified as six active switching states ( $I_1$ - $I_6$ ) and three zero switching states ( $I_7$ - $I_9$ ) as shown in Fig. 1.11. The space vector diagram can be divided into 6 vectors and the linear modulation range is 0-1. The switching state can be represented by two digital number to indicate the turn on switches. For example, the zero state [1,4] represents that switches S<sub>1</sub> and S<sub>4</sub> in inverter phase leg A conduct simultaneously and the other four switches are off, which means the DC current is bypassed. The current reference  $I_{ref}$  can be synthesized by two adjacent active vectors and one zero vector, the dwell time of each vector is calculated as

$$\begin{cases} T_1 = m_a \sin(\pi/6 - \theta) T_s \\ T_2 = m_a \sin(\pi/6 + \theta) T_s; -\frac{\pi}{6} < \theta \le \frac{\pi}{6} \\ T_0 = T_s - T_1 - T_2 \end{cases}$$

(1.1)

where  $T_1$  and  $T_2$  are the total dwell time of the two adjacent active vectors, while  $T_0$  is the dwell time of zero vector.  $T_s$  is the carrier period and  $\theta$  indicates the current reference position in each sector.

Fig. 1.11. Space vector modulation of CSC, (a) CSC diagram, (b) space vector diagram.

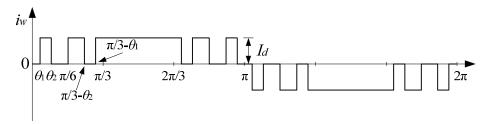

#### B. Selective Harmonic Elimination

SHE is an off-line modulation scheme, which can eliminate specific number of low-order unwanted harmonics in the output current. Normally, the pause angles are pre-calculated and imported into the digital controller. Fig. 1.12 shows a typical SHE waveform, there are five pulses per half-cycle with five switching angles in the first quarter period, where only two out of the five angles are independent as the PWM is half-wave symmetric and the 5th and 7th harmonics can be eliminated. Multilevel SHE was proposed in [63] for parallel CSC applications, where the pause angle freedoms will be increased and more orders of

Fig. 1.12. Selective harmonic elimination modulation.

unwanted harmonics can be eliminated to get better output current. However, the pause angle calculation is much more complex due to large numbers of freedoms.

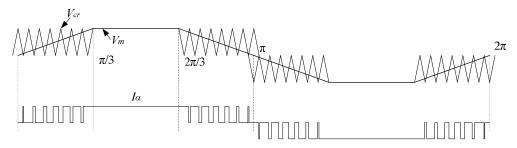

#### B. Trapezoidal pulse-width modulation

The principle of TPWM is shown as Fig. 1.13, where  $v_m$  is a trapezoidal modulating wave and  $v_{cr}$  is a triangular carrier wave, the amplitude index is defined by  $V_m/V_{cr}$ , where  $V_m$  and  $V_{cr}$  are the peak values of modulating and carrier waves, respectively. Similar as the carrier-based PWM scheme for VSC, the gate signal is generated by comparing the carriers and modulation waveform. However, the trapezoidal modulation does not generate gating in the center  $\pi/3$  interval of the positive half-cycle or in the negative half-cycle of the inverter fundamental frequency, which causes limited DC current utilization range. Moreover, the adoption of trapezoidal carrier will result in poor harmonic performance. A phase shifted TPWM was introduced in [53] to obtain better harmonic performance for multilevel CSC while keeping low device switching frequency, where the shifting angle was mainly determined by the switching frequency and harmonic distortion.

Fig. 1.13. Trapezoidal pulse-width modulation.

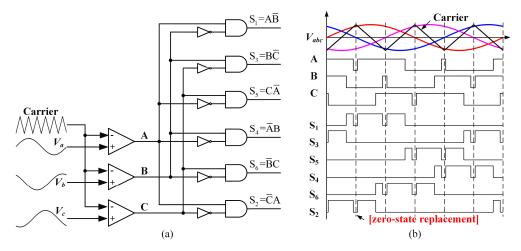

#### C. Bi-tri logic SPWM

The BTSPWM was first introduced in [54]. The Bi-tri logic method is based on the duality between three-phase VSC and CSC, where VSC line-to-line voltage is dual to CSC phase current. The main idea is translating Bi-logic switching signals of VSC to tri-logic signals applied in CSC through Bi-tri logic translation as shown in Table 1.1. The digital implement of Bi-tri logic translation had been thoroughly analyzed in [55], the relations of VSC three phase Bi-logic signals  $X_A$ ,  $X_B$ ,  $X_C$  and CSC tri-logic signals  $Y_A$ ,  $Y_B$  and  $Y_C$  can be expressed as

$$\begin{cases} Y_{A} = A\overline{B} - \overline{A}B = A - B = 1/2(X_{A} - X_{B}) \\ Y_{B} = B\overline{C} - \overline{B}C = B - C = 1/2(X_{B} - X_{C}) \\ Y_{C} = C\overline{A} - \overline{C}A = C - A = 1/2(X_{C} - X_{A}) \end{cases}$$

(1.1)

where A, B, C are generated by comparing the triangular carrier with three phase voltage references ( $V_a^*$ ,  $V_b^*$  and  $V_c^*$ ), which can directly drive the upper switches of VSC.

| Table 1.1. DI-uti togic translation |                   |    |    |                    |    |    |                |  |  |  |

|-------------------------------------|-------------------|----|----|--------------------|----|----|----------------|--|--|--|

| Voltage<br>Vector                   | Bi-Logic<br>(VSC) |    |    | Tri-Logic<br>(CSC) |    |    | Current        |  |  |  |

|                                     | XA                | Хв | Хс | YA                 | YB | Yc | Vector         |  |  |  |

| V01                                 | +1                | +1 | +1 | 0                  | 0  | 0  | I7, I8, I9     |  |  |  |

| $V_{02}$                            | -1                | -1 | -1 | 0                  | 0  | 0  | I7, I8, I9     |  |  |  |

| $V_1$                               | +1                | -1 | -1 | +1                 | 0  | -1 | $I_2$          |  |  |  |

| $V_2$                               | +1                | +1 | -1 | 0                  | +1 | -1 | I <sub>3</sub> |  |  |  |

| $V_3$                               | -1                | +1 | -1 | -1                 | +1 | 0  | <b>I</b> 4     |  |  |  |

| $V_4$                               | -1                | +1 | +1 | -1                 | 0  | +1 | <b>I</b> 5     |  |  |  |

| $V_5$                               | -1                | -1 | +1 | 0                  | -1 | +1 | <b>I</b> 6     |  |  |  |

| $V_6$                               | +1                | -1 | +1 | +1                 | -1 | 0  | $I_1$          |  |  |  |

Table 1.1. Bi-tri logic translation

Based on the bi-tri logic translation, the gating signal of each CSC device can be expressed as

$$\begin{cases} S_1 = A\overline{B}; S_3 = B\overline{C}; S_5 = C\overline{A} \\ S_4 = \overline{A}B; S_6 = \overline{B}C; S_2 = \overline{C}A \end{cases}$$

(1.2)

where  $S_{Ap}$ ,  $S_{Bp}$ ,  $S_{Cp}$  and  $S_{An}$ ,  $S_{Bn}$ ,  $S_{Cn}$  are the gating signals of upper and lower switches of CSC, respectively. However, it produces invalid states translated states from the zero states of VSC ( $V_{01}$ ,  $V_{02}$ ) which all switches are turned off.

Fig. 1.14. Space vector diagram, (a) VSC, (b) CSC.

The space vector diagrams of VSC and CSC are shown as Fig. 1.14 (a) and (b), respectively. Through bi-tri logic translation, the six active vectors ( $V_1$  to  $V_6$ ) can be transferred to corresponding active vectors ( $I_1$  to  $I_6$ ). The invalid states are replaced with zero vectors ( $I_7$ ,  $I_8$ ,  $I_9$ ) by turning on the two switches in one leg.

Fig. 15 (a) shows the digital implement of bi-tri logic translation. However, the gating signals generated by bi-tri logic translation cannot be adopted in CSC directly since they generate states that cause all switches to be turned off as shown in Fig. 15(b). This all off state can not guarantee the continuity of inductor current, which should be replaced with zero states by turning on two switches in one leg [55]. The replaced zero state is normally selected by minimizing the switching frequency. Interleaved BTSPWM can be adopted in parallel CSC system to achieve multilevel output by interleaving the carrier for each module. However, the zero state replacement (ZSR) method would be more complex due to the increased redundant switching states.

Fig. 1.15. Bi-tri logic SPWM, (a) bi-tri logic translation, (b) gating signals.

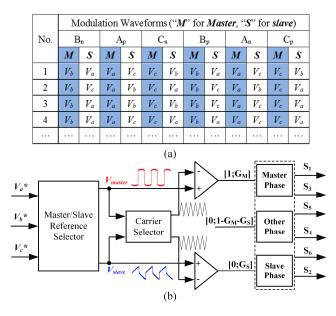

#### D. Six-step Direct Pulse-width Modulation

The SS-DPWM is an improved method derived from VSC which only use two of the three-phase voltage references which called *master* and *slave* references. The fundamental cycle is divided into six 60° intervals, only two references are compared with the carriers in each interval. The master reference has the maximum absolute value, and the slave reference can be selected from either of the other two references, which cause 64 possible cases for single CSC and Fig. 1.16 (a) lists part of them. The carriers are symmetrical triangular waveforms. When the master reference is positive, the upper switch in its phase will be turned on, while the lower switch in its phase will be turned on for a negative master reference. The compared carrier also needs to be selected based on the sign.

To explain the operation principle, interval  $C_n$  is taken as an example.  $S_{Cn}$  is always turned on, while  $S_{An}$  and  $S_{Bn}$  are always turned off due to the negative master reference in this interval. A turn-on signal is given to  $S_{Cp}$  when  $V_c^*$  is higher than down carrier. At the same time,  $V_b^*$  can be selected as the slave reference to determine other two up switches  $S_{Ap}$  and  $S_{Bp}$ . A turn-on signal is given to  $S_{Bp}$  in case  $V_b^*$  is higher than up carrier. The gating signal of anther up switch  $S_{Ap}$  can be generated based on complementary rule. The digital implement process of SS-DPWM is summarized as Fig. 1.16 (b).

Fig. 1.16. SS-DPWM principle, (a) modulation waveforms, (b) digital implement.

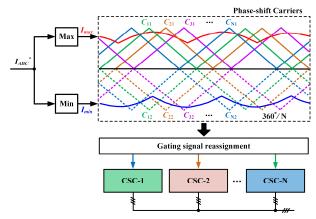

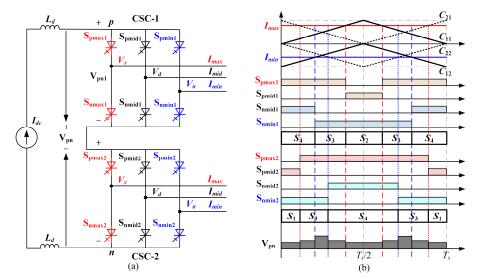

#### E. Direct Duty-ratio Pulse-width Modulation

The DDPWM was first introduced in [60], which can directly produce the gating signals of CSC without any logic translation. Besides dual relationship, the isomorphic relationship between VSC and CSC presented in [64], which can

sufficiently reveal the essential principle of DDPWM. It is verified the 3-phase CSC and single phase 3-level VSC are isomorphic pairs and they shared the same modulation features.

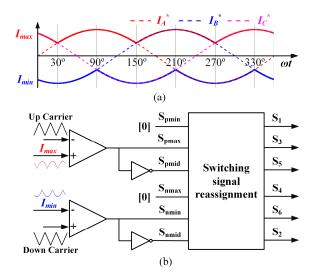

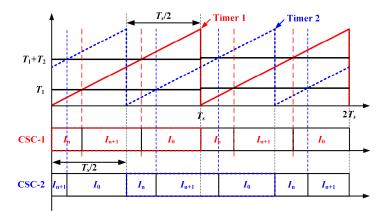

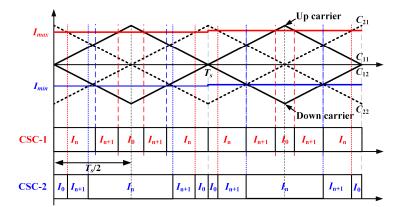

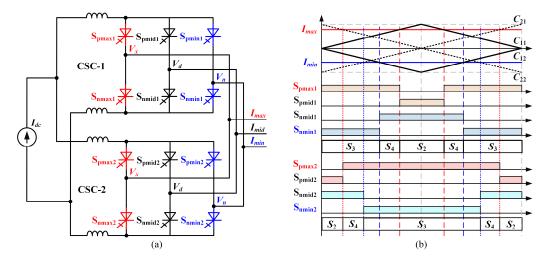

To achieve DDPWM, the six switches are identified as  $S_{pmax}/S_{nmax}$ ,  $S_{pmid}/S_{nmid}$ , and  $S_{pmin}/S_{nmin}$  according to the magnitude of three phase references  $(I_A^*, I_B^*, and I_C^*)$ . The output phases are renamed as Max-Mid-Min phase instead of A-B-C phase. The maximum, medium and minimum values  $(I_{max}, I_{mid}, and I_{min})$  among the three phase references can be obtained as  $I_{max}$ =max  $(I_A^*, I_B^*, I_C^*)$ ,  $I_{mid}$ =medium  $(I_A^*, I_B^*, I_C^*)$  and  $I_{min}$ =min  $(I_A^*, I_B^*, I_C^*)$  by comparing their magnitudes. In Max-Mid-Min phase,  $I_{max}$ ,  $I_{mid}$ , and  $I_{min}$  are synthesized by  $S_{pmax}/S_{nmax}$ ,  $S_{pmid}/S_{nmid}$ , and  $S_{pmin}/S_{nmin}$ , respectively. The waveforms of  $I_{max}$  and  $I_{min}$  with balanced three phase references are shown in Fig. 1.17 (a). As can be seen,  $I_{max}$  is always bigger than 0, and  $I_{min}$  can be synthesized by using  $-I_{dc}$  and 0. That means the lower leg of Max phase  $S_{nmax}$  and upper leg of Min phase  $S_{pmin}$  are never turned on ( $S_{nmax} = S_{pmin} = 0$ ). As one and only one switch among the three upper and lower switches should be on, which can be restricted by  $S_{pmax} + S_{pmid} + S_{pmin} = 1$  and  $S_{nmax} + S_{nmin} + S_{nmin} = 1$ . The switch logical relations are expressed as

$$S_{pmax} = \begin{cases} 1, \text{ if } I_{max} \ge C_1 \\ 0, \text{ if } I_{max} < C_1 \end{cases}; S_{n\min} = \begin{cases} 1, \text{ if } I_{min} < C_2 \\ 0, \text{ if } I_{min} \ge C_2 \end{cases}$$

(1.3)

Fig. 1.17. DDPWM principle, (a) I<sub>max</sub> and I<sub>min</sub> waveforms, (b) digital implement.

where  $C_1$  is the upper carrier and  $C_2$  is the lower carrier. Once the gating signals of S<sub>pmax</sub>, S<sub>pmid</sub>, S<sub>pmin</sub>, S<sub>nmax</sub>, S<sub>nmid</sub> and S<sub>nmin</sub> are obtained based on equation (1.3), they can be reassigned to A-B-C phase according to the magnitudes of three phase current references as shown in Fig. 1.17 (b). For example, when  $I_{max}=I_C^*$ ,  $I_{mid}=I_A^*$ , and  $I_{min}=I_B^*$ , thus the switching signals can be reassigned as S<sub>Cp</sub>=S<sub>pmax</sub>/S<sub>Cn</sub>=S<sub>nmax</sub>; S<sub>Ap</sub>=S<sub>pmid</sub>/S<sub>An</sub>=S<sub>nmid</sub> and S<sub>Bp</sub>=S<sub>pmin</sub>/S<sub>Bn</sub>=S<sub>nmin</sub>.

#### **1.2.3 Comparison of CSC Modulation**

The PWM output features such as total harmonic distortion (THD), harmonic spectrum and switching frequency are highly depend on the sequence design. To compare the different modulation introduced above, the PWM sequences are first compared. Since the harmonic performances of SHE and TPWM had been well addressed in literature. The detail comparisons between SVM, BTSPWM, SS-DPWM, and DDPWM will be conducted.

Table 1.2 shows the PWM sequences of these modulations in half fundamental cycle. The PWM sequence of SVM is very flexible and different segment form can be easily achieved. Normally, the 3-segment SVM is adopted for high power CSC application in order to reduce switching losses with only 3 switching actions in each sampling period. Both SHE and TPWM just utilize active vectors and the zero vectors are not used, which result in relatively low switching frequency and the actual switch time is related to the operation frequency. Among the three carrier-based SPWM, the conventional BTSPWM has 6 switching actions in each sampling period and the switching frequency is

| Interval    | SVM   | SHE/<br>TPWM | BTSPWM        | SS-DPWM   | DDPWM     |  |  |  |  |  |

|-------------|-------|--------------|---------------|-----------|-----------|--|--|--|--|--|

| [0°-30°]    | 6-1-8 | 6-1          | 8-1-6-8-6-1-8 | 1-6-8-6-1 | 6-1-7-1-6 |  |  |  |  |  |

| [30°-60°]   | 6-1-8 | 6-1          | 7-2-1-7-1-2-7 | 1-6-8-6-1 | 1-6-9-6-1 |  |  |  |  |  |

| [60°-90°]   | 1-2-7 | 1-2          | 7-2-1-7-1-2-7 | 2-1-7-1-2 | 1-2-9-2-1 |  |  |  |  |  |

| [90°-120°]  | 1-2-7 | 1-2          | 9-3-2-9-2-3-9 | 2-1-7-1-2 | 2-1-8-1-2 |  |  |  |  |  |

| [120°-150°] | 2-3-9 | 2-3          | 9-3-2-9-2-3-9 | 3-2-9-2-3 | 2-3-8-3-2 |  |  |  |  |  |

| [150°-180°] | 2-3-9 | 2-3          | 8-4-3-8-3-4-8 | 3-2-9-2-3 | 3-2-7-2-3 |  |  |  |  |  |

Table 1.2. Switching sequence with different modulations

Note: 1-6 Active states; 7-9 zero states

same as carrier frequency. Meanwhile, the PWM sequence is leading 30° compared with other modulation and the DC utilization range is limited. To solve this problem, third-order harmonic injection can be applied. Both SS-DPWM and DDPWM are 5-segment PWM and the switching frequency is 2/3 carrier frequency. All three SPWMs adopt two adjacent active vectors and one zero vector to synthesize the current references. However, the active vector order and zero state selection are different. The DDPWM divide each sector into two sub-sectors equally due to different active vector order.

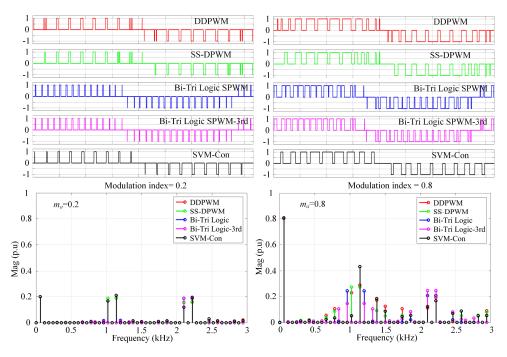

The output PWM waveforms and their harmonic distribution of different modulations are shown as Fig. 1.18. The output frequency is 60Hz, the carrier frequency is 1080Hz. The switching frequency difference is easily to determine, the conventional 3-segment SVM enjoys the smallest while the switching frequency of BTSPWM is the highest.

Fig. 1.18. PWM waveforms and harmonic distribution with different modulations.

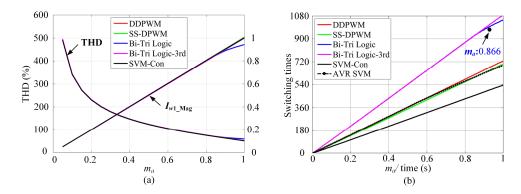

The THD and switching time performance under different modulation index are shown as Fig. 1.19. As can be seen, the conventional BTSPWM has limited DC utilization range (0-0.866), and the third-order harmonic injection method can increase solve this drawback and increase the DC utilization range to 0-1. The

Fig. 1.19. THD and switching time comparison with different CSC modulations.

overall THD performances of these modulation strategies are similar although their harmonic spectrums are different. The switching frequency of conventional 3-segment SVM is half of carrier frequency while the switching frequencies of both conventional BTSPWM and BTSPWM with third-order harmonic injection (continuous BTSPWM) are same as the carrier frequency. While, the switching frequency SS-DPWM and DDPWM is 2/3 of carrier frequency.

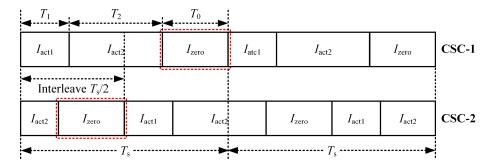

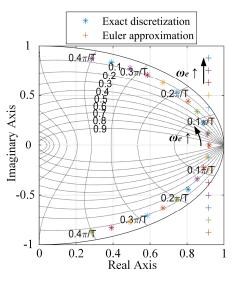

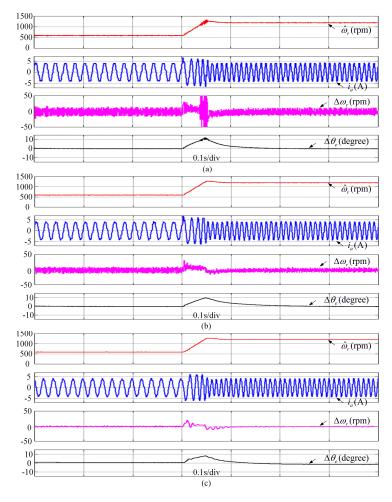

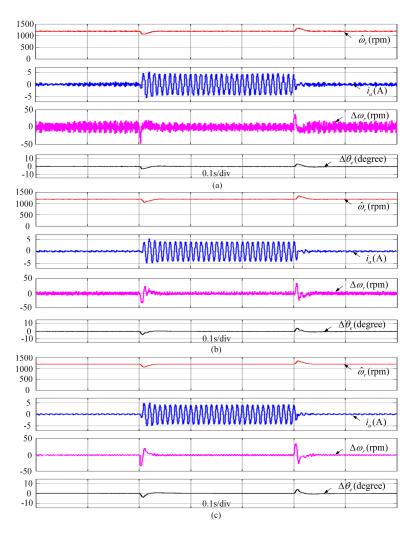

#### **1.2.4 Modulation Strategies for Parallel CSC System**