### Review and Simulation of Voltage Source Converters for HVDC Grid Development

by

Hadi Alyami

A thesis submitted in partial fulfillment of the requirements for the degree of

Master of Science

in

**Energy Systems**

Department of Electrical and Computer Engineering

University of Alberta

© Hadi Alyami, 2017

## Abstract

For over a century, the electric energy generation, transmission, distribution and utilization patterns have been essentially based on Alternating Current (AC), throughout time the AC technologies have been pushed into their thermal and/or technical limitations. The Direct Current (DC) technologies have as a result and mean of support been recurred. This reappearance of the DC technologies has resulted in a volume of knowledge that is counterpart in some cases and complementary in others. Therefore, this thesis concerns with reviewing the latest knowledge of High-voltage DC (HVDC) technologies, and thereafter draws a critical comparison by putting a variety of the related promising and common exercises into PSCAD/EMTDC<sup>®</sup> simulations.

With a particular focus on the Voltage Source Converters (VSCs) in HVDC application, the review is shaped to induce a critical reference that groups and classifies the growing scope, thereby providing an insightful evaluation of where the VSC-HVDC technology stands and is heading. Subsequently, the review is augmented by arguing the staged-development practice for the realization of MTDC grid. A number of HVDC project developers are supposedly ascertained that the possibility of erecting an MTDC grid shall occur in stages by interlinking the existing point-to-point HVDC systems. However, the transition requirements can differ greatly in one sense, and function in synchronism in another. Thus, a vital staging analysis of HVDC with Modular Multilevel Converters (MMC) is applied to show how the classical point-to-point structure (stage-1) can be a stepping-stone towards a radial structure (stage-2), after which a DC grid can be established (stage-3).

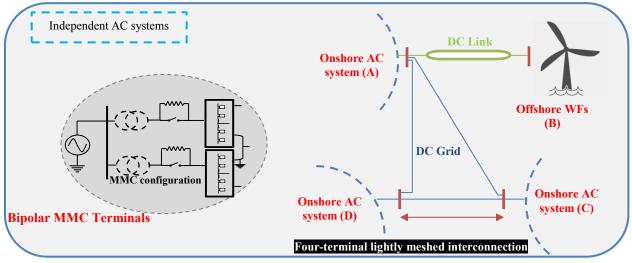

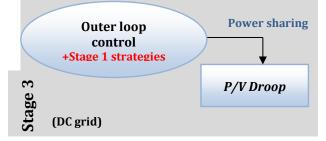

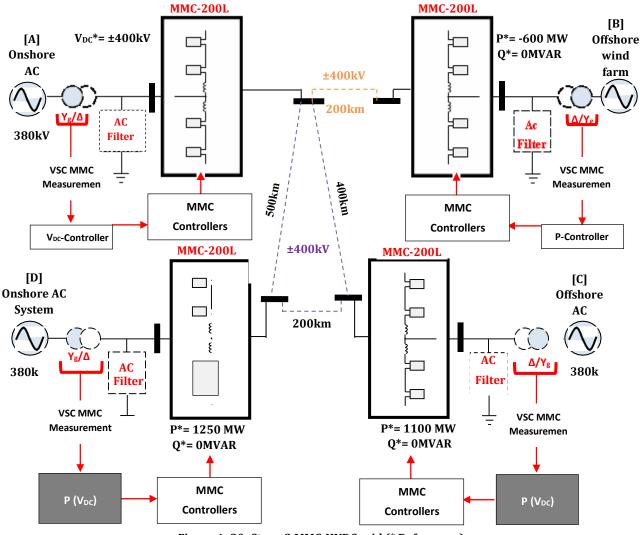

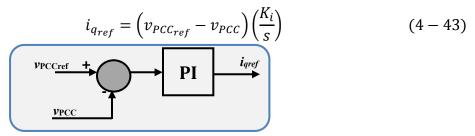

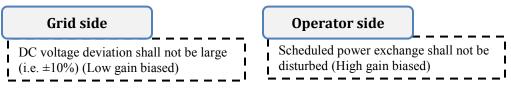

The key focus upon each stage transition is the individual and cooperative performance of the interlinked MMC terminals. In stage-1 and stage-2, the performance of the interconnected MMC terminals is implemented with the master-slave based strategies. Stage-3 comprises one offshore windfarm and three ring-linked onshore AC systems, forming an MTDC grid. In many DC voltage coordination studies addressing MTDC grids, droop methodology is seemingly the primary option to redistribute the power unbalance, thereby precluding the onshore MMCs from hunting each other. Although droop method is effective; especially in damping the dynamics, it is not optimum for controlling  $V_{DC}$ . Incorporating one MMC terminals take over  $V_{DC}$  regulation ensures a better  $V_{DC}$  coordination. Thus, in stage-3, the master-slave concept is adopted in normal operation conditions and combined with droop control that is only active in disturbed operation conditions, where the transition boundaries dictate by the dead-band P/V<sub>DC</sub> characteristics.

# Acknowledgment

First and foremost, I would like to express my infinite gratitude to my supervisor, Professor Yasser Abdel-Rady I. Mohamed, for his support, guidance, and understanding throughout the duration of my studies at the University of Alberta. Without Professor Mohamed's positivity and encouragement, I would never have come this far, and to him I am indebted. He has permitted me to draw freely on my research studies.

I was very fortunate to have been educated by leading professors in the area of Energy Systems at the University of Alberta and as of this I can confidently peruse any career whose callings are based on a strong possession of knowledge in power systems. This includes my thesis committee Professor Yunwei (Ryan) Li and Professor Amit Kumar to whom I am truly grateful.

I would like also to thank all Professor Mohamed's research group members in the Department of ECE (Energy Systems) for the friendly and productive atmosphere.

My studies are financed by King Abdullah Scholarship program, and this is deeply acknowledged.

Finally yet importantly, I would like to show my sincere thankfulness to my mother and family members, who despite the distance, have always been there for me.

Dedicated to my deceased father who shaped my life...

# Contents

| Ackno | wledgmentiii                                                     |

|-------|------------------------------------------------------------------|

| Intro | oduction1                                                        |

| 1.1   | Background1                                                      |

| 1.2   | Motivation                                                       |

| 1.3   | Aims and Objectives                                              |

| 1.4   | Research Definition                                              |

| 1.5   | Outline                                                          |

|       |                                                                  |

| HVD   | C Development Survey                                             |

| 2.1   | Preliminary Time-Frame                                           |

| 2.2   | The Conventional Power Grid and HVDC Solution                    |

| 2.2.  | AC Network Staging and HVDC Potential                            |

| 2.2.2 | AC Networks Challenges and Flexibility Concept Applied to HVDC10 |

| 2.2.  | 3 HVDC: Towards more Flexible Power Grid11                       |

| 2.3   | HVDC Transmission11                                              |

| 2.3.  | 1 Current Source (CS) and Voltage Source (VS)11                  |

| 2.3.2 | 2 LCC-HVDC and VSC-HVDC12                                        |

| 2.4   | VSC-HVDC Networks                                                |

| 2.4.  | 1 Definition for HVDC Schemes14                                  |

| 2.    | 4.1.1 Short Circuit Behaviour in HVDC System vs. HVDC Grid       |

|     |     | -                                                      |    |

|-----|-----|--------------------------------------------------------|----|

| 2.4 | .2  | VSC-HVDC Architecture and Main Component               | 16 |

| 2.4 | .3  | VS Cell Structure and VSC Topologies for HVDC Networks | 18 |

| 2.4 | .4  | MMC Conversion and SM Implementation                   | 21 |

| 2.5 | HVD | OC Design Criteria                                     | 24 |

| rol and Modelling Survey <sup>1</sup>           | 25                                                                                                                        |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| General VSC-HVDC Modelling and Simulation Tools |                                                                                                                           |

| General VSC-HVDC Power Transfer Mechanism       | 28                                                                                                                        |

| General VSC-HVDC Control Principles             | 29                                                                                                                        |

| 1 VSC-HVDC Control Structure and Design         | 31                                                                                                                        |

| Frequency Controlled VSC-HVDC Philosophy        | 39                                                                                                                        |

|                                                 | General VSC-HVDC Power Transfer Mechanism<br>General VSC-HVDC Control Principles<br>VSC-HVDC Control Structure and Design |

| 3.4.1 Synchronization Rationale                           |         |

|-----------------------------------------------------------|---------|

| 3.4.1.1 Phase-Locked Loop (PLL)                           | 41      |

| 3.4.1.2 Power Synchronization (PS) Loop                   |         |

| 3.4.2 Islanding Concept                                   | 43      |

|                                                           |         |

| <b>Design of MMC-HVDC Schemes "Staged-Development</b>     | <b></b> |

| 4.1 MMC Modelling                                         |         |

| 4.1.1 MMC Mathematical Representation                     |         |

| 4.1.1.1 Switching Function                                | 51      |

| 4.1.2 Detailed Equivalent Model                           |         |

| 4.2 Frame Transformation                                  | 53      |

| 4.3 Control Assembly                                      | 54      |

| 4-3-1 Vector Current Control (Upper-Level Control)        |         |

| 4.3.1.1 Inner Loop Control                                |         |

| 4.3.1.2 Outer Loop Control                                |         |

| 4.3.2 MMC Terminal Control (Lower-Level Control)          | 70      |

| 4.3.2.1 PSCAD VSC_Lib                                     | 70      |

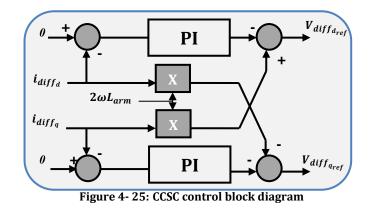

| 4.3.2.2 Circulating Current Suppressing Controller (CCSC) | 71      |

| 4.3.2.3 Nearest Level Control (NLC)                       | 72      |

| 4.3.2.4 Capacitor balancing controller (CBC)              | 73      |

| 4.4 MMC Terminal Fault Behaviour and DC-Link Cable        | 73      |

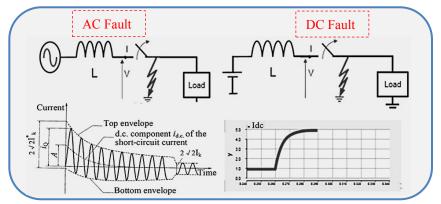

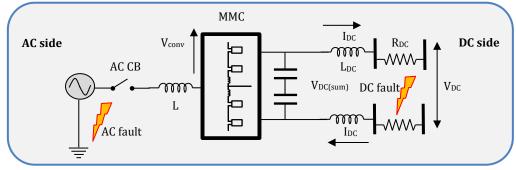

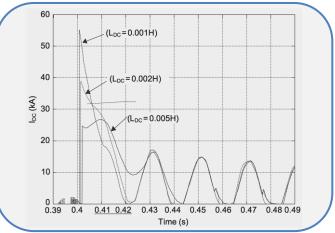

| 4.4.1 DC Fault                                            | 75      |

| 4.4.2 AC Fault                                            | 76      |

| 4.4.3 DC-link Cables                                      | 76      |

| 4.4.4 Overhead DC Lines                                   | 77      |

| Simulation Analysis and Comparison                        |         |

| 5.1 Standards and Definitions                             |         |

| 5.1.1 MMC Terminals and Link Specifications               |         |

| 5.1.2 Simulation Scenarios                                |         |

| 5.2 Two-terminal Point-to-point System                    |         |

| 5.3 Three-terminal Radial MMC-HVDC System                 |         |

| 5.4 Four-terminal DC Grid                                 |         |

| 5.5 Comparative Discussion                                |         |

| 5.5.1     | Structural and Operational Assessment            |  |

|-----------|--------------------------------------------------|--|

| 5.5.2     | MMC Possibilities in Upper-level Control Targets |  |

| 5.5.3     | Reliability upon Disturbed Operations            |  |

| 5.5.4     | Security and Standardization                     |  |

|           |                                                  |  |

| Conclusio | n and Future Prognosis                           |  |

|           | usion                                            |  |

|           | e Trends                                         |  |

|           | iC-based VSC-HVDC                                |  |

| 6.2.2 P   | rotection Schemes Development                    |  |

| 6.3 Furth | er work                                          |  |

|           | 2                                                |  |

|           | es                                               |  |

|           | A: VSC Capability                                |  |

|           | B: MMC Model based on NFSS                       |  |

| Appendix  | C: Technical Parameters                          |  |

# List of Figures

| Figure 1- 1: Transmission distance vs. cost for AC and DC power transmission (Left), distance to power effinition and compared to DC systems (Right) |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1- 2: Single line diagram of stage-1                                                                                                          |    |

| Figure 1- 2: Single line diagram of stage-2                                                                                                          |    |

| Figure 1- 4: Single line diagram of stage-3                                                                                                          |    |

| rigure 1- 4. Single line diagram of stage-5                                                                                                          | 0  |

| Figure 2-1: The historical milestones in the progress of HVDC transmission technology                                                                | 9  |

| Figure 2- 2: Different HVDC utilisations within power systems                                                                                        |    |

| Figure 2-3 : Main advantages of HVDC technologies                                                                                                    |    |

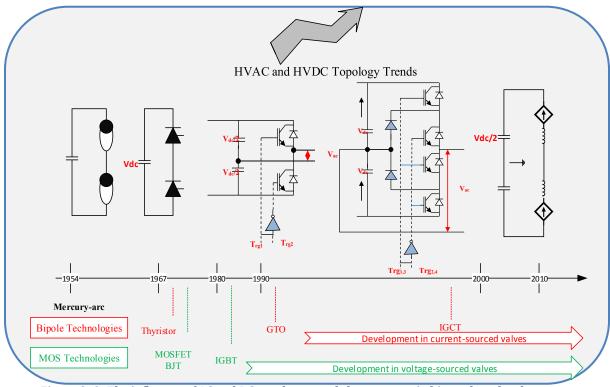

| Figure 2-4: HVAC and HVDC topology trends reflected to power switching valves development                                                            |    |

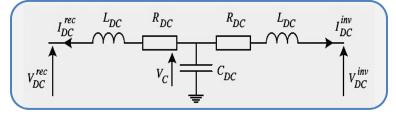

| Figure 2- 5: LCC-HVDC T-model                                                                                                                        |    |

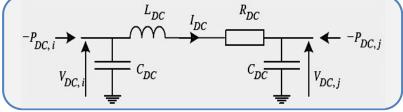

| Figure 2- 6: VSC-HVDC $\pi$ -model (Power injection)                                                                                                 |    |

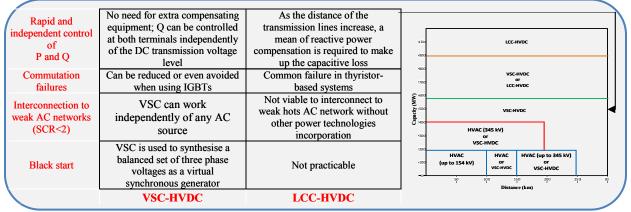

| Figure 2-7 : VSC-HVDC advantages over LCC-HVDC                                                                                                       |    |

| Figure 2-8: future visualisation of the European Supergrid showing various HVDC constructions                                                        |    |

| Figure 2- 9: VSC-HVDC main structure and components                                                                                                  |    |

| Figure 2- 10: HVDC networks arrangements via various VSC units' configurations                                                                       |    |

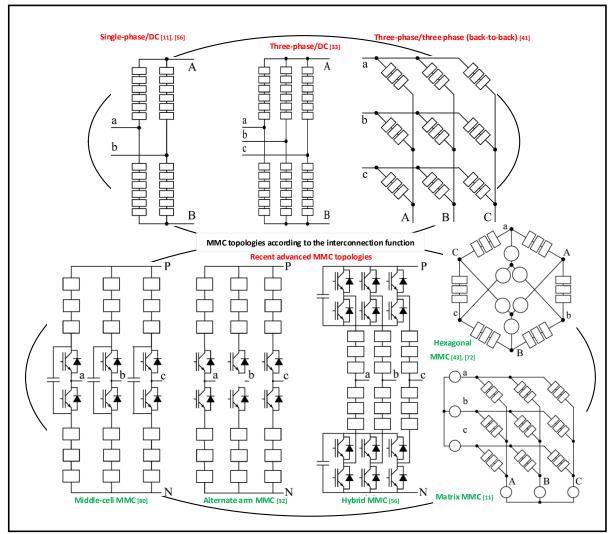

| Figure 2- 11: VSC classifications shown MMC expansion                                                                                                |    |

| Figure 2-12: Various voltage cells topologies with their corresponding voltage level                                                                 | 20 |

|                                                                                                                                                      |    |

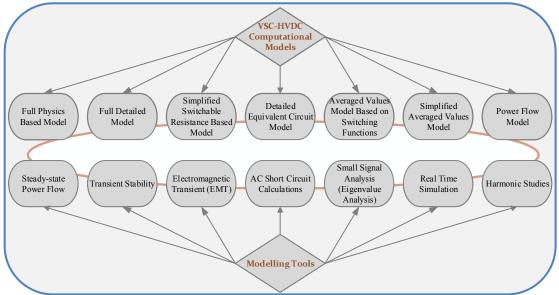

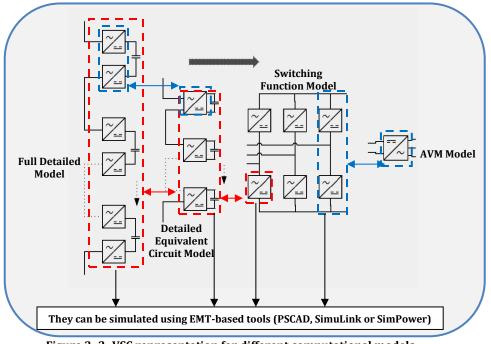

| Figure 3-1: Various types of VSC-HVDC computational models and all the possible analysis tools                                                       | 25 |

| Figure 3- 2: Physical representation of a VSC-HVDC system with different models                                                                      | 28 |

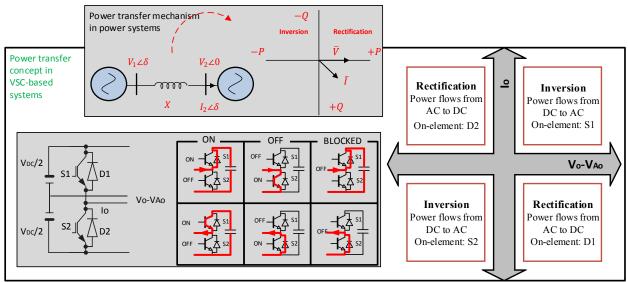

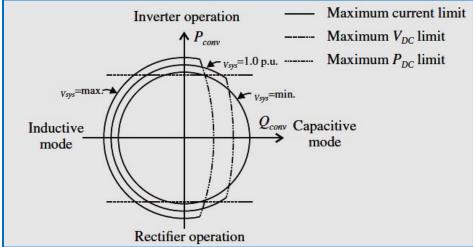

| Figure 3- 3: VSC power transfer capability                                                                                                           | 28 |

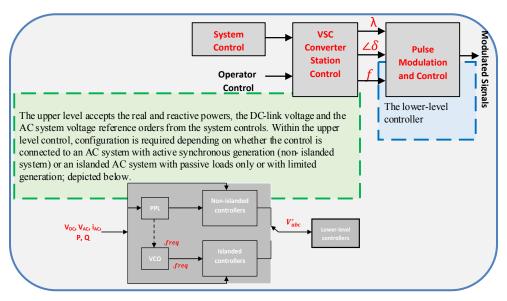

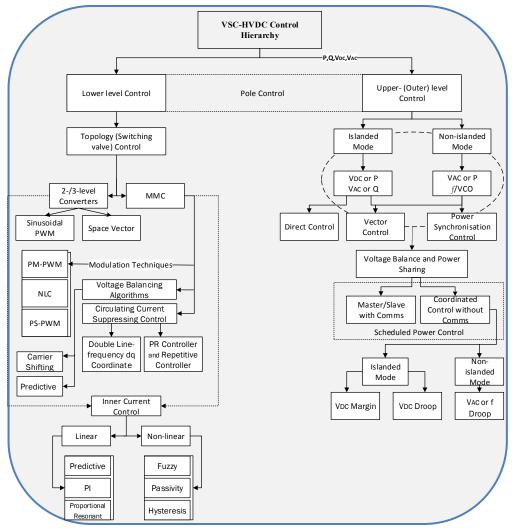

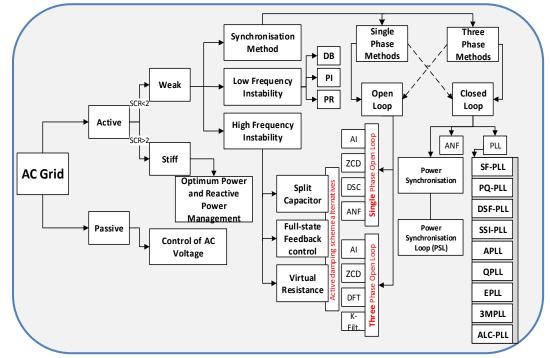

| Figure 3- 4: Generic VSC-HVDC control categorisations                                                                                                | 30 |

| Figure 3- 5: VSC-HVDC control detailed hierocracy                                                                                                    |    |

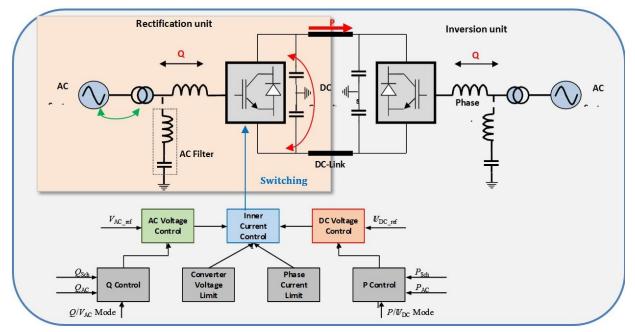

| Figure 3- 6: Single phase representation of two terminals point-to-point VSC-HVDC and its corresponding                                              |    |

| control scheme                                                                                                                                       |    |

| Figure 3-7: Single phase representation of MMC-HVDC and its corresponding control scheme                                                             |    |

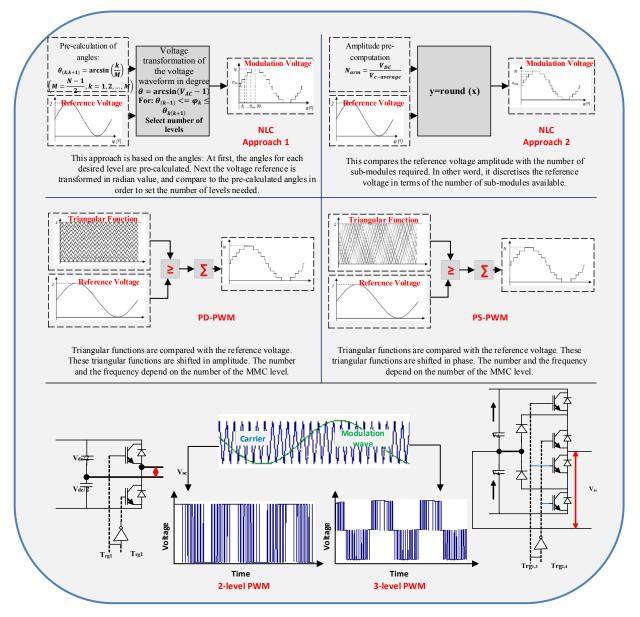

| Figure 3-8: Different VSC-HVDC modulation strategies for MMC, two-level and three-level arrangements.                                                |    |

| Figure 3- 9: Various approaches for DC link voltage balance                                                                                          |    |

| Figure 3-10: AC grid classes and their corresponding control schemes (Grid-tied synchronisation method                                               |    |

|                                                                                                                                                      |    |

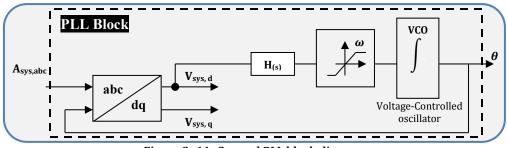

| Figure 3- 11: General PLL block diagram                                                                                                              |    |

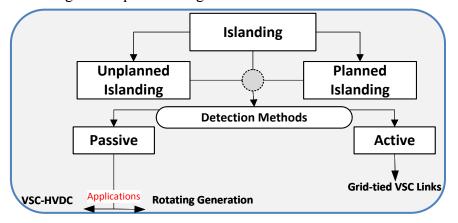

| Figure 3- 12: Islanding classes and their corresponding detection methods                                                                            | 44 |

|                                                                                                                                                      |    |

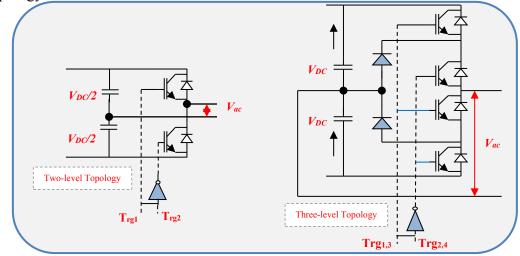

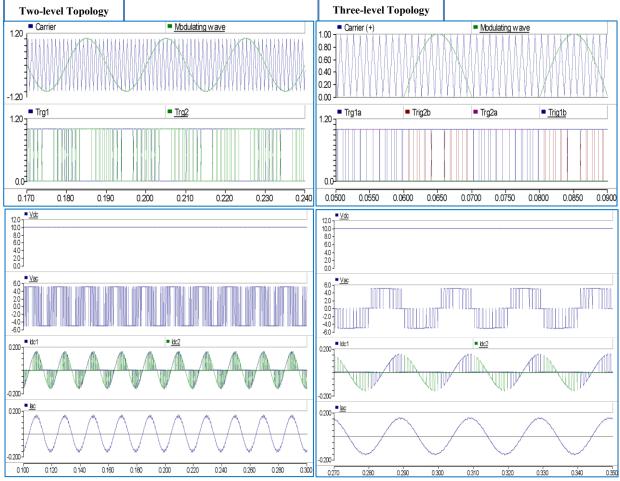

| Figure 4- 1: Single phase two-level and three-level VSC converters using PWM strategy                                                                |    |

| Figure 4- 2: PWM-controlled 2-level and 3-level VSC converters waveforms in PSCAD/EMTDC®                                                             |    |

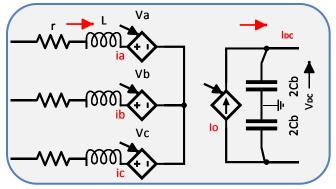

| Figure 4- 3: AVM VSC model                                                                                                                           |    |

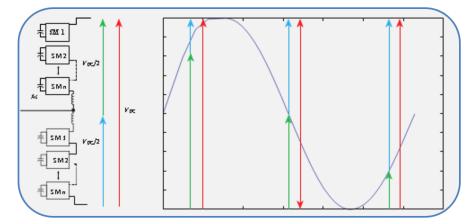

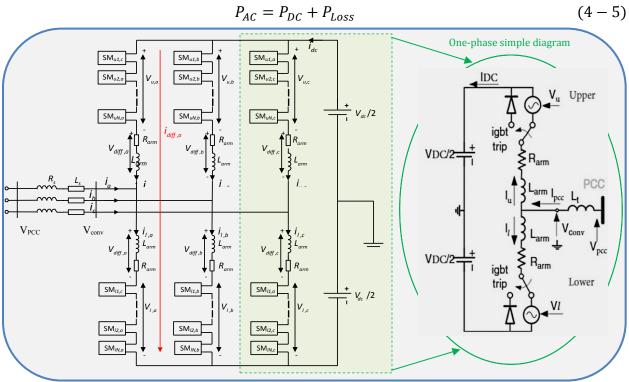

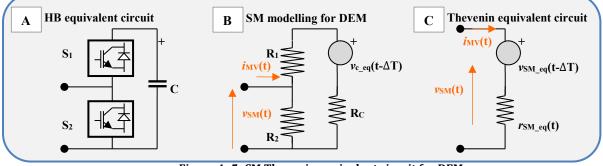

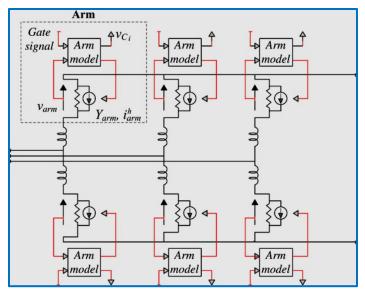

| Figure 4- 4: Three phase MMC generic scheme for N-level arrangement                                                                                  |    |

| Figure 4- 5: Submodule Thevenin equivalent circuit for DEM                                                                                           |    |

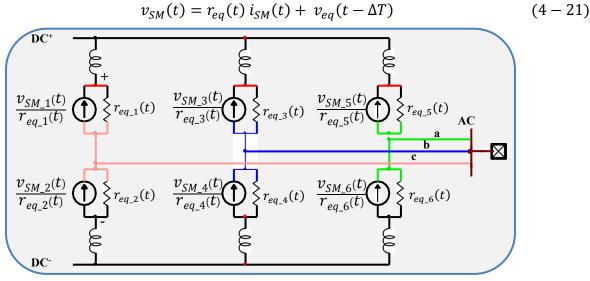

| Figure 4- 6: MMC equivalent circuit based on EDM model                                                                                               |    |

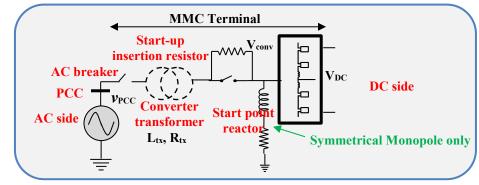

| Figure 4- 7: MMC-HVDC terminal layout developed by Alstom [4]                                                                                        |    |

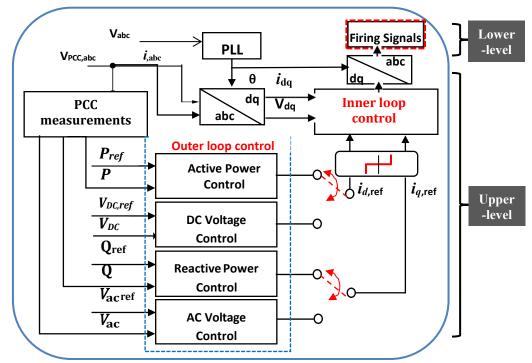

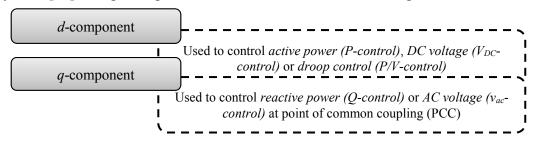

| Figure 4-8: Upper-level and Lower-level control structure for non-islanded MMC terminal                                                              |    |

| Figure 4- 9: Typical Monopole configuration of an MMC terminal                                                                                       |    |

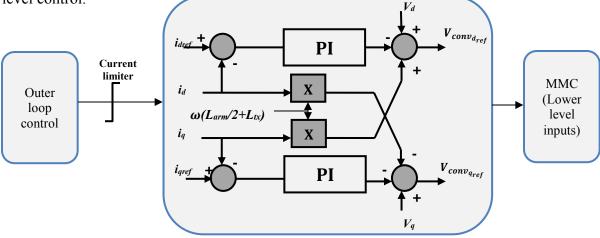

| Figure 4- 10: Inner control loop diagram                                                                                                             |    |

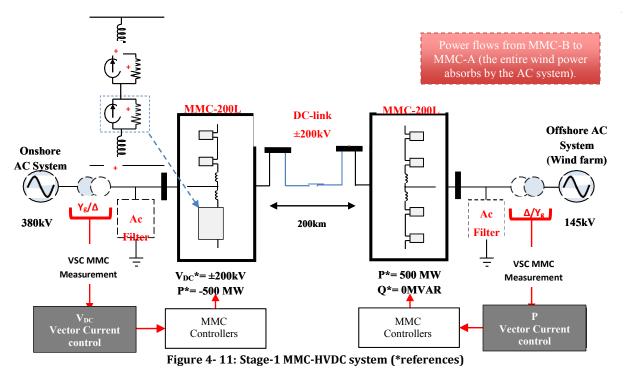

| Figure 4- 11: Stage-1 MMC-HVDC system                                                                                                                |    |

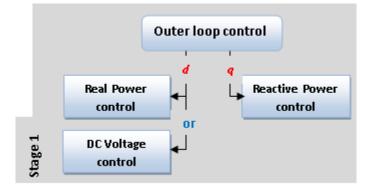

| Figure 4- 12: Equipped outer-loop controllers for Stage-1                                                                                            |    |

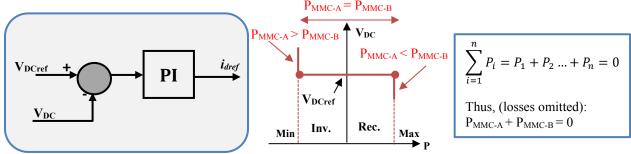

| Figure 4- 13: V <sub>DC</sub> schematic diagram and V <sub>DC</sub> /P characteristic curve                                                          |    |

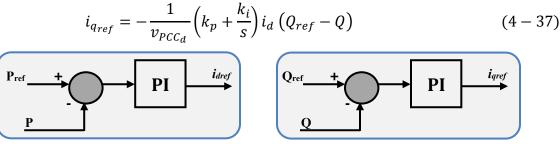

| Figure 4- 14: P-control and Q-control block diagrams                                                                                                 |    |

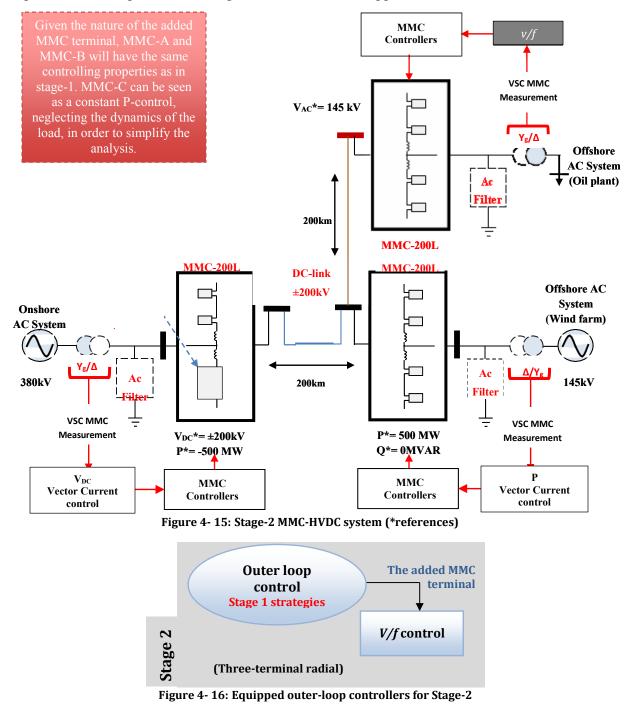

| Figure 4- 15: Stage-2 MMC-HVDC system                                                                                                                |    |

| Figure 4- 16: Equipped controllers for Stage-2                                                                                                       |    |

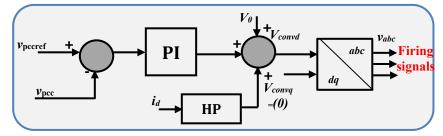

| Figure 4- 17: Islanded control structure                                                                                                             | 63 |

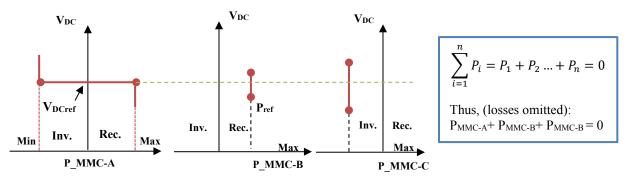

| Figure 4- 18: Stage-2 P/V <sub>DC</sub> characteristics curve                                                                                                                                                              | 63    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 4- 19: Equipped controllers for Stage-3                                                                                                                                                                             | 63    |

| Figure 4- 20: Stage-3 MMC-HVDC grid (* References)                                                                                                                                                                         | 64    |

| Figure 4- 21: vac-control block diagram                                                                                                                                                                                    |       |

| Figure 4- 22: Stage-3 droop block diagram for P-controllers                                                                                                                                                                | 68    |

| Figure 4- 23: Voltage Droop control with dead-band                                                                                                                                                                         | 69    |

| Figure 4- 24: Lower-level control for MMC terminal                                                                                                                                                                         | 70    |

| Figure 4- 25: CCSC control block diagram                                                                                                                                                                                   |       |

| Figure 4- 26: NLC control block diagram                                                                                                                                                                                    | 72    |

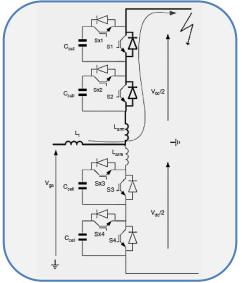

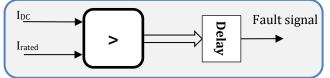

| Figure 4- 27: AC current to DC current faults comparison                                                                                                                                                                   |       |

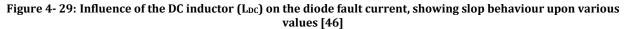

| Figure 4- 28: One phase of HB MMC during a DC fault [54]                                                                                                                                                                   | 75    |

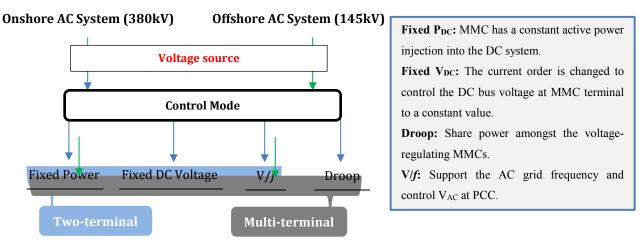

| Figure 5-1: Possible control strategies for MMC terminals based on their hosted AC systems                                                                                                                                 | 79    |

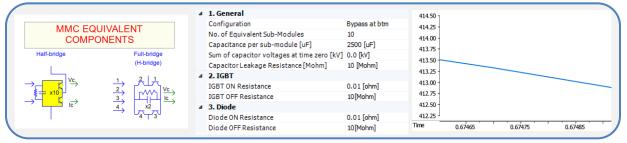

| Figure 5-2: PSCAD adapted MMC half-bridge terminals in VSC Technology© library                                                                                                                                             |       |

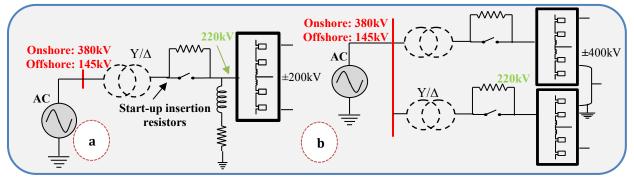

| Figure 5-3: (a) monopole, (b) bipolar MMC configuration                                                                                                                                                                    |       |

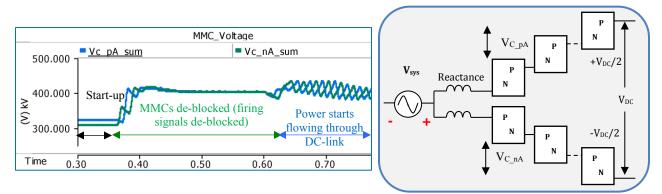

| Figure 5–5: The positive and negative voltage sums for MMC-B phase-a pre- and post-steady state                                                                                                                            |       |

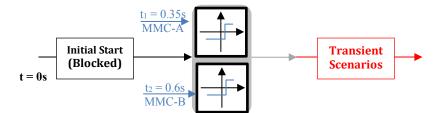

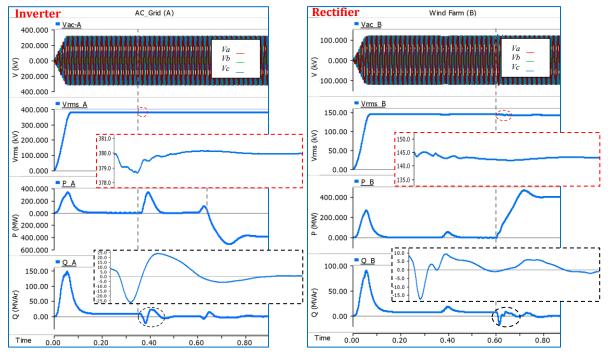

| Figure 5-6: System behaviour following MMC terminals de-blocking: AC voltages at PPC V <sub>AC</sub> -A= 220kV                                                                                                             |       |

| $V_{AC}$ -B= 120kV; L-L rms voltages $V_{rms}$ -A= 380kV and $V_{rms}$ -B= 145Kv; $P_{meas}$ and $Q_{meas}$ are the measured as                                                                                            |       |

| and reactive powers at the respective AC bus                                                                                                                                                                               |       |

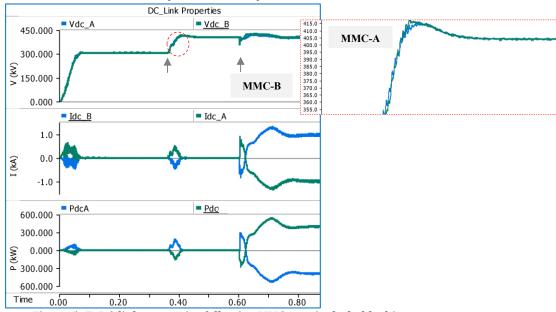

| Figure 5- 7: DC-link properties following MMC terminals de-blocking                                                                                                                                                        |       |

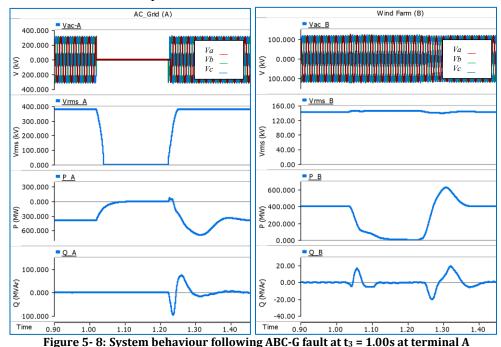

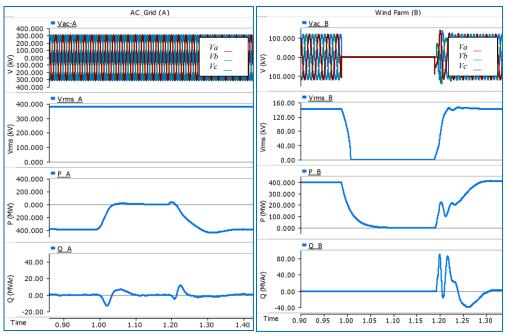

| Figure 5-8: System behaviour following ABC-G fault at $t_3 = 1.00s$ at terminal A                                                                                                                                          |       |

| Figure 5- 9: System behaviour following ABC-G fault at t <sub>4</sub> = 1.00s at terminal B                                                                                                                                |       |

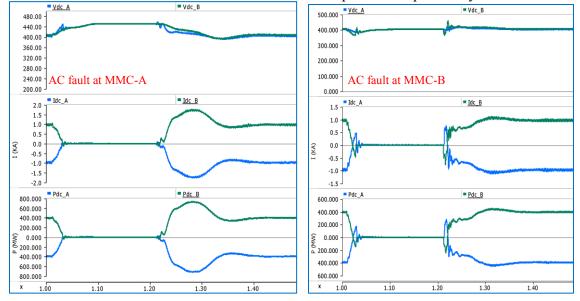

| Figure 5- 10: DC-link behaviour during AC faults taking place at both MMC terminals                                                                                                                                        |       |

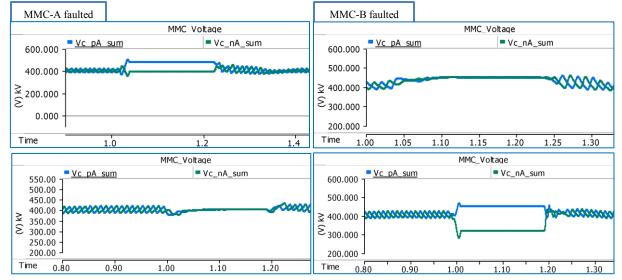

| Figure 5- 11: MMC behaviour (phase-A) positive and negative sums following system's transients                                                                                                                             |       |

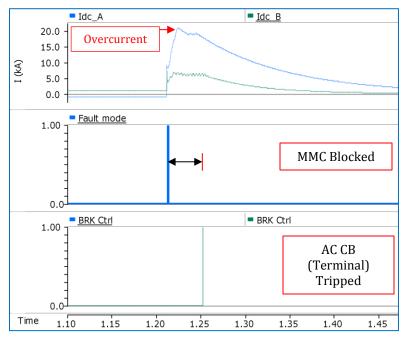

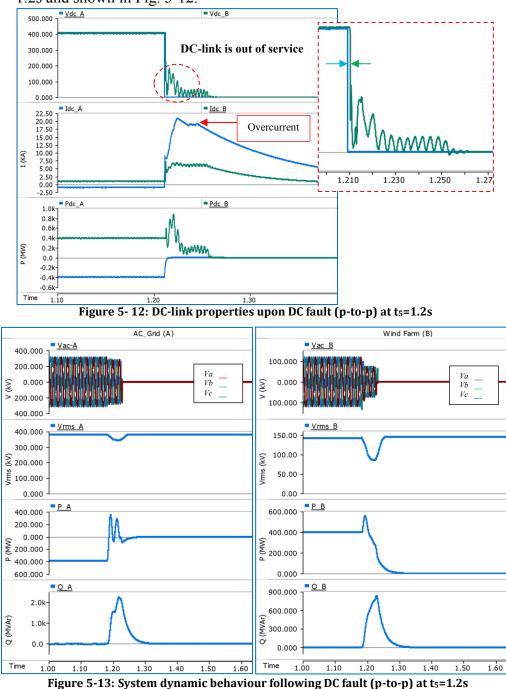

| Figure 5- 12: DC-link properties upon DC fault (p-to-p) at t <sub>5</sub> =1.2s                                                                                                                                            |       |

| Figure 5-13: System dynamic behaviour following DC fault (p-to-p) at t <sub>5</sub> =1.2s                                                                                                                                  |       |

| Figure 5- 14: P/V <sub>DC</sub> characteristics for MMC-A terminal                                                                                                                                                         |       |

| Figure 5-15: System behaviour following MMC terminals de-blocking: AC voltages at PPC VAC-A= 220k                                                                                                                          |       |

| V <sub>AC</sub> -B = V <sub>AC</sub> -C= 120kV; L-L rms voltages V <sub>rms</sub> -A= 380kV and V <sub>rms</sub> -B = V <sub>rms</sub> -C= 145Kv; P <sub>meas</sub> and Q <sub>meas</sub> are                              | e the |

| measured active and reactive powers at the respective AC bus                                                                                                                                                               | 92    |

| Figure 5-16: DC-link properties following all MMC terminals de-blocking at different timeslots                                                                                                                             | 92    |

| Figure 5- 17: The positive and negative voltage sums for MMC terminals (phase-a) pre- and post-stead                                                                                                                       | -     |

| $\Gamma_{\rm c}$                                                                                                                                                                                                           |       |

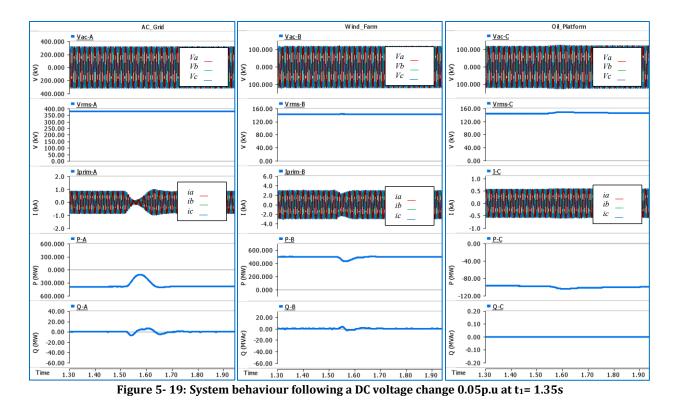

| Figure 5- 18: DC-link performance during DC voltage change 0.05p.u at t <sub>1</sub> = 1.35s                                                                                                                               |       |

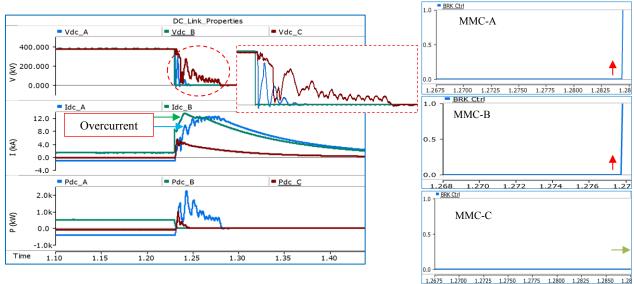

| Figure 5- 19: System behaviour following a DC voltage change 0.05p.u at t <sub>1</sub> = 1.35s<br>Figure 5- 20: DC-link properties upon DC fault (p-to-p) at t <sub>1</sub> =1.23s                                         |       |

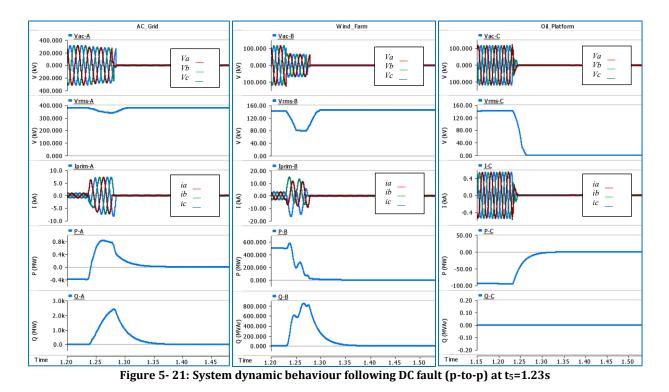

| Figure 5- 20: DC-link properties upon DC fault (p-to-p) at t <sub>1</sub> =1.23s<br>Figure 5- 21: System dynamic behaviour following DC fault (p-to-p) at t <sub>5</sub> =1.23s                                            |       |

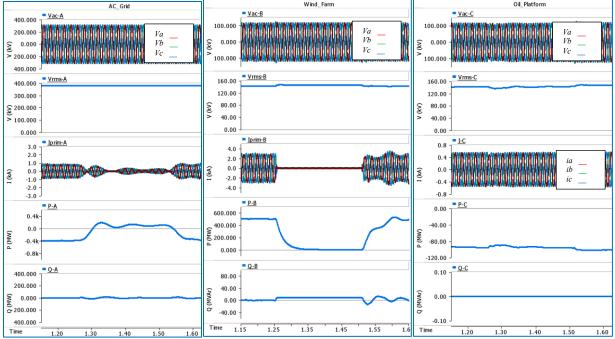

| Figure 5- 21: System behaviour following permanent trip of terminal B at $t_2=1.23s$ and cleared at $t_3=1$                                                                                                                |       |

| Figure 5-22. System behaviour following permanent trip of terminal D at $t_2$ =1.2set and cleared at $t_3$ =1 Figure 5-23: P/V <sub>DC</sub> characteristics for all MMC terminals within and outside the dead-band margin |       |

| Figure 5-24: System behaviour following MMC terminals de-blocking: AC voltages at PPC $V_{AC}$ -A = $V_{AC}$ -                                                                                                             |       |

| $D = 220$ kV and $V_{AC}$ -B= 120kV; L-L rms voltages $V_{rms}$ -A= $V_{rms}$ -C = $V_{rms}$ -D 380kV and $V_{rms}$ -B = 145Kv; $P_{me}$                                                                                   |       |

| $Q_{\text{meas}}$ are the measured active and reactive powers at the respective AC bus                                                                                                                                     |       |

| Figure 5- 25: DC-link properties following all MMC terminals de-blocking at different timeslots                                                                                                                            |       |

| Figure 5- 26: System performance upon terminal A outage at $t_5 = 2.25s$                                                                                                                                                   |       |

| Figure 5-27: Power transfer profiles for all MMC terminals upon MMC-A outage (Droop activated)                                                                                                                             |       |

| Figure 5-28: DC-link properties following MMC-A outage at $t_5 = 2.25s$ (Droop activated)                                                                                                                                  |       |

| Figure 5- 29: System dynamic behaviour following DC fault (p-to-p) at t <sub>6</sub> =1.5s close to MMC-D                                                                                                                  |       |

| Figure 5- 30: DC-link properties following DC fault near MMC-D at $t_5 = 1.5s$                                                                                                                                             |       |

| Figure 5- 31: Power transfer profiles for all MMC terminals upon DC fault near MMC-D                                                                                                                                       |       |

|                                                                                                                                                                                                                            |       |

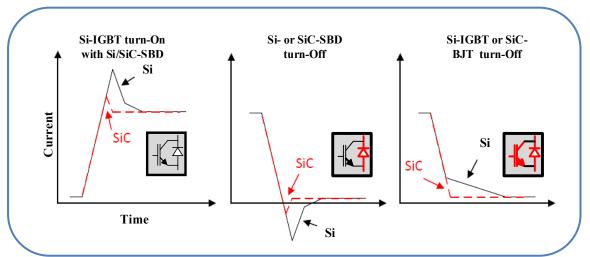

| Figure 6- 1: Benefit of SiC hybrid modules and full SiC modules compared to the current Si module (IGB' | T)  |

|---------------------------------------------------------------------------------------------------------|-----|

| proposed by [84]                                                                                        | 118 |

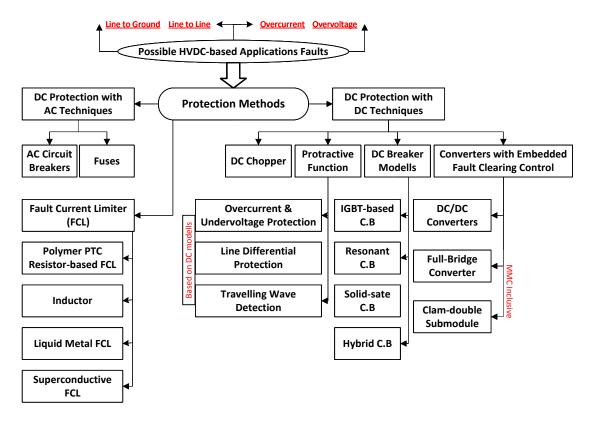

| Figure 6- 2: HVDC protection methods classified based on their AC/DC functions                          | 119 |

# List of Tables

| Table 1- 1: Thesis content                                                                     | 7        |

|------------------------------------------------------------------------------------------------|----------|

| Table 2-1: Comparison among the different VSC-HVDC configurations shown in Fig 2-10            |          |

| Table 2- 2: MMC voltage cells comparison                                                       |          |

| Table 3- 1: Comparison among the various VSC-HVDC models                                       | 26       |

| Table 3- 2: Functionality and capability of various VSC-HVDC models                            |          |

| Table 3- 3: Most common modelling tools used for HVDC studies and analysis                     |          |

| Table 3- 4: Description of the general upper-level control schemes                             |          |

| Table 3- 5: Different possible control arrangement for a two terminals VSC-HVDC system         |          |

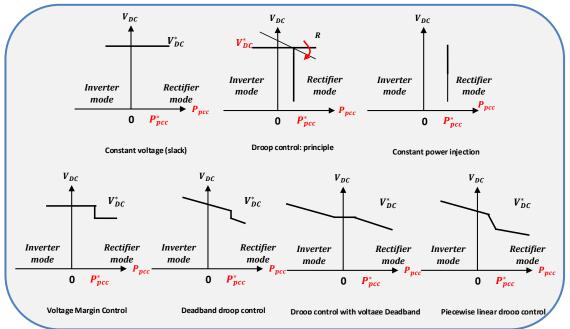

| Table 3- 6: DC-link voltage balance approaches description                                     |          |

| Table 3-7: Comparison among some open-loop strategies shown in Fig. 3-10                       |          |

| Table 3- 8: Comparison among PLL-based techniques shown in Fig. 3-10                           | 42       |

| Table 4- 1: The parameters of the cable layers shown in Fig. 4-31                              | 77       |

| Table 5-1: Various Fault scenarios to assess various MMC-HVDC links control and protection sch | emes82   |

| Table 5- 2: Stage-1 control data                                                               | 83       |

| Table 5- 3: Stage-2 control data                                                               |          |

| Table 5- 4: Stage-2 control data                                                               |          |

| Table 5- 5: Architecture comparison of the studied MMC-HVDC schemes                            |          |

| Table 5- 6: Studied stages comparison upon disturbed conditions                                |          |

| Table 5-7: The used MMC terminals control modes and possible alternatives (Redundancy assess   | ment)109 |

| Table 6- 1: Comparison among various SiC-based devices reported in the literature              |          |

| Table 6- 2: Key comparison of technological DC/DC converters for HVDC applications             |          |

# Nomenclature

| abc   | Three-phase stationary reference frame                                 |

|-------|------------------------------------------------------------------------|

| AC    | Alternating Current                                                    |

| AVM   | Average Value Model                                                    |

| CBA   | Capacitor Balancing Algorithm                                          |

| CCSC  | Circulating Current Suppressing Controller                             |

| CSC   | Current Source Converter                                               |

| C&P   | Control and Protection                                                 |

| DC    | Direct Current                                                         |

| DECM  | Detailed Equivalent-Circuit Model                                      |

| dq    | Direct-Quadrature Rotating Reference Frame                             |

| EHV   | Extra High Voltage                                                     |

| EMF   | Electromagnetic Field                                                  |

| FB    | Full-Bridge                                                            |

| GTO   | Gate Turn Off                                                          |

| HB    | Half-Bridge                                                            |

| HV    | High Voltage                                                           |

| HVAC  | High Voltage Alternating Current                                       |

| HVDC  | High Voltage Direct Current                                            |

| IGBT  | Insulated Gate Bipolar Transistor                                      |

| LCC   | Line Commutated Converter                                              |

| L-L   | Line-to-Line                                                           |

| LV    | Low Voltage                                                            |

| MMC   | Modular Multilevel Converter                                           |

| MMC-j | <i>j</i> represents the different MMC terminals in the studied schemes |

| MTDČ  | Multi-Terminal Direct Current                                          |

| MV    | Medium Voltage                                                         |

| NLM   | Nearest Level Modulation                                               |

| PCC   | Point of Common Coupling                                               |

| PI    | Proportional-Integral                                                  |

| PLL   | Phase-locked loop                                                      |

| PSL   | Power-Synchronisation Loop                                             |

| PWM   | Pulse Width Modulation                                                 |

| rms   | Root Mean Square                                                       |

| SM    | Submodule                                                              |

| SCR   | Short Circuit Ratio                                                    |

| VSC   | Voltage Source Converter                                               |

| VS    | Voltage Source                                                         |

| XLPE  | Cross-Linked Poly-Ethylene                                             |

| WBG   | Wideband Gap                                                           |

|       |                                                                        |

### **HVDC Definitions and Thesis Terminologies**

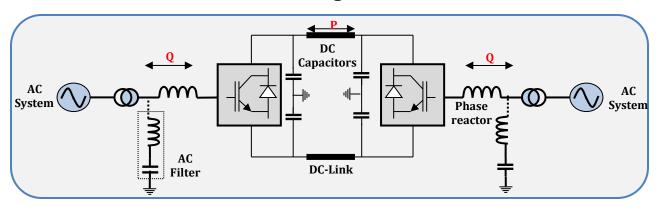

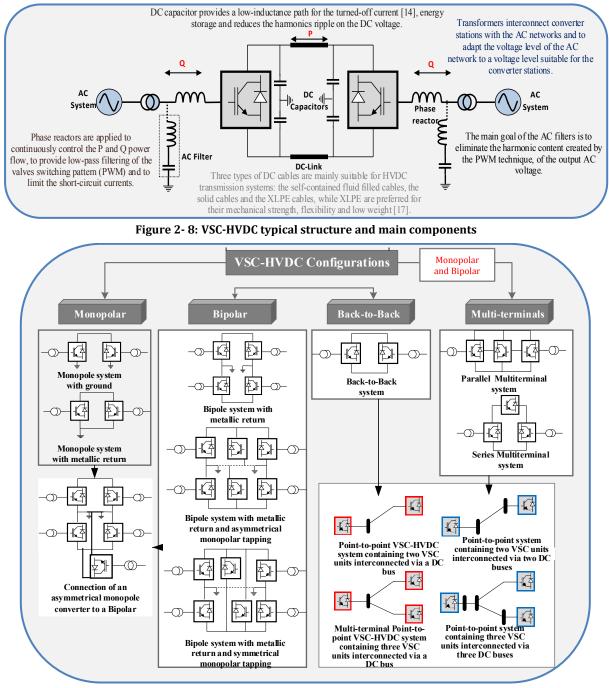

### • Transformer

It can be observed that transformers are implemented to interconnect the VSC terminals with the AC systems. Their main function is to adapt the voltage level of the AC system to a voltage level suitable for the converter terminal. This voltage level can be controlled using a tap changer, which will maximize the reactive power flow.

### • Phase Reactor

Phase reactors, or converter reactors, are applied to continuously control the active and reactive power flow. According to [14], phase reactors have three main functions:

- 1. Providing a low-pass filtering of the IGBTs switching pattern (PWM) in an effort to deliver the desired fundamental frequency voltage,

- 2. Providing active and reactive power control; the active and reactive power flow between the AC and the DC sides is defined by the fundamental frequency voltage across the reactors [14], and

- 3. Limiting the short-circuit currents. Typically, the short-circuit voltage of the phase reactor is 15%.

### • AC Filter

The main goal of the AC filters is to eliminate the harmonic content, which was created by using the PWM technique, of the output AC voltage. In MMC-based HVDC, AC filter can be omitted.

### • DC-link Capacitor

It is apparent that on the DC side, there are two capacitors stacked with the same power rating. The main goal of the DC-link capacitor is to provide a low-inductance path for the turned-off current [14]. Moreover, DC capacitor serves as an energy storage and it reduces the harmonics ripple on the DC voltage. Depending on the size of the DC side capacitor, DC voltage variations caused by disturbances in the system; such as AC faults, can be limited [14].

### • DC Cable

Three types of DC cables are mainly suitable for HVDC transmission systems. These are: the selfcontained fluid filled (oil filled, gas pressurized) cables, the solid cables and the XLPE polymer extruded cables. Following the recent advancement in both power electronics and then HVDC schemes, XLPE seems to be the preferred choice for VSC-based HVDC transmission system, because of its mechanical strength, flexibility and low weight [17].

### • MMC Terminals

MMC terminals are attributed to the DC/AC conversion unit (MMC converter), the transformer, the submodule DC capacitors, control equipment and arm reactors.

### • AC Systems

AC systems representation depends heavily on the purpose of the study. For example, when transients being examined, they can be modelled as voltage sources (R-R/L configurations of Thevenin source impedance), whereas in transient stability studies actual machine representations are required. Thus, AC systems can be represented as "source" or "machine" forms.

### Thesis Terminologies

**HVDC** scheme signifies a transmission system that utilizes high DC voltage and is not purely based on DC technologies. The scheme can be arranged in either HVDC system or HVDC grid (DC grid).

**HVDC** system is an autonomous HVDC link, which operates at a single DC high nominal voltage. In a HVDC system, all busses are directly connected [29]. Protection devices such as circuit breakers can be series-connected within the HVDC system, even though that is not principally a direct conductor interconnection.

**HVDC Grid** refers to a DC transmission system of more than two terminals with at least one meshed DC line. It can also consist of two or more interlinked HVDC systems. The main operational difference between HVDC system and HVDC grid is the way of dealing with unplanned disturbances.

**MMC Terminal** is a converter station where power is exchanged between the AC and DC sides and it contains all the MMC converter equipment along with an ideal transformer.

## **Chapter 1**

# Introduction

This chapter defines the research statement and the method to approach it. It comprises the research question, aims and objectives and thesis outline.

### 1.1 Background

The characteristics and structure of High-Voltage Direct Current (HVDC) power conversion terminals have stayed practically unaltered for the initial 50 years of commercial operation [1]. Confined by the switching mechanisms, earlier of the mercury arc valve and later of the silicon-operated rectifier, HVDC demanded an extra support; especially at the link terminals to warrant a stable operation [1].

The recent enhancement of high-power semiconductors in their ratings, controllability and operation has taken hold in many power applications, including HVDC schemes [2-6]. HVDC as a technology encapsulates a variety of semiconductor controllers developed mainly to augment the performance of the conventional grid at large. However, it is the complete structure of such HVDC link that provides transmission flexibility, rather than a particular controller. It is; therefore, clear that the attitude towards HVDC links has changed as power semiconductor kept moving forwards, resulting in a number of power conversion topologies with higher controllability and switching frequencies. Despite the major market for HVDC systems is yet thyristor-based, a modern transistor-based (IGBT) technology has gained a substantial attention whether in academia or industry, and is already being deployed throughout the world [4]. Allowing for a large and stable power transfer, containing fast emergency controls to evade large fault current levels and delivering or absorbing the needed reactive power to sustain the predetermined voltages at the exchanged buses are such enhancements in modern HVDC schemes.

Thus, the modern HVDC interconnections are probably the most flexible power transmission systems [6]. Nevertheless, the consequential HVDC transmission flexibility comes at the expense of either higher complexity or lower efficiency. Therefore, when regarding a new HVDC scheme, it is paramount to decide on the degree of the entailed flexibility for a specific application.

The traditional HVDC transmission schemes, which are based on thyristor valves, were known to the real-world since 1950s, following a renewed attention to the utilization of DC technology that was long disregarded after the "war of currents" [7-9]. The interest was mainly driven by the need for a long distance power transfer that the AC technology found to be unviable for virtue of the power capacity of an AC cable reduces considerably, owning to the excessive charging current. This holds true even for moderate voltage levels and distances [8].

The first HVDC transmission scheme with IGBT valves employment was put into practice in Sweden in 1997 [5]. It was a 50MW underground DC link, interconnecting the mainland Sweden to Gotland Island. Despite the appearance of DC links in the context of cable transmission, an overhead line transmission beyond 100km seems cost-effective to the AC sense, where transmission capacity is increasingly limited due to stability considerations. The progress in VSC technology and its technical benefits lead to an increasing demand for this converter type for HVDC applications [9]. Thus, the need for configurational test philosophies, useful control and modelling test procedures and reasonable acceptance criteria and classifications for VSC technology in HVDC arose.

### **1.2** Motivation

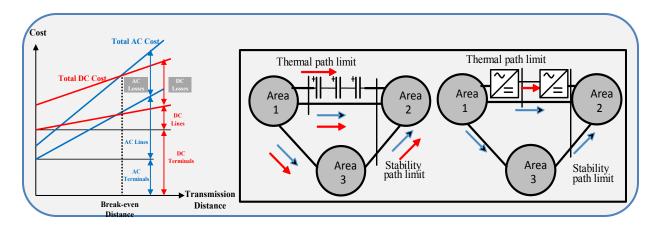

It is acknowledged in [3-14] that HVDC links are more economical for a long distance power transmission compared with AC power transmission as shown in Fig. 1-1.

Figure 1- 1: Transmission distance vs. cost for AC and DC power transmission (Left), distance to power effects in AC systems compared with DC systems (Right)

The HVDC curve is not as steep as the HVAC curve because of the considerably lower line costs per km. For long AC lines, the cost of intermediate reactive power compensation needs

to be taken into account [10]. The break-even distance is in the range of 400 to 800km. The distance to power effects in AC systems compared with DC systems are also depicted in Fig. 1.1 [10], which shows a new transmission line between Area-1 and Area-2 utilizing AC and DC transmission approaches. In the former approach, the adopted series Reactive Power compensation allows for more power transfer on the added line, whilst an AC-DC-AC conversion approach is incorporated in the DC system. In the AC line, the power will transfer through the new and existing lines, while in the DC line, the power can be scheduled to pass through the new path [9-11]. This dynamic area of power transmission, where DC technologies seem superior to AC technologies, will be a matter to argue in this thesis. In other words, thesis's research is motivated by the practical optimization that DC technologies have brought into AC power systems, allowing more power applications to hold true in real-world.

The massive installation of renewable energies provides an opportunity of deprecating the classical point-to-point connections in favour of the concept of MTDC grid, which links more than two terminals in various arrangements (ring, radial or heavily meshed) [10]. A number of HVDC projects developers are seemingly ascertained that the possibility of developing an MTDC grid shall be via interconnecting the existing point-to-point HVDC schemes.

#### **Cigre B4-107 committee agreed that**

"It is unlikely that the final solution [to the European SuperGrid] consists of a single large interconnected offshore grid: roadmaps usually come up with several offshore grids not connected together by DC branches..." [8].

#### HVDC experts at ABB stated that

"DC grids are likely to be erected and developed gradually, either starting from existing point-to-point DC connections, or via different project phases (as planned for the Atlantic Wind Connection project in [2]) ...Inherent modularity in the design of HVDC converter stations means that HVDC technology is well suited to staged-development. The staged development of transmission capacity allows for the deferment of a portion of the capital cost until the additional transmission capacity is required. This might be a desirable approach, particularly when integrating renewable energy, where planned generation assets may be commissioned over a period of many years," [11].

Therefore, a paramount aspect in realizing an MTDC grid will be the interoperability among various individual HVDC projects. Interoperability entails standardization of the common philosophies of design, testing procedures, and operation of MTDC grids. For example, if the DC-link voltage and load-flow control principles are not standardized, it might not be feasible to interconnect the existing HVDC schemes and create an MTDC grid [12]. Therefore, the research

study also motivates by adopting various HVDC schemes implementing in three stages, where the MTDC grid concept is the final stage.

Until recently, VSC converters for HVDC applications employed two-level or three-level topologies that apply equivalent voltage levels to the AC terminal of the converter. A critical drawback of these topologies is the significant switching power loss resulting from large voltage swings [15]. One approach to improving the waveform and reducing switching losses is to use multilevel converters, which provide an output waveform with several voltage levels so that each step in voltage waveform is a fraction of the total voltage swing [16]. The resulting waveform can be designed to be closer to that of a sine-wave. The recent introduction of a new topology that is the modular multilevel converter (MMC) is a major step forward in VSC technologies for HVDC transmission. Therefore, measuring the possibility of adapting MMC into HVDC schemes is an active research area with the motivation that MMC already seems to introduce a new era of DC power transmission, allowing more reliable and cost-effective power system.

MTDC is seen as the solution to the massive integration of renewable energies and large interconnection of power systems, while increasing the reliability of the system by providing redundancy in paths and allowing a greater power exchange capability [2-11]. However, the technology is still relatively under development and knowledge is superficial. The assessment of MTDC grid that incorporates VSC is another motive in this thesis for the reason that MTDC grids are seemingly superior to the conventionally structured HVDC links, and yet the later is still dominating the industry. This is due to the fact that a number of challenges including different aspects of modelling, control, operation and optimization of MTDC grids are yet to be investigated.

### **1.3** Aims and Objectives

The business case for VSC-HVDC is becoming popular in power transmission systems. Despite their superior potential compared with the AC and LCC-HVDC technologies, a large MMC-MTDC grid is yet to be realized in practice. Operation, control, modelling and protection of MMC-MTDC grids are arguably power engineering challenges that the academia and industry are presently engaged in. Moreover, there is a lack of clarity about whether and how an MTDC grid could be implemented, operated and controlled to support the hosted AC systems. The prerequisite to studying the aforementioned aspects in a systematic approach is to develop a

framework of modelling and stability analysis for MMC-MTDC grid that is compatible with those for conventional AC systems. The research work encapsulates several broad objectives that are categorized as

- VSC-HVDC credibility,

- MMC-HVDC expandability and

- MMC-HVDC operation.

These broad objectives are relatedly approached by the following contributions

- establishing a comprehensive reference that criticizes the significance of HVDC in the future power industry as well as summarizing the areas, where the DC technologies show promising effects in the conventional AC applications. Additionally, the HVDC industrial experience is taken into account for the sake of a broad reference,

- incorporating through PSCAD/EMTDC® simulation the concept of staging by developing an MTDC grid from point-to-point MMC-HVDC links, and

- comparing the operational requirements and control redundancy upon each stage expansion.

### **1.4 Research Definition**

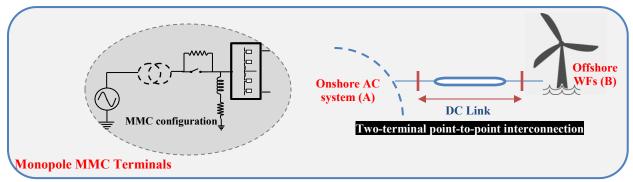

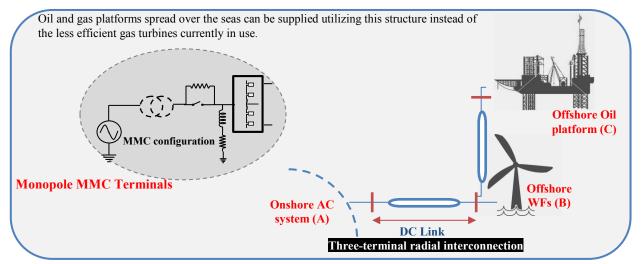

Despite the implementation of VSC technology in HVDC schemes has undergone an intensive examination in the last ten years, the gap of research is still wide; especially for MMC-based HVDC applications. The fast-pace of HVDC research has resulted in a volume of knowledge that is counterpart in some cases and complementary in others. This thesis attempts to bring the latest literature in HVDC into implementation of the most industrialized interconnections that are depicted in Fig. 1-2, Fig. 1-3 and Fig. 1-4.

The analysis endeavours at identifying critical modes of the interconnected DC and AC systems and revealing how these modes are associated with the scheme configuration and the different fragments of each MMC terminal controllers. It is clear that the point-to-point scheme is firstly envisioned and corroborated as an exploratory case and steppingstone towards the three-terminal radial scheme, which is then expanded into a four-terminal lightly meshed DC grid. Various HVDC based technologies have been incorporated throughout the expansion to validate the theories shown in the survey.

Figure 1-2: Single line diagram of stage-1 (Typical windfarms to onshore structure)

Figure 1-3: Single line diagram of stage-2 (Oil and gas platforms structure)

Figure 1-4: Single line diagram of stage-3 (MTDC grid structure)

## 1.5 Outline

Thesis chapters are organized as shown in Table 1-1 and are divided into two main categories that are either survey-related or analysis-related chapters.

| Relevance | Chapter                                                                              | Content                                                                                                                                                                                                                                                                                                                                                  |

|-----------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Survey    | Chapter 2:<br>HVDC Theoretical<br>Development<br>Survey                              | A state-of-the-art evaluation is concerned in this chapter in an effort to act as a reference that groups, classifies and provides insightful remarks of where the HVDC technology stands and is heading.                                                                                                                                                |

| Sarvey    | Chapter 3:<br>Control and<br>Modelling Aspects                                       | There is a wide range of VSC-HVDC modelling and controlling strategies that are injected into the literature in the past ten years. This chapter presents the most promising modelling and control aspects thereof in a wide range of analysis.                                                                                                          |

| Framework | Chapter 4:<br>Design Technicallity<br>of Staged-<br>Development MMC-<br>HVDC Schemes | This chapter endeavours to argue the various technologies presented in chapter 2 and<br>chapter 3 by implementing the most common HVDC links in industry. It shows how a<br>specific MMC-HVDC scheme calls for specific operational requirements. The<br>operational requirements are measured as the MMC-HVDC scheme undergone<br>through an expansion. |

|           | Chapter 5:<br>Simulation Analysis<br>and Comparsion                                  | The behaviour of the MMC-HVDC schemes in chapter 4 is investigated in various steady state and disturbed conditions using PSCAD/EMTDC <sup>®</sup> . The operation of each stage is hence compared, showing their operational supreme and defective aspects.                                                                                             |

| Summary   | Chapter 6:<br>Conclusion and<br>Reccomendadtions                                     | This chapter summarizes the concerned research and suggests future recommendations whom influence will push the MMC-MTDC theories into more practical cases.                                                                                                                                                                                             |

#### Table 1-1: Thesis content

## **Chapter 2**

# **HVDC Development Survey**<sup>1</sup>

For over a century, the electric energy generation, transmission, distribution and utilization techniques have been essentially based on Alternating Current (AC), throughout time the AC technologies have been pushed into their thermal and/or technical limitations. The Highvoltage DC technologies have as a result and mean of support been recurred. Therefore, a great volume of contributions tackling the domains and aspects that the DC-based technologies offer to the current AC power transmission systems are released, which include many configuration, modelling and control strategies. Thus, a state-of-the-art evaluation is aimed in this chapter to show the extending frontier of knowledge of HVDC applications.

### 2.1 Preliminary Time-Frame

Escalation in electrical power demand, and the relatedly in pace power generation results in a new load-flow pattern that is deemed difficult to accommodate; particularly in ultra-electric networks reside in North America and Europe [1-15]. The transmission system reinforcements in the AC systems and often the conventional method to construct an Ultra High-Voltage AC lines over the existing transmission systems are such approaches that can handle the ever-increased power demand/generation pattern. However, the experience of the last fifty years indicates that such approaches are either time and/or effort consuming and/or jurisdictionally voided [16]. Therefore, HVDC practicability has not only cleared the challenges of transmitting bulk of electric power over long distances, but is also being evident to resolve the current AC networks environmental and economical challenges along with the technical challenges of power flow control, stability, power quality and asynchronous interconnection.

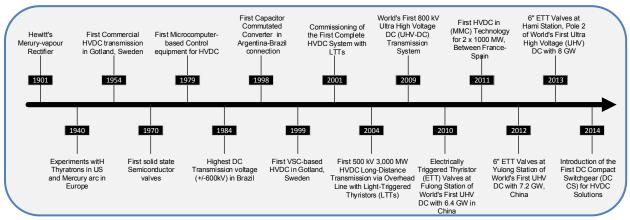

The development of HVDC systems executed since the 1930s, when mercury arc rectifiers were devised [10]. In 1941, a 60 MW commercial HVDC link was realized to supply Berlin city through a 115km underground cable. The system was dismantled during the World War II and never became in use. It was only in late 1954 that the first HVDC link of 10MW ratings was developed in Gotland and; consequently, HVDC links measured heavily in both industry and academia for their interconnection and stability aspects [11-15]. The historical milestones in the progress of HVDC transmission technology can be summarized in Fig. 2-1.

<sup>&</sup>lt;sup>1</sup> Hadi Alyami and Yasser Mohamed, "The Development of VSC-HVDC Structure, Modelling and Control Schemes" Submitted to Sustainable Energy, Grids and Networks, Elsevier. (Under review)

Figure 2-1: The historical milestones in the progress of HVDC transmission technology

HVDC transmission link with IGBTs was put into practice in Sweden in 1997. It was a 50MW underground DC link interconnecting the mainland Sweden to Gotland Island.

### 2.2 The Conventional Power Grid and HVDC Solution

### 2.2.1 AC Network Staging and HVDC Potential

It is a supreme principle that in conventional (AC-based) power networks, the power source must operate at a precisely matching frequency – 50Hz or 60Hz – and in a perfect synchronism [17]. Synchronous generators with a vastly foreseeable supply of fuel are typically employed, wherein each generation unit controls the level of its terminal voltage through the phase angle and the excitation current by means of the mechanical torque introduced by the turbine. A number of voltage transformers are incorporated to achieve a certain level of ratings according to the relatively low generated power [18]. The voltage level surrogates from low to high for efficient power transmission purposes and vice versa for a safe and economic power distribution [19].

Within a conventional power system, the utilization of interconnected primary transmission systems, to what the new power stations are linked, has been the commonly accepted philosophy behind the advancement of a competent power system [7]. Until the rated switchgear fault level was exceeded, the expansion of the primary transmission systems was typically executed. A new primary transmission system of higher fault levels and voltage was created beyond that point, whilst the existing system continued growing in a number of separate secondary systems [20]. The secondary transmission systems in return supplied several distribution feeders [23]. Therefore, the traditional power system has conventionally subsumed three separate systems namely *generation, transmission* and *distribution*, where all of which

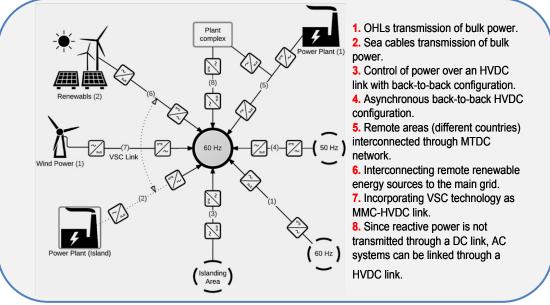

inflexibly tied by the synchronous restrains. As a result, the conventional power systems have been effectively enhanced in both reliability and functionality upon the introduction of HVDC links and this includes many power based applications, which are depicted in Fig. 2-2.

Figure 2-2: Different HVDC utilizations within power systems

### 2.2.2 AC Networks Challenges and Flexibility Concept Applied to HVDC

The traditional practice of a HVDC scheme is bulk power transmission over long distances because there is no stability constrain related to the amount of power or the transmission distance, which exist in the AC transmission systems mainly due to the increasing of Q consumption and capacitive current loss [2-15]. However, HVDC as a technology finds a great deal of applications, wherein it plays the major role as shown in Fig. 2-2. These applications were confined or rather impracticable before the DC transmission resurgence, which generally

- requires no synchronism among the different linked AC systems,

- is not limited to the length of transmission mediums; particularly sea cables,

- does not possess imaginary (reactive) part to which no Q is generated by the reactance. This means DC power transmission contains more P that is utilized for the actual power consumption than AC power transmission and hence more efficient.

- applies to all AC system conditions either with high or low SCR ratio,

- preserves an independent management of frequency and generator control, and

- enhances the AC system's stability and; accordingly, enhances the inner power-carrying capacity, by power modulation in response to power swing, frequency or line rating [24].

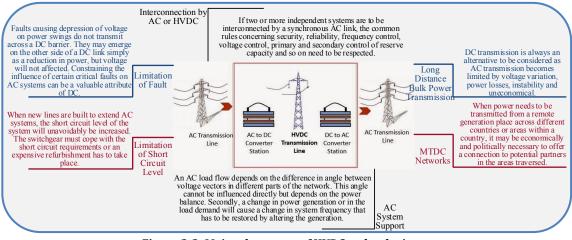

It is; therefore, applicable for HVDC links to play a key role in the future power systems, given the technical advantages that are visualized in Fig. 2-3.

Figure 2-3: Main advantages of HVDC technologies

### 2.2.3 HVDC: Towards more Flexible Power Grid

A variety of environmental, economical and technical reasons affect the various power grid activities, including transmission of power, are driving contemplation on the traditional power system development philosophy. The challenge is that, there is an increasing opposition to the acceptance of new transmission systems – principally the over-headlines – and ever growing primary transmission voltages [27-30]. On the other hand, there is a recognition that power system interconnections result in paramount benefits, including wider choices of generating plants, economies of scale, reduction in reverse capacity and pooling opportunities [29].

It is clear that a significant factor in the solution is the likelihood of turning up the power carrying capability of the employed transmission lines. In this respect, the traditional AC transmission is exasperatingly limited by the need to keep the two systems interlinked by the line in synchronism after disturbances, which is a condition of transient stability [31]. Thus, a rise in the steady-state power carrying capability is tied to the improvement in transient stability patterns that in return entail faster controllability [31].

### 2.3 HVDC Transmission

### 2.3.1 Current Source (CS) and Voltage Source (VS)

There are two fundamental electrical energy sources regarding the basic network theory. They are the *current source (CS)* and the *voltage source (VS)* [3]. As such, all the DC/AC conversion units are constructed to act as either a CS converter (CSC) or a VS converter (VSC).

The persistent progress in the HV-High-power switching valves has a paramount impact on the power electronic technologies utilized in power system [33]. The advancement of HVDC topologies according to the power switching valves evolution is depicted in Fig. 2-3. Appropriate topologies appeared to be initially composed with Mercury-arc valves in 1954 that was followed by line-commutated thyristor valves in early 1967, which are still intensively used in today's high DC power transmission [34]. Thyristors have been developed to include the turn-off capability that is featured in Gate Turn-off (GTO) thyristors and later in Integrated Gate-Commutated (IGCT) thyristors [34]. MOSFETs including the IG-Bipolar Transistor (IGBT) existed in late 1970s and; therefore, established a new field of high power valves [34]. HVDC links have thus gained numerous attention and a variety of applications, which are normally distinguished as CS- or VS-operated, appeared.

### 2.3.2 LCC-HVDC and VSC-HVDC

There exist two types of HVDCs: LCC-HVDC, which is line commutated, and VSC-HVDC, which is self-commutated. LCC-HVDC is a thyristor-based and CS-operated, where the direction of the current in the DC link does not change [37]. In a VSC, the voltage polarity in the DC link stays unchanged [31]. LCC-HVDC cannot perform an independent control of P and Q but

control them through variation of the converter firing angle  $\alpha$  [21]. By assuming the six-pulse topology and from the  $\alpha$  signal, the converter can be considered as an inverter or a rectifier, thus

$$V_{DC}^{inv} = \frac{3\sqrt{2}}{\pi} n V_{sys} \cos\beta - \frac{3X_c}{\pi} I_{DC}^{inv}$$

(2-1)

$$V_{DC}^{rec} = \frac{3\sqrt{2}}{\pi} n V_{sys} \cos \alpha - \frac{3X_c}{\pi} I_{DC}^{rec}$$

(2-2)

where  $V_{conv}$  and  $\theta_{conv}$  are the converter voltage and angle respectively, *n* is the transformer ratio,  $\beta = 180^{\circ} - \alpha$ ,  $V_{sys}$  is the voltage at the AC bus and  $X_c$  is the commutating reactance. An LCC-HVDC link is usually represented by a *T*-model to measure the DC side dynamics [34].

Figure 2-4: LCC-HVDC T-model

The DC line currents I<sub>DC</sub> and DC capacitance voltage V<sub>C</sub> can be given as

$$\frac{d}{dt}I_{DC}^{rec} = \frac{1}{L_{DC}}(V_C - V_{DC}^{rec} - R_{DC}I_{DC}^{rec})$$

(2-3)

$$\frac{d}{dt}I_{DC}^{inv} = \frac{1}{L_{DC}} \left( V_C - V_{DC}^{inv} - R_{DC}I_{DC}^{inv} \right)$$

(2-4)

$$\frac{d}{dt}V_C = \frac{1}{C_{DC}} \left( -I_{DC}^{rec} - I_{DC}^{inv} \right) \tag{2-5}$$

This permits for basic calculation of the instantaneous power flow from the DC link to each converter terminals and is expressed as

$$P_{DC} = I_{DC} V_{DC} \tag{2-6}$$

If converter terminals are deemed lossless, thus  $P_{conv} = P_{DC}$ . On the other hand, VSC-HVDC link is commonly represented by  $\pi$ -model as shown in Fig. 2-5.

Figure 2- 5: VSC-HVDC  $\pi$ -model (Power injection)

The DC line currents  $I_{DC}$  and voltages  $V_{DC}$  can be expressed as

$$\frac{d}{dt}V_{DC,i} = \frac{1}{C_{DC}} \left( -\frac{P_{DC,i}}{V_{DC,i}} - I_{DC} \right)$$

(2-7)

$$\frac{d}{dt}V_{DC,j} = \frac{1}{C_{DC}} \left( -\frac{P_{DC,j}}{V_{DC,j}} + I_{DC} \right)$$

(2-8)

$$\frac{d}{dt}I_{DC} = \frac{1}{L_{DC}} \left( -I_{DC}R_{DC} + V_{DC,i} - V_{DC,j} \right)$$

(2-9)

Similar to LCC-HVDC, if converter terminals are deemed lossless, thus  $P_{conv} = P_{DC}$ .

Although VSC-HVDC attributes as being less mature than LCC-HVDC, the interest in the former is increasing as it offers several benefits that are depicted in Fig. 2-6.

Figure 2-6 : VSC-HVDC advantages over LCC-HVDC

VSC-HVDC is seemingly solving the challenges that LCC-HVDC suffers from; nonetheless, they still cannot offer an economical solution at  $P \le 500$ MW, given the cost of multiple AC/DC terminals and cables required. The choice among LCC-HVDC, VSC-HVDC and AC systems is then influenced by the power amount transmitted and the distance as shown in Fig. 2-6.

### 2.4 VSC-HVDC Networks

The technical progress in VSC technology leads to an increasing demand for this converter type in HVDC applications. Thus, the need for understandable test philosophies, useful test procedures and reasonable acceptance criteria for VSC technology in HVDC arose [38].

### 2.4.1 Definition for HVDC Schemes

The scientific community in the form of academic publications has gained an interest in the field of HVDC links, where such adopted schemes are referred to as either *HVDC systems* or *HVDC*

*grids*. The whole area of research is literally at the moment missing a systematic terminology, as there are two existing areas merging: HVDC technology and AC electrical power systems. This can bring communication problems, given most of the terms in use do not have a unique and clear definition. A number of publications [8-14] have identified this lack of definitions and terminologies; particularly the North Sea Offshore and Storage Network initiative, which describes it as "*a definitions' barrier*" among power engineers and HVDC experts [33], [39-42].

In general, a HVDC link refers to an electrical network that utilizes high DC voltage and does not need to be purely based on DC systems [44]. It majorly includes power conversion through intermediate AC stages, but it cannot include AC transmission lines between AC nodes or areas. A network consisting of AC and DC transmission lines is a hybrid network [6]. To this definition, a distinction can be made between the two types of HVDC schemes.

A VSC-HVDC system is an autonomous HVDC link, which operates with a single DC high nominal voltage [22]. In a VSC-HVDC system, all busses are directly connected. Protection devices such as circuit breakers can be series-connected within the VSC-HVDC system, even though that is not principally a direct conductor interconnection. A VSC-HVDC system can only operate at a sole nominal voltage level, due to the direct conductor connection; likewise, a synchronous AC power system, which can only operate at a sole nominal frequency [13].

A VSC-HVDC grid is an interconnected HVDC scheme consisting of two or more VSC-HVDC systems, which can be referred to as sub-systems [6]. Dissimilar to VSC-HVDC systems, a VSC-HVDC grid does not require a direct conductor connection among all busses [22]. A VSC-HVDC grid can then operate at multiple voltage levels connected by power converters. Likewise to AC systems that can be observed when regarding interconnected AC grids consisting of several synchronous sub-systems, which operate at multiple nominal frequencies.

### 2.4.1.1 Short Circuit Behaviour in HVDC System vs. HVDC Grid

In case of a short-circuit takes place within the VSC-HVDC system, the voltage collapses in the entire HVDC system, if it was not prevented by a protection scheme, which quickly separates the faulty part from the healthy part. Thus, it is why large HVDC systems are essentially demanding

strict protection requirements. The short-circuit behaviour is one of the most relevant differences between HVDC systems and HVDC grids [14].

Upon a short-circuit presence within the VSC-HVDC grid, the voltage does not collapse in the entire HVDC grid, but only within the affected VSC-HVDC sub-system. This is why large VSC-HVDC grids do not necessarily entail as demanding requirements towards the protection system as large VSC-HVDC systems do [22]. However, it has been noticed in the literature that large multi-terminal VSC-HVDC systems can be referred to as VSC-HVDC grids. Nevertheless, it can generally be observed that the term VSC-HVDC system is mostly used for smaller welldefined VSC-HVDC links, while HVDC grid often refers to future larger VSC-HVDC schemes such as the envisioned European Super Grid that is depicted in Fig. 2-7 with various HVDC arrangements [5], [9].

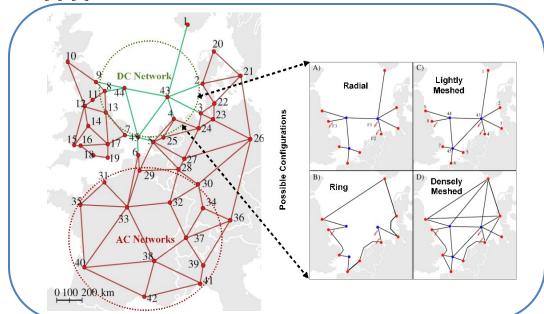

Figure 2-7: Future visualization of the European Supergrid with various suggested MTDC topologies

### 2.4.2 VSC-HVDC Architecture and Main Component

The typical construction of a VSC-based HVDC transmission system is presented in Fig. 2-8, which comprises VSCs, phase reactors, transformers, DC capacitors, AC filters and DC cables. The two main current and voltage ratings to be considered, when designing equipment; particularly converter transformers, can be expressed as  $I_L = \sqrt{3/2} I_{DC}$  and  $V_L = \frac{V_{DC}}{1.35}$ . Thus, the apparent power (S) of the transformer is  $S = \sqrt{3}I_LV_L$ . Terminals based on VSC can be

realized in many configurations, where the objective in the system's integration is to assure a bidirectional power flow [42].

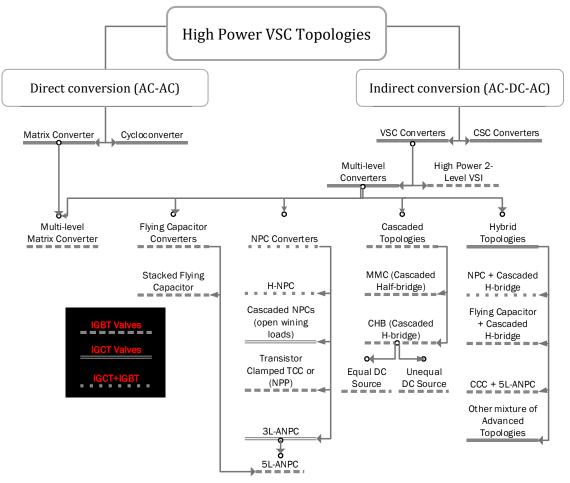

Figure 2-9: Various VSC-HVDC links arrangements

Fig. 2-9 summarizes the main VSC arrangements that a specific VSC-HVDC scheme can be resembled as, and it shows the broad freedom of assembling VSC terminals into a HVDC scheme. However, each configuration has its own functionalities; for example, back-to-back is usually considered to interconnect two asynchronous AC networks, whilst the bipolar is generally used for long distance applications [43]. Table. 2-1 reviews these configurations, comparing their functionalities, VSC terminal required, and availability during outages [3], [23], [25], [40], [44].

| Configuration <sup>[12-</sup><br>32]               | VSC<br>Requirements                             | Features                                                        | Boundaries                                                                                                          | Cable<br>Requirements                         | Availability                                                             |

|----------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------|

| Back to Back                                       | 1 x Rectifier<br>1 x Inverter<br>(At same site) | Simple, and operating<br>the links<br>independently             | No transmission of power with a DC-link <sup>[17]</sup>                                                             | N/A                                           | Zero during pole<br>outage                                               |

| Monopole<br>Earth/Sea<br>Return                    | 1 x Rectifier<br>1 x Inverter                   | Simple construction                                             | Issues with corrosion of<br>pipelines, production of<br>chlorine and ship<br>navigation                             | 1 x HVDC (plus<br>earth<br>electrode systems) | Zero output during<br>cable or pole<br>outages.                          |

| Monopole<br>Metallic<br>Return                     | 1 x Rectifier<br>1 x Inverter                   | Avoiding constant<br>current in Monopole<br>earth/sea return    | High transmission losses<br>(Higher resistance of the<br>metallic return path<br>compared with the earth<br>return) | 1 x HVDC<br>1 x LVDC                          | Zero output during<br>pole or cable<br>outages                           |

| Symmetric<br>Monopole                              | 1 x Rectifier,<br>1 x Inverter                  | Reliable configuration<br>for bulk power<br>transmission        | If a cable or converter is faulted then all transfer capability is lost.                                            | 2 x HVDC                                      | Zero output during<br>pole<br>or cable outages                           |

| Bipolar Metallic<br>Return (fully<br>rated return) | 2 x Rectifier,<br>2 x Inverter                  | Improve system reliability and outage of                        | Promising configuration<br>for future HVDC grids<br>but expensive <sup>[25]</sup>                                   | 2 x HVDC<br>1 x LVDC                          | Half capacity during<br>pole or cable<br>outages                         |

| Bipolar without<br>Metallic<br>Return              | 2 x Rectifier,<br>2 x Inverter                  | a conductor can be<br>tolerated (re-routing the<br>power)       | DC current flowing<br>through earth due to its<br>low resistance compared<br>to metallic return                     | 2 x HVDC                                      | Half capacity during<br>pole, but zero<br>output during cable<br>outages |

| Multi-terminal                                     | Multi                                           | Allow large amount of<br>power transmission,<br>highly scalable | Complex construction and control schemes                                                                            | Multi (can be<br>cables or/and<br>OHL)        | Dependent on the<br>network<br>arrangement                               |

Table 2-1: Comparison among the different VSC-HVDC configurations shown in Fig 2-9

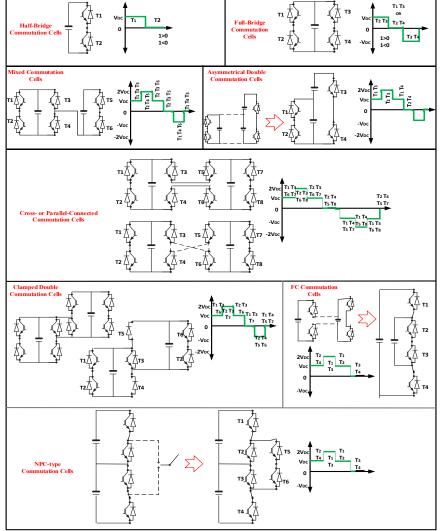

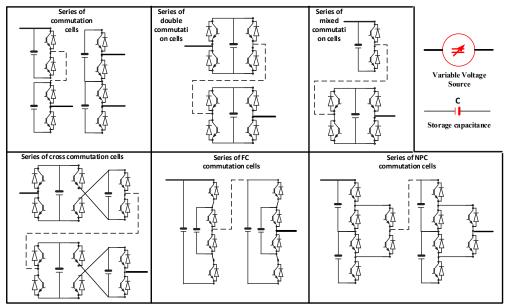

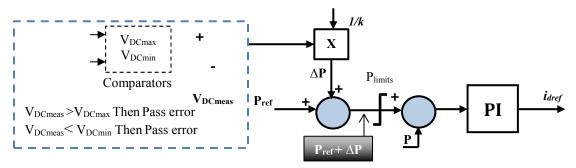

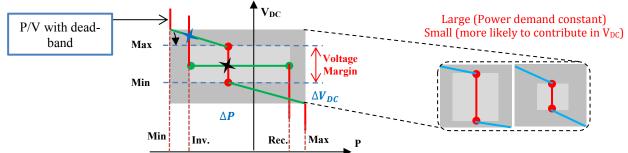

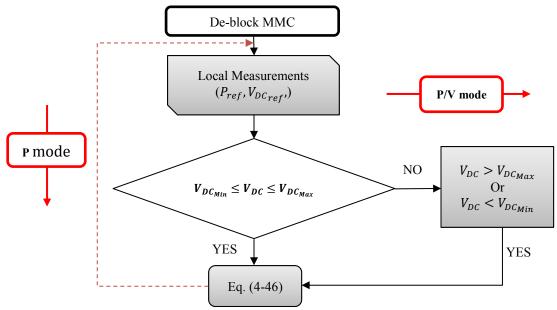

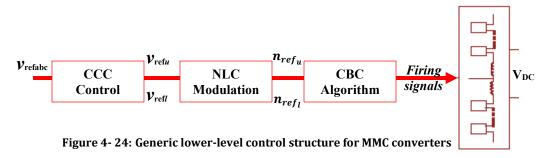

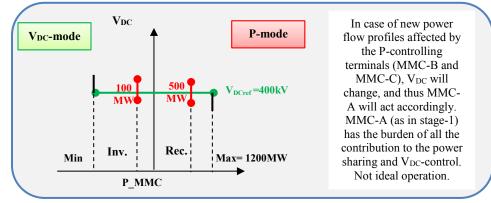

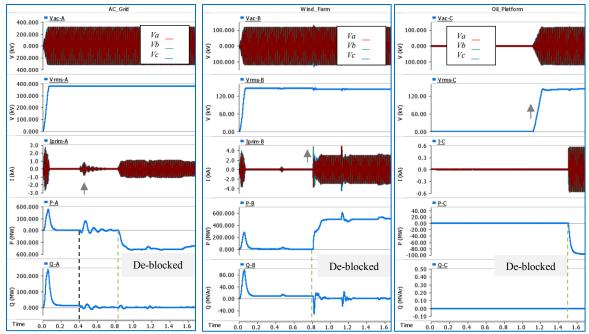

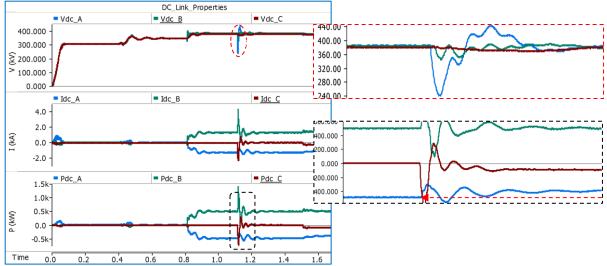

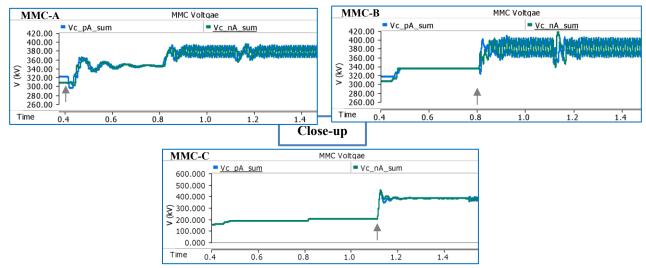

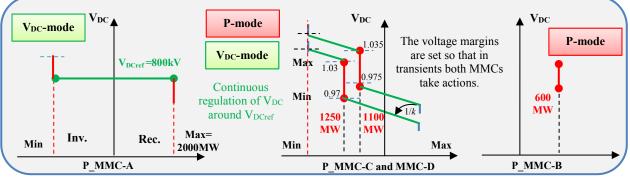

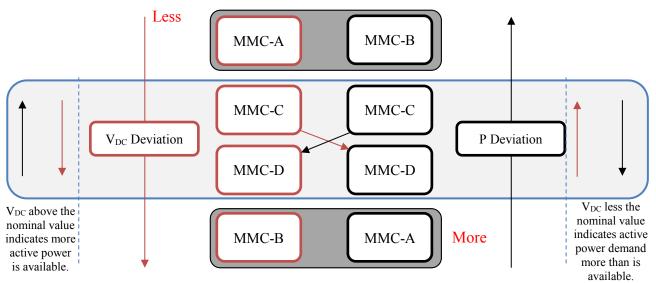

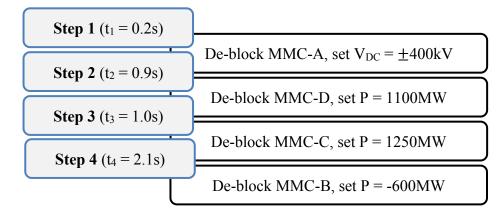

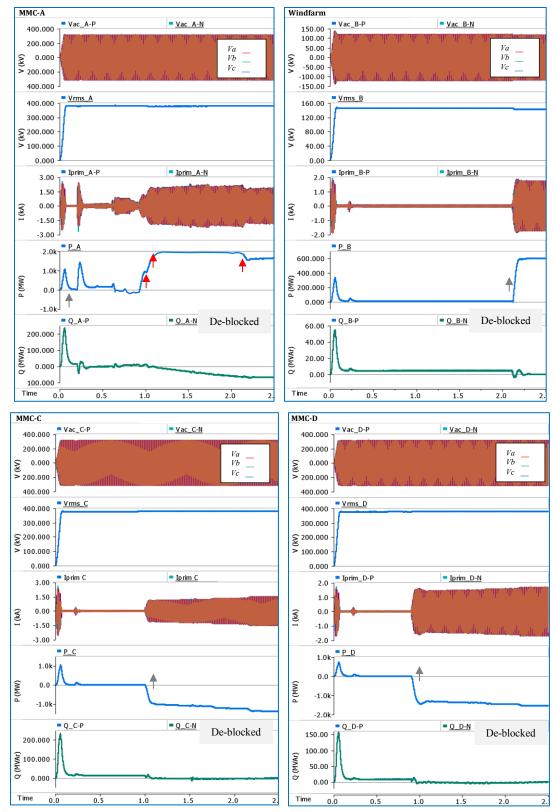

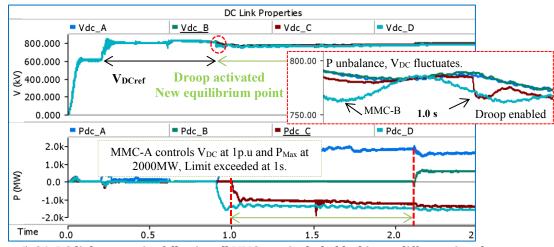

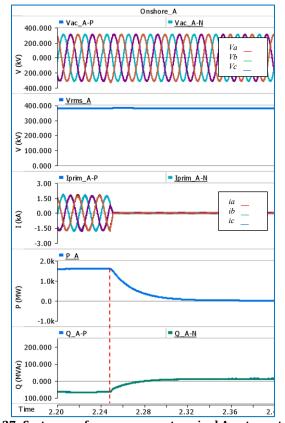

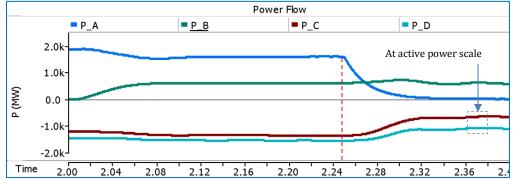

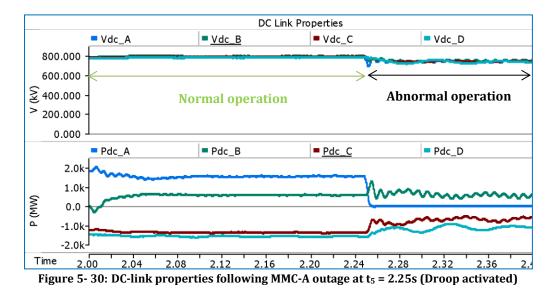

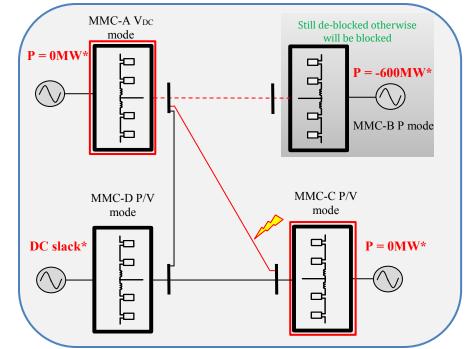

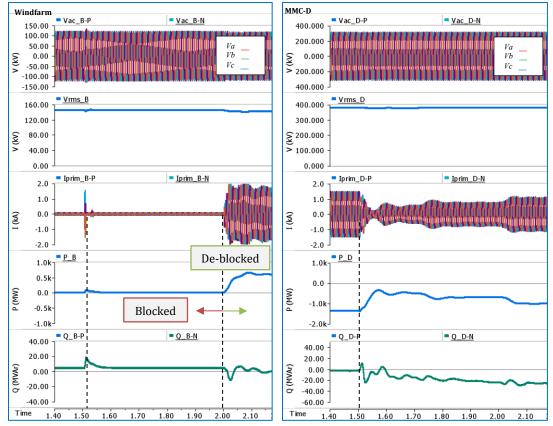

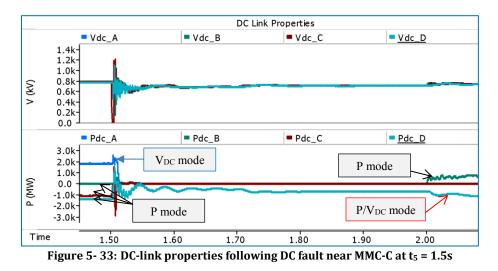

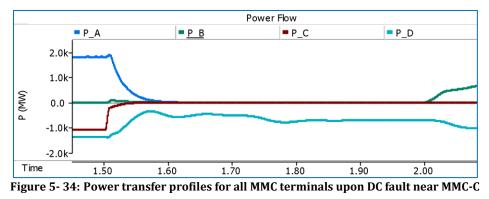

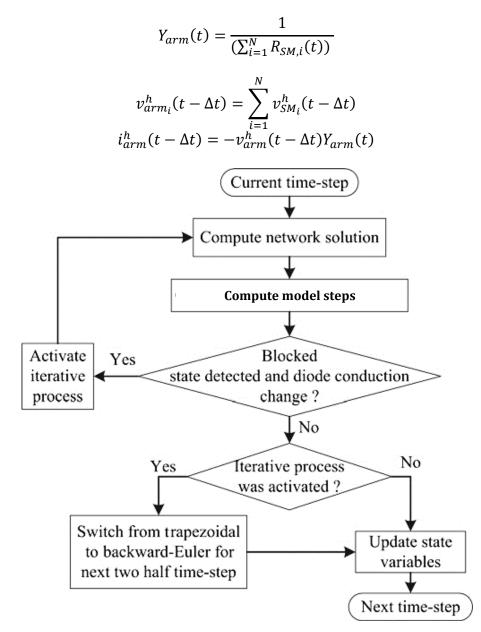

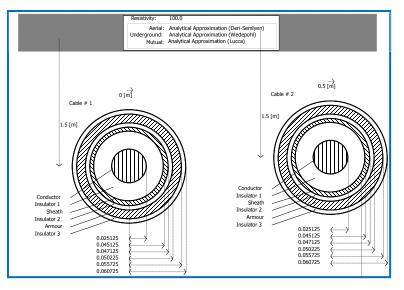

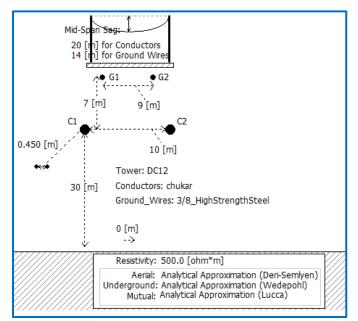

### 2.4.3 VS Cell Structure and VSC Topologies for HVDC Networks