**University of Alberta**

#### HIGH-SPEED ALIAS-LOCKED LOOP FREQUENCY SYNTHESIS

by

Leendert Jan van den Berg

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of **Master of Science**

in

**Computer, Microelectronic Devices, Circuits and Systems**

Department of Electrical and Computer Engineering

Edmonton, Alberta Fall 2008

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-55121-9 Our file Notre référence ISBN: 978-0-494-55121-9

#### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission. AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Canada

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant. We are at the very beginning of time for the human race. It is not unreasonable that we grapple with problems. But there are tens of thousands of years in the future. Our responsibility is to do what we can, learn what we can, improve the solutions, and pass them on.

- Richard Feynman

To Mom and Dad, and all ancestors who came before.

### Abstract

This work presents a divider-less frequency synthesis architecture called an aliaslocked loop. The division in the feedback path of the phase-locked loop (PLL) is modified by the addition of a latch that samples the local oscillator at a much lower frequency. Thus, rather than just performing frequency division, the local oscillator is sub-sampled, generating a lower-frequency aliased signal, which is utilized as in any standard PLL. Using a sampling latch rather than a divider significantly loosens the constraints placed on the feedback circuits. With a non-linear simulation model that describes the time-domain behaviour of our architecture, stable modes of operation with bounded orbits in phase-space are demonstrated. Simulations of an implementation in 90-nm CMOS technology confirm the feasibility of the aliasing approach. In noise and offset free circuit simulations of sampling latches using a 90-nm CMOS process, we demonstrate successful sub-sampling of a 230 GHz signal, which is greater than  $f_{max}$ .

### Acknowledgements

The research presented here has been supported by the Natural Sciences and Engineering Research Council of Canada (NSERC), CMC Microsystems and the University of Alberta.

First of all, I would like thank my supervisor, Dr. Duncan Elliott, for his advice, guidance, and continuous support during my research. His unusually astute insights into the engineering of various electronic systems and circuits have shown me how to look at design challenges from a new perspective. Additionally, I appreciate the freedom granted to me during my studies, which have enriched my experience by allowing me to be involved in various projects not related to my thesis topic.

Additionally, I would like to thank the professors that have shaped the atmosphere of the lab into a stimulating and welcoming environment with ample opportunities for collaboration: Dr. Bruce Cockburn, Dr. Vincent Gaudet, and Dr. Stephen Bates.

I also wish to thank all the individuals that have been part of the VLSI and HDCD labs for their friendship and camaraderie, including: John Koob, Tyler Brandon, Ramkrishna Swamy, Maziyar Khorasani, Dr. Amirhossein Alimohammad, Saeed Fouladi Fard, Wesam Al-Haddad, Anthony Ho, and Russell Dodd.

Finally, I wish to thank my parents and sibblings for their unconditional love and support independent of my achievements and choices in life.

## **Table of Contents**

| 1 | Introduction |         |                                                  |

|---|--------------|---------|--------------------------------------------------|

|   | 1.1          | I nesis | Organization                                     |

| 2 | Bacl         | kground |                                                  |

|   | 2.1          | Overvi  | ew                                               |

|   | 2.2          | Freque  | ncy Synthesizer History                          |

|   | 2.3          | Freque  | ncy Synthesizer Properties                       |

|   |              | 2.3.1   | Tuning Range                                     |

|   |              | 2.3.2   | Settling Time                                    |

|   |              | 2.3.3   | Output Signal Statistics                         |

|   |              |         | 2.3.3.1 Time Domain                              |

|   |              |         | 2.3.3.2 Frequency Domain                         |

|   |              | 2.3.4   | Other Concerns                                   |

|   | 2.4          | Freque  | ncy Synthesis Methods                            |

|   |              | 2.4.1   | Direct Synthesis                                 |

|   |              |         | 2.4.1.1 Direct Analog Synthesis                  |

|   |              |         | 2.4.1.2 Direct Digital Synthesis                 |

|   |              | 2.4.2   | Indirect Synthesis                               |

|   |              |         | 2.4.2.1 Delay-Locked Loop Frequency Synthesis 14 |

|   |              |         | 2.4.2.2 Phase-Locked Loop Frequency Synthesis 16 |

|   |              | 2.4.3   | Hybrid Frequency Synthesis                       |

|   | 2.5          | Phase-  | Locked Loop Implementation                       |

|   |              | 2.5.1   | Common Building Blocks                           |

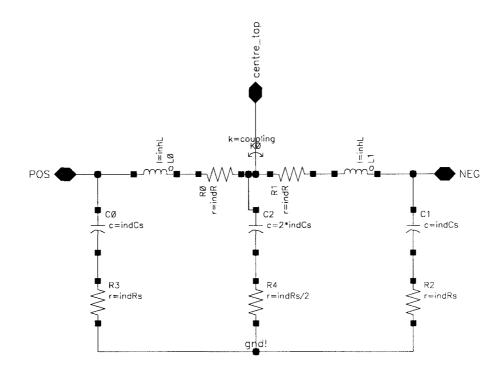

|   |              |         | 2.5.1.1 Oscillator                               |

|   |              |         | 2.5.1.2 Phase Comparator                         |

|   |              |         | 2.5.1.3 Loop Filter                              |

|   |              |         | 2.5.1.4 Feedback Divider                         |

|   | 2.6          | Aliasir | ng                                               |

|   |              | 2.6.1   | Previous Subsampling Architectures               |

|   | 2.7          | Curren  | t High-Frequency Synthesis Methods               |

|   |              | 2.7.1   | Direct Analog and Hybrid Systems                 |

|   |              | 2.7.2   | PLL Only                                         |

|   | 2.8          | Summ    |                                                  |

| 3 | Alia | s-Locke | ed Loop Architecture                         | 28 |

|---|------|---------|----------------------------------------------|----|

|   | 3.1  | Overvi  | iew                                          | 28 |

|   | 3.2  | Propos  | sed Architecture                             | 28 |

|   |      | 3.2.1   | Alias-Locked Loop Frequency Synthesis        | 29 |

|   |      | 3.2.2   | Implications                                 | 31 |

|   |      |         | 3.2.2.1 Feedback Signal Time Discretization  | 32 |

|   |      |         | 3.2.2.2 VCO Frequency Determination          | 34 |

|   |      |         | 3.2.2.3 Loop Filter Design                   | 35 |

|   |      | 3.2.3   | Variations                                   | 35 |

|   |      |         | 3.2.3.1 Sampler and Divider in Feedback Path | 36 |

|   |      |         | 3.2.3.2 Multiple Sample Frequencies          | 37 |

|   |      |         | 3.2.3.3 Digital Phase-Error Processing       | 37 |

|   | 3.3  | Sampl   | ing Circuit Requirements                     | 38 |

|   |      | 3.3.1   | Sampling Latch Properties                    | 39 |

|   |      | 3.3.2   | Duty Cycle Correction                        | 40 |

|   |      |         | 3.3.2.1 Duty Cycle Measurement Algorithm     | 41 |

|   | 3.4  | Summ    | ary                                          | 42 |

|   |      |         |                                              |    |

| 4 |      | -       | rcuit Design and Simulation                  | 43 |

|   | 4.1  | Overvi  |                                              | 43 |

|   | 4.2  | Latch   | Circuits                                     | 43 |

|   |      | 4.2.1   | Latch Performance Evaluation Methodology     | 44 |

|   |      |         | 4.2.1.1 Maximum Frequency Test               | 44 |

|   |      |         | 4.2.1.2 Latch Sensitivity Function Analysis  | 46 |

|   |      | 4.2.2   | Standard Cell D Flip-Flop                    | 48 |

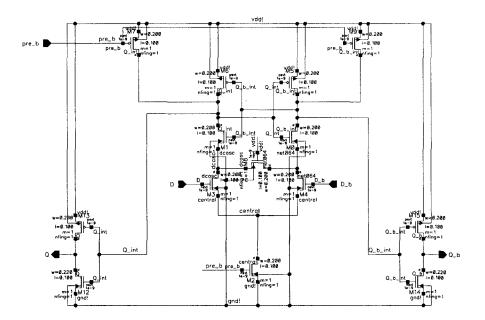

|   |      |         | 4.2.2.1 Circuit Design                       | 48 |

|   |      |         | 4.2.2.2 Circuit Simulation                   | 49 |

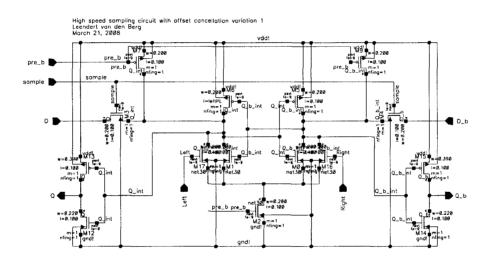

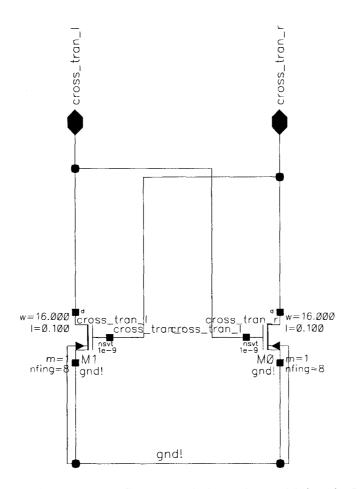

|   |      | 4.2.3   | Differential Pass-Transistor Pulsed Latch    | 51 |

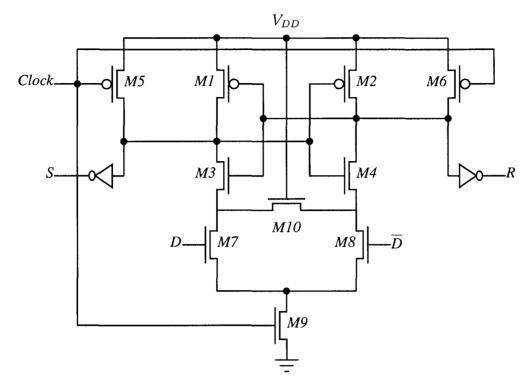

|   |      |         | 4.2.3.1 Circuit Design                       | 52 |

|   |      |         | 4.2.3.2 Circuit Simulation                   | 52 |

|   |      |         | 4.2.3.3 Latch Hysteresis Buffer              | 55 |

|   |      | 4.2.4   | Sense-Amplifying Latch Circuit               | 58 |

|   |      |         | 4.2.4.1 Circuit Design                       | 58 |

|   |      |         | 4.2.4.2 Circuit Simulation                   | 58 |

|   |      | 4.2.5   | Latch Simulation Results Summary             | 61 |

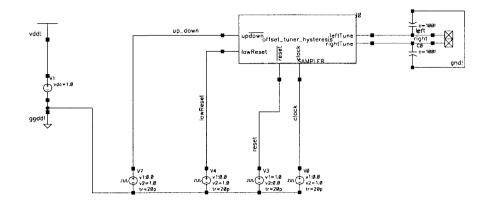

|   | 4.3  | Input 7 | Threshold Correction                         | 61 |

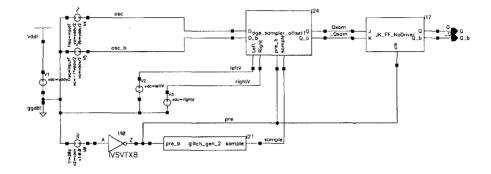

|   |      | 4.3.1   | Circuit Design                               | 62 |

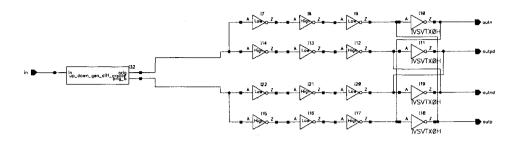

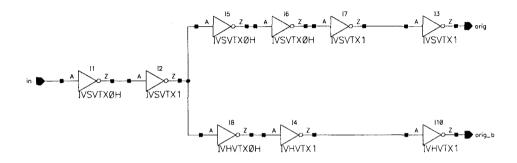

|   |      |         | 4.3.1.1 Duty-Cycle Tolerance Circuit         | 65 |

|   |      | 4.3.2   | Circuit Simulation                           | 67 |

|   | 4.4  | Summ    | nary                                         | 70 |

| 5  | Ana         | lysis and System Simulation Results                       | 72  |

|----|-------------|-----------------------------------------------------------|-----|

|    | 5.1         | Overview                                                  | 72  |

|    | 5.2         | Non-Linear Model                                          | 72  |

|    |             | 5.2.1 Model Assumptions                                   | 73  |

|    |             | 5.2.2 Model Description                                   | 73  |

|    | 5.3         | Non-Linear Model Simulation                               | 77  |

|    |             | 5.3.1 Jitter and Phase Noise                              | 82  |

|    |             | 5.3.2 Impact of Sample and Reference Signals Choices      | 84  |

|    |             | 5.3.2.1 Increasing the Sampling Clock Frequency           | 85  |

|    |             | 5.3.2.2 Non-Integer Ratio of Sample and Reference Clock   |     |

|    |             | Frequencies                                               | 85  |

|    |             | 5.3.2.3 Subsampling and Frequency Division                | 86  |

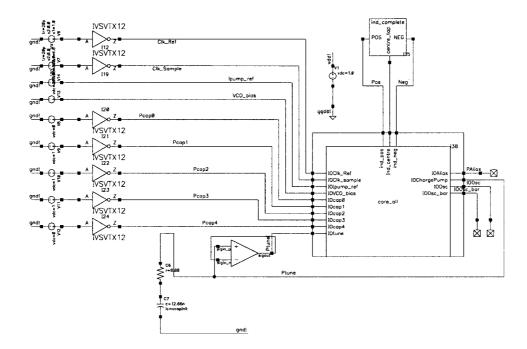

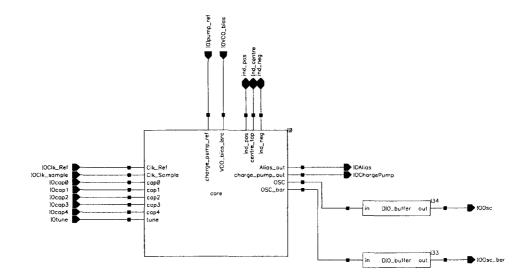

|    | 5.4         | 90-nm CMOS Implementation                                 | 88  |

|    |             | 5.4.1 90-nm Simulation Versus Non-Linear Model            | 88  |

|    |             | 5.4.2 90-nm Pull-In Simulation                            | 91  |

|    | 5.5         | Summary                                                   | 92  |

| 6  | Con         | clusion                                                   | 94  |

| U  | 6.1         | Accomplishments                                           | 95  |

|    | 6.2         | Future Work                                               | 95  |

|    | 0.2         |                                                           | ))  |

| Bi | bliogr      | raphy                                                     | 98  |

| Α  | Spic        | e Circuit Simulation Settings                             | 104 |

|    | A.1         | Sample Circuit Simulations                                | 104 |

|    | A.2         | Duty Cycle Detection Simulation                           | 105 |

|    | A.3         | 90-nm ALL model                                           | 106 |

| в  | Som         | rce Code                                                  | 108 |

| -  | B.1         | Alias-Locked Loop Simulation Program                      |     |

|    | B.2         | Alias-Locked Loop Histogram Generation Program            |     |

|    | B.3         | Latch Sensitivity Plot Generation Program                 |     |

|    | B.4         | Latch Sampling Window Sensitivity Plot Generation Program |     |

| C  | Cim         | wit Discusses for 00 nm Implementation                    | 121 |

| С  | Circ<br>C.1 |                                                           |     |

|    |             | Latches and Latch Test Benches                            |     |

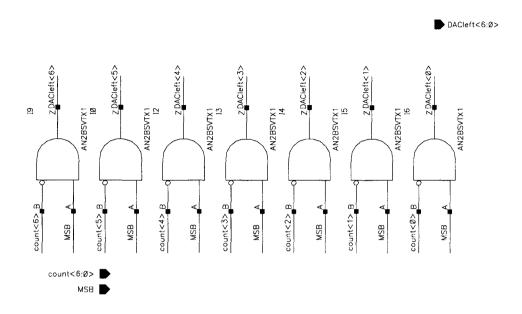

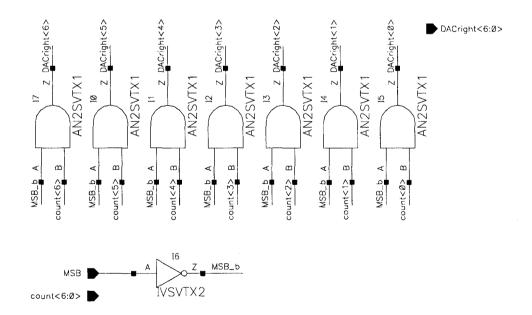

|    | C.2<br>C.3  | Latch Threshold Correction and Detection Circuits         |     |

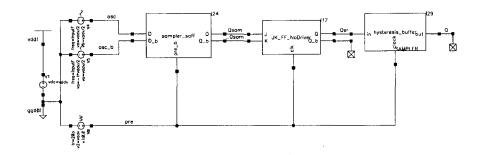

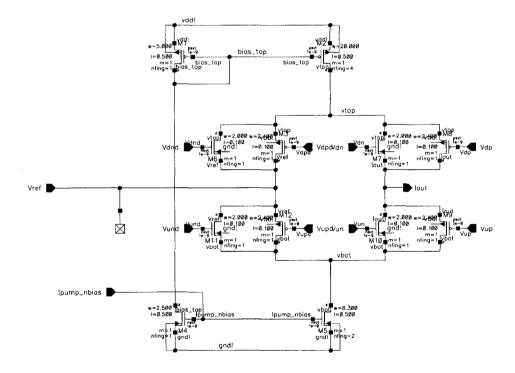

|    | C.3         | 90-nm CMOS ALL Circuit Implementation                     | 149 |

## **List of Tables**

| 2.1        | Comparison of fastest VCOs and frequency dividers in the litera-<br>ture, given as maximum operating frequency (GHz) |

|------------|----------------------------------------------------------------------------------------------------------------------|

| 4.1        | Maximum input frequencies for latch designs 61                                                                       |

| A.2<br>A.3 | Latch circuit transient noise simulation settings                                                                    |

# **List of Figures**

| 2.1       Illustrative power spectral density plot of an oscillator       9         2.2       A direct analog synthesis system block diagram, based on [1]       12         2.3       High-level direct digital synthesis architecture block diagram       12         2.4       Block diagram of a tapped delay-line delay-locked loop frequency multiplier       15         2.5       Block diagram of a multiplying delay-locked loop       16         2.6       Block diagram of a frequency synthesis phase-locked loop       17         2.7       Phase-frequency detector circuit       21         2.8       Graphical illustration of oversampling, showing the original signal, double oversampling impulse train and reconstructed signal       23         2.9       Graphical illustration of subsampling, showing the original signal, subsampling impulse train and reconstructed signal       30         3.2       Graphical illustration of binary sampling, showing the original signal, subsampling impulse train and binary aliased signal       32         3.3       Graphical illustration of binary sampling, showing the original signal, subsampling impulse train and binary aliased signal       33         3.4       Block diagram of a test bench for a sampling latch       44         4.2       Standerd cell master-slave D flip-flop circuit       49         4.3       Alias signal for standard cell D flip-flop subsampling simulation with a 13.01 GHz s     |   |      |                                                                      |   |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|----------------------------------------------------------------------|---|-----|

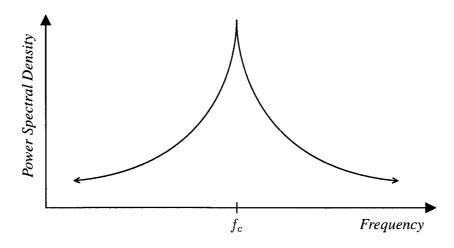

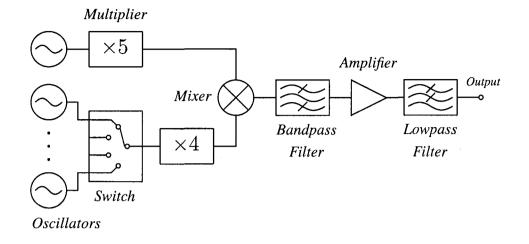

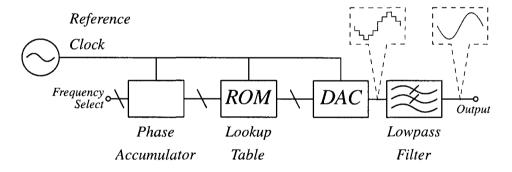

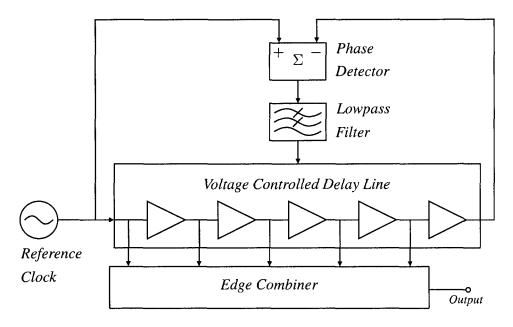

| <ul> <li>2.3 High-level direct digital synthesis architecture block diagram</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2 | 2.1  | Illustrative power spectral density plot of an oscillator            |   | 9   |

| <ul> <li>2.4 Block diagram of a tapped delay-line delay-locked loop frequency multiplier</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2 | 2.2  | A direct analog synthesis system block diagram, based on [1]         |   | 12  |

| multiplier       15         2.5       Block diagram for a multiplying delay-locked loop       16         2.6       Block diagram of a frequency synthesis phase-locked loop       17         2.7       Phase-frequency detector circuit       21         2.8       Graphical illustration of oversampling, showing the original signal, double oversampling impulse train and reconstructed signal       23         2.9       Graphical illustration of subsampling, showing the original signal, subsampling impulse train and reconstructed signal       24         3.1       Block diagram of a frequency synthesis alias-locked loop       30         3.2       Graphical illustration of binary sampling, showing the original signal, subsampling impulse train and binary aliased signal       32         3.3       Graphical illustration of binary sampling, showing the original signal, subsampling impulse train and binary aliased signal       32         3.3       Graphical illustration of binary sampling, showing the original signal, subsampling impulse train and binary aliased signal       33         3.4       Block diagram of a test bench for a sampling latch       44         4.2       Standerd cell master-slave D flip-flop circuit       49         4.3       Alias signal for standard cell D flip-flop subsampling simulation with a 13.0 Graphical signal sampled at 1 GHz       50         4.4       Alias signal for standard cell D flip-flop       < | 2 | 2.3  | High-level direct digital synthesis architecture block diagram       |   | 12  |

| <ul> <li>2.5 Block diagram for a multiplying delay-locked loop</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2 | 2.4  | Block diagram of a tapped delay-line delay-locked loop frequency     |   |     |

| <ul> <li>2.6 Block diagram of a frequency synthesis phase-locked loop</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |      | multiplier                                                           |   | 15  |

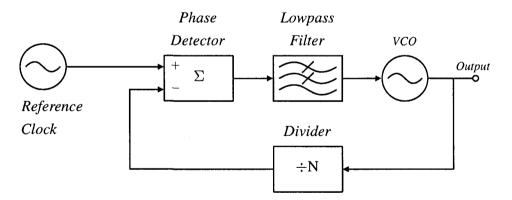

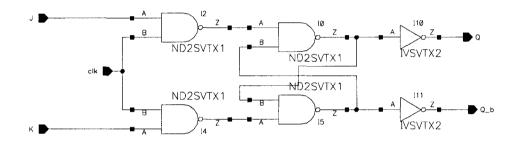

| <ul> <li>2.7 Phase-frequency detector circuit</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2 | 2.5  | Block diagram for a multiplying delay-locked loop                    |   | 16  |

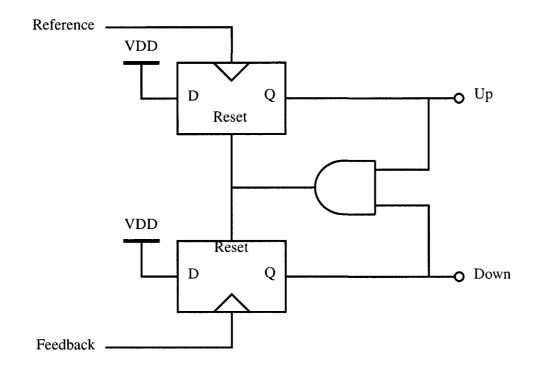

| <ul> <li>2.7 Phase-frequency detector circuit</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2 | 2.6  |                                                                      |   | 17  |

| double oversampling impulse train and reconstructed signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2 | 2.7  |                                                                      | 2 | 21  |

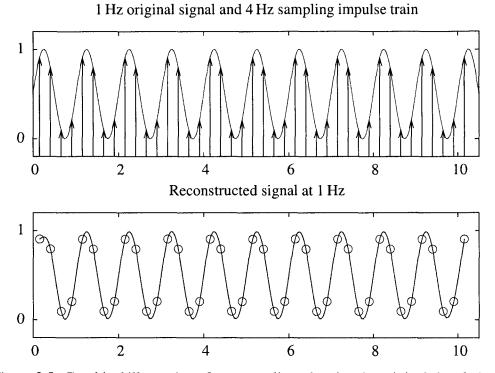

| double oversampling impulse train and reconstructed signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2 | 2.8  | Graphical illustration of oversampling, showing the original signal, |   |     |

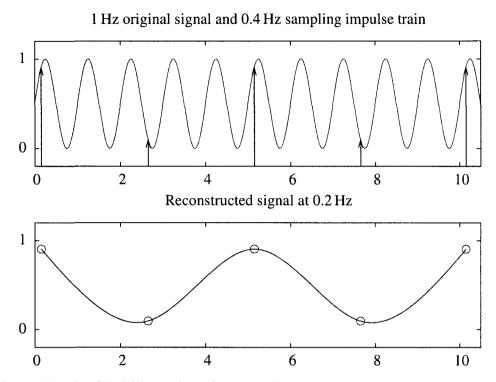

| <ul> <li>2.9 Graphical illustration of subsampling, showing the original signal, subsampling impulse train and reconstructed signal</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |      |                                                                      |   | 23. |

| subsampling impulse train and reconstructed signal       24         3.1       Block diagram of a frequency synthesis alias-locked loop       30         3.2       Graphical illustration of binary sampling, showing the original signal, subsampling impulse train and binary aliased signal       32         3.3       Graphical illustration of binary sampling, showing the original signal, subsampling impulse train and binary aliased signal       32         3.3       Graphical illustration of binary sampling, showing the original signal, subsampling impulse train and binary aliased signal       33         3.4       Block diagram of a modified frequency synthesis alias-locked loop       36         4.1       Block diagram of a test bench for a sampling latch       44         4.2       Standerd cell master-slave D flip-flop circuit       49         4.3       Alias signal for standerd cell D flip-flop subsampling simulation with a 13.1 GHz sinusoidal signal sampled at 1 GHz       49         4.4       Alias signal for standard cell D flip-flop       50         4.5       Latch sensitivity plot for standard cell D flip-flop       51         4.6       Latch sampling window plot for standard cell D flip-flop       51         4.7       Differential pass-transistor pulsed latch circuit       53         4.8       Pulse generator circuit for pulsed latch       54         4.9       Toggling alias s                                        | 2 | 2.9  |                                                                      |   |     |

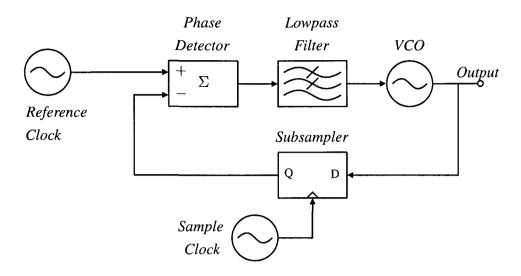

| <ul> <li>3.1 Block diagram of a frequency synthesis alias-locked loop 30</li> <li>3.2 Graphical illustration of binary sampling, showing the original signal, subsampling impulse train and binary aliased signal</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      |                                                                      | 2 | 24  |

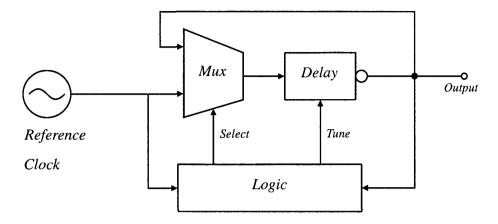

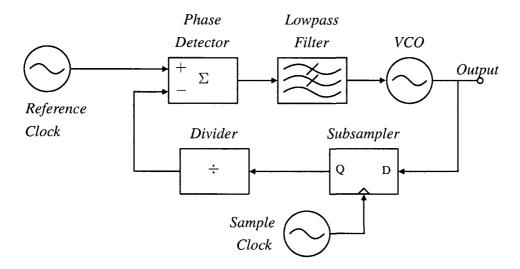

| <ul> <li>3.2 Graphical illustration of binary sampling, showing the original signal, subsampling impulse train and binary aliased signal</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |      |                                                                      |   |     |

| <ul> <li>nal, subsampling impulse train and binary aliased signal</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      |                                                                      |   | 30  |

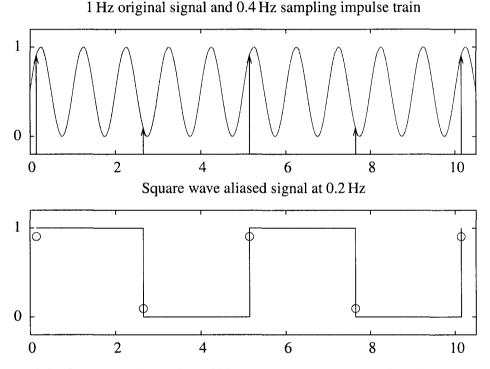

| <ul> <li>3.3 Graphical illustration of binary sampling, showing the original signal, subsampling impulse train and binary aliased signal</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3 | 3.2  |                                                                      |   |     |

| <ul> <li>nal, subsampling impulse train and binary aliased signal</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _ |      |                                                                      |   | 32  |

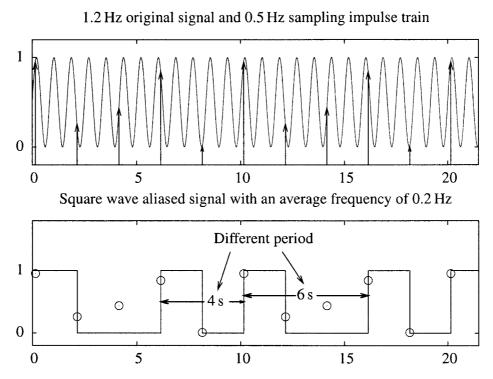

| <ul> <li>3.4 Block diagram of a modified frequency synthesis alias-locked loop 36</li> <li>4.1 Block diagram of a test bench for a sampling latch</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3 | 3.3  |                                                                      |   |     |

| <ul> <li>4.1 Block diagram of a test bench for a sampling latch</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |      |                                                                      |   |     |

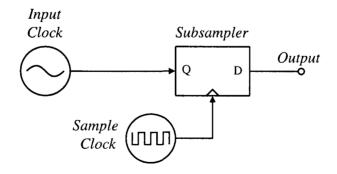

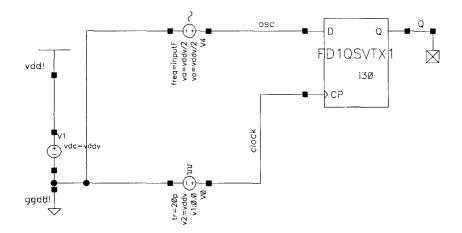

| <ul> <li>4.2 Standerd cell master-slave D flip-flop circuit</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3 | 3.4  | Block diagram of a modified frequency synthesis alias-locked loop    |   | 36  |

| <ul> <li>4.2 Standerd cell master-slave D flip-flop circuit</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4 | 4.1  | Block diagram of a test bench for a sampling latch                   | 4 | 44  |

| <ul> <li>4.3 Alias signal for standerd cell D flip-flop subsampling simulation with a 13.1 GHz sinusoidal signal sampled at 1 GHz</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      |                                                                      |   |     |

| <ul> <li>with a 13.1 GHz sinusoidal signal sampled at 1 GHz</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |      |                                                                      |   |     |

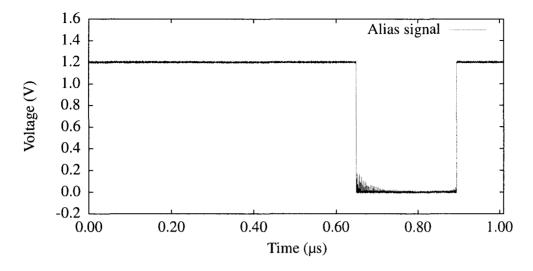

| <ul> <li>4.4 Alias signal for standard cell D flip-flop subsampling simulation with a 13.001 GHz sinusoidal signal sampled at 1 GHz 50</li> <li>4.5 Latch sensitivity plot for standard cell D flip-flop 51</li> <li>4.6 Latch sampling window plot for standard cell D flip-flop</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      |                                                                      | 4 | 49  |

| <ul> <li>with a 13.001 GHz sinusoidal signal sampled at 1 GHz</li> <li>4.5 Latch sensitivity plot for standard cell D flip-flop</li> <li>4.6 Latch sampling window plot for standard cell D flip-flop</li> <li>51</li> <li>4.7 Differential pass-transistor pulsed latch circuit</li> <li>53</li> <li>4.8 Pulse generator circuit for pulsed latch</li> <li>54</li> <li>4.9 Toggling alias signal at the switching threshold of a DPTPL subsampling circuit, simulated with transient noise and a 58.001 GHz</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4 | 1.4  |                                                                      |   |     |

| <ul> <li>4.5 Latch sensitivity plot for standard cell D flip-flop</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      |                                                                      |   | 50  |

| <ul> <li>4.6 Latch sampling window plot for standard cell D flip-flop 51</li> <li>4.7 Differential pass-transistor pulsed latch circuit</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4 | 1.5  |                                                                      |   |     |

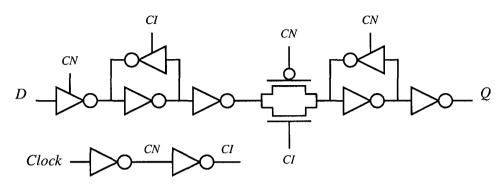

| <ul> <li>4.7 Differential pass-transistor pulsed latch circuit</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4 |      |                                                                      |   | 51  |

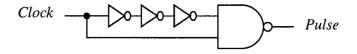

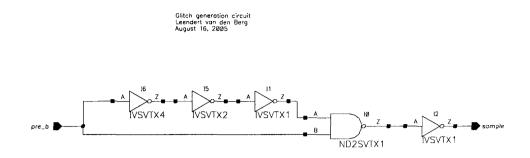

| <ul> <li>4.8 Pulse generator circuit for pulsed latch</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4 |      |                                                                      |   |     |

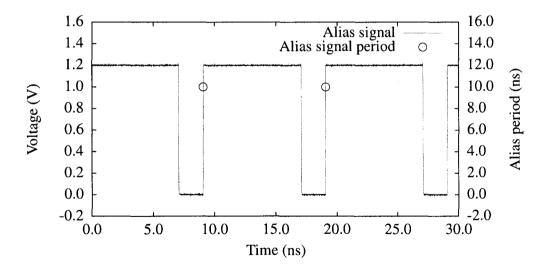

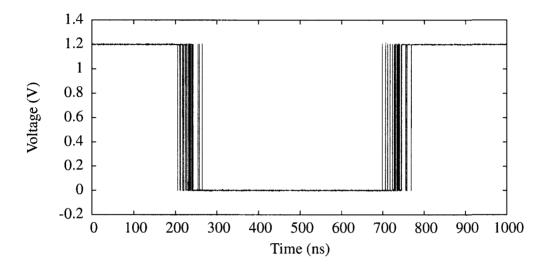

| 4.9 Toggling alias signal at the switching threshold of a DPTPL sub-<br>sampling circuit, simulated with transient noise and a 58.001 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4 | 1.8  |                                                                      |   | 54  |

| sampling circuit, simulated with transient noise and a 58.001 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4 | 1.9  |                                                                      |   |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |      |                                                                      |   |     |

| sinusoidal input signal sampled at 1 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |      | sinusoidal input signal sampled at 1 GHz                             | 1 | 54  |

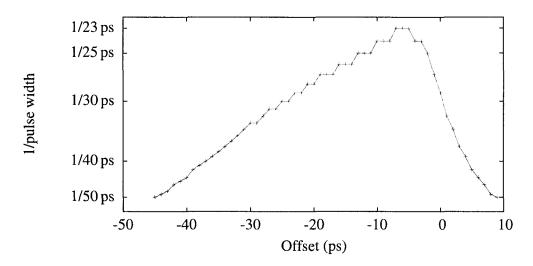

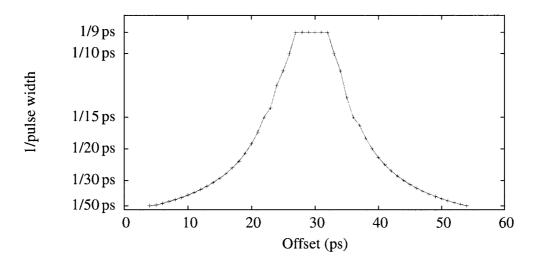

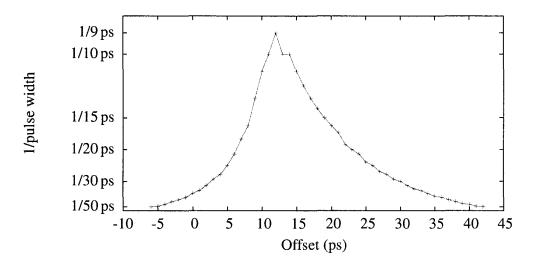

| 4.10 Latch sensitivity plot for DPTPL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4 | 4.10 |                                                                      |   | 55  |

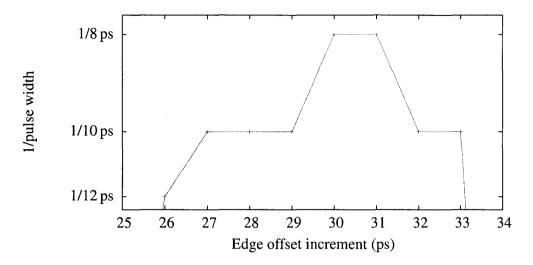

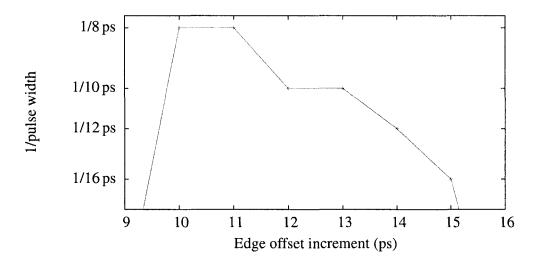

| 4.11 Latch sampling window plot for DPTPL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |      |                                                                      |   | 56  |

| 4.12        | Hysteresis buffer for sampling latches.                                 | 57   |

|-------------|-------------------------------------------------------------------------|------|

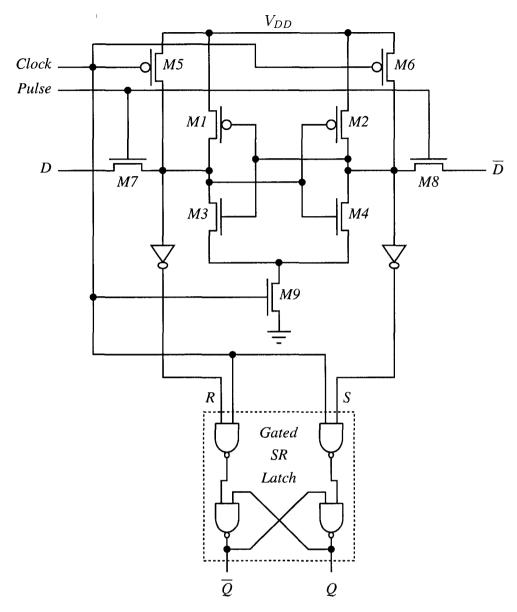

| 4.13        | Sense-Amplifying Flip-Flop                                              | 59   |

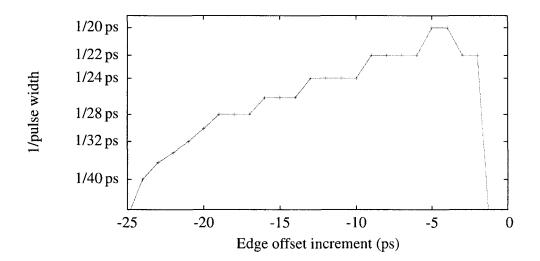

| 4.14        | Latch sensitivity plot for SAFF                                         | 60   |

| 4.15        | Latch sampling window plot for SAFF                                     | 60   |

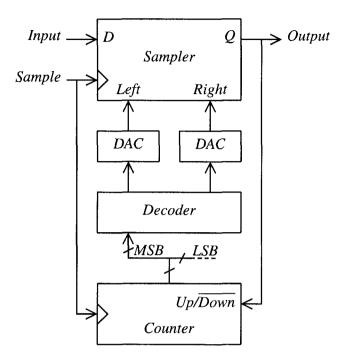

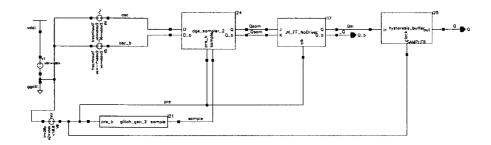

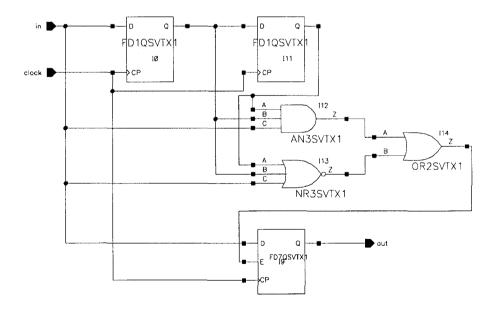

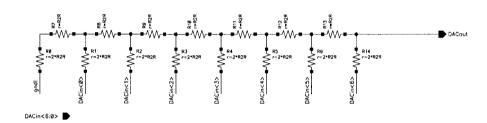

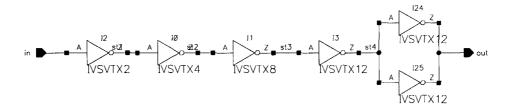

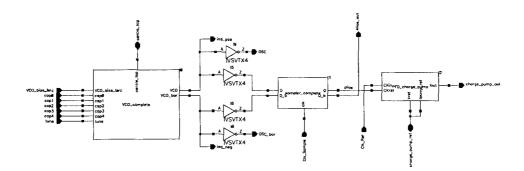

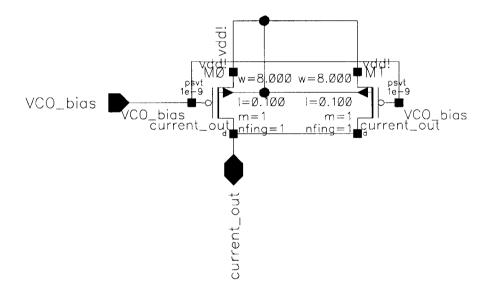

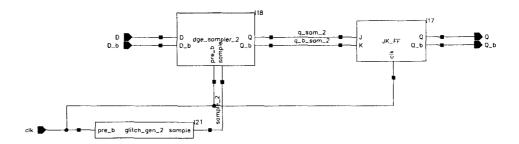

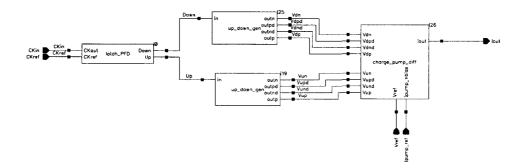

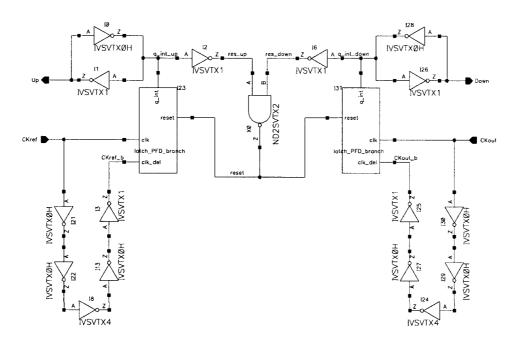

|             | Block diagram of basic duty cycle correction system                     | 63   |

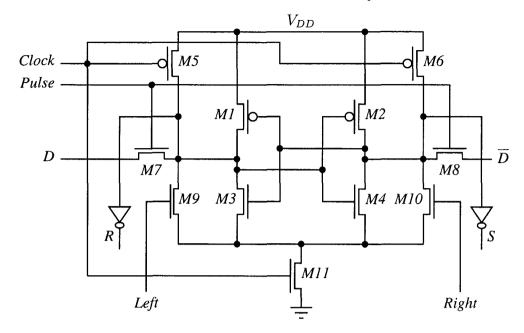

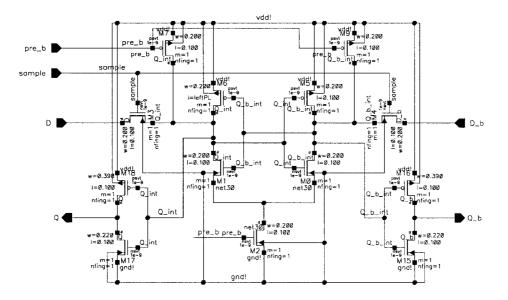

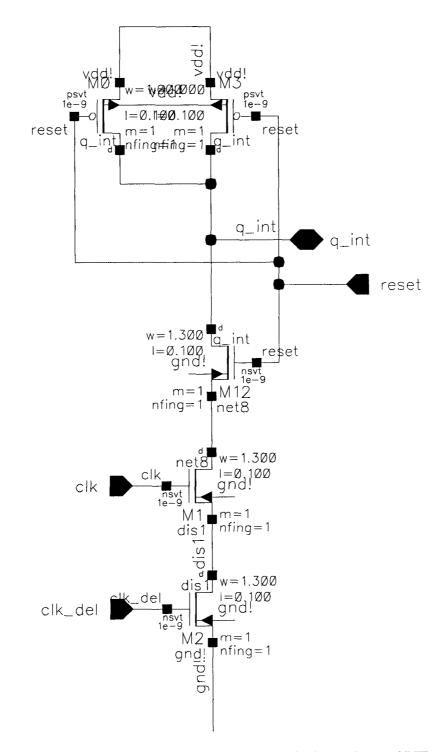

| 4.17        | Differential pass-transistor pulsed latch circuit with input threshold  |      |

|             | correction transistors                                                  | 64   |

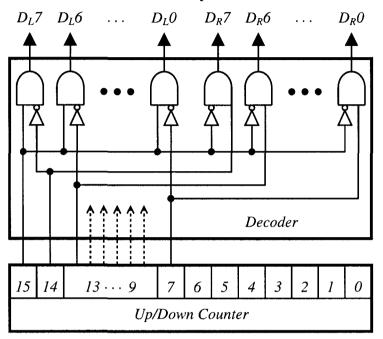

| 4.18        | Block diagram of decoder circuit with up/down counter                   | 65   |

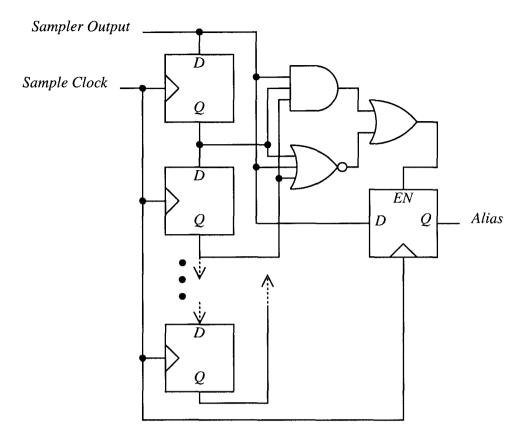

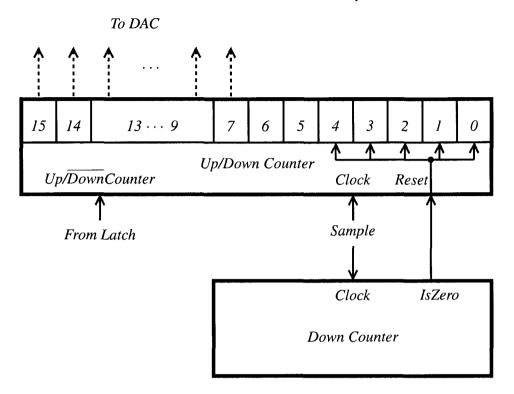

| 4.19        | Block diagram of duty cycle detector with periodic reset                | 66   |

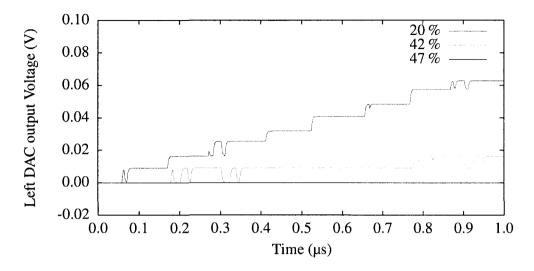

| 4.20        | Left DAC output voltage versus time for various duty cycle input        |      |

|             | signals                                                                 | 69   |

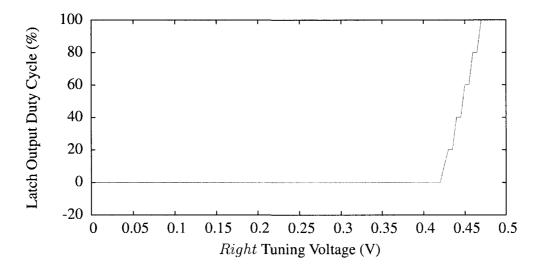

| 4.21        | Mismatched DPTPL duty cycle versus applied offset correction volt-      |      |

|             | age with a 150.1 GHz input signal                                       | 70   |

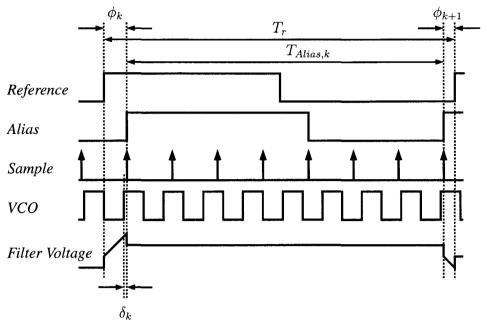

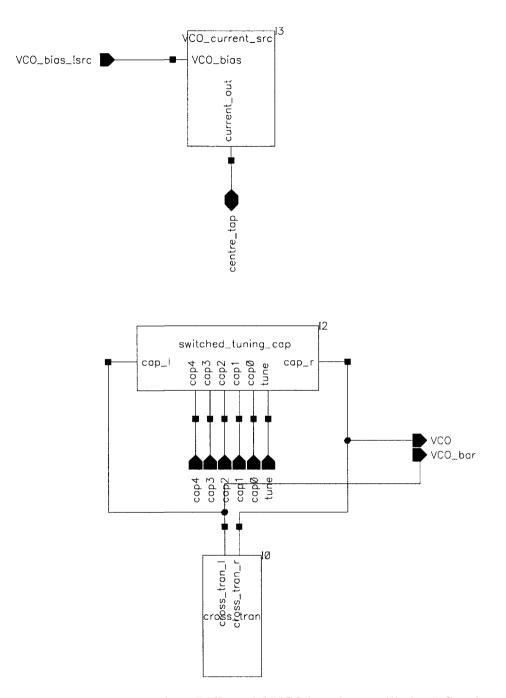

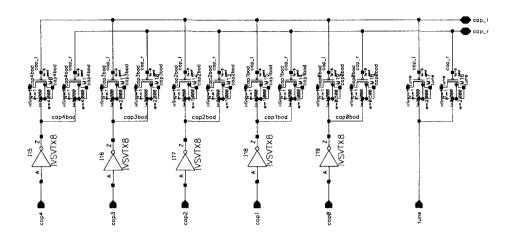

| 5.1         | Alias looked loop timing for non-linear model                           | 74   |

|             | Alias-locked loop timing for non-linear model                           |      |

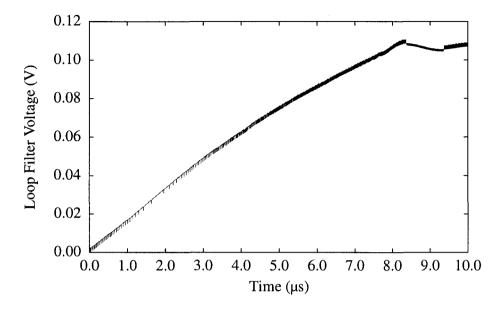

| 5.2         | Low-pass Filter Waveform                                                | 77   |

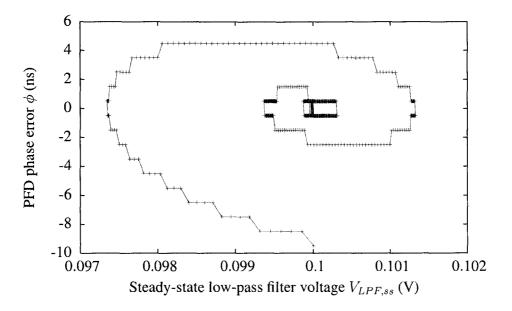

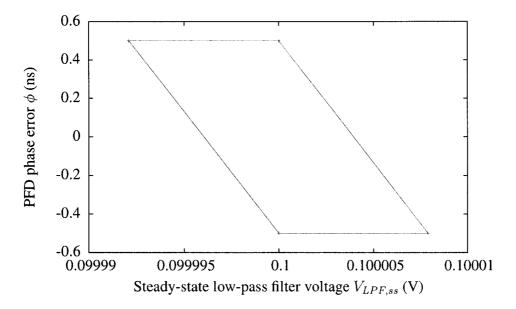

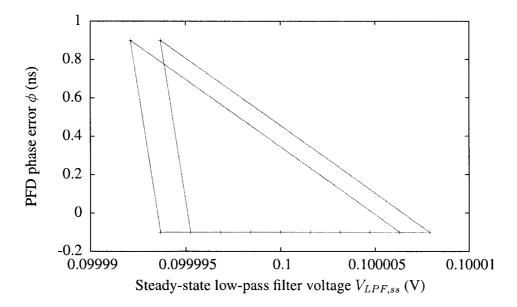

| 5.3         | Phase-space diagram of PFD phase error $\phi$ and the steady-state loop | 70   |

| 5 1         | filter voltage with a -9.5 ns initial phase-error                       | 78   |

| 5.4         | Phase-space diagram of PFD phase error $\phi$ and the steady-state loop | 70   |

|             | filter voltage with a -0.5 ns initial phase-error                       | 79   |

| 5.5         | Phase-space diagram of PFD phase error $\phi$ and the steady-state loop | 70   |

| = (         | filter voltage with a -0.1 ns initial phase-error                       | 79   |

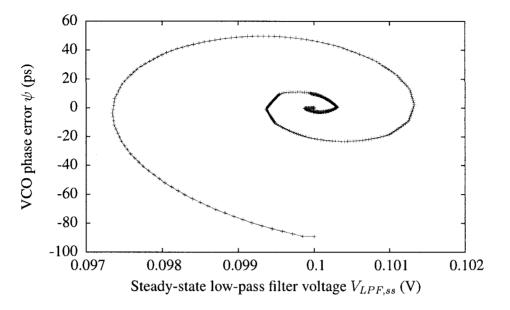

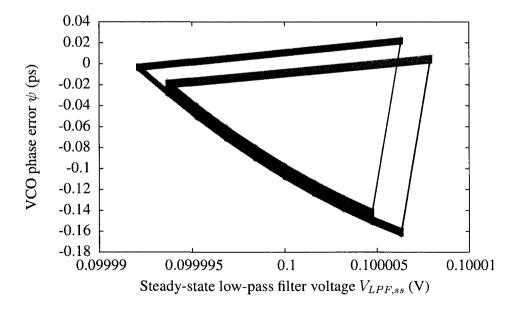

| 5.6         | Phase-space diagram of VCO phase error $\psi$ and the steady-state      | 00   |

| <i>-</i> -  | loop filter voltage with a -9.5 ns initial phase-error                  | 80   |

| 5.7         | Phase-space diagram of VCO phase error $\psi$ and the steady-state      | 0.1  |

| <b>~</b> 0  | loop filter voltage with a -0.5 ns initial phase-error                  | 81   |

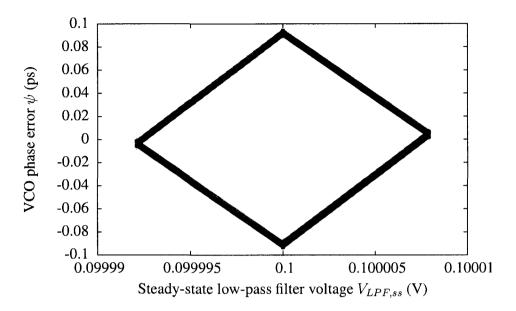

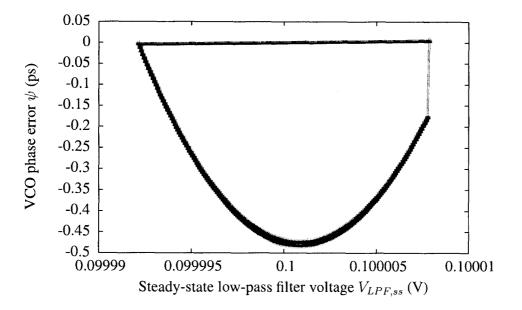

| 5.8         | Phase-space diagram of VCO phase error $\psi$ and the steady-state      | 0.1  |

| <b>5</b> 0  | loop filter voltage with a -0.1 ns initial phase-error                  | 81   |

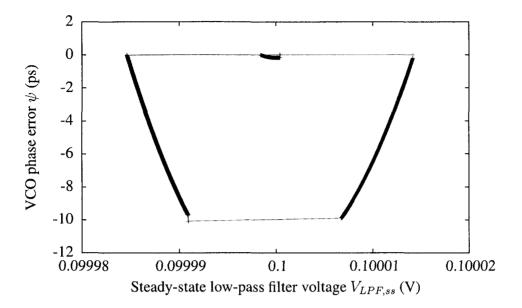

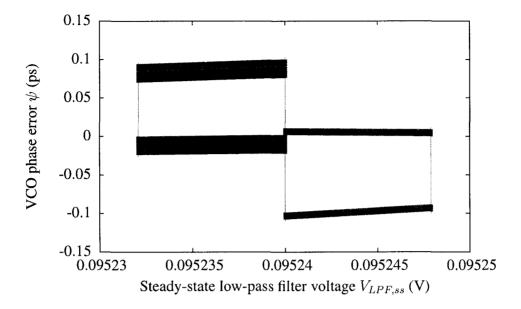

| 5.9         | Phase-space diagram of VCO phase error $\psi$ and the steady-state      | 00   |

| <b>F</b> 10 | loop filter voltage with a -0.005 ns initial phase-error                | 82   |

| 5.10        | Phase-space diagram of VCO phase error $\psi$ and the steady-state      | •    |

| ~           | loop filter voltage with a -0.0005 ns initial phase-error               | 83   |

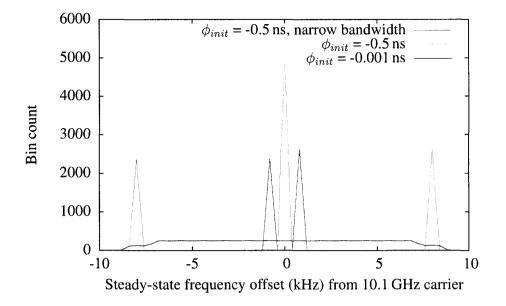

| 5.11        | Histogram plot comparing the steady-state frequency distribution        |      |

|             | for initial phase-errors of -0.5 ns and -0.001 ns                       | 84   |

| 5.12        | Phase-space diagram of VCO phase error $\psi$ and the steady-state      |      |

|             | loop filter voltage with a -0.5 ns initial phase-error for a toggling   |      |

|             | alias period                                                            | 86   |

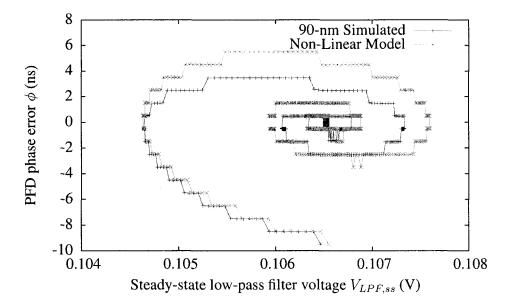

| 5.13        | Phase-space diagram of PFD phase error $\phi$ and the steady-state loop |      |

|             | filter voltage with a -9.5 ns initial phase-error, obtained from a 90-  |      |

|             | nm transistor-level simulation                                          | 89   |

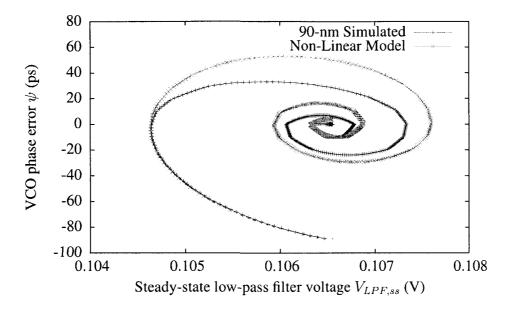

| 5.14        | Phase-space diagram of VCO phase error $\psi$ and the steady-state      |      |

|             | loop filter voltage with a -9.5 ns initial phase-error, obtained from a |      |

|             | 90-nm transistor-level simulation                                       | - 90 |

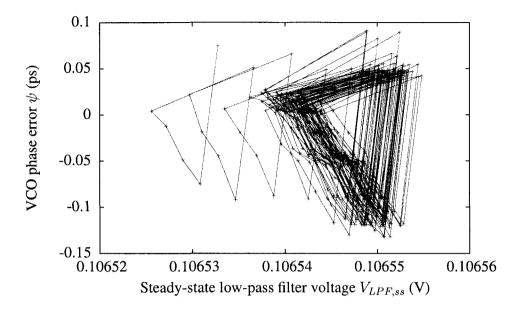

| 5.15       | Phase-space diagram of VCO phase error $\psi$ and the steady-state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|