Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file Votre référence

Our file Notre référence

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure production.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages criginales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# UNIVERSITY OF ALBERTA

# WAFER LEVEL RELIABILITY FOR APPLICATION SPECIFIC INTEGRATED CIRCUITS

by

DWIGHT E. MANNING

**©**

#### A THESIS

SUBMITTED TO THE FACULTY OF GRADUATE STUDIES AND RESEARCH IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

DEPARTMENT OF ELECTRICAL ENGINEERING

**FALL 1992**

EDMONTON, ALBERTA

National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Service Service des thèses canadiennes

Ottawa, Canada K1A 0N4

The author has granted an irrevocable nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

The author retains ownership of the cocyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation

ISBN 0-315-77102-X

#### UNIVERSITY OF ALBERTA

#### RELEASE FORM

DWIGHT E. MANNING NAME OF AUTHOR:

WAFER LEVEL RELIABILITY FOR TITLE OF THESIS:

APPLICATION SPECIFIC INTEGRATED

**CIRCUITS**

MASTER OF SCIENCE DEGREE:

YEAR THIS DEGREE GRANTED: 1992

Permission is hereby granted to the UNIVERSITY OF ALBERTA LIBRARY to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly or scientific research purposes only.

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the authors's written permisson.

(Signed)

Daught E. Mui PERMANENT AD

6925 F Rodling Drive

SAN JOSE, CALIFORNIA 95138

U.S.A.

Date: Sept 30 1992

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies and Research for acceptance, a thesis entitled WAFER LEVEL RELIABILITY FOR APPLICATION SPECIFIC INTEGRATED CIRCUITS submitted by DWIGHT E. MANNING, in partial fulfilment of the requirements for the degree of Master of Science in Electrical Engineering.

Supervisor: Dr. D.O. Koval

Dr. K.H. Stromsmoe

.....

Asproque

Date: Apt. 49...1992

This thesis is dedicated to the memory of

Allan William Edward Manning

for his loving support on the first one that led to this next one.

This thesis is also dedicated to my loving wife

Alison

for her loving support on this next one

and to my mother

Marian

for her loving support on both.

# WAFER LEVEL RELIABILITY FOR APPLICATION SPECIFIC INTEGRATED CIRCUITS

#### **ABSTRACT**

Semiconductor designs and processes have undergone rapid changes in complexity, performance and size in a response to increased economic pressures to produce parts that are cheaper and more reliable than ever before in this highly competitive industry. New semiconductor processes, testing methodologies and procedures are being developed to increase the amount of reliability assurance testing through Wafer Level Reliability Testing, a new and emerging field in this industry, the subject of this thesis. The fundamentals of semiconductor manufacturing processes (e.g., photolithography, ion implantation and diffusion, thin film deposition, etching, etc.) are presented as part of a knowledge base required to understand the possible failure mechanisms, test structures and burn in reliability necessary to understand the application of Wafer Level Reliability Testing to custom ASIC (i.e. Application Specific Integrated Circuits) semiconductor devices and its importance to traditional life time reliability testing methodologies. Wafer Level Reliability (i.e., WLR) Testing fundamentals involving the fabrication and integration of test structures and production parts on a single wafer and specific tests for these test structures are presented. These unique WLR structures presented in this thesis for ASIC manufacturing have not been published to date in the literature. Empirical test results of traditional life time reliability testing for designed and fabricated wafers containing test structures and ASIC parts are presented. The empirical results are analyzed in detail to determine if there is any correlation between existing process monitor test and the reliability of the product to develop WLR lifetime models. Based on the empirical test results, the benefits and limitations of Wafer Level Reliability in controlling manufacturing processes of ASIC semiconductor devices will be discussed in detail in this thesis.

#### ACKNOWLEDGEMENTS

The author would like to thank Tom Long for the assistance and support in the beginning of the thesis and to thank Emery Sugasawara for supporting the completion of this thesis.

The author would also like to thank his supervisor, Dr. D. O. Koval, for all his guidance, support and insight during the preparation of this thesis.

The author would also like to thank and acknowledge the assistance of Brian Root and Tim Turner, the developers of the electromigration SWEAT test for their insights and updates on their technique.

The author would also like to thank the support of LSI Logic Corporation of Canada and LSI Logic Corporation for the support and the data enabling this thesis to be completed.

The author would also like to thank Mike Stover, Corporate Reliability Manager and Vish Bhide, head of the Wafer Level Reliability committee for their support. Joesph Zhou for his assistance in the data collection. The author would also like to thank his fellow Wafer Level Reliability team members for their contributions to the project: Ravindra Alluri, Sudhir Chopra, Abid Husain, Laique Khan, Daniel Gitlin, Napoleon Domingo, Liang Lie, Uresh Patel, Charles McDonald, Arthur Kuo and Bill Stevenson.

The author would also like to recognize the assistance of: Ross Manning and Xerox Canada for reproductions, Vivian Wells and Alison Manning for proof reading, Dr. C.R. and Arline James for transportation, Wayne and Heather Campbell for accommodation, and Ken Orr for the suggestion of a glossary.

# TABLE OF CONTENTS

|    | CHAPTER |                     | <b>IGE</b>                                     |    |

|----|---------|---------------------|------------------------------------------------|----|

| I. | INT     | RODUCTION           |                                                | 1  |

|    | 1.1     | Yield and Reliabili | ty                                             | 2  |

|    | 1.2     | Wafer Level Relial  | bility                                         | 5  |

|    | 1.3     | ASIC Circuits       |                                                | 5  |

|    | 1.4     | ASIC Wafer Level    | Reliability                                    | 5  |

|    | 1.5     | Thesis Objectives   | ••••••••••••                                   | 6  |

|    | 1.6     | Scope of Thesis.    | ••••••••••••••••••                             | 7  |

| IJ | i. VL   | SI BASIC MAN        | UFACTURING PROCESSES                           | 9  |

|    | 2.1     | Introduction        | ***************************************        | 9  |

|    | 2.2     | Clean Room Tech     | nnology                                        | 10 |

|    | 2.3     |                     |                                                | 12 |

|    |         |                     | n Deposition                                   |    |

|    |         | 2.3.2 Photolith     | nography                                       | 14 |

|    |         |                     | •••••••••••••                                  | 18 |

|    |         |                     | antation and Diffusion                         | 23 |

|    |         | 2.3.5 Overall 1     | Processing                                     | 30 |

|    | 2.4     | ASIC Logic Circ     | cuit Basic Operation                           | 37 |

| 1  | m. Yi   | ELD AND REL         | IABILITY FUNDAMENTALS                          | 45 |

|    | 3.1     |                     | ••••••••••••••••••••••                         |    |

|    | 3.2     | Defects             | ••••••••••••••••••                             | 47 |

|    | 0       |                     | Densities                                      |    |

|    | 3.3     |                     | ••••••                                         |    |

|    | 3.4     |                     | cuits Test Methodology                         |    |

|    | 3.5     |                     | liability Testing                              |    |

|    | J.J     |                     | nigration and Stress Void Reliability Failures |    |

|         | 3.5.2 Transistor and Dielectric Reliability Failures | i   |

|---------|------------------------------------------------------|-----|

| 3.6     | Reliability Defect Detection and Testing             | 2   |

| 3.7     | Summary 6                                            | 5   |

| <b></b> |                                                      |     |

| IV. EL  | ECTROMIGRATION FUNDAMENTALS 6                        | 8   |

| 4.1     | Introduction 6                                       |     |

| 4.2     | Electromigration Physics 6                           | 9   |

|         |                                                      | 9   |

|         | 4.2.2 Ion Potential Bonding and Diffusion            | 0   |

|         | 4.2.3 Ion Electromigration                           | 14  |

| 4.3     | Electromigration MTTF                                | 18  |

| 4.4     | Electromigration Test Techniques                     | 30  |

|         | 4.4.1 SWEAT Test                                     | 31  |

|         |                                                      | 88  |

|         | 4.4.3 Other Test Techniques                          | 91  |

| 4.5     | Electromigration in VLSI Manufacturing               |     |

| 4.6     | Summary                                              | 93  |

|         |                                                      |     |

| V. T    | EST CHIP DESIGN                                      | 95  |

| 5.1     |                                                      |     |

| 5.2     |                                                      | 96  |

| 5.3     |                                                      | 98  |

|         | 5.3.1 SWEAT Structures                               | 98  |

|         | 5.3.2 Topology Test Structure                        |     |

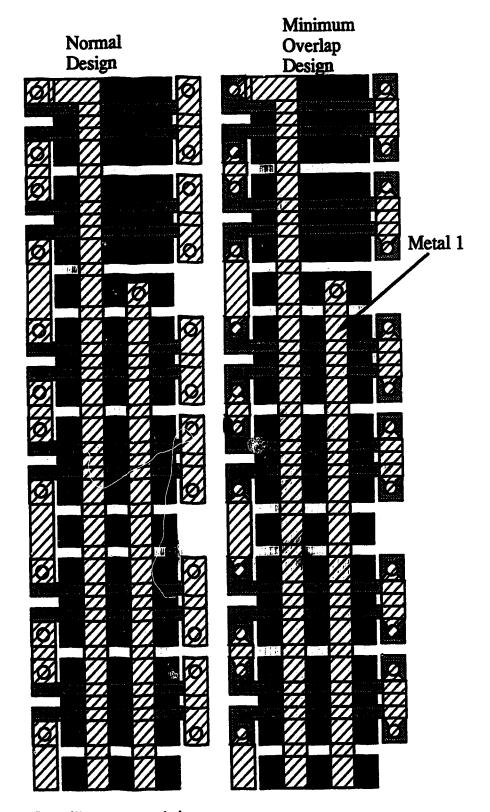

|         | 5.3.3 Contact and Via Test Structures                | 105 |

| 5.4     |                                                      | 112 |

| 5.5     |                                                      | 118 |

| 5.6     |                                                      | 123 |

|         |                                                      | 125 |

| 5.7     | Sufficient                                           |     |

| VI. B | URN IN R  | ELIABILITY                              | 126     |

|-------|-----------|-----------------------------------------|---------|

| 6.1   |           | ion                                     |         |

| 6.2   |           | y Basics                                |         |

| 6.3   |           | y Distributions                         |         |

| 6.4   |           | ate Measurements                        |         |

| 6.5   |           | s Equation                              |         |

| 6.6   |           | quationquation                          |         |

| 6.7   |           | ted Reliability Testing                 |         |

| 6.8   | Semicon   | ductor Reliability Testing              | 142     |

|       | 6.8.1     | High Temperature Dynamic Lifetest       | 143     |

|       |           | High Voltage Dynamic Lifetest           |         |

|       |           | Low Temperature Dynamic Lifetest        |         |

|       |           | High Temperature Storage                |         |

|       |           | High Temperature / Humidity Lifetest    |         |

|       |           | Temperature Cycling                     |         |

|       | 6.8.7     | Vibration / Shock Testing               |         |

|       | 6.8.8     | Soft Error / Radiation Hardness Testing |         |

| 6.9   | Reliabil  | lity Monitoring                         |         |

| 6.1   |           | ITY                                     |         |

|       |           | TION OF WAFER LEVEL RELIABILITY TEST I  | )ATA152 |

|       |           | ction                                   |         |

| 7.    | 1 Introdu | ICHON                                   | .152    |

| 7.    | _         | mental Procedure                        | 152     |

|       | 7.2.1     | •                                       | 157     |

|       | 7.2.2     | Test Wafer Layouts                      | .159    |

| 7.    | 3 Empiri  | ical Testing Results                    | 140     |

|       | 7.3.1     | Wafer Level Reliability Tests           | 144     |

|       | 7.3.2     | Wafer Sort and Final Test               |         |

|       | 7.3.3     | Reliability Stress Tests                | 102     |

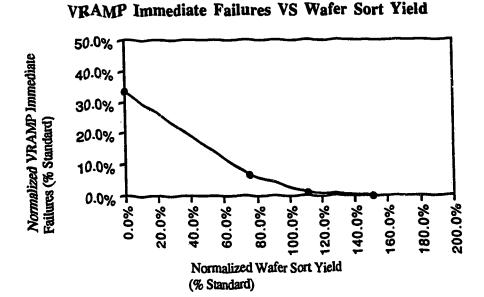

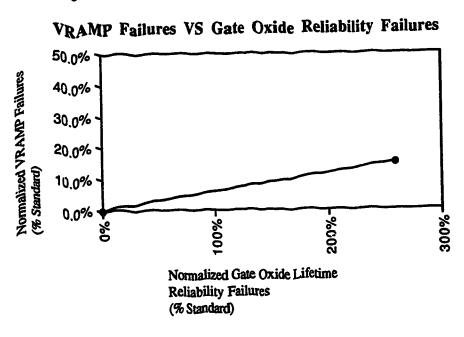

| 7.4     | Data Analysis                   | 169 |

|---------|---------------------------------|-----|

|         | Data Aliasysis                  | 174 |

| 7.5     | Wafer Level Reliability         |     |

|         | 7.5.2 Product Lifetime Modeling |     |

| 7.6     | Summary                         |     |

| vIII. ( | CONCLUSION                      | 185 |

| tv n    | EFERENCES                       | 189 |

# LIST OF TABLES

| TABLE |                                                       | PAGE |  |

|-------|-------------------------------------------------------|------|--|

| 3.1   | Common yield and reliability defects                  | 63   |  |

| 3.2   | Wafer reliability tests                               |      |  |

| 6.1   | Acceleration factors for semiconductor reliability    | 141  |  |

| 6.2   | Lifetime data                                         | 149  |  |

| 7.1   | Wafer Level Reliability test runs                     | 160  |  |

| 7.2   | VRAMP normalized data                                 |      |  |

| 7.3   | VRAMP normalized failure results                      | 162  |  |

| 7.4   | QBD normalized test results                           |      |  |

| 7.5   | BVOX normalized failure results                       |      |  |

| 7.6   | Normalized wafer sort yields                          |      |  |

| 7.7   | Normalized final test yields                          |      |  |

| 7.8   | Average normalized final test yields                  |      |  |

| 7.9   | Reliability stress test configuration                 |      |  |

| 7.10  | -                                                     |      |  |

| 7.11  |                                                       |      |  |

| 9 1   | Semiconductor failure rates in different environments |      |  |

# LIST OF FIGURES

| FIG  | FIGURE                                                        |      |

|------|---------------------------------------------------------------|------|

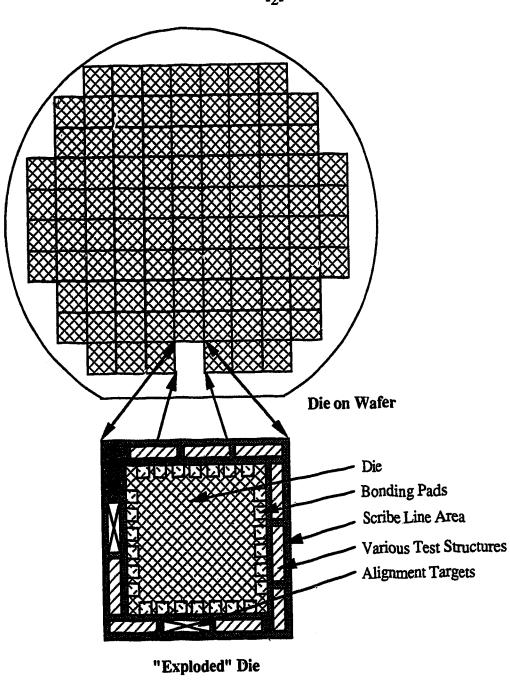

| 1.1  | Exploded view of a die on a wafer with test structures        | 2    |

| 2.1  | -                                                             | 14   |

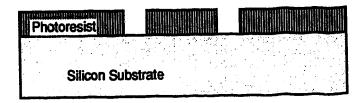

| 2.2  |                                                               | 16   |

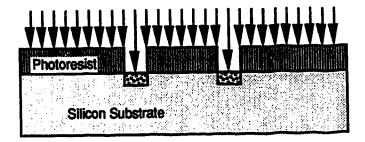

| 2.3  | Step 3 - photoresist exposure                                 | 17   |

| 2.4  | Step 4 - photoresist develop                                  | 17   |

| 2.5  | Step 4 - photoresist develop                                  | 20   |

| 2.6  | Step 5 - metal/polysilicon etch                               | 20   |

| 2.7  | Step 6 - photoresist etch                                     | 20   |

| 2.8  | First two steps in defining a hole                            | 21   |

| 2.9  | Steps 3 to 6 in defining a hole                               | 22   |

| 2.10 | First process step for low energy ion implantation            | 25   |

| 2.11 | Process steps 2 through 5 for low energy ion implantation     | 26   |

| 2.12 | Process step 6 for low energy ion implantation                | 27   |

| 2.13 | Process steps 1 and 2 for high energy ion implantation        | 27   |

| 2.14 | Etching process steps 3 to 6 for high energy ion implantation | 28   |

| 2.15 | Etching process steps 7 to 9 for high energy ion implantation | 29   |

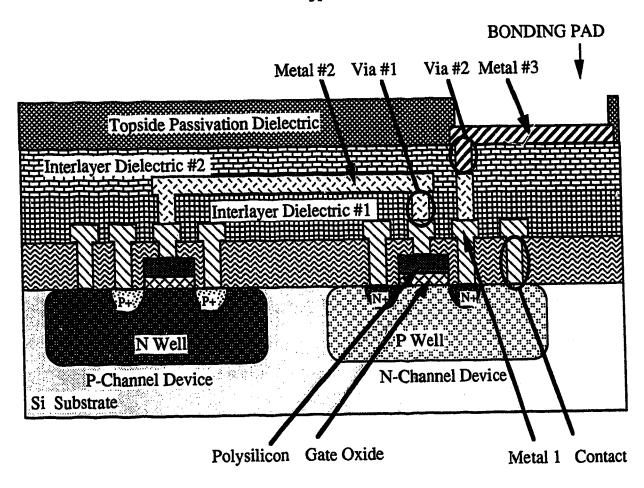

| 2.16 | Cross section of a 3 layer metallized CMOS device             | 31   |

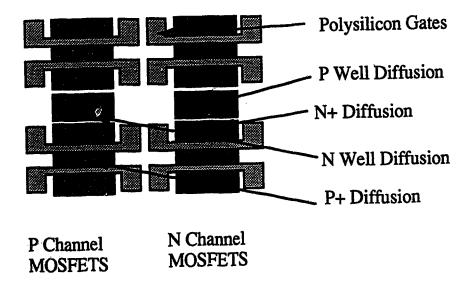

| 2.17 | Basic CMOS cell - base array - one cell                       | 32   |

| 2.18 | Basic CMOS cell - contact holes defined                       | 32   |

| 2.19 |                                                               |      |

| 2.20 |                                                               | 34   |

| 2.21 |                                                               | 35   |

| 2.22 | • •                                                           |      |

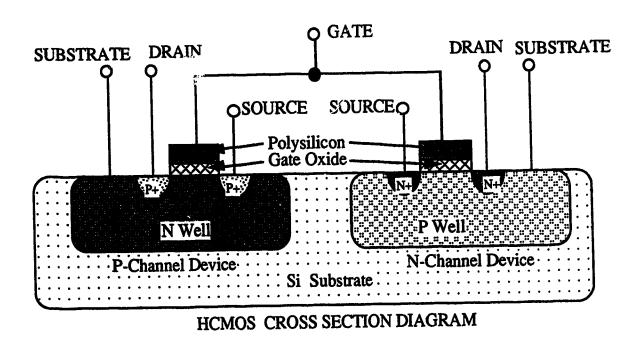

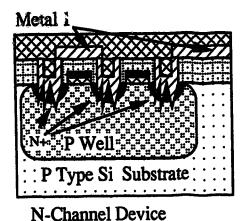

| 2.23 | Cross section of CMOS transistors                             | . 37 |

| 2.24 |                                                               | . 38 |

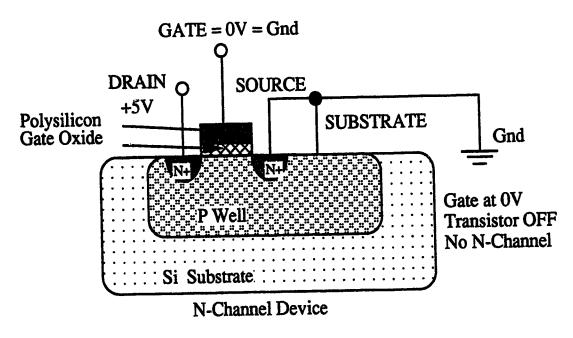

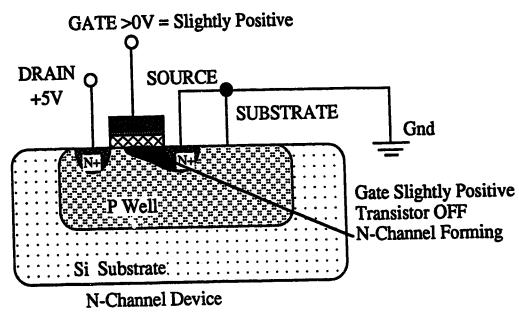

| 2.25 | N-Channel transistor with gate voltage > 0 volts              | . 39 |

| 2.26 | Fully on N-Channel transistor                                 | . 40 |

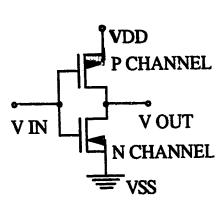

| 2.27 | Basic invertor circuit                                                   |

|------|--------------------------------------------------------------------------|

| 2.28 | Double invertor circuit diagram                                          |

| 2.29 | CMOS basic logic gates                                                   |

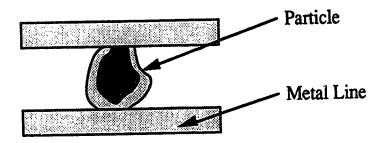

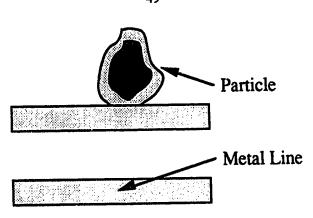

| 3.1  | Killing defect 48                                                        |

| 3.2  | Non-killing defect 49                                                    |

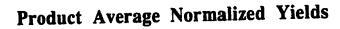

| 3.3  | Comparison of yield models 54                                            |

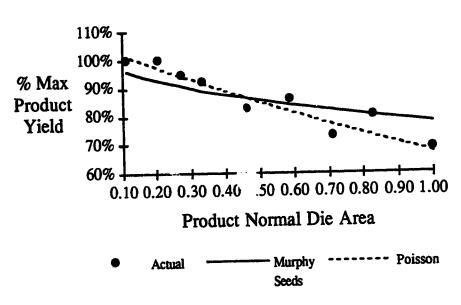

| 3.4  | Potential reliability defect particle example                            |

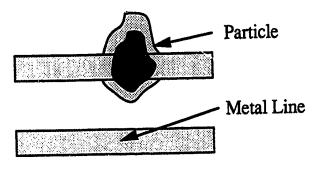

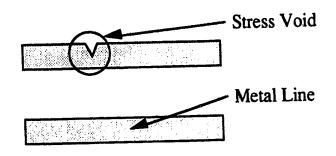

| 3.5  | Stress void in a metal line                                              |

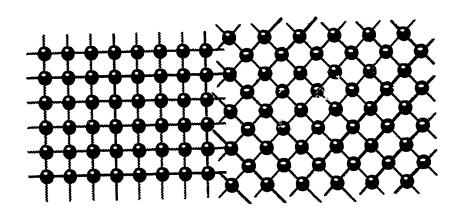

| 4.1  | Crystal lattice structure 70                                             |

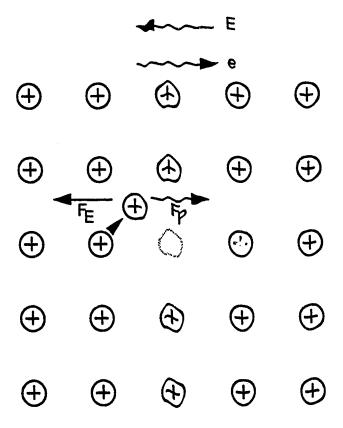

| 4.2  | Ion self diffusion diagram 72                                            |

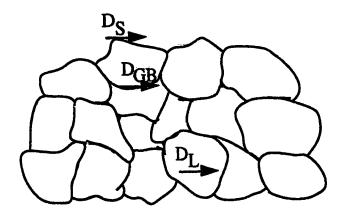

| 4.3  | Types of Diffusion within a Thin Film                                    |

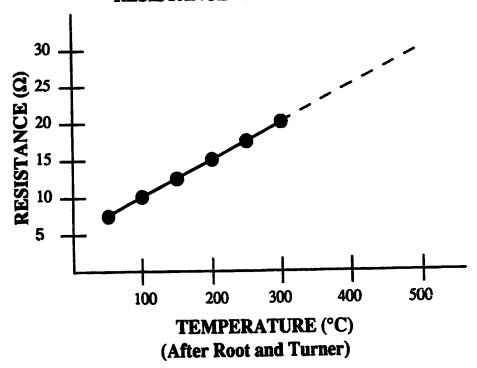

| 4.4  | SWEAT structure resistance/temperature relationship                      |

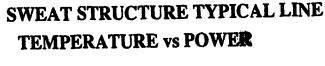

| 4.5  | SWEAT power/temperature relationship                                     |

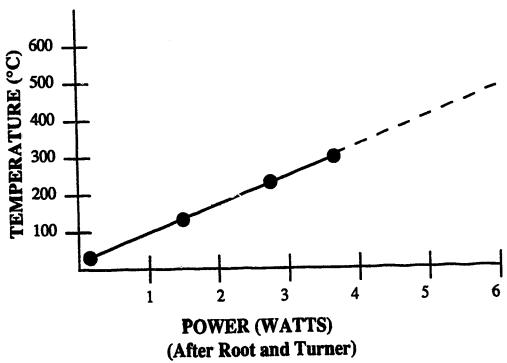

| 4.6  | Typical SWEAT test structure                                             |

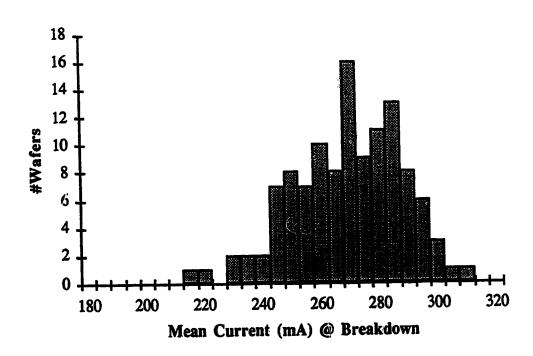

| 4.7  | Histogram of BEM breakdown currents of production wafers 90              |

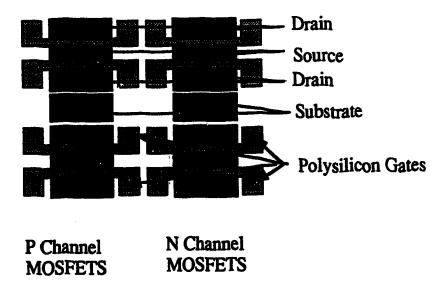

| 5.1  | Gate array cell 96                                                       |

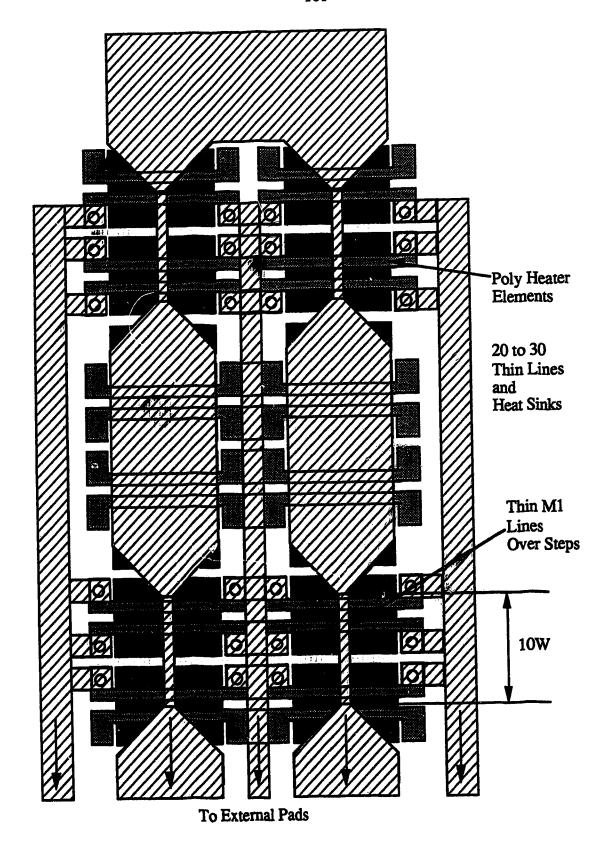

| 5.2  | Metal 2 SWEAT test structure 100                                         |

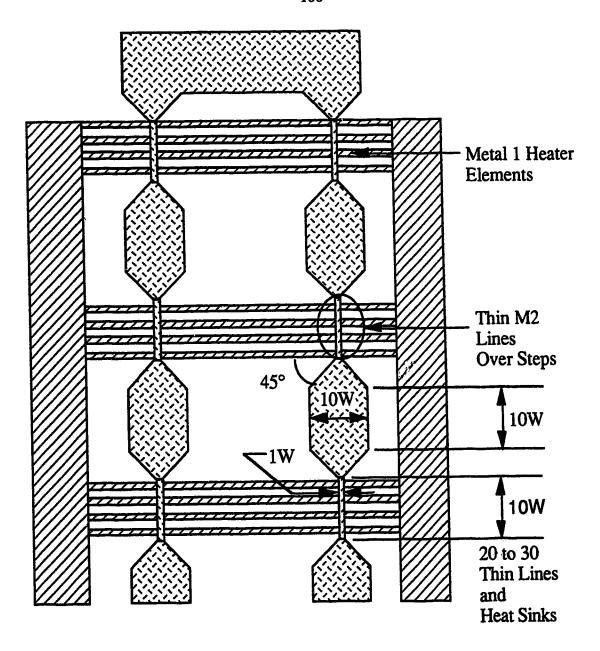

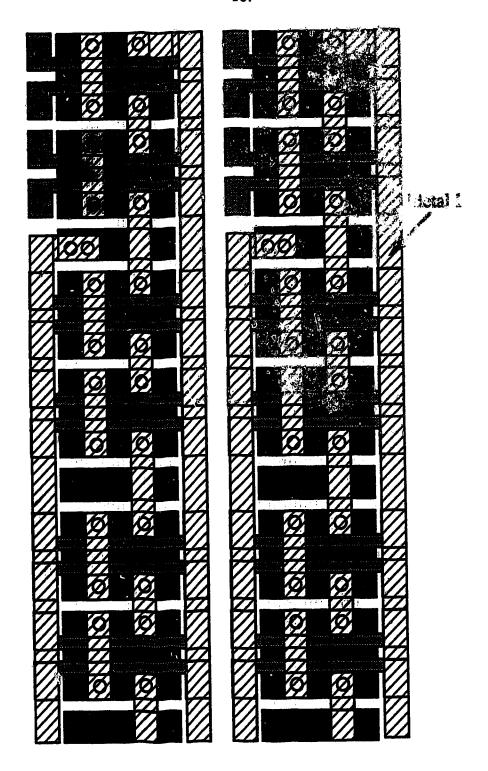

| 5.3  | Metal 1 SWEAT test structure 101                                         |

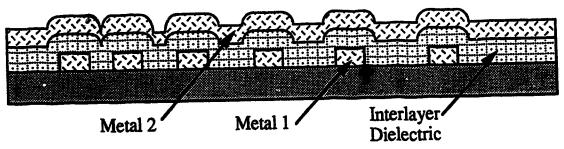

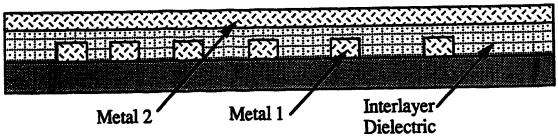

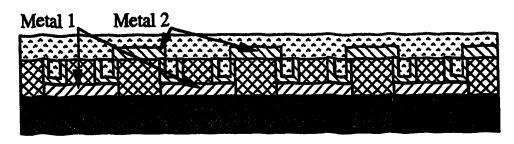

| 5.4  | Cross section of topology test structure with dielectric topology 102    |

| 5.5  | Cross section of topology test structure with no dielectric topology 103 |

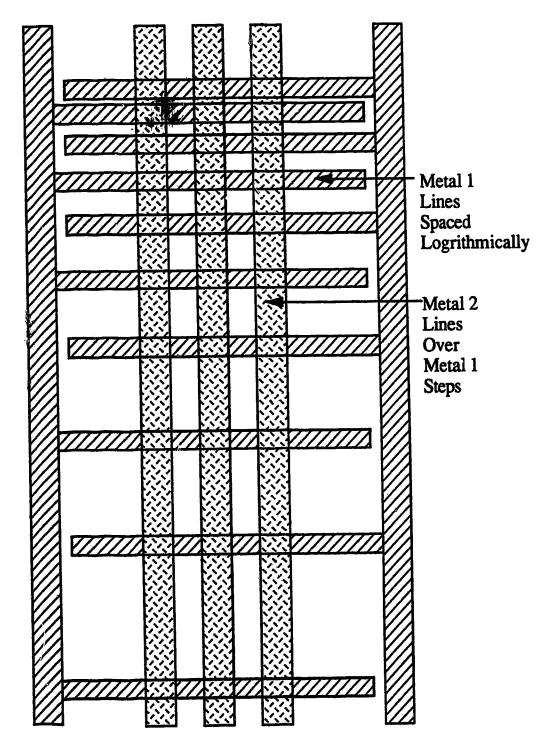

| 5.6  | Topology electromigration test structure                                 |

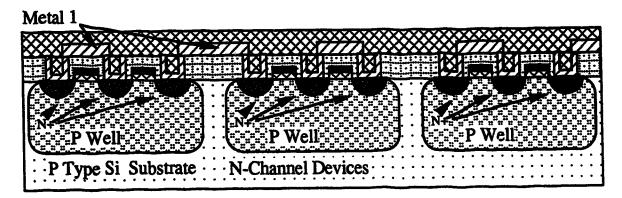

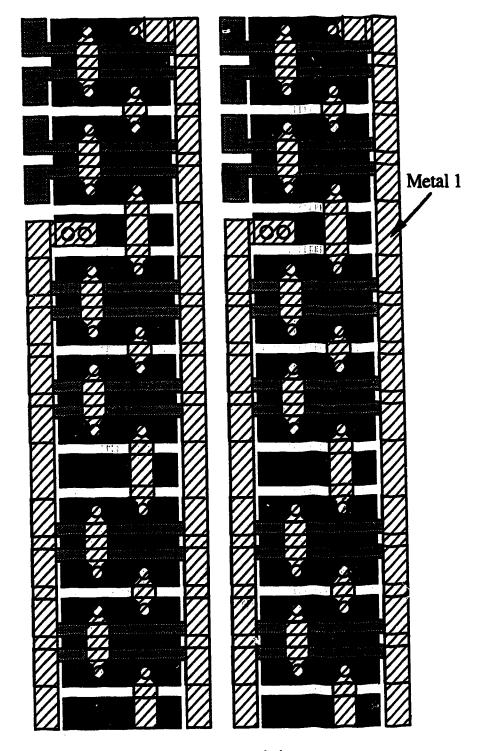

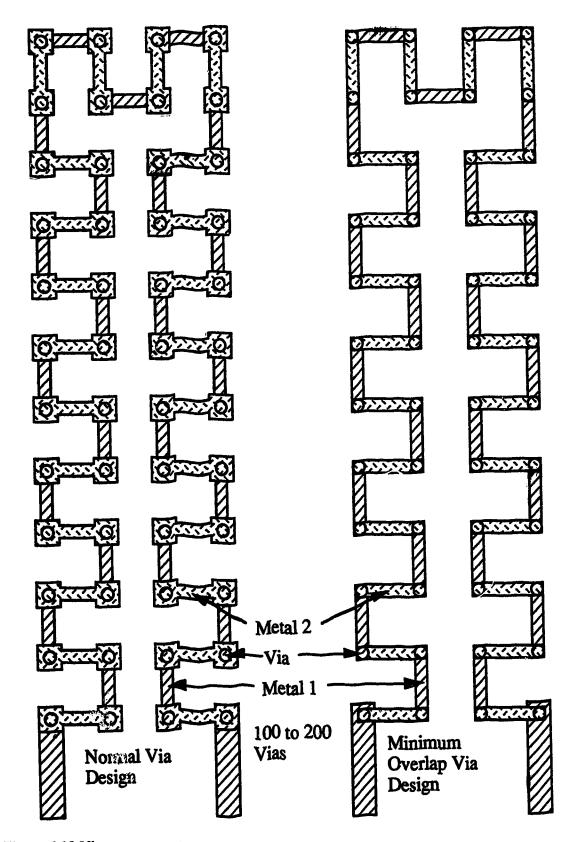

| 5.7  | N+ contact chain cross section 106                                       |

| 5.8  |                                                                          |

| 5.9  | N+, P+ contact chain test structures                                     |

| 5.1  | •                                                                        |

| 5.1  | 1 Polysilicon contact chain test structures                              |

| 5.1  | · <del>-</del>                                                           |

| 5.1  |                                                                          |

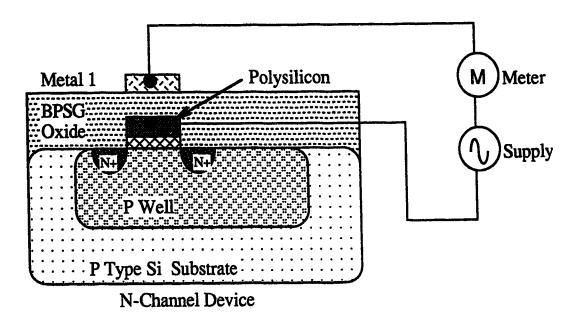

| 5.1  | 4 Gate oxide test circuit                                                |

|      |                                                                          |

|      | 114                                                                                 |

|------|-------------------------------------------------------------------------------------|

| 5.15 | BPSG oxide test circuit                                                             |

| 5.16 | Interdielectric test circuit                                                        |

| 5.17 | Gate oxide and BPSG test capacitor structures 116                                   |

| 5.18 | Interdielectric test capacitor structure                                            |

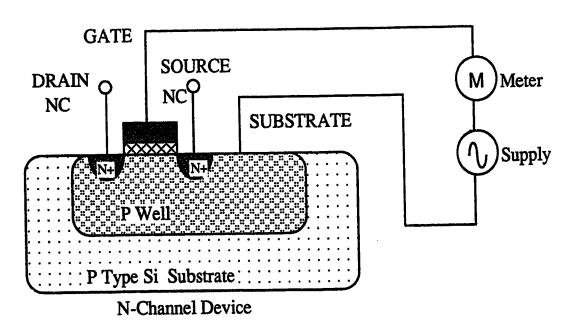

| 5.19 | Electron flow in N-Channel MOS device                                               |

| 5.20 | Hot electron injection into N-Channel MOS gate oxide                                |

| 5.21 | Hot carrier test circuit                                                            |

| 5.22 | Hot carrier test structure                                                          |

| 5.23 | Test chip layout                                                                    |

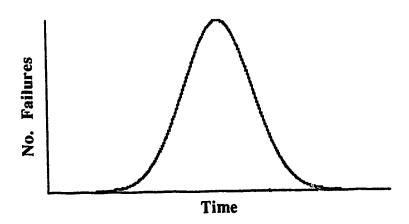

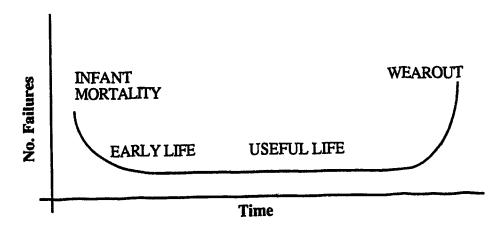

| 6.1  | Normal probability density function, f(t)                                           |

| 6.2  | "Bathtub" failure probability density function, f(t)                                |

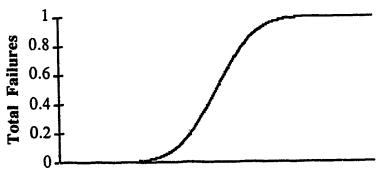

|      | Cumulative density function, F(t) of a normal f(t) function                         |

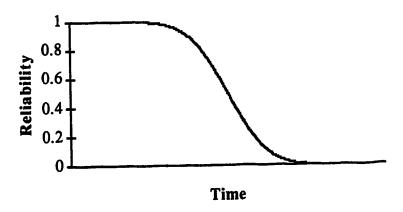

| 6.3  | Reliability function, R(t) of a normal f(t) function                                |

| 6.4  |                                                                                     |

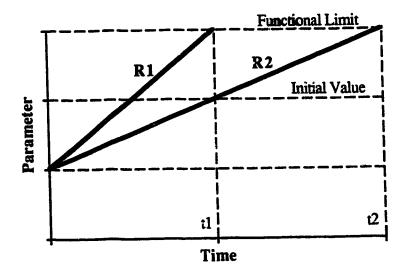

| 6.5  | Component lifetime at two different reaction rates, R <sub>1</sub> & R <sub>2</sub> |

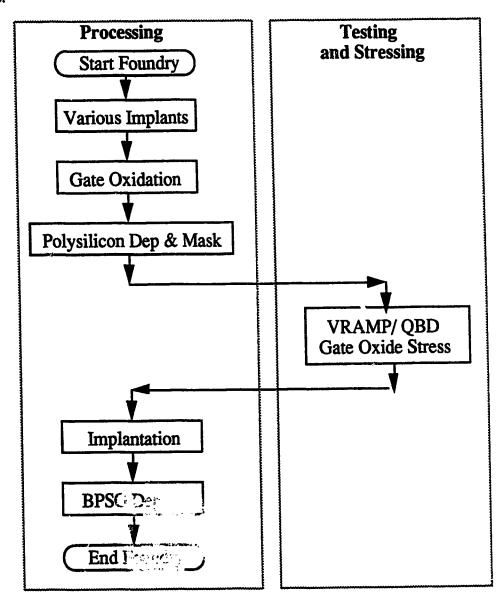

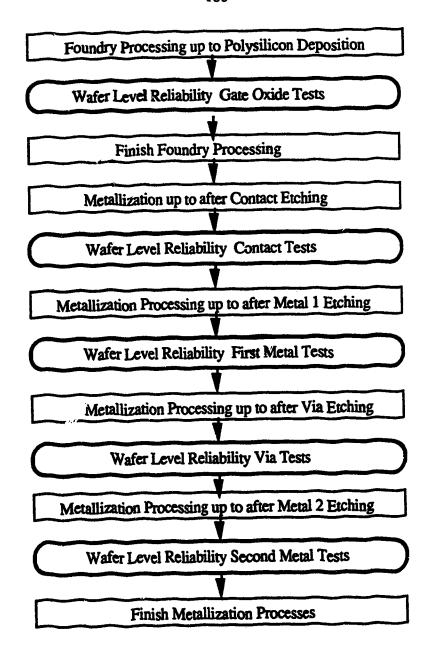

| 7.1  | Test run foundry process flow                                                       |

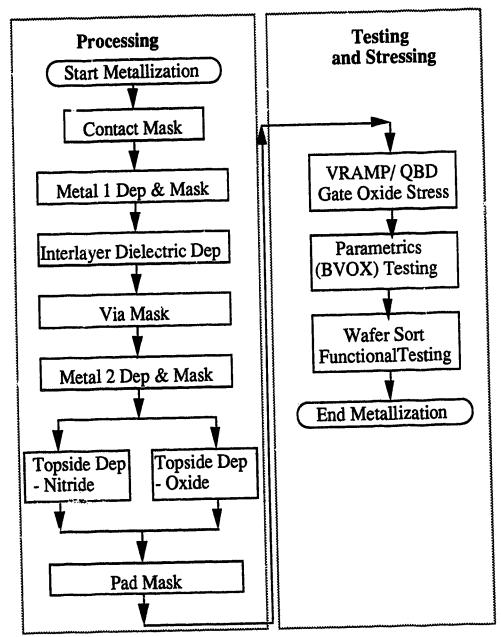

| 7.2  | Test run metallization process flow                                                 |

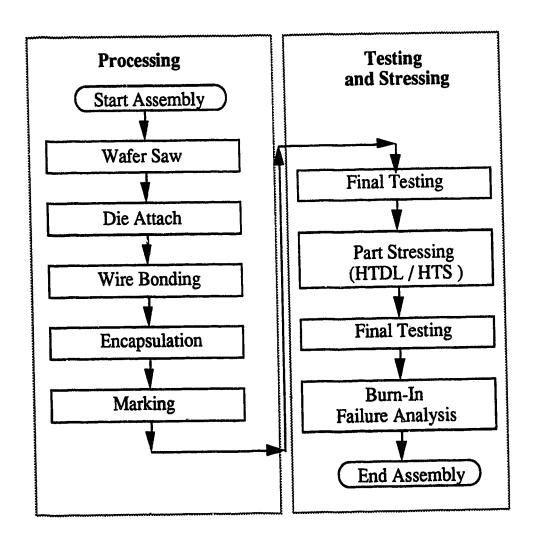

| 7.3  | Test run assembly process flow 156                                                  |

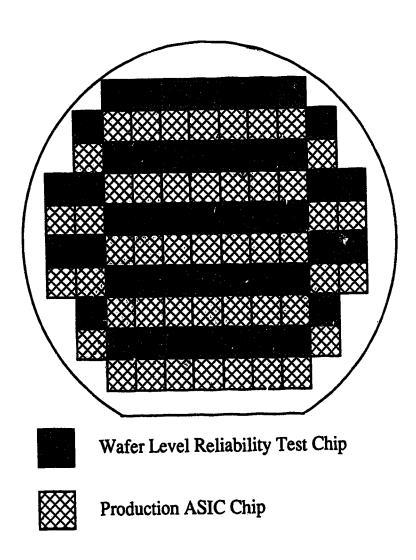

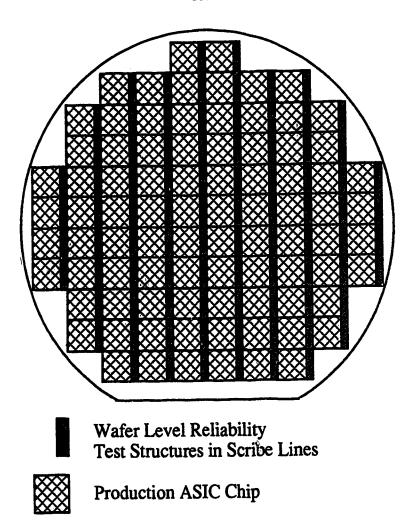

| 7.4  | Test wafer layout                                                                   |

| 7.5  | Example of Wafer Level Reliability scribe line test structures                      |

| 7.6  | Wafer dielectric failure versus wafer sort yields                                   |

| 7.7  | Wafer failures versus gate oxide lifetime reliability failures                      |

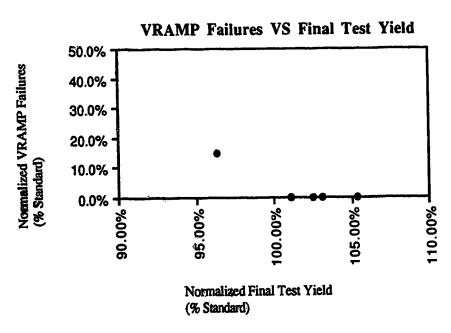

| 7.8  | Wafer failures versus final test yield                                              |

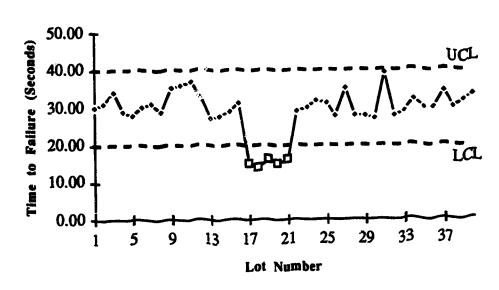

| 7.9  | SWEAT electromigration control chart                                                |

| 7.10 | 180                                                                                 |

#### **GLOSSARY OF TERMS**

Anisotropic: An etch profile that is straight down or totally vertical with no horizontal

etch.

Array: A matrix of uncommitted logic functions countained in a single chip of

silicon.

Assembly: The process in semiconductor manufacturing where a completed die is put

into a package or mounted directly onto a circuit board and connecting wire

bonds are defined between the die and the package or circuit board.

ASIC: Application Specific Integrated Circuit. This is a custom chip with an unique

design. This part is not mass produced, and is generally referred to as a

custom integrated circuit.

Base Array: A gate array with the gates built up to the transistor level only. These wafers

are not customized at this point and consist of standard sizes of chips with

varying number of gates.

Bipolar The transistor type that works on current to switch or amplify.

Transistor:

BEM: Electromigration test methodology that uses Median Energy to failure -MEF.

Burn In:

The acceleration of semiconductor parts to provide stress to shorten the lifetime of the parts such that information about the reliability can be obtained. Burn in usually involves heat as a stress and can be for infant mortality screening or product lifetime testing.

Chip:

A small piece of silicon that is a complete semiconductor device or integrated circuit.

Clean Room:

A room where the environment is strictly controlled and the level of airborne particulates is controlled through air filtration.

**Contact:**

A hole in the BPSG dielectric to allow first metal to connect to the transistor or doped silicon regions of a circuit.

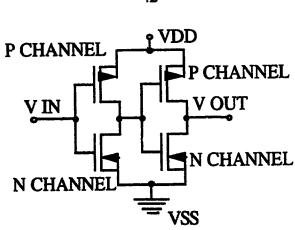

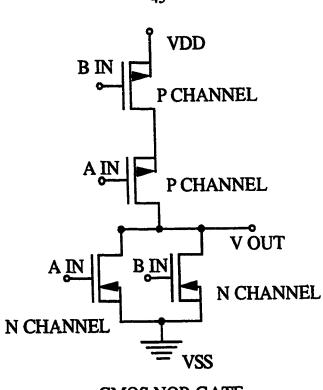

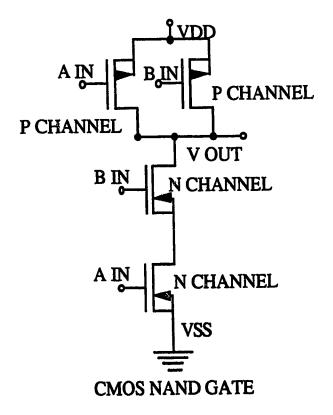

CMOS:

Complementary Metal Oxide Silicon. Both N-channel and P-channel transistors are used together to form logic circuits. CMOS logic is low power.

Contamination:

Undesirable material. In semiconductor manufacturing, this refers to foreign matter in the circuit or chemicals/gases used in the manufacture of the circuits.

CVD:

Chemical Vapor Deposition - The process of depositing thin films on a wafer in a reactor by chemicals in gas form, reacting and growing a thin film on a wafer.

Defect:

A problem in a circuit on a wafer that can cause malfunction of the circuit.

Deposition:

The process in semiconductor manufacturing in which thin films are grown on a wafer.

DI Water:

De-Ionized Water is water that has been purified to the point where most of the ions usually present in water have been removed. This ultra-pure water is used throughout the manufacturing of semiconductor integrated circuits.

Die:

An integrated circuit that is in wafer form and is in the process of being manufactured.

Diffusion:

In semiconductor manufacturing, this refers to the process of using heat to allow movement of impurities through the semiconductor crystal structure and helps to define the conductive areas in transistors.

Doping:

The process of injecting impurities into the semiconductor crystal structure to help define the conductive properties of the device.

Downstream

**Etcher:**

A type of plasma etcher, that has the gas plasma formed away from the wafer, so that the wafer is subjected to the minimum plasma damage. The wafer sits "downstream", closer to the vacuum pump, rather than closer to where the plasma is ignited.

DUT:

Device Under Test. This refers to the integrated circuit that is being tested by a computerized testing system.

ESD:

Electrostatic Discharge. Static damage is one way an integrated circuit can be damaged to cause failure in the circut.

Fab:

FET:

An industry common term that is an abbreviation for the Wafer Fabrication Facility.

Field Effect Transistor. This type of transistor uses voltage to build up a

charge or electric field. This voltage is then amplified or used to switch on

and off the transistor.

Final Test:

Upon completion of the assembly processes, the finished semiconductor product is subjected to a full functional test, fully testing the circuit to operational logic and functionality.

Foundry:

In ASIC gate array manufacturing, this refers to the initial processes in wafer manufacturing in which the silicon wafer has the transistor and logic gate structures defined up to the protective BPSG layer.

Gate Array:

A type of ASIC circuit that consists of logic gates.

**HCMOS**:

High Speed CMOS circuits.

Impurity:

In semiconductor manufacturing, this refers to atom(s), ion(s) or chemicals in the crystal structure of the semiconductor or a material that is not the material in question. Impurities in semiconductors are sometimes desirable. Impurities are used to define the conduction characteristics in the semiconductors.

Integrated

A circuit that is realized in a single semiconductor part.

Circuit (IC):

Invertor Gate: A basic logic gate that inverts the input or changes the input from high to

low or from low to high.

Ion A semiconductor process that is used in manufacturing to put impurities into

Implantation: semiconductors to define conductive regions. A specialized machine is used

to ionize impurities and accelerate them into the target; the wafer.

Isotropic: An etch profile that is rounded. The etch rate of the vertical etch rate is the

same as the horizontal etch rate.

Killing Defect: A defect on a die that prevents the circuit from working.

Laminar Flow: In semiconductor manufacturing, this refers to the continuous flow of

filtered air in a clean room. The filters usually cover the entire ceiling area in

VLSI manufacturing. This causes the flow to be everywhere within the

clean room.

Line Yield: This yield is the amount of good wafers or parts that are left after a particular

process step(s).

Mask / The plates that contain the patterns which are imprinted onto a wafer during

Reticle / the photolithographic process.

Photomask:

Masterslice: Another term for a base array. A masterslice consists of uncommitted,

unconnected logic functions only finished to the transistor level.

Memory Chip: A chip that contains circuitry that can store data in the form of binary digits

for later retrieval.

MEF: Median Energy to Failure. The median amount of energy used in BEM

electromigration testing that causes a test structure to fail.

Metallization: The finishing processes in wafer manufacturing in which the metal

interconnections of the uncommitted circuitry is defined.

Micron: An unit of measure that is one-millionth of a meter.

Misalignment: One or more layers of a chip are not lined up properly with the other layers.

This is a mistake or defect caused in the photolithographic process.

MOS: Metal Oxide Silicon transistor. An abbreviation for MOSFET, a type of field

effect transistor. The metal-oxide-silicon refers to the physical construction

of the transistor. There is an insulating oxide underneath the gate conductor.

MOSFET: Metal Oxide Silicon Field Effect Transistor. See MOS

MTTF: Median Time to Failure. The point in time where 50% of a population has

failed.

N-Channel A type of MOSFET with N-type semiconductor source and drain regions.

Transistor:

N-Type Silicon: Silicon with impurities implanted in the crystal structure, usually a type IV

element, that gives an extra electron in the orbital shell.

NAND Gate: A basic logic gate.

Nitride An abbreviation for Silicon Nitride thin film which is used in the

manufacturing of semiconductors.

Non-Killing: A defect that has not stopped the circuit from working.

**Defect**

NOR Gate: A basic logic gate.

Oxide: An abbreviation for Silicon Dioxide thin film which is used in the the

manufacturing of semiconductors.

P-Channel A type of MOSFET with P-type semiconductor source and drain regions.

Transistor:

P-Type Silicon: Silicon with impurities implanted in the crystal structure, usually a type III

element, that gives an extra space for an electron or a "hole" in the orbital

shell.

Parametric A test of the basic transistor circuit parameters usually done on specific test

Test: transistors and other associated structures in the scribe lines.

Parametric A type of tester that is used to test out basic transistor or circuit electrical

Tester: parameters.

Particle: A piece of contamination that could end up on a die.

PECVD: Plasma Enhanced CVD. The energy of the plasma gas is used to provide the

energy for the chemical reaction.

Photolithography: The process in semiconductor manufacturing of transferring the design from

masks to wafers and defining the design in photo sensitive resist.

Plasma Etching: The process in semiconductor manufacturing of etching exposed areas of

materials through the use of excited reactive gases in the plasma state.

Process An in process test where tests are performed on wafers during the

Monitor: manufacturing fabrication processes. This can be done on dedicated test

wafers or production wafers.

Reliability In semiconductor manufacturing, this refers to how long the circuit will

continue to work after manufacturing.

RIE: Reactive Ion Etcher. This type of plasma etcher uses ion bombardment to

assist the plasma etching. Wafers sit on the powered electrode.

Semiconductor: A solid crystalline material (e.g. silicon) whose electrical conductivity is

intermediate between conductors and insulators.

Scribe line: The area between the die on the wafer where test structures,

photolithography alignment targets and alignment measurement structures

are located. This is the area also reserved for the width of the cutting saw

when the wafer is cut up into individual die during the assembly processes.

Stepper:

A camera system which is used in the photolithographic process. This camera system only exposes a single or a few die at a time, called a field. After exposure of a field, the system moves or "steps" to the next location where it aligns to the previous layer(s) and exposes the same field in the next location.

Substrate:

A Silicon base upon which the logic functions are fabricated. The substrate influences the electrical characteristics of the transistors, which make up the circuit and also isolates the transistors from one another.

SPC:

Statistical Process Control. The application of statistics to build quality into a manufacturing process and product. Processes are reacted to before they are in an out of control condition. This is an entire manufacturing philosophy.

**SWEAT**

Standard Wafer-level Electromigration Acceleration Test - A test methodology and types of structure used in accelerated electromigration lifetime testing.

**Test Structure:**

A specific sub-circuit that is designed to test for one particular failure mode or to provide specific data. These structures can either exist on a die or in the scribe line area.

Thin Film:

A very thin layer of material deposited in a substrate, usually in the order of microns thick.

Transistor:

A semiconductor device that acts primarily as an amplifier or a switch.

ULSI: Ultra large Scale Integrated circuits. This refers to the fabrication of circuits

containing a high number of devices. Usually refers to over 100,000 logic

gate devices.

Via: A hole in the interdielectric material to allow one layer of metal interconnect

to connect with another layer of metal interconnect.

VLSI: Very Large Scale Integrated Circuits. This refers to the fabrication of circuits

containing a high number of devices. Usually refers to over 10,000 logic

gate devices.

Wafer: A thin disk of semiconductor material in which many chips are fabricated at

one time.

Wafer The processes in which the desired integrated circuit is manufactured and

Fabrication: fabricated into a wafer.

Wafer Sort: The functional test that is done at the wafer level to determine which die are

operating within normal specified parameters.

Yield: The number of good devices or parts at the end of a process.

#### **CHAPTER 1**

#### INTRODUCTION

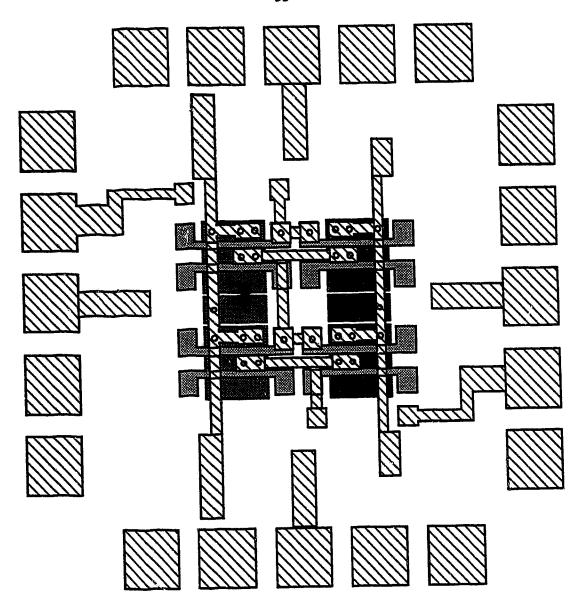

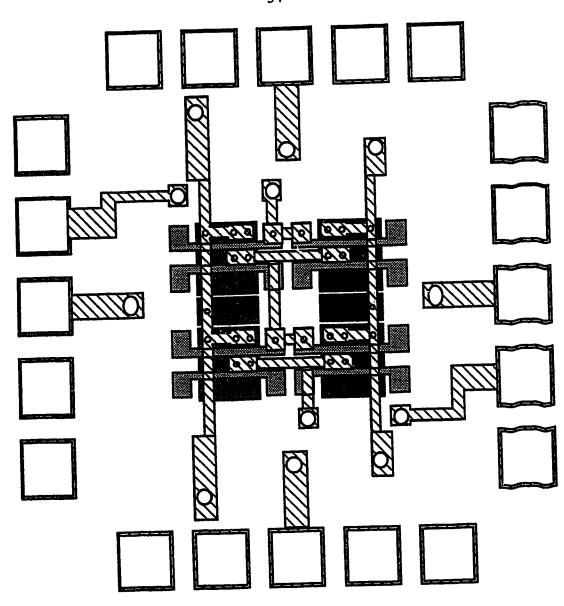

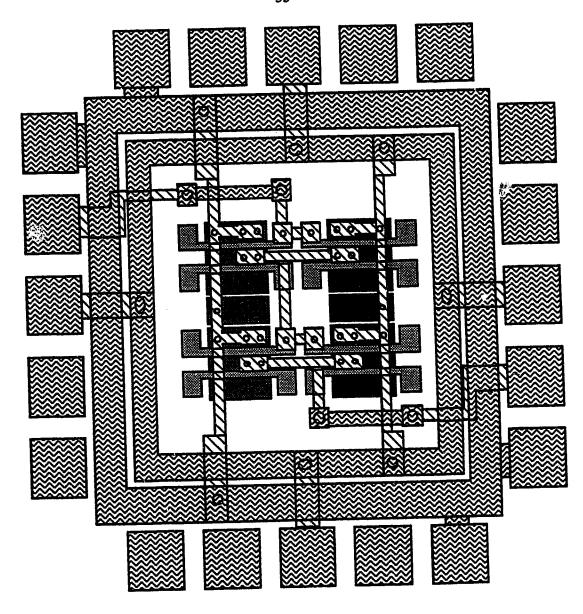

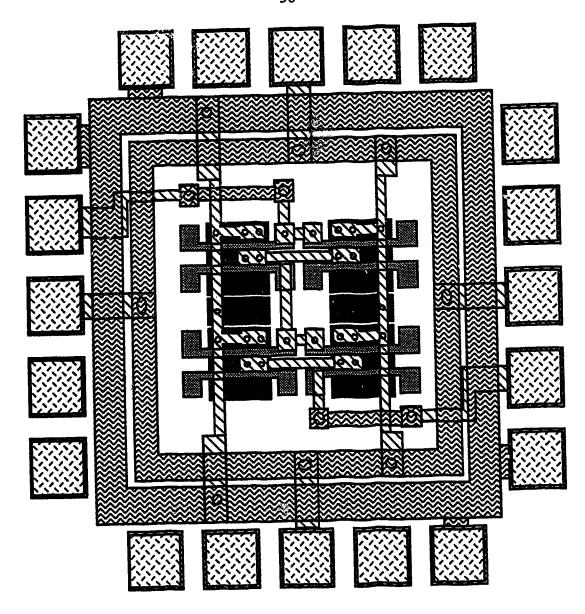

The manufacturing of Semiconductor circuits is a complex, highly technical process. Todays industrial trends are to fabricate more complex circuits with smaller and smaller geometries and with more complex combination of materials and layers. These Integrated Circuits, (IC) are manufactured on wafers. A wafer contains many die (i.e., die are called ICs in the final stages of fabrication) which are the individual circuits being constructed as illustrated in Figure 1.1 with various test structures for Wafer Level Reliability. All the die on a wafer are usually duplicates of the same circuitry and design.

Not all of the die on a wafer will function upon the completion of the manufacturing process. The number of working, functional die on a wafer is referred to as the wafer yield. For a completed circuit to work, all of the individual circuits that make up the die must be fully functional. A defect is a physical imperfection on a die that can cause part of a circuit not to work. A killing defect is a defect that actually prevents the circuit in question from working. In a working die, there must be no killing defects on the die. Defects do occur on die but are located such that they do not interfere with the operation of the circuit in question. These defects are called non-killing defects and do not reduce the yield of the wafer.

The wafer sort yield of a wafer is determined by fully functional testing of every die on the wafer with a tester and a test program upon completion of the manufacturing processes. After wafer sort testing, the ICs are tested again after each die has been packaged and the results are called Final Test. An IC is working, but for how long? Some non-killing defects can cause infant mortality reliability problems or early wear our reliability problems that significantly reduce the life expectancy of the IC. These failures are a major problem in the semiconductor industry

Figure 1.1 Exploded view of a die on a wafer with test structures

# 1.1 Yield and Reliability

In semiconductor manufacturing, the yield and reliability of the parts have been traditionally treated as separate issues. It was believed that the defects that caused yield problems could be

detected at the wafer sort step of the fabrication process and the reliability of the parts (i.e., individual ICs) was tested through burn in procedures. These procedures control infant mortality and collect data on circuit lifetime. The feedback from the burn in procedures was communicated to the engineers involved with the processing set up and control. The processing engineers tended to be more concerned with the immediate yield concerns and keeping their processes in control. Traditionally, reliability tasks involved initial burn in of finished parts to detect and weed out infant mortality failures and involved life time testing though accelerated stressing of the ICs and re-testing the ICs after the stressing. The wafers tended to be sampled from lots and these life time tests results were not known for a period of months. This delay prevented immediate feedback to correct out-of-control manufacturing processes.

But the industry has changed. Some of the assumptions that were valid five and ten years ago are now questionable. The majority of defects in the past tended to be infant mortality [1], e.g., similar to human life expectancy. The IC parts are now more sensitive due to the smaller geometries. The defect densities have decreased, enabling semiconductor factories to get yields on devices that were considered impossible several years ago. This has meant that there has been a shift towards more early wear out reliability failures. These early wear out failures (i.e., life expectancy greater than infant mortality) are becoming more dominant than the infant mortality failures that were seen in the past [1]. Because the dimensions are smaller, the parts are more susceptible to failures associated with current densities, materials, material stresses, etc.

Another issue of significance is that more processing is now done in a single wafer than ever before. The sampling plans for reliability were generally based on a lot by lot bases. Now the processes that individual wafers may see within a lot may have more variability than the variability in processing wafers from lot to lot. Some sampling plans that are based on lot variation may now be invalid. [1].

One of the biggest factors influencing the reliability picture of semiconductor devices is that customers are demanding higher quality than ever along with higher assurances of quality at an ever decreasing cost. To insure higher levels of quality through testing and yet continue to reduce the cost of the final product is an almost impossible task. To sample more ICs the

traditional way that reliability testing was done costs more.

The answer? The semiconductor industry is working on incorporating more Wafer Level Reliability testing into the manufacturing processes. What Wafer Level Reliability testing refers to is the design of test and test structures that are sensitive to known physical attributes, that are carefully tested to control the stress variables and that promote a single primary failure mechanism while minimizing other failure mechanisms. These are placed on wafers that contain production die. These test structures are tested on a parametric tester. To test on a parametric tester, the structures and the tests have to be designed so that the tests can be performed quickly, usually in under a minute. The principle behind wafer reliability testing is the continuation of building in quality. It is being proactive rather than being reactive.

Traditionally, testing for product lifetime meant a life test through the use of five common types of stressing on the parts – temperature, voltage, current, humidity and temperature cycling [2]. Most product lifetimes are determined through temperature acceleration, based on the Arrhenius Equation [3]. Parts (i.e., ICs) are "burned in" to determine their lifetimes. Burn in refers to placing packaged parts in a burn in oven operated at elevated temperatures (e.g., 125°C), powering the parts up, and periodically testing the parts during the time terminated failure tests (e.g., common test procedures are terminated at the end of 1000 hours).

Upon failure, analysis is done to determine the defects that caused the failure. The procedure of burn in and analysis usually takes a period of months to complete. Most semiconductor manufacturers today adhere to an industry accepted military Standard MIL\_STD\_883 [4]. This involves a 1000 hour operating life test at 125°C. The problem is that the time involved here is a period of months. With the complex processing that is going on in todays semiconductor manufacturers, many unreliable products can be produced during this period before manufacturing problems are detected and rectified. This is a costly proposition for the semiconductor industry. The feedback from a single problem could take months. With Wafer Level Reliability testing, rapid feedback is now possible. Wafer Level Reliability will not replace the traditional burn in testing that is done for both infant mortality and long term life time testing, rather it will supplement this testing. It will provide additional data over a larger sample size that will ensure outgoing quality levels and provide quick feedback to control

the on-going manufacturing process.

#### 1.2 Wafer Level Reliability

Wafer Level Reliability is the testing of structures at the wafer level to determine reliability. Traditional semiconductor reliability testing has identified certain reliability failure mechanisms. Test routines and test structures have been proposed to test for these failures at a wafer level. These test routines and structures have been designed to allow for quick testing by a parametric tester. A parametric tester is a tester designed to test the electrical characteristics of semiconductor parts.

Wafer Level Reliability uses the combination of test structures and electrical stress to test for known reliability failures. The types of failures that these structures detect are: failure in metallization due to electromigration, stress voiding, contamination; failure in dielectrics due to trapped charges, radiation damage during processing, impurities, film stress; and failure in transistors due to hot electrons, ion impurities and improper processing.

#### 1.3 ASIC Circuits

ASIC manufacturing is the manufacturing of Application Specific Integrated Circuits. Each product manufactured is a different chip. These are custom chips that are manufactured specifically for individual customers. This differs from other semiconductor manufacturers who manufacture standard devices where large quantities of a few designs are manufactured for multiple customers. There are basically two types of custom chips manufactured: array based and cell based [6]. Array based designs have the customized layers as the metal interconnection of circuits only. Array based designs have base array wafers. These base array wafers are used by multiple customers. They are only finished up to the transistor level and have the building blocks such as transistors, logic gates, memory, etc. are predefined. The designer customizes the circuit by specifying how these blocks are interconnected. Cell based designs are fully customized with the designer choosing which building blocks to use and the interconnection of them.

# 1.4 ASIC Wafer Level Reliability

Variation of customers designs results in variations in yield and reliability. A specific design on a array ASIC can have its own yield and reliability problems that are not seen on another

design on the same base array. Todays ASICs are more complicated than they were ten years ago. ASICs now can contain on a single chip microprocessors, RAM, ROM, bipolar transistors, high current drivers in addition to the standard logic gates.

The problems with traditional Reliability testing through life time and infant mortality stressing are even greater with ASIC parts. There can be as few as two wafers run in a year for a particular design. ASIC manufacturers tend to have a great number of designs with just a few wafers each being manufactured for those designs at any given time, than do manufacturers of standard parts.

The traditional sampling plans for testing reliability failures through burn in are not adequate to account for all the different designs and circuits run in an ASIC plant. They tend to test for generic process failures. In the beginning of the ASIC manufacturing this was probably a valid assumption, but with the complexity of todays ASICs, there is a variation of physical structure and function between designs such that this may no longer be valid. The reliability of one design may not mean that another design is reliable.

The answer to this problem is to do testing on all designs. This can be economically accomplished by Wafer Level Reliability testing. However, there are still unique difficulties and challenges to doing Wafer Level Reliability on ASICs. Specifically, Wafer Level Reliability has been done on standard products in production lines that have few designs. ASIC production has hundreds of different designs. ASIC production involves the use of base arrays. The challenge is in adapting the Wafer Level Reliability test structures to utilize the existing base array structures.

### 1.5 Thesis Objectives

This thesis is directed at investigating Wafer Level Reliability, a key new area in today's semiconductor industry. To fully investigate Wafer Level Reliability on ASICs, the following thesis objectives will be presented and discussed in detail:

To present the basic VLSI/ASIC manufacturing process knowledge base necessary to understand the types and design of circuits being developed today, the types of failures encountered, the methods and equipment that test the parts and the types of reliability screening and testing used.

- 2. Adaptation of existing Wafer Level Reliability test structures to an ASIC Base Array.

- 3. Development of Test Routines to perform Wafer Level Reliability using a Parametric Tester.

- 4. Evaluate the results of Test Wafer Chips that were tested for Wafer Level Gate Oxide Reliability. These wafers contained real ASICs that will be subjected to traditional reliability burn in and lifetime tests.

- 5. Compare test structure lifetime reliability data with the production ASIC lifetime reliability data.

The Wafer Level Reliability test structures are not the same as the structure of the production IC circuitry. Answers to the following questions will be presented and discussed in some detail in this thesis: (1) Will the test structures accurately predict product life time? (2) Do the results of traditional reliability testing correlate with Wafer Level Reliability predictions?

Wafer Level Reliability structures and test methodologies will be adapted to the ASIC manufacturing environment. Structures, test programs and test methodologies will be designed to work within the constraints of ASIC manufacturing. The failures predicted by Wafer Level Reliability will be compared with the failures on ASIC product that have been subjected to life time burn in reliability testing. This thesis will investigate Wafer Level Reliability and evaluate its adequacy in predicting lifetime failures and provide immediate reliability failure mode analysis to control wafer fabrication processes.

# 1.6 Scope of Thesis

Chapter II will describe the basic VLSI manufacturing processes necessary to understand the nature of defects that cause failures in semiconductor circuits. Chapter III will present the fundamentals on yield and reliability concepts and definitions. Chapter IV will present the

fundamentals of electromigration, a significant failure mechanism in very large scale integrated circuits. In this chapter a description of today's electromigration testing techniques will be presented. Chapter V presents the details of ASIC gate array Wafer Level reliability test chip design and layout incorporating electromigration, dielectric breakdown and hot carrier test structures. Chapter VI will present the basics of semiconductor reliability accelerated testing and monitoring. The fundamentals of the VLSI manufacturing processes, failure mechanisms, test chip design and burn in reliability presented in Chapter III to VI will provide a knowledge base for evaluating monitored processes and reliability test results. Actual normalized process monitoring and product reliability test results conducted on selected lots by LSI Logic Corporation will be presented and analyzed in detail in Chapter VII. Chapter VIII will present the conclusions and discussions of the thesis.

## CHAPTER II VLSI BASIC MANUFACTURING PROCESSES

#### 2.1 Introduction

In modern manufacturing and fabrication of Integrated Circuits, the production of cost effective and reliable working parts is the key to success. Over the last twenty years, the fabrication of Integrated Circuits, (IC) has gone from a fledgling industry to one of the most important and demanding manufacturing technologies in the world today. Today's ICs are larger, more dense, faster and require a higher level of manufacturing technology than even the circuits manufactured five years ago. To keep competitive, a manufacturer must have good yields. This means that a manufacturer must always try to maximize the number of good reliable parts. The yield is nothing more than the ratio of good parts to the total parts manufactured. This is not as simple as it sounds. With the increasing demands on performance, quality, cost and reliability of the finished ICs, yield becomes extremely important and harder to maintain. The state-of-the art in terms of manufacturing continues to change quickly in the industry.

To properly examine what yield and reliability is in today's Integrated Circuit manufacturing technology, one must have a basic understanding of the manufacturing processes involved. There must be an understanding of the types and design of circuits being manufactured, the types of failures encountered, the methods and equipment that test the parts and the types of reliability screening and testing used. This interrelationship is becoming more complex. With the demand to make circuits better, faster, and with higher performance, understanding their interrelationships are important to understanding why integrated circuits fail. A basic overview of some of the processing steps is important to understand where circuit failures can occur.

#### 2.2 Clean Room Technology

In today's Integrated Circuit (IC) manufacturing sechnology, ICs are manufactured in factories that contain clean rooms. A clean room is a room which the a controlled environment that is compatible with the requirements for manufacturing of Very Large Scale Integrated circuits (VLSI) and Ultra Large Scale Integrated circuits (ULSI). Most manufacturing of VLSI and ULSI involves dimensions in the one micron and sub-micron regions. Therefore, controlling the environment is critical in obtaining working circuits. To what level is the invitational controlled? The level of control of the environment is partially dependent on the processing steps that are being performed in the particular clean room or clean room module in question. Most clean rooms are controlled by microprocessor controller systems that monitor and adjust the environment in the clean rooms to a high degree of accuracy.

Traditionally, clean rooms were rooms that had just the level of airborne contamination minimized and controlled. By controlling the level of airborne contamination, the number of defects due to these particles of contamination getting into the circuit is reduced. Airborne particulate levels are controlled by having a laminar air flow within the room. Motor blower units force air through Hepa filters. These Hepa filters filter particles of size 0.1µm and larger. By having a laminar flow of air, the rooms tend to clean themselves and any airborne particulates are swept away in the air flow. These particulates are eliminated.

But the cleanliness of air is not the only factor that must be controlled in order to make a clean room "clean". The materials that go into construction, the tables used, the process equipment and any other material must be clean room compatible. That is, all objects, including people, in a clean room must be clean room compatible. To be clean room compatible is to be particulate free. All tables must be constructed as to not hamper the flow of the clean air. All people in the clean room must wear garments that are not particulating called clean room garments or "bunny suits". Even though it is impossible to entirely eliminate contamination within the clean room, the goal is to minimize the sources of contamination as much as is practical.

In addition to cleanliness, there are other environmental factors that must be controlled in VLSI and ULSI fabrication facilities of today. Temperature is a factor in many processes. In most photolithography areas, the temperature must be controlled to  $\pm 0.5$  °C to keep the sensitive

photolithography camera systems in focus. Humidity is also an important factor. Photoresists used in today's process can absorb moisture or dry out changing the photo speed of the resist and also changing its ability to resist etching processes. As has been seen, a clean room is not only a room that has Hepa filtering and laminar flow, it has evolved with the technology to become a controlled environmental area that is conducive to the manufacture of large circuits with very small structure dimensions.

But controlling the environment inside the clean room is only part of the challenge. The facilities that supply the clean room and the process equipment must be of a very high purity level. These can be another source of contamination. Some examples of what these facilities are: Clean dry air, Pure Nitrogen, Process Gases, De-Ionized (DI) Water and House Vacuum. Clean dry air is used to run pneumatics on the various process equipment used in the manufacturing of ICs. Pure Nitrogen is usually 99.9999% pure and is used in almost all processing equipment for venting from vacuum, purging, etc. DI Water is De-Ionized Water and has been filtered and purified through reverse osmosis and passed through resin beds. The water's purity is measured by its resistivity which for VLSI and ULSI is  $18 \text{ M}\Omega$  (Megaohms) pure. The house vacuum is a source of vacuum to hold wafers in place during regular process steps.

In addition to these facilities, there are chemicals and ultra pure gases that are used in the processes themselves. These have to meet stringent requirements as to their composition and as to their level of contamination or impurities. The process equipment itself must be designed and constructed to very strict requirements. They must perform the processes in question, be compatible with the clean room environment and handle see wafers in such a fashion as to minimize the amount of contamination on the wafers.

The demanding requirements of VLSI and ULSI manufacturing technology puts high demands on the environment and processes that are used in this manufacturing. The clean room and its facilities are as important as the processes themselves. If an essentially contamination free environment and contamination free processes do not exist, then there will be very few working parts out of the factory. Clean rooms today have to provide this very high level of environmental purity and control to be able to manufacture the highly complex circuits.

### 2.3 Basic Semiconductor Processing

In order to properly understand the nature of defects that cause failures in semiconfector circuits, there has to be a fundamental understanding of the basic processes involved in the manufacture of these circuits. As the complexity of the circuits increase, so do the amount of process steps required to manufacture the circuits. With more steps, there are more chances for problems, mistakes and misprocessing to occur. To understand the failures caused by these difficulties, one must understand how the basic process steps are performed.

In Integrated Circuit (IC) manufacturing, circuits are constructed in a layer by layer process. For example, a metal interconnect layer is first constructed before an insulator layer with via holes is constructed. One layer is finished before another is built. Even though there are many steps to building a completed wafer with working circuits, most of the steps fall into four basic processes: Thin Film Deposition, Photolithography, Etching, and Ion Implantation and Diffusion. A basic understanding of the fundamentals of these processes is important to understanding the failures that can occur because of these processes.

# 2.3.1 Thin Film Deposition

Thin film deposition is one of the "four" basic processes. The thickness of films used in semiconductor technology usually ranges in thickness from hundreds of Angstroms to a few microns. Hence the name, "thin films" because of the small dimensions. Thin films have unique properties because of their very thin nature. This allows atoms and ions to move around and diffuse easily. Properties such as this in thin films can cause yield and reliability problems. Many factors have to be controlled in the thin films that are deposited. Factors such as film composition, film stress, film grain size, thickness of the film, purity of the film, uniformity of the thickness, and the film density can all be important. The critical factors are dependent upon the process, circuit design and the intended use of the film in question.

Wafers are constructed in a layer by layer process. The layers are built up through subsequent depositions. The layers have different materials deposited to give the desired properties that each individual layer requires. For example, polysilicon and metals are used for conduction, oxides and nitrides for insulation.

Oxidation is one method used to grow thin films, especially in Silicon MOS technology. Silicon dioxide, SiO<sub>2</sub>, is grown thermally in the presence of oxygen on silicon wafers. Silicon dioxide is commonly referred to as "oxide" and silicon nitride is commonly referred to as "nitride" in the industry. Three things are needed for oxidation of a silicon wafer - a source of oxygen, energy (usually thermal energy in the form of heat) and a silicon substrate. Oxygen comes from using oxygen gas or water vapour. With the assistance of heat, the oxygen diffuses through the already grown oxide and reacts with the silicon to form more oxide. Silicon is consumed in the process.

Chemical Vapour Deposition is another method of depositing thin films. Films are grown in a reactor by having process gases react and form on the wafer. How the reaction takes place depends on the type of reactor and the film grown. There are three basic types of reactors used: atmospheric chemical vapour deposition (CVD), low pressure chemical vapour deposition (LPCVD), and plasma assisted chemical vapour deposition (PECVD). LPCVD is done under a vacuum, hence the name "low pressure". PECVD uses radio frequency power to ignite the process gases into a plasma state. Heat was usually used to provide energy for the reactions to take place. In PECVD, the plasma provides the energy for the reactions. The reactor used depends upon the film grown and the process goals.

Evaporation is a traditional technique used in the deposition of metals on wafers in semiconductor processing. Metals that have been commonly used are aluminium, copper, tungsten and gold. Evaporation is a technique that uses a high vacuum chamber. The metal to be deposited is heated in this high vacuum. The metal is heated through a number of different means and is referred to as the source. The metal evaporates in the high vacuum and is deposited on the wafers.

Another technique for deposition of metals is called sputtering. In this procedure, ions are accelerated through a high vacuum and strike a target. The target is made up of the metal that is to be deposited. The momentum of the ions are transferred to the atoms of the material and the material is transferred in vapour form to the wafers. The ions act as "bullets". Argon is typically used in sputter systems to act as the accelerating ions, or "bullets". The ions are accelerated through electric and or magnetic field attraction. The metal can be titanium, platinum, gold, tungsten, copper, aluminium, etc. This procedure is a purely physical phenomenon, involving no

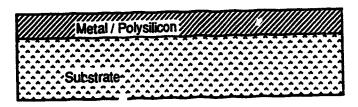

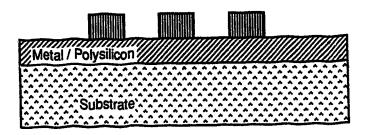

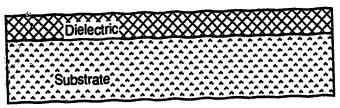

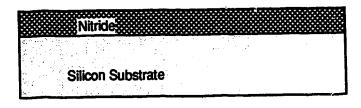

chemical reactions. To define a line in a material such as polysilicon or aluminium, the material is deposited on the previous layers or substrate first. The result of this deposition is shown in Figure 2.1.

Figure 2.1 Step 1 - metal / doped polysilicon deposition

Through all of these techniques, the materials or thin films that are used in the manufacture of ICs are deposited on wafers. The uniformity and control of the composition of these films are critical. Any impurities or mistakes in either the composition or deposition of these films may cause defects that will affect the yield and reliability of the finished ICs.

#### 2.3.2 Photolithography

Photolithography is the process used in IC manufacturing to transfer the design for a particular layer into photoresist on a semiconductor wafer. Since the majority of manufacturing done in the world today is on optical steppers, this is the type of system that will be described here. The principles are the same for projection aligners, direct write Electron Beam systems and other pattern transfer systems. The goal of photolithography is to accurately reproduce on the wafer the circuit layout in photoresist for the particular layer in question. The photolithography step is repeated many times throughout the process. The photoresist is used to resist etching materials or to prevent underlying layers from being damaged or doped during ion implantation.

The pattern that is to be reproduced is usually on a glass and chrome plate and this plate is referred to as a mask. A mask can consist of one layer of a single die or one layer of a few die. Some masks even have multiple layers on them, but all masks have only one layer used at a time. It depends on the size of the die being manufactured and the photolithographic camera equipment for the number of die exposed at one time. Most steppers today have a maximum field size of 1.5 cm by 1.5 cm. Some new steppers can go as big as 2.0 cm by 2.0 cm. A field is a region on a mask that consists of a single layer for one or more die that is exposed in a single exposure by the

camera system. The size of the fields are limited by the lens technology.

A stepper is a camera system that operates in the following fashion. The stepper first finds alignment targets that have been defined at a previous layer. It then uses these targets to line up the layer with the mask that is to be exposed. When the alignment is within the machine's alignment tolerance, an ultraviolet light is projected through the mask and onto the photoresist on the wafer, thus exposing the wafer. The stepper system then "steps" to the next alignment site. One or a few die are exposed at each exposure.

The reason why the best steppers in the world today only have a field size of 2cm by 2cm is because this is the area in which the stepper manufacturers guarantee minimum distortion. Distortion in the lens will cause errors in the reproduction of the mask image on the wafer. This distortion can cause various defects in the finished IC.

Even though an individual lens element within a lens system can not be manufactured without distortion, a particular lens element can be manufactured with a known distortion and another lens element with the opposite lens distortion. These two particular lens elements may be part of a lens system that makes up the stepper lens. The cumulative effect of these two lens in a multi-lens element system is to minimize the distortion in question. It is through this highly specialized multi-lens element lens system that the effects of optical distortion are minimized. In todays leading edge stepper technology, the lens can consist of up to twenty elements. The design of these precision optics is another very sophisticated high technology field. The larger the field, the harder it is to manufacture a lens system free of defects.

It is important to understand some of the basics of stepper technology in order to understand some of the defects that are caused by mistakes in the photolithographic processes. If there are any problems on the mask or with the operation of the stepper, this can affect every die on all the wafers being run. The defect is not limited to a single or few die but is repeated through the stepping and exposing action of the stepper camera system. This kind of defect is referred to as a "repeating defect".

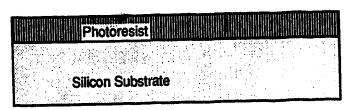

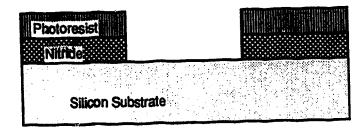

The photolithographic process consists of three basic steps - photoresist deposition on the wafer, exposing of the desired pattern on the wafer and developing and hardening the patterned photoresist that is on the wafer. A layer of photoresist is deposited on the wafer in a very uniform

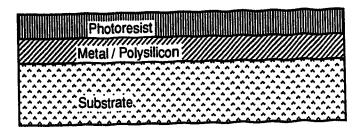

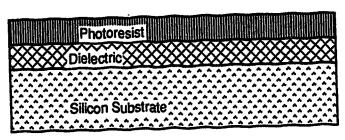

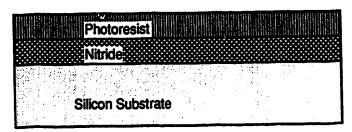

fashion. This photoresist deposition is usually done in the following fashion. The photoresist or resist is delivered in a solvent form to a spinning system. The wafer sits on a spin chuck and photoresist is deposited on the wafer. Through the action of spinning, the excess resist is spun off and a very uniform controlled thickness of photoresist is left on the wafer. The wafer is then baked to drive off the excess solvents. With too many solvents, the under exposed areas may mix with the exposed areas after exposure. By using the cross section diagram shown in Figure 2.1, the photolithography process of transferring a line pattern from a mask to photoresist can be illustrated. If we take the same substrate that was used in Figure 2.1 with its thin film on it and spin the photo resist on top, the cross section now will look like Figure 2.2.

Figure 2.2 Step 2 - photoresist deposition

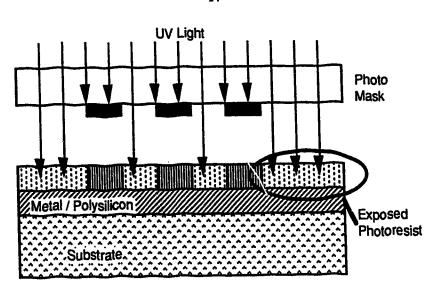

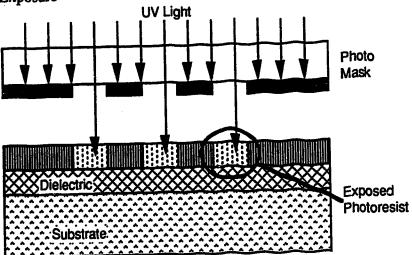

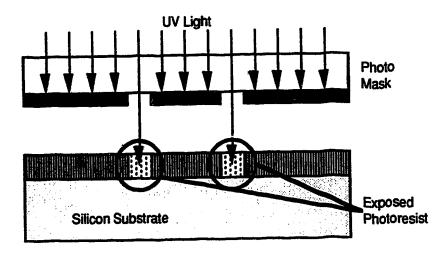

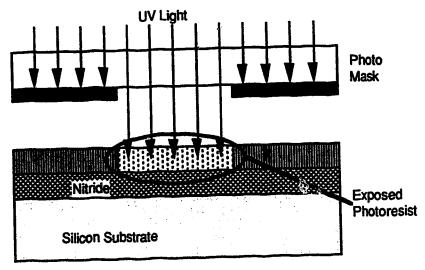

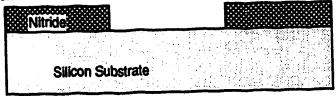

Masks for the layer in question are loaded into the stepper system. The wafers are exposed as described above. Photoresist (i.e., called resist) undergoes a molecular transformation called polymerization when exposed to ultra violet light. Exposed areas under go a chemical change. During developing, only the exposed pattern remains. If we return to our example of defining lines in a thin film material, the process of exposing the photoresist is illustrated in Figure 2.3.

Figure 2.3 Step 3 - photoresist exposure

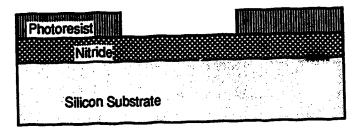

Through the process of developing, the undesired areas are washed away leaving only the desired pattern on the wafer in photoresist. The wafers then go through a hard bake process that hardens the photoresist. Hardening the photoresist makes the photoresist more resistant to the etching and implantation processes. Again after the developing, the cross section of our example now has the lines defined in the photoresist. This is illustrated in Figure 5.

Figure 2.4 Step 4 - photoresist develop

The processes described above is a basic description of the photolithographic processes. There are additional types of pattern transfer techniques that wafer fabrication factories may use, depending upon the application. The overview given above still applies in these more "specialized"

cases. Most photolithographic processes in production today are based on this "basic description."

## 2.3.3 Etching

Etching is the method of removing materials in semiconductor processing. Etching usually transfers the pattern that has been defined in photoresist into the material in question. The etching processes that do not transfer the patterns are usually blanket removal etches, such as the blanket removal etch of the photoresist.

Today, most etches are done with the use of excited gases through plasma etching. Plasma etching refers to the state of the etching gases. In a vacuum, etchant gases are excited through the application of electrical RF energy. The gases are in an excited, highly energetic state. The gases tend to exist in this plasma as single ions and atoms. These chemical species are highly volatile and react with the material placed in the etcher, such as the semiconductor wafer.

Different etchant gases are used for different plasma etches. For example, chlorine is used for aluminium and polysilicon, freons for oxide and nitride, and oxygen for photoresist. The goal of the plasma etching is to have the etchant gas in a plasma state, have the reactive species react with the desired material, and have the reaction by-products be gaseous so that they can be easily removed from the etching chamber. The material to be etched determines what chemical reactions will take place and therefore, what etchant gases will be used to form the reactions in the plasma etch chamber.

Plasma etching is not only the chemical reactions. With the application of RF electrical energy, ions are accelerated towards the electrodes in the system. The electrical bias on the electrodes will determine the amount of acceleration. Basically there are three types of plasma assisted etchers. The different types of etchers are defined by where the wafer is located in the etching system. Reactive Ion Etchers (RIE) have the wafer sit on the powered electrode. Here, the biases that are seen are usually in the hundreds of volts region. This high bombardment is generally used to etch species that are difficult to etch, such as aluminium. Aluminium is very difficult to etch because a native oxide, aluminium oxide, is formed on contact with oxygen in the air. This layer is very unreactive and requires high bombardment with the ions to be removed.

Plasma etchers are plasma assisted etchers that have the wafer on the grounded electrode. Here tens of volts of bias are used to accelerate the ions. These are lower ion bombardment machines.

The etch rate is more dependent upon the chemical reaction in a plasma etcher than in the RIE systems. They tend to run at higher pressures. The higher pressure means more reactants. This is how the plasma etchers etch materials as fast as the RIE systems.

Another type of etchers used in manufacturing of semiconductors is the down stream etcher. The wafers are "down stream" from where the plasma is generated. The excited etch species are created between the two electrodes. These species are then transported to the wafer where the reaction takes place. The wafers are situated near the vacuum source, and hence "down stream" from the area where the plasma gas is generated. The goal here is to have no ion bombardment and the reactions that take place are purely chemical in nature, and not ion assisted.

Before down stream etchers, purely chemical etching was done with the use of wet chemicals. Wet chemical etching involves baths in which wafers are submerged in the etchant solution or machinery that "sprays" the etchant solution onto the wafer. The wet chemical processes are generally harder to control and dirtier, but this does not mean that they are useless in processing. They do not cause any damage to the wafers through ion bombardment. Wet chemical etching is cheaper than plasma etching. This is how wafers were traditionally processed before plasma etchers were available. Wet chemical etching is still in use in most manufacturing processes today, usually in non-critical applications or applications that are sensitive to damage that a plasma assisted etcher may cause.

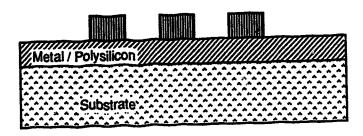

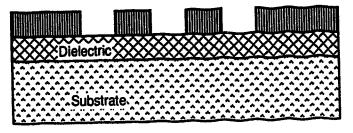

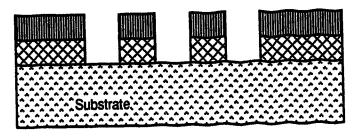

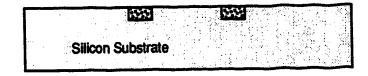

Most etching processes that define structures involve at least two etch steps. The first step involves the etching of the desired material. The pattern is transferred into the material because the photoresist protects the areas that are not to be etched. The second step of this etching process is the etching of the photoresist layer. Once the photoresist layer is removed, the only place where underlying material is left is where the photoresist was. This structure corresponds to the circuit design for that layer and the pattern that was on the mask. For example, metal lines are defined in aluminium by first etching the unprotected aluminium and then etching the photoresist that protected the aluminium. After this step, there are the metal conductor lines left that correspond exactly to the lines on the mask and in the design. This is how the pattern is transferred from the exposed photoresist to the material layer. To illustrate this process, the example of lines defined in the photoresist defined in Figure 2.4 is repeated in Figure 2.5

Figure 2.5 Step 4 - photoresist develop

After etching, the cross section is altered to that shown in Figure 2.6

Figure 2.6 Step 5 - metal/polysilicon etch

The lines are now defined in the thin film (metal/polysilicon) to complete the process. The photoresist is then etched off or stripped. The final cross section is shown in Figure 2.7 below.

Figure 2.7 Step 6 - photoresist etch

The goals of the process determine which type of etcher to be used. Plasma assisted etchers allow the more precise control of etch rate, uniformity of etching across the wafer, the etch profile

and the selectivity of etch rates. The selectivity refers to the ratio of etch rates between two different materials. For example, the selectivity of aluminium etch rate to oxide etch rate is the ratio of these two etch rates. This is important in the etching of aluminium lines. Aluminium or its alloys are a common conductor used to interconnect circuits together in semiconductor processing. This is usually deposited on an insulator such as silicon dioxide, or "oxide". The goal of etching metal lines is to etch the metal and not the underlying oxide. Therefore, the selectivity of aluminium etch rate to oxide etch rate should be as high as possible, to minimize the etching of the underlying oxide. Etching too much oxide can cause the aluminium lines to lift or provide topology related problems at subsequent layers.

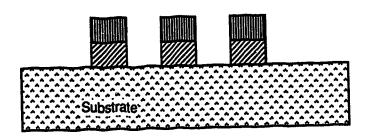

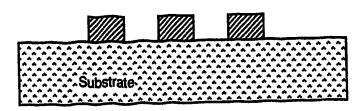

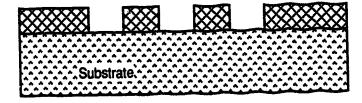

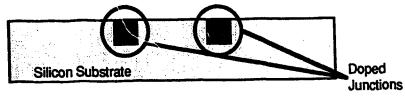

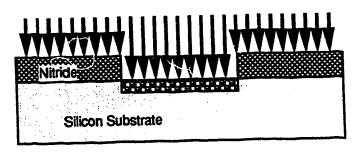

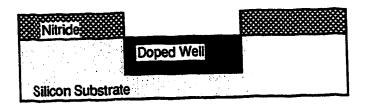

In the previous example, line were defined in a thin film such as a metal or polysilicon. The process is similar for holes in a dielectric such as silicon dioxide or silicon nitride. The entire process of defining holes such as contact or via holes is illustrated in the sequence of steps shown in the diagrams of Figures 2.8 and 2.9, respectively..

Step 1 - Dielectric Deposition

Step 2 - Photoresist Deposition

Figure 2.8 First two steps in defining a hole

Step 3 - Photoresist Exposure

Step 4 - Photoresist Develop

Step 5 - Dielectric Etch

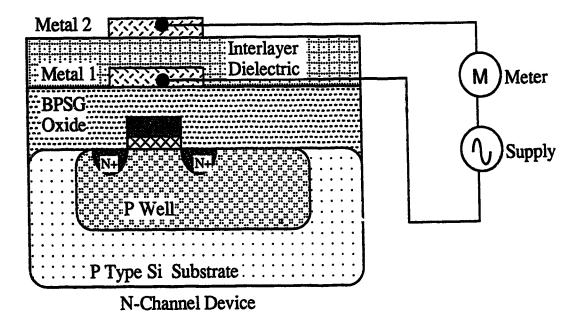

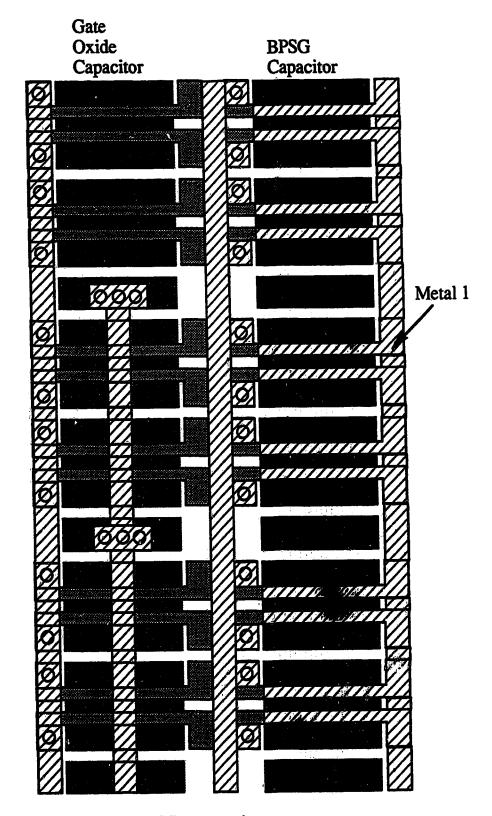

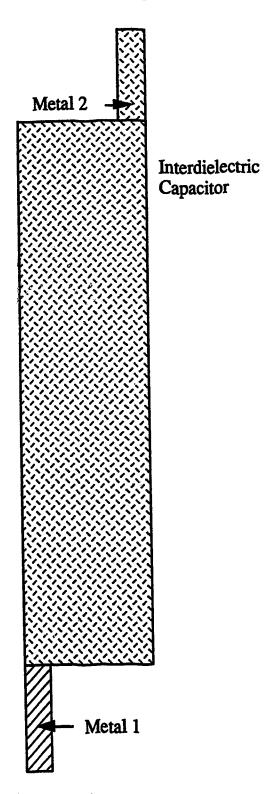

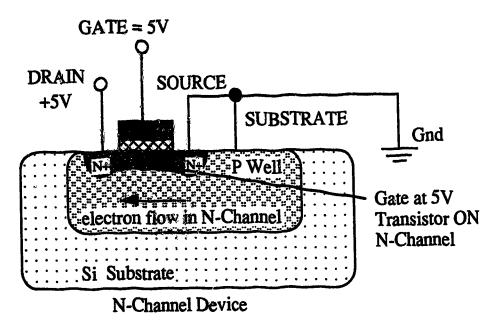

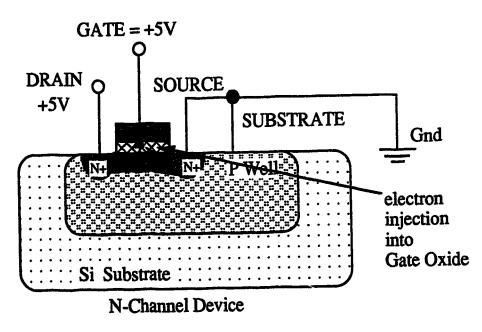

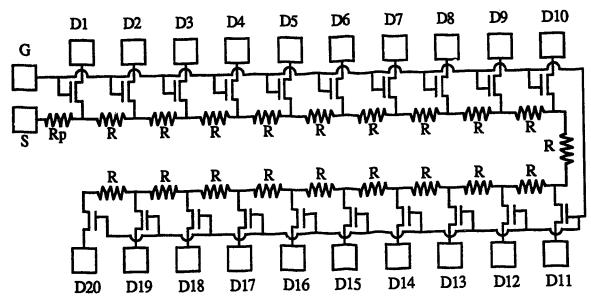

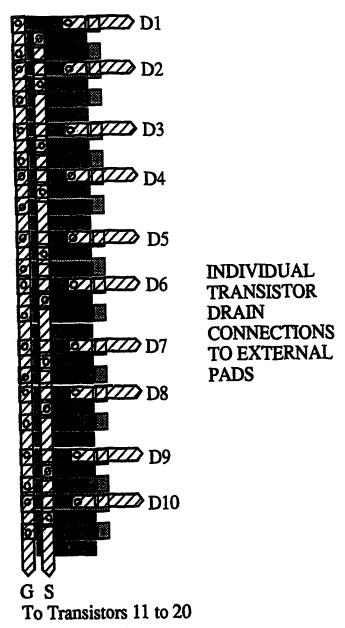

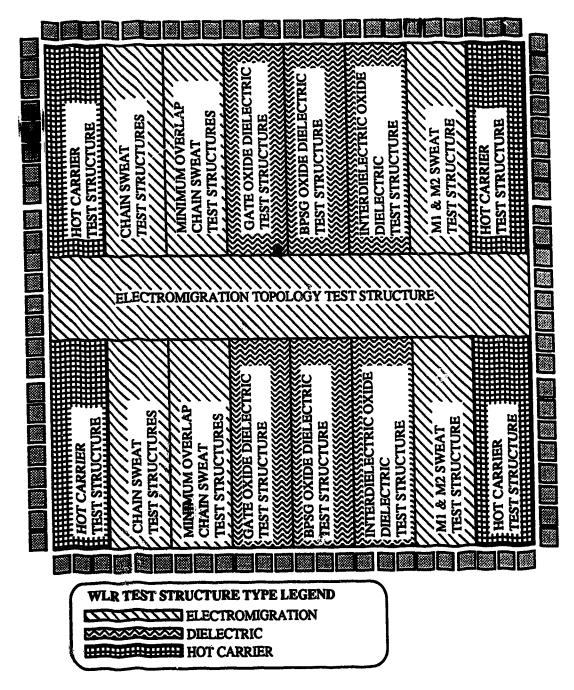

Step 6 - Photoresist Etch