## CANADIAN THESES ON MICROFICHE

I.S.B.N.

## THESES CANADIENNES SUR MICROFICHE

Canadian Theses on Microfiche Service

Ottawa, Canada K1A 0N4 Bibliothèque nationale du Canada Direction du développement des collections

Service des thèses canadiennes sur micròfiche

#### NOTICE

The quality of this microfiche is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages-were typed with a poor typewriter ribbon or if the university sent us a poor photocopy.

Previously copyrighted materials (journal articles, published tests, etc.) are not filmed.

Reproduction in full or in part of this film is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30. Please read the authorization forms which accompany this thesis.

THIS DISSERTATION

HAS BEEN MICROFILMED

EXACTLY AS RECEIVED

#### **AVIS**

La qualité de cette microfiche dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'univer sité nous a fait parvenir une photocopie de mauvaise qualité.

Les documents qui font déjà l'objet d'un droit d'auteur (articles de revue, examens publiés, etc.) ne sont pas microfilmés.

La reproduction, même partielle, de ce microfilm est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30. Veuillez prendre connaissance des formules d'autorisation qui accompagnent cette thèse.

> LA THÈSE A ÉTÉ MICROFILMÉE TELLE QUE NOUS L'AVONS REÇUE

National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Division

Division des thèses canadiennés

Ottawa, Canada K1A 0N4

56901

## PERMISSION TO MICROFILM — AUTORISATION DE MICROFILMER

Please print or type — Écrire en lettres moulees ou dactylographier

Full Name of Author - Nom complet de l'auteur

ALYNN BRETT KLASSEN

Date of Birth - Date de naissance

Country of Birth — Lieu de naissance

CANADA

18 FEB 51

Permanent Address — Résidence fixe

#1311,8510-111st

EDMONTON ALTA

766 IH7.

Title of Thesis — Titre de la these

S\*(QM-1): AN EXPERIMENTAL EVALUATION OF THE HIGH LEVEL MICROPROGRAMMING LANGUAGE S\* AVENTES THE NANODATA QM-1.

University — Université

UNIVERSITY OF ALBERTA

Degree for which thesis was presented — Grade pour lequel cette thèse fut présentée

M. 8 C

Year this degree conferred — Année d'obtention de ce grade

81

Name of Supervisor - Nom du directeur de thèse

DR. Subrata DASGUPTA.

Permission is hereby granted to the NATIONAL LIBRARY OF CANADA to microfilm this thesis and to lend or sell copies of the film.

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.

L'autorisation est, par la présente, accordée à la BIBLIOTHÈ-QUE NATIONALE DU CANADA de microfilmer cette thèse et de prêter ou de vendre des exemplaires du film.

L'auteur se réserve les autres droits de publication; ni la thèse ni de longs extraits de celle-ci ne doivent être imprimés ou autrement reproduits sans l'autorisation écrite de l'auteur.

Date

01 Sept 81

Signature

& Klassen

## THE UNIVERSITY OF ALBERTA

S\*(QM-1): AN EXPERIMENTAL EVALUATION OF THE HIGH LEVEL

MICROPROGRAMMING LANGUAGE SCHEMA S\* USING THE NANODATA QM-1

by

(C)

Alynn B. Klassen

#### A THESIS

SUBMITTED TO THE FACULTY OF GRADUATE STUDIES AND RESEARCH

IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE

OF MASTER OF SCIENCE

IN

COMPUTING SCIENCE

DEPARTMENT OF COMPUTING SCIENCE

EDMONTON, ALBERTA

FALL 1981

## THE UNIVERSITY OF ALBERTA

#### RELEASE FORM

NAME OF AUTHOR

Alynn B. Klassem.

TITLE OF THESIS

S\*(QM-1): AN EXPERIMENTAL EVALUATION OF

THE HIGH LEVEL MICROPROGRAMMING LANGUAGE

SCHEMA S\* USING THE NANODATA QM-1

DEGREE FOR WHICH THESIS WAS PRESENTED MASTER OF SCIENCE

YEAR THIS DEGREE GRANTED 1981

Permission is hereby granted to THE UNIVERSITY OF ALBERTA LIBRARY, to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly or scientific research purposes only.

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission. IDVI

(SIGNED)

PERMANENT ADDRESS:

Apt 1311,

8510-111 St.,

Edmonton, Alberta.

T6G-1H7.

DATED September 1, 1981

# THE UNIVERSITY OF ALBERTA FACULTY OF GRADUATE STUDIES AND RESEARCH

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies and Research, for acceptance) a thesis entitled S\*(QM-1): AN EXPERIMENTAL EVALUATION OF THE HIGH LEVEL MICROPROGRAMMING LANGUAGE SCHEMA S\* USING THE NANQUATA QM-1 submitted by Alynn B. Klassen in partial fulfilment of the requirements for the degree of MASTER OF SCIENCE in COMPUTING SCIENCE.

Supervisor

Workenft

. Truck a solicina

Date..... August. 6.,.. 1981

#### Abstract

The high level language schema S\* is a partially specified, machine-independent microprogramming language which is used as a tool in the development of machine-dependent languages. S\* is instantiated into S\*(M1), for a particular microprogrammable machine M1, by completing the language specification based on the architectural features of M1. The use of S\* is introduced in the context of the family of architectural design and implementation languages [S\*], using as an example the development of a language directed architecture.

A high level language S\*(QM-1) for nanoprogramming the Nanodata QM-1 is instantiated to determine the usefulness and viability of S\* based on actual experiences. During this instantiation we also focused our attention on the specification and underlying philosophy of S\* and (, investigated the process of instantiation.

We conclude that S\*, with several minor changes and additions, is indeed a valuable tool for the development of high level microprogramming languages. The parallel and sequential flow of control constructs play an especially important role in ensuring correct programs in S\*(QM-1). The adoption of a new construct parbegin is recommended for use in specifying a series of data independent statements which may be executed in any order allowing for the most efficient production of code possible.

## Acknowledgements

I wish to express my deep appreciation to Dr. Subrata

Dasgupta for his guidance, intellectual stimulation and editorial comments during the research and writing of this thesis. I would also like to thank Dr. John Tartar for his support during the initial research stage.

Special thanks are extended to the other members of the QM-1 User's Group, namely Steven Sutphen, Marius Olafsson and Douglas Rideout for their comments and criticisms during the development of S\*(QM-1). Thanks also to Leo Hartman and Chris Grey for their comments on the final draft of the thesis.

Finally, I would like to thank my wife, Angela, for her patience and encouragement during all phases of this work.

## Table of Contents

| Cha | apter                                                           | Page |

|-----|-----------------------------------------------------------------|------|

| 1 : | Introduction                                                    | 1    |

|     | 1.1 Thesis Organization                                         | 4    |

|     | 1.2 Background                                                  | 6    |

| 2.  | S* and the Process of Instantiation                             | 10   |

|     | 2.1 A Design Methodology                                        | 10   |

|     | 2.1.1 [S*] Family of Languages                                  | 10   |

|     | 2.1.2 A Design Approach to An Application Directed Architecture | 12   |

|     | 2.1.3 Users of S*(M1)                                           | 14   |

| ,   | 2.2 The Process of Instantiation                                | 15   |

| •   | 2.2.1 Goal Establishment                                        | 15   |

|     | 2.2.2 Arbitration Phase                                         | 17   |

|     | 2.2.3 The Testing Phase                                         | 18   |

|     | 2.2.4 Feedback Phase                                            | 19   |

|     | 2.3 S* Constructs and Some Recommended Changes                  | 19   |

|     | 2.3.1 The Declaration Block                                     | 20   |

|     | 2.3.2 The Execution Block                                       | 21   |

|     | 2.3.3 Recommended Changes to S*                                 | 24   |

| •   | 2.3.3.1 Reserved Words                                          | 24   |

|     | 2.3.3.2 Pre-defined Variables                                   | 24   |

|     | 2.3.3.3 Procedures                                              | 27   |

|     | .2,3.3.4 Branch Statements                                      | 27   |

|     | 2.3.3.5 Statement Sequencing                                    | 28   |

| 3.  | An Architectural Investigation of the QM-1                      | 30   |

|     | 3 1 Overview                                                    | 30   |

|    | 3.2 Nanostore and Control Store               | 3          |

|----|-----------------------------------------------|------------|

|    | 3.3 F-Store and Residual Control              | 5          |

|    | 3.4 Local Store and Data Transformations      |            |

|    | 3.4.1 Alu and Shifter                         |            |

|    | 3.4.2 MPC Unit4                               | 0          |

|    | 3.4.3 Index Alu                               | 1          |

| 4. | An Instantiation of S* to S*(QM-1)4           | 4          |

|    | 4.1 Introduction4                             | 4          |

|    | 4.2 The Declaration Block4                    | 6          |

|    | 4.3 Initialization Block4                     | 9          |

|    | 4.4 Éxecution Block5                          | 0          |

|    | 4.4.1 Assignment Statements                   | 1          |

|    | 4.4.11 Transfer Statements5                   | 1          |

|    | 4.4.1.2 Function Statements5                  | 3          |

|    | 4.4.1.3 Test Expressions5                     | 6          |

|    | 4.4.2 Procedures5                             | 8          |

|    | 4.4.2.1 Instruction Procedures                | 8          |

|    | 4.4.2.2 Subroutine Procedures                 | 0          |

|    | 4.4.2.3 Interrupt Procedures                  | <b>3</b> 1 |

|    | 4.4.3 Transfer of Control Statements          | 32         |

|    | 4.4.4 Conditional Statements                  | 33         |

|    | 4.4.5 Parallel Statements                     |            |

|    | 4.4.6 Case Statement                          |            |

| 5. | The S*(QM-1) Compiler                         | <u>3</u> 7 |

| `  | 5.1 A Partial Compiler                        | 36         |

|    | 5.2 Translation and the Intermediate Language | 7          |

|    | r o . The Compution of Inanclation            | 7 /        |

| 6. | . Conclusions                             |        |

|----|-------------------------------------------|--------|

|    | 6 1 Recommendations                       | 82     |

|    | 6.2 Future Work                           |        |

|    | ibliography                               |        |

| Βi | ibliography                               | 20     |

| ΑP | PPENDIX 1. SYNTAX AND SEMANTICS OF S*(QM  | -1),90 |

|    | PPENDIX 2. S#(QM-1) PREDEFINED DATA OBJE  | CTS133 |

| ΑF | APPENDIX 3. A SHORT PROGRAMMING EXAMPLE . | 139    |

### List of Figures

| Figure . |                                            | Page |    |

|----------|--------------------------------------------|------|----|

| 1.       | [S*] Family of Design Languages            |      | 11 |

| 2.       | Language Directed Architecture Development |      | 13 |

| 3.       | Process of Instantiation                   |      | 16 |

| 4.       | QM-1 Functional Components and Data Paths  |      | 31 |

| 5.       | MPC Incrementing Unit                      |      | 41 |

| 6.       | Operation of the Index Alu                 |      | 42 |

| 7.       | S*(QM-1) Language Model                    |      | 45 |

| 8.       | A Skeleton Program                         |      | 45 |

| 9.       | Jeclaration Block                          |      | 47 |

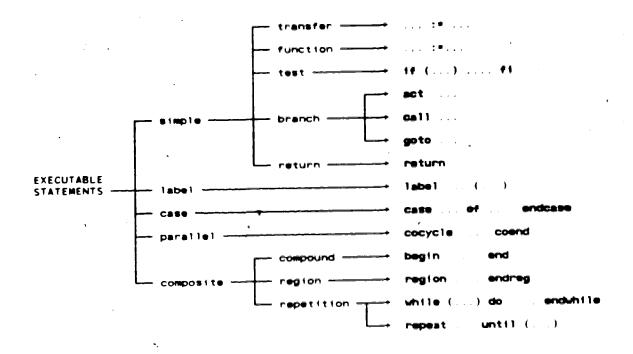

| 10.      | Exécutable Statements                      |      | 51 |

| 11.      | S*(QM-1) Nanostore Layout                  |      | 59 |

## Chapter 1

#### Introduction

The development of a computer architecture from its inception to final implementation is an intellectually difficult, time consuming and arduous task. To meet these challenges and produce a result which is correct, acceptable, and on time, the designer must rely on as many tools as possible. In the initial planning stages an overall design methodology should be selected which encourages communication and employs a hierarchical top-down approach with smooth transitions from the specification phase through progressively more complex levels. One such methodology, presently under development, is the family of design and implementation languages, [S\*] [DASG81a].

One member of the [S\*] family is the high level microprogramming language schema, S\*, which is to be the focus of this thesis. S\* was first presented by Dasgupta [DASG78] and:

... is a partially specified (and therefore, partially machine independent) language such that for a given host machine M1, a particular language S\*(M1) obtains when M1's properties are used to complete the specifications of S\*. We say that S\* is

instantiated into S\*(M1) with respect to M1.

As the above quote intimates S\* is not a panacea presenting us with the long awaited universal microprogramming language but attacks the problem of language development from a different direction.

In [DASG78] three ground rules are established upon which a microprogramming language should be based:

- a. The ability to construct control structures for designating clearly, and without ambiguity, both . sequential and parallel flow of control.

- b. The ability to describe and name arbitrarily, microprogrammable data objects or parts of such data objects.

- c. The ability to construct microprograms whose structure and correctness can be determined and understood without reference to any control store organizations.

With these points in mind S\* provides essentially a framework employing many programming constructs found in the high level block structured language PASCAL. These constructs have been added to, and tailored to meet the needs and requirements of the horizontal microprogramming environment where timing, data dependencies and resource

<sup>1</sup> Subrata Dasgupta, "Some Implications of Programming Methodology for Microprogramming Language Design", Microprogramming, Firmware and Restructurable Hardware, ed. G. Chroust and J. Mulbacker, (Amsterdam: N-H, 1980), p. 244.

conflicts play a significant role.

- Since its inception the language schema S\* has, except for a partial example instantiation for the VARIAN 75 [DASG78], remained untried and untested. The objective of this thesis is the evaluation of S\* using a threefold approach:

- To examine the specification and underlying philosophy.

of the high level microprogramming language schema S\*.

- To investigate the process of instantiation and tools which may aid in this procedure.

- 3. To draw conclusions about the usefulness and viability of S\* based upon experiences gained from performing an actual instantiation.

The Nanodata QM-1 [NANO79] was chosen as the experimental vehicle because it is widely recognized, with its 360-bit wide horizontal instruction word and use of residual control, to be one of the most difficult user-microprogrammable machines to program. With the successful development of an instantiated language S\*(QM-1), it would be reasonable to expect that the process of instantiation would be no harder for most other machines.

In addition, the benefit of a high level language for algorithm design and implementation would be invaluable for users of the QM-1 who up to this time have had to program in a low level nanoassembler language. The difficulty of learning and using this language goes a long way in

explaining why only one major project [DEMC76] has been completed since the QM-1 was purchased in 1973 by the Department of Computing Science at the University of Alberta.

To solve the problems involved with the development of a high level nanoprogramming language a QM-1 Architecture. Group headed by Dasgupta2 was established in September 1980. Two avenues of attack were chosen one of which was the design of a language and compiler. The other tackled the thorny problem of microcode compaction [RIDE81a] which deals with the detection of parallelism between microoperations which are then packed in the fewest number of horizontal words while at the same time remaining conflict free. Both endeavors have been progressing relatively autonomously with the only interaction being the development of an intermediate tuple-oriented language.

#### 1.1 Thesis Organization

A review of high level microprogramming languages is presented to provide the reader with a perspective of the language schema S\* with respect to related work in this field. The second chapter introduces S\* by placing it in the context of the family of design languages [S\*] and illustrates its use in the overall design and implementation of an application-directed architecture. This is followed by

<sup>&</sup>lt;sup>2</sup>Other members included Steven Sutphen, Marius Olafsson, Douglas Rideout, and the author.

an examination of the process of instantiation to shed light on the general approach to language design based on S\*. Next the description of S\* constructs is considered and based on this review and our experience with S\*(QM-1) some initial recommendations for changes in S\* are made.

Chapter three introduces the QM-1 and supplies the necessary architectural background so that language design decisions involving the instantiation of S\*(QM-1) may be understood. The more important factors affecting the instantiation are presented in the fifth chapter. S\* is expanded by adding several new constructs and a language which is solely procedure oriented is obtained, supporting the designer's objective for the QM-1 architecture. A complete description of the syntax and semantics of S\*(QM-1) is included in Appendix 1. Chapter six details the design of a compiler and associated preprocessor, and discusses the communication between the parsing and semantic analysis phase, and the compaction phase.

The final chapter discusses conclusions and recommendations about S\*, the process of instantiation, S\*(QM-1) and the QM-1. The QM-1 is included to show how slight modifications in its design could provide more flexibility in its use.

and the second of the second o

### 1.2 Background

The adaptation of high-level language constructs, structured programming and related concepts for microprogram development have been under active investigation since 1970. The motive behind this work is clear—these constructs and programming methods reduce the chance of errors through well structured programs which are easier to understand and modify. The programmer is freed from the more intricate details of coding, allowing a less complex transformation of algorithms into programs, resulting in a more reliable product.

Most researchers have been content to use constructs and methods employed in existing languages such as PL/1, ALGOL 60, and PASCAL. With the exception of S\*, little attention has been paid to implementing new constructs specific to microprogramming to supplement those in existing languages. Rather, researchers use these languages as a ready-made vehicle to support more complex fields of study. Three broad categories can be identified: detection of parallelism and optimization of microcode (efficiency), machine independence of microprograms (portability), and formal verification of microprograms (correctness). We shall briefly review five languages found in the literature and show how they have contributed to this field of study.

The first attempt at a high level language for microprogramming was MPL by Eckhouse [ECKH71]. The language was designed around PL/1 and addressed the problem of

machine independent programs for compilation into a vertical microinstruction format. It employed procedures with local and global variables based on six data types from register (one dimensional arrays) through events (machine, testable conditions) to constants. A limited set of constructs—if...then...(else), goto and assignment—are used; looping is accomplished using a conditional statement. The language is now of historical interest only as the difficulties associated with horizontal microinstructions, with several microoperations executing concurrently, soon became the center of attention.

SIMPL [RAMA74] was the first language to address horizontal microinstruction formats with the objective of writing machine independent programs using a sequential statement specification. A single identity principle based on the multiprocessing concept of the single assignment property was developed which ignored the ordering of statements and relied solely on data dependencies to perform microcode optimization. Constructs found in ALGOL 60 were used: if...then...else, while... do, for...do, and case statements for multiway branching. The controversy surrounding the goto was avoided by not including it in the language. No data structuring was available, variables were identified only with registers and the set of operators was fixed.

Three languages, two of which emerged from doctoral theses, followed the introduction of SIMPL. One, STRUM

[PATT76], was devised to provide a method for the formal verification of well structured microprograms. The language was machine dependent and implemented in the Burroughs D-Machine. A rich set of constructs derived from PASCAL were used: if....then...else, case, select, while...do, repeat...until, for...do, loop...pool, macros and procedures. Arithmetic operations were limited to those that could be accomplished in one pass through an ALU or shifter. The designer concluded that formal verification coupled with well structured programming was a realistic method for providing reliable, efficient microprograms.

The final two, EMPL [DEWI76a, DEWI76b] and S\*, address the question of efficiency and portability. Both investigators developed algorithms for the detection of parallelism from a sequential specification and proposed methods to handle portability.

EMPL's approach to portability is via the extensibility concept, such as is found in ALGOL 68, where a completely specified core language is extended by a programmer to customize it for use with a particular target machine. New data types, and operations which may be performed on them, are created to take advantage of particular micro-operations, such as a hardware instruction decoding unit, not directly supported by the core language.

Portability was assured by compilers, for machines without this direct support, by supplying code to implement the missing feature. The core language has limited constructs

(which may not be added to) and permitted only one core type, the integer and vectors of integers.

Dasgupta's approach was to implement two new parallel constructs cobegin...coend, and dur...do...end based on his work in developing algorithms for the detection of parallelism [DASG76] in sequentially specified programs. These would, for the first time, allow programmers the ability to explicitly specify parallelism within their programs. With these constructs in mind he developed a language schema, S\*, using data structures (the most powerful seen to date in microprogramming) and constructs from PASCAL which provide a partially specified "core" language. The language designer completes the syntactic and semantic definition of S\* for a particular machine based on its idiosyncrasies. Thus there would be a different language, but similar in its constructs, for each different microprogrammable machine.

### Chapter 2

## S\* and the Process of Instantiation

### 2.1 A Design Methodology

## 2.1.1 [S\*] Family of Languages

[S\*] is a family of design and implementation languages for the description and realization of computer architectures based on a unified top-down approach. It presently incorporates a three tier procedure where each lower level represents an increase in complexity with which the designer is faced. The transition from one level to the next is meant to be as smooth and natural as possible and is accomplished, in part, by having each language as similar, as may reasonably be expected, with the next.

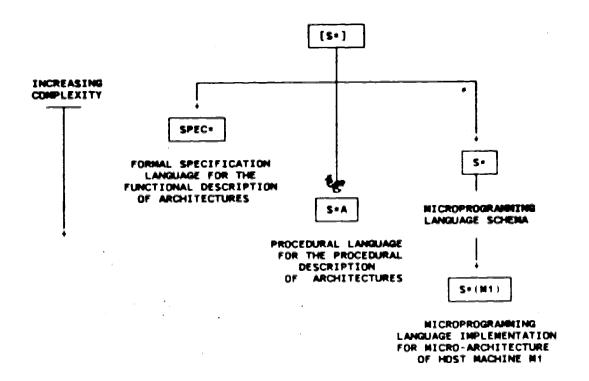

Fig. 1 illustrates the ordering of the languages with respect to their descriptive power. First, SPEC\* [DASG81b] permits the designer to formally specify the functional aspects of the architecture under design. The architecture is partitioned into integral parts with an input/output criterion being associated with each component. Each component states that for a given input, a specific output will result. Using this language a stepwise refinement is possible which allows the designer to begin with a global view (one component) and gradually increase the information content (many components) of his design.

At some stage in the architectural development the

Figure 1. [S\*] family of Design Languages

designer will want to actually indicate how component inputs are transformed to the outputs. This represents an increase in the information content (increasing complexity) from the SPEC\* description and is represented by a "program" written in the procedural architecture description language S\*A. Taken together SPEC\* and S\*A represent the design of the architecture.

The implementation of the design is the final and most complex of the three tiers and is based on the high level microprogramming language schema S\*. Simply put, this is a partially defined microprogramming language from which the designer constructs a language, S\*(M1), for programming the host machine, M1, upon which the architecture is going to be implemented.

The S\*A description is then transformed to the implementation language, S\*(M1), compiled and run on the host resulting in the realization of the architecture under design.

# 2.1.2 A Design Approach to An Application Directed Architecture

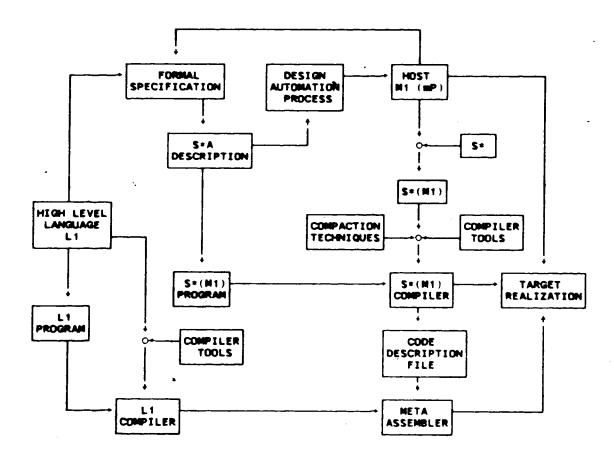

Applying the concepts introduced in the previous section an informal architectural design methodology for the implementation of a language-directed architecture may now be presented. As Fig. 2 illustrates the design begins with a high level language L1, such as Pascal or C. The instruction set, formats, and support systems such as the calling mechanism and minimum number of registers are carefully laid out. This is a complicated phase involving tradeoffs between such things as code density and opcode optimization [JOHN79]. A functional specification is then constructed for its architectural representation. This is then expanded into a procedural S\*A description.

One of two possibilities now presents itself: either a microprogrammable host machine such as the QM-1 will be chosen; or a design automation process will be selected to build the host based on the S\*A description. If an existing host is chosen it will, of course, influence the formal specification depending upon its inflexibilities.

In order to microprogram the host a high level language S\*(M1) based on S\* and the host's capabilities are

Figure 2. Language Directed Architecture Development

instantiated. A compiler is then developed for S\*(M1) using compiler tools, optimization and compaction techniques [LAND80]. The tools will save development time and the compaction techniques are necessary for the production of efficient code without which the compiler would be of little value. We are now in a position to translate, by hand, the S\*A description into an S\*(M1) implementation program which may be compiled and run on the host thus achieving the realization of the target architecture.

The user of the target machine may now write programs in the language L1 and compile them into an intermediate

language, such as an assembly language. The compiled code is then run through a universal, or META, assembler which uses as one of its inputs a code description file produced by the S\*(M1) compiler. This file provides the necessary information: opcodes, mnemonics, instruction sizes, and type of parameters, needed to perform the translation from assembly code to machine code. This file in effect allows the L1 compiler writer and the S\*A description implementor to be relatively autonomous in the detailed specification of the instruction set.

## 2.1.3 Users of S\*(M1)

A high level microprogramming language should allow the user freedom to express his algorithms in a clear, easy to understand fashion. This must be balanced with his need to exploit the machine to its fullest extent in the areas of sequential and parallel flow of control and resource usage. The implication of the previous two statements is that the programmer must have the fullest access possible to the machine which leads to the conclusion that the programmer must be as knowledgeable (at least initially) about the machine's characteristics as a microassembler programmer.

We view the S\*(M1) representation of algorithms to consist mainly of sequential statements, interwoven with parallel ones. These parallel statements are used only when the operations must be performed in parallel to maintain the correctness of the program. It is then up to the compiler to

compact the resulting (basically sequential) code into the smallest, correctly executable machine code possible. This sequential aspect of programming stems from the author's belief that programmers want to express themselves sequentially and do not want to be overly burdened by the (possibly) parallel aspects of their algorithms.

## 2.2 The Process of Instantiation

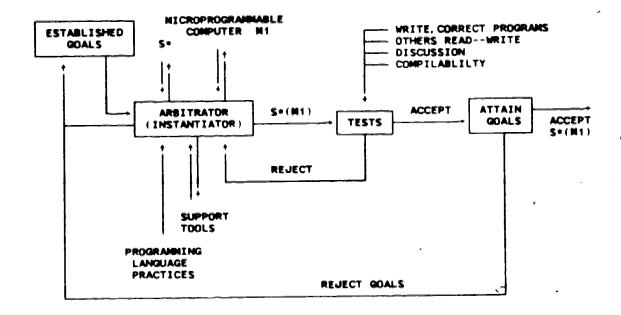

The process of instantiation, illustrated by Fig. 3, is considered to be evolutionary, in that several iterations may be required before an acceptable language is obtained. Four related phases, to be discussed in the following sections, form a method for the design of a language based on S\*, the host machine, and a variety of other factors. A method of feedback is established so that experiences gained from a particular instantiation need not be wasted.

Flexibility in approach seems to be a key to success and we have found that the UNIX [KERN81] operating system has allowed us to incorporate methods which permit changes to be made easily and effectively without an undue loss of time.

#### 2.2.1 Goal Establishment

The first priority of an "instantiator" concerns the determination of goals which will act as a guide through the complete instantiation process. They also help to assess, in the final analysis, if the language fulfilled its initial

Figure 3. Process of Instantiation

objectives.

The goals established for the S\*(QM-1) instantiation are:

- 1. A programmer using S\*(QM-1) must have the capability of writing well structured programs which may exploit the inherent parallelism of the QM-1 at the nano-architectural level, and yet would remain independent of the structure of nanostore and its associated sequencing logic.

- 2. The programmer, in designing programs, should be able to employ a hierarchical top down approach by which algorithms can be naturally transformed into S\*(QM-1).

- 3. A flexible manner of program representation should be available so that features such as residual control can be fully exploited.

4. Finally, magrams must be easier to read and understand than programs written in nanoassembler code.

#### 2.2.2 Arbitration Phase

Having established the language design goals we are now in a position to begin the instantiation itself. First, study the constructs and program structuring provided by S\*. Then couple this information with the micro-architecture of M1 trying to overlay the concepts supplied by S\* onto the capabilities of the machine. M1 should also be considered from the assembly programs that have been written (how it was used), and how it was originally designed to be used.

S\* constructs should now be mapped onto M1 with machine dependent constructs and statements added to complete the language specification. We take the view that initially the compiler should not retain any decision making duties, i.e. which ALU to use or which data path to select. Once experience has been gained a decision may be made relax this restriction allowing the compiler to perform certain decision activities, although with the understanding that no limitations should be imposed on the programmer.

Support tools now come into play, the advantages of which must be closely weighed against any restrictions they may impose. For example, in the instantiation of S\*(QM-1) the UNIX tools LEX [LESK79] and YACC [JOHN80] have been selected to aid in the construction of a parser and lexical analyser. The only restriction imposed was S\*(QM-1) had to be in the class of LR(1) grammars [AH079], which was not

considered to be a major drawback.

The compaction and optimization techniques which are going to be employed in the compiler should also be considered, since the language may not allow enough programmer control, i.e. it is too general, for effective compaction or optimization to be performed.

#### 2.2.3 The Testing Phase

The testing phase is important as the instantiator may, by this point in time, be locked into a mental set and feel that the language is quite acceptable when in fact it is not. The first step is to write correct programs and check them syntactically against the definition of the language. The compiler tools allowed the grammar to be built up in a manner (similar to a BNF definition) which could be used as an input specification for YACC and LEX so that the generated parser could perform syntactic analysis, at the same time as the language was being developed. The parser was modified to give better diagnostics of its actions, allowing errors in design and implementation to be quickly identified and changed.

A decision can now be made to accept or reject the instantiation. If the language does not meet the original design goals then either the goals are too broad or the language is not acceptable. It may also turn out that the goals were not broad enough and should be expanded to meet the instantiated language.

## 2.2.4 Feedback Phase

After having gained experience using the language schema, support tools and microprogrammable machine we feel it is the user's responsibility to provide feedback to the originators. This involves such things as additional constructs for \$\* resulting from new architectures or technological changes, or suggested changes to the microprogrammable computer which the original manufacturer did not envisage.

## 2.3 S\* Constructs and Some Recommended Changes

The objective of this section is to review S\* as it been presented in three papers by Dasgupta (see references) entitled: "Towards a Microprogramming Language Schema" (1978), "Some Implications of Programming Methodology for Microprogramming Language Design" (1980), and "Some Aspects of High Level Microprogramming" (1980). Based on this review we will conclude with some recommended changes to S\* which have been incorporated into S\*(QM-1), the syntax and semantics of which may be found in Appendix 1. In order to be concise and accurate and to aid in clarity, quotes in this section will be referred to directly, based solely on the page number provided.

S\* has been presented to the public in a semi-complete format with many formal syntactic and semantic definitions. On one hand this is a sensible approach as it allows some experience to be gained before S\* is formally 'cast in

stone'. On the other hand, without a formal syntactic and semantic document (schema definition) the potential instantiator is left with some discrepancies due to the construct and definition changes between the earlier paper (1978) and the later ones (1980). We shall discuss these points in detail and attempt to present a balanced and clear view of S\*.

The approach taken is top-down, beginning with a program definition, the basic form of which is prog {name};

<declaration-block>: (also known as <decln-block>)

<execution-block> end.

## 2.3.1 The Declaration Block

sequence of one or more data-object/synonym/procedure declarations"(151), or "is a sequence of declarations"(317). This block functions as a means of describing the resources of the machine to which the programmer will be referring within his program, that is "a microprogrammer must declare all data-objects before referencing them"(313). A resource is referred to as a variable data-object and is defined in terms of a data type. Data types, which are built up from the primitive data type--a bit (0,1), may be structured in terms of sequences of bits, arrays and associative arrays of more primitive types; stacks which permit only the top element of the resource to be accessed, and finally tuples(as in PASCAL records) which are resources consisting

of two or more variables of possibly different types grouped together under one name. An optional pointer, with ..., may be used to specify which data objects are used to access the stack or array. Also, a special class of variables called synchronizers is employed for synchronizing microprocesses.

Pseudovariables provide an abstraction of variable data objects which allow non-variable resources, such as bits in a microinstruction control field, to be used in the same manner as variables.

Once declared a variable data-object may be renamed by using the synonym declaration which may only appear in the declaration section or in a proc-head (to be explained below). Constant data objects are pre-defined, invariant and "correspond to a machine defined literal constant located in a read-only memory element" (146).

## 2.3.2 The Execution Block

The execution block consists of "a sequence of one or more regions, sequential microstatements or program

blocks"(151), or "is a sequence of executable statements"(317). Executable statements are divided into two groups: single microstatements, in turn divided into five subtypes which are dependent to some degree upon the instantiation: and composite statements consisting of parallel microstatements, or one of four other groupings of statements which are all fixed in S\*.

Simple statements are listed variously in "three classes" (146), or "four types" (314), and consist of transfer, function, primitive (simple) selection, procedure call and goto statements. The transfer statement is concerned with the direct data transfer from one resource to one or more other resources, whereas the function statement deals with data transformations determined by "primitive machine-defined operations" (146). We are informed that "primitive operators in the instantiated language are mostly contained in the operator set defined in S\*" (314) however these operators are not given in the literature.

The primitive selection is an order-independent, multiple if statement using single clauses, not unlike the PASCAL case statement, in which at most one of the multiple if conditions may be true at any one time. The action associated with a true test is a simple statement which may not be a primitive selection statement.

The method of procedure call varies from the earlier to the later papers. Initially we are informed that a procedure is invoked (called) by the "statement call "name" where "name" is a procedure name"(150) and later "A procedure call is simply denoted by a ... procedure name with or without parameters"(315) which indicates that the reserved word call is no longer required.

Parallel constructs begin as the simple concurrent microstatement cobegin ... coend, the local sequential parallel microstatement cocycle ... end, and finally the extended concurrent microstatement dur ... do ... end. These were deleted, modified and expanded (without the reader being explicitly informed) until there now exists a cocycle ... coend and stcycle ... end statement, where the cocycle takes the place of the old cobegin and cocycle, and stcycle replaces the dur construct. The cocycle handles the cases, of parallel and sequential micro-operations within a single microcycle and stcycle handles extended concurrency.

The use of 'D' (a new delimiter introduced in the 1980 paper) and ';' within a cocycle or stcycle indicates in the former that for a cocycle the statements must be executed together within a single microcycle and for the stcycle are to begin in the same microcycle but the time to termination is left unspecified. The ';' indicates for the cocycle that the statements are to be executed in a strict sequential ordering within a single microcycle, and for the stcycle the statements must begin in the specified order within a single microcycle but their termination is left unspecified.

The sequential microstatement begin ... end and region ... end constructs are basically directives to the compiler

1.7

that in the first case, statements within the construct should be optimized and in the second case the statements are order dependent and the sequential flow of control is to remain unchanged.

The generalized selection statement "which is simply a generalization of the primitive selection statement" (3.6) is introduced but not elaborated upon. The same holds true for the "parentheses" (316) do ... od. Finally we have the standard repetition statements while ... do ... and repeat ... until ...

## 2.3.3 Recommended Changes to S\*

The following catalog of recommended changes to S\* is based on the comments of the previous section and the experience gained with S\* in the instantiation of S\*(QM-1).

#### 2.3.3.1 Reserved Words

We recommend that the end reserved word be expanded wherever possible to aid in the readability of a program, for example a program should be terminated by endprog, stoycle by stend, while by endwhile. A complete syntactic list of reserved words used in S\*(QM-1) may be found in Appendix 1.

#### 2.3.3.2 Pre-defined Variables

All types, variable data-objects and machine-dependent constants should be designated by the instantiator (or

compiler writer) when S\* is implemented for a particular machine. They would thus constitute a formal pre-defined description of the machine indicating the totality of resources to which a programmer has access. In order to aid in the description of resources and do away with "host-machine defined" (146) synonyms an expanded method of data-object declaration is proposed where a single resource may be declared as a multiple grouping of type structures. This method of description is used in the S\*(QM-1) pre-defined data-objects to be found in Appendix 2.

To provide the reader with some idea of the nature of declarations, and to indicate the new method of specifying differently "perceived" register variables the structure of a register bank called *local store* is presented:

tuple

endtup

a : f\_register b : f\_register

| opcode      | : | seq | [ | 60. | bit |

|-------------|---|-----|---|-----|-----|

| a_parameter | : | seq | [ | 40  | bit |

| b_parameter | : | Seq | [ | 50  | bit |

| enditup     |   |     |   |     |     |

#### endtup

The method of referencing this type of multiple definition is as expected. We can say local\_store[2] to directly access the array data type or local\_store.index[3] or local\_store.instruction\_reg.b to access a tuple member. Where there is no naming conflict the tuple header name may be dropped as in instruction\_reg.b or simply b. The with pointer is used as an index for entering data into an array. Local\_store[feod] assumes that F-register FEOD (to be discussed later) has been assigned a value between zero and thirty-one; note that it is incorrect to say local\_store.general\_purpose[faod] as this pointer is not associated with that particular portion of the variable local store.

The scope of these pre-defined data-objects is global and the programmer retains the ability to rename them as he chooses using the synonym declaration, to aid in textual clarity. These synonym names are global if declared in the declaration block and local to a procedure if declared in a procedure head.

The programmer should also be able to define literal constants in the same manner that invariant read-only memory constants are declared by the instantiator.

A new construct should be added, declaration ... endec, to delineate the declaration block.

#### 2.3.3.3 Procedures

A new reserved word endproc should be used in place of reth which in turn should be expanded to return in order to signify a return is to be made from the called procedure. With the incorporation of declaration ... endec construct we recommend that procedure declarations should be made after endec but before any executable statements. We feel that the begin ... end construct is superfluous within the bounds of a procedure and may be left out if desired. The method of invoking a procedure is clarified in the next section.

#### 2.3.3.4 Branch Statements

A new type of executable statement should be incorporated into S\* consisting of the reserved words: call, return, act and goto. The call statement (call "name" where name is the name of a procedure) is used to call a procedure in such a way that control is returned to the next statement on procedure termination either through "falling out the bottom" (endproc) or after an explicit return statement is encountered.

act is used in the same manner as call and serves to activate a procedure with the understanding that control will not be returned, and as such it is up to the procedure to carry on the flow of control (this is essentially a goto to a procedure). The goto may only be used to transfer control within a procedure or execution block.

## 2.3.3.5 Statement Sequencing

The last recommendation concerns statement sequencing in relationship to the role of a compactor. We feel that the statement separator ';' should be limited solely to executable statements where its use will have a more pronounced significance. Its normal function will be as a weak sequential delineator indicating to the compactor that the statements are to be compacted as well as timing, data dependencies and resource conflicts will allow. Its use within the region construct indicating a strict sequential flow of control is to be maintained within the construct since the programmer may know of some conflict which the compactor would not be able to discover due to, possibly, residual control effects.

Once several statements are bound together by a region, stcycle, or cocycle constructs they may be compacted up into previous statements, or have statements compacted into them with the provision that the timing specifications within the construct are not be disturbed, and no other conflicts arise. As an example consider the following partial program:

#### endreg ;

S12 :

where the S's represent single statements. Statements S3, S4 and S5 must execute within the same microcycle and if there are no conflicts (data dependencies, resource contentions, or timing constraints) with S2, they may all be executed together (compacted up). S7 must complete execution before S8 commences and S9, S10 must execute together and may not start until S8 finishes. If no conflicts arise S7 may be executed at the same time as S6, and similarly S12 may be executed with S11 or even S7 if no conflicts arise with any intervening statements.

## Chapter 3

# An Architectural Investigation of the QM-1

This chapter presents the reader with a model of the QM-1 at the nano-architectural, or component and data-path level as seen by a nanoprogrammer. The intention is to provide a global view of the QM-1 in order that the reasoning behind certain S\*(QM-1) design decisions may be understood. Additional background material may be found in [AGRA76, SALI76]. The QM-1 Hardware User's Manual [NANO79] should be consulted for a more detailed account of the QM-1.

#### 3.1 Overview

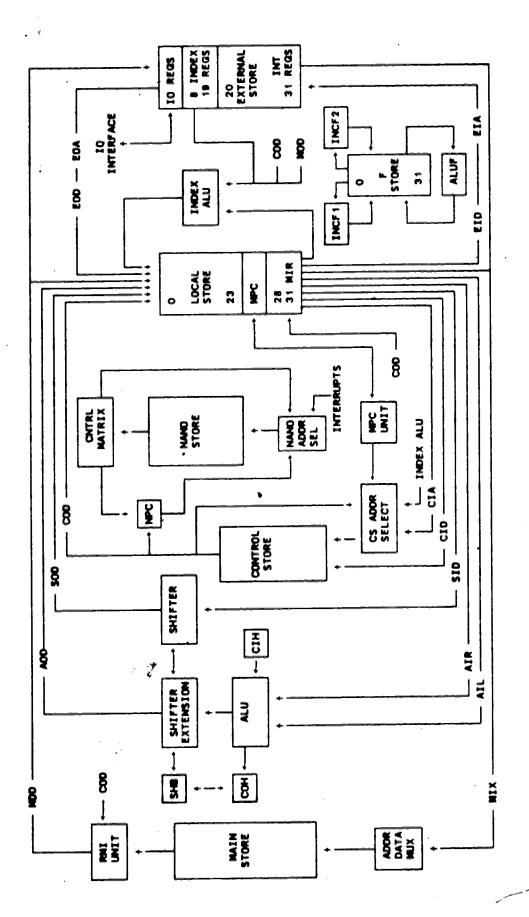

The QM-1 was designed as a user microprogrammable computer for indirect emulation of environments and existing computers and for the implementation of higher level languages, among other things [ROSI72]. As Fig. 4 demonstrates it is centered around local store, thirty-two 18-bit registers; and F-store, thirty-two 6-bit registers, which provide residual control and 6-bit temporary storage.. The 32nd local store register, R31, also acts as three 6-bit, (C, A and B) registers for communication with F-store.

The designers felt that, when emulating a computer, setup or residual control registers could be used to control data transfer paths, acting solely as indexes into local or

Figure 4. QR-1 Functional Components and Data Paths

external store. Once set, these registers would remain fairly invariant throughout the emulation, thus negating the need to place source and destination register fields in the nanoword [FLYN71].

The data transformers include a 6-bit ALU, two 18-bit ALUs, a shifter capable of eighteen or 36-bit shifts and a special local store incrementing facility. *External store*, thirty-two 18-bit registers, provides interrupt addressing and enabling, 18-bit constant storage, and an eight register external interface.

18-bit data buses are indicated, in Fig. 4, by lines joining components, with the data flow direction shown by an arrow. Each of these components operate in parallel and may send data to, or receive data from, local store independent of any other.

The QM-1 employs a three level memory structure in which the target machine, with its instructions in main store (18-bit 10 nsec memory), is defined and interpreted by a microprogram in control store (18-bit 164 nsec memory). Each 18-bit microinstruction, consisting of a fixed 7 bit opcode, a 5-bit parameter and a 6-bit parameter, is in turn defined and interpreted by one or more 360-bit nanowords [NANO79].

#### 3.2 Nanostore and Control Store

Nanostore contains up to 1024 360-bit nanowords, arranged in segments of 128 word pages. Each word consists of five 72-bit partitions: a K-vector and four T-vectors, T1 through T4. A priority selection mechanism determines which nanoword is to be selected for gating into the control matrix, where it becomes the active nanoword.

When a nanoword becomes active eight 6-bit constant fields from the K-vector, which may be considered to be stored in registers, are activated providing two constants, ALU and shifter control signals, and three test masks.

Alternatively, the control signal and mask registers may be used to house constants if their primary function is not required. The remaining twenty-four bits of the K-vector are used for additional control such as for conditional branch addressing (10 bits), and enabling interrupts.

The constant "registers" retain their contents during the time a nanoword is active and are immediately replaced with the values in the next nanoword when it is gated into the control matrix. These 6-bit constants are the only means a nanoprogrammer has of introducing constants into registers directly from nanostore.

At any time only a single 72-bit T-vector is active and as such its control fields (nanoprimitives), many of which are further decoded by the control matrix, provide the logic signals required to control the machine. A T-vector is active for 82 nsec (this time span may be doubled if the

stretch bit is set in the T-vector) and on completion the next T-vector in the sequence T1-T2-T3-T4-T1...., becomes active. This cyclic process continues until a new nanoword is gated into the control matrix. A single T-vector may be conditionally bypassed using the nanoprimitive skip, as explained below. The skipped T-vector is still activated, that is 82 nsec elapse before the next T-vector, but its actions are inhibited.

On the nanoprimitive signal read ns the priority mechanism determines the next nanoword to be read, and places it on the nanostore output lines. The highest priority address is the 10-bit next address field in the active K-vector and it is chosen if the branch bit in the K-vector is set. The next alternative consists of thirty interrupts, arranged in descending order, the addresses of which are held in a condensed form (6-bits) in external store registers (22-31). To be selected the interrupt must be latched, enabled—by previously having set a bit in an appropriate external store register (18-19), and allowed by having a bit set in the active K-vector. As a last resort the nanoprogram counter, NPC, will be selected.

Once the selected nanoword is ready it may be conditionally or unconditionally gated into the control matrix. If a conditional gate is requested the specified mask, a K-vector control field, is ANDed with the appropriate test bits and a true result causes the gate to occur making the nanoword active. If the result is false the

nanoword is not gated and the next cyclic T-vector becomes active. A conditional branch is obtained by setting the branch bit and alt branch bit, which cycles the branch bit each time a read ns is encountered. Thus a false conditional gate test (no gate) followed by a read ns causes the NPC to be selected as opposed to the next address field.

The NPC may be loaded in one of three ways: from the next address field in the active K-vector, sequentially by adding one to itself, and from the control store output data bus (COD). Specifying the CDD causes three page pointer bits from a special F-store register, FIDX, to be concatenated with the seven high order bits on the COD and placed into the NPC. The low-order eleven bits are saved in a dedicated register for later loading into the instruction register, local store register thirty-one, under programmer control using the nanoprimitive Load R31.

This method of loading the NPC provides an 18-bit parameterized shorthand for invoking one or more nanowords which will interpret the instruction. Therefore, it is seen that microinstructions in control store are interpreted by one or more 360-bit nanowords in nanostore, and that the maximum number of different instructions obtainable, without extraneous escapes by changing FIDX, is 128.

Extending this concept one step further, it is easily seen that mainstore instructions may be decoded and executed by one or more control store routines. Limitations do not exist concerning instruction format or size. This scheme is

known as indirect emulation as opposed to direct emulation which uses nanoprograms to directly execute mainstone instructions. The advantage of indirect emulation is that the programming task is broken into two more easily managed divisions at the cost of a (possibly) slower emulation.

A nanoprimitive, write ns, is available for writing data into nanostore. The B field of R31 specifies which of twenty 18-bit bytes in a nanoword will receive the data which is taken from the EOD bus. The nanoword address is formed in the low order ten bits of the CA fields of R31. The modified nanoword is at the same time read from nanostore in a manner similar to the read ns nanoprimitive. If an illegal byte (>19) is specified, the write operation does not change anything and the addressed nanoword is read from nanostore in readiness for gating into the control matrix.

## 3.3 F-Store and Residual Control

The first fourteen F-store registers provide residual control over the 18-bit bussing structure of the QM-1. The contents of an F-register indicate which local store, and in some cases external store, register is to be connected to the bus controlled by it. If the 18-bit register is a source, i.e. an input data/address bus "ID, IA", its contents are available to the bus and remain so until the contents of the F-register is changed.

If the 18-bit register acts as a *sink*, i.e. from an output data bus "OD", the data on the bus must be explicitly gated into the register with the appropriate (one of six) gate nanoprimitive. This gating procedure allows all data transformers to be asynchronous, that is always in operation, using data presently available on their input bus(es) placing the results onto the output bus. Data operations are controlled by the use of programmed timing delays which allow time for the correct results to propagate through the transformer to the output bus before it is gated into a local store register.

There is a discrepancy between the number of local store registers, thirty-two, and range available to an F-register, sixty-four. The following data values result when a value greater than thirty-one is placed in the associated F-register: the buses CID, CIA, MIX, EID, AIR, AIL and SID each take values of all ones and the EOD bus is set to zero. The F-register FMOD, controlling the mainstore output bus MOD, is used in such a manner that the values 0-31 refer to the local store registers and the values 32-39 refer to the first eight external store registers. A value greater than thirty-nine results in a null operation, that is, the data is transferred to nowhere. The remaining four buses are used solely as inputs to local store registers and as such ignore the high order bit in the controlling F-register.

The six F-registers, 14-19, provide additional control

signals such as the nanostore page pointer, the local store register (23-27) to be used as the microprogram counter, global status conditions and a special phantom register. The remaining eleven registers are known as the g-registers and provide 6-bit temporary storage. A 6-bit ALU provides F-store with sixteen standard arithmetic operations and in addition two single register incrementers (f+1, f-1) are available.

Values for these registers may only be introduced via constants in the active K-vector or through the three 6-bit fields in R31.

## 3.4 Local Store and Data Transformations

For the purpose of data operations local store may be conveniently represented as a single array of thirty-two registers for use with the ALU and shifter. In addition it may be viewed as twenty-eight registers, which act as sinks and sources for the index ALU, surrounding four register (23-24) which are connected to the microprogram counter incrementing unit.

## 3.4.1 Alu and Shifter

The main ALU, as shown in Fig. 4, has two input buses AIR and AIL (alu input right/left) and is continuously performing one of thirty-two (16 logical and 16 arithmetic) operations determined by the value in the K-vector "register" KALC. Four status bits: carry, sign, result and

overflow are continuously being produced and may be tested for conditional skipping or gating with the K-vector mask KT. The local test bits may be transferred, under program control, to the global test F-store register, FIST, for later testing, if the alu status enable bit is set in the active K-vector. FIST may be tested using the K-vector test mask KS.

The shifter has one input bus, SID (shifter input data), and is controlled by two K-vector "registers", KSHC (shifter control) and KSHA (shift amount). The shifter operations consist of left and right--circular, logical and arithmetic shifts of either eighteen or 36-bits. If a double shift (36-bit) is selected the shifter extension with data from the ALU is used for the high-order 18-bits. The amount of the shift is specified in KSHA with the correct modulo value being used to suit the type of control. A shift of zero bits simply passes the data directly through the shifter.

Two local condition bits, SLB and SHB (the low/high bits present on the SOD bus) are available for testing with the mask KT. These bits may also be transferred to FIST if the shifter status enable bit is set in the active K-vector.

A 16-bit mode is available for both the shifter and ALU by setting the high-order bit in the special F-register, FIDX. This may be overridden with a bit in the active K-vector, force 18-bit mode. In the case of the ALU the two high-order bits on the input buses are automatically

replicated from their respective third high order bits, the sign of the 16-bit value. The shifter performs operations on the low order sixteen or thirty-two bits of data. Also, the local conditions: sign, result, overflow and SHB are redefined to reflect the 16-bit mode.

Two flip-flops, CIH (carry in hold) and COH (carry out hold) are used for carry control with the ALU and shifter apparatus, and are controlled by a 3-bit field in the active T-vector. Each may be set or, cleared directly. The CIH is always used as a carry in to the ALU and may also be set with the carry value last generated by the alu. The COH may be loaded with the latest carry value (it becomes the local carry test), or loaded with the low order bit of the SID bus, or from the shifter end bit which is the last bit shifted out of the high end of the shifter extension.

#### 3.4.2 MPC Unit

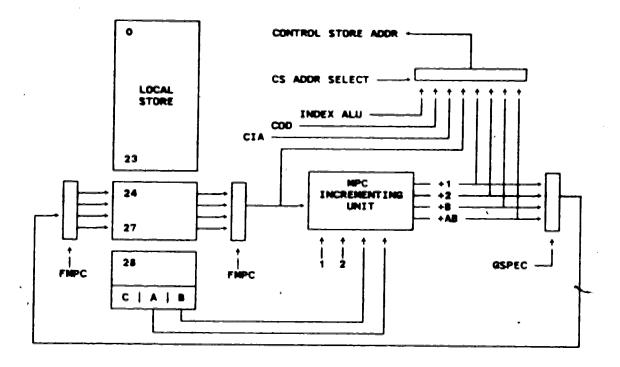

Fig. 5 provides a detailed model of the MPC unit and the associated control store address mechanism. The component is asynchronous, continuously placing on its four output lines the local store register, as selected by the F-store register, FMPC (mod 4), plus: one, two, the 6-bit B field in R31 and the low order eleven bits of R31.

The single input and four outputs may be used directly as control store addresses, as determined by the control store address select field in the active T-vector, along with the data on the index ALU output data bus, the contents

Figure 5. MPC Incrementing Unit

of the control store output data bus and finally the contents of the local store register indexed by FCIA.

One of the four outputs is selected by the low order two bits from a 4-bit field, gspec, in the active T-vector. The result will be gated into the local store register indexed by FMPC if the *inc mpc gate* bit is also set.

#### 3.4.3 Index Alu

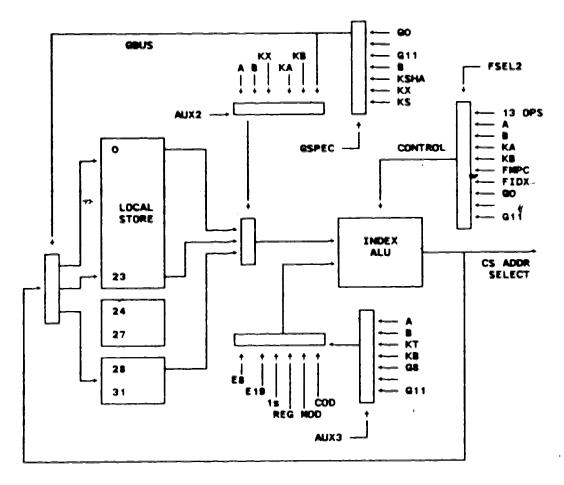

The index ALU, Fig. 6, is the most complicated data manipulator in the QM-1 as it uses one, two and sometimes three levels of indirection to determine the inputs, operation and output data destination. Its logical and arithmetic operations are computationally equivalent to the ALU. Use of the A and B parameter fields in R31 makes this

Ŧ

)

Figure 6. Operation of the Index Alu

unit particularly attractive for quick index operations required by control store instructions.

operation of the index ALU. The field aux2 selects one of six 6-bit inputs to a multiplexor which determines the local store register selected as the left input. A special case is the gbus which requires a further level of indirection through the 4-bit gspec field. The right input is one of: twelve external store registers (8-19), a special CPU control register, a source of all ones and the data on either the mainstore or control store output buses; and is

selected by the 6-bit contents of a register designated by the aux3 field. The arithmetic operation to be performed is controlled by the fsel2 field which may select thirteen operations directly, or 32 operations indirectly through the contents of one of eighteen 6-bit registers.

The local store register to receive the ALU result data is specified by the six bits on the gbus and will be gated if the *index gate* bit is set in the active T-vector. Recall, also, that the result may be selected for use as an address into control store.

#### Chapter 4

#### An Instantiation of S\* to S\*(QM-1)

#### 4.1 Introduction

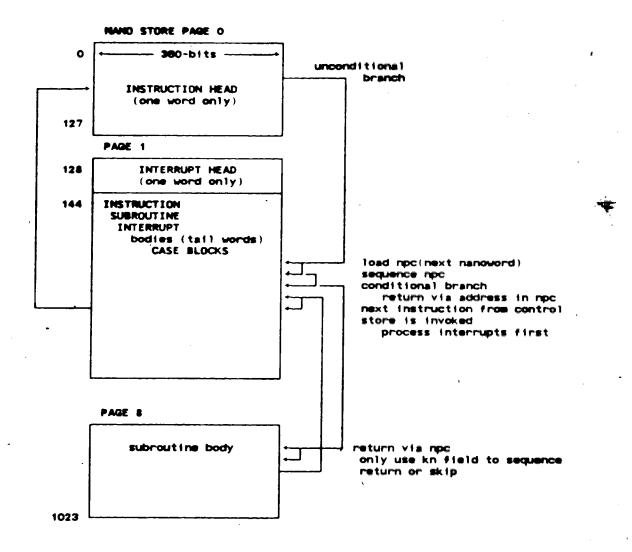

In keeping with the S\* objective of constructing and understanding microprograms which are independent of control store organization [DASG78] (nanoprograms in nanostore) and the fact that the QM-1 was designed for indirect emulations (section 3.1) we have instantiated a language, S\*(QM-1), which is solely procedure based. As mentioned in the previous chapter nanostore acts as a control store interpreter. It does so using only three types of nanoprogram routines: control store instruction interpreters, interrupt handlers, and subroutines which provide support for the interpreters and handlers. For each of these three nanoprogram types we have proposed a different procedure which informs the compiler where to position the nanowords within nanostore, the method of transferring control from one nanoword to the next within the procedure, and what, if any, auxiliary actions need to be performed.

As this is the first version of S\*(QM-1) we have developed a language in which the programmer exercises absolute program control over the QM-1 leaving the compiler with no decision making capabilities.

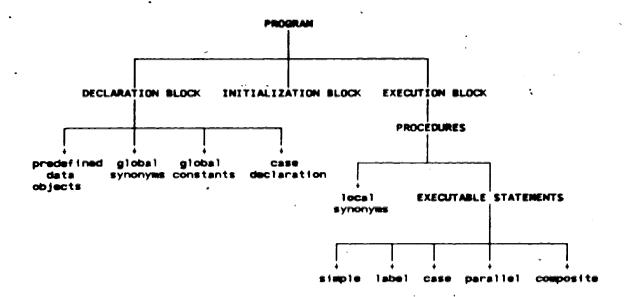

Fig. 7 illustrates the general structure of S\*(QM-1).

Figure 7. S\*(QM-1) Language Model

```

declaration

endec

init

endinit

proc ( instruction, ..., interrupt, ...)

endproc

additional procedures

endprog

```

Figure 8. A Skeleton Program

\*

Fig. 8 demonstrates the basic organization of a program written in S\*(QM-1). Each of the "blocks" will be explored in the following three sections. A complete syntactic and semantic description is included in Appendix 1. Appendix 3 provides the reader with a short program example. A more extensive example based on the mode calculations for a PDP-11 emulator [DEMC76] may be found in the technical report on S\*(QM-1) [KLAS81].

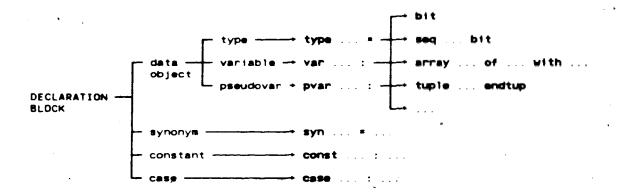

#### 4.2 The Declaration Block

As Figs. 7 and 9 reveal, the declaration block consists of four divisions which may in turn be divided into two groups: pre-defined data objects; and synonym, constant and case declarations. The case declaration is a new construct and will be described in a later section.

Pre-defined data objects consist of variables, var's and pseudo variables, pvar's, to which the programmer has access. They are global in scope, and are defined in terms of bits, sequences of bits, types, arrays and tuples.

Appendix 2 provides a full listing of these data objects.

The number of psuedo variables has been limited to the fewest number possible. They are not true variables in the sense that they may hold a range of values or may have their values transferred to another variable, but are in fact abstractions of certain fields within a nanoword. In the case of pvar's the type bit indicates the pvar may be set to one or zero, and a sequence indicates that a range of values

Figure 9. Declaration Block

may be used. These pvar's must always be on the left hand side (sink) of an assignment (transfer) statement.

A perusal of Appendix 2 shows that a variable identifier such as *local\_store* may be used in several different contexts depending on the bus in question. For example:

refers to the same register as control\_store\_address\_source.register\_address.local\_store[5] but in the former case the bus connects local store to external store via the EIA bus and in the latter to the control store address bus, CIA. As discussed in section 3.3 residual control registers may contain values exceeding the number of local store registers in which case either the bus is set to a value of all zeros, or all ones. This is made clear by the tuple construct enclosing local store followed by all\_ones, or all\_zeros, which effectively describes the array directly preceding it. For example:

var alu\_input

: array [ 0..63 ] of seq [ 17..0 ] bit with fair, fail

: tuple

local\_store : array [ 0..31 ] of ls\_register

all\_ones : array [ 0..31 ] of source\_all\_ones

endtup

Synonyms in the declaration block allow programmers to globally rename pre-defined data objects so that more appropriate variable identifiers may be employed. Appendix 3 provides several examples of how the construct is used. A range of registers may be renamed as in:

syn pdp11\_register = local\_store[0..7]

which indicates that the first eight local store registers

may be referenced by the variable identifier pdp11\_register.

The programmer is responsible for his own bounds checking,

as it is unreasonable, due to space restrictions, for the

compiler to include run time checking. Due to the effects of

residual control registers the lower bound must always be

zero.

Constants and literals are the only means a programmer has of introducing values into registers from an S\*(QM-1) program. The reason for this, as explained in sections 3.2 and 3.3, is that they must be encoded (by the compiler) into a K-vector constant field. Thus they may not exceed  $2^6-1$  (63), which implies that they may only be assigned to 6-bit

registers, that is, of type  $f\_register$  or  $k\_vector\_register$ . The obvious exception is when literals or constants are assigned to pvar's which have their own restrictions.

Constants have a bracketed decimal number associated with them to indicate the number of bits the value is to be encoded into, always six for var's and either one or two for pvar's. Constant declarations and literals have a modifier: bin, oct, dec or hex to indicate the radix of the number. If the modifier for a literal is not present a decimal radix is assumed.

## Examples:

const left\_and\_not\_right : bin (6) 10

fail := 30;, fail := bin 1101;

local\_store[10] := 7654; /\* incorrect \*/

fair := 72; /\* incorrect \*/

#### 4.3 Initialization Block

When using S\*(QM-1) the programmer requires a method for initializing registers before emulation begins. For example the local store register to be used as the microprogram counter must be established, bus control F-registers may need to be initialized, and external store constants for use with the index ALU may need to be setup. To provide the programmer with this facility we have incorporated a new construct into S\*(QM-1):

init ... endinit

which follows the declaration block.

The register initializations and interrupt procedure specifications, which are used to setup interrupt bits and address fields in external store, are placed in a table by the compiler. The last action of the QM-1 loader, immediately before execution begins, is to use this table to initialize the three register stores. Those that are not explicitly initialized will be set to zero.

## 4.4 Execution Block

The execution block, as shown by Figs. 7 and 8, is made up solely of procedures. Each procedure may have as its first statements synonym declarations which rename variable identifiers locally for the duration of the procedure. The scope of a local synonym applies only to the procedure in which it is declared and does not extend to any called procedures. Fig. 10 illustrates the basic statement constructs and the reserved words associated with each. The approach in this section is to first explore assignment statements and tests, followed by the semantics of procedures. Branch, conditional, repetition, and parallel statements are then discussed followed by the new case

Figure 10. Executable Statements

construct.

## 4.4.1 Assignment Statements

## 4.4.1.1 Transfer Statements

The transfer statement <code>sink:= source</code> is the simplest form of assignment and is used when there is a direct connection between the <code>sink</code> and <code>source</code> via a residual control register, 6-bit or 18-bit bus or through main or control memory. When the <code>sink</code> is a local store register and the source is an 18-bit bus, or a local store and external store register, the <code>':='</code> is simply an abstraction for the <code>gate nanoprimitive</code> associated with the transfer.

The use of an array pointer--a residual control register--indicates that no action other than the gating is

required, otherwise the appropriate residual control register must first be setup. This residual control setup also applies to function statements. Thus:

local\_store[fcod] := control\_store\_output\_bus; signifies to the compiler that the F-register FCOD already points to the proper local store register and only the gate cs nanoprimitive need be issued. The semantics for these types of transfers is straightforward. If a pointer is used it must be the correct one (there is only one) for the bus in question. If the source is a local store register and the sink is a bus only the appropriate F-register is setup as no gating is involved.

A memory reference to either main or control store is handled in the same manner except the memory array pointer will specify the address. Memory reads may be placed onto the appropriate data bus or gated directly into a local store register. A full main store read would look like:

local\_store[11] :=

mainstore[mainstore\_source[local\_store[10]]];

or if the F-registers were previously set:

local\_store[fmod] := mainstore[fmix];

The main store write is slightly more complex as the MIX.

input bus multiplexes both the address and data. The address

must first be established on the bus (controlled by the

F-register FMIX) after which the data is supplied to the

same bus by (possibly) changing the contents of FMIX to

point to the local store register containing the data. For

example:

main\_store[fmix] := local\_store[10];

will leave the value 10 in the F-register FMIX which may not have been there originally. For a full read or write operation from memory to a local store register the compiler will include the looping code necessary to test for memory ready and data ready. The programmer has control over this and may substitute his own code for looping if desired.

Several options are available to the programmer for accessing control store as shown in Fig. 5. Four increment operators: +1, +2, +b and +ab for use with the MPC unit have been incorporated. Thus, for example, to read +b words past the present location pointed to by the microprogram counter the following would be used:

local\_store[food] := control\_store[index[fmpc] +b]

# 4.4.1.2 Function Statements

Function statements represent data transformations and where sink is an sink := expression have the form: output data bus, a local store register, or an F-store register. The expression may contain a maximum of two terms separated by a single operator which is limited to functions performed with one pass through an ALU or the shifter [SALI76]. To avoid ambiguities we have incorporated new reserved words into S\*(QM-1) to specify QM-1 related operators.

For example, there are four distinct methods of

symbols: incl. xincl. and +1 (representing two distinct increments, determined by context). The operator incl indicates that the left input of the ALU is to be incremented while xincl causes the left input to the index alu to be incremented. The +1 operator is used for incrementing the 6-bit F-store registers and the four special local store registers that can serve as microprogram counters.

The effect of the residual control registers requires a strict ordering in two term ALU operations. The register to the left of the operator is the left input and the one on the right the right input. Thus the ordering for the ALU is:

local\_store[faod] := local\_store[fail] <alu op>

local\_store[fair]

Index ALU operations (Fig. 6) are differentiated from the ALU by context where the sink is a local store register pointed to by gspec as in local\_store[g\_store[3]] which indicates that the third G-register (F-register 22) points to the local store register to receive the index ALU output. Ordering of expression terms is not as important as with the ALU, as the compiler is able to determine the inputs by context, but are retained for consistency.

An analysis of over 17,000 lines of source Manoassembler code (resulting in approximately 700 nanowords), taken primarily from Demco's PDP-11 emulator and MULTI nanocode [NAN075], was undertaken to choose which data

words. For example, from a total of 32 different operations available for the ALU's, five--addition, pass left, increment left, pass right, and subtraction--were used 80% of the time, and 17 operations were never used at all. The analysis resulted in forty reserved words being chosen from an approximate total of 135 operations.

i

In the event a nonreserved word operation is required, provision has been made for the programmer to use it at the expense of using a slightly lower level of programming. The operator may be specified indirectly as a constant or as a k\_vector\_register, enclosed in brackets to indicate that the appropriate value has been previously assigned to the K-vector field. This is also a method for introducing either a or b parameters of a control store instruction (through R31) by assigning the parameter to a k\_vector\_register before the operation is performed. In the case of the index ALU only constants may be used in this fashion with the index ALU as the operation must be encoded by the compiler into the fsel2 field in the T-vector.