8

# AC-DC Converters

# 8.1 Overview

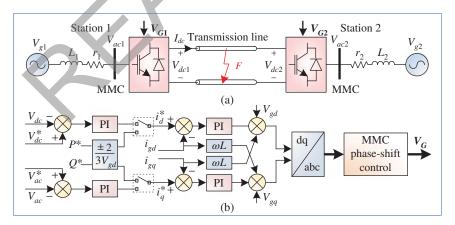

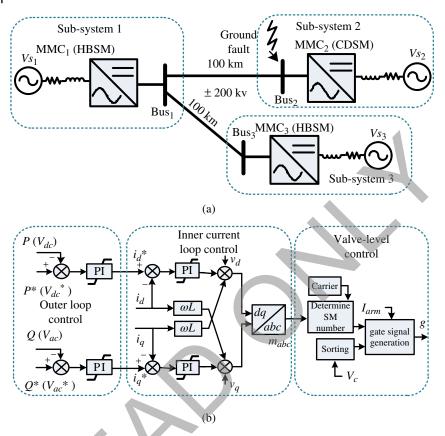

The voltage source converters (VSCs) including the AC/DC and DC/AC types categorized as the rectifier and inverter, respectively, are the interfaces that interlink the AC grid and its DC counterpart. In this chapter, they are uniformly named as the AC–DC converter, which has mainly three configurations, i.e. the two-level VSC, the neutral-point clamped (NPC) converter, and the modular multi-level converter (MMC). Currently, the most popular topology for VSCs for both high- and medium-voltage applications is the MMC. Therefore, the focus of this chapter is primarily on the MMC topology.

The complexity of a converter model is not solely determined by the circuit topology; in fact, demand for the extent of information to be revealed for various purposes by the simulation also has a significant impact. For example, the grid-connected two-level VSC with all its six IGBT/diode pairs adopting the physics-based model or the nonlinear behavioral model is computationally more challenging to the simulator than the MMC using merely the two-state resistor model, albeit the latter has dozens or hundreds of IGBT/diode pairs. Therefore, it is reasonable to classify the VSCs according to the power semiconductor switch models they contain rather than their topology in the electromagnetic transient (EMT) simulation, and according to Chapter 7, the general categories are the following:

- 1. Average value model (AVM);

- 2. Detailed model including its equivalent;

- 3. Iterative nonlinear device-level model, including the hybrid model.

Sorted out by the complexity, it becomes more time-consuming for the CPU, as well as the field-programmable gate array (FPGA) or other types of processors, to simulate the converter when its modeling complexity increases from the AVM to the iterative nonlinear models not only because of a much larger node

301

<sup>© 2021</sup> The Institute of Electrical and Electronics Engineers, Inc. Published 2021 by John Wiley & Sons, Inc.

number due to a sharp increase in model order but also the nonlinear nature of the insulated gate bipolar transistor (IGBT) and diode which require repetitive calculations in a single time-step in the form of Newton-Raphson iterations to ensure numerical correctness and convergence. Nevertheless, as mentioned in Chapter 7, a high-order model provides more information that is helpful to the converter design assessment in addition to system-level preview and therefore, it has aroused a wide interest in recent years following the rapid development of converter topologies applied in power system which resulted in a large amount of power loss during operation. Among all the aforementioned basic converter configurations, the MMC is the most promising topology in forming the high voltage direct current (HVDC) grid, where this VSC has been gaining momentum and is expected to overtake traditional thyristor-based line-commutated converters as the main vehicle for electrical energy conversion due to its advantages such as resilience to commutation failure and capacity of regulating reactive power. Meanwhile, it also has merits over traditional two-level or other multilevel converters such as high-power quality quasi-sinusoidal output waveforms, obviating the need for bulky filtering equipment and scalability, which allows for the number of submodules to be flexibly changed to adjust to different voltage stresses or to produce the demanded voltage levels.

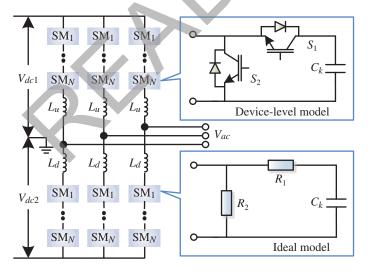

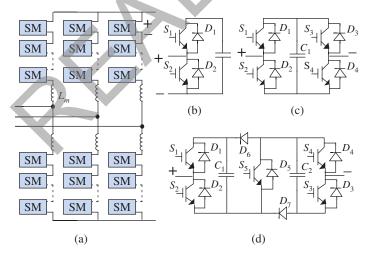

In Figure 8.1, a three-phase MMC adopting the half-bridge submodule (HBSM) is shown, where the IGBT/diode models can be either device-level or use the ideal switch model based on two-state resistors. Hitherto, the detailed model including its Thévenin or Norton equivalents is the most popular type in terms of MMC

Figure 8.1 MMC configuration and its half-bridge submodule models.

modeling and EMT simulation [160]. It certainly is more detailed than the AVM, which to the utmost is merely able to provide harmonics and the submodule capacitor voltages that barely fit the requirement of EMT simulation. However, when it comes to simulating the DC line fault which is one of the common contingencies in an actual grid, the challenge shows up, i.e. the AC grid inappropriately halts feeding electricity to the low-impedance DC side after the blocking order from the secondary protection devices is executed because both models fall short of the diode freewheeling feature. Though technically, it can be solved by introducing the converter-level performance, it is less convincing since the MMC performance at this stage is based on the analysis of the overall converter and a desired operation status is always assumed, which is why we need a device-level to reveal the fault mechanism from a more specific level involving every individual power semiconductor switch.

In addition, using power semiconductor device-level models for converter EMT simulation addresses the growing emphasis on power efficiency in modern power systems by being able to provide abundant detailed information of each submodule including conduction and switching power losses, junction temperatures, and linearized or natural switching transient waveforms of IGBT modules, which are important indicators for converter design guide and assessment, including but not limited to

- 1. evaluating the power converter efficiency under various control methods;

- 2. tuning control parameters such as switching frequency based on converter efficiency and thermal requirements;

- 3. choosing appropriate current rating for IGBT modules and design qualified heat sink based on thermal requirements;

- 4. obtaining a more accurate fast Fourier transform (FFT) analysis for MMC voltage and current waveforms when considering nonideal switching characteristics.

Therefore, in this chapter, all three models of the MMC are introduced and compared. Details of the one based on device-level model are specifically given, along with the hardware architecture design on the FPGA and subsequent emulation results.

# 8.2 Detailed Model

The detailed model describes the converter that is topologically identical to a real configuration, as has been demonstrated in Figure 8.1, where each IGBT/diode pair is taken as a gate-pulse controlled two-state resistor, i.e. the

power semiconductor switch is either under on-state or off-state with two distinct fixed resistances, and the transition between the two states is completed instantly.

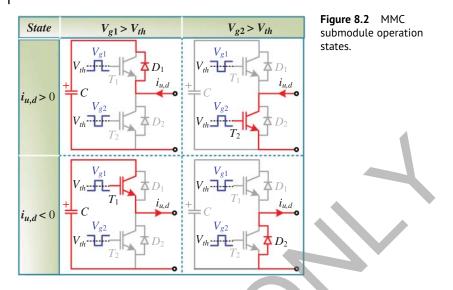

In the HBSM, when the upper switch is under on-state, the DC capacitor is either charging or discharging, meaning the terminal voltage in this case is equal to the capacitor voltage; otherwise, the submodule is bypassed and the submodule terminal voltage is 0, as given in Figure 8.2. Therefore, summing all the submodule outputs yields the multiple voltage levels.

# 8.2.1 Detailed Equivalent Circuit Model

The basic one-step integration method determines that the reactive components can be converted into the Thévenin or Norton equivalences, meaning that circuit simplification by merging all parallel or series components turn out to be possible, which is exactly the case in the MMC detailed equivalent model. Using any one-step integration methods such as the Trapezoidal rule or Backward Euler method, the Thévenin equivalent circuit of a submodule can be expressed by the following set of two equations:

$$R_{eq} = \frac{R_1 R_2 + R_2 Z_{Ck}}{R_1 + R_2 + Z_{Ck}},\tag{8.1}$$

$$V_{eq}(t) = \frac{R_2 V_{Ceqk}(t)}{R_1 + R_2 + Z_{Ck}},$$

(8.2)

where  $Z_{Ck}$  and  $V_{Ceqk}$  compose the Thévenin equivalent circuit of the submodule capacitor,  $R_1$  and  $R_2$  are resistances of the two complementary switches. Therefore,

the N submodules in an arm can be summarized, and to further eliminate internal node caused by the arm inductor, the entire arm is merged, leading to

$$R_{arm\_eq} = Z_{Lu,d} + \sum_{i=1}^{N} R_{eq(i)},$$

(8.3)

$$V_{arm\_eq}(t) = V_{Leq}(t) + \sum_{i=1}^{N} V_{eq}(t),$$

(8.4)

where  $Z_{Lu,d}$  and  $V_{Leq}(t)$  constitutes the Thévenin equivalent circuit of the arm inductor. For the convenience of solving the nodal voltages as a vector in EMT computation, it is not difficult to convert the above two equations into the Norton equivalent circuit form:

$$G_{arm\_eq} = \frac{1}{Z_{Lu,d} + \sum_{i=1}^{N} R_{eq(i)}},$$

$$J_{arm\_eq}(t) = G_{arm\_eq}\left(V_{Leq}(t) + \sum_{i=1}^{N} V_{eq}(t)\right).$$

(8.5)

(8.6)

#### **Equivalenced Device-Level Model** 8.3

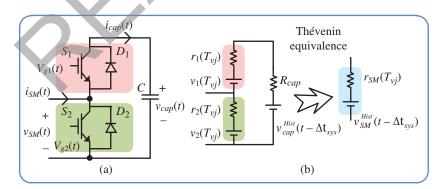

Figure 8.3a shows the SM structure of a two-level half-bridge topology consisting of an upper IGBT  $S_1$ , an upper diode  $D_1$ , a lower IGBT  $S_2$ , a lower diode  $D_2$ , and an energy-storing capacitor C. As mentioned in Figure 8.2, with different combinations of gate signals  $V_{g1}(t)$  and  $V_{g2}(t)$ , the SM has on-state, off-state, blocking, and the short-circuit mode if both power semiconductor switches are turned on, which is not allowed due to its potential damage to the devices and even the entire

Figure 8.3 The sub-module: (a) two-level half bridge topology, (b) temperaturedependent modeling and Thévenin equivalence.

MMC system. In off-state, current goes through either  $S_2$  or  $D_2$  without affecting the capacitor voltage, while in on-state, the capacitor is charging or discharging according to the direction of the SM current  $i_{SM}(t)$ . Other than fault, blocking mode also appears in dead-time period when the gate signals are retrieved from both switches.

As there are three nodes in the HBSM, node reduction is carried out, as demonstrated in Figure 8.3b, where the linear static curve-fitting model using series r-vcircuit introduced in Chapter 7 is adopted. The capacitor voltage  $v_{cap}(t)$  of the SM is derived using Trapezoidal integration rule with the history value  $v_{cap}^{Hist}(t - \Delta t_{sys})$ expressed as follows:

$$v_{cap}(t) = (2 - \alpha)R_{cap}i_{cap}(t) + v_{cap}^{Hist}(t - \Delta t_{sys}),$$

(8.7)

where

$$R_{cap} = \frac{\Delta t_{sys}}{2C}, \quad \text{and}$$

(8.8)

$$v_{cap}^{Hist}(t - \Delta t_{sys}) = \alpha R_{cap} i_{cap}(t - \Delta t_{sys}) + v_{cap}(t - \Delta t_{sys}),$$

(8.9)

$$\alpha = 2\left(\frac{t_{gate} - t_{comm} - (t - \Delta t_{sys})}{\Delta t_{sys}}\right), \quad (0 \le \alpha \le 2).$$

(8.10)

*C* is the capacitance of the SM capacitor;  $i_{cap}(t)$  is the current through the capacitor;  $\Delta t_{sys}$  is the system-level time-step;  $t_{gate}$  is the exact time when the emulator receives the updated gate signals;  $t_{comm}$  is the communication delay of gate signals from the controller to the real-time emulator. The coefficient  $\alpha$  is introduced for the purpose of reducing the capacitor voltage error when gate signals are changing, while, for the rest of the time,  $\alpha$  shall be 1 for the Trapezoidal integration rule. This coefficient is only necessary when gate signal sampling time-step is significantly smaller than the system-level time-step and the communication delay cannot be neglected. In this section, the circuit and its controller are designed on the same FPGA board, and the communication delay can be neglected since it is only one clock cycle or 10 ns. Moreover, the gate signal sampling rate is the same as that of system-level computation, and therefore,  $\alpha$  is always set as 1.

Using Thévenin equivalence, the circuit model for the SM is represented by  $r_{SM}(T_{vj})$  and  $v_{SM}^{Hist}(t - \Delta t_{sys})$  in series, and the SM output voltage  $v_{SM}(t)$  is given as follows:

$$v_{SM}(t) = r_{SM}(T_{vj})i_{SM}(t) + v_{SM}^{Hist}(t - \Delta t_{sys}),$$

(8.11)

where

$$r_{SM}(T_{vj}) = \frac{r_2(T_{vj})(r_1(T_{vj}) + R_{cap})}{r_1(T_{vj}) + r_2(T_{vj}) + R_{cap}},$$

(8.12)

#### 8.3 Equivalenced Device-Level Model 307

$$v_{SM}^{Hist}(t - \Delta t_{sys}) = \frac{r_1(T_{vj}) + R_{cap}}{r_1(T_{vj}) + r_2(T_{vj}) + R_{cap}} v_2(T_{vj}) + \frac{r_2(T_{vj})}{r_1(T_{vj}) + r_2(T_{vj}) + R_{cap}} \left( v_{cap}^{Hist}(t - \Delta t_{sys}) - v_1(T_{vj}) \right).$$

(8.13)

Similarly, Thévenin equivalence for all SMs of the MMC are processed in parallel on the FPGA.  $r_{arm}(T_{vj})$  and  $v_{arm}^{Hist}(t - \Delta t_{sys})$  representing all SMs in one converter arm are the interface circuit elements to the system-level calculation, which are given as follows:

$$r_{arm}(T_{vj}) = \sum_{k=1}^{n} r_{SM}^{k}(T_{vj}),$$

$$v_{arm}^{Hist}(t - \Delta t_{sys}) = \sum_{k=1}^{n} v_{SM}^{k,Hist}(t - \Delta t_{sys}),$$

(8.14)

(8.15)

where *n* is the number of SMs in one converter arm. The dynamics of the other linear passive elements can also be discretized by Trapezoidal rule. After solving the nodal equations for the circuit of entire MMC system,  $i_{SM}(t)$ , which is the same as  $i_{arm}(t)$ , is known.  $i_{cap}(t)$  for each SM capacitor is updated as follows:

$$\dot{i}_{cap}(t) = \frac{r_2(T_{vj})\dot{i}_{SM}(t) + v_1(T_{vj}) + v_2(T_{vj}) - v_{cap}^{Hist}(t - \Delta t_{sys})}{r_1(T_{vj}) + r_2(T_{vj}) + R_{cap}}.$$

(8.16)

Finally, a recursive equation is applied for the calculation of  $v_{cap}^{Hist}$ , given as follows:

$$v_{cap}^{Hist}(t) = 2R_{cap}i_{cap}(t) + v_{cap}^{Hist}(t - \Delta t_{sys}).$$

(8.17)

Equation (8.17) is applicable when the coefficient  $\alpha$  for capacitor voltage error correction is 1, otherwise (8.7)–(8.10) are used to update  $v_{cap}^{Hist}(t)$ . At this point, a set of electrical circuit solution equations (8.7)–(8.17) and (7.84) and (7.85) in Chapter 7) for the SM are established.

#### 8.3.1 **Power Loss Calculation**

After the system-level calculation and the update of capacitor voltages, the power losses of the IGBTs and the diodes in the SMs can be calculated for each system-level time-step. The power losses calculation method used in this chapter is the same in [161]. Power losses for IGBT  $P_{loss}^{IGBT}(t)$  are mainly composed of conduction power losses  $P_{cond}^{IGBT}(t)$ , turn-on power losses  $P_{on}^{IGBT}(t)$ , and turn-off power losses  $P_{off}^{IGBT}(t)$ , while the power losses for diode  $P_{loss}^{Diode}(t)$  are mainly from conduction power losses  $P_{cond}^{Diode}(t)$  and reverse recovery power losses  $P_{rr}^{Diode}(t)$ .

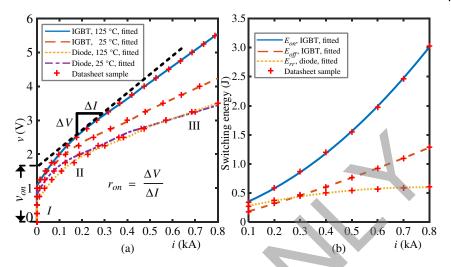

The equations of conduction power losses for the IGBT and the diode during a system-level simulation time-step  $\Delta t_{sys}$  are given as follows:

$$P_{cond}^{IGBT}(t) = \left(r_{on}^{IGBT}(T_{vj})i_{C}(t) + v_{on}^{IGBT}(T_{vj})\right)i_{C}(t),$$

(8.18)

$$P_{cond}^{Diode}(t) = \left(r_{on}^{Diode}(T_{vj})i_F(t) + v_{on}^{Diode}(T_{vj})\right)i_F(t),\tag{8.19}$$

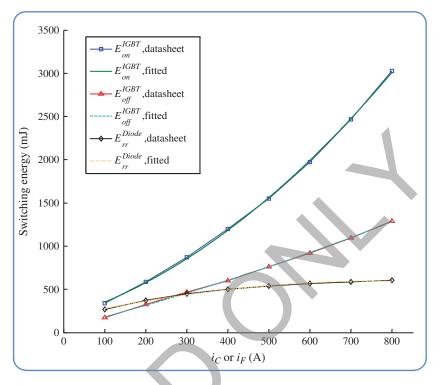

where  $i_C(t)$  is the collector current in IGBT and  $i_F(t)$  is the forward current in diode, which can be determined based on  $i_{SM}(t)$  and switching condition.  $r_{on}^{IGBT}(T_{vj}), v_{on}^{IGBT}(T_{vj}), r_{on}^{Diode}(T_{vj})$ , and  $v_{on}^{Diode}(T_{vj})$  are slope resistances and threshold voltages of either upper or lower IGBT and diode pair. The IGBT switch-on energy  $E_{on}^{IGBT}$ , switch off energy  $E_{off}^{IGBT}$ , and the diode reverse recovery energy  $E_{rr}^{IGBT}$  as functions of the current  $i_C(t)$  or  $i_F(t)$ , when junction temperature  $T_{vj}$  is 125 °C and the voltage across the switch in off-state is the rated value  $v_{rated}$  (1800 V), are provided in the datasheet [162]. Second-order polynomials are adopted here to fit these curves with the  $T_{vj}$  of 125 °C ( $T_2$ ), given as follows:

$$E_{sw}^{T_2}(i(t), v(t)) = (a \cdot i^2(t) + b \cdot i(t) + c) \cdot \frac{v(t)}{v_{rated}},$$

(8.20)

where  $E_{sw}^{T_2}$  represents  $E_{on}^{IGBT,T_2}$ ,  $E_{off}^{IGBT,T_2}$  or  $E_{rr}^{Diode,T_2}$ , i(t) represents  $i_C(t)$  or  $i_F(t)$ , v(t) represents the voltage across the switch in off-state.

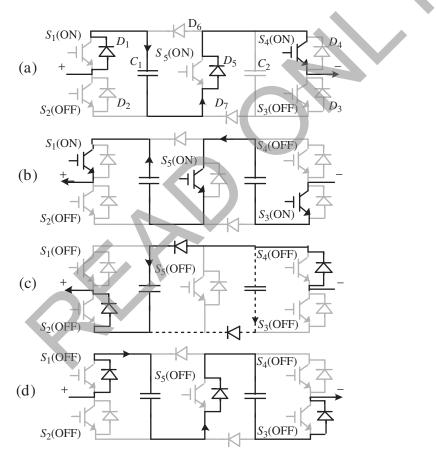

Based on the datasheet information, the fitting parameters are presented in Table 8.1, and the comparison between fitting curves and original curves from datasheet is shown in Figure 8.4. However, besides the loss curves at 125 °C, the datasheet only provides the switching energy losses at the rated value (400 A) and 25 °C. Based on the assumption that all points with different currents in the switching loss curves at 25 °C ( $T_1$ ) follow the proportional relationship of the rated current case, and the curves at other junction temperature are linearly distributed, the energy estimation equations can be derived as follows:

$$E_{sw}(T_{vj}, i(t), v(t)) = \frac{T_2 - T_{vj}}{T_2 - T_1} \left( E_{sw}^{T_1}(i(t), v(t)) - E_{sw}^{T_2}(i(t), v(t)) \right) + E_{sw}^{T_2}(i(t), v(t)),$$

(8.21)

**Table 8.1** Extracted *a*, *b*, and *c* for switching energy curve fitting.

| $E_{sw}^{T_2}(T_2 = 125 \ ^{\circ}C)$ | а           | b     | с     |

|---------------------------------------|-------------|-------|-------|

| $E_{on}^{IGBT,T_2}$                   | 0.002575    | 1.478 | 179.7 |

| $E_{off}^{IGBT,T_2}$                  | 0.0003982   | 1.209 | 58.23 |

| $E_{rr}^{Diode,T_2}$                  | -0.00068631 | 1.075 | 177.2 |

**Figure 8.4** Switching energy losses at the  $T_{vj}$  of 125 °C from fitted equations and datasheet.

where

$$E_{sw}^{T_1}(i(t), v(t)) = \frac{E_{sw}^{T_1, rated}}{E_{sw}^{T_2, rated}} E_{sw}^{T_2}(i(t), v(t)).$$

(8.22)

$E_{sw}^{T_1,rated}$ , and  $E_{sw}^{T_2,rated}$  are the energy losses at rated test condition at  $T_1$  and  $T_2$ . The averaged switching power loss in one system-level time-step is given as follows:

$$P_{sw}(T_{vj}, i(t), v(t)) = \frac{E_{sw}(T_{vj}, i(t), v(t))}{\Delta t_{sys}}.$$

(8.23)

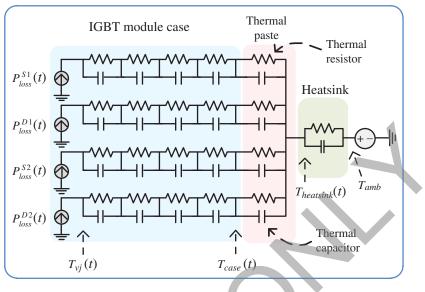

# 8.3.2 Thermal Network Calculation

The calculated power losses now become the input of the thermal network to compute the junction temperatures for all IGBTs and diodes in the SM. Partial fraction thermal circuit model composed of multiple levels of thermal resistor and

Figure 8.5 Thermal circuit structure.

capacitor pairs are employed to compute the junction temperature, as shown in Figure 8.5. The junction temperature  $T_{ij}(t)$  can be calculated as follows:

$$T_{vj}(t) = P_{loss}(t) \cdot (Z_{thjc} + Z_{thch}) + P_{total}(t) \cdot Z_{thha} + T_{amb},$$

(8.24)

where  $P_{loss}(t)$  is the power loss for a single IGBT or diode;  $P_{total}(t)$  is the power loss for all devices mounted on the same heatsink;  $T_{amb}$  is the ambient temperature which is fixed in the emulation;  $Z_{thjc}$ ,  $Z_{thch}$ , and  $Z_{thha}$  are the thermal impedances from junction to case, case to heatsink, and heatsink to ambient, respectively. In this work, we consider that two IGBT modules are mounted on the same 10 K/kW water-cooled heatsink. The thermal impedance  $Z_{thjc}$  and thermal resistor  $R_{thch}$ from case to heatsink are given by the datasheet. All the thermal impedance parameters for this work are shown in Table 8.2 in the form of thermal resistances and time constants.

Applying Trapezoidal rule, the numerical equation to solve for the junction temperature for either the IGBT or the diode is given as follows:

$$T_{vj}(t) = \sum_{i=1}^{6} \Delta T_{th}^{i}(t) + T_{amb} = \sum_{i=1}^{5} (\alpha_{i}(P_{loss}(t) + P_{loss}(t - \Delta t_{thm})) + \beta_{i} \Delta T_{th}^{i}(t - \Delta t_{thm})) + \alpha_{6}(P_{total}(t) + P_{total}(t - \Delta t_{thm})) + \beta_{6} \Delta T_{th}^{6}(t - \Delta t_{thm}) + T_{amb},$$

(8.25)

|                           | <b>Z</b> <sub>thjc</sub> |              |              |              | <b>Z</b> <sub>thch</sub> | <b>Z</b> <sub>thha</sub> |

|---------------------------|--------------------------|--------------|--------------|--------------|--------------------------|--------------------------|

| Thermal impedance         | <i>i</i> = 1             | <i>i</i> = 2 | <i>i</i> = 3 | <i>i</i> = 4 | <i>i</i> = 5             | <i>i</i> = 6             |

| $R_{th}^{i,IGBT}$ (K/kW)  | 11.475                   | 6.375        | 1.53         | 6.12         | 24                       | 10                       |

| $	au_{th}^{i,IGBT}$ (s)   | 0.03                     | 0.1          | 0.3          | 1            | 3                        | 45                       |

| $R_{th}^{i,Diode}$ (K/kW) | 22.95                    | 12.75        | 3.06         | 12.24        | 48                       | 10                       |

| $	au_{th}^{i,Diode}$ (s)  | 0.03                     | 0.1          | 0.3          | 1            | 3                        | 45                       |

Table 8.2

Impedances for thermal network.

where

$$\alpha_{i} = \frac{R_{th}^{i} \cdot \Delta t_{thm}}{2\tau_{th}^{i} + \Delta t_{thm}},$$

$$\beta_{i} = \frac{2\tau_{th}^{i} - \Delta t_{thm}}{2\tau_{th}^{i} + \Delta t_{thm}}, \quad i = 1, 2, \dots, 6.$$

(8.26)

(8.27)

$\Delta t_{thm}$  is the thermal time-step, which has the same value as  $\Delta t_{sys}$  in this work. Considering the fact that thermal time constant is much longer than the MMC system emulation time-step, the thermal network can have a separate time-step that could be set larger without a significant impact on accuracy.

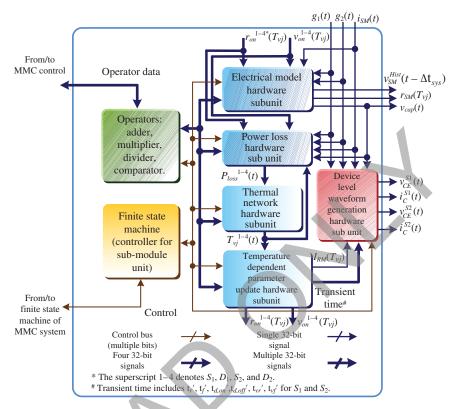

# 8.3.3 Hardware Emulation of SM Model on FPGA

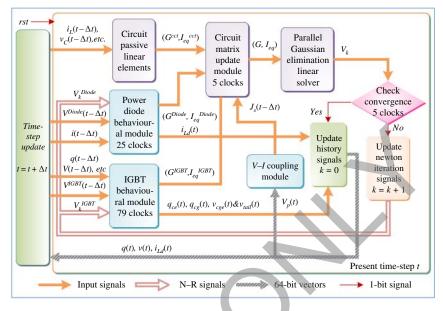

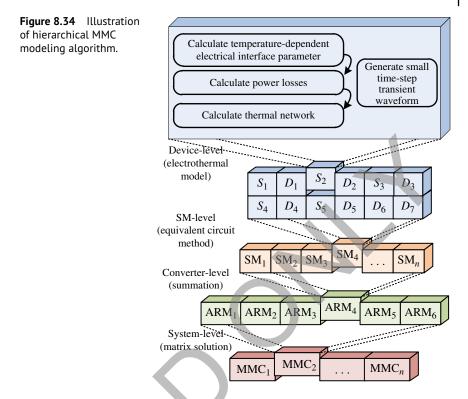

For each SM in the MMC system, a dedicated SM hardware unit such as Figure 8.6 emulated on the FPGA consists of operators, the FSM, and five hardware subunits: the electrical model hardware subunit, the power loss hardware subunit, the thermal network hardware subunit, the temperature dependent parameter update hardware subunit, and the device-level waveform generation hardware subunit. All SM hardware units run simultaneously, which means the computation time for SM hardware units of the MMC will not increase with the number of SMs.

In Figure 8.6, the signal flow routes and the execution of hardware subunits follows the algorithm described in Section 8.3.2. For instance, the power loss hardware subunit requires the gate signals  $g_1(t)$ ,  $g_2(t)$  and the direction of SM current  $i_{SM}(t)$  from the MMC controller and the system network solution to figure out the SM operation mode, which determines the conditions of all switching devices (switch-on, switch-off, conduction or off). Then,  $r_{on}(T_{vj})$ ,  $v_{on}(T_{vj})$ ,  $T_{vj}(t)$  of the corresponding devices,  $v_{cap}(t)$ ,  $i_{SM}(t)$  and other constants are substituted to (8.18)–(8.23), completing the power loss calculation.

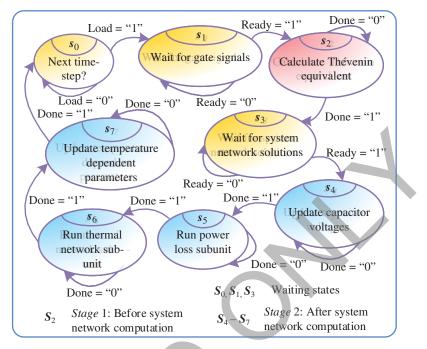

The finite state machine controls the execution sequence for other hardware subunits in the SM hardware unit and receives the control signals from the FSM

Figure 8.6 Submodule hardware unit emulation on FPGA.

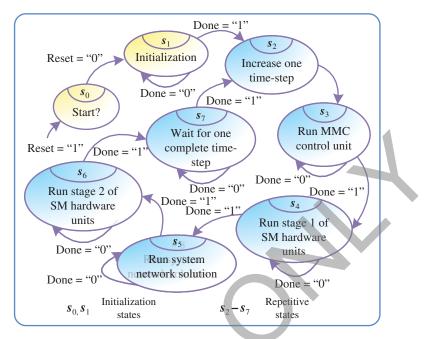

of the entire MMC emulation hardware. Figure 8.7 shows the periodic state chart for the SM hardware unit, which begins from  $S_1$ , the start of a new emulation time-step. After the gate signals are received, the Stage 1 of the SM hardware unit is activated by first calculating  $v_{SM}^{Hist}(t - \Delta t_{sys})$  and  $r_{SM}(T_{vj})$ , which are then used for system network calculation. After  $i_{SM}(t)$  is received from the system network solution, Stage 2 starts from  $S_4$  to  $S_7$ , corresponding to the four hardware subunits in the middle column of Figure 8.6: electrical model, power loss, thermal network, temperature-dependent parameter update hardware subunits. When all the calculations are finished, the FSM return to  $S_0$  to wait for the arrival of next time-step.

Because of the sequential relation among the hardware subunits except for the device-level waveform generation hardware subunit, they share the same set of floating-point operators with pipelined structure and multiplexed input registers in this design, including one adder (3 clocks), one multiplier (3 clocks), one divider (9 clocks), and one comparator (2 clocks). The calculation times for the subunits

Figure 8.7 Finite state machine for SM hardware unit.

| Table 8.3         Latencies of various subunits in the SM hardware unit |

|-------------------------------------------------------------------------|

|-------------------------------------------------------------------------|

| Subunit                             | Total computation time with<br>one set of operators (clock cycles) |

|-------------------------------------|--------------------------------------------------------------------|

| Stage 1 electrical models           | 27                                                                 |

| Stage 2 electrical models           | 18                                                                 |

| Power loss                          | 38                                                                 |

| Thermal network                     | 72                                                                 |

| Parameters update                   | 18                                                                 |

| SM hardware unit total clock cycles | 173                                                                |

| Percentage in 1000 clock cycles (%) | 17.3                                                               |

with one set of operators and the percentage of total computation time for the SM hardware unit are listed in Table 8.3. Since the FPGA runs at the clock frequency of 100 MHz, and system-level time-step is 10  $\mu$ s, there are 1000 clock cycles available for a complete computation for one system-level time-step. Using more operators can decrease the delay significantly due to the parallelism existing in those hardware subunits, which requires more FPGA resources.

The device-level waveform generation hardware subunit generates the voltage and current waveforms of the upper and lower IGBTs,  $v_{CE}^{S1}(t)$ ,  $i_C^{S1}(t)$ ,  $v_{CE}^{S2}(t)$ , and  $i_C^{S2}(t)$ , with linearized transients continuously at the time-step of 10 ns, which means the output waveforms will update at each FPGA clock cycle. The received voltage and current will be first converted into fixed-point format, since fixed-point adders are much faster than those of floating-point. The fixed-point operators will add or substrate a specific value to the voltage and current during a specific time period determined by temperature dependent transient times.

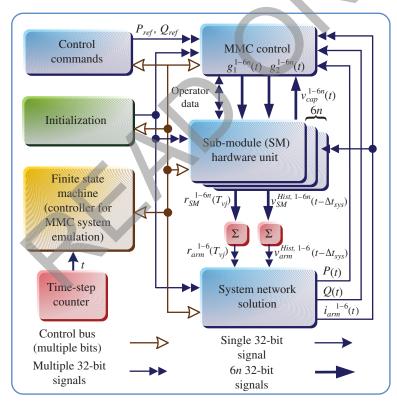

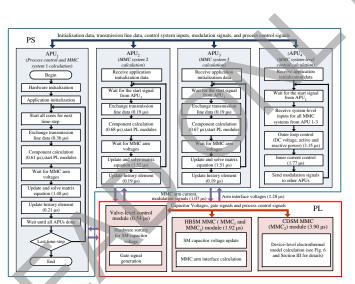

# 8.3.4 MMC System Hardware Emulation

The MMC system hardware emulation and state chart on FPGA are shown in Figures 8.8 and 8.9, respectively. The finite state machine controls the entire emulation flow by interacting with the state machines of other hardware units through the control bus. It activates different hardware units according to the sequence

Figure 8.8 MMC system hardware emulation.

Figure 8.9 Finite state machine for the MMC system.

shown in the state chart. Following a definitive reset order, the FPGA-based emulator goes into the initialization state  $S_1$  through  $S_0$ . During the initialization, some constants which will be periodically used in later computation, such as  $\alpha_i$  in (8.26), are calculated, and the matrix simplification requested by system network solution is also done. Then the time-step counter starts to work, providing the exact time *t* of the real-time emulation to the FSM, which is used to determine the arrival moment of next time-step in  $S_2$ .

In  $S_3$ , the MMC control unit receives the active and reactive commands from the control commands unit as well as the data from the SM hardware units and the system network solution unit, and then generates the gate signals to SM hardware units. In practice, the MMC control unit and the control commands unit are the devices under test during the real-time emulation. In this work, they are integrated onto the FPGA board in the demonstration design. Since the pulse width modulation (PWM) method based on phase-shift control (PSC) strategy generates drive signals for each SM, the process requires 6n sets of operators to ensure full parallelism. In this design, the MMC control unit and the SM hardware units share the same sets of operators, indicated by the bidirectional operator data bus. The detailed internal structure and algorithm of MMC control unit and SM hardware units are presented in Sections 8.3.1–8.3.4. State  $S_4$  involves the Stage 1 of SM hardware units and the summation for  $r_{SM}^{1-6n}(T_{vj})$  and  $v_{SM}^{Hist,1-6n}(t - \Delta t_{sys})$ . For clarity, two summation units are drawn in Figure 8.8. However, they are multiplexed in the actual design to save resources without affecting the speed, since the calculation of  $v_{SM}^{Hist,1-6n}(t - \Delta t_{sys})$  involves more steps and are completed later than  $r_{SM}^{1-6n}(T_{vj})$ . The system network solution unit receives the interface components  $r_{arm}(T_{vj})$  and  $v_{arm}^{Hist}(t - \Delta t_{sys})$  for the six arms from Stage 1 of SM hardware units and then solves the nodal equations for the entire circuit topology in  $S_5$ . The outcome  $i_{arm}^{1-6}(t)$  are then used to complete the Stage 2 of the SM hardware units in  $S_6$ , including the power loss and thermal network calculation. When the moment of next time-step arrives, the finite state machine changes from  $S_7$  to  $S_2$ , starting a new emulation cycle.

# 8.3.5 Real-Time Emulation Results

### 8.3.5.1 Test Circuit and Hardware Resource Utilization

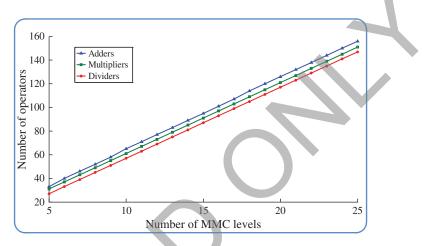

Two case studies for MMC systems: a single-phase five-level MMC and a three-phase nine-level MMC, were emulated on the Xilinx® Virtex-7® XC7VX485T FPGA (Table 1.2) at the clock frequency of 100 MHz to validate both system-level and device-level results. The three-phase test case has the same topology of Figure 8.1, while the single-phase test case is connected to a passive load instead of the grid. The circuit parameters for the two cases are given in Appendix A.7. The emulation results were captured by a four-channel oscilloscope connected to the 16-bit 4-channel digital-to-analog converter, which received the data from the FPGA. The major resource utilization summary is presented in Table 8.4, and the percentage data are indicated for Virtex-7 XC7VX485T and XC7V2000T FPGAs, respectively. Since the designs only use distributed registers as memory units, the BRAM utilization is 0. The 17-level and 25-level MMCs were synthesized on the Xilinx® Virtex-7® XC7V2000T FPGA [12], which has more logic resources (4× more logic cells and CLB slices, and 2.6× more distributed RAM) than the XC7V485T FPGA used for demonstration. Figure 8.10 shows the exact number of operators, including adders, multipliers, and dividers, utilized for MMC emulation hardware with different levels. The FPGA designs which only contain SM hardware units and summation units by the electrothermal model and the Thévenin equivalence method with two-state resistor model for IGBT modules were synthesized on XC7V2000T for resource comparison purpose. The same FPGA design methodology was applied for both cases, which is using one set of operators for each SM. When using two-state resistor model for IGBT modules, only one adder and one multiplier are required for each SM. Sharing the same set of operators among multiple SM hardware units reduces the resource consumption; however, can increase the time delay, which is not adopted in this work. The maximum SM number accommodated on XC7V2000T device for the

| Device    | Levels | SM numbers | Registers      | LUTs         | DSP slices |

|-----------|--------|------------|----------------|--------------|------------|

| XC7VX485T | 5      | 24         | 180 447(28%)   | 157 735(51%) | 130(4%)    |

|           | 9      | 48         | 315 931(52%)   | 294 554(97%) | 236(8%)    |

| XC7V2000T | 17     | 96         | 686 767(28%)   | 639 887(52%) | 420(19%)   |

|           | 25     | 144        | 1 020 845(41%) | 991 004(81%) | 612(28%)   |

Table 8.4

Hardware resource utilization for three-phase MMC.

Figure 8.10 Operator count for the MMC system with increasing number of levels.

electrothermal model and two-state resistor model are 276 and 1104, respectively. Under normal operation, the power losses and junction temperatures are in the same level for different SMs, verified by Table 8.5, therefore, emulating all SMs by the electro-thermal model is not necessary with limited FPGA resources. A combination of using the above two methods can greatly reduce the resource consumption. With these optimization and simplification schemes, the FPGA design can be very flexible to meet the resource usage and time delay requirements.

Moreover, according to Table 8.4 and Figure 8.10, the resource usage and the operator numbers for the electrothermal model increase almost linearly with the number of MMC levels, which indicates that with more advanced FPGA devices, such as the Xilinx<sup>®</sup> UltraScale series, or using multiple FPGA boards, MMCs with larger number of levels can be configured and emulated quite efficiently.

The off-line simulation tool SaberRD<sup>®</sup> was used to validate the real-time emulated results for the single-phase five-level MMC test case. Electrothermal behavioral IGBT and power diode model with parameters extracted from the datasheet were employed in the SaberRD<sup>®</sup> model with a variable time-step strategy.

|      |           | S                     | 1                          | D                     | 1                          | S                     | 2                          | D                     | 2                          |

|------|-----------|-----------------------|----------------------------|-----------------------|----------------------------|-----------------------|----------------------------|-----------------------|----------------------------|

| Arm  | Submodule | P <sub>loss</sub> (W) | <i>Т<sub>vj</sub></i> (°С) |

| _    | SM(1)     | 256.3                 | 72.44                      | 243.2                 | 83.83                      | 1425.1                | 130.28                     | 51.1                  | 64.81                      |

| arm  | SM(2)     | 255.9                 | 72.40                      | 242.9                 | 83.78                      | 1424.2                | 130.23                     | 50.1                  | 64.68                      |

| Pos. | SM(3)     | 255.1                 | 72.31                      | 239.5                 | 83.39                      | 1424.3                | 130.19                     | 49.1                  | 64.53                      |

| Ц    | SM(4)     | 257.0                 | 72.48                      | 242.3                 | 83.75                      | 1425.8                | 130.33                     | 51.5                  | 64.86                      |

| d    | SM(1)     | 255.4                 | 72.31                      | 239.6                 | 83.39                      | 1424.7                | 130.20                     | 49.1                  | 64.54                      |

| arm  | SM(2)     | 257.1                 | 72.49                      | 242.7                 | 83.75                      | 1426.3                | 130.33                     | 51.5                  | 64.86                      |

| Neg. | SM(3)     | 256.3                 | 72.44                      | 243.3                 | 83.83                      | 1425.0                | 130.30                     | 51.1                  | 64.81                      |

| 2    | SM(4)     | 256.3                 | 72.41                      | 243.0                 | 83.78                      | 1424.3                | 130.24                     | 50.3                  | 64.70                      |

**Table 8.5**Average power dissipation and junction temperature of IGBTs and diodes insteady-state operation.

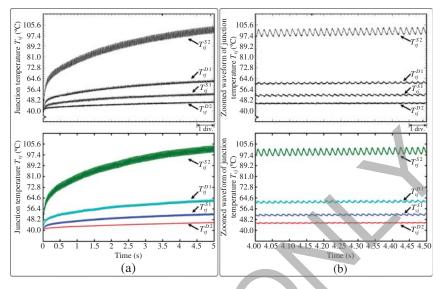

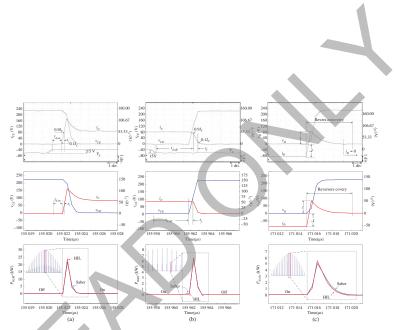

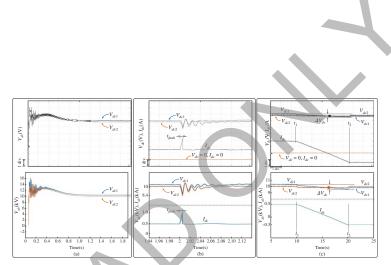

## 8.3.5.2 Results and Comparison for Single-Phase Five-Level MMC

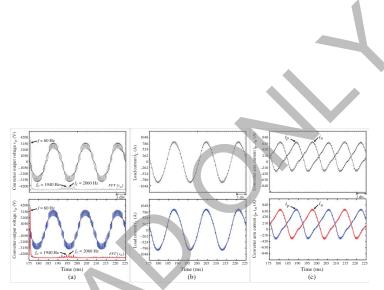

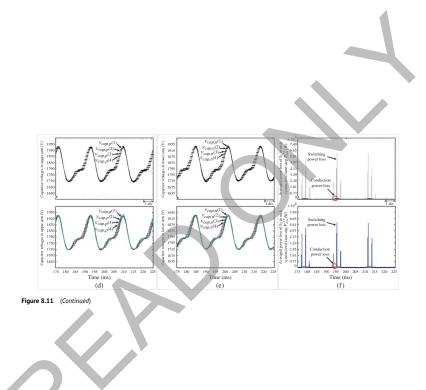

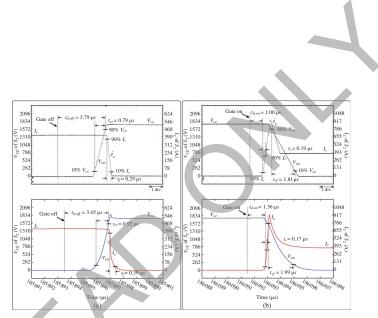

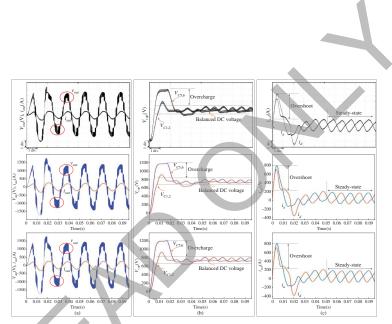

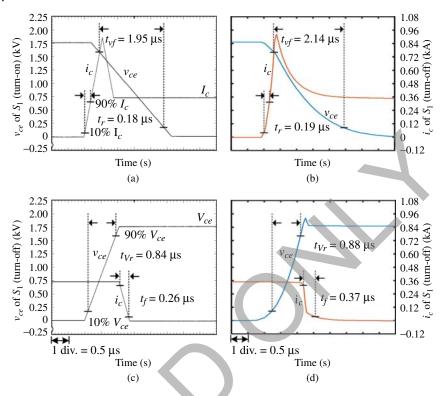

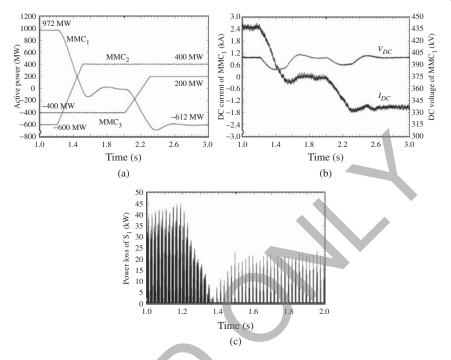

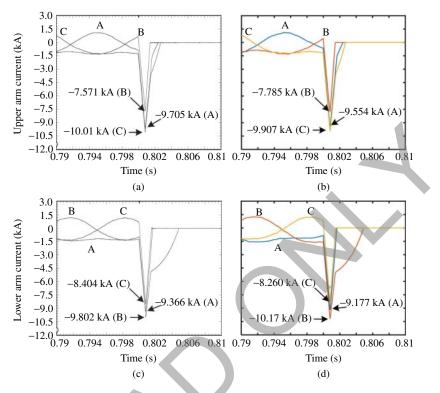

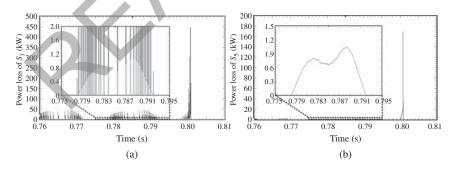

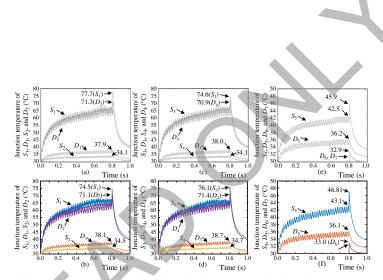

Figure 8.11a-e present the system-level results including the converter output voltage  $v_0$ , the load current  $i_L$ , the converter arm current  $i_n$  and  $i_n$ , and the capacitor voltage of all SMs in positive and negative converter arm  $v_{cap,p}$  and  $v_{cap,p}$ . The FFT analysis was applied to  $v_0$ . Despite the line frequency, harmonics around 2 kHz are notable in both hardware emulation and SaberRD® results, which is expected, since the switching frequency is 500 Hz and each converter arm has four SMs. Figures 8.11f-i to 8.13 present the device-level results for the IGBTs and diodes in the first SM of the positive converter arm. Figure 8.11f,h shows the averaged power losses of  $S_1$  and  $S_2$  in each system-level time-step ( $P_{loss}^{S1}$  and  $P_{loss}^{S2}$ ). The conduction power losses  $P_{cond}^{S1}$  and  $P_{cond}^{S2}$  are particular shown in Figure 8.11g,i, where switching power losses are removed for clarity. The junction temperature of  $S_1$ ,  $S_2, D_1$ , and  $D_2(T_{vj}^{S1}, T_{vj}^{D1}, T_{vj}^{S2}$  and  $T_{vj}^{D2}$ ) in first five seconds and the zoomed waveforms during 0.5 second are shown in Figure 8.12a,b, respectively. Figure 8.13a,b shows the switching transients of  $S_2$  during IGBT turn-off and turn-on ( $v_{CE}$  and  $i_C$ ). Table 8.6 shows the averaged switching and conduction power losses between 0.175 and 0.225 second from SaberRD® and FPGA hardware emulation. The apparent errors exist for device-level results, since the solver and IGBT module model used in the emulation and SaberRD<sup>®</sup> are very different. The datasheet does not provide adequate data for switching power losses when the current through the IGBT module is low. The switching power losses from curve fitting in hardware emulation are higher than those from the off-line simulation results from SaberRD<sup>®</sup>, which can be observed from Figure 8.11e,f. This explains the largest power loss error occurs in the reverse recovery loss of  $D_2$  in Table 8.6, where the smallest current goes through. The IGBT switching transient parameters are extracted based

Figure 8.11 System-level and device-level power loss results for single-phase five-level MMC system from real-time hardware emulation (top in (a)–(i)) and off-line simulation by SaberRD® (bottom in (a)–(i)) at 500 Hz switching frequency. Scale: (a)–(i) x-axis: 5.0 ms/div.

**Figure 8.12** Junction temperature for single-phase five-level MMC system from real-time hardware emulation (top sub-figure) and off-line simulation by SaberRD<sup>®</sup> (bottom sub-figure). Scale: (a) *x*-axis: 0.5 s/div, (b) *x*-axis: 0.05 s/div.

on the power losses and the current rise and fall time under rated cases. The linear interpolation scheme used to estimate the nonlinear curves for other nonrated cases induced the errors. From the perspective of power loss matching, the transient time of nonlinear SaberRD\* waveforms are slightly longer than the linear curves from hardware emulation. The diode reverse recovery process greatly expedites the turn-on process of the IGBT, therefore,  $t_r$  of IGBT from both the real-time and off-line simulation shown in Figure 8.13b is almost half the value in the datasheet, which is  $0.4 \,\mu$ s. Since the datasheet does not provide the detailed information for the drive circuit, they are simply modeled as the ideal voltage sources in series with the gate resistors in SaberRD\*'s model, which caused the differences for turn-on and turn-off delay times. Despite all of the above, the hard-ware emulation and SaberRD\* results are quite close.

Table 8.5 also shows the average power dissipation and junction temperature of IGBTs and diodes for all SMs under steady-state operation. These data are collected from the real-time emulation after 369 seconds, which is more than eight times longer than the largest thermal time constant (45 seconds). The power losses and junction temperatures of the corresponding devices in different SMs are very close to each other, which verifies the advantage of even usage of SMs for PSC–PWM control scheme.

Figure 8.13 Device-level switching waveforms for IGBTs in single-phase five-level MMC system from real-time hardware emulation (top sub-figure) and off-line simulation by SaberRD $^{\circ}$  (bottom sub-figure). Scale: (a) and (b) x-axis: 1 µs/div.

| Power<br>dissipation | SaberRD® (W) | FPGA (W) | Error (%) |

|----------------------|--------------|----------|-----------|

| $P^{S1}_{on}$        | 60.6         | 61.2     | 1.0       |

| $P_{off}^{S1}$       | 41.7         | 42.2     | 1.2       |

| $P_{cond}^{S1}$      | 137.3        | 134.4    | 2.1       |

| $P_{rr}^{D1}$        | 72.2         | 74.3     | 2.9       |

| $P^{D1}_{cond}$      | 136.3        | 130.3    | 4.4       |

| $P_{on}^{S2}$        | 293.7        | 280.1    | 4.6       |

| $P_{off}^{S2}$       | 168.1        | 163.6    | 2.7       |

| $P_{cond}^{S2}$      | 722.0        | 723.5    | 0.2       |

| $P_{rr}^{D2}$        | 24.7         | 26.8     | 8.5       |

| $P^{D2}_{cond}$      | 13.5         | 14.0     | 3.7       |

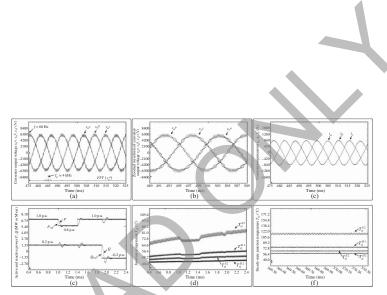

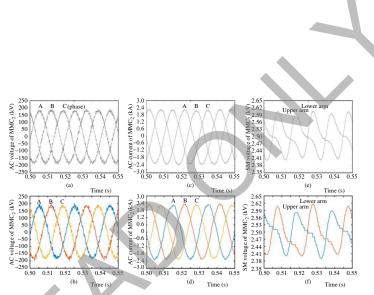

# 8.3.5.3 Results for Three-Phase Nine-Level MMC

The emulated three-phase nine-level MMC is the largest circuit which can be configured in the Virtex-7<sup>\*</sup> VC707 board with XC7VX485T FPGA whose resources are listed in Table 1.2. Figure 8.14a,b shows the converter output phase voltages  $(v_o^a, v_o^b,$  and  $v_o^c)$  during 50*ms* and the zoomed waveforms during 20 ms, while Figure 8.14c shows the output line current  $(i_a, i_b,$  and  $i_c)$ . Figure 8.14d shows the active and reactive power tracking performance, with the rated power of 7 MW, and Figure 8.14e shows the junction temperature transients of the switching devices in the first positive arm SM of phase A during the same time period. Figure 8.14f shows the steady-state junction temperatures with 1.0 p.u. active power and -0.2 p.u. reactive power after 369 seconds.

# 8.4 Virtual-Line-Partitioned Device-Level Models

While MMC arm aggregation is enabled by the linear curve-fitting IGBT/diode switch model in Section 8.3, it is not always feasible in device-level simulation of the modularized converter, e.g. the existence of transconductance in the nonlinear behavioral model deprives it of the discrete time domain equivalent circuit, not to mention merging the elements to yield the Norton equivalent circuit. Consequently, the many submodules connecting to each other introduce plenty of meshes and nodes, making direct solution of the converter impractical. Therefore, a more general method applicable to all MMCs regardless of the power

Figure 8.14 System-level and device-level results for three-phase nine-level MMC system from real-time hardware emulation (oscilloscope) at 500 fr2 switching frequency. Scale: (a) x-axis: 5.0 ms/div, (b) x-axis: 2.0 ms/div, (c) x-axis: 5.0 ms/div, (d) and (e) x-axis: 0.2 s/div, (f) x-axis: 0.1 s/div.

$e^{1}$

semiconductor switch model is introduced in this section. Circuit partitioning is an effective method in reducing the corresponding matrix equation's dimension. Based on the fundamental principle that the section to be split should have a stiff voltage or current, and the fact that the complexity of MMC model is caused by its power semiconductor switches in the SM, the MMC arm turns out to be the ideal partitioning interface to create a group of independent subcircuits. Therefore, the original large admittance matrix for the MMC is split into a number of smaller matrices and parallel computation can be achieved on the FPGA to accelerate hardware-in-the-loop (HIL) emulation.

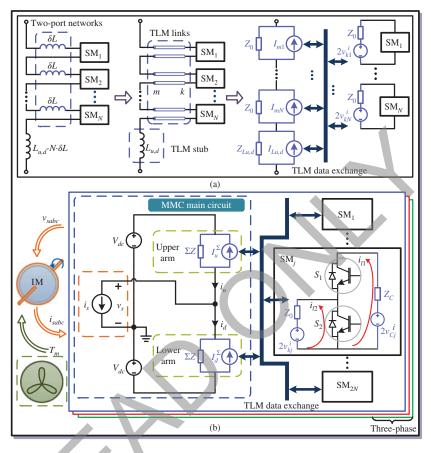

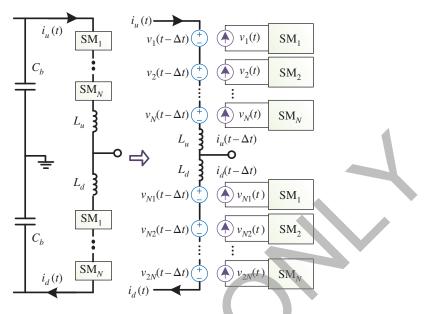

# 8.4.1 TLM-Link Partitioning

As the three-phase MMC is symmetrical, it is reasonable to carry out analysis based on one phase. Figure 8.15a shows the process of splitting a large MMC network consisting of a considerable number of nodes and meshes into several structurally independent, electrically related subcircuits. The arm inductor is first divided into (N + 1) parts which are redistributed so that a new inductor  $\delta L$  is connected in series with each submodule to constitute a two-port network, and consequently, the remaining inductance for the arm inductor is  $L_{u,d} - N \cdot \delta L$ . Then, these new inductors are replaced by transmission line modeling (TLM) links, discretization of which leads to the separation of submodules from the rest of the converter (MMC main circuit), enabling the replacement of the originally large impedance or admittance matrix by a number of submatrices with smaller dimensions, which, if processed in parallel on the FPGA, would be much more time and resource efficient.

The selection of the value of  $\delta L$ , which decides the characteristic impedance  $Z_0$  and vice versa, plays a significant role on the emulation results. The principle, as stated, is an appropriate value of  $\delta L$  should ideally keep the arm inductor current identical to before its introduction [163]. Nevertheless, neighboring values resulting in a tiny change might also be allowed depending on the requirement of simulation accuracy. Thus, the optimum value can be selected from its range by running Matlab simulation of the MMC and comparing the current changes. It shows that the final value of  $\delta L$  is negligible compared with the arm inductance so that the latter can still be deemed as  $L_{u,d}$ , e.g. around 0.1%.

For the MMC main circuit, where the Norton equivalent circuit part of TLM link's hybrid model locates, by merging all the Norton circuits in the upper and lower arms, respectively, there is actually only one node since the potentials at all other three nodes are known, as shown in Figure 8.15b, the overall schematic for MMC. Then, the nodal voltage equation at *n*th time-step can be derived by applying KCL:

$${}_{n}\mathbf{V}_{s}=\mathbf{G}^{-1}\cdot{}_{n}\mathbf{I},\tag{8.28}$$

**Figure 8.15** TLM-based model for (N + 1)-level MMC: (a) MMC partitioning approach, and (b) discretized schematic for the overall system.

where these  $1 \times 1$  matrices are

$$\mathbf{G} = \left[\frac{2}{N \cdot Z_0 + Z_{Lu,d}}\right],\tag{8.29}$$

$${}_{n}\mathbf{I} = \left[\frac{nJ_{u}^{\Sigma} - nJ_{d}^{\Sigma}}{\Sigma Z} - ni_{s}\right] = \left[2 \cdot \frac{\sum_{j=N+1}^{2N} nv_{mj}^{i} + nv_{Ld}^{i} - \left(\sum_{j=1}^{N} nv_{mj}^{i} + nv_{Lu}^{i}\right)}{N \cdot Z_{0} + Z_{Lu,d}} - ni_{s}\right].$$

(8.30)

In (8.30),  $\Sigma Z$ ,  ${}_{n}I_{u}^{\Sigma}$ , and  ${}_{n}I_{d}^{\Sigma}$  are the impedance and current sources of the Norton equivalent circuitw voltage vector  ${}_{n}\mathbf{V}_{s}$  is numerically equal to the stator voltage  ${}_{n}v_{s}$ . It should also be pointed out that all variables keep constant for a whole time-step. Prior to calculating reflected pulses for the next time-step, the upper and lower

arm currents should be updated based on the obtained nodal voltages, as briefly expressed by

$$\begin{bmatrix} ni_u \\ ni_d \end{bmatrix} = \begin{bmatrix} \frac{1}{\Sigma Z} & \frac{-1}{\Sigma Z} \\ \frac{1}{\Sigma Z} & \frac{1}{\Sigma Z} \end{bmatrix} \cdot \begin{bmatrix} V_{dc} \\ nv_s \end{bmatrix} + \begin{bmatrix} -nI_u^{\Sigma} \\ -nI_d^{\Sigma} \end{bmatrix}.$$

(8.31)

The 2N sub-circuits containing the Thévenin equivalent circuit part of the TLM link are identical. When the CFM is adopted for the IGBT/diode, all SMs have two meshes, so according to KVL, the mesh current equations under steady state can be written uniformly as

$$\begin{bmatrix} ni_{l1} \\ ni_{l2} \end{bmatrix} = \begin{bmatrix} Z_C + r_1 + r_2 & -r_2 \\ -r_2 & r_2 + Z_0 \end{bmatrix}^{-1} \begin{bmatrix} 2 \cdot nv_{Cj}^i \\ -2 \cdot nv_{kj}^i \end{bmatrix},$$

(8.32)

where  $_{n}i_{l1}$  and  $_{n}i_{l2}$  are mesh currents,  $Z_{C}$  is the characteristic impedance of DC capacitor. On the other hand, when the transient stage takes place, the collector current can be expressed as a definitive percentage of the arm current, leading to

$$_{n}i_{C1,2} = _{n}k \cdot |_{n}i_{u,d}|,$$

(8.33)

from which it is convenient to calculate the mesh currents by

$$ni_{l1} = ni_{C1},$$

(8.34)

$$_{n}i_{l2} = {}_{n}i_{C1} - {}_{n}i_{C2}.$$

(8.35)

Then, the voltage across each Thévenin equivalent circuit, regardless of the stage, can be calculated by

$$\begin{bmatrix} {}_{n}v_{Cj}\\ {}_{n}v_{kj} \end{bmatrix} = \begin{bmatrix} -Z_{\mathcal{C}} & 0\\ 0 & Z_{0} \end{bmatrix} \cdot \begin{bmatrix} {}_{n}i_{l1}\\ {}_{n}i_{l2} \end{bmatrix} + \begin{bmatrix} 2_{n}v_{Cj}^{i}\\ 2_{n}v_{kj}^{i} \end{bmatrix}.$$

(8.36)

Thus, calculation of reflected pulses can be carried out by substituting the acquired terminal voltages, and the time-step ends with updating the incident pulses.

#### Hardware Design on FPGA 8.4.2

In this section, the MMC with curve-fitting model is applied to drive an induction machine (IM). The hardware design on FPGA is first carried out, followed by real-time emulation results demonstration, analysis, and validation.

| FPGA  | System               | LUT            | FF             | DSP           | f <sub>max</sub> (MHz) |

|-------|----------------------|----------------|----------------|---------------|------------------------|

|       | $MMC_5(3ph)$         | 233 K (76.74%) | 134 K (22.08%) | 966 (34.50%)  | 116                    |

| XC7V- | $MMC_7(1ph)$         | 114 K (37.50%) | 64 K (10.57%)  | 490 (17.50%)  | 115                    |

| X485T | $MMC_11(1ph)$        | 168 K (55.38%) | 109 K (18.03%) | 901 (32.18%)  | 116                    |

|       | MMC <sub>5</sub> -IM | 249 K (82.06%) | 143 K (23.62%) | 1155 (41.25%) | 115                    |

|       | $MMC_5(3ph)$         | 233 K (19.08%) | 134 K (5.49%)  | 966 (44.73%)  | 125                    |

| XC7V- | $MMC_7(3ph)$         | 350 K (28.67%) | 194 K (7.94%)  | 1530 (70.83%) | 121                    |

| 2000T | $MMC_11(1ph)$        | 168 K (13.80%) | 111 K (4.53%)  | 901 (41.71%)  | 121                    |

|       | MMC <sub>5</sub> -IM | 250 K (20.51%) | 143 K (5.87%)  | 1155 (53.47%) | 125                    |

Table 8.7

Hardware utilization of the MMC-IM system.

#### 8.4.2.1 Hardware Platform

The hardware design of the MMC-IM system was carried out on the Xilinx<sup>®</sup> XC7VX485T FPGA, and Table 8.7 lists an estimation of hardware utilization when different levels of MMCs are implemented on two types of FPGA devices, and the maximum operational frequency  $f_{max}$  of each design is also shown. A higher operational frequency gives a larger speed margin for a certain time-step, but the chip power dissipation increases along with it; on the contrary, a lower frequency leads to less power dissipation but the design may fail to attain real-time execution. Therefore, a trade-off is made and the operational frequency of 100 MHz is chosen, with the corresponding clock period of the FPGA  $T_{clk}$  as 10 ns.

The hardware resources of XC7VX485T are sufficient for running a single-phase 11-level MMC but falls short of driving the induction machine with even seven-level MMC due to a lack of LUTs. As can be seen from the table, the demand for one phase accounts for 37.50% and will exceed the total available resources if the size triples. This can be avoided if the design is deployed to another FPGA device with abundant LUTs like the XC7V2000T, although it has fewer DSPs for implementing the three-phase 11-level MMC, as shown in the same table.

#### 8.4.2.2 Controller Emulation

For the MMC-IM system, the controller is twofold, referred to as the MMC inner control and induction machine outer control, respectively. The former is in charge of SM DC capacitor voltages, and the latter regulates the induction machine's angular velocity. Detailed control algorithms for MMC and the induction machine

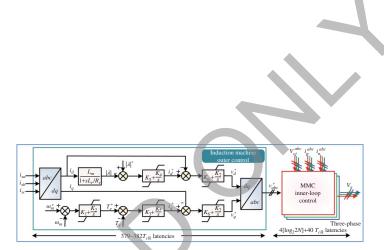

have been separately developed [164, 165], and the overall controller combing both is shown in Figure 8.16. Three-phase stator currents  $i_{sa}$ ,  $i_{sb}$  and  $i_{sc}$  as well as  $\omega_m$  and its reference  $\omega_m^*$  are the inputs for the outer controller, which produces three-phase modulation signals  $v_{abc}^*$  and sends them to the inner controller as its inputs. Then the three-phase MMC inner controller generates driving pulses to control the switches.

As can be seen, regardless of what the conditions of surrounding devices such as the induction machine are, the hardware latency of the outer controller is restricted in a small range between 379 and 382  $T_{clk}$ , while the latency of the inner controller is a logarithmic function of the number of submodules in a leg due to the averaging of DC capacitor voltages, and the hardware delay is

$$L_{inner} = (T_{adder} \cdot \lceil \log_2(2N) \rceil + 40) \cdot T_{clk}, \tag{8.37}$$

where  $T_{adder}$  is the latency of the adder, which takes four clock cycles for single precision numbers, and the rounding function is equivalent to setting *N* to its nearest even number times of 4. Hence, for the five-level MMC that has eight submodules, the controller latency is 52  $T_{clk}$ , or 520 ns time delay, slightly over the time-step of 500 ns for the MMC circuit, and for the seven-level MMC this delay increases to 560 ns, so using the same time-step would hinder achieving real-time. The solution is to utilize multiple time-steps for these two subsystems emulated in parallel: 1 µs for the MMC inner controller and 4 µs for the IM outer controller. Theoretically, with this time-step setting, the inner controller is able to deal with MMCs with thousands of levels for real-time HIL emulation purpose, but in reality, the number of voltage levels is restricted by hardware resources.

### 8.4.2.3 MMC Emulation on FPGA

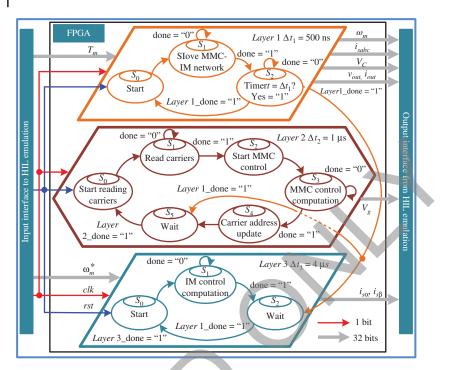

Table 8.8 is a summary of the latencies of each hardware module in the five-level MMC-IM system and the emulation time-steps for these subsystems. Based on the update frequency of variables, the whole system is dispatched to three layers, each satisfying the following criterion that ensures real-time:

$$T_{clk} \cdot max\{L_1^i, L_2^i, \dots, L_n^i\} \le \Delta t_i,$$

(8.38)

where  $L_1^i, L_2^i, \ldots, L_n^i$  are the latencies of hardware modules that the *i*th layer with the time-step  $\Delta t_i$  contains.

In order to run the five-level MMC HIL emulation in real-time, the time-step for *Layer 1* should be close to 370 ns, if the induction machine is not taken into account. According to the device datasheet, this minimum time-step is approximately the rise/fall time of the selected Infineon<sup>®</sup> IGBT FZ400R33KL2C\_B5 ( $V_{CES} = 3300 \text{ V}, I_C = 400 \text{ A}$ ) when its gate resistor is 10  $\Omega$ . This means that under these circumstances, a maximum of two values can be caught during rise/fall

Figure 8.16 Control algorithm for the MMC-IM system.

| Hardware module   | Maximum latency     | Time-step (μs)     | Layer   |

|-------------------|---------------------|--------------------|---------|

| MMC main circuit  | 37T <sub>clk</sub>  |                    |         |

| Induction machine | $41T_{clk}$         | $\Delta t_1 = 0.5$ | Layer 1 |

| Submodule         | $37T_{clk}$         |                    |         |

| MMC controller    | $52T_{clk}$         | $\Delta t_2 = 1.0$ | Layer 2 |

| IM controller     | 382T <sub>clk</sub> | $\Delta t_3 = 4.0$ | Layer 3 |

**Table 8.8**Latencies of different hardware modules in the five-levelMMC-IM system.

process and that section of the switching curve is straightened. On the other hand, the transient process is not limited to the aforementioned region, and there are other sections of the curves that distribute beyond it; thus, the time-step can be set a little larger to 500 ns and the voltage and current waveforms can be represented by piecewise linearized lines, one of which contains the rise/fall process.

Table 8.8 also shows that the induction machine has the largest latency in *Layer 1*. However, when the number of submodules increases, as the only part whose latency is affected, the MMC main circuit latency begins to overtake the IM as the dominant factor to determine real-time operation. The latency incremental for (M + 1)-level MMC main circuit can be deduced from its (N + 1)-level counterpart by

$$\Delta t_{N \to M} = \left( T_{adder} \cdot \left\lceil \log_2 \frac{M+1}{2^{\lceil \log_2(N+1) \rceil}} \right\rceil \right) \cdot T_{clk}.$$

(8.39)

Thus, the maximum number of levels that can achieve for real-time HIL emulation with a 500 ns time-step is 64, when the latency of the MMC main circuit reaches 49  $T_{clk}$ .

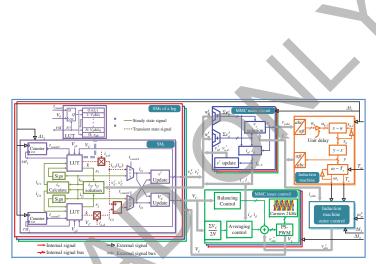

The hardware structure and signal flow routes for the MMC-IM system are drawn in Figure 8.17, where *j*th submodule structure can be seen out of the total 2*N* submodules. There are two levels of parallelism in the design: layers with different time-steps run simultaneously, and all hardware modules within a certain layer are also in parallel. In *Layer 1*, after each time-step  $\Delta t_1$ , the MMC main circuit exchanges TLM link information with the submodules and updates the three-phase voltages for the induction machine, from which stator currents are received. Then there are information exchanges between the layers. Data going to the IM outer controller will not take effect unless an entire time-step  $\Delta t_3$  ends and produces the three-phase modulation waves for the inner one. For *Layer 2*, since  $\Delta t_2$  is between two other time-steps, the values of modulation waves are kept constant for  $\frac{\Delta t_3}{\Delta t_2}$  cycles and the DC capacitor voltages  $\mathbf{V}_C$  and arm currents from *Layer 1* can participate in the control only when a new time-step begins.

Figure 8.17 Hardware structure and signal flow diagram for the FPGA emulation of the MMC-IM system.

Figure 8.18 Finite state machine of the overall MMC-IM system for hardware emulation.

One of the benefits with such a hardware design is that all external and internal signals as well as the hardware other than LUTs in the submodules will not change if a new piecewise linear switch model is established to replace the original one. Even if a more complex switch model such as physics-based model is introduced, the only alteration occurs within submodules, thus there is no necessity to redesign the hardware for other parts.

With regard to the specific structure of each hardware module, their corresponding functions are written in C/C++ in Xilinx<sup>®</sup> Vivado HLS<sup>®</sup>. In this hardware design there are totally five types of function blocks: the induction machine, the MMC main circuit and submodules as well as the two controllers. Each is coded as an independent function in a separate program, whose inputs and outputs include all external signals of that block. Meanwhile, detailed mathematical as well as logic operations within a function block, such as those in Figure 8.17, are represented by the programming language in a pipelined fashion. Although Vivado HLS<sup>®</sup> also has a pipeline directive option, which could further increase the maximum operational frequency of the designs, it was not used because the frequency improvement is at the cost of more hardware resource utilization and 100 MHz was deemed sufficient to ensure real-time execution. By running C synthesis of the completed code and the exporting RTL operation that follows, an IP core, the hard-ware module corresponding to the function block, is generated. However, these modules are yet to be linked with each other. This is realized by very high-speed integrated circuit hardware description language (VHDL) coding in the form of signal exchange that takes place at the end of every time-step, and so is the finite state machine that achieves the multilayer design and decides the time sequence of each module.

Figure 8.18 shows the relationship between different layers and how they cooperate to execute the entire MMC-IM system by finite state machine. It should be pointed out that the maximum latency in each layer is smaller than corresponding time-step, meaning that the MMC-IM system will proceed faster than real-time. Therefore, a timer is introduced in Layer 1 to achieve exact real-time, when it counts to  $\Delta t_1$ , that value is reset and the calculation for the next time-step begins. The command is also sent to the other two layers to enable their respective FSMs to enter a new stage, if they are already waiting. In Layer 2, the values of carriers are needed before the control starts, and near the end of each time-step, the carrier addresses are updated so that in the next time-step new values can be referred to. For the last layer, the operation is similar to the first layer, other than the fact that shifting to state  $S_0$  is controlled by the command from the latter. When the reset order is issued, the states in all three layers begin to circulate and the HIL emulation of the MMC-IM system is ongoing. Thus, by giving proper speed and torque orders through the input interface, the status of the overall system can be observed via the output interface.

# 8.4.3 Real-Time Emulation Results

# 8.4.3.1 MMC

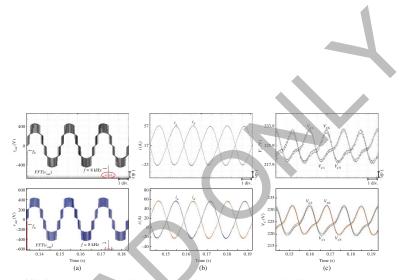

In this part, functions of different levels of MMCs are tested with R-L load. In the test, the DC line voltage is maintained at 900 V, meaning that when the number of levels increases, the DC capacitor voltages will decline accordingly. However, the values of other circuit components such as the arm inductance will not be changed, as shown in Appendix A.7, and the switching frequency is 2000 Hz. To validate the results from HIL emulation, SaberRD<sup>®</sup> simulations are also carried out with a maximum time-step 500 ns to ensure transient processes are recorded. The IGBT and diode models employed in simulations are  $igbt1_3$  and dp1.

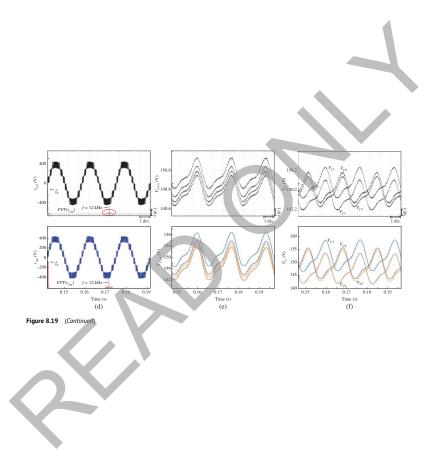

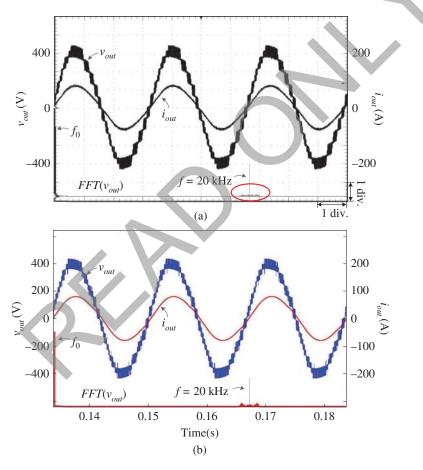

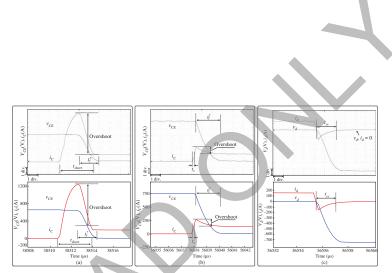

In Figure 8.19 specific system-level performances of the five-level MMC and its seven-level counterpart are shown. Figure 8.19a,d are the 60 Hz, single-phase output voltages of the five-level and seven-level converter, respectively. As can be observed, the voltage waveform in the latter has two more levels than the former, but their peak values are virtually the same, both close to 430 V, and high

Figure 8.19 Comparison of performances of five-level ((a), (b) and (c)) and seven-level ((d), (e), and (f)) MMC between real-time HIL emulation (top) and SaberRD® (bottom). (a) five-level MMC output voltage, (b) arm currents, (c) DC voltage ripples of submodules in upper and lower arms, (d) seven-level MMC output voltage, and (e), (f) DC voltage ripples of submodules. Oscilloscope axes settings: (a), (d) x-axis 5 ms/div, y-axis 133.34 V/div (v<sub>out</sub>) and 66.67 V/div (FFT); (b) x-axis 5 ms/div, y-axis 13.333 A/div; (c), (e) and (f) x-axis 5 ms/div, y-axis 13.34 V/div (z), (e) and (f) x-axis 5 ms/div, y-axis 5 ms/

symmetry is also observed. Moreover, voltage spectral analysis is carried out by the oscilloscope, which demonstrates that for the five-level MMC, its output voltage harmonics mainly distribute around 8 kHz - four times higher than the switching frequency, while for the seven-level converter, the major harmonics center around 12 kHz. This phenomenon agrees with the theory that for (N + 1)-level MMC, the effective switching frequency is N times higher. The results are verified by SaberRD® simulations as they give identical waveforms. Figure 8.19b demonstrates the upper and lower arm currents of the five-level converter, the results from oscilloscope and simulation agree with each other quite well in both waveshape and values. Figure 8.19c shows the DC voltage ripples of the submodules in upper and lower arms for the five-level converter. These values fluctuate around the reference of 225 V, indicating the inner controller is working properly. The peak-valley difference is estimated to be around 13.3 V from the oscilloscope and simulation. In Figure 8.19e,f, some DC capacitor voltages of seven-level MMC are shown and compared. The former indicates that for submodules in the same arm, the rising/declining trends of DC voltage ripples are same, while the latter shows the trend in the opposite arm is totally in contrary. The average values of these DC voltages, as can be read from these figures, are about 150 V since the number of submodules in an arm increases to six while DC line voltage is kept constant.

Figure 8.20 gives the switching process and power losses in the five-level MMC and the shape of these waveforms in seven-level MMC are almost the same and are therefore not shown. Figure 8.20a,b are the transient IGBT voltage and current waveforms during the turning on and off processes. After exerting a positive driving pulse on the gate and a period of turn-on delay lasting for 1 µs, the voltage begins to drop and a current surge can be observed from both HIL emulation and SaberRD<sup>®</sup> simulation. Then the current gradually stabilizes and the voltage finally remains slightly above zero due to the conduction resistance. The rise time is defined as the time interval between 10% and 90% of collector current under steady state, which is around 0.33 µs, slightly below 0.4 µs provided in the datasheet. When the driving pulse disappears, the turning off process takes place after a turn-off delay of approximately 4 µs; it is an opposite process during which  $v_{CE}$  rises to DC capacitor voltage and collector current goes to zero, but the fall time has a similar definition to rise time and its value is near 0.42 µs, a little larger than the datasheet value of 0.35 µs. In Figure 8.20c, diode reverse recovery process is shown. As can be seen after plunging to peak value, which virtually has the same amplitude as the steady-state current, the reverse current begins to decay to zero and voltage over the diode climbs to DC capacitor voltage. It is observable that the current tail in the SaberRD® simulation is a little longer, but since the value of the final stage is extremely small it is forced to zero in the diode model and that will not cause a significant error when calculating power loss. Meanwhile, the forward voltage of diode is also nonzero attributing to the exponential static

Figure 8.20 Details of switching processes and power losses of IGBT or diode from HIL emulation (top) and SaberRD® simulation (bottom). (a) IGBT turning on, (b) IGBT turning off, and (c) diode reverse recovery. Oscilloscope axes settings: x-axis 1 µs/div, y-axis 40 V/div and 26.67 A/div.

I-V characteristics. The power loss corresponding to each process is also shown, a high degree of consistency between HIL emulation and SaberRD<sup>®</sup> simulation is observed.

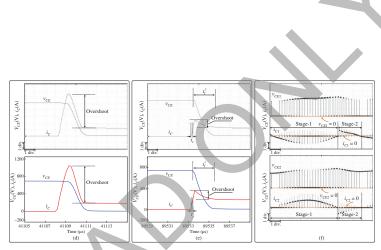

To validate the effectiveness and convenience of the circuit partitioning method in achieving real-time, the seven-level MMC is expanded to 11-level and emulated execution on the FPGA. Figure 8.21a is the 11-level output voltage and the load current from HIL emulation, compared with those of five- and seven-level MMC. The voltage quality is higher and as anticipated that the voltage spectral analysis yields an array of harmonics around 20 kHz, but they are almost negligible. The root mean square value of fundamental component is same to those of other two,

**Figure 8.21** System-level behavior of 11-level MMC: (a) real-time oscilloscope results; (b) SaberRD<sup>®</sup> simulation results. Oscilloscope axes settings *x*-axis 5 ms/div, *y*-axis 133.34 V/div ( $v_{out}$ ), 66.67 V/div (FFT), and 66.67 A/div.

all about 280 V. The output current, due to filtering effect of inductors, is sinusoidal and it reaches a peak value of 80 A, agrees with its theoretical value. The results from SaberRD<sup>®</sup> are also shown in Figure 8.21b for comparison, which indicates the hardware implementation of MMC is correct.

Table 8.9 lists the time each switching process takes. The IGBT turn-on delay from HIL emulation is exactly what was provided in the datasheet, while its turn-off delay and diode reverse recovery time are both rounded to integers because the HIL emulation time-step is 500 ns. The errors for IGBT rise and fall time are relatively large, because their values are smaller than the time-step and, consequently, both processes are located on straightened lines and affected by the slopes.

For the upper switch in a submodule, the maximum current flows through the antiparallel diode while for the lower switch, the maximum current emerges in the IGBT; thus, their power losses are important. Table 8.10 shows the energy consumption of IGBT and diode during the transient process and steady-state when the current reaches largest in five- and seven-level MMC, where the errors are in their absolute forms to avoid negative values. As can be seen from Figure 8.20, the maximum steady-state current for both IGBT/diode pairs is about 60 A.

| Time                     | Description           | HIL (µs) | Datasheet/<br>SaberRD® (μs) |

|--------------------------|-----------------------|----------|-----------------------------|

| $t_{IGBT}^{d,on}$        | Turn-on delay         | 1.00     | 1.00                        |

| $t_{IGBT}^{r}$           | Rise time             | 0.33     | 0.40                        |

| $t_{IGBT}^{d,off}$       | Turn-off delay        | 4.00     | 3.90                        |

| $t_{IGBT}^{f}$           | Fall time             | 0.42     | 0.35                        |

| t <sup>rr</sup><br>diode | Reverse recovery time | 5.00     | 4.80                        |

#### Table 8.9 Switching times of IGBT and diode.

| Table 8.10 | Eneray cons | umption validatior | of IGBT | and diode | model in | MMC |

|------------|-------------|--------------------|---------|-----------|----------|-----|

|------------|-------------|--------------------|---------|-----------|----------|-----|

| ммс                   | 5L-          | ммс       | 7L-MMC             |     |

|-----------------------|--------------|-----------|--------------------|-----|

| Energy (mJ)           | HIL/SaberRD® | Error (%) | HIL/SaberRD® Error | (%) |

| $E_{IGBT}^{turn-on}$  | 14.01/13.43  | 4.32      | 7.93/8.33 4.80     |     |

| $E_{IGBT}^{turn-off}$ | 6.38/6.77    | 5.76      | 5.41/5.43 0.37     |     |

| $E_{IGBT}^{conduct}$  | 2.59/2.58    | 0.39      | 2.40/2.39 0.42     |     |

| $E_{diode}^{rr}$      | 9.28/9.56    | 2.90      | 4.69/5.03 6.76     |     |

| $E_{diode}^{conduct}$ | 1.75/1.76    | 0.57      | 1.69/1.64 3.05     |     |

The steady-state power losses are quite accurate because the static V-I characteristics are provided in the datasheet, whereas the transient waveforms are obtained by curve-fitting, and therefore, the error is a bit larger, but still they are precise and can be referred to when designing the MMC as well as the cooling system. Moreover, with the increase of output voltage level, the power consumed by switches decreases along with voltage and current stresses. Generally, the HIL system is able to offer accurate power losses of both steady-state and transient stages in the MMC despite the variation of its voltage level and the load. It is more convenient compared with measuring power losses by setting up an experimental MMC prototype whose excitations as well as the loads should be adjusted repeatedly in order to provide the switches with the same electromagnetic environment. In addition, although knowing the steady-state current from simulation of conventional MMC models with ideal switches enables direct acquisition of steady-state power loss from the device datasheet, estimating the transient portion based on the turn-on and turn-off energy losses provided by datasheet is less accurate, since they were obtained in an experimental setup with distinct testing conditions.

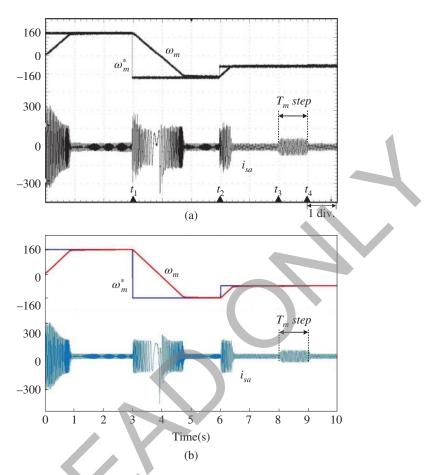

#### 8.4.3.2 Induction Machine Driven by Five-Level MMC

The speed of the induction machine can only be regulated by five-level MMC when the emulation was done on the XC7VX485T FPGA. As shown in Table 8.7, the LUT is not enough for the other two MMCs to extend to three phases.

Figure 8.22a shows the regulation of the mechanical angular velocity by real-time HIL emulation. The initial speed reference is 160 rad/s, so the machine starts and the velocity goes up to the reference value in about one second. Meanwhile, a large stator current can be observed in all three phases and only phase A is shown since they are symmetrical. After one second, the actual speed is very close to the reference and the machine operates under steady-state with stator currents reduce significantly to around 20 A in amplitude. Then at  $t_1 = 3$  seconds,  $\omega_m^*$  plummets to -160 rad/s, meaning that the rotation direction is reversed so that the positive speed slows down to zero and later increases in the opposite direction until it reaches the reference value, which sees a slight increase at  $t_2 = 6$  seconds to -80 rad/s. Consequently, the real speed follows and the machine quickly enters steady state. Between  $t_3 = 8$  seconds and  $t_4 = 9$  seconds, a pulse of 100 N·m is applied to the torque, following this change is a temporary rise of stator current, but the impact it has on the angular velocity is negligible. As can be seen throughout the whole period, a large angular velocity leads to a higher current frequency demonstrated by the density of the waveform. For comparison, Matlab/Simulink simulation is carried out, and corresponding system-level performance is shown in Figure 8.22b, which proves that both controllers are functioning normally and the design theory is correct.

**Figure 8.22** Regulation of induction machine speed by five-level MMC: (a) real-time oscilloscope results, and (b) off-line simulation results. Oscilloscope *x*-axis: 1 s/div.

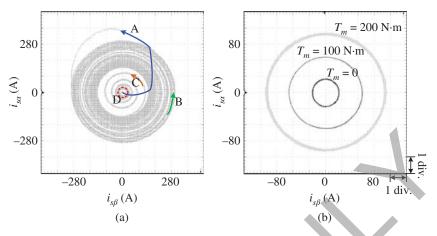

The starting of the induction machine with different values of torques was also tested. In Figure 8.23a, the locus of stator currents in  $\alpha - \beta$  frame are drawn for the starting period when the mechanical angular velocity climbs up from 0 to 160 rad/s without any load. A momentary current surge at the vertical axis is observed immediately after starting, indicated by curve *A*. Then, as can be seen from curve *B*, the current steadily reduces from 300 to 150 A, and following a sudden decline shown by curve *C*, the current finally stabilizes around the region *D*.

The loci of stator currents for three torques under steady-state are shown in Figure 8.23b. As expected it shows that a larger torque yields a circle with greater

**Figure 8.23** Real-time oscilloscope results of stator current in  $\alpha - \beta$  frame under (a) starting period, and (b) steady-state with  $T_m = 0$ , 100 and 200 N·m, respectively. Oscilloscope *x*- and *y*-axis settings: (a) 93.34 A/div; (b) 26.67 A/div.

radius. Other information such as the relation between the duration of transient process and torque is also available. When  $\omega_m^* = 160 \text{ rad/s}$ , it takes 0.52, 0.65, 0.86, 1.31, and 2.68 seconds for the machine to reach 95% of  $\omega_m^*$  when the torques are  $-200, -100, 0, 100, \text{ and } 200 \text{ N} \cdot \text{m}$ , respectively, indicating a larger torque leads to a longer time to approach steady state, while the reverse is true for  $\omega_m^* = -160 \text{ rad/s}$ .

# 8.5 MMC Partitioned by Coupled Voltage-Current Sources

## 8.5.1 V-/ Coupling

The coupled voltage–current sources (V-I) can be inserted between the arm and submodule in an exact manner, where the TLM-link is applied [166]. However, the V-I coupling does not require the additional characteristic impedance that TLM-link has, as shown in Figure 8.24. The current source is placed on the submodule side since it contains nonlinear IGBT/diode models solved by nodal equations. While on the left side, the MMC main circuit can either be solved by mesh current or nodal voltage equations – in the latter case, the coupled voltage sources need to be converted to current sources first.

The partitioning method induces a unit delay to both sides. At the instant  $t - \Delta t$ ,  $i_u(t - \Delta t)$  and  $i_d(t - \Delta t)$  are obtained by solving the matrix equation corresponding to the left circuit, and they are sent to the submodules. Then, the time instant

Figure 8.24 MMC partitioning by V-I coupling.

*t* begins. On the submodule side, based on the SM current it just received, its port voltage  $v_k(t)$  can be derived. Thus,  $v_k$  is one time-step ahead of  $i_u$  and  $i_d$  on the SM side, while the reverse is the case for the MMC arm. Nevertheless, under the circumstance that the circuit computation frequency is much higher than that of the arm current,  $i_u$  and  $i_d$  can be deemed as constants in two neighboring time-steps. Consequently, the impact of unit-delay methods, e.g. V-I coupling and TLM-link, on simulation accuracy is negligible.

The nodal voltage equation on the SM side is determined by the IGBT/diode type it uses, with an *k*-node IGBT/diode model, the SM generally has the following admittance matrix:

$$\mathbf{G}_{SM} = \begin{bmatrix} G_{C} & \mathbf{0}_{1 \times (2k-3)} \\ \mathbf{0}_{(2k-3) \times 1} & \mathbf{0}_{(2k-3) \times (2k-3)} \end{bmatrix} + \begin{bmatrix} m \cdot \mathbf{G}_{\mathbf{S}k \times k} & \mathbf{0}_{(k-2) \times (k-2)} \\ \mathbf{0}_{(k-2) \times (k-2)} & \mathbf{0}_{(k-2) \times (k-2)} \end{bmatrix} \\ + \begin{bmatrix} \mathbf{0}_{(k-1) \times (k-1)} & \mathbf{0}_{(k-1) \times (k-1)} \\ \mathbf{0}_{(k-1) \times (k-1)} & m \cdot \begin{bmatrix} G_{S11} & \cdots & G_{S1(k-1)} \\ \vdots & \ddots & \vdots \\ G_{S(k-1)1} & \cdots & G_{S(k-1)(k-1)} \end{bmatrix} \end{bmatrix},$$

(8.40)

where the element  $G_C$  represents the conductance of SM capacitor; the second matrix lists all elements in the *k*-node upper switch, while its lower counterpart is placed in the third matrix, which only contains  $(k - 1) \times (k - 1)$  elements after

the *k*th node is naturally grounded. Similarly, the current contribution vector can be expressed by

$$\mathbf{J}_{SM} = \begin{bmatrix} I_{hisC} & 0 & \cdots & 0 & J_s |_{(k)} & 0 & \cdots \end{bmatrix} + m \cdot \begin{bmatrix} J_{S1} & J_{S2} & \cdots & J_{Sk} & 0 & 0 & \cdots \end{bmatrix} \\ + m \cdot \begin{bmatrix} 0 & 0 & \cdots & J_{S1} |_{(k)} & J_{S2} & \cdots & J_{S(k-1)} \end{bmatrix},$$

(8.41)

where  $I_{hisC}$  and  $J_s$  are the capacitor's history current and arm current, respectively. The SM nodal voltages are subsequently obtained by

$$\mathbf{U}_{SM} = \mathbf{G}_{SM}^{-1} \cdot \mathbf{J}_{SM}.$$

(8.42)

On the main circuit side, the arms have a fixed form, e.g. the Thévenin equivalent circuit is

$$Z_{arm} = Z_{Lu,d} + r_{arm},$$

$$U_{arm} = 2v_{Lu,d}^{i} + \sum_{k=1}^{N} v_{k}(t - \Delta t),$$

(8.43)