43589

National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Division

Division des thèses canadiennes

Ottawa, Canada. K1A 0N4

## PERMISSION TO MICROFILM — AUTORISATION DE MICROFILMER

| Please print or type — Écrire en lettres moulées ou dactylogra                                                                                                                      | aphier                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Full Name of Author — Nom complet de l'auteur                                                                                                                                       |                                                                                                                                                                                                   |

| ROBERT G. WILLONER                                                                                                                                                                  |                                                                                                                                                                                                   |

| t .                                                                                                                                                                                 | •                                                                                                                                                                                                 |

| Date of Birth - Date de naissance                                                                                                                                                   | Country of Birth — Lieu de naissance .                                                                                                                                                            |

| MAY 15, 1950                                                                                                                                                                        | HUNGARY                                                                                                                                                                                           |

| Permanent Address — Résidence fi                                                                                                                                                    | 4                                                                                                                                                                                                 |

| Rot Willoner,<br>1906 Mountain Hi<br>North Vancouver,                                                                                                                               |                                                                                                                                                                                                   |

| British Columbia                                                                                                                                                                    |                                                                                                                                                                                                   |

| Title of Thesis — Titre de la thèse                                                                                                                                                 |                                                                                                                                                                                                   |

|                                                                                                                                                                                     | RALLEL ARITHMETIC UNIT                                                                                                                                                                            |

|                                                                                                                                                                                     |                                                                                                                                                                                                   |

| <del>-</del>                                                                                                                                                                        |                                                                                                                                                                                                   |

|                                                                                                                                                                                     | ı                                                                                                                                                                                                 |

|                                                                                                                                                                                     | •                                                                                                                                                                                                 |

|                                                                                                                                                                                     |                                                                                                                                                                                                   |

| University — Université                                                                                                                                                             |                                                                                                                                                                                                   |

| UNIV. OF ALBERTA                                                                                                                                                                    |                                                                                                                                                                                                   |

| Degree for which thesis was presented — Grade pour lequel cett                                                                                                                      | to this of litt principality                                                                                                                                                                      |

| PH.D.                                                                                                                                                                               |                                                                                                                                                                                                   |

| Year this degree conferred - Année d'obtention de ce grade                                                                                                                          |                                                                                                                                                                                                   |

| -                                                                                                                                                                                   | Name of Supervisor Nom du directeur de thèse                                                                                                                                                      |

| 1979                                                                                                                                                                                | DR. I.N. CHEN                                                                                                                                                                                     |

| ·                                                                                                                                                                                   |                                                                                                                                                                                                   |

| Permission is hereby granted to the NATIONAL LIBRARY OF CANADA to microfilm this thesis and to lend or sell copies of the film.                                                     | L'autorisation est, par la présente, accordée à la BIBLIOTHÈ<br>QUE NATIONALE DU CANADA de microfilmer cette thèse et di<br>prêter ou de vendre des exemplaires du film.                          |

| The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission. | L'auteur se réserve les autres droits de publication; ni la thèse<br>ni de longs extraits de celle-ci ne doivent être imprimés ou<br>autrement reproduits sans l'autorisation écrite de l'auteur. |

|                                                                                                                                                                                     |                                                                                                                                                                                                   |

| Date                                                                                                                                                                                | Signature                                                                                                                                                                                         |

| September 13,1979                                                                                                                                                                   | Rob Willows                                                                                                                                                                                       |

NL-91 (4/77)

National Library of Canada

Cataloguing Branch Canadian Theses Division

Ottawa, Canada K1A 0N4

NOTICE

Bibliothèque nationale du Canada

Direction du catalogage Division des thèses canadiennes

**AVIS**

The quality of this microfiche is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us a poor photocopy.

Previously copyrighted materials (journal articles, published tests, etc.) are not filmed.

Reproduction in full or in part of this film is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30. Please read the authorization forms which accompany this thesis.

THIS DISSERTATION

HAS BEEN MICROFILMED

EXACTLY AS RECEIVED

La qualité de cette microfiche dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de mauvaise qualité.

Les documents qui font déjà l'objet d'un droit d'auteur (articles de revue, examens publiés, etc.) ne sont pas microfilmés.

La reproduction, même partielle, de ce microfilm est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30. Veuillez prendre connaissance des formules d'autorisation qui accompagnent cette thèse.

> LA THÈSE A ÉTÉ MICROFILMÉE TELLE QUE NOUS L'AVONS REÇUE

## THE UNIVERSITY OF ALBERTA

ON THE DESIGN OF A PARALLEL ARITHMETIC UNIT

bу

(C) ROBERT G. WILLONER

### A THESIS

SUBMITTED TO THE FACULTY OF GRADUATE STUDIES AND RESEARCH

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE

OF DOCTOR OF PHILOSOPHY

DEPARTMENT OF COMPUTING SCIENCE

EDMONTON ALBERTA CANADA

FALL 1979

## THE UNIVERSITY OF ALBERTA

## FACULTY OF GRADUATE STUDIES AND RESEARCH

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies and Research, for acceptance, a thesis entitled "ON THE DESIGN OF A PARALLEL ARITHMETIC UNIT", submitted by Robert Willoner in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

I Ngo Chen (supervisor)

John Tartar,

Stanley Cakay

Douglas Bates

-kinived

Kishor Trivedi (external)

Date <u>August 31, 1979</u>

In this study, the feasibility of performing the four basic arithmetic operations "on-line" and in linear time is investigated. The operands and the results are assumed to be fixed point and in binary notation. An operation is said to perform in <u>linear time</u> if its execution time is bounded from above (and below) by some constant multiple of the length of the longest of the operands. The on-line property satisfied if, in order to generate the ith bit of the result, it is necessary and sufficient to have the operands available to the ith bit only. The operands are assumed to arithmetic unit in bit-by-bit, through the: least-significant-bit-first fashion, and the results are produced in the same manner. The advantages of this mode of computation stem from the fact that a sequence of operations be performed in an overlapped fashion, resulting in a significant . spéeding up over traditional algorithms.

The proposed multiplier consists of a set of modules, one for each bit of the product. A basic module of the multiplier is only slightly more complex than a full adder; instead of three inputs and two outputs, it has five inputs and three outputs, and is designed to execute in the same time as the adder. A divider is designed which accepts its inputs and produces a remainder and quotient in the same

bit-sequential right-to-left fashion, but with an initial time delay proportional to the word length. The divider, which also operates in linear time, consists of three separate circuits executing concurrently, each of approximately the same complexity as the circuits for the other three operations.

Suitable applications for this proposed mode of arithmetic operation are considered. The evaluation of expressions and the use of linear on-line arithmetic in associative memories are prominent among these. A new, superior method of performing modular exponentiation using these concepts is developed. Using this, a high speed hardware device for encoding and decoding messages in a "public-key cryptosystem" is designed.

#### AC KNOWLEDGEMENTS

I wish to express sincere gratitude to my supervisor, Dr. I-Ngo Chen, for his guidance and assistance at every stage in the development of this thesis. I thank the members of my committee, Drs. John Tartar, Stan Cabay, Doug Bates and Kishor Trivedi, who have been invaluable in their thorough assessment of this dissertation. All the people in the Computing Science department have contributed to making my four year stay here a most enjoyable experience.

Special thanks must go to my fiancee, Annie, for providing the motivation necessary for the completion of this work. Above all, I am grateful to my father, Guido, to whom this thesis is dedicated, for instilling in me his belief in the value of education.

## TABLE OF CONTENTS

| Cha        | apter                                                          |    |     |     |        |     |     | рā         | age        |

|------------|----------------------------------------------------------------|----|-----|-----|--------|-----|-----|------------|------------|

| ¹ <b>1</b> | INTRODUCTION                                                   | •  | •   | •   | •      | •   | •   | •          | 1          |

| 2          | LINEAR ON-LINE ADDITION AND SUBTRACTION                        |    | ÷   | •   | . •    | •   | ٠,  | -          | 10         |

|            | 2.1 The Concept of Redundant Notation .                        | •  |     | •   | •      | •   | •   | , <b>-</b> | 10         |

| ı          | 2.2 A Bit-Sequential View of the Ripple-0                      | ar | ry  | y A | dd     | ler | :   | •          | 11         |

| 3          | THE MULTIPLIER                                                 | •  | •   | •   | •      | •   | • , | •          | 23         |

|            | 3.1 Previous Proposals for Multipliers .                       | •  | •   | •   | -      | •   | •   | •          | 24         |

|            | 3.2 A Linear Cn-Line Design                                    | •  | •   | •   | •      | •   | •   |            | 32         |

|            | 3.3 Logical Realization and Application                        | •  | •   | •   | •      | •   | -   | •          | 43         |

|            | 3.4 An Optimal Algorithm for Multiple-Pre-Multiplication       | ci | .si | .01 | 1<br>• | •   | •   | •          | 50         |

| 4          | THE DIVIDER                                                    | •  |     | •   | -      | •   | •   | •          | 68         |

|            | 4.1 Fixed-Point Dividers                                       | •  | •   | • ′ |        | •   | •   | •          | 68         |

|            | 4.2 A New Proposal for a Divider                               | •  | •   | • ` | •,     | •   | •   | •          | <b>7</b> 5 |

| 5          | ASSOCIATIVE MEMORY APPLICATIONS                                | •  | •   | •   | . •    | •   | •   | •          | 82         |

|            | 5.1 An Associative Processor Model                             | -  | •   | •   |        | •   | •   | •          | 82         |

|            | 5.2 Addition of a Sequence of Numbers in Associative Processor | an |     | •   | •      | •   | ٠.  | *          | 87         |

|            | 5.3 Multiplication of a Sequence of Number                     | rs | ;   | 4   | •      | -   | •   |            | 95         |

| ·          | 5.4 Vector and Matrix Operations                               |    |     | -   |        |     |     |            | 99         |

| 5 | APPLICATIONS IN CRYPTOGRAPHY                       | 107 |

|---|----------------------------------------------------|-----|

|   | 6.1 What is a Public-Key Cryptosystem?             | 107 |

|   | 6.2 An O(n²) Algorithm for Modular Exponentiation. | 110 |

| 7 | CONCLUSIONS                                        | 120 |

|   | BIBLIOGRAPHY                                       | 125 |

# LIST OF FIGURES

|   | figure | e de la companya de | pε | age          |

|---|--------|---------------------------------------------------------------------------------------------------------------|----|--------------|

|   | 1.1    | Flynn's categorization of parallel processors                                                                 | ٠. | 3            |

|   | 1. 2   | A linear pipeline illustrated                                                                                 | •  | 7            |

|   |        |                                                                                                               |    |              |

|   | 2.1    | Addition and subtraction tables                                                                               | •  | - <b>1</b> 2 |

|   | 2.2    | Examples of addition and subtraction                                                                          | -  | 13           |

|   |        | A sequential adder, viewed in the context of this thesis                                                      |    | 14           |

| 7 | 4      | One of the modules of the parallel adder                                                                      |    | 18           |

| • | 2.5    | Linkage of the adder modules                                                                                  | -  | <b>1</b> 9   |

|   |        |                                                                                                               |    |              |

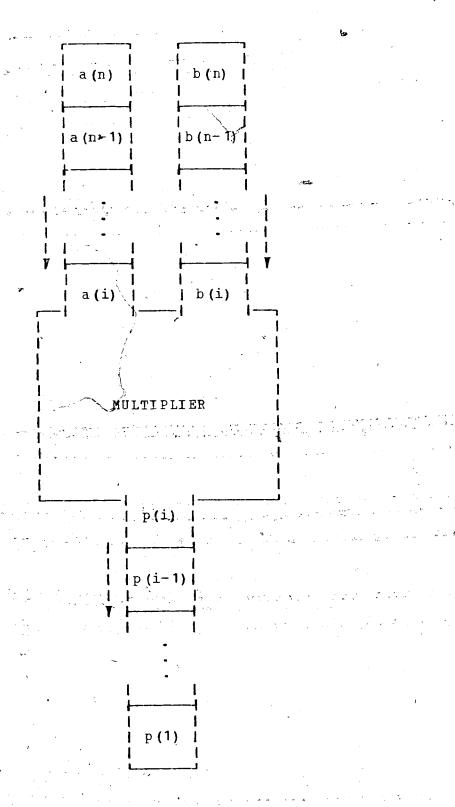

|   | 3.1    | The multiplier immediately before initiating step i in the computation of the product of A and B              | •  | 27           |

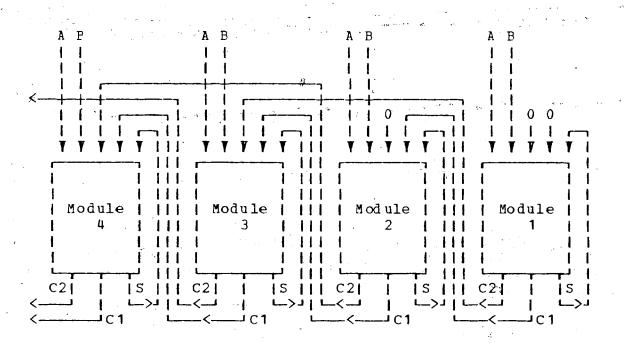

|   | 3.2    | One of the modules of the parallel multiplier                                                                 | •  | 36           |

|   | 3.3    | Linkage of the multiplier modules                                                                             | •  | 38           |

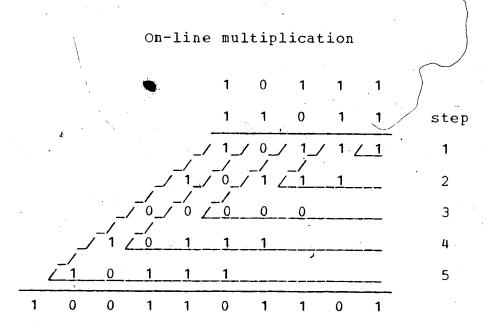

|   | 3.4    | Generation of the elements of the multiplication rhombus                                                      | •  | 39           |

|   | 3.5    | Example of generation of A(i,j)'s and B(i,j)'s .                                                              | •  | 44           |

|   | 3.6    | Full multiplication example. The 5 inputs to each module are arranged as shown at the bottom right            |    | 45           |

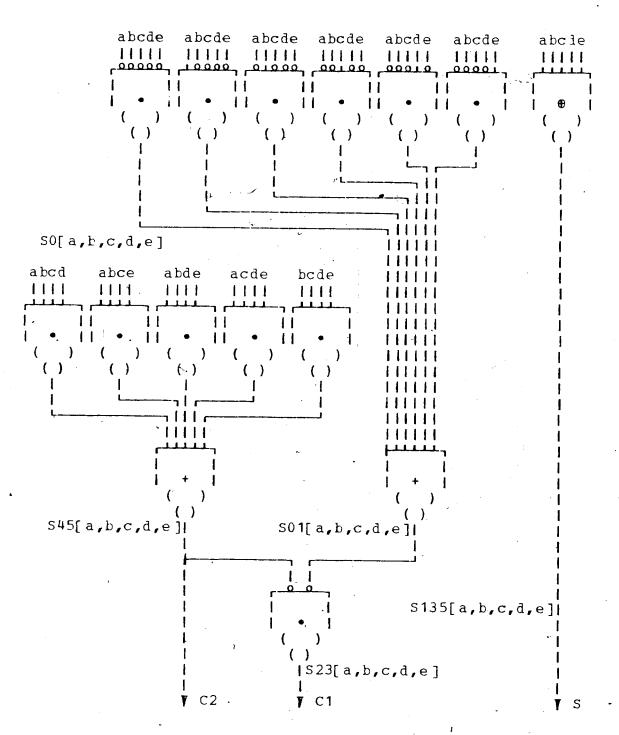

|   | 3.7.   | Legend for logic diagrams, illustrated with examples                                                          | •  | 46           |

|   | 3.8    | Logical realization of a multiplier module                                                                    | -  | 47           |

|   | 3.9    | Pipelined computation of (A*B - C*D + E) * F                                                                  |    | 49           |

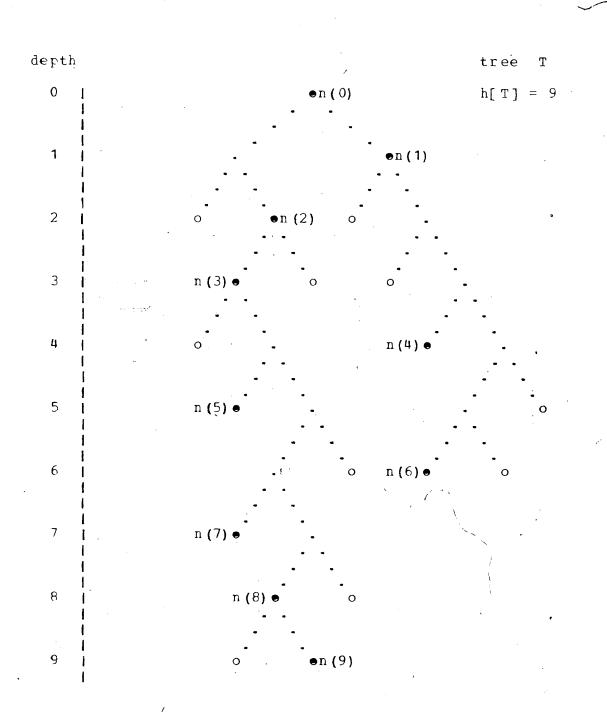

|   | 3. 10  | A compact computation tree, T                                                                                 | •  | 58           |

|   | 3.11   | A computation tree, T', similar to T                                                                          | •  | 60           |

|   | 3.12   | A sample evaluation of the function "t"                                                                       |    | 62           |

| •    |                                                                          |

|------|--------------------------------------------------------------------------|

| 4.1  | Example of standard division method 69                                   |

| 4.2  | The same example, modified for machine implementation                    |

| 4.3  | Example of reciprocal evaluation                                         |

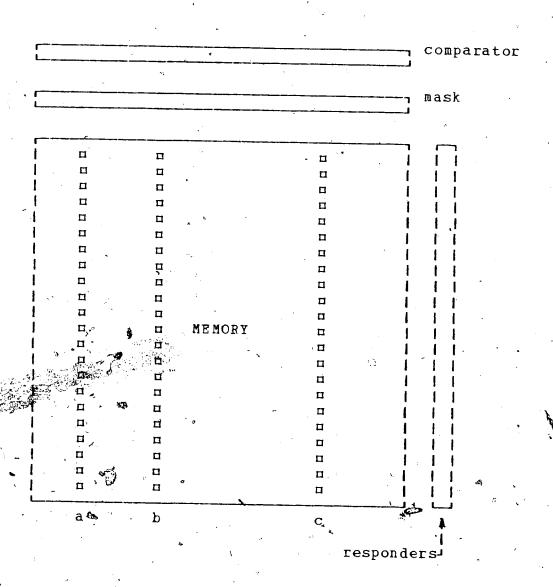

| 5.1  | An associative processor with bit-slice capabilities                     |

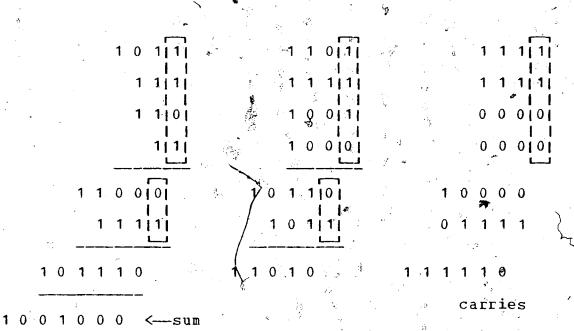

| 5. 2 | Example of bit-slice on-line addition in an associative memory           |

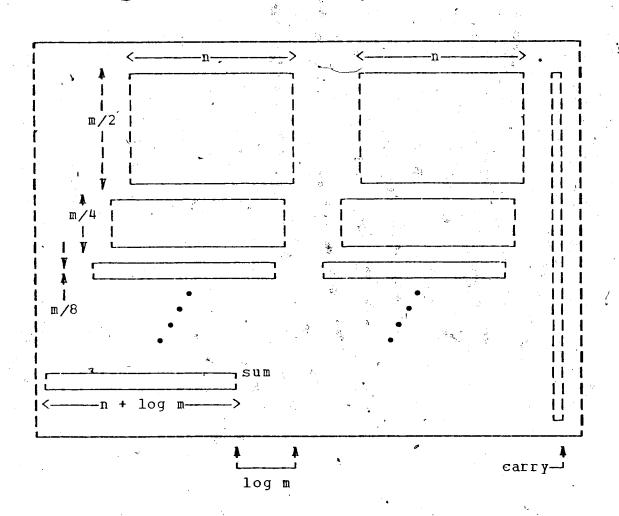

| 5.3  | Addition of m numbers in an associative memory 91                        |

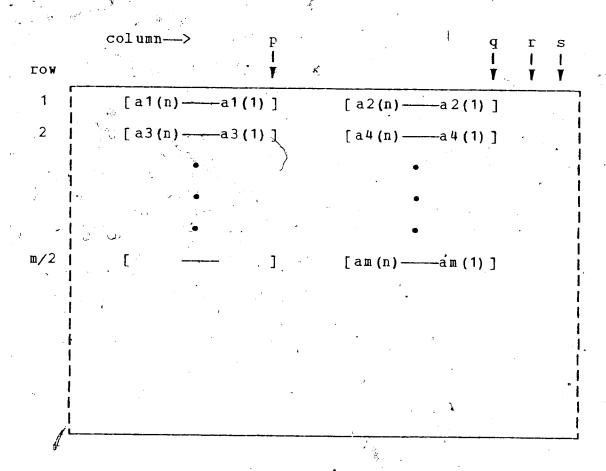

| 5.4  | Initial layout of operands in memory prior to addition                   |

| 5.5  | Example of bit-slice on-line multiplication in an associative memory     |

| 5.6  | Computation of dot product 101                                           |

| 5.7  | Summary of applications of linear on-line circuits in associative memory |

| 6.1  | Example of modular exponentiation                                        |

| , .  |                                                                          |

| ٠.   |                                                                          |

|      |                                                                          |

|      |                                                                          |

## LIST OF ALGORITHMS

| algori |                                                                       |       | page     |

|--------|-----------------------------------------------------------------------|-------|----------|

| 2. 1   | Linear on-line addition                                               |       | 21       |

|        |                                                                       |       |          |

| 3.1    | Linear on-line multiplication                                         | • •   | . 41     |

| 3.2    | Evaluation of the intermediate function "t"                           | • •   | 61       |

| 4.1    | Restoring division algorithm                                          | • •   | 73       |

| 4.2    | Non-restoring division algorithm                                      | •     | 74       |

| 4.3    | Recursive function for computing reciprocals                          |       | 78       |

| 5.1    | Associative memory addition                                           |       | 94       |

| 5.2    | Associative memory multiplication                                     | •     | 96       |

|        |                                                                       | :     | e Torres |

| 6.1    | Modular exponentiation by repeated squaring multiplication            | and   | . 113    |

| 6.2    | Modular exponentiation algorithm suitable for hardware implementation | r<br> | . 114    |

## chapter one INTRODUCTION

Parallel processors have been categorized in a number of different ways[49]. Perhaps the categorization most commonly accepted is one based on the stream concept Flynn[19]. A stream is a sequence of introduced bу instructions or data as executed or operated on by a Using this concept, parallel computers are processor. classified by the magnitude (either in space or in time) of interactions of their instructions and data streams. In the simplest case, an SISD (single instruction stream, single data stream) machine, only one instruction can be operating on one set fof data at any given time. SIMD (single instruction stream, multiple data stream) computers have only one stream of instructions in execution at any time, but each instruction may affect many different data items. These parallel computers are further categorized in [19] as follows:

- parallel in space, as an structured array computers e.g. ILLIAC IV, OMEN-60, SIMDA;

- unstructured linear array computers, or <u>ensembles</u>

e.g. PEPE, Goodyear STARAN S;

- parallel primarily in time, as are pipelined computers

- e.g. Amdahl 470 V/7, Cray-1, TI ASC;

associative processors whose memories are addressed by contents rather than by addresses e.g. PEPE, Goodyear STARAN S.

MIMD (multiple instruction stream, multiple data stream) machines have more than one stream of instructions, in fact, as many streams as there are data streams. These parallel computers are essentially interconnected sequential computers, usually called multiprocessors. The UNIVAC 1108 is an example of such a machine. Flynn's categorization is summarized in Figure 1.1, along with examples.

arithmetic unit is the heart for computation on a digital computer, and as such, has been focus of the research in the hardware area from the time the field was defined. The standard ripple-carry adder[31] is the simplest to build, and it performs in O(n) time, where n is the number of bits of the addends. This adder is both linear and on-line. A "ripple-borrow" subtractor performs in an analogous manner. Theoretically, each of these can speeded up to O(log n) by the use of "carry-lookahead"[31], bu t the cost of enormously increasing the complexity of circuitry. Information-theoretic arguments can be used the

D A T A

|                                           |                                   | Single<br>Data<br>Stream<br>(SD)        | Multiple Data Stream (MD)                                       |

|-------------------------------------------|-----------------------------------|-----------------------------------------|-----------------------------------------------------------------|

| Single Instruction Stream (SI)            | H<br>H<br>H<br>H<br>H             | Unit Processor  e.g. IBM 360            | F=====================================                          |

| Multiple<br>Instruction<br>Stream<br>(MI) | н<br>,н<br>,н<br>н<br>н<br>н<br>н | Pipelined Processor e.g. Amdahl 470 V/6 | Multiprocessor<br>  Multiprocessor<br>    e.g.<br>  UNIVAC 1108 |

Figure 1.1. Flynn's categorization of parallel processors.

that this is asymptotically optimal. The simplest algorithm for performing multiplication without the use of parallelism requires O(n2) time. Knuth[30] has shown that this can be reduced to  $O(n 1 (1+\epsilon))$  for any arbitrarily small  $\varepsilon$ , but this result is not practical as the algorithms become increasingly complex as  $\epsilon \longrightarrow 0$ , causing the constant of proportionality to become extremely large. Schonhage and Strassen[44] have shown a serial algorithm that is a considerable improvement: C(n log n log log n). This is the known algorithm but it is not yet known whether or fastest is optimal. Knuth shows a division algorithm of the order of time complexity, based the Schonhage-Strassen multiplication algorithm.

Atrubin[5] the was first to show that by allowing parallelism, it is possible to perform multiplication in time O(n). He also showed a linear on-line algorithm, considerably more complex than the one to be demonstrated, for evaluating the three-operand expression A\*B + C. This algorithm will be discussed in some detail in Chapter 3. Atrubin's work is of interest because it introduced the concept of linear on-line arithmetic, which is the focus of interest in this thesis. An operation is said to perform in linear time if its execution time is bounded from above (and below) by some constant multiple of the length of the longest of the operands. The on-line property is satisfied +The symbol "" is used to denote exponentiation

if, in order to generate the ith bit of the result, it is necessary and sufficient to have the operands available to the ith bit only. The operands and the results are assumed to be fixed point and in binary notation. They are further assumed to flow through the arithmetic unit in a bit-by-bit, least-significant-bit-first fashion, and the results are produced in the same manner.

A number of studies have been made of algorithms which execute on-line, but which perform in a left-to-right, most-significant-bit-first fashion. The most recent result, with references to others, is given by Trivedi and Ercegovac[51]. The nature of their algorithms necessitates the use of a redundant digit set, at least for the bits of the result. This implies the need for post-processing of the results. The algorithms presented here use a redundant notation internally, but produce all results in customary binary notation. Trivedi and Ercegovac present algorithms for multiplication and division which have an inherent fixed time delay independent of the length of the operands.

The advantages of arithmetic operations being performed on-line and in linear time stem from the fact that a sequence of operations can be performed in an overlapped fashion, resulting in a significant speeding up over traditional sequential algorithms. This technique is known as <u>pipelining</u>. Pipelining is a commonly used hardware design

technique utilizing parallelism to for increase computation rate of a computer. The effectiveness of this technique is highly dependent on the structures of the algorithm and of its input data. For certain types of computations, pipelining can result in a significant increase in performance, whereas for others, a noticeable gain may be impossible to achieve.

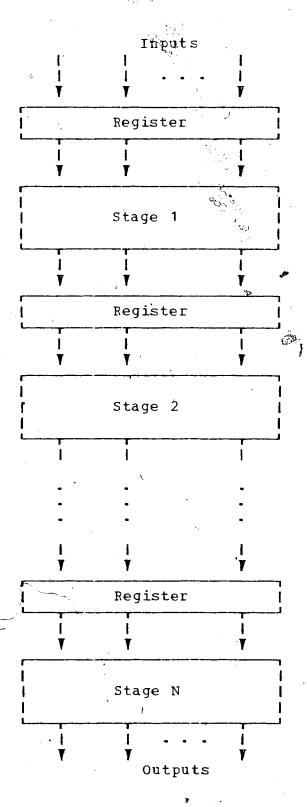

general, pipelining can be used effectively to Ιn realize, an algorithm whenever that algorithm can be divided into a fixed number of steps that are to be executed in sequence. A pipelined realization of such an algorithm consists of several hardware stages separated by registers. There is one stage for each step of the algorithm and they are interconnected in the same order that the steps are executed. This is illustrated in Figure 1.2. Many computers today use this technique for instruction execution. However, the arithmetic computation phase of · an arithmetic instruction is currently always a single stage in the pipeline. The development of on-line techniques in this thesis and in other work allow the potential of breaking up individual arithmetic operations into yet another level of stages to be pipelined.

A number of recent technological developments make the results of this thesis particularly applicable. The bit-sequential nature of the arithmetic discussed herein is

Figure 1.2. A linear pipeline illustrated.

entirely compatible with the nature of bubble memories and CCD's (charge-coupled devices), which are essentially continuous shift registers. The modular construction of each of the devices to be described allows for representation in the bit-slice architecture which is currently popular with many microprocessor manufacturers. Furthermore, the small number of inputs and outputs on each of the designs to be described permit LSI implementation wherein the limited number of pins per chip is a constant constraint.

thesis begins with a discussion of redundant The notation in computer arithmetic, in Chapter 2. ripple-carry adder ~and ripple-borrow subtracter are introduced in preparation for the development and explanation of the multiplier. The next chapter discusses multiplier in detail. A logical the linear on-line realization of the central part of this multiplier is given. It is seen to be simple in construction and, most important, compatible in timing with the adder and subtracter. Chapter with section concerning multiple-precision a multiplication \ in an SIMD processor. Ap algorithm described and proxed to be optimal. The significance of this result lies in the corollaries which follow from it. Lower bounds can be tightened on a number of multiple-precision algorithms, as ( determinant computation, such multiplication, and the solution of a system of linear equations.

ATTERNATION OF THE STATE OF THE

Chapter 4 describes the problems imposed by division. It is shown that strictly on-line division is not possible. The introduction of a delay between inputs and outputs allows the construction of a suitable divider. This proposed divider makes use of the on-line multiplier and adder/subtracter in an iterative convergent reciprocal algorithm.

A number of applications for these elementary results are considered. In Chapter 5, a strong correspondence between on-line arithmetic and bit-slice operations in an associative processor is demonstrated. This leads to a interesting applications in an associative processor, such as efficient algorithms for many vector and matrix operations. Another major application of on-line arithmetic appears in Chapter 6. This concerns the problem of modular exponentiation, which is useful in certain proposed implementations of public-key cryptosystems. The standard cubic algorithm for this problem is improved to one of quadratic complexity.

## chapter two

## LINEAR ON-LINE ADDITION AND SUBTRACTION

A brief discussion of adders and subtracters presented. Ripple-carry and carry-lookahead adders described and compared in time and design complexity. The redundant arithmetic is defined and discussed. notion Ripple carry adders are discussed in view of the arithmetic unit to be proposed.

## 2.1 The Concept of Redundant Notation

The adder and subtracter presented here are capable of producing a result in a redundant notation[26] in unit time (independent of the length of the operands). In the case of the adder, the redundant notation is an extension of standard binary, by allowing the digit 2 in a position. For illustration of the subtracter, it is most convenient to allow the digit -1, denoted 1. Since the result of each of these operations can be performed in unit time, the result in non-redundant form can be produced after n time steps, by effectively performing n ripple-carries.

For the purposes of the multiplier and divider which are to be discussed in the next two chapters, it will also be necessary to have a means of producing a sum in redundant form when one of the two addends is in redundant form, in unit time. An analogous result will be needed for

subtraction. These can all be done, and the corresponding tables appear in Figure 2.1. A few examples which should illustrate the algorithms are given in Figure 2.2. It is easy to realize the required functions as Boolean logic circuits.

## 2.2 A Bit-Sequential View of the Ripple-Carry Adder

The design of the arithmetic unit to be described in this thesis was motivated by observation of the performance of a ripple-carry adder[31]. Let us examine the operation of this simple adder. Assume, throughout this thesis, that all computations are done in fixed point integers and that all numbers are expressed in binary notation. The two addends which are input to this adder must initially be lined up, "right justified", so that the least significant bits of the inputs are in the same position. The adder can then be thought of as a device which moves over the two addates from right to left, putting out a bit of the sum as it passes over each pair of bits of the operands.

A point to be noted is that the adder will have to have some kind of temporary store (possibly denoted as a change of state) which is equivalent to the carry bit.

In this thesis, it will be more useful to think of this same adder as it is depicted in Figure 2.3. The addends "move through" the adder, one bit at a time with the least

#### ADDITION

### SUBTRACTION

|       | without     carry |            | <b>.</b><br>•           |       | without <br> borrow3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |              |

|-------|-------------------|------------|-------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------|

| 0 + 0 | 0                 | 1 1        | <del>  -</del><br> <br> | 0 - 0 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1   | ├─-<br> <br> |

| 0 + 1 | 1 1               | 2          | <br>                    | 0 - 1 | 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0   | <br>         |

| 1 + 0 | 1 1               | 2          |                         | 1 - 0 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0 [ | !            |

| 1 + 1 | 0                 | <b>1</b>   |                         | 1 - 1 | annora de la constante de la c | 1   | <br> <br>    |

| 2 + 0 | 0                 | <b>1</b>   | <br>  ,<br>             | 1 - 0 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0   |              |

| 2/+ 1 | 1 1               | 2          | . s.                    | 1 - 1 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1   | <br> <br>    |

|       |                   | <b>a</b> . | l                       | •/    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1   | I            |

In ADDITION,

1"without carry" means 0, 1, or 0 in column to right

1 2 2

2"with carry" means 1, 0, or 1 in column to right

In SUBTRACTION,

3"without borrow" means 0, 0, or 1 in column to right 0, 0, or 1 in column to right 4"with borrow" means 1, 0, or 1 in column to right

Figure 2.1. Addition and subtraction tables.

102

0 2 1 2 1 1 0

Figure 2.2. Examples of addition and subtraction.

Figure 2.3. A sequential adder, viewed in the context of this thesis.

significant bit first. The sum emerges in the same fashion—one bit at a time, least significant bit first. It begins to emerge exactly one time step after the first bits of the addends are received. Hence, it is not necessary to know the full addends before addition can begin; it is only desirable to supply the input bits at a rate fast enough to keep the adder continuously busy.

The construction of such an adder is trivial. Subtraction has all the simple properties of addition, and the construction of a sequential subtracter along the same lines is equally easy. The design of an adder which accepts three or more operands and still operates in bit-sequential input/output mode would proceed in a similar manner. In fact, an arithmetic circuit could be designed which would accept any fixed number of operands and could perform a fixed sequence of additions/subtractions in bit-sequential input/output mode. Such circuits are not practical, however, because of the fixed number of operands and the fixed sequence of operations required.

A different approach to the problem of evaluating an expression consisting of only additions and subtractions is suggested if a number of parallel adders and subtracters of the above type are available. The expression

$$((A + B) - C) + D$$

can be evaluated by cascading two adders and one subtracter.

This concept is referred to as chaining in the language of the Cray-1[39], and forwarding in the language of the IBM 360/91/3]. Assume the rightmost bits of each of the four operands is available initially, and that successive bits can be supplied one per time step. The first adder can start working on A + B immediately. One time step later, the subtracter can start working on (A + B) - C, and one time step after that, the second adder can start working on the entire expression. Hence, three time steps after the start of the computation, the first bit of the answer is computed. In general, the first bit of the answer is completed after  $\phi$ ø is the number of operations in the steps, where expression. The entire answer is complete after  $n + \emptyset$  steps, where n is the number of bits of the answer. For arbitrary expressions, define n to be the word length of the machine.

The virtues of an arithmetic unit which operates in the above parallel manner are obvious. Newly presented in this thesis are circuits for performing multiplication and division in bit-sequential input/output, right-to-left fashion, thus completing the arithmetic unit capable of operating in this mode.

Multiplication by the traditional algorithm is inherently done in right-to-left fashion, but the complete multiplier and multiplicand are needed before the computation can begin. The circuit to be described uses a

modified version of this algorithm to precisely fulfill the properties required. One time step after the first bits of the inputs are available, the least significant bit of the product emerges. After that, successive bits of the product emerge, one bit per time step.

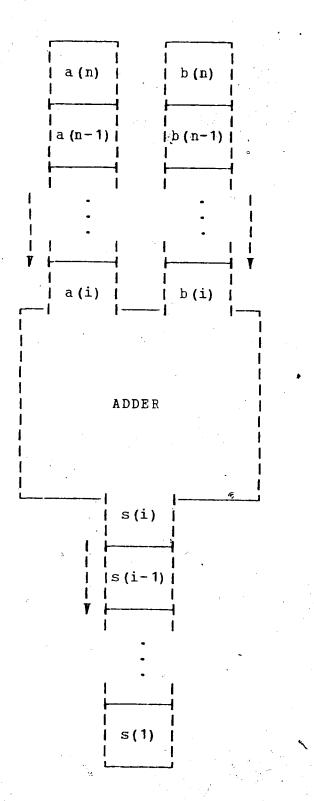

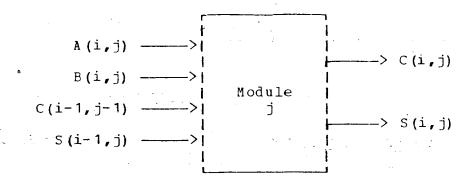

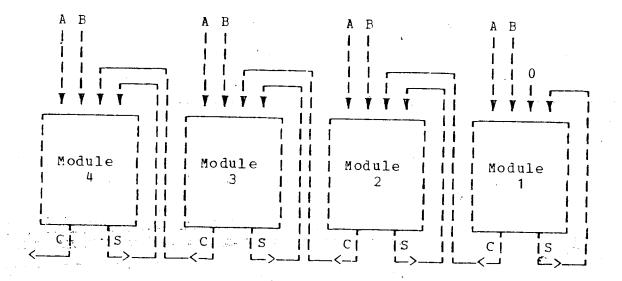

Let us now examine the familiar ripple-carry adder in a format compatible with the descriptions of the other three parallel circuits. Let [a(n)——a(1)] represent the number A The other addend, B, and the sum, S, are in bit form. an analogous way. Internally, the parallel represented in adder consists of a set of n+1 modules, where n is the maximum length of the addends. It is to be noted that only module is operational at any given time, and that the description consisting of several modules is useful only for comparison with the multiplier to be introduced in the next chapter. Each module has four inputs and two outputs; see Figure 2.4 and Figure 2.5. The four inputs consist of two inputs, A and B, from the addends, one carry, C, from the previous module at the previous time step, and a sum bit, S, which is cycled back from the current module at the previous time step. The two outputs from each module consist of a carry bit, C, and a sum bit, S, which is cycled back to the module. Although there are four inputs, it is never same possible to have four ones, which would require two carries, either A and B are both 0 and S is 0 or 1, or S is 0 B are 0 and Hence, one carry bit, C is or 1.

Figure 2.4. One of the modules of the parallel adder.

. Figure 2.5. Linkage of the adder modules.

sufficient. The four input bits generated for the jth module during the ith iteration of the addition algorithm are as follows:

$$A(i,j) = \begin{bmatrix} a(i) & \text{if } i = j-1 \\ 0 & \text{otherwise} \end{bmatrix}$$

$$B(i,j) = \begin{bmatrix} b(i) & \text{if } i = j-1 \\ 0 & \text{otherwise} \end{bmatrix}$$

$$C(i,j) = \begin{bmatrix} 0 & \text{if } j = 1 \\ 0 & \text{otherwise} \end{bmatrix}$$

$$C(i,j) = \begin{bmatrix} 0 & \text{if } j = 1 \\ 0 & \text{otherwise} \end{bmatrix}$$

$$C(i-1,j-1), S(i-1,j) \end{bmatrix} \text{ otherwise}$$

$$S(i,j) = \begin{bmatrix} 0 & \text{if } j = 1 \\ 0 & \text{otherwise} \end{bmatrix}$$

In the above, the functions S13 and S23 represent the symmetric function[31]. For example, S13[v, w, x, y] is 1 if exactly 1 or 3 of the arguments v, w, x, and y are 1; and 0 otherwise. A(i,j) and B(i,j) are the ith bits of the addends. These bits are available at the ith time step. The functioning of the n+1 modules of the parallel adder is presented as Algorithm 2.1.

This algorithm is written serially, but most of it is executed in parallel by the parallel adder. Lines 1-7 are initializations and can be considered to be done at the

## Algorithm 2.1

#### Linear on-line addition

#### begin

```

comment given a(1), a(2), . . . , a(n), and b(1),

b(2), . . . , b(n), the bits of the two numbers to

be added (least significant bit first), this

algorithm computes s(1), s(2), . . . , s(n),

s(n+1), the bits of the sum (again, least

significant bit first):

for i \leftarrow 1 until n+1 do

1.

begin

2.

3.

A (i)

<-- 0;

4.

B(i) \leftarrow 0;

5.

C(i) \leftarrow 0;

6.

S(i) \leftarrow 0

7.

end:

8. .

for i <- 1 until n do

begin

10 -

for j <-- 1 until n do

11.

begin

12.

A(j) \leftarrow 0;

13.

B (j) ← 0

14.

end;

15.

A(i) \leftarrow a(i);

16.

B(i) \leftarrow b(i);

17.

for j \leftarrow n step -1 until 1 do

18.

begin

comment Define C(0) = 0;

19.

t(1) \leftarrow S23[A(j), B(j), C(j-1),

S(j)];

20.

t(2) \leftarrow S13[A(j), B(j), C(j-1),

S(j)];

21.

C(j) \leftarrow t(1);

S(j) \leftarrow t(2)

22.

23.

end

24.

end

and which the policy operation is group as

for i \leftarrow 1 until n+1 do s(i) \leftarrow S(i)

```

And the second of the second o

start of the calculation. The block in lines 10-14 and in lines 15-16 is executed in one parallel operation. This is followed by execution of the block in lines 17-23, also in one parallel operation. Note that there is no need for the temporary variables t(1), and t(2), if the algorithm is executed in parallel rather than serially. The last step, line 25, is a retrieval of the answer. This can be done while computation of the previous steps is under way, with judicious timing such that the result bit of the sum is not retrieved until the circuit has executed a sufficient number of times (bit s(i) of the sum is ready for retrieval after i+1 time steps).

The parallel subtracter is constructed in an analogous manner, and will not be presented. The important property of the traditional addition algorithm which allowed for the previous description also holds for the subtraction algorithm; in subtraction, the carry bit is replaced by a "borrow" bit. For the purposes of this presentation, the possibility of the minuend being larger than the subtrahend causes no more concern than the possibility of an overflow in addition; both leave a carry (borrow) bit after the leftmost position.

## chapter three THE MULTIPLIER

for fast multiplies proposals Previous discussed[26, 54], along with a summary of the known theoretical limitations of such designs. Then, a new parallel multiplier with a very simple configuration is suggested. This multiplier operates in time O(n), where n is maximum of the lengths of the multiplier and multiplicand, both of which are fixed point, expressed in binary notation. It is a logical circuit consisting of 2n modules, each being only slightly more complex than a full adder; instead of three inputs and two outputs, each module has five inputs and three outputs. A logical circuit realization is given for the modules. But perhaps the most significant aspect of this design is the property that the input is required only bit-sequentially and the output is. generated bit-sequentially, both at the rate of one bit per time step, least significant bit first. The advantages of such bit-sequential input and output arithmetic units are described.+

<sup>+</sup>A significant part of this chapter is to appear as a full paper[12] in the October 1979 issue of IEEE Transactions on Computers

## 3.1 Previous Proposals for Multipliers

The design of fast, efficient multipliers is currently very active area[54]. Many scientific and engineering applications such as inversion of matrices, solution of differential equations, computation of eigenvalues, modular exponentiation, etc. require large numbers of multiplications. Especially in the light of technology[48], it is important for computer hardware designers to be aware of current research concerning multipliers which are as efficient as theoretically possible.

most primitive method of multiplication for binary numbers is a direct adaptation of the traditional "school boy method". This algorithm proceeds as follows. accumulator (which is to eventually contain the product) is initialized to 0. Then, each bit of the multiplier is examined, with the rightmost (least significant) bit first. As each bit is scanned, the multiplicand is shifted left one. Whenever a 1 bit is found in the multiplier, the position. multiplicand is added to the accumulator. When all the 1 bits in the multiplier have been exhausted, the accumulator holds the required product. This elementary algorithm is not used in computers with hardware multipliers because of its relative inefficiency. However, in machines

multiplication must be performed through software routines, variations of this method are often used.

simple analysis of the time required to perform a multiplication by the above algorithm should suffice to convince the reader why it is not in common use. Let n be maximum of the lengths (numbers of bits) of the multiplier and the multiplicand. Assuming that the shifts of multiplicand and examinations of the bits of the multiplier can be done in negligible time (a realistic assumption), the problem reduces to that of a number of additions. The number of additions required is one less than the number of 1 bits in the multiplier. In the worst case, this means n-1 additions. The lengths of the addends in each case is not more than 2n. A standard ripple-carry adder can addition in O(n) time steps. Thus, the perform such multiplication requires  $(n-1) \circ (n) = 0 (n^2)$ steps. Theoretically, this can be speeded up by use of a carry-lookahead adder[54, 9], but at the cost of enormously increasing the complexity of the circuitry. The carry-lookahead adder can add two binary numbers of length n time O(log n). Hence, incorporating this in the above multiplication algorithm yields a multiplier which performs in time O(n log n). In practice, the n stages of an adder are divided into groups such that each group contains a full carry-lookahead adder, while a carry ripple is maintained between the groups[9]. This gives a multiplier whose time

complexity lies between O(n log n) and O(n2).

The concept of a parallel multiplier was first introduced by Dadda[13]. Parallel multipliers are discussed by Wallace[53], by Karatsuba and Ofman[28] and more recently by Stenzel et al.[46]. An excellent overview of hardware multipliers is given by Waser[54]. Such parallel multipliers generally operate in time proportional to the maximum of the lengths of the multiplier and multiplicands.

Winograd[58] derived an absolute lower bound on the computation time of a parallel multiplier. He showed if each element of the logical circuit of the multiplier has a fan-in lower than r, then the circuit has a gate delay of at least log  $(n-2)/\log r$ ; thence,  $O(\log n)$  is an asymptotic lower time bound for multiplication, as it is for addition.

The type of multiplier that is of interest to us in this study involves bit-sequential input and output. The operation of such a device is illustrated in Figure 3.1, which depicts a "snapshot" of the multiplier just before the start of the ith step of its procedure. Traditional ripple-carry adders and subtracters have this bit-sequential property. An entire arithmetic unit consisting only of circuits of this type would have an advantage over traditional units, much as the concept of pipelining can be used to perform different segments of hardware instructions +All logarithms in this thesis are taken to base 2

Figure 3.1. The multiplier immediately before initiating step i in the computation of the product of A and B.

independently and simultaneously. Arithmetic operations during the computation of an expression could be overlapped time. For example, in the computation of A\*B+C, it would in not be necessary to complete the computation of the product a and b before the addition can be initiated. As soon as the first bit of A\*B is computed, the addition can be started. In fact, if the length of C were less than the length of A\*B, the expression would be computed in the same length of time as the simple product A\*B. Other authors have discussed the problem of extending a multiplier to compute expression such as A\*B+C. The first example of this was given by Atrubin[5]; this is discussed below. Advanced Micro Devices[1] manufactures an MSI device, the AMD 25805, which computes this expression using an iterative array. The multiplier described herein can also be easily extended to compute this expression, but that is not the gist of this design. The point is that with the bit-sequential nature of the algorithm, any expression could be effectively speeded up (assuming a suitable control device is available).

The generalization to more complicated arithmetic expressions is evident. The success of such a system depends on a number of factors:

<sup>(</sup>i) each circuit must operate in bit-sequential input/output mode;

- (ii) the time required for outputting (and inputting) each bit must be constant, and the same as the time required for a full adder (presumably, this cannot be reduced for more advanced operations);

- (iii) there must be such a circuit for each of the four arithmetic operations (+, -, \*, and /).

In this chapter, a multiplier which meets these requirements is described. A standard ripple-carry adder and subtracter will suffice to satisfy these. A simple counterexample shows that knowledge of the least significant bits of the divisor and the dividend do not determine the least significant bit of either the quotient or the remainder of a division operation, so a divider meeting these strict constraints cannot be designed, but slight relaxations of these restrictions could possibly lead to a divider which would make the system complete. Further discussion of this is given in the next chapter.

A further desirable property of any multiplier is that its components consist of one basic circuit type, much as a ripple-carry adder consists of a sequence of full adders; this leads to economical large-scale integration. Atrubin[5] refers to such bit-sequential circuits as operating in

"real-time", and he discusses one such multiplier. His multiplier consists of a linear iterative array of automata, each of which can be in a finite set of states, at each step of the computation. Each automaton is too complex to operate in time corresponding to a full adder, so that property (ii) above is not met. To the author's knowledge, this multiplier has 'never been implemented. Atrubin's idea was subsequently simplified by Knuth[30]. The following is the basic idea behind their construction. Suppose the product of A and B is desired, and that the bits of these operands are made available sequentially, least significant bit first. Let the bits of A and B be a(1), a(2), . . . , a(n), and b(1), b(2), .,b(n) respectively, least significant bit first. Initially, the first automaton recognizes a(1) and b(1), so is able to output a(1)b(1) at time 1. Then, it sees a(2) and b(2), so it can output  $\{a(1)b(2) + a(2)b(1) + c\} \mod 2$ , where c is the carry left over from the previous step, at time 2. Next it sees a(3) and b(3), and outputs  $\{a(1)b(3) + a(1)b(3) + a(2) + a(3) +$ + a(3)b(1) + c} mod 2; furthermore, its state records the values of a(3) and b(3) so that the second automaton will be able to sense these values at 'time 3, and will be able to compute a(3)b(3) for the benefit of the first automaton at time 4. Thus, the first automaton arranges to start the second one multiplying {a(3), b(3)}, {a(4), b(4)}, . . . . . and the second automaton will ultimately, give the third one the job of multiplying (a(5),

b(5)}, {a(6), b(6)}, . . ., etc. Approximately n/2 automata are required to multiply two n-bit numbers. All bits of the product are output by the first automaton, one per time step, least significant bit first.

In contrast, the multiplier described herein has one module (automaton) for each bit of the product, and the result bits are output by their respective modules. There are 11 inputs to each of the Knuth-Atrubin automata, leading to a possible 2<sup>11</sup> states per automaton; by comparison, the present modules have only 5 inputs.

Trivedi and Ercegovac[51] refer to such bit-sequential circuits as "on-line" circuits. They approach the problem with the inputs and outputs being involved with the most significant bit first. Using a redundant number system and allowing a certain constant time delay (independent of the length of the operands), they design an on-line multiplier and divider. It is not possible to perform a conversion from the redundant system to a non-redundant binary system in bit-sequential mode (most significant bit first). However, their design can accept operands in redundant notation, so the conversion from redundant notation to binary notation can be insignificant in cost when a large number of operations are involved.

#### 3.2 A Linear On-Line Design

In this section, we shall describe a multiplier which takes two n-bit numbers A (the multiplier) and B (the multiplicand) and outputs their product P. It inputs one bit of A and one bit of B at each time step (least significant bit first) and outputs one bit of P at each time step after the first (again, least significant bit first). Just before the start of step i, the multiplier may be visualized as in Figure 3.1. After 2n steps, the product is complete; after n steps, A and B are consumed.

Let [a(n) - a(1)] represent the number A in bit form, with [a(1)] being its degenerate form. Also, let [a(k) - a(1)], for  $k \le n$ , represent the first k bits of A. The number B is represented in an analogous manner. We will denote the full product p by [p(2n) - p(1)] and the partial product of [a(k) - a(1)] and [b(k) - b(1)] by [p(2k) - p(1)]. Then, the traditional method of multiplication may be derived as follows:

$$[p(2n) - p(1)] = [a(n) - a(1)][b(n) - b(1)]$$

$$= \underbrace{\begin{cases} \\ \\ \\ \end{aligned}}_{i=1}^{n} a(i) \cdot 2 \downarrow (i-1) \end{cases} \underbrace{\begin{cases} \\ \\ \\ \end{aligned}}_{i=1}^{n} b(i) \cdot 2 \downarrow (i-1) \end{cases}$$

$$\frac{n}{i=1} = \frac{n}{j=1}$$

$$\frac{n}{j=1}$$

$$\frac{n}{j=1}$$

$$\frac{n}{i=1}$$

$$\frac{n}$$

By contrast, the multiplier to be constructed in this thesis is derived in the following way:

$$[p(2k) - p(1)] = [a(k) - a(1)] [b(k) - b(1)]$$

$$= \{a(k) \cdot 2 \} (k-1)$$

$$+ [a(k-1) - a(1)] [b(k) - b(1)]$$

$$= a(k) [b(k) - b(1)] \cdot 2 \} (k-1)$$

$$+ [a(k-1) - a(1)] \{b(k) \cdot 2 \} (k-1)$$

$$+ [b(k-1) - b(1)] \}$$

$$= [p(2k-2) - p/(1)]$$

$$+ a(k) [b(k) - b(1)] \cdot 2 \} (k-1)$$

$$+ b(k) [a(k-1) - a(1)] \cdot 2 \} (k-1)$$

$$for k > 1$$

Two main points are to be noted about this recursive formula:

[p(1)] = a(1)b(1)

- (i) To compute [p(2k)—p(1)] from [p(2k-2)—p(1)] requires at most two additions (a(i) and b(i) are either 0 or 1) of numbers of length n. Using parallelism, we shall show how a sufficient portion of these additions can be carried out in one time step to output the least significant bit of the sum, and to generate enough carry information to allow processing of the next pair of input addends. Thus we shall be able to compute [p(2n)—p(1)] in 2n time units.

- (ii) In the computation of the sequence [p(1)], [p(2) p(1)], . . . [p(2i)—p(1)], a(i) and b(i) are involved only in the last step. Hence, at the ith step in the computation of [p(2i)—p(1)], only the least significant i bits of A and B are required.