#### University of Alberta

Jit4OpenCL: A Compiler from Python to OpenCL

by

Xunhao Li

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of

Master of Science

Department of Computing Science

©Xunhao Li Fall 2010 Edmonton, Alberta

Permission is hereby granted to the University of Alberta Libraries to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly or scientific research purposes only. Where the thesis is converted to, or otherwise made available in digital form, the University of Alberta will advise potential users of the thesis of these terms.

The author reserves all other publication and other rights in association with the copyright in the thesis and, except as herein before provided, neither the thesis nor any substantial portion thereof may be printed or otherwise reproduced in any material form whatsoever without the author's prior written permission.

## **Examining Committee**

José Nelson Amaral, Computing Science

Duane Szafron, Computing Science

Marek Reformat, Electrical and Computer Engineering

To my beloved family.

## Abstract

Heterogeneous computing platforms that use GPUs and CPUs in tandem for computation have become an important choice to build low-cost high-performance computing platforms. The computing ability of modern GPUs surpasses that of CPUs can offer for certain classes of applications. GPUs can deliver several Tera-Flops in peak performance. However, programmers must adopt a more complicated and more difficult new programming paradigm.

To alleviate the burden of programming for heterogeneous systems, Garg and Amaral developed a Python compiling framework that combines an ahead-of-time compiler called unPython with a just-in-time compiler called jit4GPU. This compilation framework generates code for systems with AMD GPUs. We extend the framework to retarget it to generate OpenCL code, an industry standard that is implemented for most GPUs. Therefore, by generating OpenCL code, this new compiler, called jit4OpenCL, enables the execution of the same program in a wider selection of heterogeneous platforms. To further improve the target-code performance on nVidia GPUs, we developed an array-access analysis tool that helps to exploit the data reusability by utilizing the shared (local) memory space hierarchy in OpenCL.

The thesis presents an experimental performance evaluation indicating that, in comparison with jit4GPU, jit4OpenCL has performance degradation because of the current performance of implementations of OpenCL, and also because of the extra time needed for the additional just-in-time compilation. However, the portable code generated by jit4OpenCL still have performance gains in some applications compared to highly optimized CPU code.

# Acknowledgements

First and foremost, I would like to show my deepest gratitude to my supervisor, Professor José Nelson Amaral. Without your constant guidance, inspiration, supervision, support in researching and thesis writing, this thesis would not have been completed. You not only taught me the knowledge and methodology but also encouraged me to be a person of persistence, industriousness and integrity. I would have lost myself without your generous help.

I am also grateful to Rahul Garg. Thanks to the unPython + jit4GPU framework you constructed, I did not need to start from scratch. Your brillant idea makes a solid foundation to our work, I am heartily thankful to you.

I would also like to thank Professor Duane Szafron from Computing Science and Professor Marek Reformat from Electrical Engineering for helping me examine my work. Your suggestions and advices are of great help to me.

I especially want to thank my mentor, Professor Yu Zhang in USTC, for your great help in both my technical and personal development. She opened my mind and told me to pursue whatever I love, and offered advice and suggestions whenever I need them. I treasure those time we worked and shared together.

Last but not least, I wish to thank my parents, for bearing me, raising me and sheltering me. Nothing can substitute the love and comfort they give me. I love you both. To you I dedicate this thesis.

# Contents

| 1        | Intr | roduction                                              | 1  |

|----------|------|--------------------------------------------------------|----|

|          | 1.1  | Contributions                                          | 2  |

|          | 1.2  | Thesis Organization                                    | 3  |

| <b>2</b> | Bac  | kground on CUDA and OpenCL                             | 4  |

|          |      | Programming for GPUs                                   | 4  |

|          |      | 2.1.1 GPU Characteristics                              | 4  |

|          | 2.2  | nVidia GPGPU Hardware                                  | 6  |

|          |      | 2.2.1 The Tesla Architecture                           | 6  |

|          |      | 2.2.2 Execution                                        | 7  |

|          | 2.3  | CUDA GPU Computing Framework                           | 7  |

|          | 2.4  | 1 0                                                    | 10 |

|          |      |                                                        | 11 |

|          |      | · v                                                    | 11 |

|          | 2.5  |                                                        | 12 |

|          |      |                                                        | 14 |

|          | 2.6  |                                                        | 17 |

| •        | ъ    |                                                        | 10 |

| 3        |      |                                                        | 18 |

|          | 3.1  | , 0 0                                                  | 18 |

|          |      |                                                        | 19 |

|          |      |                                                        | 19 |

|          | 0.0  | v ,                                                    | 20 |

|          | 3.2  |                                                        | 20 |

|          | 0.0  | v                                                      | 21 |

|          | 3.3  | 11 010                                                 | 22 |

|          | 3.4  | • •                                                    | 23 |

|          | 3.5  | Chapter Conclusion                                     | 25 |

| 4        | Res  | earch Problem Formulation                              | 26 |

|          | 4.1  | The Goal                                               | 26 |

|          | 4.2  | Problem Statement                                      | 27 |

|          | 4.3  |                                                        |    |

|          |      | 4.3.1 Identifying Array Access Elements                |    |

|          |      | 4.3.2 Program Transformation and RCSLMAD Decomposition |    |

|          |      | 4.3.3 Ordering                                         |    |

|          |      | 4.3.4 RCSLMAD Decomposing Example                      |    |

|          | 4.4  | Discussion on LMAD-based Analysis for GPGPU            |    |

| <b>5</b> | Ger | neration of OpenCL code from Python                           | 38 |

|----------|-----|---------------------------------------------------------------|----|

|          | 5.1 | Dealing with Overlapping LMADs                                | 38 |

|          | 5.2 | OpenCL Program Generation                                     | 39 |

|          |     | 5.2.1 Host Code Generation                                    | 40 |

|          |     | 5.2.2 Grid Configuration Generation                           | 41 |

|          |     | 5.2.3 Kernel Code Generation                                  | 41 |

|          |     | 5.2.4 Transforming Loops                                      | 42 |

|          |     | 5.2.5 Scenario Example of Kernel Transformation               | 45 |

|          | 5.3 | Chapter Conclusion                                            | 47 |

| 6        | Exp | perimental evaluation                                         | 49 |

|          | 6.1 | Methodology                                                   | 49 |

|          | 6.2 | Result Analysis                                               | 50 |

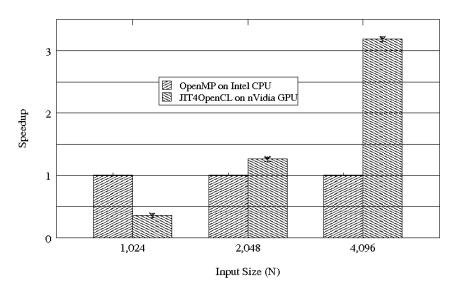

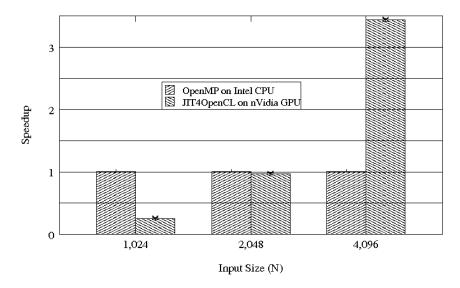

|          |     | 6.2.1 Results on nVidia Machine                               | 50 |

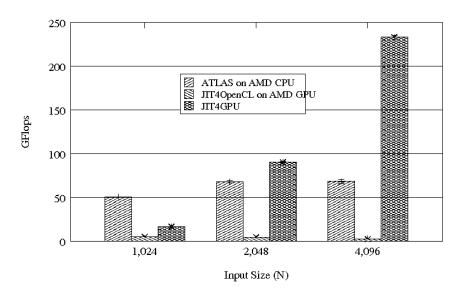

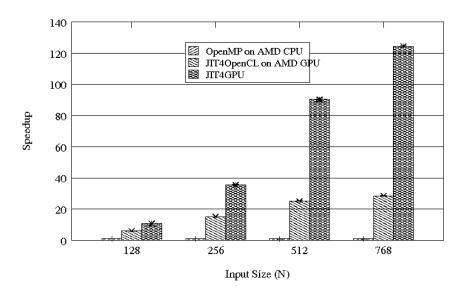

|          |     | 6.2.2 Jit4OpenCL Results Compared with Jit4GPU on AMD Machine | 54 |

|          |     | 6.2.3 Performance Analysis                                    | 57 |

|          | 6.3 | Concluding Remarks                                            | 68 |

| 7        | Rel | ated Work                                                     | 69 |

|          | 7.1 | Other Compilations of Scripting Languages                     | 69 |

|          |     | 7.1.1 Dynamic Scripting Language Embedders                    | 69 |

|          |     | 7.1.2 Dynamic Scripting Language Compilers                    | 69 |

|          | 7.2 | Loop Access Analysis                                          | 70 |

|          | 7.3 | Optimizing GPU Programs                                       | 71 |

|          | 7.4 | Compiling for Hybrid Systems                                  | 71 |

| 8        | Cor | nclusions                                                     | 74 |

|          | 8.1 | Future Work                                                   | 75 |

# List of Figures

| 2.1  | Graphic Rendering Pipeline                                                           |

|------|--------------------------------------------------------------------------------------|

| 2.2  | Tesla Architecture (from [16])                                                       |

| 2.3  | ${\tt CUDA\ Processing\ Flow, (extracted\ from\ http://en.wikipedia.org/wiki/CUDA,}$ |

|      | Mar 11th, 2010)                                                                      |

| 2.4  | The Organization of CUDA threads (from [34])                                         |

| 2.5  | OpenCL Platform Model (from [18])                                                    |

| 2.6  | Example OpenCL Program Flowchart                                                     |

| 2.7  | Tiled Memory Access Example                                                          |

| 3.1  | jit4GPU Workflow                                                                     |

| 4.1  | Example of legal RCSLMAD                                                             |

| 4.2  | Domain Decomposition Example                                                         |

| 4.3  | 3-Dimensional LMAD example                                                           |

| 4.4  | Decomposing LMAD into small Groups                                                   |

| 5.1  | Modified jit4GPU Analysis Flowchart                                                  |

| 5.2  | Stencil Program Thread Grid Example                                                  |

| 6.1  | Matrix Transpose Result (nVidia)                                                     |

| 6.2  | Stencil Result (nVidia)                                                              |

| 6.3  | Matrix Multiplication Result (nVidia)                                                |

| 6.4  | Coulomb Potential Energy Result (nVidia)                                             |

| 6.5  | N-Body Simulation Result (nVidia)                                                    |

| 6.6  | Blackscholes Filter Result (nVidia)                                                  |

| 6.7  | Mandelbrot Result (nVidia)                                                           |

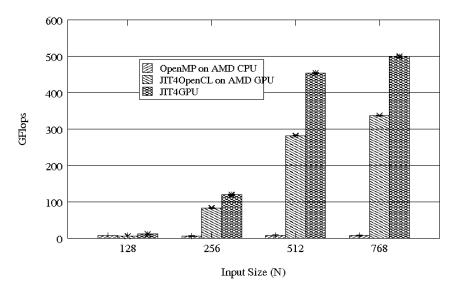

| 6.8  | Matrix-Multiplication Result on AMD                                                  |

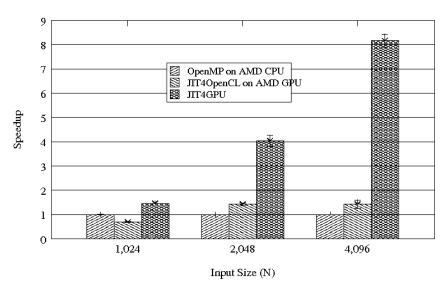

| 6.9  | CP Result on AMD                                                                     |

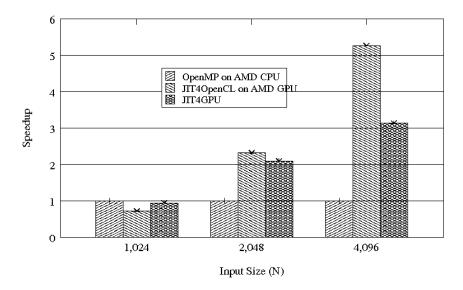

|      | N-Body Result on AMD                                                                 |

|      | Blackscholes Result on AMD                                                           |

|      | Mandelbrot Filter Result on AMD                                                      |

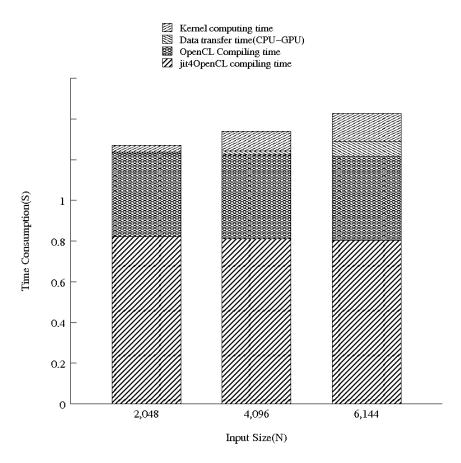

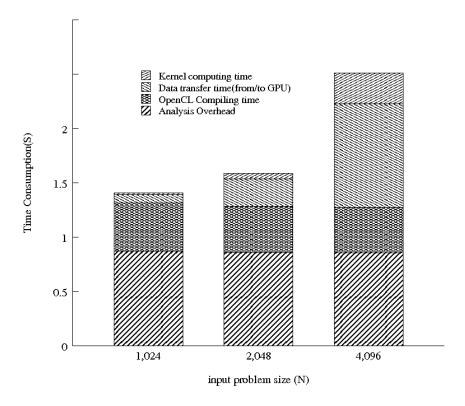

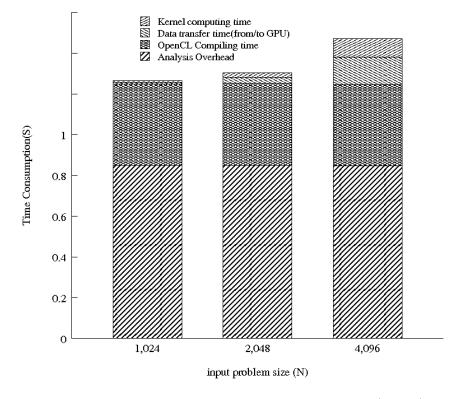

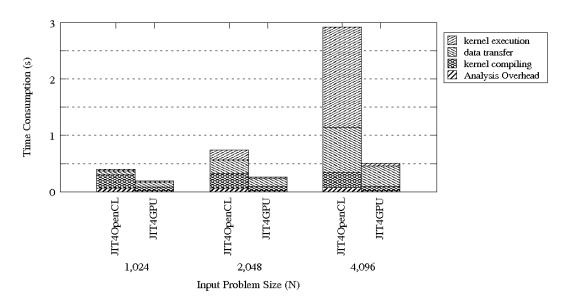

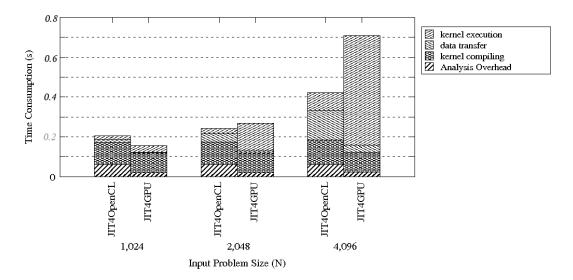

|      | Matrix multiplication Execution Time Decomposition (nVidia) 59                       |

|      | Matrix Transpose Execution Time Decomposition (nVidia) 60                            |

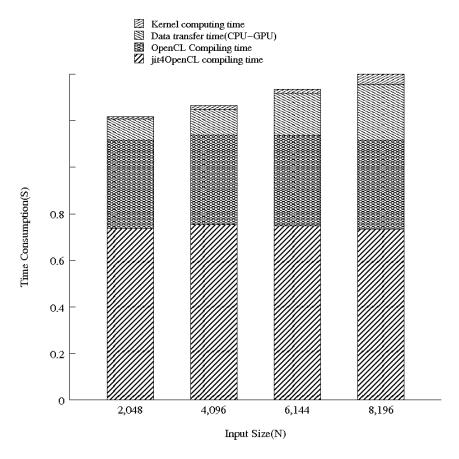

|      | Stencil Execution Time Decomposition (nVidia) 61                                     |

|      | CP Execution Time Decomposition (nVidia)                                             |

| 6.17 | N-Body Execution Time Decomposition (nVidia)                                         |

|      | Blackscholes Execution Time Decomposition (nVidia)                                   |

| 6.19 | Mandelbrot Execution Time Decomposition (nVidia)                                     |

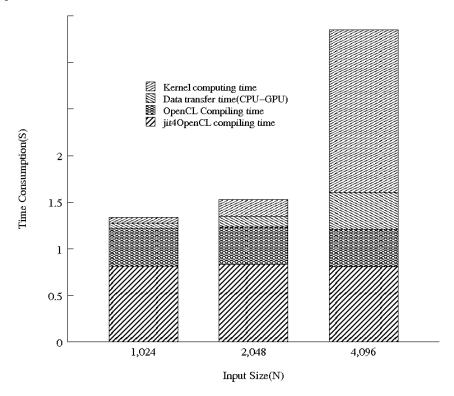

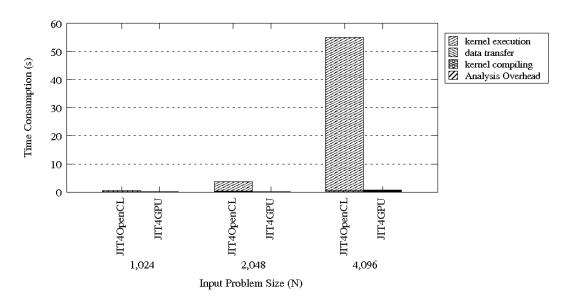

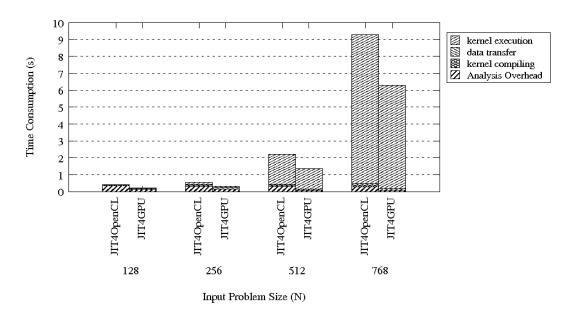

|      | Matrix-Multiplication Execution Time Decomposition (AMD) 64                          |

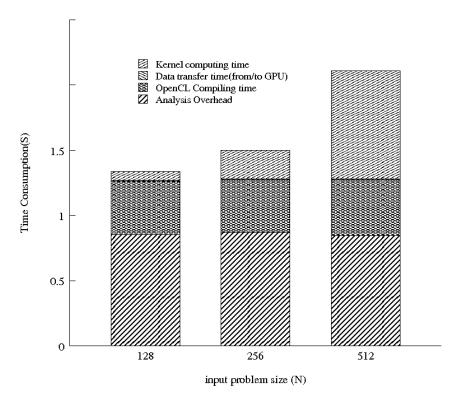

|      | CP Execution Time Decomposition (AMD)                                                |

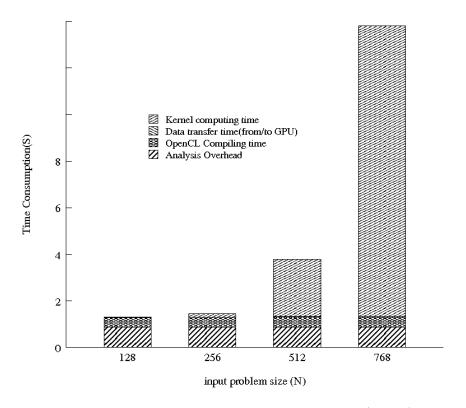

|      | N-Body Execution Time Decomposition (AMD)                                            |

|      | Blackscholes Execution Time Decomposition (AMD)                                      |

|      | Mandelbrot Execution Time Decomposition (AMD) 66                                     |

# List of acronyms and symbols

**API** Application Programming Interface

CAL Compute Abstract Layer language

CPU Central Processing Unit

CSLMAD Constant Stride Linear Memory Access Descriptor

**DRAM** Dynamic Random Access Memory

**CUDA** Compute Unified Device Architecture

GPGPU General Purpose Graphics Processing Unit

**GPU** Graphics Processing Unit

**JIT** Just-in-time

OpenCL Open Computing Language

RAM Random Access Memory

LMAD Linear Memory Access Descriptor

CSLMAD Constant-Stride Linear Memory Access Descriptor

RCSLMAD Restricted Constant-Stride Linear Memory Access Descriptor

SIMD Single Instruction Multiple Data

SM Stream Multiprocessor

SP Stream Processor

**SPMD** Single Program Multiple Data

STMD Single Thread Multiple Data

TPC Thread Processor Cluster

# Chapter 1

## Introduction

Scientific computing is a field that focuses on the execution of numerical computation to solve scientific and engineering mathematical problems. Ever since computers were used to model and simulate scientific problems, scientists and engineers were constantly demanding greater computing power.

Comutation on computers involves a software platform and a hardware platform.<sup>1</sup> On the software platform side, high-productivity scientific programming languages, such as FORTRAN and MATLAB, are designed to enable people to implement high-performance software with a reasonable amount of effort. The constant development of compiler optimization delivers higher performance by reducing the amount of time required to execute computer programs.

Thanks to abundant support and extensions, the Python language has become one of the major language choices for scientific computing. Python features a plethora of library support, simple syntax, a flexible programming model, lightweight execution, agile development, and cross-platform portability. Using Python as the programming language has some advantages over competing programming languages and platforms for scientific computing. With the help of an extension library called NumPy, Python can support flexible multi-dimensional array abstractions that are essential to scientific computing. Drawbacks of using Python for scientific computing include the interpretation overhead that limits the execution speed and the lack of support for parallel execution. To eliminate interpretation overhead for scientific computation, numerical libraries, such as NumPy, are written in the C programming language and are linked to interpreted Python programs.

On the hardware platform side, conventional hardware development, by increasing CPU clock rate in order to gain higher computing ability, is approaching the possible limit of clock rate, forcing micro-chip engineers and computing scientists to adopt multi-core designs to improve performance. As the number of cores constantly increases, a revolution of

<sup>&</sup>lt;sup>1</sup> "Computing on computers" sounds redundant today, but there was a time when a "computer" was a person, and the "computing" was done with pencil and paper. Such computing was not only for accounting but also for scientific purposes.

computing is emerging. Programmers need to adapt to this programming paradigm shift in order to exploit the potential of hardware.

An aggressive example of parallel execution occurred in graphic processing units (GPU). GPUs are designed to be processors dedicated to graphic processing. Its architecture is drastically different from conventional CPU. Recently GPUs have evolved from a fixed-function graphical processing hardware pipeline to a programmable general-purpose graphic processing unit (GPGPU), allowing programmers to implement software code that can make use of the computing ability of the GPU. However, the huge architecture difference demands that programmers adopt a stream processing paradigm, which greatly increases the difficulty of programming.

A computing platform consisting of CPUs and GPUs is a heterogeneous computing system. Thanks to the many cores in a GPU chip, GPU excels in numerical computing that is highly parallelizable. In modern heterogeneous computing, GPUs undertake the majority of the computation tasks. However, programming for heterogeneous computing systems requires fully understanding of the application and the programming paradigms involved. In the case of GPGPU the random data access of the CPU and the streaming data of the GPU need to be integrated. Stream processing can handle a subset of scientific applications efficiently, but programming an stream-oriented hardware efficiently is more difficult than programming a random-access hardware. This programming-paradigm shift is a major obstacle for beginning GPGPU programming.

Some researchers are working to eliminate the gap of shifting to a new programming paradigm when programming for GPGPUs [35][38][15]. They adapt mainstream programming models to GPGPU programming to reduce the efforts required and the complexity of programming for GPGPUs. An example is the unPython and jit4GPU compilation framework developed by Garg and Amaral [12]. UnPython compiles a subset of annotated Python program into C++ and OpenMP code. Jit4GPU interprets the program at runtime and handles program execution on AMD GPU. Although unPython and jit4GPU can deliver significant performance improvements, it comes with the cost of less portability, limiting its target platform to a system containing AMD GPUs. This thesis presents an extension to jit4GPU, named jit4OpenCL, that interprets the program into an industry-standard language for heterogeneous computing: OpenCL. This change will make jit4OpenCL executable on platforms that support OpenCL.

#### 1.1 Contributions

This thesis presents the following contributions:

• an extension to the existing RCSLMAD array access analysis usable in SIMD program

generation and optimization.

- a new just-in-time compiling framework for generating OpenCL for annotated Python program on the fly.

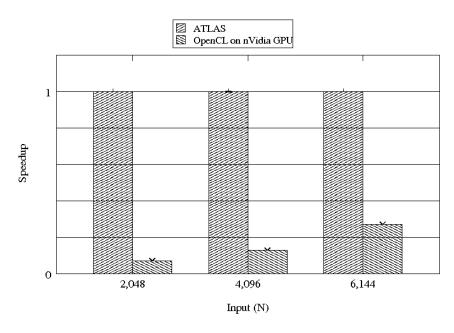

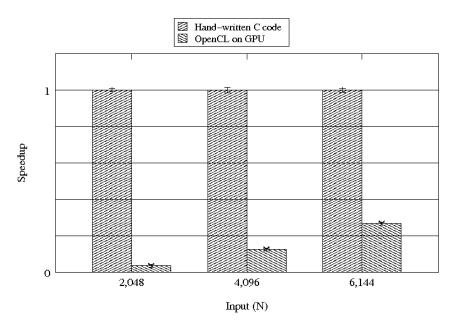

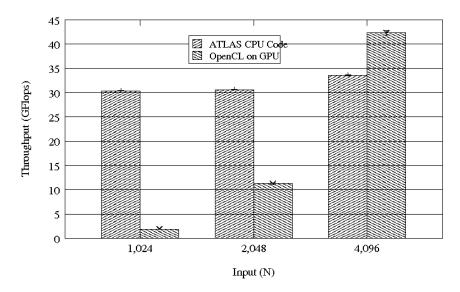

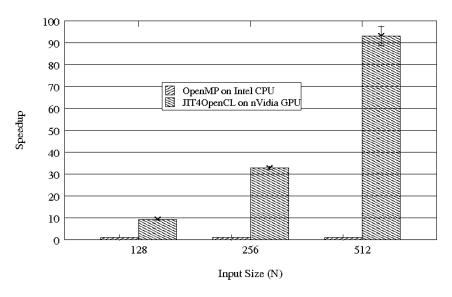

- an experimental evaluation showing that, with the GPU assistance, annotated Python programs can result in performance gain up to 91 times compared to hand-written CPU code in some applications.

#### 1.2 Thesis Organization

The first two of the following chapters serve as a review of background material. Chapter 2 briefly introduces GPGPU computing, including concepts, the nVidia Tesla architecture, CUDA programming model and OpenCL platform. Chapter 3 describes the Python language, NumPy scientific computing package and unPython compiling framework. Chapter 4 is a formal statement of the array access analysis problem and the solution. Chapter 5 states the methods and algorithms used by jit4OpenCL to generate OpenCL code. Chapter 6 evaluates and analyzes the experimental result. Chapter 7 briefly examines related work. Chapter 8 concludes this thesis.

# Chapter 2

# Background on CUDA and OpenCL

This chapter presents a brief introduction of computing on mainstream nVidia GPGPU (General Purposed GPU), including an anatomy of GPGPU hardware architecture, two GPGPU programming frameworks (CUDA and OpenCL), along with examples as supplementary materials for reader's reference. Throughout the chapter is the explanation of the difference of programming paradigms between the conventional CPU programs and the GPGPU programs for those readers that are familiar with CPU programming. Our compiling framework's backend targets the code generation on OpenCL; thus understanding the programming platform of GPGPUs is fundamental to our analysis.

#### 2.1 Programming for GPUs

#### 2.1.1 GPU Characteristics

GPU is the place for rendering process. Rendering is the computing process that generates digital image/video from an object model describing the objects shape, appearance, geometry, texture and lighting. Rendering may also be referred to as the process of generating digital graphic effects. It is a very common computing task in computer-aided simulation and design, video gaming, movie creation, and others.

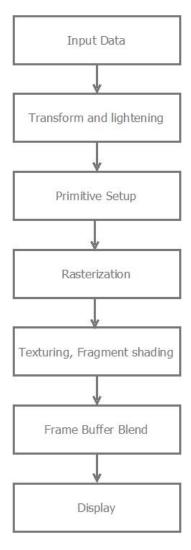

Commodity graphics hardware, such as nVidia and AMD GPUs, have a graphic pipeline to perform rasterization-based rendering. For a graphic pipeline hardware, the input of the rendering process to GPU is a set of vertices, indicating the shape and size of the object. Those vertices then must undergo linear transformation and per-vertex lighting in vertex-shader units to geometrically shape the polygon of the object and make the object lit according to the lighting atmosphere. The object is then clipped if necessary, then rasterized on Render Output Units into fragments. Those fragments may undergo texturing on Texture Mapping Units to add textures to the fragments. Finally, those fragments are

stored in a buffer frame for display. Figure 2.1 shows the process.

Figure 2.1: Graphic Rendering Pipeline

Because most of the computing described above is based on individual vertex, and each of the vertices shares a same processing pipeline, the pipeline can exploit the benefits of the **stream processing**<sup>1</sup> to accelerate the computing by parallelizing the operations. GPU designers are fully aware of this situation and commodity GPUs are designed to be a parallel stream processing computing environment that are Single Instruction Multiple Data (SIMD) capable.

<sup>&</sup>lt;sup>1</sup>stream processing is a restricted parallel programming paradigm that let a stream of data goes through a processing pipeline consists of a sequence of operatons. There are no dependencies between two different data element in the stream, which makes the stream processing fully parallizable.

#### 2.2 nVidia GPGPU Hardware

A General-Purpose GPU (GPGPU) is programmable to acclerate a wide range of applications besides graphic processing. NVidia's Tesla series GPU is the first GPU series from nVidia that supports general-purpose computing. Different from conventional CPUs, the Tesla GPU is a large-scale parallel processing unit with hundreds of computing cores that can perform computation at the same time.

#

#### 2.2.1 The Tesla Architecture

DRAM

DRAM

Figure 1. Tesla unified graphics and computing GPU architecture. TPC: texture/processor cluster; SM: streaming multiprocessor; SP: streaming processor; Tex: texture, ROP: raster operation processor.

DRAM

Figure 2.2: Tesla Architecture (from [16])

DRAM

DRAM

DRAM

Figure 2.2 shows a block diagram that describes the internal structure of a Tesla GPU. Basically, in a typical Tesla GPU there is an array of Thread Processor Clusters(TPC), which is shown in the middle of the figure. Within each TPC there are 2 or 3 Stream Multiprocessors (SM). About 8 to 12 Stream Processors (SP) are encapsulated in each SM, along with at least two Super Function Units (SFUs), Stream Processors and Super Function Units are small cores where computing actually happens. There is also an instruction fetch/dispatch scheduler in a Thread Processing Cluster that reads, decodes, and schedules instruction execution for each Stream Processor inside. There are also register file space

for storing registers, local memory space for storing spilled registers when the register file cannot hold all the registers. In order to serve as an intermediate software-managed cache hierarchy for fast memory access, there is an on-chip, small memory storage space ranging between 16KB to 32KB in each Stream Multiprocessor called shared-memory space. Finally, the GPU is connected with an Interconnection network to the off-chip large-capacity DRAM memory, which is used to load/store processing data.

#### 2.2.2 Execution

Tesla is designed to support parallel threading; its hundreds of Stream Processors enables a Tesla GPU to have more than ten thousand threads issued concurrently and thousands of threads running in parallel at a same time. To reduce the complexity of hardware for handling thousands of threads, a simplified scheduling schema is used: Instead of handling each thread individually, the scheduler handles one "warp" at a time, which consists of a group of threads. Scheduling by warps reduces the hardware scheduling overhead, thus reducing the complexity of the hardware design. A thread warp has the following characteristics:

- consists of 32 threads.

- threads in a warp share a single program counter, thus they progress together. For example, if a warp is chosen to be executed for the next cycle in an 8-core SM, then it will take 4 consecutive cycles to let all the threads proceed one instruction.

- there can be several warps executing concurrently on the same SM. When a warp is executed, the other warps will wait for their turn.

A thread running on GPUs can only access the memory space in off-chip DRAM on the same graphic card and the shared-memory space. Threads that are executing on the same SM share a limited-sized on-chip register file. Using too many registers may cause threads to spill the values from the register file to a local memory.

#### 2.3 CUDA GPU Computing Framework

#### Introduction to CUDA Architecture

As a stream processor, the architecture of the Tesla GPU is drastically different from the architecture of conventional computer. As a result, traditional programming models are not suitable for application implementation on Tesla GPUs. The Compute Unified Device Architecture (CUDA) was developed to help programmers implement software code on nVidia's Tesla GPUs.

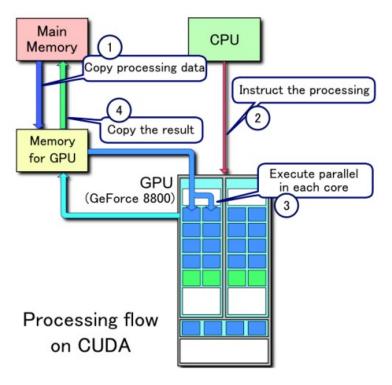

CUDA implements a Single-Instruction-Multiple-Thread (SIMT) programming model to fit with the parallel GPU architecture. SIMT is an abstraction of the Single-Instruction-Multiple-Data (SIMD) programming model. The difference is that, in SIMD the CPU can issue vector instructions, but in SIMT vectors of threads are issued rather than vectors of instructions. In general, SIMD is not scalable but SIMT is. When programming in an SIMD model, programmers need to specify the instruction width (the vector width), or the width is an characteristic of the hardware. In SIMT, programmers only describe the behaviours of the threads, CUDA will issue as many threads as the width of the vector, which can be decided at runtime. This dynamic-thread issuing technique makes a compiled program compatible with new hardware models released in the future, as long as the architecture remains the same. Figure 2.3 shows the processing flow of the CUDA platform.

Figure 2.3: CUDA Processing Flow, (extracted from http://en.wikipedia.org/wiki/CUDA, Mar 11th, 2010)

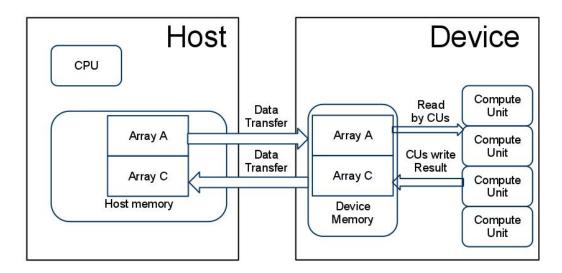

In Figure 2.3, the actual computing stage (steps 2 and 3) requires the overhead of copying processing data to GPU memory and copying the result back to main memory (CPU memory) (step 1 and step 4). However, often the time used on this extra work can be compensated by the fast processing speed of GPU core execution.

#### **CUDA Programming Model**

CUDA models a heterogeneous architecture that consists of a host and one or several devices. A host is a conventional CPU, and a device is a General Purpose GPU (GPGPU). The host and the devices have to collaborate in order to achieve successful CUDA program execution. Due to the hardware design, the CUDA programming model on Tesla architecture is only suitable for computing tasks that adopt the stream-processing programming paradigm.

Tasks that cannot be parallelized in stream processing are not suitable for execution on this platform.

A complete CUDA program consists of one or more phases. Each phase is implemented either in serial host code or parallel device code. Phases implemented in device code execute on one or several devices, while those in host code only execute on the host. It is a programmer's duty to specify whether a computing phase exhibits data parallelism. A data-parallel phase must be implemented in device code rather than host code. Such device code is called a "kernel function" or just "kernel".

The relationship between a CUDA host and a CUDA device is a master/slave relationship. Device code cannot be invoked outside of host code. Therefore, a CUDA program always starts serially from the host. Before invoking a kernel, the host prepares the execution on GPU by transferring processing data to the GPU memory, setting up execution parameters and then invoking the device code asynchronously. After the device code execution terminates, the host takes over the execution again until the next kernel is invoked. This processing flow is shown in Figure 2.3.

#### **CUDA Kernel Execution Organization**

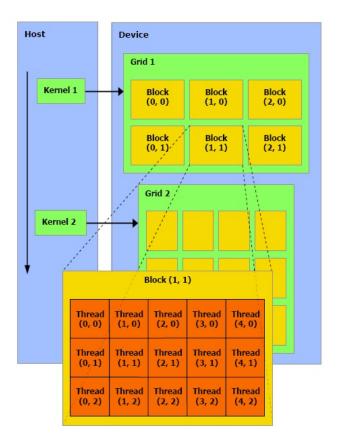

The launching of *device* code in CUDA requires the launching of many kernel threads. In a typical CUDA program, when the Step 1 in Figure 2.3 is finished, the host launches kernel threads for computing. These threads are organized into a 1, 2 or 3-dimensional array. The array is further divided into a grid (1, 2, or 3-dimensional), which is comprised of many thread blocks as shown in Figure 2.4.

CUDA's programming model is tailored to be capable of efficient execution on Tesla Architecture. The execution follows these rules:

- All the threads from a thread block are executed on a single Stream Multiprocessor (SM) in a Thread Processor Cluster (TPC).

- The GPU scheduler divides the task into a queue of thread blocks. An SM accepts one thread block at a time. Once all the threads in a thread block finish their execution, the scheduler immediately assigns a new thread block to the SM from the queue, until the queue is empty. The sequential execution of thread blocks in an SM guarantees that each thread block has exclusive access to shared-memory space while executing.

- The execution of threads follows the rules described in Section 2.2.2.

Threads in a thread block can communicate by:

- synchronizing execution to avoid hazardous memory accesses.

- accessing the on-chip low-latency shared memory space.

Figure 2.4: The Organization of CUDA threads (from [34])

• accessing the off-chip high-latency global memory space.

The only means of communication available for threads in different thread blocks is the off-chip global memory.

Threads and thread blocks have their own IDs. The index representing the position of a thread in the array is called *global ID*. The index representing the position in the thread block is called *local ID*. The index of a block in the grid is called *block ID*. Those IDs may be 1, 2 or 3-dimensional, depending on the thread grid configuration. Figure 2.4 shows an example where the launched kernel 1 has a 2-dimensional thread grid, which is divided into  $2 \times 3$  blocks. The figure also shows the inside of a block with block ID (1,1) (the indexes of the first dimension and of the second dimension are both 1), which consists of  $5 \times 3$  threads. Their local IDs are also 2-dimensional, indicating their position in the block.

### 2.4 OpenCL Framework

One significant drawback of the CUDA architecture is that it is developed exclusively for the nVidia Tesla architecture. Programs written in CUDA are not portable to any other heterogeneous computing architectures, such as platforms that have AMD GPUs. Due to the lack of portability, programmers have to implement several versions of each computing kernel if to implement a same program for different computing platforms.

In 2009, the industry announced a new open, cross-platform, royalty-free computing framework called OpenCL. OpenCL was proposed by Apple, and developed in collaboration with nVidia, AMD, Intel, and IBM, etc. Now OpenCL is under the management of the non-profit organization Khronos Group, and implementations on different platforms are emerging quickly since its specification 1.0 announcement in 2009.

Mac OSX 10.6 Snow Leopard comes with native support for OpenCL 1.0, which is the first operating system that supports OpenCL nVidia has released its OpenCL implementation to registered GPU programmers starting from mid-2009, and AMD published its OpenCL support for its CPUs later in 2009 and for its GPUs in early 2010. Thus, OpenCL is now available for tens of millions of personal computers.

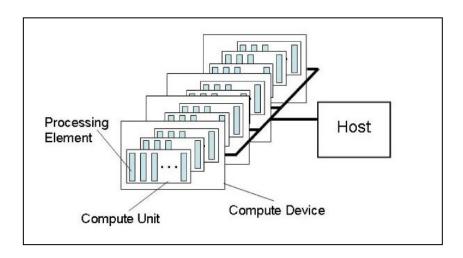

#### 2.4.1 OpenCL Portability

Generally speaking, the OpenCL Architecture is a framework for parallel programming, including a C99-like language, a set of OpenCL API, a set of libraries and a runtime support system. OpenCL represents programs at a higher level of abstraction when compared with a program written in CUDA.

As a general, standard framework designed for heterogeneous computing, OpenCL creates a general parallel computing framework used for CPU-GPU computing system, regardless of the 3D graphics API, such as OpenGL or DirectX. Still, OpenCL programs can execute on homogeneous computing systems containing only GPUs. OpenCL supports parallel computing natively. Programs implemented in OpenCL are extremely portable. OpenCL programs can be, without any modification, compiled to and executed on such hardware platforms as mobile devices, ordinary desktop computers or dedicated personal supercomputers, as long as the platform has OpenCL support.

#### 2.4.2 Similarities with CUDA

OpenCL and CUDA share the following features.

- They are both heterogeneous computing platforms. They both have a host, and the

host takes control of a set of devices.

- They are both parallel computing platforms adapting SIMT paradigm. In OpenCL, a program issues many thread instances for execution; these thread instances, called work-items, and work-items, are grouped into work-groups. These concepts correspond to threads and thread-groups in CUDA.

- In OpenCL, all work-items in a work-group have access to dedicated fast local-memory space. In CUDA, all threads in a thread group have access to dedicated shared memory.

- Both OpenCL and CUDA have an index space for identifying work-items/threads. Both index spaces are divided into a grid. Each element in the grid is a work-group (OpenCL) or a thread-group (CUDA).

- Their kernel instances have the same restrictions:

- Can only have access to GPU memory space (shared memory space and global memory space).

- Can only be declared to have a void return type.

- Cannot have recursive structure.

- Cannot have static variables.

- Cannot have variable number of arguments.

Figure 2.5: OpenCL Platform Model (from [18])

#### 2.5 OpenCL in Examples

This section uses a program example to show how to implement an OpenCL Program. Consider the computation of the matrix multiplication  $(C = A \times A)$ . For an element in C, say, (i, j), the following computation must be performed:

$$C(i,j) = \sum_{k=1}^{N} A(i,k) \times A(k,j)$$

The host code is straightforward. First the host program allocates two memory buffer on device — a memory buffer refers to a contiguous memory space in global memory. In this

Code 2.1: OpenCL Matrix Multiplication

```

__kernel void multiply(__global float *a, __global float *c,

1

int N){

2

int row = get_global_id(0);

col = get_global_id(1);

3

float sum = 0.0f;

4

(int i = 0; i < N; i++){}

5

sum += a[row*N + i]*a[i*N+col];

6

}

7

8

c[row*N + col] = sum;

}

```

example there will be one memory buffer for array A and another for array C. Then, the CPU executes instructions to copy array A from the host memory to device memory so that the computing units can have access to A. After the transfer, the CPU sends instructions to computing units to start the execution of a kernel function. The computing units calculate every element of array C and store the result into device memory. Once all the computing is done, the result stored in the device memory is transferred back to host memory, and the computing on the device terminates while the host can continue to execute. Figure 2.6 illustrates the decomposition of the whole process.

Clearly for any two different elements in C, C(a,b), C(c,d), there is no dependency between the two, thus the computation follows the stream processing paradigm. Therefore, we can create  $N \times N$  threads, each thread computes a single element in C. Assuming the array is row major, Code 2.1 shows the kernel function for computing C.

Figure 2.6: Example OpenCL Program Flowchart

In the kernel function shown in Code 2.1, lines 2 and 3 get the thread's first and second

dimension IDs, respectively. Lines 5-7 accumulate the sum. Line 8 stores the result to global memory. In line 6, a[row\*N + i] and a[col+i\*N] are array accesses. The subscript uses the local variables row and col to calculate the memory location offset. The performance of this OpenCL program is low because it frequently accesses the high-latency global memory (the memory space storing array A). The bandwidth usage to transfer from off-chip DRAM to the chip is  $2 \times N^3$ , which is the performance bottleneck for this program.

#### 2.5.1 An optimized Kernel

The implementation in the last example is not optimized because it takes up a great amount of bandwidth to transfer between DRAM and the GPU. The latency for each global-memory access is often as high as 300 to 500 GPU cycles. Moreover, the global-memory access of each column is strided, which causes banking conflicts because of restrictions in the hardware architecture, resulting in even longer access latency. In the Code 2.1, most of the kernel execution time is wasted waiting for the retrieval of data, rather than computing sums.

An analysis of the source code quickly reveals that Code 2.1 have redundant global-memory accesses. Although the size of the array stored in global memory is  $N^2$ , the kernel consumes  $2 \times N^3$  global-memory bandwidth. A better strategy is to utilize the on-chip shared memory space because accessing shared memory is much cheaper than accessing global memory. The replacement of global-memory accesses with shared-memory accesses can greatly reduce both bandwidth consumption and access latency. In OpenCL, shared-memory space is a limited-sized cache that is software-managed by threads. Therefore the optimized kernel must include code that issues loads and stores to the shared memory.

Different threads may need to read the same element in the array. For instance, threads with the same value of either row or col have to access the same strip of row or col of the array. The bandwidth demand can be reduced by moving array elements into shared memory by tiles, and then letting the program have tiled access to the array in the shared memory. The bigger the tile is, the less the bandwidth demand will be.

It is not possible to move all the processing data to shared memory at once because shared memory is a scarce resource. The traditional solution is to divide the data into small sections, and to reuse the shared memory space by moving one small section of data to it at a time. This strategy requires the programmer to *stripmine* the innermost loop-*i* in order to allow the program to perform tiled array accesses.

**Definition 1.** Loop stripmining is a compiler optimization that splits a single loop a into nested loops a' and a''. Assume that a' is the outer loop and a'' is the inner loop. The loop a' only iterates over a smaller section of the loop a, and the loop a' executes a'' multiple times to make a'''s iterations cover all the iterations of a.

Loop stripmining refers to the transformation of a single loop. In some cases when more

Code 2.2: OpenCL Matrix Multiplication

```

1

__kernel void multiply(__global float *a, __global float *c,

int N){

get_global_id(0);

2

3

get_global_id(1);

float sum = 0.0f;

4

(int tile_i = 0; tile_i < N; i+=tile_size){</pre>

5

for (int i = 0; i < tile_size; i++){</pre>

6

sum += a[row*N + (tile_i+i)]*a[col + (tile_i+i)*N];

7

8

9

}

10

c[row*N + col] = sum;

}

11

```

than one loop is involved, loop tiling is used to enable the program to have tiled array accesses.

**Definition 2.** Loop tiling is a compiler optimization that breaks a loop's iteration space into smaller blocks (each block is also called a "tile"), and let the loop iterate over tiles of data.

Loop stripmining and loop tiling are common compiler optimization techniques used to ensure that the block size fits in the cache line size, preventing cache-line spilling. In this example loop stripmining is used to divide the processing-data sections. Code 2.2 presents the kernel code with loop i stripmined.

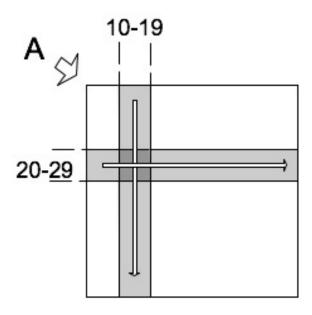

From the view of thread groups, once the loop i is stripmined in the kernel, the array access is tiled. Assume the tile size is 10, Figure 2.7 shows the array accesses of a  $10 \times 10$  rectangle thread group with row value ranging from 10 to 19 and col from 20 to 29. In the figure, grey areas are the memory sections that the threads in the thread group have to access in order to complete computing the sum. The access direction is also shown in the figure. Code 2.3 shows the kernel that have tiled access for shared memory utilization.

In Code 2.3, two shared (local) memory array spaces, a Tile1 and a Tile2, are declared as parameters for intermediate fast storage space. In the kernel body, threads interleave the computation with shared-memory loading operations. The outer loop tiled\_i holds the code that loads the global-memory tile to shared-memory space and the synchronization that maintains data consistency. The barrier statements immediately around the inner loop i (lines 17 and 21) ensure that all threads in a thread group finish computing their tile before the computation of the next set of tiles starts. These two barriers guarantees the inner loop has access to the desired elements in shared memory space. With the data loading and barriers together, most global memory accesses are eliminated.

A thread loads two elements — one for aTile1 and one for aTile2 — to shared memory in each tile, but accesses  $2 \times TILE\_SIZE$  elements in shared memory space, thus eliminating

Figure 2.7: Tiled Memory Access Example

Code 2.3: OpenCL Matrix Multiplication

```

//TILE_SIZE is a constant

__kernel void multiply(__global float *a, _global float *c,

3

__local float aTile1[TILE_SIZE*TILE_SIZE],

4

__local float aTile2[TILE_SIZE*TILE_SIZE]){

5

float sum = 0.0f;

6

int x = get_local_id(0);

7

int y = get_local_id(1);

8

9

int gidx = get_group_id(0);

int gidy = get_group_id(1);

10

11

int row = gidx*TILE_SIZE + x;

int col = gidy*TILE_SIZE + y;

12

13

for (int tiled_i = 0; tiled_i < N; tile_i+=TILE_SIZE){</pre>

14

15

aTile1[y*TILE_SIZE+x] = a[(gidy*TILE_SIZE*N+tiled_i)+y*N+x];

aTile2[y*TILE_SIZE+x] = a[(tiled_i*N+gidx*TILE_SIZE)+y*N+x];

16

barrier(LOCAL_MEM_FENCE);

17

for (int i = tiled_i; i < tiled_i +TILE_SIZE; i++){</pre>

18

sum += aTile1[y*TILE_SIZE+i] *aTile2[i*TILE_SIZE+x];

19

20

barrier(LOCAL_MEM_FENCE);

21

22

c[(gidy*TILE_SIZE+y)*N + gidx*TILE_SIZE+x] = sum;

23

^{24}

```

global memory accesses. Assume that both the tile size and the thread group size are also  $TILE\_SIZE \times TILE\_SIZE$  and the matrix size is  $N \times N$ . The total bandwidth consumption is only  $\frac{1}{TILE\_SIZE}$  of the non-optimized kernel, which results in around 10x speedup in performance.

Another difference between Code 2.2 and Code 2.3 is that Code 2.3 uses thread local ID together with group ID to compute the array offset. The results computed by these two method are the same.

#### 2.6 Conclusion Remarks

This chapter presents the idea of GPGPU heterogeneous computing, along with a short primer on GPGPU hardware and its programming model. GPU is a massive parallel computing equipment that has many cores on-chip with a restricted execution model. A GPU is most suitable for stream computing. For the sake of exploiting the GPU architecture, CUDA and OpenCL programming framework are designed to be the programming environment for GPGPUs. Common GPGPU applications show strong computing ability compared to CPU applications; however they require programmers a paradigm shift to stream programming. To alleviate the burden of such paradigm shift is a main goal of our compiling framework.

# Chapter 3

# Background on Python, NumPy, and unPython

Chapter 2 introduces the nVidia GPGPU hardware and programming framework that are used in our analysis and compiling framework. This chapter continues to supply the readers with background knowledge of the compiling framework's source language and front-end framework. Section 3.1 discusses relevant features of the Python language; Section 3.2 shows one of Python's extension, NumPy, on which our framework is based; Finally the compiling framework's frontend and backend, unPython and jit4GPU are explained in Section 3.3 and Section 3.4 respectively.

#### 3.1 The Python Language

Python is an object-oriented, full-fledged but flexible scripting language developed by a Dutch programmer Guido van Rossum in 1989. Ever since its creation, Python has always been a fast, light-weight, concise language with extreme flexibility, portability; it provides high productivity to the programmers. Because of these features it affords, after 20 years of development and establishment, Python is now widely used by millions of people in the fields of industry, scientific research and entertainment (game scripting).

There are several other benefits of using Python language:

- It's simple, with concise language syntax.

- It's easy to learn, easy to understand.

- It's free and open.

- It's high level.

- It supports multiple programming paradigms, including functional, imperative, objectoriented, reflective, etc.

- It's extensible and embeddable.

- It has strong library support.

#### 3.1.1 Features

The most significant feature of Python is that it is a dynamic, scripting language. As a scripting language, Python is written in plain text format and is interpreted by Python virtual machine at runtime. Using a virtual machine, Python enables itself to provide such features as dynamic memory management, name resolution (late-binding) and dynamic typing.

Python has its own dynamic typing system. Typing system are used in every programming language to ensure the correct interpretation and memory allocation of variables. Static typing system enforces a variable to have a type and it performs type checking at compile time as many static languages do, while dynamic typing system enforces a value to have a type rather than enforcing a variable to have a type, which leads to postponing the type-checking until runtime. A dynamic typing system provides a more flexible programming environment than a static one, but it also makes the runtime check sophisticated and interpreter design restricted by some additional constraints. Many scripting languages cannot perform static typing check ahead of time due to the language features they offer, so dynamic typing system is dominant among those languages.

#### 3.1.2 Performance Limitations

Although Python has brought so many exciting new features, the biggest limitation of this language is the performance. Because of its runtime interpretation and optimization, Python programs is often more than 10 times slower than C/C++ implementation that does the same job. This is a common problem in dynamic scripting languages, which hinders their expansions.

Although itself very suitable for GUI, text processing, controlling scripting, etc, pure Python programs are indeed not capable for computing-intensive core programs that requires high performance. However, developers of Python did not seek solutions to this by aggressively optimizing Python running speed overnight(which was, of course, impossible at the moment), but to provide internal APIs to Python programmers in order to allow them to have internal control over Python objects. By implementing custom Python objects in other languages like C by hand, programmers not only can have grasp on those functions Python does not ship with originally, but also achieve better performance because customized Python modules that are written using those APIs will be compiled statically and do not require runtime interpretation.

#### 3.1.3 Python/C API

One of the reason Python is popular is that it is extremely extensible. Python gives programmers the privileges of using other programming languages in working with Python modules for Python so that programmers can have implementations of extension modules in languages other than Python (extending Python), and use Python-written modules as components in a larger application implemented in other languages (embedding Python).

Python/C API is Python's gateway for C/C++ programmers for extending Python. It allows C/C++ programmers to create Python modules in C/C++. The reasons to utilize Python/C APIs may include:

- Calling functions in existing libraries written for C/C++.

- Optimizing cores for performance.

- Adding new built-in types for Python.

Python/C API enables Python developers to do what exceeds Python's capability, like creating distributed computing platforms not supported natively. For details please refer to official Python/C API documentation [1].

#### 3.2 Scientific Computing Tools for Python – NumPy

Many popular Python extensions are created using Python/C API; one of the important product essential to our work is the NumPy library module. NumPy is a Python extension module created specifically for granting Python the scientific computing ability [20]. NumPy comes as a bundle that includes:

- a powerful N-dimensional array object which is not supported natively by Python

- sophisticated (broadcasting) functions

- tools for integrating C/C++ and FORTRAN code

- useful linear algebra, Fourier transform, and random number capabilities.

- additional NumPy C APIs that allow programmers to write high performance C extensions.

In the following context we will focus on the array object, as it is connected to the "unPython+jit4GPU" framework.

#### 3.2.1 The Array Object

#### **Functions**

The core of NumPy is the flexible multi-dimensional array object implemented using Python/C API. a NumPy array object is an object that represents a multi-dimensional array in the memory, it comes with its member methods for setting or getting the objects attributes and values, like initialization, sub-matrix slicing, dimension change, etc.

Code 3.1: Example of NumPy array

```

from numpy import array

a = array([1,2,3,4,5,6])

print a

b = a.reshape(3,2)

print b

```

Code 3.1 and Code 3.2 together illustrates the programmer's view of NumPy. Code 3.1 shows an example of manipulating a NumPy array object, and Code 3.2 shows the output of the example in terminal. In Code 3.1, line 2 creates an array object from a list, which contains 6 elements. Line 1 in Code 3.2 shows the structure of the object pointed to by a, it is a 1-dimensional array with 6 elements. Line 4 in Code 3.1 assigns a "reshaped" view of the same object to variable b and , line 5 prints it. The printing result is shown in Code 3.2, which is a 2-dimensional array consists of the same values.

Code 3.2: Output of Code 3.1

```

1 >>>[1 2 3 4 5 6]

2 >>>[[1 2]

3 [3 4]

4 [5 6]]

```

#### Object Structure

An array object has a member variable pointer pointing to an allocated raw array buffer in the memory pool, and a list of strides that defines the the layout of the array. Given a variable a refers to an n dimensional object, a set of indices of each dimension (the i<sup>th</sup> dimension's index denoted as  $d_i$ ), the memory pointer ptr that points to the raw array buffer, and the list of strides s, then the memory location of  $\mathbf{a}[d_0,d_1,\ldots,d_{n-1}]$ , denoted as m, can be calculated as:

$$m = ptr + \sum_{i=0}^{n-1} s[i] \times d_i$$

Given the same ptr, same  $d_i$  where  $i=0,\ldots,n-1$ , but with different strides s, the shape of the array is different. The line 4 of Code 3.1 creates another array object from the object **a** points to. **b** and **a** share a same raw array buffer area but with different lists of

strides. Array shape manipulation operations are all based on the manipulation of strides. This is different from other array types in C or C++. In the view of a C programmer, the strides in multi-dimensional addressing is statically defined.

NumPy array object also provides public access to its raw data information for programmers to take full control or build extensions for NumPy [21]. This is essential to the analysis in unPython. In the following section we are going to take a look at unPython and its analysis.

#### 3.3 unPython – unwrapping python to C

unPython is a Python library compiling framework created by Rahul Garg [11], which unwraps Python programs into C programs. Newer version of unPython translates an annotated Python program into an OpenMP program and an AMD CAL program(which requires the runtime support from jit4GPU). The translated program can be executed on CPUs (using generated OpenMP code) or on AMD GPUs (using generated AMD CAL code), depending on the machine hardware availability. The choosing of execution hardware is one of the jobs of jit4GPU, which will be introduced later.

#### Language Model Extension

The language model of unPython is an extension to the conventional Python language model. In unPython, annotations that describe parameter type information, and new object types that serve as compiler directives for declaring parallel loops are introduced in the language model. The extension is designed in such a ways that it is still compliant with Python interpreter (adding a line starting with @ immediately before the definition of a function). To be specific, decorator type declares the parameter types in its own parameter list, an iteration over a gpurange is declared to be a parallel iteration. The extended Python program can be compiled successfully by a Python interpreter without altering the program. However, in the view of unPython compiler, the injected compiler directives (annotations and new types) provide additional information and instruction for generating parallel code. Code 3.3 shows a function that is written in unPython format.

Code 3.3: Example of unPython Program Extension

```

from unpython import gpurange

gtype('ndarray[int32_1]', 'ndarray[int32_1]', 'int32', 'int32')

def f(A,B,C,n):

sum = 0

for i in gpurange(N):

C[i] = A[i] + B[i]

sum += C[i]

return sum

```

The code states that the first three parameters from the left, A, B and C are 1 dimensional arrays with element data type int32; the last parameter is a variable of int32; the return type is also int32 (indicated by the last element in the annotation list). In the function there is a parallel iteration that calculates array C and sums up its elements.

#### Benefits and Constraints

Standard Python language does not ship with support for parallel programming. unPython introduces parallelism that works as an alternative way of developing Python programs. What is more, the extended programming model is fully compatible with standard Python interpreters. Programs written for unPython can execute as a standard Python program without modification, this would benefit programmers in debugging programs and porting to new software and hardware environments.

However, unPython is not omni-potent. Due to the dynamic typing system in Python, unPython requires additional parameter typing information declared in annotation to generate efficient target code. Also, at present unPython only compiles a subset of Python program features for efficient compiling. unPython cannot support features like runtime code execution, higher order functions, generators, meta-classes or special methods [11].

#### 3.4 jit4GPU – Just In Time Compiling for GPU

Jit4GPU is the just-in-time support component of Garg's unPython+jit4GPU Python compiling framework. The main job of jit4GPU is to dynamically translate the program into AMD CAL code, and to deal with data allocation, data transferring.

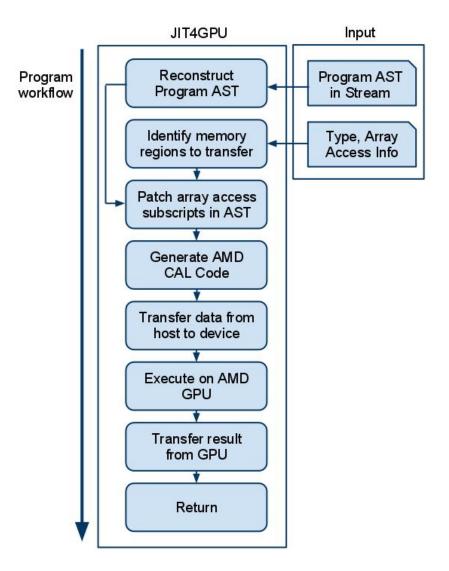

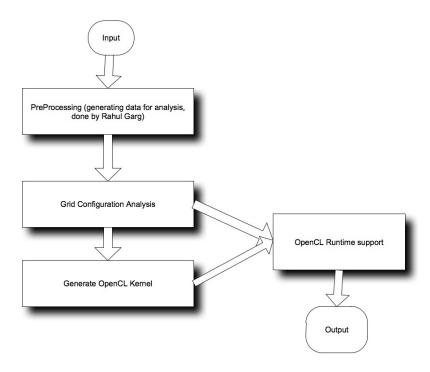

Figure 3.1 shows jit4GPU GPU execution workflow, what does not show in the figure is that whenever jit4GPU encounters an program pattern it cannot handle, it will exit immediately to fallback to CPU execution.

Jit4GPU accepts as parameters the program abstract syntax tree (AST) in stream format, variable type information and array access information. Jit4GPU first rebuild a new AST from the stream, then it does the following jobs:

#### Computing the Memory Region for Data Transfer

Jit4GPU computes the processing array element memory regions from array access information (the discussion of array access information is in Chapter 4). For each array access reference in the program, it calculates a rectangular memory region that covers all its memory locations that the reference points to. If two or more rectangular regions overlap, a bigger rectangular region is calculated to cover them all. The computing result is a set of disjoint rectangular memory regions, which will be transferred to device memory.

Figure 3.1: jit4GPU Workflow

Transferring data between host memory and device memory costs time due to the relatively small bandwidth between the two. Transferring rectangular regions rather than the whole bunch of memory locations helps to reduce the required bandwidth.

# Code Patch, GPU Code Generation, Device Memory Allocation and Data Transfer

The array access references in the program must be altered due to the change of memory place and layout. Before actually generating GPU code, jit4GPU patches all the array access references on the AST tree, re-directing array header pointers to new place, and changing array access subscripts.

Besides code generation, jit4GPU also handles device memory operations and data transfer. Jit4GPU does the following jobs:

- 1. generate AMD CAL code by traversing the patched AST tree

- 2. allocate device memory objects, initialize with size

- before GPU code execution, copy rectangular memory regions of processing arrays to device memory space

- 4. handle GPU execution

- 5. after GPU code execution, copy results from device memory space back to host memory space

After fetching results from device memory, jit4GPU exits and hands in the execution to its caller function.

#### 3.5 Chapter Conclusion

As a swift and flexible programming language, Python is a very popular widely used language. With the extension module NumPy, Python now supports various scientific operations and functions. NumPy also provides its own C APIs to allow programmers to build further customized extensions. These APIs provide a good opportunity for those who wants to expand Python's computing ability by directly taking control over NumPy objects.

To extend the Python language to allow execution on parallel machines such as heterogeneous computing platforms consisting of CPUs and GPUs, the unPython+jit4GPU framework translates annotated Python program with NumPy array objects as main data structure for computing into CPU and AMD GPU code. Our jit4OpenCL framework aims at replacing jit4GPU in the unPython+jit4GPU framework in order to expand its portability.

# Chapter 4

## Research Problem Formulation

One of the great difference between CPU and GPU programming is the control of their memory hierarchy. NVidia GPUs have a software-managed cache space called shared-memory space (discussed in Chapter 2) that is used to reduce data-movement requirements between off-chip DRAM space and the GPU itself. Automatically generating code, by a compiler, which can utilize the additional memory space is the key for performance optimization. This chapter introduces the array-access analysis based on RCSLMAD used in jit4OpenCL. This analysis allows jit4OpenCL to exploit the potential data reuse for array accesses. Specifically, Section 4.1 gives an overview of the goal of the analysis; Section 4.2 presents a problem statement that the analysis must solve; Section 4.3 formalizes the problem solution; Section 4.4 concludes this chapter.

#### 4.1 The Goal

The goal of this research is to let one of the existing array access analysis methods, Linear Memory Address Descriptors (LMADs), which is deployed in unPython and jit4GPU, be applied on jit4OpenCL compiler for successful OpenCL code analysis, optimization and code generation. This chapter describes the problem statement and the modifications to this analysis that were necessary for our own purposes.

Jit4OpenCL has to restructure loops, including loop strip mining, loop domain dividing, etc, in order to make the data fit into the limited memory resources in the GPUs. Therefore the analysis must be able to identify memory locations that are accessed within a parallel loop nest as well as the memory locations accessed by any single iteration of the loop. Most importantly, the analysis must be suitable for stream processing that can be used to generate SIMD-style programs.

#### 4.2 Problem Statement

Given a set of array access references S in a parallel loop nest P: use S to identify the tiled memory accesses in P', which is a transformation of P. The transformation may include parallelization, strip mining and tiling.

#### 4.3 Refined Array Access Analysis

This section first starts by introducing the LMAD-based analysis, and then discusses the adaptation of this analysis to jit4OpenCL.

#### 4.3.1 Identifying Array Access Elements

In array access analysis, a memory location (noted as l) indicates a position in the memory space. Let M be the set of memory locations referenced by an array access throughout the program's execution.

Given a loop nest of depth d, the memory references within the loop nest may be represented by a function f, whose input is a d-component vector  $\vec{i} = (i_1, i_2, i_3, ..., i_d)$ , where  $i_k$  is the  $k^{th}$  loop index in the loop nest. The set of legal loop indices  $\vec{i}$  forms the d-dimensional iteration domain D. D is represented in the following format:  $D = (l_1..u_1, l_2..u_2, ..., l_d..u_d)$ , where for any  $0 < k \le d$ ,  $l_k$  and  $u_k$  are the lower and upper bounds of loop k, respectively, and  $l_k \le u_k$ . For normalized loops, the lower bound of each loop counter is 0. We further constrain D by requiring the upper bound to be an affine function of the outer loop indices. Such constraint does limit the analysis on applications that has certain memory accessing patterns, but a large portion of scientific applications can be implemented with such constraints.

Let  $f: \vec{i} \to \mathbb{N}$  be the following affine function:

$$f(\vec{i}) = b + \sum_{k=1}^{d} s_k \times i_k | \vec{i} \in D$$

where  $s_k|k=1,2,...,d$  are the increment strides of each loop counter, b is the base of the array access descriptor. The function  $f(\vec{i})$  is an array descriptor called a Constraint-Stride LMAD (CSLMAD) [11]. Assume that the strides are sorted in decreasing order. Let  $s_{r_k}$  be the  $k^{th}$  stride in this sorted list,  $u_{r_k}$  be the upper bound, and  $r_k$  be the position in the sorted list of the loop with stride  $s_{r_k}$ . Let  $s_{r_m} = \min(s_{r_k})|s_{r_k} \neq 0$ .

A CSLMAD is a Restricted Constant-Stride LMAD (RCSLMAD) if and only if for every  $s_{r_k}$  we have:

$$s_{r_k} \ge s_{r_m} - 1 + \sum_{j=k+1}^m u_{r_j} \times s_{r_j}$$

This restriction guarantees that in a RCSLMAD the references with small strides do not overlap with references with larger strides.

A function  $f(\vec{i})$  and a loop-iteration domain D define a set of memory locations  $L_f(D) = \bigcup_{\vec{j} \in D} f(\vec{j})$ . The memory space between  $min(f(\vec{j}))$  and  $max(f(\vec{j}))$  for all  $\vec{j} \in D$  is the region defined by f on D, and is denoted as  $|D|_f$ . Not all locations within this region are necessarily referenced by the loop. The locations that are referenced are called the *effective memory locations* in this analysis. Figure 4.1 shows an example of a region. Grey blocks are effective memory locations while white blocks are not.

**Theorem 1.** Given  $\vec{i} \in D$  and  $\vec{j} \in D$ , such that  $f(\vec{i})$  and  $f(\vec{j})$  are RCSLMADs. If  $\vec{i} \neq \vec{j}$  then  $f(\vec{i}) \neq f(\vec{j})$ .

*Proof.* For the sake of contradiction, assume that there are two vectors  $\vec{i}$  and  $\vec{j}$  in an iteration domain D such that  $\vec{i} \neq \vec{j}$  and  $f(\vec{i}) = f(\vec{j})$ . Therefore:

$$f(\vec{i}) - f(\vec{j}) = 0$$

(4.1)

$$\sum_{k=1}^{d} i_k \times s_k - \sum_{k=1}^{d} j_k \times s_k = 0 \tag{4.2}$$

$$\sum_{k=1}^{d} (i_k - j_k) \times s_k = 0 \tag{4.3}$$

$$\sum_{k=1, i_k \neq j_k}^{d} (i_k - j_k) \times s_k = 0 \tag{4.4}$$

In an RCSLMAD, strides are sorted in decreasing order. Let p be the dimension for which  $s_p \geq s_k$  for all k such that  $i_k \neq j_k$ , and assume that  $i_p > j_p$ . Equation (4.4) can be rewritten as:

$$(i_p - j_p) \times s_p + \sum_{k>p, i_k \neq j_k}^d (i_k - j_k) \times s_k = 0$$

(4.5)

To prove that Equation (4.5) cannot be true, we refer to the definition of a RCSLMAD. In the definition, the strides satisfy the following condition:

$$s_p \ge s_d - 1 + \sum_{j>p}^d u_j \times s_j \tag{4.6}$$

Thus, replacing  $s_p$  in the left hand side of Equation (4.5) with (4.6) will yield:

$$(i_{p} - j_{p}) \times s_{p} + \sum_{k>p, i_{k} \neq j_{k}}^{d} (i_{k} - j_{k}) \times s_{k} \ge$$

$$(i_{p} - j_{p}) \times (s_{d} - 1 + \sum_{k>p}^{d} u_{k} \times s_{k}) + \sum_{k>p, i_{k} \neq j_{k}}^{d} (i_{k} - j_{k}) \times s_{k}$$

(4.7)

$i_p - j_p \ge 1$  because  $i_p \ne j_p$ , thus:

$$(i_{p} - j_{p}) \times (s_{d} - 1 + \sum_{k>p}^{d} u_{k} \times s_{k}) + \sum_{k>p, i_{k} \neq j_{k}}^{d} (i_{k} - j_{k}) \times s_{k}$$

$$\geq (s_{d} - 1 + \sum_{k>p}^{d} u_{k} \times s_{k}) + \sum_{k>p, i_{k} \neq j_{k}}^{d} (i_{k} - j_{k}) \times s_{k}$$

$$\geq (s_{d} - 1) + \sum_{k>p, i_{k} \neq j_{k}}^{d} (u_{k} + i_{k} - j_{k}) \times s_{k}$$

$$(4.8)$$

Now we will show that the sum in expression 4.8 must be strictly positive. For any values of  $i_k$  and  $j_k$ ,  $(i_k - j_k) \ge -|i_k - j_k|$ . Therefore:

$$\sum_{k>p, i_k \neq j_k}^{d} (u_k + i_k - j_k) \times s_k \ge \sum_{k>p, i_k \neq j_k}^{d} (u_k - |i_k - j_k|) \times s_k \tag{4.9}$$

For  $i_k$ ,  $j_k$  we have that :  $0 \le i_k < u_k$ ,  $0 \le j_k < u_k$ . The difference between two numbers that are strictly smaller than  $u_k$  must be less than or equal to  $(u_k - 1)$ , therefore:

$$|i_k - j_k| \le (u_k - 1)$$

$-|i_k - j_k| \ge (1 - u_k)$  (4.10)

Combining expressions 4.10 and 4.9 results in:

$$\sum_{k>p, i_{k}\neq j_{k}}^{d} (u_{k} + i_{k} - j_{k}) \times s_{k} \geq \sum_{k>p, i_{k}\neq j_{k}}^{d} (u_{k} + (1 - u_{k})) \times s_{k}$$

$$\sum_{k>p, i_{k}\neq j_{k}}^{d} (u_{k} + i_{k} - j_{k}) \times s_{k} \geq \sum_{k>p, i_{k}\neq j_{k}}^{d} s_{k}$$

$s_k$  is always positive, therefore we can conclude that:

$$\sum_{k>p, i_k \neq j_k}^{d} (u_k + i_k - j_k) \times s_k > 0$$

(4.11)

Using expression 4.11 we conclude that the left-hand side of equation 4.5 is strictly greater than 0. That is, under the assumption that  $i_p > j_p$ ,  $f(\vec{i}) - f(\vec{j})$  cannot be 0, which means that there cannot exist two different vectors  $\vec{i}$ ,  $\vec{j}$  in domain D such that  $f(\vec{i}) - f(\vec{j}) = 0$ .

Thus from the contradiction it is proven that  $f(\vec{i}), i \in D$  is a one to one mapping.  $\Box$

Corollary 1. Given  $D_1 \subseteq D$  and  $D_2 \subseteq D$  such that  $D_1 \cup D_2 = D$ ,  $D_1 \cap D_2 = \emptyset$  then  $L_f(D_1) \cup L_f(D_2) = L_f(D)$ ,  $L_f(D_1) \cap L_f(D_2) = \emptyset$ .

*Proof.*  $L_f(D_1) \cup L_f(D_2) = L_f(D)$  is a straightforward deduction from the fact that:

$$\left(\bigcup_{a\in D_1}\{f(a)\}\right)\bigcup\left(\bigcup_{b\in D_2}\{f(b)\}\right)=\bigcup_{c\in D_1\cup D_2}\{f(c)\}$$

To prove that  $L_f(D_1) \cap L_f(D_2) = \emptyset$ , we use the fact that  $\vec{i} \to f(\vec{i})$  is a one-to-one mapping from Theorem 1. If we have  $\forall \vec{t} \notin D$  then  $f(\vec{t}) \notin \bigcup_{\vec{p} \in D} f(\vec{p})$ . Let  $\vec{j} \in D_1$  and  $\vec{i} \in D_2$  where  $D_1 \cap D_2 = \emptyset$ . Then  $f(\vec{j}) \notin \bigcup_{\vec{p} \in D_2} f(\vec{p})$  and  $f(\vec{i}) \notin \bigcup_{\vec{p} \in D_1} f(\vec{p})$ . Therefore  $\bigcup_{j \in D_1} f(\vec{j}) \cap \bigcup_{i \in D_2} f(\vec{i}) = \emptyset$ , that is  $L_f(D_1) \cap L_f(D_2) = \emptyset$ .

There may be unnecessary elements (non-effective memory locations) interleaved with effective memory locations, creating "holes" in the memory region. It is a waste to leave these holes in shared memory because transferring data between different levels of device memory is expensive. Consider the example shown in Figure 4.1. The figure represents array access of the following RCSLMAD (assuming that the starting address is 0):

$f((i,j)) = 2 \times i + 12 \times j$

$$0 \leq i < 3 \text{ and } 0 \leq j < 3$$

Figure 4.1: Example of legal RCSLMAD

Although the region of the RCSLMAD covers a large area, there are only 9 effective memory locations. In some cases transferring the whole RCSLMAD region to the device shared memory would be extremely expensive because the effective memory locations only occupy a small portion of the region.

The solution to this is to compress the RCSLMAD to squeeze the holes out. If  $f(\vec{i}), \forall \vec{i} \in D$  is a RCSLMAD, where the  $j^{\text{th}}$  dimension's lower bound is 0, upper bound is  $u_j$ , then we can construct another RCSLMAD function  $g(\vec{i})$  such that its strides are  $s_{r_d} = 1, s_{r_k} = \sum_{j=k+1}^d u_{r_j} \times s_{r_j}$ , where  $r_l, l=1,2,...,d$  is the dimension index sorted in stride's decreasing order. This transformation of RCSLMADs eliminates the access holes from the region defined by g on D,  $|D|_g \leq |D|_f$  and  $|L_g(D)| = \prod_{i=1,u_i \neq 0}^d u_i$ . Most importantly, the memory

space occupied by the effective memory locations in  $f(\vec{i})$  is  $|D|_q$ .

**Theorem 2.** All memory locations in the region of D on g (that is, the memory space spreading from  $max(L_g(D))$  to  $min(L_g(D))$ ) are effective memory locations.

*Proof.* It is obvious that:

- 1.  $g(\vec{i}), \vec{i} \in D$  is a RCSLMAD;

- 2. there are  $|L_g(D)| = \prod_{i=1, u_i \neq 0}^d u_i$  effective elements in  $f(\vec{i})$ ,  $g(\vec{i})$ , and  $|D|_g$ , which means that every memory location in  $g(\vec{i})$  is an effective memory location.

For instance, consider the example shown in Figure 4.1. The constructed RCSLMAD function  $g(\vec{i})$  is:  $g((i,j)) = 1 \times i + u_1 \times j = i + 3j$ , and  $|D|_g = 9$ , resulting in no waste of shared memory.

In a compiler implementation, LMADs are transferred to shared memory and are compressed to reduce the usage of scarce shared memory using Theorem 2. In other words, given a RCSLMAD  $f(\vec{i})$  representing processing data elements in device global memory, our compiler creates a new RCSLMAD  $g(\vec{i})$  in device shared memory, and maps every legal  $f(\vec{i})$  to its destination  $g(\vec{i})$  before computing. After the computation  $f(\vec{i})$  is updated if  $g(\vec{i})$  has any change.

#### 4.3.2 Program Transformation and RCSLMAD Decomposition

In some real-world scientific computing applications the computer needs to crunch large amount of input data. Due to the size restriction of the on-chip shared-memory architecture used in present nVidia GPGPU, programmers cannot process big RCSLMADs on device shared memory for data reuse. To generate efficient code, the compiler must decompose the RCSLMAD into smaller RCSLMADs, so that:

- 1. each of the smaller RCSLMADs fits to shared memory size;

- 2. any of the stream processor in GPU can process one decomposed RCSLMAD at a time;

- 3. the collective result of the access to the decomposed RCSLMADs is exactly the same as accessing RCSLMADs that are not decomposed.

In this compiler implementation, the domain for RCSLMAD is manipulated for decomposing. Given a RCSLMAD  $f(\vec{i}), \vec{i} \in D$ , split the domain D into disjoint sub domains  $D_1$ ,  $D_2 \ldots D_n$  such that  $\forall i, j, D_i \cap D_j = \emptyset$ ,  $D_1 \cup D_2 \cup \ldots \cup D_3 = D$ , thus n smaller RCSLMADs are

formed. These RCSLMADs are:  $f(\vec{i}), \vec{i} \in D_1, f(\vec{j}), \vec{j} \in D_2, ..., f(\vec{k}), \vec{k} \in D_n$ . According to Corollary 1,  $\forall i, j$  we have  $L_f(D_i) \cap L_f(D_j) = \emptyset$ , and  $L_f(D_1) \cup L_f(D_2) \cup ... \cup L_f(D_n) = L_f(D)$ .

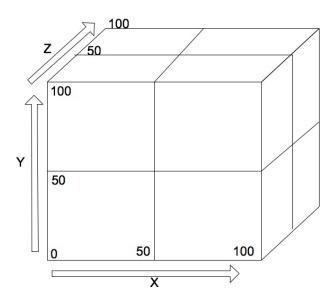

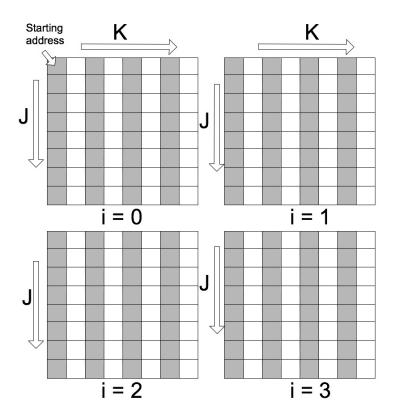

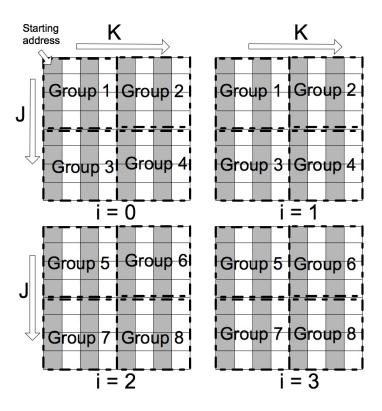

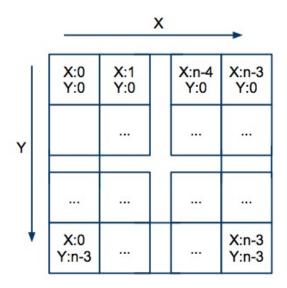

D is split in such a way that every dimension of D is divided into contiguous regions. This way D is decomposed from a large cube into many smaller cubes. Each small cube represents the region of a sub domain. In this thesis this process is called RCSLMAD decomposition. RCSLMAD decomposition requires transformations to the program source code: for a parallel loop nest that contains sequential loops with array accesses in the body, the compiler makes the array accesses tiled by strip-mining the sequential loops and dividing parallel loop domains. These transformations will split D into many sub-domains. By iterating over a tiled array access, the corresponding iteration sub-domain is traversed. Figure 4.2 is an example showing a 3-dimensional domain  $(100 \times 100 \times 100)$  decomposed into 8 smaller contiguous sub-domains, each sub-domain consists of  $\frac{1}{8}$  of the bigger domain's space (the size is  $50 \times 50 \times 50$ ). This is done by splitting each dimension in half.

Figure 4.2: Domain Decomposition Example

#### 4.3.3 Ordering

Sorting all the elements in a RCSLMAD enables the compiler to generate shared-memory transfer code through memory-address mapping. Threads have their own, unique IDs, the compiler must know which elements in a RCSLMAD should a thread load to shared memory. Creating an order among those memory locations pointed by a RCSLMAD will also create a correspondence relationship between threads and the elements of RCSLMADs.

#### Ordering Elements for Different Memory Layer Mapping

Elements in  $f(\vec{i}), \vec{i} \in D$  can be ordered because a RCSLMAD is a one-to-one mapping from vector value to scalar value. To calculate this order number, we have to reuse some concepts defined before: in previous context, we used the stride list sorted in decreasing order,  $S_{r_j}|j=1,2,\ldots,d$  to explain the idea of RCSLMAD, where the subscript  $r_j|j=1,2,\ldots,d$  is the the domain index of the  $j^{\text{th}}$  stride in this sorted list,  $u_{r_j}$  and  $l_{r_j}$  are the upper bound and lower bound corresponding to  $S_{r_j}$  respectively, and the  $r_m$ th stride represents the smallest non-zero stride in the list. The order number of element  $f(i_1, i_2, \ldots, i_d)$  in this thesis is defined as:

$$Order(\vec{i}) = \sum_{j=1}^{r_m - 1} \left( (i_{r_j} - l_{r_j}) \left[ \prod_{k=j+1}^{r_m} (u_{r_k} - l_{r_k}) \right] \right) + (i_{r_m} - l_{r_m})$$

(4.12)

Expression (4.12) constructs a unique order ID of an element using those non-zero strides. In our analysis each RCSLMAD is normalized, so  $l_{r_i} = 0, i = 1, 2, ..., d$ , (4.12) can be simplified to:

$$Order(\vec{i}) = \sum_{j=1}^{r_m - 1} \left( i_{r_j} \left[ \prod_{k=j+1}^{r_m} u_{r_k} \right] \right) + i_{r_m}$$

(4.13)

Conversely, given  $Order(\vec{i})$ , and D, we can calculate  $\vec{i}$ . Assume that we have the value of  $Order(\vec{i})$ , that the bounds of D are  $(l_1 \ldots u_1, l_2 \ldots u_2, \ldots, l_d \ldots u_d)$ , and that the strides are  $(s_1, s_2, \ldots, s_d)$ . Let  $s_{r_k}$  be the  $k^{th}$  largest stride, then  $\vec{i} = (i_1, i_2, \ldots, i_d)$  can be found as described below. The first non-zero index,  $i_{r_m}$  is given by:

$$i_{r_m} = \begin{cases} Order(\vec{i}) & \text{if } m = 1\\ Order(\vec{i}) & (\text{mod } u_{r_m} - l_{r_m}) & \text{if } m \neq 1 \end{cases}$$

$$(4.14)$$