### CANADIAN THESES ON MICROFICHE

I.S.B.N.

# THESES CANADIENNES SUR MICROFICHE

National Library of Canada Collections Development Branch

Canadian Theses on Microfiche Service

Ottawa, Canada K1A 0N4 Bibliothèque nationale du Canada Direction du développement des collections

Service des thèses canadiennes sur microfiche

### NOTICE

The quality of this microfiche is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree,

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us a poor photocopy.

Previously copyrighted materials (journal articles, published tests, etc.) are not filmed.

Reproduction in full or in part of this film is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30. Please read the authorization forms which accompany this thesis.

THIS DISSERTATION

HAS BEEN MICROFILMED

EXACTLY AS RECEIVED

### **AVIS**

La qualité de cette microfiche dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de mauvaise qualité.

Les documents qui font déjà l'objet d'un droit d'auteur (articles de revue, examens publiés, etc.) ne sont pas microfilmés.

La reproduction, même partielle, de ce microfilm est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30. Veuillez prendre connaissance des formules d'autorisation qui accompagnent cette thèse.

LA THÈSE A ÉTÉ MICROFILMÉE TELLE QUE NOUS L'AVONS REÇUE

53

National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Division

Division des thèses canadiennes

Ottawa, Canada K1A 0N4

60.281

# PERMISSION TO MICROFILM — AUTORISATION DE MICROFILMER

Please print or type — Écrire en lettres moulées ou dactylographier

Full Name of Author - Nom complet de l'auteur

FRASTÓ MUGANYIZI KASHORO

Date of Birth — Date de naissance

Country of Birth — Lieu de naissance

August 8,1945

TANZANIA

Permanent Address — Résidence fixe

PHYSICS DEPARTMENT UNIVERSITY BOX 35063, DAR ES SALAAM, TANZANIA

Title of Thesis - Titre de là thèse

A HIGH FREQUENCY CURRENT-CONTROLLED

OSCILLATOR FOR INTEGRATED CIRCUITS

University - Universite

UNIVERSITY OF ALBERTA

Degree for which thesis was presented — Grade pour lequel cette thèse fut présentée

Ph. D.

Year this degree conferred — Année d'obtention de ce grade

FALL 1982

Name of Supervisor - Nom du directeur de thèse

PROF. K.A. STROMSMOE

Permission is hereby granted to the NATIONAL LIBRARY OF CANADA to microfilm this thesis and to fend or sell copies of the film.

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.

L'autorisation est, par la présente, accordée à la BIBLIOTHÈ-QUE NATIONALE DU CANADA de microfilmer cette thèse et de prêter ou de vendre des exemplaires du film.

L'auteur se réserve les autres droits de publication; ni la thèse ni de longs extraits de celle-ci ne doivent être imprimés ou autrement reproduits sans l'autorisation écrite de l'auteur.

Date

August 3, 1982

Signature

Indiashoro

# THE UNIVERSITY OF ALBERTA

A HIGH FREQUENCY CURRENT-CONTROLLED OSCILLATOR

FOR INTEGRATED CIRCUITS

bv

(C)

ERASTO M. KASHORO

A THESIS ...

SUBMITTED TO THE FACULTY OF GRADUATE STUDIES AND RESEARCH

IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE

OF DOCTOR OF PHILOSOPHY

DEPARTMENT OF ELECTRICAL ENGINEERING

EDMONTON, ALBERTA

FALL, 1982

THE UNIVERSITY OF ALBERTA

RELEASE FORM

NAME OF AUTHOR: Erasto M. Kashoro

TITLE OF THESIS: A HIGH FREQUENCY CURRENT-CONTROLLED OSCILLATOR

FOR INTEGRATED CIRCUITS

DEGREE FOR WHICH THESIS WAS PRESENTED: Doctor of Philosophy

YEAR THIS DEGREE GRANTED: Fall 1982

Permission is hereby granted to THE UNIVERSITY OF ALBERTA LIBRARY to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly or scientific research purposes only.

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.

(Signed) ....

PERMANENT ADDRESS:

Dept. of Electrical Engineering

University of Alberta

Edmonton, Alberta, T6G 2G7

July 7,

DATED ......1982

# THE UNIVERSITY OF ALBERTA

# FACULTY OF GRADUATE STUDIES AND RESEARCH

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies and Research, for acceptance, a thesis entitled A HIGH FREQUENCY CURRENT-CONTROLLED OSCILLATOR FOR INTEGRATED CIRCUITS submitted by ERASTO M. KASHORO in partial fulfilment of the requirements for the degree of DOCTOR OF PHILOSOPHY..

Delaworsly Undang

Date: July 7, 1982

### DEDICATION

To my parents for enabling me to pursue an advanced education.

### ABSTRACT

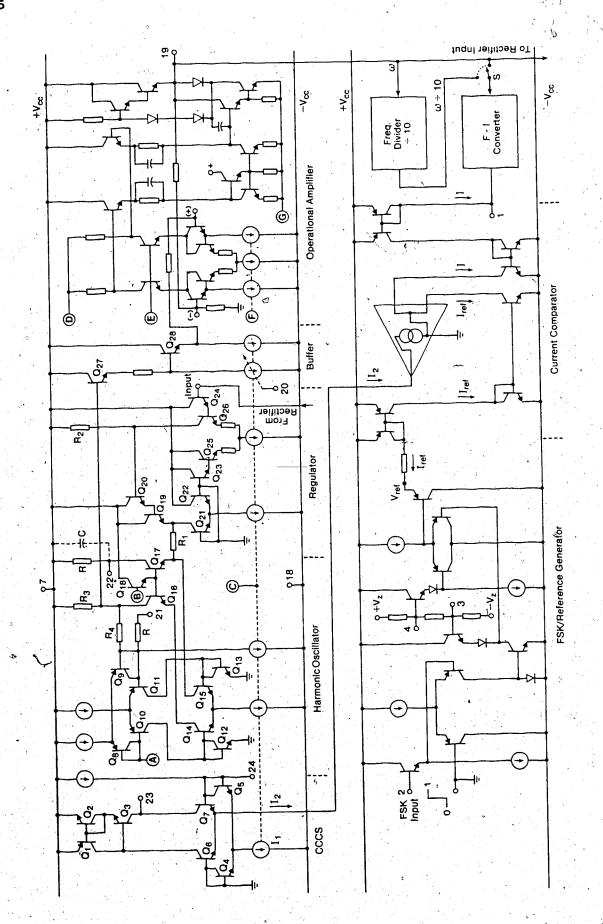

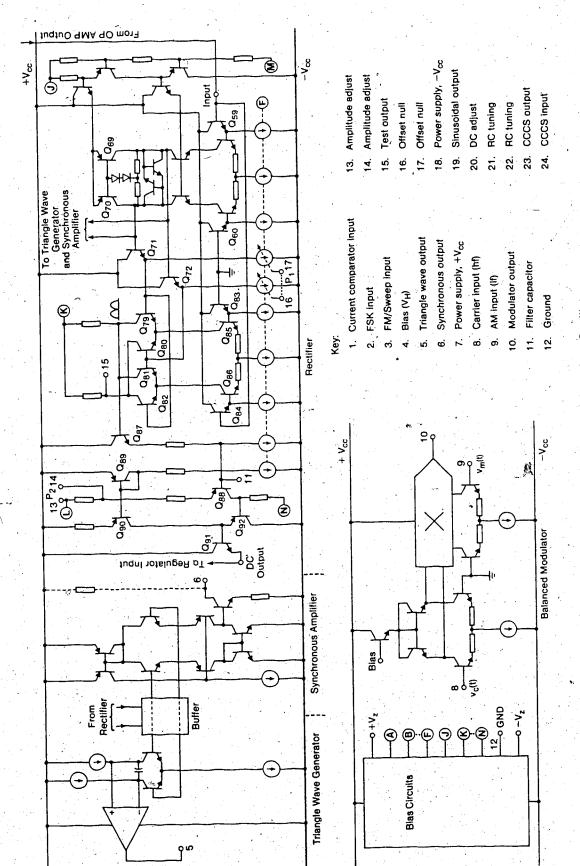

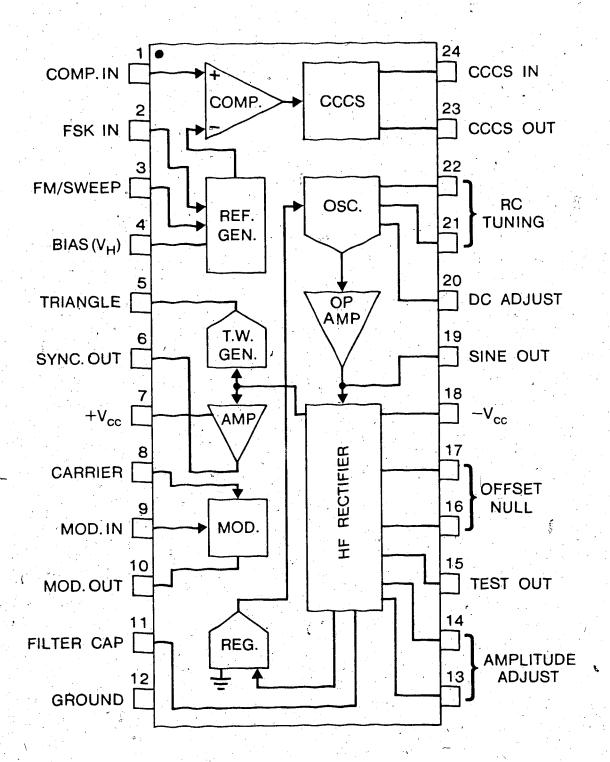

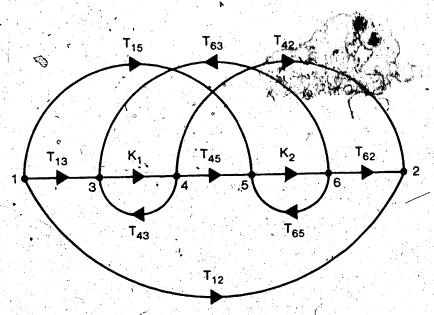

A sinusoidal RC-oscillator built around a current-controlled current amplifier is presented. Three main poblems associated with RC-oscillators, namely poor frequency, before amplitude drift and a large temperature coefficient of frequency, are addressed, and ways of solving these problems are discussed. The large temperature sensitivities typical of active RC networks were reduced by eliminating the active portion of the drift. This was accomplished through the use of thermally balanced amplifiers whose operation is independent of transistor parameters. It is shown that the frequency performance of a typical Wien-oscillator is significantly improved when fast current amplifiers are used to replace commercial voltage operational amplifiers. The generation of a sinusoidal signal directly from the oscillator gave a lower total harmonic distortion (THD) than in the more popular approaches using multivibrators and shaping networks.

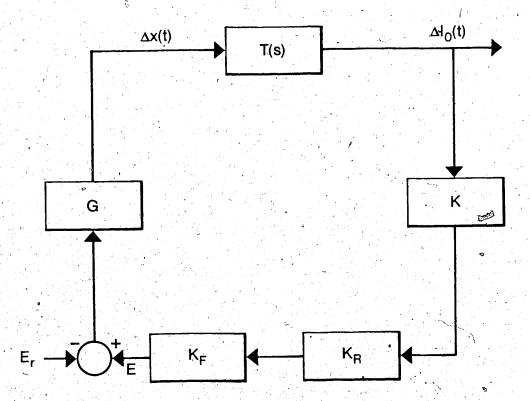

A new method for stabilizing the amplitude of oscillation has been developed. It employs a high frequency rectifier and a comparator in a feedback loop which is connected to the RC network of the oscillator through an active current divider. The feedback loop regulates the current in the RC network and thereby stabilizes the amplitude. A linear automatic gain control (AGC) model was developed and the stability requirements for the amplitude control loop were studied.

Frequency stabilization for oscillators is a very difficult task.

Most communication systems requiring tight frequency stability incorporate frequency synthesizers which have a large IC count and are expensive.

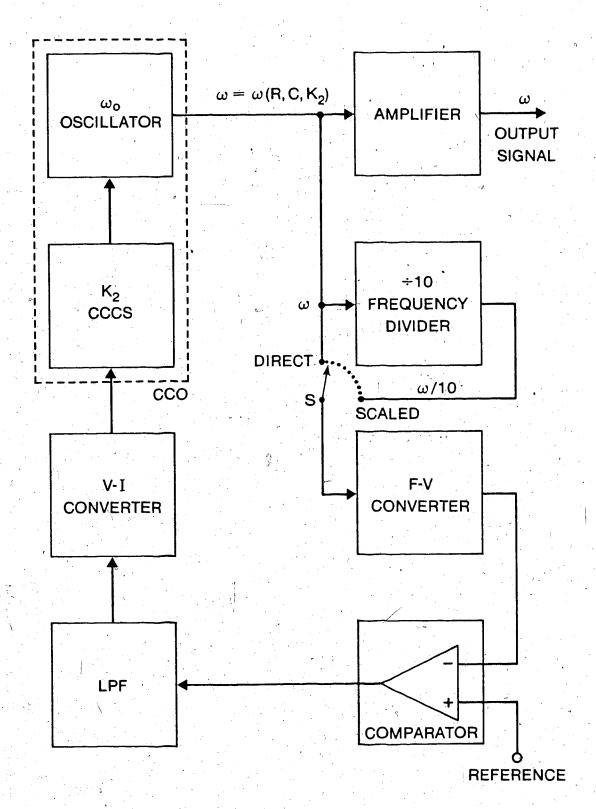

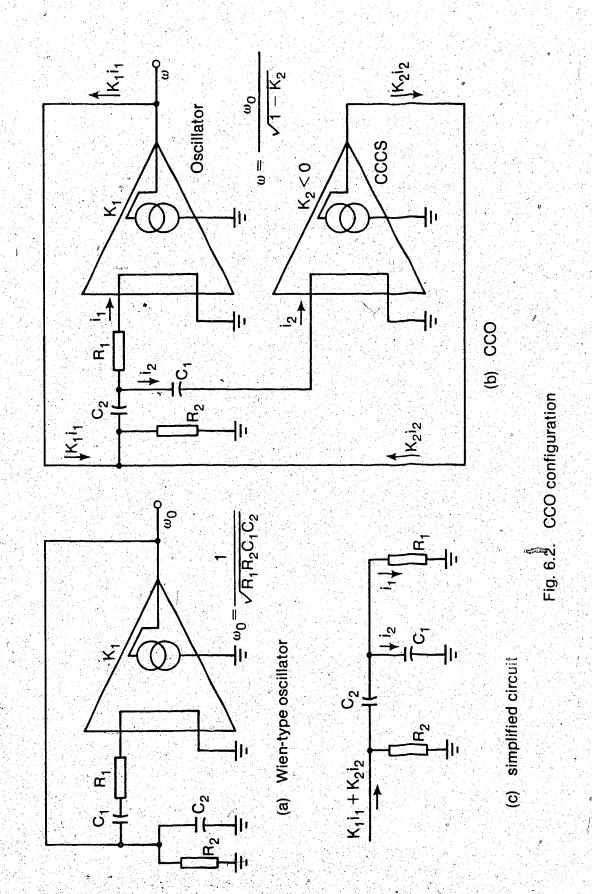

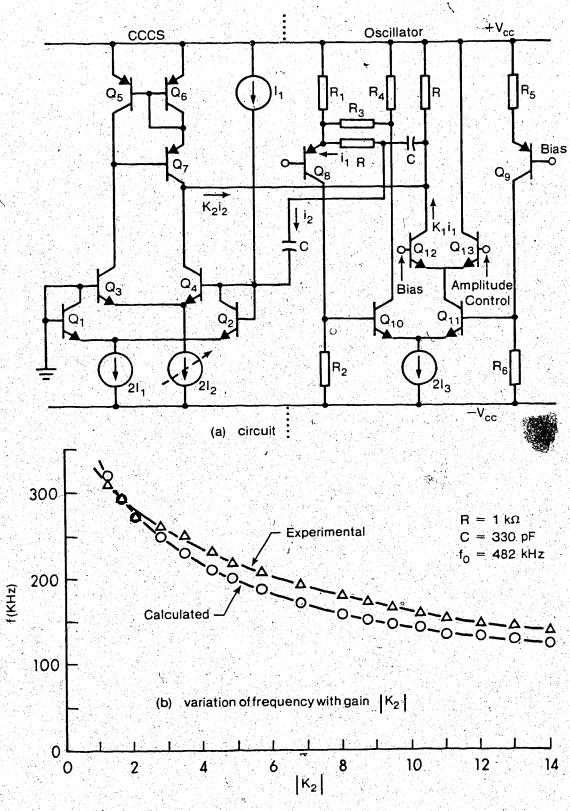

In this presentation a low-cost frequency stabilization scheme is described. A variable gain current-controlled current source (CCCS) was combined with a modified Wien-bridge oscillator to realize a current controlled oscillator (CCO). The frequency was stabilized by a feedback loop in which a frequency to current converter and a current comparator are the main control elements. The feedback controlled CCO has a linear tuning characteristic. It also incorporates AM and FSK capabilities. The results show that it is possible to realize the thermal drift of frequency for a general purpose RC-oscillator by more than an order of magnitude with a circuit which is completely realizable as a small scale IC.

### ACKNOWLEDGEMENTS

The author would like to thank Dr. Keith A. Stromsmoe who supervised this project. His encouragement and help have contributed greatly to the achievements of this work. The financial assistance for the purchase of electronic components and the preparation of technical diagrams is mostly appreciated.

Thanks also go to Dr. Igor M. Filanovsky for initiating this project. Without his advice, support and encouragement, especially during some critical times when his help was most needed, this work could not have been accomplished. His motivation was a very important factor in the success of this project.

The financial support of the Canadian Government through the Canadian Commonwealth Scholarship and Fellowship Administration is greatly appreciated.

The author also thanks the Government of Tanzania and the University of Dar es Salaam for allowing him to study at the University of Alberta.

The financial assistance by the Department of Electrical Engineering,

University of Alberta, in the form of a Graduate Teaching Assistantship

is gratefully acknowledged.

Appreciation is also extended to the staff of the University's Technical Services and Printing Services for their expertise and help in the production of this thesis.

The author wishes to express his thanks to Barbara J. Peck for her excellent typing of this thesis.

# TABLE OF CONTENTS

| ٠,        | <sub>,</sub> Chapter |                                                                                                                                                      | rage       |

|-----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| البع<br>ا | ī                    | INTRODUCTION                                                                                                                                         | 1          |

|           |                      | 1.1 Background to the Problem                                                                                                                        | 1          |

|           |                      | 1.2 Goals of the Project                                                                                                                             | . <b>3</b> |

|           |                      | 1.3 Main Features                                                                                                                                    | 4          |

|           |                      | 1.4 Presentation of the Material                                                                                                                     | 6          |

|           |                      |                                                                                                                                                      |            |

|           | 11                   | BASIC THEORY                                                                                                                                         | 8          |

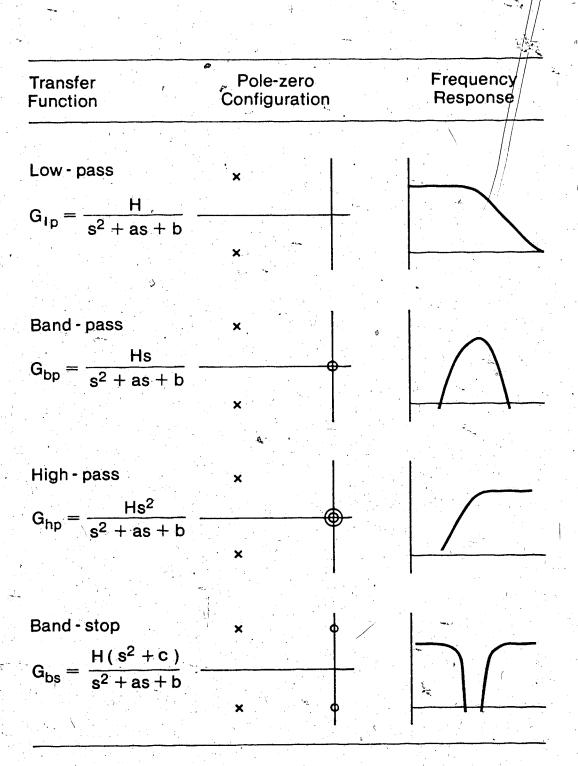

|           |                      | 2.1 Classification                                                                                                                                   | 8          |

|           | <b>.</b>             | 2.2 Choice of Convenient Circuit                                                                                                                     | 12         |

|           |                      | 2.3 The Oscillation Condition                                                                                                                        | 13         |

|           |                      | 2.4 Limitations on Oscillation Frequency                                                                                                             | 15         |

|           | N.                   | 2.5 Variable Frequency Oscillators                                                                                                                   | <b>Q</b> 3 |

|           |                      |                                                                                                                                                      |            |

|           | III                  | PRACTICAL CONSIDERATIONS                                                                                                                             | 27         |

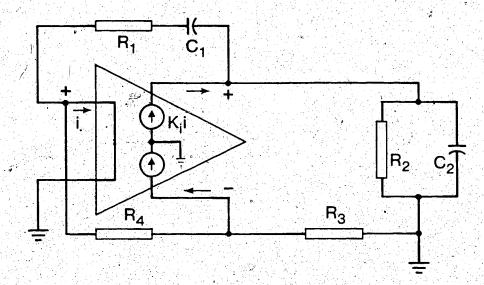

| •         |                      | 3.1 Experimental Circuit                                                                                                                             | 27         |

| <u> </u>  |                      | 3.2 Measurements                                                                                                                                     | 33         |

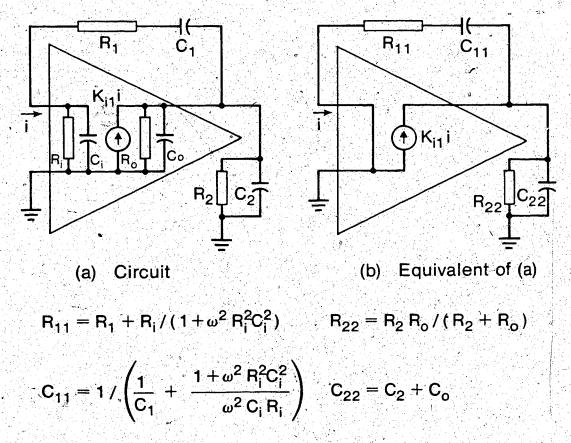

|           |                      | 3.3 Improved Circuit and hf Behaviour                                                                                                                | 33         |

|           |                      |                                                                                                                                                      |            |

|           | IV                   | DESIGN OF BASIC CIRCUIT BLOCKS                                                                                                                       | 45         |

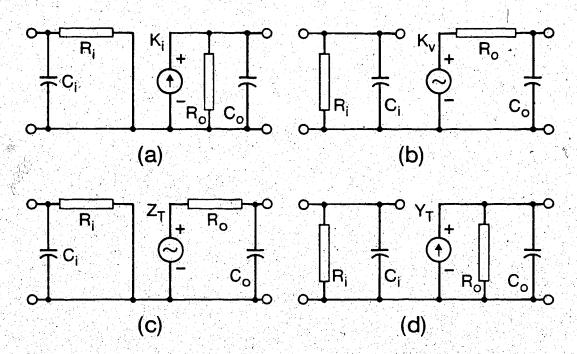

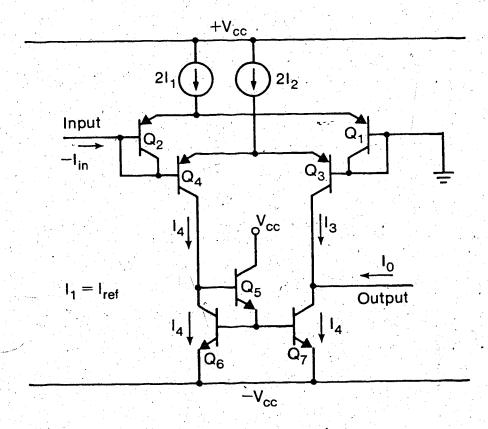

|           |                      | 4.1   Current Amplifier                                                                                                                              | 45         |

| 1. A      |                      | 4.2 Oscillating Network                                                                                                                              | 54         |

|           |                      | 4.3 High-speed Operational Amplifier                                                                                                                 | 57         |

|           |                      | 4.3.1 Introduction                                                                                                                                   | 57         |

|           |                      | 4.3.2 Input Stage                                                                                                                                    | 59         |

|           |                      | is a constant of $\chi$ . The constant $\chi$ , the constant $\chi$ , $\chi$ |            |

| Chapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | • •   |                                         | Page |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------|------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A - 2 | 4.3.3 Level-shifting Stage              | 61   |

| 1/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       | 4.3.4 Output Stage                      | 69   |

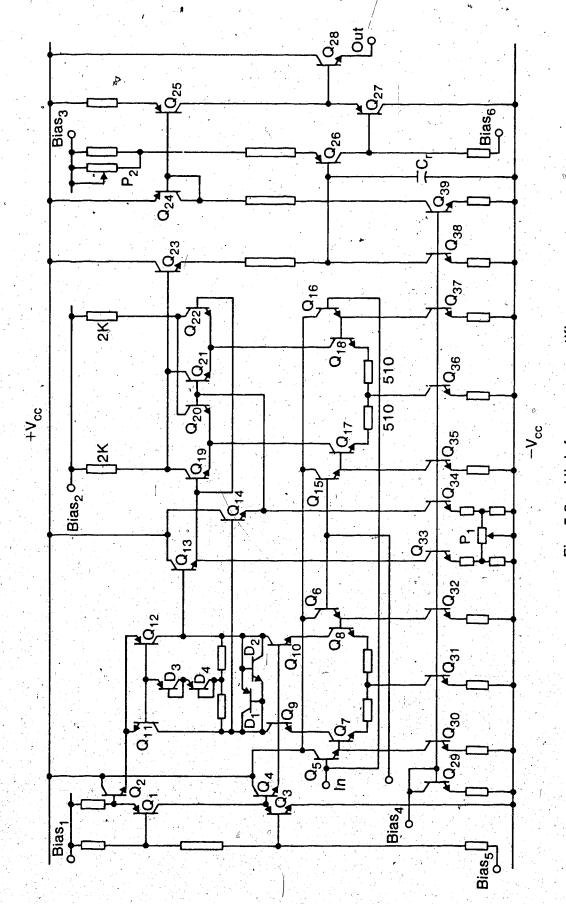

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | 4.3.5 Complete Amplifier Circuit        | 70   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |                                         | , "  |

| V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | AUTOM | ATIC GAIN CONTROL                       | 78   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.1   | Amplitude Regulation                    | 79   |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       | 5.1.1 Experimental Circuit              | 79   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | · ·   | 5.1.2 Interpretation of Results         | 81   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | 5.1.3 Amplitude Control Principle       | 87   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ·     | 5.1.4 Improved Amplitude Regulation     | 90   |

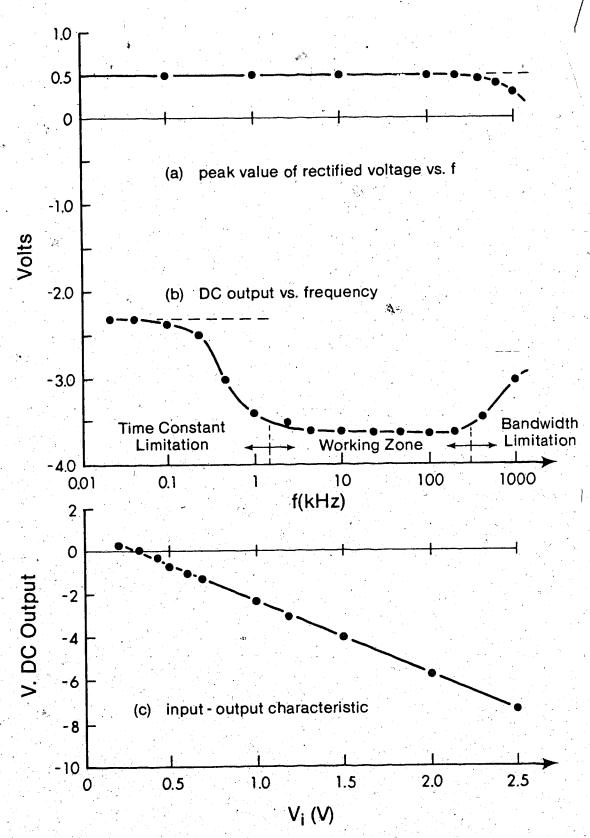

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.2   | High-frequency Rectifier                | 91   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | 5.2.1 Operation of Basic Rectifier      | 92   |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ,     | 5.2.2 Conversion Errors                 | 95   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | 5.2.3 Complete Rectifier Circuit        | 95   |

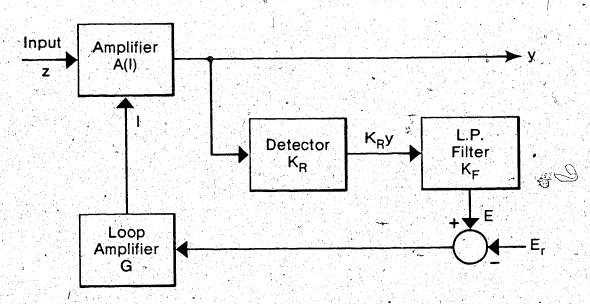

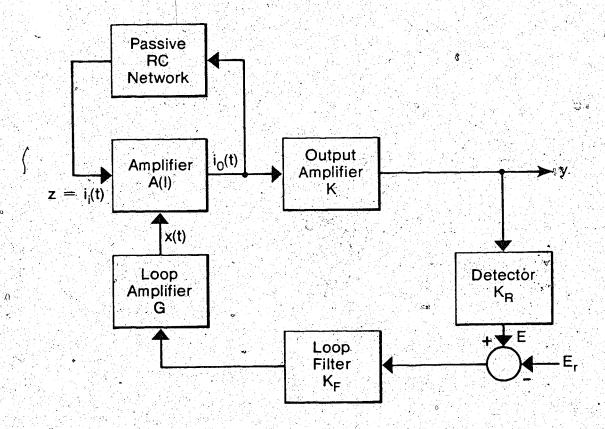

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.3   | AGC Loop                                | 98   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | 5.3.1 Linear AGC Model for Oscillators  | 100  |

| ***************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       | 5.3.2 Stability Analysis of AGC Loop    | 107  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.4   | Summary                                 | 113  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |                                         |      |

| VI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | FREQ  | UENCY CONTROL                           | 115  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6.1   | Introduction                            | 115  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6.2   | Current-controlled Oscillator           | 117  |

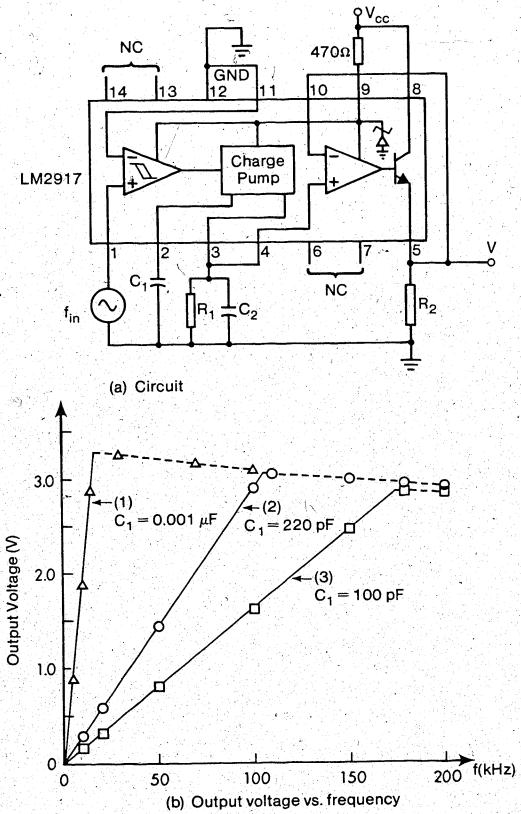

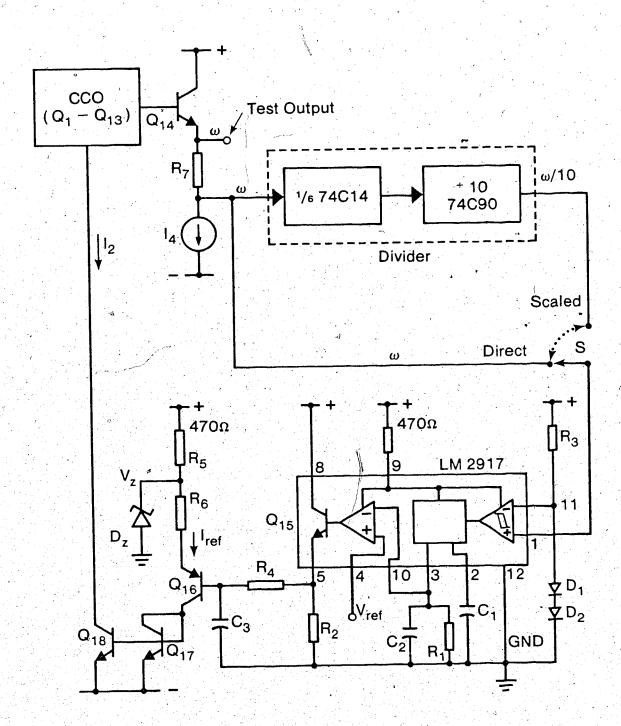

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6.3   | Frequency-to-Voltage Converter          | 122  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6.4   | Simple Frequency Control Circuit        | 123  |

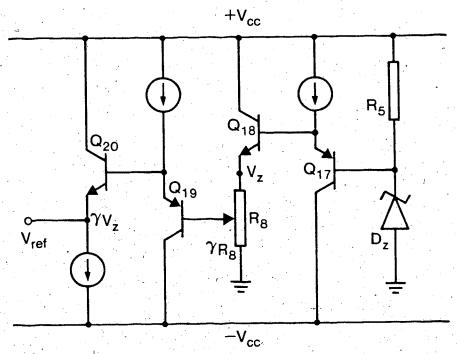

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6.5   | Improved Circuits                       | 127  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | 6.5.1 Simple Variable Reference Voltage | 128  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | 6.5.2 Current Comparator                | 128  |

| TO THE STATE OF TH |       |                                         |      |

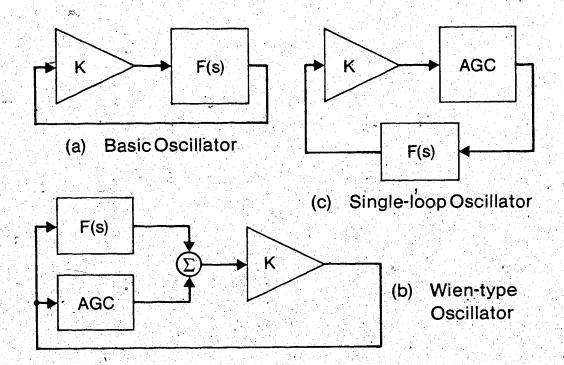

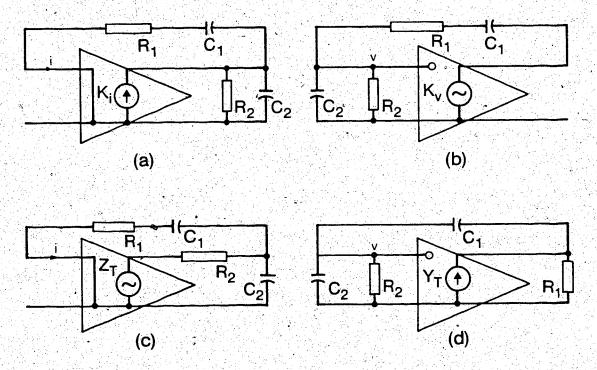

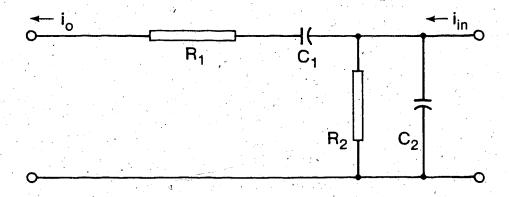

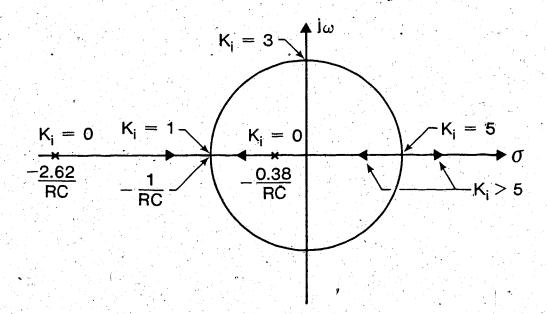

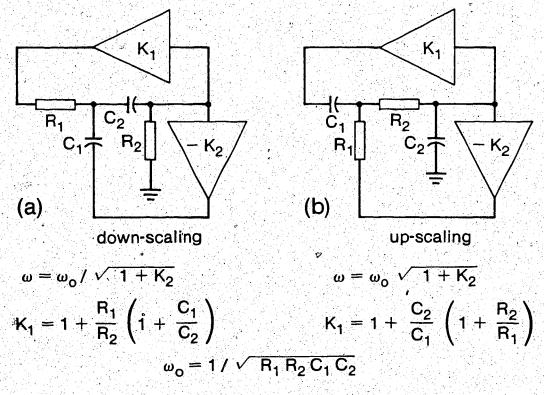

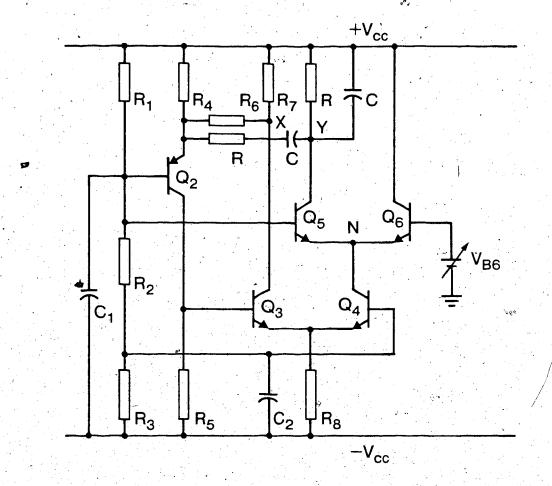

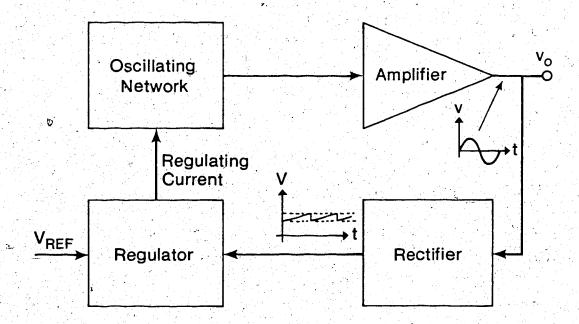

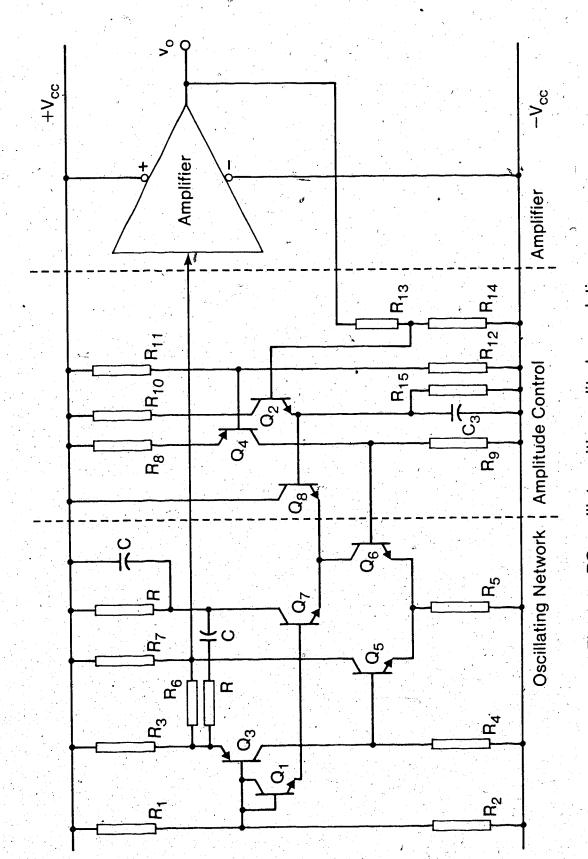

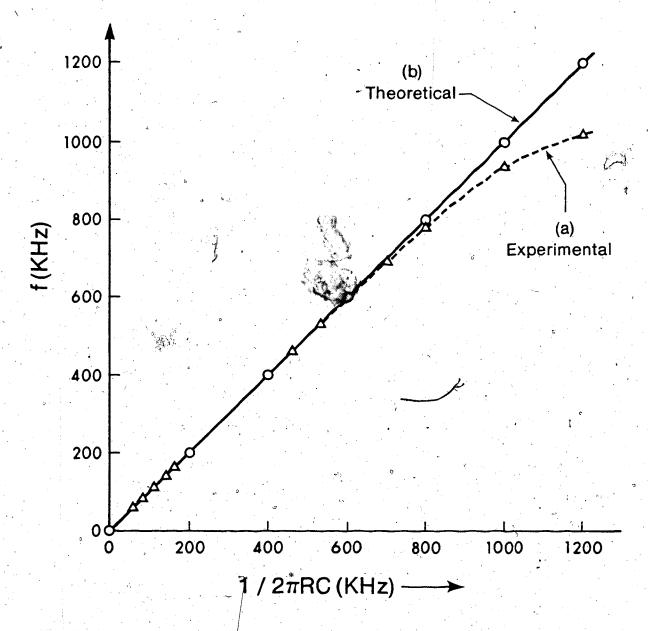

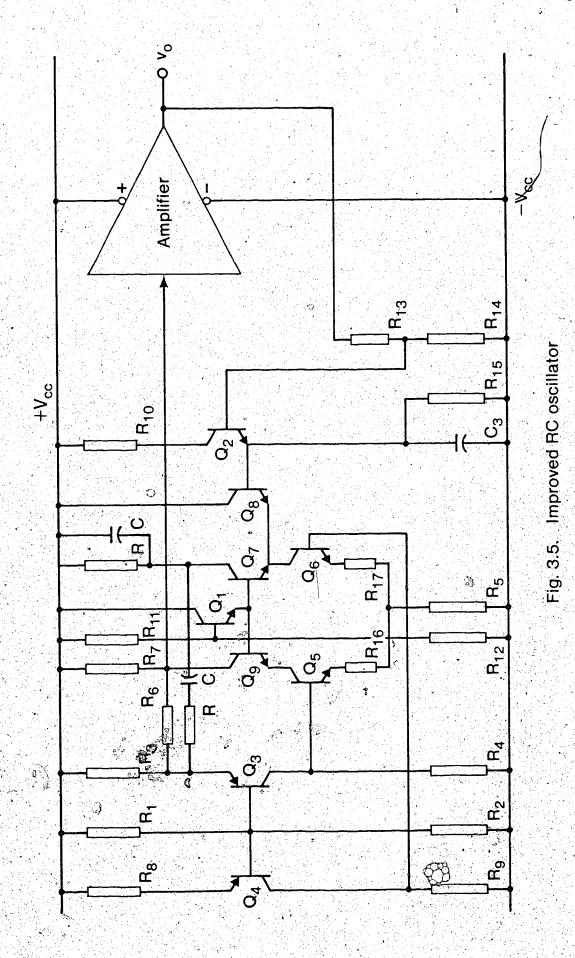

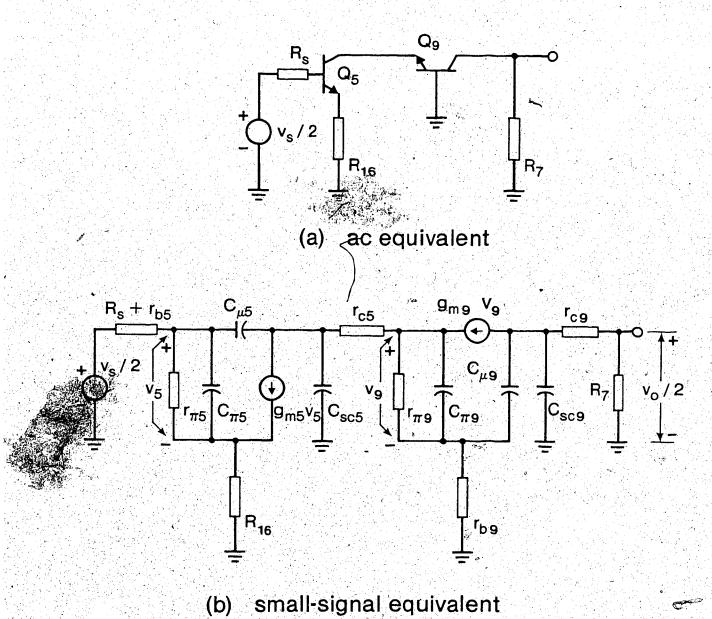

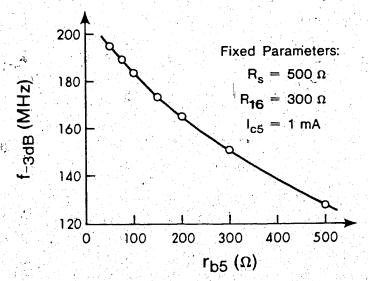

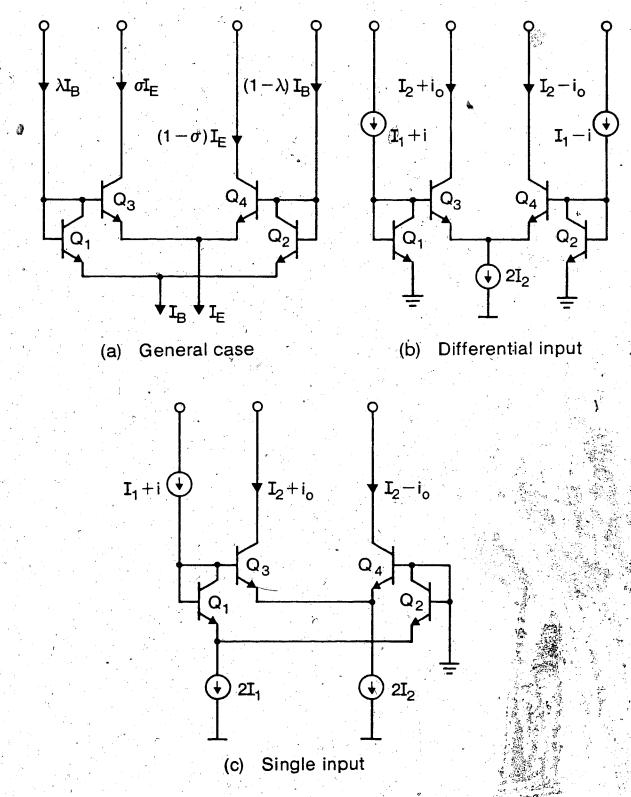

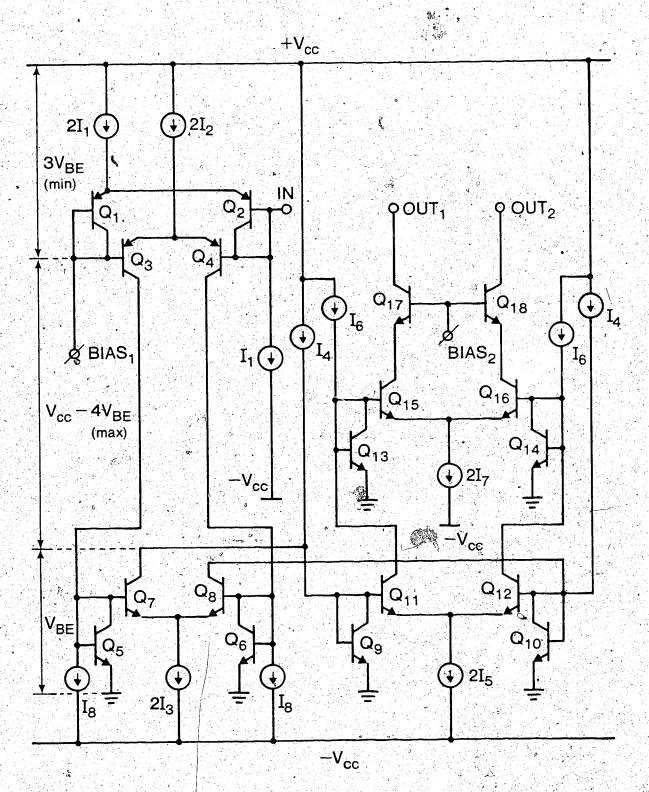

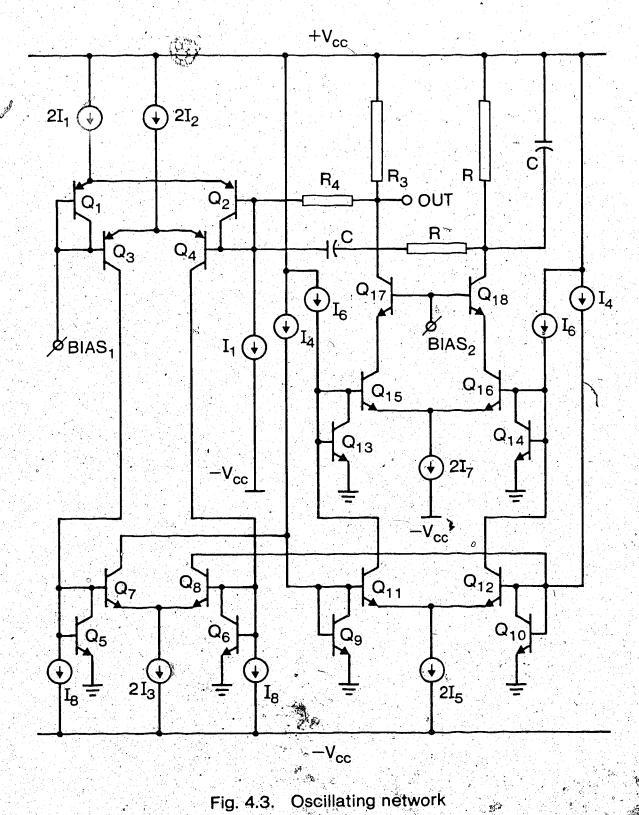

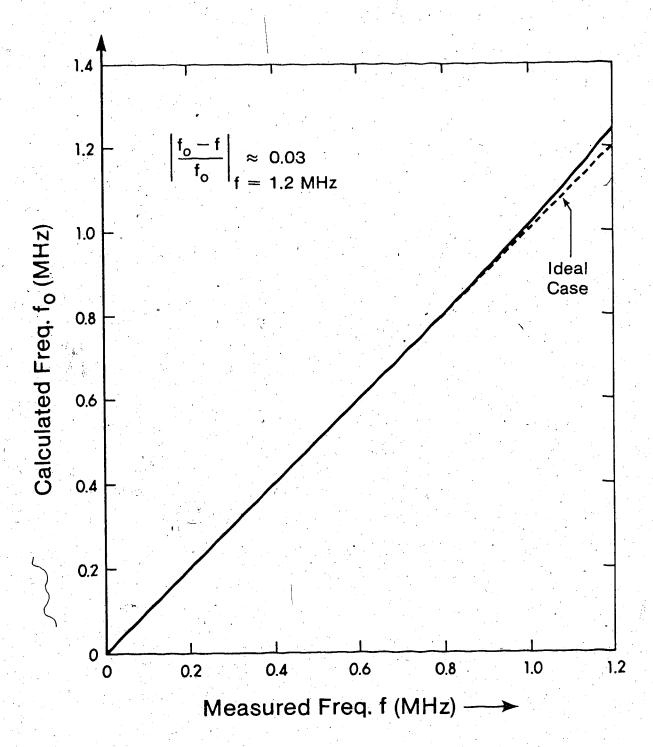

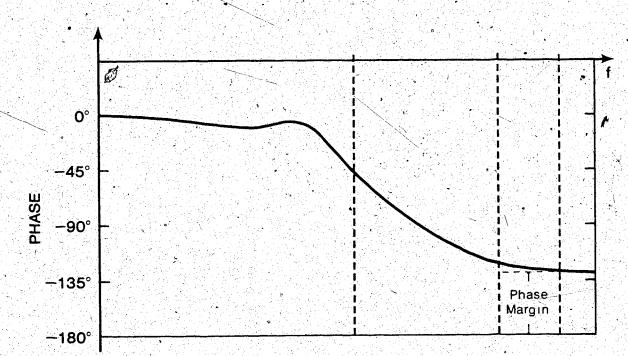

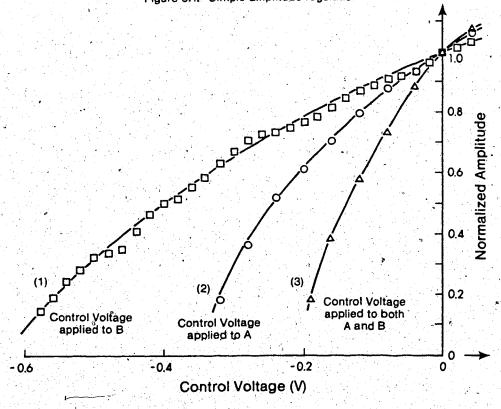

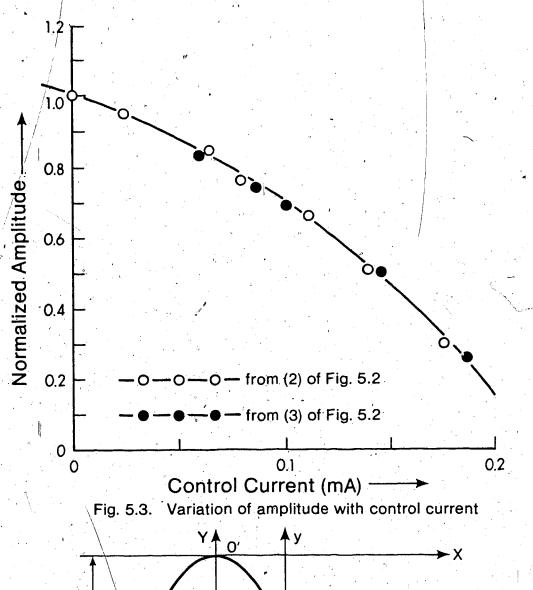

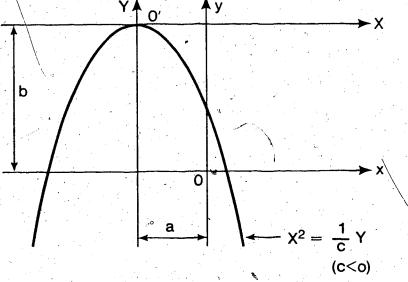

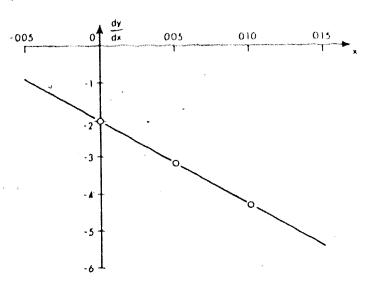

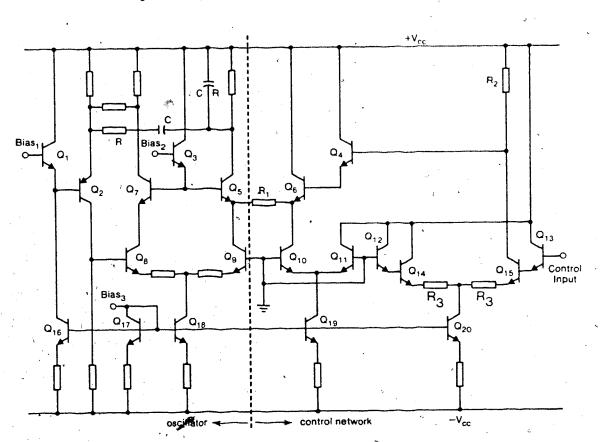

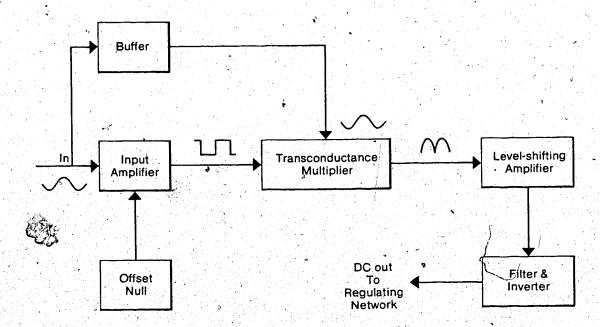

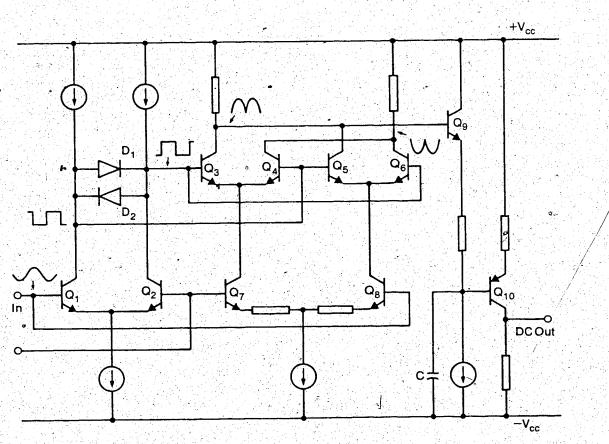

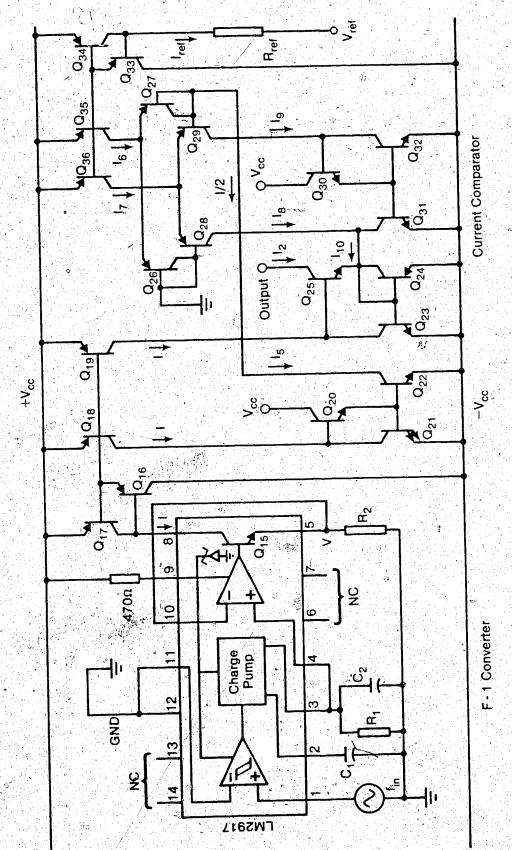

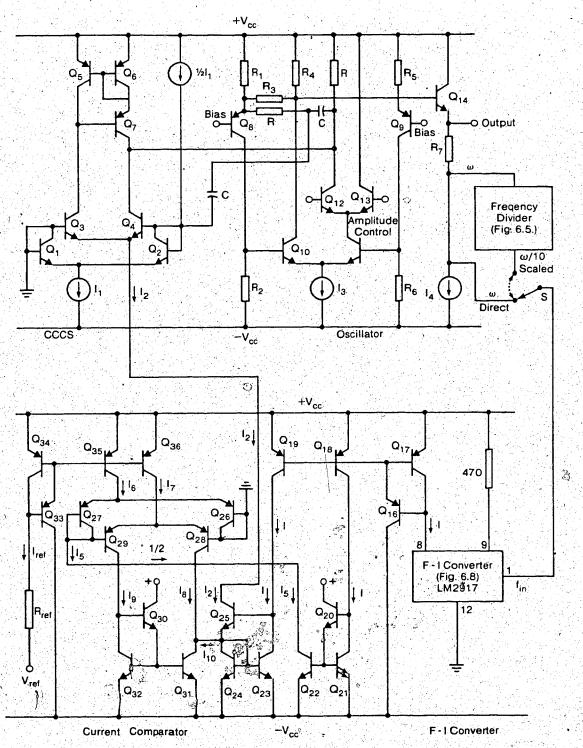

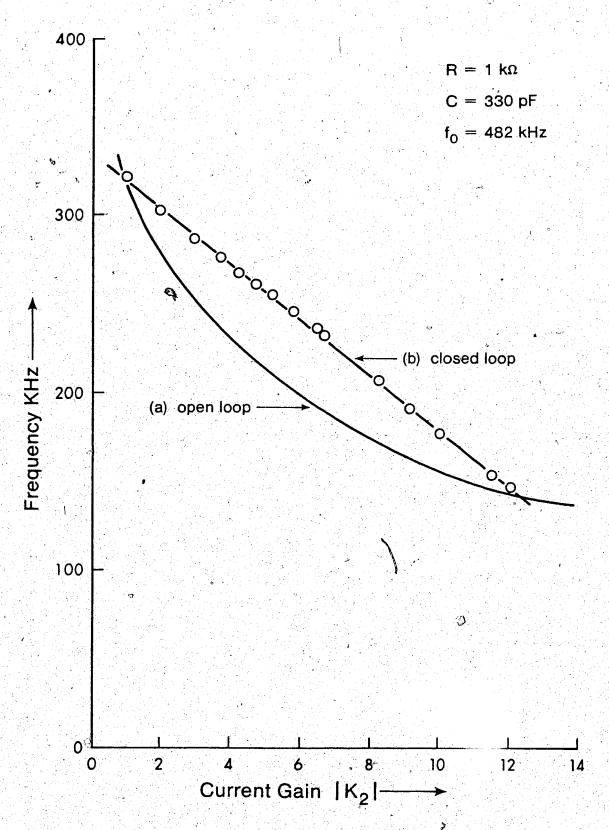

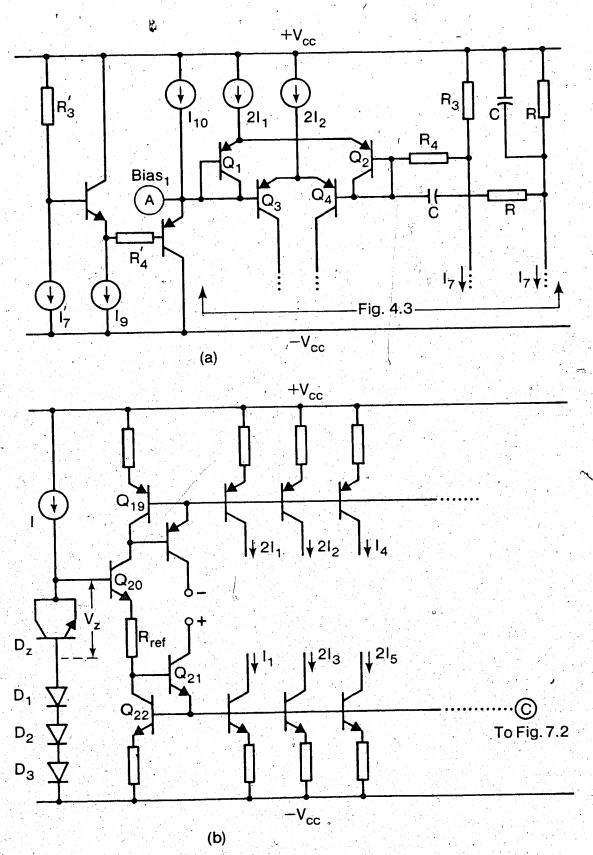

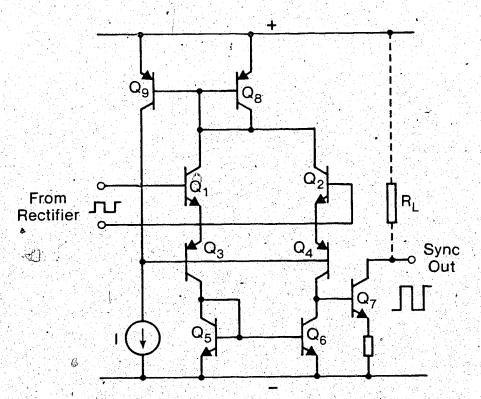

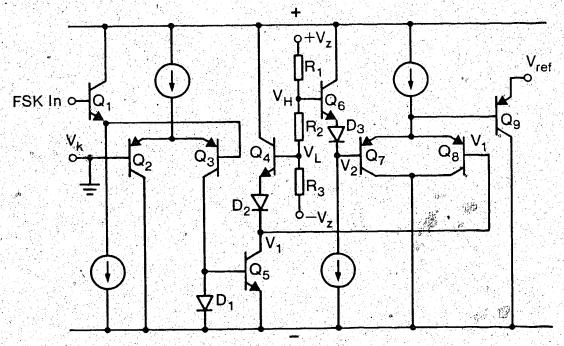

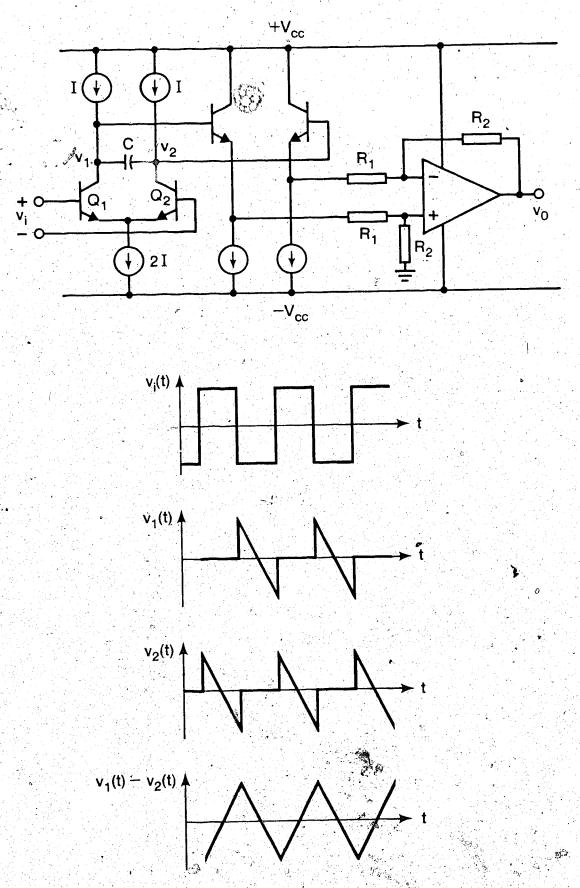

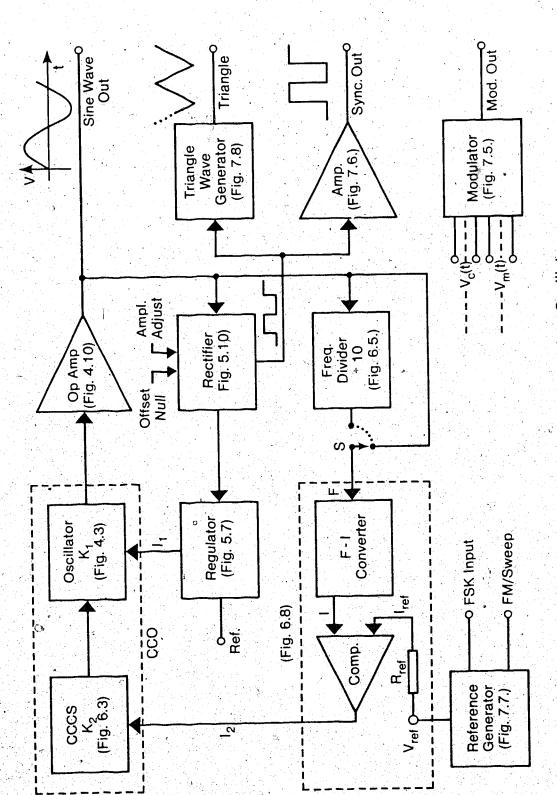

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |                                         |      |