### **University of Alberta**

### Design and FPGA Implementation of a Log-Domain High-Speed Fuzzy Control System

by

### Md Ali Razib

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of

Master of Science

in Software Engineering and Intelligent Systems

Electrical and Computer Engineering

©Md Ali Razib Spring 2010 Edmonton, Alberta

Permission is hereby granted to the University of Alberta Libraries to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly or scientific research purposes only. Where the thesis is converted to, or otherwise made available in digital form, the University of Alberta will advise potential users of the thesis of these terms.

The author reserves all other publication and other rights in association with the copyright in the thesis and, except as herein before provided, neither the thesis nor any substantial portion thereof may be printed or otherwise reproduced in any material form whatsoever without the author's prior written permission.

### **Examining Committee**

Scott Dick, Electrical and Computer Engineering

Vincent Gaudet, Electrical and Computer Engineering

Marek Reformat, Electrical and Computer Engineering

Nelson Amaral, Computing Science

### Abstract

The speed of fuzzy controllers implemented on dedicated hardware is adequate for control of any physical process, but too slow for today's high-complexity data networks. Defuzzification has been the bottleneck for fast implementations due to the large number of computationally expensive multiplication and division operations. In this thesis, we propose a high-speed fuzzy inferential system based on log-domain arithmetic, which only requires addition and subtraction operations. The system is implemented on a Xilinx Virtex-II FPGA with a processing speed of 67.6 MFLIPS having a maximum combinational path delay of 4.2 ns. It is a clear speedup compared to the reported fastest 50 MFLIPS implementation. A pipelined version of the controller is also implemented, which achieves a speed of 248.7 MFLIPS. Although a small approximation error is introduced, software simulation and hardware implementation on FPGA confirm high similarity of the outputs for control surfaces and a number of second-order plants.

# Acknowledgments

I express my sincere gratitude to Russell Dodd, Eric Son and Ji Sun for their valuable suggestions during the implementation of log-domain controller on FPGA.

# Dedication

In loving memory of my father

Md Farman Ali

(1944 - 2007)

# TABLE OF CONTENTS

| Abstract i                                             |

|--------------------------------------------------------|

| Acknowledgments ii                                     |

| Dedicationiii                                          |

| Table of Contents iv                                   |

| List of Tables viii                                    |

| List of Figures ix                                     |

| List of Symbols/ Acronyms xii                          |

| CHAPTER 1: INTRODUCTION 1                              |

| CHAPTER 2: BACKGROUND LITERATURE                       |

| 2.1 Overview of Control Systems                        |

| 2.1.1 Basic Feedback Control 5                         |

| 2.1.2 Modes of Control 6                               |

| 2.1.3 Laplace Transformation                           |

| 2.1.4 Transfer Functions 12                            |

| 2.1.5 Step Responses of Continuous-Time Linear Systems |

|        | 2.1.6 Digital Control Systems                                 | 16 |

|--------|---------------------------------------------------------------|----|

|        | 2.1.7 Z-Transform                                             | 18 |

|        | 2.1.8 Discrete Transfer Functions                             | 18 |

|        | 2.1.9 Continuous-to-Discrete Transfer Function Transformation | 19 |

|        | 2.1.10 Stability                                              | 20 |

| 2.2 Fu | zzy Logic and Fuzzy Control                                   | 21 |

|        | 2.2.1 Basic Concepts of Fuzzy Logic                           | 22 |

|        | 2.2.2 Membership Functions                                    | 23 |

|        | 2.2.3 Fuzzy Set Operations                                    | 24 |

|        | 2.2.4 Fuzzy Logic                                             | 27 |

|        | 2.2.5 Fuzzy Controller                                        | 29 |

|        | 2.2.6 Components of Fuzzy Controller                          | 30 |

|        | rdware Implementations of Fuzzy Controllers                   | 33 |

|        | 2.3.1 Analog Implementations                                  | 33 |

|        | 2.3.2 Digital Implementations                                 | 36 |

|        | 2.3.3 Fast Defuzzification                                    | 39 |

| CHAPTER 3: PROPOSED LOG-DOMAIN CONTROLLER 41          |

|-------------------------------------------------------|

| 3.1 Logarithmic Arithmetic                            |

| 3.2 Approximate Correction Factor                     |

| 3.3 Design of the Controller                          |

| 3.4 Simulation Design 44                              |

| 3.4.1 Typical Fuzzy Controller 44                     |

| 3.4.2 Log-Domain Controller with Correction Factor    |

| 3.4.3 Log-Domain Controller without Correction Factor |

| CHAPTER 4: EXPERIMENTAL RESULTS IN SIMULATION 47      |

| 4.1 Experiment 1 47                                   |

| 4.1.1 Controllers 48                                  |

| 4.1.2 Results 49                                      |

| 4.1.3 Analysis 54                                     |

| 4.2 Experiment 2 55                                   |

| 4.2.1 Controllers 55                                  |

| 4.2.2 Results                                         |

| 4.2.3 Analysis 61                     |

|---------------------------------------|

| CHAPTER 5: HARDWARE IMPLEMENTATION 63 |

| 5.1 Design Considerations             |

| 5.2 Log-domain Controller             |

| 5.2.1 Results                         |

| 5.3 Pipelined Log-domain Controller   |

| 5.3.1 Results                         |

| 5.4 Comparative Analysis              |

| CHAPTER 6: FUTURE RESEARCH            |

| CHAPTER 7: CONCLUSION                 |

| BIBLIOGRAPHY                          |

## List of Tables

| Table 4.1: Rule base for the fuzzy controllers    48                                       |

|--------------------------------------------------------------------------------------------|

| Table 4.2: Rise time, settling time, and overshoot for different controllers with a        |

| sampling period of 0.01 s 51                                                               |

| Table 4.3: RMS difference between control surfaces    52                                   |

| Table 4.4: Rule base for the fuzzy controller    56                                        |

| Table 4.5: Rise time, settling time and overshoot for the plant $400/(s^2+20s)$ 58         |

| Table 4.6: Rise time, settling time and overshoot for the plant $400/(s^2+48.5s) \dots 59$ |

| Table 4.7: Rise time, settling time and overshoot for the plant $400/(s^2+360s) \dots 59$  |

| Table 4.8: RMS difference between control surfaces    61                                   |

| Table 5.1: FPGA resource utilization for log-domain controller                             |

| Table 5.2: FPGA resource utilization for pipelined log-domain controller 74                |

| Table 5.3: Comparisons of rise time, settling time, overshoot and speed between            |

| non-pipelined and pipelined version of log-domain controller                               |

# List of Figures

| Figure 2.1: Basic control system                                     |

|----------------------------------------------------------------------|

| Figure 2.2: Open-loop control system                                 |

| Figure 2.3: An example of feedback control system                    |

| Figure 2.4: PID controller                                           |

| Figure 2.5: Proportional controller                                  |

| Figure 2.6: PI controller                                            |

| Figure 2.7: Discrete pulse                                           |

| Figure 2.8: Under damped response 15                                 |

| Figure 2.9: Over damped response 16                                  |

| Figure 2.10: Critically damped response                              |

| Figure 2.11: Digital control system 17                               |

| Figure 2.12: Examples of stable and unstable responses               |

| Figure 2.13: Notion of fuzzy sets                                    |

| Figure 2.14: (a) Trapezoidal and (b) triangular membership functions |

| Figure 2.15: Fuzzy control system                                    |

| Figure 2.16: Fuzzy controller block diagram 30                                     |

|------------------------------------------------------------------------------------|

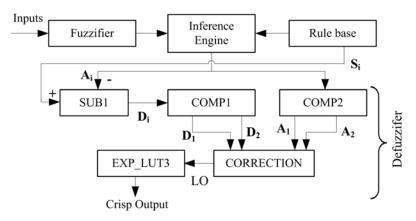

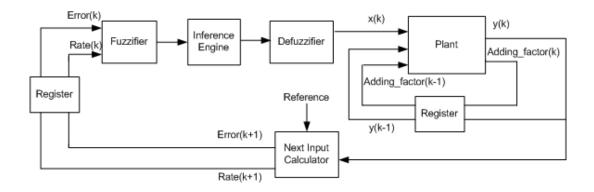

| Figure 3.1: Block diagram of the log-domain controller                             |

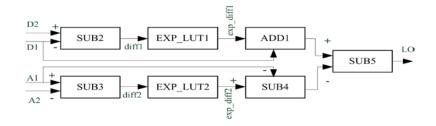

| Figure 3.2: Block diagram of CORRECTION 44                                         |

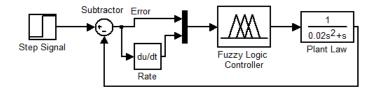

| Figure 3.3: Simulink diagram for typical fuzzy controller                          |

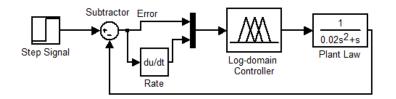

| Figure 3.4: Simulink diagram of log-domain controller 45                           |

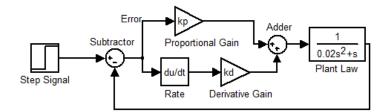

| Figure 4.1: PD controller                                                          |

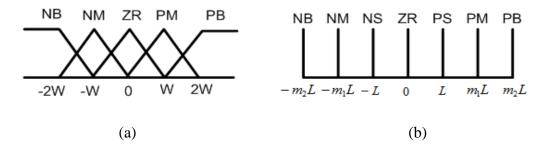

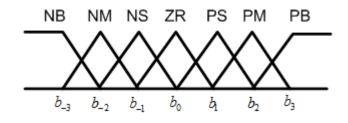

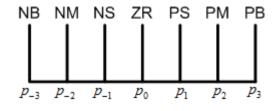

| Figure 4.2: (a) Input and (b) output membership functions 48                       |

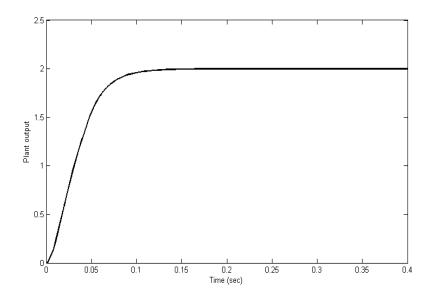

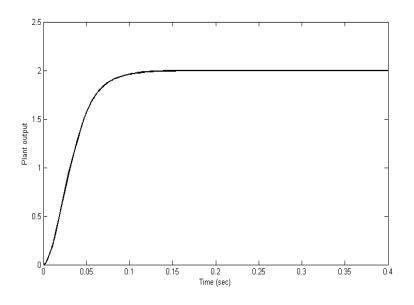

| Figure 4.3: Step responses of different controllers - (a) linear PD, (b) typical   |

| fuzzy, (c) log-domain without a correction factor and (d) log-domain with a        |

| correction factor                                                                  |

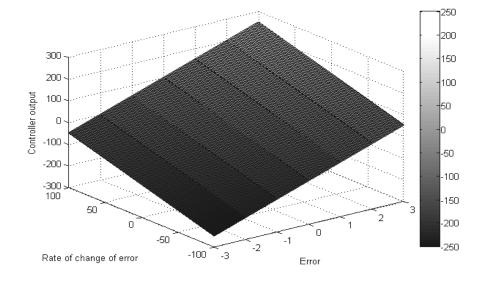

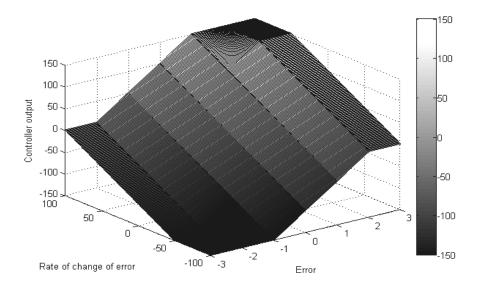

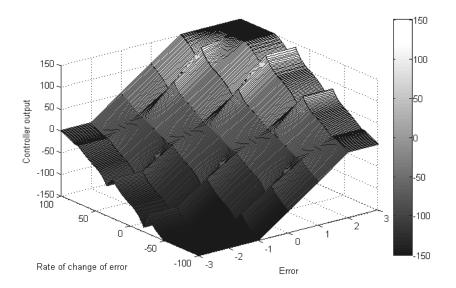

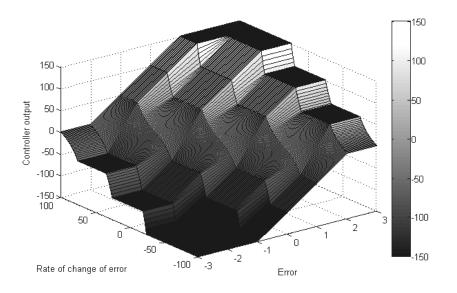

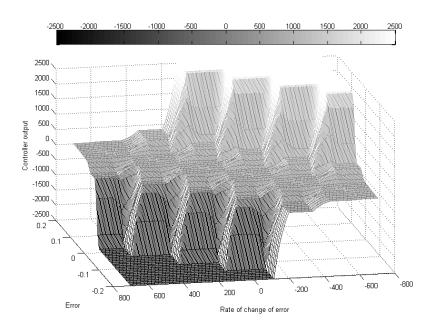

| Figure 4.4: control surfaces of different controllers - (a) linear PD, (b) typical |

| fuzzy, (c) log-domain without a correction factor and (d) log-domain with a        |

| correction factor                                                                  |

| Figure 4.5: (a) Input and (b) output membership functions 55                       |

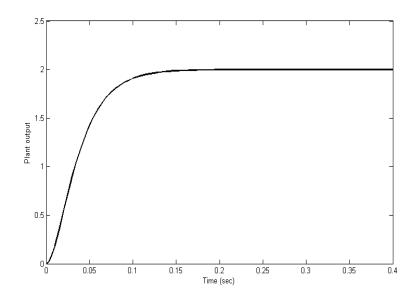

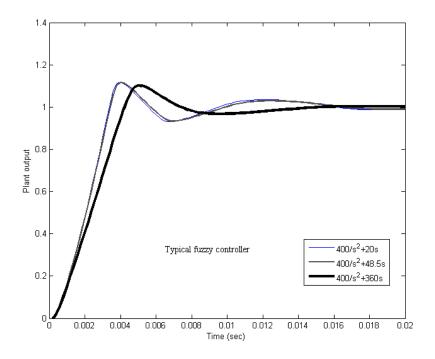

| Figure 4.6: Step response of typical fuzzy controller 57                           |

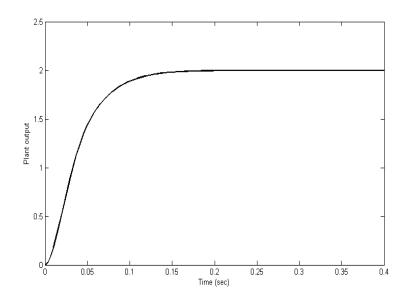

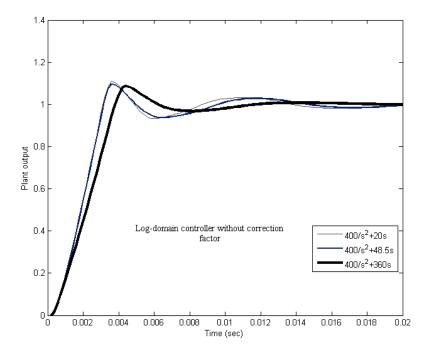

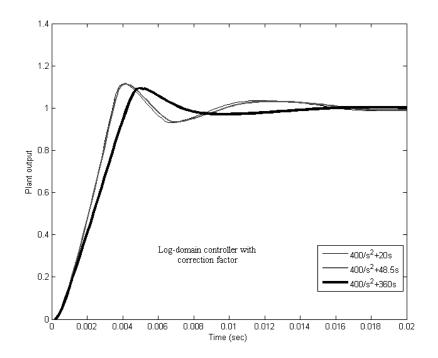

| Figure 4.7: Step response of log-domain controller without correction factor 57    |

| Figure 4.8: Step response of log-domain controller with correction factor 58       |

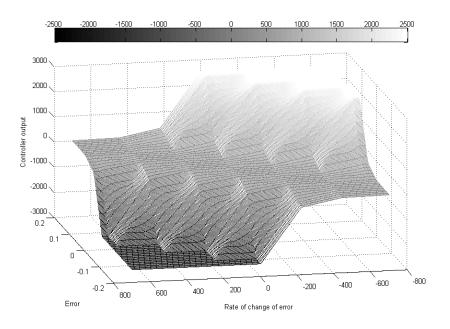

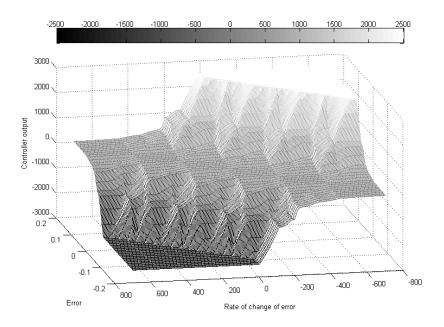

| Figure 4.9: Control surface for typical fuzzy controller 60                      |

|----------------------------------------------------------------------------------|

| Figure 4.10: Control surface for log-domain controller without correction factor |

|                                                                                  |

| Figure 4.11: Control surface for log-domain controller with correction factor 61 |

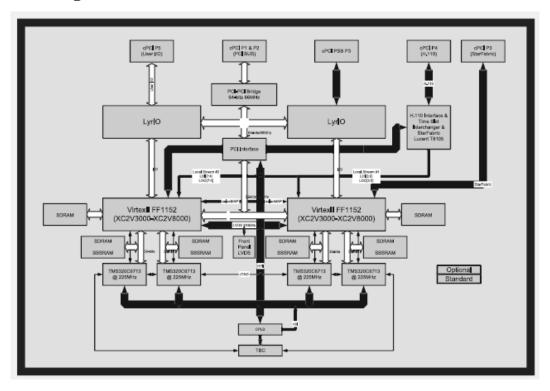

| Figure 5.1: Block Diagram of Lyrtech SignalMaster board which consists of a      |

| DSP, a Virtex-II FPGA and multiple input/output expansions                       |

|                                                                                  |

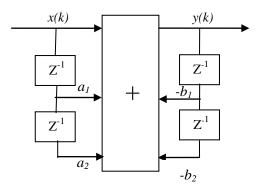

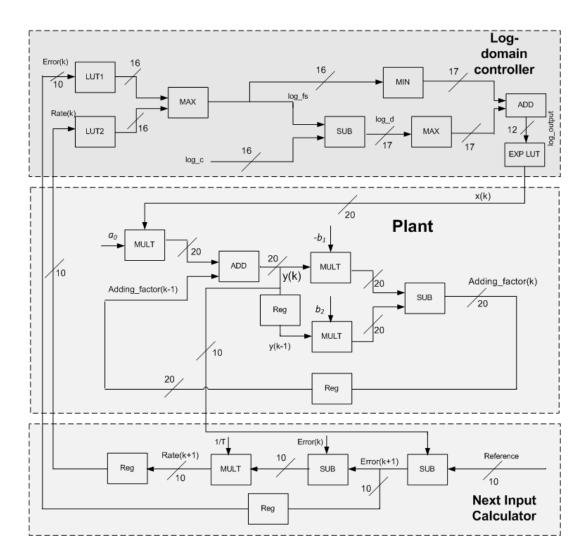

| Figure 5.2: Second order digital filter implementation on FPGA 64                |

| Figure 5.3: Block diagram of log-domain controller with plant as implemented on  |

| Xilinx Virtex-II FPGA                                                            |

| Figure 5.4: Operations inside the control system                                 |

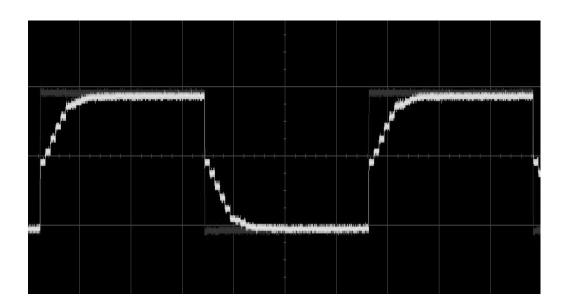

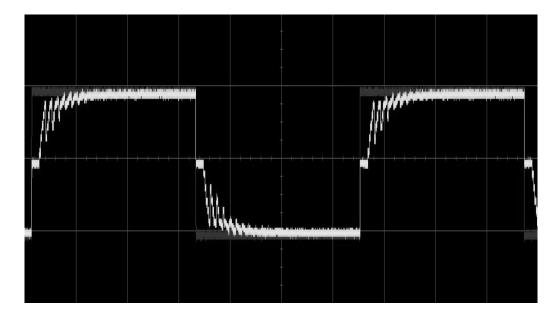

| Figure 5.5: Plant outputs for log-domain controller implemented on FPGA and      |

| displayed on an oscilloscope for both positive and negative cycles               |

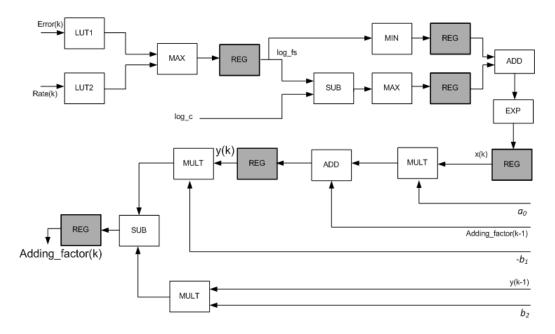

| Figure 5.6: Pipeline stages of log-domain controller                             |

| Figure 5.7: Plant outputs for pipelined log-domain controller implemented on     |

| FPGA and displayed on an oscilloscope for both positive and negative cycles 73   |

# List of Symbols/ Acronyms

| DSP:   | Digital Signal Processing               |

|--------|-----------------------------------------|

| FLIPS: | Fuzzy Logic Inferences Per Second       |

| FPGA:  | Field Programmable Gate Array           |

| VLSI:  | Very Large Scale Integration            |

| PI:    | Proportional-Integral                   |

| PD:    | Proportional-Derivative                 |

| PID:   | Proportional-Integral-Derivative        |

| LUT:   | Look-Up Table                           |

| COG:   | Center Of Gravity                       |

| MOM:   | Mean Of Maxima                          |

| PWL:   | Piece Wise Linear                       |

| MOS:   | Metal-Oxide Semiconductor               |

| CMOS:  | Complementary Metal Oxide Semiconductor |

| NLL:   | Normalized Locked Loop                  |

| I-V:   | Current to Voltage                      |

| FPAA: | Field Programmable Analog Array         |

|-------|-----------------------------------------|

| A/D:  | Analog to Digital                       |

| D/A:  | Digital to Analog                       |

| VLSI: | Very Large Scale Integration            |

| ROM:  | Read-Only Memory                        |

| RAM:  | Random Access Memory                    |

| ASIC: | Application-Specific Integrated Circuit |

| FPE:  | Fuzzy Processing Element                |

| FALU: | Fuzzy Arithmetic Logic Unit             |

| KAFA: | KAist Fuzzy Accelerator                 |

| FRHC: | Fired Rules Hyper Cube                  |

| DA:   | Distributed Arithmetic                  |

| DC:   | Direct Current                          |

# CHAPTER 1 INTRODUCTION

Data communication networks, and particularly the Internet, play a pivotal role in modern society. To improve effective bandwidth, Quality of Service (QoS) and other performance metrics, the optimization of these networks is very important. A number of network optimization goals can be represented as control problems, and solved by traditional control algorithms. However, one drawback of traditional control is that it requires an exact mathematical model of a system, and this model is often unavailable for large and complex networks. Intelligent control systems that do *not* require exact models have become more commonplace. Fuzzy logic controllers, proposed in theory by Zadeh [9], [10], and first implemented in automatic control by Mamdani [11], [12], are a particular class of intelligent controllers built on fuzzy expert systems, that show substantial performance improvement in simulation over standard algorithms for these problems.

The implementation of a fuzzy controller, however, is not straightforward. Software simulations on general-purpose microprocessors are typically slow due to the lack of instruction-set support for fuzzy operations. This imposes a big problem for today's high-complexity and high-speed networks, requiring specialized hardware. A number of researchers have pursued fuzzy hardware development, beginning with a voltage-mode analog circuit in 1969. Although analog implementations [51] provide lower power consumption and lower chip size [50], they suffer from being slower, less accurate, less flexible and less scalable compared to their digital counterparts. Thus research into digital hardware implementations is ongoing, with reported performance of ASIC implementations ranging from 20 to 50 million fuzzy logic inferences per second (MFLIPS) [25]. This is a commonly used performance measure for fuzzy

systems<sup>1</sup>. It indicates the rate at which a defuzzified output can be computed [24]. Digital fuzzy hardware implementations, however, still have a bottleneck due to the large number of costly multiplication and division operations required in the defuzzifier, the last module in the fuzzy controller [22].

In this thesis, we propose and implement a high-speed fuzzy controller on hardware based on log-domain arithmetic. The basic principle of our approach is to represent all quantities by their logarithmic values, therefore transforming multiplication and division functions into computationally much simpler addition and subtraction operations. The logarithmic values are stored in lookup tables to facilitate instant conversion between a log value and its exponential value. The summation of a number of log-domain values is approximated as the maximum logarithmic value to simplify calculations. Although it introduces a small approximation error, simulation and hardware implementation results illustrate the similarity of the generated outputs with the expected outputs. Our system outperforms the reported fastest implementation in the literature [80] by 33% in speed. An even higher processing speed is achieved for a pipelined version, which we postulate would enable our system to be applicable in high-speed data networking applications.

The rest of the thesis is organized as follows. Chapter 2 starts with an overview of control systems and then goes on to discuss the concepts behind fuzzy controllers and their analog and digital hardware implementation. A review of published literature on fast defuzzification is also presented. Chapter 3 discusses the design of our log-domain controller and the justification of using a correction factor to improve the results. Simulation results for a number of second-order plants are detailed in Chapter 4. It also includes performance comparisons with a linear PD and a typical fuzzy controller. Chapter 5 presents the hardware implementation with speed and resource usage comparisons between a pipelined and a non-

<sup>&</sup>lt;sup>1</sup> MFLIPS are difficult to use to make comparisons since the reported number is highly dependent on the number of rules in the rule base and the computational precision.

pipelined version of the log-domain controller. Chapter 6 provides directions for future research, and Chapter 7 concludes the thesis.

# CHAPTER 2 BACKGROUND LITERATURE

#### 2.1 Overview of Control Systems

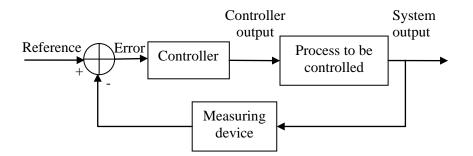

A control system is an interconnection of components forming a system configuration to generate a desired system response. Control systems deal with the behavior of dynamic systems – systems for which outputs change with time, and are a factor of the inputs. In a control system, the desired output is called the *reference* [1]. A control system produces an output for a given input, where the input and output represent the desired response and the actual response respectively. There are numerous examples of control systems being used, such as home heating and air-conditioning systems controlled by a thermostat, the cruise control of an automobile, an elevator-position control system used in high-rise multi-level buildings, human heart using a pacemaker and so on [42]. The device or process to be controlled is termed as a *plant*. The plant, for instance, can be a furnace system where temperature is the output variable. Usually the plant output is sent back for comparison with the reference to produce the next input, as shown in Figure 2.1.

Figure 2.1: Basic control system

#### **2.1.1 Basic Feedback Control**

Control systems are typically classified as open-loop or closed-loop systems. Open-loop control systems do not monitor or correct the output for disturbances, while closed-loop system keep monitoring the output and comparing it with the input. Figure 2.2 shows a general open-loop control system.

Figure 2.2: Open-loop control system

As seen from Figure 2.2, there is no way for the output to get fixed automatically if it is not at an acceptable value. Any parameter having a different value than what was anticipated causes a proportional error in the output. For instance, let us consider a gas furnace as a control system [2]. In case of no adequate temperature sensor, manually calibrating the valve is the only way to adjust the gas flow. This system would only work on average days when the room temperature remains steady. However, if external weather conditions change, the furnace would not be able to provide the desired temperature. An open-loop controller is usually an analytical tool used to design a real closed-loop system.

Closed-loop (feedback) control systems are similar to open-loop ones, except for the fact that a sensor monitors the output and it is compared with the input signal. The difference between the input and output signal is referred to as the error. An ideal feedback system produces the desired response exactly by cancelling out all errors. Continuing with the previous example, suppose a thermostat is there to measure the temperature and can be set at any required value. So for normal temperature, the system works as the open-loop system does; however, it provides greatest benefits when there is a change in temperature. The thermostat increases the valve opening if the temperature decreases, and vice versa. This dynamic compensation for changes in the output is the principle behind the feedback control system. A closed-loop control system [38] is shown in Figure 2.3.

Figure 2.3: An example of feedback control system [38]

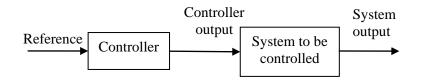

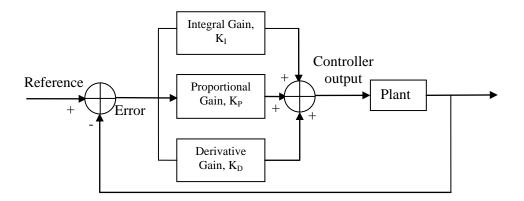

### 2.1.2 Modes of Control

Modes of control are the methods to calculate the values of the controller output variables. The modes are: proportional (P), integral (I) and derivative (D). They are most commonly used in some combination, although single modes are also possible. Among the different combinations, proportional-integral-derivative (PID) controller is very widely used in industrial control systems. Figure 2.4 shows the block diagram of a PID controller. Note that there are other types of traditional control systems available, namely – phase-lead, phase-lag and quadratic optimal controller, besides the commonly used PID controllers.

Figure 2.4: PID Controller

The proportional part calculates the reaction to the current error, the integral part considers the sum of recent errors to determine the reaction, and the derivative part focuses on the rate at which the error has been changing. The gains,  $K_P$ ,  $K_I$  and  $K_D$ , represent the weights applied to each part respectively before summing them up. To achieve specific design requirements the constant gains are tuned. In some cases, only one or two modes are needed to provide the appropriate output. This is done simply by settling the undesired gain to zero. The derivative gain is often disabled to obtain PI controllers [3]. The individual modes are discussed below.

#### **2.1.2.1 Proportional Mode**

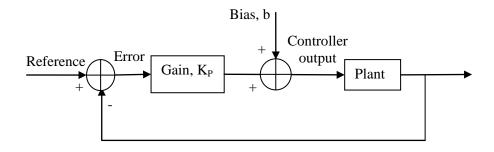

When a controller is in proportional mode, the controller output is, as the name suggests, proportional to the measured value. It does not keep track of the history of the value measured neither does it account for the rate of change in measured value. Tuning the purely proportional controller for the desired performance is relatively easy; however, a steady-state error exists between the set point and measured value in most cases. A proportional (P) controller is shown in Figure 2.5.

Figure 2.5: Proportional controller [3]

The behavior is expressed by the following equation:

$$U(t) = k_P e(t) + b \tag{2.1}$$

where U(t) is the controller output,  $k_p$  is the proportional gain, e(t) is the error and b is the output bias.

Bias or manual reset provides the value of the output when the error is zero.

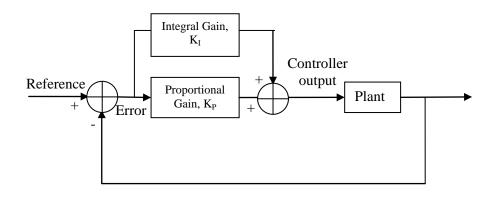

#### 2.1.2.2 Integral Mode

The contribution from the integral term is proportional to both the magnitude and duration of the error. An integral (I) mode controller consists of an integrator. Thus if the error signal (input to the integrator) is positive, the integrator output shifts upward, and it shifts downward for negative input. The output remains steady when measured value is equal to the set point. In comparison with the proportional controller, an integral controller does not need manual reset to adjust the output bias. Now the bias is automatically set by the output of the integrator. Figure 2.6 shows a PI controller.

Figure 2.6: PI controller

The equation for PI controller is:

$$U(t) = k_P e(t) + K_I ! e(t) dt$$

(2.2)

where U(t) is the controller output,  $k_p$  is the proportional gain,  $K_I$  is the integral gain and e(t) is the error.

The integral term (added with the proportional term) accelerates the movement of the process towards the set point and eliminates the residual steady-state error. However, the integral term can cause overshooting (cross over the set point and create a deviation in the other direction).

#### 2.1.2.3 Derivative Mode

Derivative term calculates the rate of change of error and multiplies it by the gain  $K_D$ . The derivative term reduces the speed of the rate of change of the controller output, hence is used to reduce the magnitude of overshoot generated by the integral term.

The equation for a PID controller is:

$$U(t) = K_P e(t) + K_I \int e(t)dt + K_D \frac{de(t)}{dt}$$

(2.3)

A tuning parameter,  $T_D$  can be used to adjust the relative effect of the derivative mode. However, derivative term can make the system unstable if the noise and derivative gain are sufficiently large [3].

#### 2.1.3 Laplace Transformation

A differential equation is one way to describe, in mathematical terms, the relationship between the input and output of dynamic systems. It depends on the components which form the dynamic system and the manner in which they are connected [2]. It is a relationship between a function of time and its derivatives.

For instance, the equations

$$\frac{dy}{dt} = 3y^2 \sin(t+y)$$

and  $\frac{d^3y}{dt^3} = e^{-y} + t + \frac{d^2y}{dt^2}$  are two

examples of differential equations [41]. The order of a differential equation is the order of the highest derivative of the function y appearing in the equation. Therefore the previous equations are first and third order differential equations, respectively.

A classic example of developing a differential equation is provided in [2] with a freely falling body through the air towards the Earth. There are two active forces being applied to the object. One is the weight of the object, W = mg, where *m* is the mass of the object and *g* is the acceleration of gravity. The other force is the air resistance acting on the object opposing the motion. To simplify things, a linear relationship is assumed between the friction force and speed, where the

friction force is equal to the product of velocity and the friction coefficient *b*, that is,

Friction  $=b\frac{dy}{dt}$ , where y is the position of the object at any value of time t.

Now, applying Newton's second law which states that force is equal to mass times acceleration,

$$\sum forces = m \frac{d^2 y}{dt^2}$$

(2.4)

where  $\frac{d^2 y}{dt^2}$  is the acceleration.

Since friction force is opposite to the weight, from (2.4),

$$W - Friction = m \frac{d^2 y}{dt^2}$$

Or,  $m \frac{d^2 y}{dt^2} + b \frac{dy}{dt} = mg$  (2.5)

This is the resulting differential equation. A differential equation can be either linear or nonlinear. A linear differential equation is any equation that can be written in the form [39]:

$$a_{n}(x)\frac{d^{n}y}{dx^{n}} + a_{n-1}(x)\frac{d^{n-1}y}{dx^{n-1}} + \dots + a_{1}(x)\frac{dy}{dx} + a_{0}(x)y = F(x)$$

(2.6)

where  $a_n(x)$ ,  $a_{n-1}(x)$ , ...,  $a_1(x)$ ,  $a_0(x)$  and F(x) depend only on the independent variable x, not on y. For example,  $\frac{d^2y}{dx^2} + y = x^3$  is a linear second-order differential equation, while  $\frac{d^2y}{dx^2} + \cos y = 0$  is nonlinear. A nonlinear differential equation does not have a solution in most cases; therefore, in practice, the equation is approximated as a linear one [39]. That is why linear differential equations are used to represent practical controllers. As the order of the differential equations grows, it becomes increasingly difficult and almost impossible to solve them using standard integration techniques. First order equations, the simplest ones, are categorized into several classes to be applicable to specific techniques of integration. For instance, if the right-hand side of the equation dx = f(x, y) can be expressed as a function that depends only on *x* times a function that depends only on *y*, then the equation is called separable equations, some approximation methods such as Euler's method, Taylor and Runge-Kutta method, have been developed.

The difficulty in solving differential equations using standard techniques gave rise to an approach called Laplace transformation. It is a very attractive method, because it converts the solution's process into a series of algebraic operations. It is also ideal for solving linear differential equations with constant coefficients. A system described by such equations is termed a linear-time-invariant (LTI) system.

The Laplace transformation of a function of time f(t) is given by [5]:

$$L[f(t)] = \int_{0}^{\infty} f(t)e^{-st}dt = F(s)$$

(2.7)

Where L[f(t)] is the shorthand notation for the Laplace integral and the parameter *s* is a complex quantity of the form  $\sigma + j\omega$ .

The transform takes a function of *t* and produces a function of *s*, which is done by multiplying f(t) by  $e^{-st}$  and then integrating with respect to *t* from 0 to  $\infty$ . However, f(t) must meet a couple of requirements to be Laplace-transformable. The requirements are – the function must be piecewise continuous over every finite interval  $0 \le t_1 \le t \le t_2$ , and the function must be of exponential order [5]. A function is piecewise continuous in a finite interval if that interval can be divided into a finite number of subintervals and the function is continuous over each of the subintervals. f(t) must also possess finite limits at the ends of each subintervals. A function f(t) is of exponential order if there exists a constant *a* such that the product  $e^{-at}/f(t)/$  is bounded for all values of *t* greater than some finite value *T*. This imposes the restriction that  $\sigma$ , the real part of *s*, must be greater than a lower bound  $\sigma_a$  for which the product  $e^{-\sigma_a t} | f(t) |$  is of exponential order.

Once the differential equation in time domain is transformed into an equation in *s*domain, it can be solved using algebraic manipulations. However, Laplace transformation is not an easy operation, except for very simple functions of f(t). Fortunately, the results can be stored in a table after the operation is performed once. Finally, to complete the solution, the F(s) needs to be converted to an f(t)using inverse Laplace transform of F(s). For this process, there is a corresponding operation, namely:

$$f(t) = L^{-1}[F(s)] = \frac{1}{2\pi j} \int_{\sigma-j\infty}^{\sigma+j\infty} F(s) e^{st} ds$$

(2.8)

As with the Laplace transform, lookup tables of inverse Laplace transforms for a number of common functions are published for convenience. When the response transform cannot be found in the tables, the general procedure is to express F(s) as the sum of partial fractions with constant coefficients. The partial fractions have a first-order or quadratic factor in the denominator and are readily found in the lookup tables. The complete inverse transform is the sum of the inverse transforms of each fraction.

#### **2.1.4 Transfer Functions**

*Transfer functions* are tools to describe the characteristics of dynamic components and systems. It provides a common language that allows engineers to communicate the behavioral aspects of a system. For a linear differential equation, the ratio of the output variable to the input variable is called the transfer function. If we take the Laplace transform of the high-order differential

equation

$$\frac{d^n y(t)}{dt^n} + a_{n-1} \frac{d^{n-1} y(t)}{dt^{n-1}} + \dots + a_0 y(t) = b_{n-1} \frac{d^{n-1} u(t)}{dt^{n-1}} + \dots + b_0 u(t)$$

, it becomes

an algebraic equation of the form, with zero initial conditions [4]:

$$s^{n}Y(s) + a_{n-1}s^{n-1}Y(s) + \dots + a_{0}Y(s) = b_{n-1}s^{n-1}U(s) + \dots + b_{0}U(s)$$

(2.9)

If

$$A(s) = s^n + a_{n-1}s^{n-1} + \dots + a_0$$

and  $B(s) = b_{n-1}s^{n-1} + \dots + b_0$ , we get  $Y(s) = G(s)U(s)$

where  $G(s) = \frac{B(s)}{A(s)}$  and G(s) is the transfer function. The denominator polynomial

A(s) is called *characteristic polynomial*. The roots of A(s) are the *poles* of G(s) and the roots of B(s) are the *zeros* of G(s).

For instance, let us consider a differential equation of the form:

$$m\frac{d^2y}{dt^2} + b\frac{dy}{dt} = w(t)$$

(2.10)

Taking the Laplace transform, assuming zero initial conditions,

$$ms^{2}Y(s) + bsY(s) = W(s)$$

(2.11)

where W(s) is the Laplace transform of w(t). Now,  $\frac{Y(s)}{W(s)} = \frac{1}{ms^2 + bs}$  is the transfer

function. Control systems and plants are usually represented by transfer functions.

#### 2.1.5 Step Responses of Continuous-Time Linear Systems

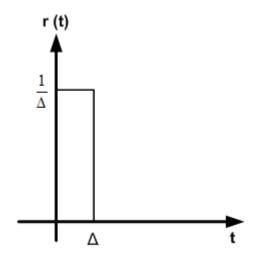

The response of a control system to a sudden input is an important issue from a practical standpoint, because depending on the amount and rate of deviations from the long term steady state, they have varying degree of impacts on the overall system. In addition, the control system response is delayed until the output settles down to some vicinity of its final value. This makes the response to an impulse or Dirac Delta function an interesting topic in the study of linear systems. Dirac Delta is the limit as  $\Delta \rightarrow 0$  of the pulse shown in Figure 2.7.

Figure 2.7: Discrete pulse

Since the Laplace transform of the Dirac Delta is 1, the transfer function of a continuous-time system is the Laplace transform of its response to an impulse with zero initial conditions. Because of the idealization implicit in the definition of an impulse, a system's dynamic behaviour is usually studied using the step response – the time behaviour of the outputs of a system when its inputs change from zero to one in a very short time.

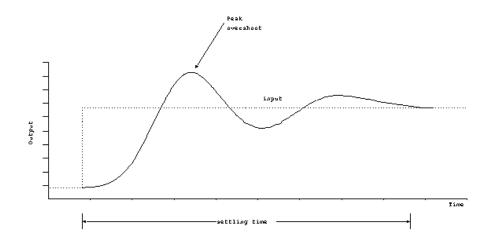

For a sample step response shown in Figure 4.3 in [4], a set of parameters describing certain properties of the system is as follows:

Steady-state value is the final value of the step response.

**Rise time** is the time elapsed up to the instant at which the step response reaches, for the first time, 90% of the final value.

**Overshoot**, expressed as a percentage of the steady-state value, is the maximum instantaneous amount by which the step response exceeds its final value.

**Undershoot** is the absolute value of the maximum instantaneous amount by which the step response falls below zero. It is also expressed as a percentage of the steady-state value.

Settling time is the time elapsed until the step response enters a specific deviation band,  $\pm \delta$ , around the final value and does not get out of the band. The deviation is defined as percentage of the steady-state value.

A control system can respond to a step input in three ways – under damped, over damped and critically damped response.

#### **Under Damped Response**

The system will change the output quickly to the new value. However, there will always be an overshoot and the output will settle into the new value after a number of oscillations. Figure 2.8 shows an under damped response.

Figure 2.8: Under damped response [33]

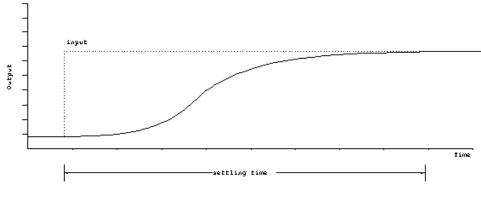

#### **Over Damped Response**

In this case, there will be no overshoot, but the response is quite slow to reach the final value, illustrated by Figure 2.9.

Figure 2.9: Over damped response [33]

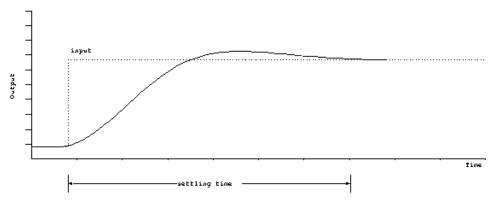

#### **Critically Damped Response**

In this case, there may or may not be any overshoot, but there will be no oscillation. Critically damped system reaches the final value in the minimum amount of time. Figure 2.10 shows a critically damped response.

Figure 2.10: Critically damped response [33]

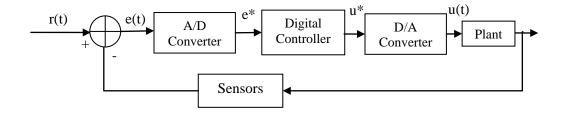

### 2.1.6 Digital Control Systems

Throughout the past few decades, modern control systems have been implemented on digital computers. Apart from the fact that the expense of a computer have gone down significantly with the advent of mass-produced microprocessors and microcontrollers, there are other contributing factors, such as, any changes or tuning are easily achieved with software, implementation is not susceptible to changes due to external conditions, data can be easily transferred to any distant location without delay, and exponential growth in the speed of the microcontrollers [2]. Digital computers work with sequences of numbers rather than continuous functions of time. Information is read and updated at discrete points in time – referred to as *sampling*. For instance, a radar tracking system provides information on an airplane's position and motion to a digital processor at discrete periods of time. When there is no such inherent sampling, an analog-to-digital (A/D) converter must be incorporated in a digital control system. The output of the controller is later converted from discrete form into an analog signal by a digital-to-analog (D/A) converter. A block diagram of a digital control system is shown in Figure 2.11.

Figure 2.11: Digital control system

The notations  $e^*$  and  $u^*$  denote that these signals are sampled at specific time intervals. The extent of the information loss due to sampling depends on the sampling method and the related parameters. If a sequence of samples is taken of a signal f(t) every  $\Delta$  seconds, then the sampling frequency needs to be large enough in comparison with the maximum rate of change of f(t). Otherwise high frequency components will be mistakenly interpreted as low frequencies in the sampled sequence, a phenomenon known as *aliasing*.

For example, let us consider a signal  $f(t) = 3\cos 2\pi t + \cos(20\pi t + \frac{\pi}{3})$ . If the sampling period  $\Delta$  is chosen to be 0.1 sec, then

$$f(k\Delta) = 3\cos(0.2k\pi) + \cos(2k\pi + \frac{\pi}{3}) = 3\cos(0.2k\pi) + 0.5$$

(2.12)

which illustrates the fact that the high frequency component has been shifted to a constant.

The output of a digital controller is another sequence of numbers, which need to be converted back to continuous time functions before they can be applied to the plant. Usually, this is done by interpolating them into a staircase.

#### 2.1.7 Z-Transform

The discrete equivalent of a differential equation is called a *difference equation*. A linear high-order difference equation is of the form [4]:

$$y[k+n] + a_{n-1}y[k+n-1] + \dots + a_0y[k] = b_{n-1}u[k+n-1] + \dots + b_0u[k]$$

(2.13)

The Z-transform is the discrete equivalent of the Laplace transform. It is used to turn the difference equations into algebraic ones. For a sequence  $\{y[k]; k = 0, 1, 2, ...\}$  the Z-transform pair is given by [4]:

$$Z[y[k]] = Y(z) = \sum_{k=0}^{\infty} z^{-k} y[k]$$

(2.14)

$$Z^{-1}[Y(z)] = y[k] = \frac{1}{2\pi j} \oint z^{k-1} Y(z) dz, \ j = \sqrt{-1}$$

(2.15)

where Z(.) indicates the Z-transform operation and  $Z^{-1}(.)$  represents the inverse Z-transform. The function Y(z) is essentially a power series in  $z^{-k}$  with coefficients equal to the values of the number sequences  $\{y(k)\}$  [6].

#### 2.1.8 Discrete Transfer Functions

If we take Z-transform on each side of the high-order difference equation (4) with zero initial condition,  $A_q(z) Y_q(z) = B_q(z) U_q(z)$ , where  $Y_q(z)$  is the Z-transform of the sequences  $\{y[k]\}$ ,  $U_q(z)$  is the Z-transform of the sequences  $\{u[k]\}$ ,  $A_q(z) = z^n$  $+ a_{n-1} z^{n-1} + ... + a_0$ , and  $B_q(z) = b_m z^m + b_{m-1} z^{m-1} + ... + b_0$ .

So,

$$Y_q(z) = G_q(z) U_q(z)$$

, where  $G_q(z) = \frac{B_q(z)}{A_q(z)}$  and  $G_q(z)$  is the discrete transfer

function. As in the continuous-time case, the transfer function uniquely determines the input-output behavior at the discrete sampling times. However, the input-output behavior at times other than the sampling instant is undefined.

#### 2.1.9 Continuous-to-Discrete Transfer Function Transformation

This transformation refers to turning the transfer function from the *s*-domain to the *z*-domain. There are different approaches to achieve this transformation, but two are most commonly used: bilinear transform and backward rule approach [36]. Tustin or bilinear transformation is a first-order approximation of the natural logarithm function that is an exact mapping of the *s*-domain to the *z*-domain. Since  $z = e^{st}$ , where *T* is the sample time or the reciprocal of the sampling frequency,

$$s = \frac{1}{T}\ln(z) = \frac{2}{T}\left[\frac{z-1}{z+1} + \frac{1}{3}\left(\frac{z-1}{z+1}\right)^3 + \frac{1}{5}\left(\frac{z-1}{z+1}\right)^5 + \dots\right] \approx \frac{2}{T}\frac{z-1}{z+1}$$

(2.16)

Thus the bilinear transform essentially uses first-order approximation and substitutes into the continuous-time transfer function as  $s \leftarrow \frac{2}{T} \frac{z-1}{z+1}$ . Bilinear transform gives a one-to-one mapping between analog frequency axis  $s = j\omega_a$  and the digital frequency axis  $z = e^{j\omega_a T}$ , where *T* is the sampling interval. Thus the amplitude response is exactly the same on both axes, while the only defect being a *frequency warping* such that equal increments along the unit circle in the *z*-plane correspond to larger and larger bandwidths along the  $j\omega$  axis in the *s*-plane [37].

The backward rule approach to continuous-to-discrete mapping stems from the definition of the derivative. The backward difference form of the derivative is [2]:

$$\frac{de}{dt} = \frac{e(t) - e(t - T)}{T}$$

(2.17)

Taking the Laplace transform, assuming all the initial conditions being zero,

$$sE(s) = \frac{E(s) - E(s)e^{-sT}}{T}$$

Or,  $s = \frac{1 - e^{-sT}}{T}$  (2.18)

Since

$$z = e^{sT}$$

,  $s = \frac{1 - z^{-1}}{T} = \frac{z - 1}{Tz}$  (2.19)

Like the bilinear transform, the backward rule approach preserves stability (discussed in the next subsection) of the system and is free of aliasing. However, backward rule approximation requires that the sampling interval be small for accurate conversion [36].

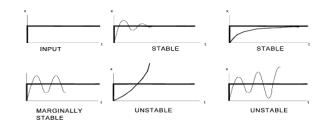

#### 2.1.10 Stability

A dynamic system is said to be *stable* if the output eventually reaches a finite steady-state value after an input or a disturbance. When the output oscillates with ever-increasing amplitude or it increases or decreases unidirectionally and without limit, the system is *unstable*. Let us consider a typical second-order system equation of the form [31]:

$$(a_2D^2 + a_1D + a_0)x = f(D)y$$

(2.20)

The transient response, and hence stability, of such system depends on the coefficients  $a_0$ ,  $a_1$  and  $a_2$ . If all the coefficients are above zero, the function will not contain any positive time exponentials and the system will be stable. However, if either  $a_1$  or  $a_2$  is less than zero, the transient response will contain positive exponentials and the system will be unstable. Figure 2.12 shows some stable and unstable responses [31].

Figure 2.12: Examples of stable and unstable responses

Routh-Hurwitz stability conditions determine whether a system is stable or unstable. Let us consider the generalized equation [31]:

$$(a_n D^n + a_{n-1} D^{n-1} + \dots + a_1 D + a_0) x = f(D) y$$

(2.21)

Assuming  $a_0$  is positive; a matrix is created of the coefficients:

| $a_1$          | a <sub>0</sub> | 0   | 0              | 0              | 0              | 0              | •              | •   | •              |

|----------------|----------------|-----|----------------|----------------|----------------|----------------|----------------|-----|----------------|

| a <sub>3</sub> | a <sub>2</sub> | a 1 | a <sub>0</sub> | 0              | 0              | 0              | •              | •   | •              |

| a 5            | a <sub>4</sub> | a 3 | a <sub>2</sub> | a <sub>1</sub> | a <sub>0</sub> | 0              | •              | •   | •              |

| a <sub>7</sub> | a <sub>6</sub> | a 5 | a <sub>4</sub> | a <sub>3</sub> | a <sub>2</sub> | a 1            | a <sub>0</sub> | •   | •              |

| a 9            | a <sub>8</sub> | a 7 | a <sub>6</sub> | a 5            | a 4            | a <sub>3</sub> | a <sub>2</sub> | a 1 | a <sub>0</sub> |

For stability of an equation of degree 4, the necessary conditions are as follows:

1.

$$a_1 > 0, a_2 > 0, a_3 > 0, a_4 > 0.$$

2.

$$\begin{bmatrix} a_1 & a_0 \\ a_3 & a_2 \end{bmatrix} > 0$$

, that is,  $a_1 a_2 - a_0 a_3 > 0$

3.

$$\begin{bmatrix} a_1 & a_0 & 0 \\ a_3 & a_2 & a_1 \\ 0 & a_4 & a_3 \end{bmatrix} > 0$$

, that is,  $(a_1(a_2a_3 - a_1a_4) - a_0(a_3a_3 - a_1.0)) > 0$

Any fourth-order equation has to meet these criteria to be stable. Note that [.] refers to the *determinant* of a square matrix.

### 2.2 Fuzzy Logic and Fuzzy Control

Fuzzy logic was originally proposed in theory by Zadeh [9][10], and implemented in automatic control by Mamdani [11][12]. Fuzzy controllers are a particular class of intelligent controllers built on fuzzy expert systems. One of the advantages of fuzzy controllers is that they do not require exact mathematical models unlike the traditional controllers, therefore making it easier to create highly nonlinear controllers in a very intuitive fashion. This property is very important for today's high-complexity and large networks where a precise mathematical model is often unavailable. A fuzzy controller tries to mimic a knowledgeable human operator by applying a collection of control rules that might be overlapping and contradictory. The fuzzifier module receives data from sensor(s) as inputs and converts it by performing a simple mapping of a numeric quantity to a fuzzy set. The rulebase is formed by a collection of logical rules depicting the relationship between the input (antecedent) and output (consequent) of the controller [25]. The approximate reasoning algorithm is implemented in the inference engine whose task is to determine the firing degree of each rule, and to produce a fuzzy output by performing a weighted composition of the consequents for each rule. Finally, a module called a defuzzifier converts the fuzzy outputs to a single crisp control signal to be sent to the process.

### 2.2.1 Basic Concepts of Fuzzy Logic

The underlying mathematical construct of fuzzy logic is a fuzzy set, which is a generalization of mathematical set theory [13]. It is a set having a characteristic function with a co-domain consisting of the unit interval [0, 1] rather than the usual discrete set  $\{0, 1\}$ , and the characteristic function is known as membership function. This allows for a gradual transition from having a certain property to not having it [14].

The concepts of fuzzy sets are highly intuitive, since they work the same way humans tend to reason. In the words of Zadeh [1]:

"Clearly the 'class of all real numbers that are much greater than 1,' or 'the class of beautiful women,' or 'the class of tall men,' do not constitute classes or sets in the usual mathematical sense of these terms."

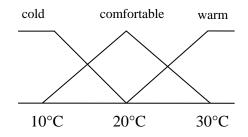

For example, let us consider a temperature of 20°C as *comfortable* [7]. In terms of mathematical set theory, anything less than 20°C would then be *not comfortable*, meaning *cold*, and anything more than 20°C would again be *not comfortable*, meaning *warm*. This makes a value of 19°C to be *cold*, which is counter-intuitive. From human perspective, it is still *quite comfortable*, which is the essence behind the idea of fuzzy sets. Likewise, the temperature value of 25°C is partially

compatible with the terms *comfortable* and *warm*, but totally incompatible with *cold*. This notion of fuzzy sets is shown in Figure 2.13, where temperature values up to 10°C are only *cold* and on or above 30°C are only *warm*. As the temperature rises from 10°C to 20°C, the degree of *cold* decreases while that of *comfortable* increases. This goes on till 20°C where degree of *comfortable* is 1 and there is no *cold*. Similarly, the degree of *warm* goes higher starting from 20°C and *comfortable* keeps going down. At 30°C, temperature is totally *warm* and not *comfortable* at all.

Figure 2.13: Notion of fuzzy sets

### **2.2.2 Membership Functions**

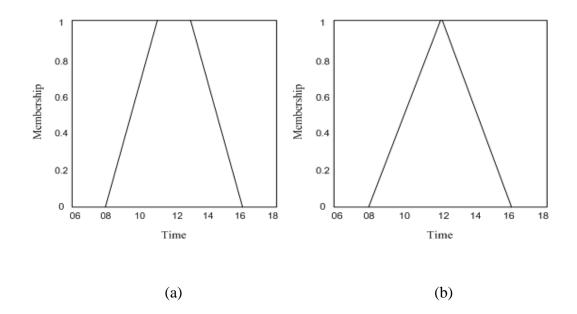

Membership functions are mappings from the universe of discourse to the unit interval [7]. There are two different ways to represent a membership function: continuous and discrete [8]. For instance, a trapezoidal membership function is a piecewise linear, continuous function, and it is based on four parameters  $\{a, b, c, d\}$  [15].

$$\mu_{Trapezoid}(x; a, b, c, d) = \begin{cases} 0, x \le a \\ \frac{x-a}{b-a}, a \le x \le b \\ 1, b \le x \le c \\ \frac{d-x}{d-c}, c \le x \le d \\ 0, d \le x \end{cases}, x \in \mathfrak{R}$$

A triangular membership function is piecewise linear, and derived from the trapezoidal membership function by setting b = c. Figure 2.14 shows the

trapezoidal and triangular membership functions representing the time 'around noon' [8].

Membership functions take many forms such as triangular, exponential, Gaussian membership functions and so on [7]. A discrete fuzzy set is defined by ordered pairs {  $(x_1, \mu(x_1)), (x_2, \mu(x_2)), \dots$  } where  $\mu(x_i)$  is an evaluation of the membership function  $\mu$  at a discrete point  $x_i$  [8].

Figure 2.14: (a) Trapezoidal and (b) triangular membership functions.

### 2.2.3 Fuzzy Set Operations

Fuzzy set operations, namely – *intersection, union* and *complement*, are defined as functions of membership values. Functions that qualify as fuzzy intersections and fuzzy unions are usually referred to in the literature as *t*-norms and *t*-conorms, respectively.

#### 2.2.3.1 Fuzzy Intersection

The intersection of two fuzzy sets A and B is defined by a binary operation on the unit interval; that is, a function of the form

$$i:[0,1] \times [0,1] \rightarrow [0,1]$$

For each element x of the universal set, this function takes as its argument the pair consisting of the element's membership grades in set A and in set B, and yield the membership grade of the element in the set constituting the intersection of A and B. Thus,

$(A \cap B)(x) = i[A(x), B(x)]$  for all  $x \in X$ .

Functions known as *t*-norms possess properties which ensure that fuzzy sets produced by i are intuitively acceptable as meaningful fuzzy intersections of any given pair of fuzzy sets [21]. Therefore, the class of *t*-norms is now generally accepted as equivalent to the class of fuzzy intersections.

A fuzzy intersection or t-norm *i* is a binary operation on the unit interval that satisfies at least the following axioms [21] for all  $a, b, d \in [0,1]$ :

Axiom I1: i(a, 1) = a (Boundary condition)

Axiom I2:  $b \le d$  implies  $i(a, b) \le i(a, d)$  (Monotonicity)

Axiom I3: i(a, b) = i(b, a) (Commutativity)

Axiom I4: i(a, i(b, d)) = i(i(a, b), d) (Associativity)

Axiom I5: *i* is a continuous function (Continuity)

Axiom I6:  $i(a, a) \le a$  (Subidempotency)

The following are some examples of *t*-norms used as fuzzy intersections:

Standard Intersection:  $\mu_{A \cap B} = \min(\mu_A, \mu_B)$

Algebraic Product:  $\mu_{A \cap B} = \mu_A * \mu_B$

Bounded Difference:  $\mu_{A \cap B} = \max(0, \mu_A + \mu_B - 1)$

Drastic Intersection:  $\mu_{A \cap B} = \mu_A$  when  $\mu_B = 1$

$\mu_B$  when  $\mu_A = 1$

### 0 otherwise

#### 2.2.3.2 Fuzzy Union

The general fuzzy union of two fuzzy sets A and B is specified by a function

```

u:[0,1] \times [0,1] \to [0,1]

```

The function returns the membership grade of the element in the set  $A \cup B$ . Thus,

$(A \cup B)(x) = u[A(x), B(x)]$  for all  $x \in X$ .

The properties of functions known as t-conorms are exactly the same as those of a function u that is acceptable as a fuzzy union; therefore, t-conorms and fuzzy unions are used interchangeably.

A fuzzy union or *t*-conorm *u* is a binary operation on the unit interval that satisfies at least the following axioms for all  $a, b, d \in [0,1]$ :

Axiom U1: u(a, 0) = a (boundary condition)

Axiom U2:  $b \le d$  implies  $u(a, b) \le u(a, d)$  (monotonicity)

Axiom U3: u(a, b) = u(b, a) (Commutativity)

Axiom U4: u(a, u(b, d)) = u(u(a, b), d) (Associativity)

Axiom U5: *u* is a continuous function (Continuity)

Axiom U6:  $u(a, a) \ge a$  (Superidempotency)

Axiom U7:  $a_1 < a_2$  and  $b_1 < b_2$  implies  $u(a_1, b_1) < u(a_2, b_2)$  (Strict monotonicity)

Some examples of *t*-conorms used as fuzzy unions are given below:

Standard Union:  $\mu_{A\cup B} = \max(\mu_A, \mu_B)$ Algebraic Sum:  $\mu_{A\cup B} = \mu_A + \mu_B - \mu_A \mu_B$

Bounded Sum:  $\mu_{A\cup B} = \min(1, \mu_A + \mu_B)$

Drastic Union:  $\mu_{A \cup B} = \mu_A$  when  $\mu_B = 0$

$\mu_B$  when  $\mu_A = 0$

1 otherwise

### 2.2.3.3 Fuzzy Complement

Let *A* be a fuzzy set on *X*. Therefore, A(x) is interpreted as *the degree to which x belongs to A*. Let *cA* be a fuzzy *complement* of *A*. Then, cA(x) may be interpreted not only as the degree to which *x* belongs to *cA*, but also as *the degree to which x does not belong to A*.

Let a complement *cA* be defined by a function  $c:[0,1] \rightarrow [0,1]$  which assigns a value c(A(x)) to each membership grade A(x) of any given fuzzy set *A*. The value c(A(x)) is interpreted as the value of cA(x). Given a fuzzy set *A*, we obtain *cA* by applying function *c* to values A(x) for all  $x \in X$ .

To produce meaningful fuzzy complements, function c must satisfy at least the following two axioms:

Axiom C1: c(0) = 1 and c(1) = 0 (Boundary condition)

Axiom C2: For all  $a, b \in [0, 1]$ , if  $a \le b$ , then  $c(a) \ge c(b)$  (Monotonicity)

The complement of a fuzzy set *A* with membership function  $\mu_A$  usually corresponds to the connective NOT, and has the membership function

$\mu_{\overline{A}} = 1 - \mu_A.$

### 2.2.4 Fuzzy Logic

The 'truth' or 'falsehood' assigned to a proposition is its truth-value [8]. For twovalued logic, truth-values can only be either 0 (false) or 1 (true). Fuzzy logic is an extension of the range of truth-values to the continuous interval [0, 1] of real numbers [16]. In mathematics, the word 'and' is used to join two sentences to form the *conjunction* of the two sentences. The word 'or' is used to form the *disjunction* of two sentences. From two sentences, we may construct one, of the form 'If...then...', called an *implication*. The sentence following 'If' is the *antecedent*, and the sentence following 'then' is the *consequent*. A sentence that is modified by the word 'not' is called the *negation* of the original sentence. The words 'and', 'or', 'If-then' are called *connectives*.

Fuzzy logic connectives are defined similarly. If p is a fuzzy set, negation is defined as set complement, that is,

$$\neg p = 1 - p$$

Disjunction is defined as set union, that is, for fuzzy sets p and q

$$p \lor q \equiv \max(p,q)$$

Conjunction is defined as set intersection, that is, for sets p and q

$$p \wedge q \equiv \min(p,q)$$

*Rules of inference* specify conclusions drawn from assertions known or assumed to be true. One such rule of inference is *modus ponens*. It is often presented in the form of an argument:

$$P => Q$$

$$----$$

$$Q$$

It means, if *P* is known to be true, and we assume that  $P \Rightarrow Q$  is true, then *Q* must be true. The assertion *P* is the *premise*, the assertion  $P \Rightarrow Q$  is the *implication*, and the last assertion is the *conclusion*.

Modus ponens generalized to fuzzy logic is the core of fuzzy reasoning. Let us consider the argument [8]:

A'  $A \Longrightarrow B$  ----- B'

It is similar to modus ponens, but the premise A' is slightly different from A and thus the conclusion B' is slightly different from B. For example [100],

This tomato is very red If a tomato is red, then the tomato is ripe

This tomato is very ripe

This is generalized modus ponens.

A fuzzy rule has the form: 'If x is A then y is B', in which A and B are fuzzy sets. This is an implication where 'x is A' is the antecedent and 'y is B' is the consequent.

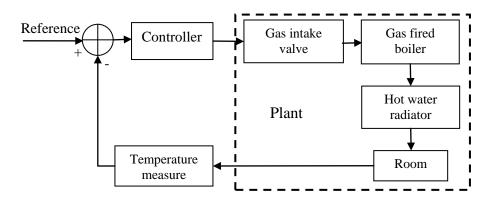

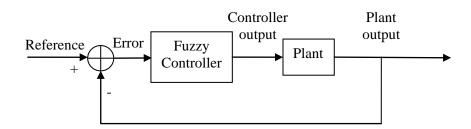

# 2.2.5 Fuzzy Controller

A fuzzy control system has a similar architecture to a conventional feedback control system. Figure 2.15 shows a fuzzy controller.

Figure 2.15: Fuzzy control system [8]

The difference between a fuzzy controller and its conventional counterpart lies in the control strategy. While the traditional system applies mathematical models using differential equations to calculate the controller output, a fuzzy controller processes the inputs based on rules expressed in a more or less natural language. The advantage of using rule-based fuzzy controller stems from the fact that mathematical models of many control processes may not exist, or may be mathematically intractable [17].

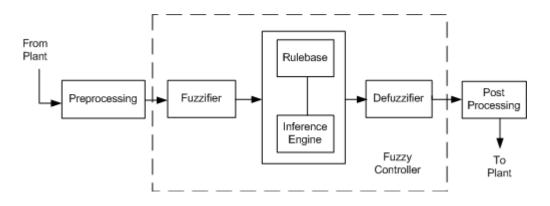

### 2.2.6 Components of Fuzzy Controller

Figure 2.16: Fuzzy controller block diagram [8]

Figure 2.16 shows the general structure of a fuzzy controller. The preprocessor prepares usable data for further processing from measured inputs by the measuring device. Preprocessing may involve quantization in connection with sampling or rounding to integers, normalization or scaling, filtering to eliminate noise, averaging to obtain tendencies, and so on [8].

### 2.2.6.1 Fuzzifier Unit

The fuzzifier module calculates the membership grades, expressed in real numbers, from the membership functions. It evaluates the input measurements according to the premises of the rules. Each premise produces a membership grade expressing the degree of fulfillment of the premise. A lookup table [18] usually contains the membership values for all possible numerical inputs. This approach, albeit requiring more memory space, can be much faster than calculating the membership values in real-time [19].

### 2.2.6.2 Rule Base Unit

Three distinct variants of the fuzzy rule base have evolved so far – Mamdani, TSK or Sugeno and Tsukamoto rule bases. They use the same general inference scheme, but differ with respect to the conclusion membership functions.

Mamdani rule base uses fuzzy sets as consequents; therefore Mamdani controllers are computationally more expensive, although the implementation is more intuitive and well suited to human inputs. TSK or Sugeno rule base replaces the consequents of Mamdani model with a polynomial equation (usually either a  $0^{th}$  or  $1^{st}$  degree polynomial) of the (non-fuzzified) input variables. The rules take the following form:

If x is A and y is B then z = f(x, y)

where *A* and *B* are fuzzy sets in the antecedent and z = f(x, y) is a crisp polynomial function in the consequent. For a zero-order Sugeno model, *z* is a constant. It is computationally efficient, works well with linear techniques, has guaranteed continuity of the output surface and well suited to mathematical analysis.

In the Tsukamoto rule base, the consequents are represented by fuzzy sets with monotonic membership functions. The rules take the form:

If x is A and y is B then

$$z = p^*x + q^*y + r$$

Scalar values are often used as consequents in practical fuzzy controllers, referred as *singleton consequents*. Some of the benefits of using singleton consequents are simpler calculations, possibility of setting extreme values for the control signal and so on [8].

### 2.2.6.3 Inference Engine Unit

For each rule, the inference engine looks up the membership value where each input intersects a membership function. The *firing strength*  $\alpha_i$  of a rule *i* is the degree of fulfilment of the rule premise. Rule *i* causes a fuzzy membership value corresponding to each input, which are aggregated using the 'and' or 'or' connective. The *activation* of a rule is the derivation of a conclusion depending on

the firing strength. Minimum or multiplication is used as the *activation operator* to activate a portion of each singleton consequent. If consequents are fuzzy sets as in the Mamdani controller, multiplication scales the membership curves while minimum clips them. However, for singletons, both operators result the same. All activated conclusions are *accumulated* using maximum or summation operator. The conclusions may contain several control actions.

### 2.2.6.4 Defuzzification Unit

The resulting fuzzy set from the inference engine has to be converted in the *defuzzifier* to a single number to form a control signal to the plant. There are dozens of defuzzification schemes, such as Center of Gravity (COG), Mean of Maxima (MOM), Bisector of Area (BOA) and so on [20], [90], [93], [96]. The crisp control value  $u_{COG}$  is the abscissa of the center of gravity of the fuzzy set. For singleton consequents, it takes the following form:

$$u_{COGS} = \frac{\sum_{i} y_i w_i}{\sum_{i} y_i}$$

(2.22)

Where  $y_i$  is the firing strength of each rule, and  $w_i$  is the consequent output. The term COGS stands for Center of Gravity for Singletons [8]. For fuzzy sets in the consequents, summations are replaced by integrals. It is a widely used method, but it is also computationally expensive.

The Bisector of Area (BOA) method finds the abscissa x of the vertical line that partitions the area under the membership function into two areas of equal size. For singleton consequents,  $u_{BOA}$  is the abscissa that minimizes

$$\left| \sum_{i=1}^{j} \mu_{c}(x_{i}) - \sum_{i=j+1}^{i_{\max}} \mu_{c}(x_{i}) \right|, \quad 1 < j < i_{\max}$$

(2.23)

Here  $i_{\text{max}}$  is the index of the largest abscissa  $x_{i_{\text{max}}}$ . Its computational complexity is also relatively high.

Another approach is to choose the point of the universe with the highest membership. Mean of maxima (MOM) is taken among several such points.

$$u_{MOM} = \frac{\sum_{i \in I} x_i}{I}, I = \{i \mid \mu_c(x_i) = \mu_{\max}\}$$

(2.24)

Where *I* is the crisp set of indices *I* where  $\mu_c(x_i)$  reaches its maximum  $\mu_{max}$ , and |I| is the number of members of the set. Although this method is not concerned about the shape of the fuzzy set, computationally it is faster.

# 2.3 Hardware Implementations of Fuzzy Controllers

Although software-based [55], approaches [56] on general-purpose microprocessors are the most flexible and economical in developing fuzzy controllers, and satisfactory results have also been obtained in the industrial areas [54]; existing software fuzzy implementations result in slow operational speed due to the fact that general-purpose computers do not have hardware computational units to implement fuzzy operations directly, making it inadequate for the high-speed processing requirement of real-time control problems [53], [58]. Therefore massive research activities on dedicated fuzzy hardware implementation manipulating both analog and digital approaches have been going on since the 1980s. Analog systems have been preferred where power consumption and resource usage are the main design criteria; whereas precision and compatibility issues favor the digital technology [23]. A fuzzy controller having a processing speed of 10 MFLIPS and developed by OMRON Corporation is considered a basic performance standard [24], although proposed prototypes in the literature have speeds up to 40 to 50 MFLIPS [25].

### **2.3.1 Analog Implementations**

Implementation of analog fuzzy controllers began with the work of Yamakawa and Miki [26] in 1986. They developed nine basic fuzzy logic circuits in current mode, containing the realization of functions, such as bounded difference, fuzzy complement, fuzzy logic union (MAX), bounded sum, fuzzy logic intersection (MIN), implication, and so on.

Although current-mode circuits are not exceedingly sensitive to changes in supply voltages, the fan-out number is limited [27], meaning that problems would arise when the inputs must be distributed to many operational blocks, a usual scenario for fuzzy rule base implementation. To overcome this issue, a tunable voltage-input current-output membership function circuit is presented in [27] using 3.5  $\mu$ m CMOS design rules based on the fact that voltage inputs can be easily distributed to many rule blocks.

N-input MIN/MAX circuits are used in the inference engine of a fuzzy controller. A current-mode multi-input MAX circuit is proposed by Baturone *et al.* in [32] and [35]. The MAX circuit also performs the MIN operation using De Morgan's law. It uses 3n + 1 transistors while achieving the same level of precision with less area and power consumption compared to 5n + 1 transistors in [28]. The MAX/MIN circuit design in [30] follows the similar structure as in [29], but it only requires n + 4 MOS transistors, which is an improvement over other implementations.

A current-mode defuzzification circuit based on the square-law MOS characteristic is described in [34] providing high linearity and large dynamic range. A square-root circuit is cascaded with a squarer circuit to implement the multiplier block. Addition is realized by wiring the outputs of the multiplier blocks together. As the use of this circuit is limited to current-mode only, a voltage-to-current (V-I) and current-to-voltage (I-V) conversions might be needed. The division in defuzzification is avoided in [28] by a Normalized Locked Loop (NLL). The denominator in the COG equation is made constant with a negative feedback loop, so it becomes a weighted sum operation instead of weighted average. The maximum simulated error is reported to be within 0.4% of the full scale current. A simple current-input voltage-output continuous-time divider circuit is implemented in [35] using a variable transresistance technique, where a resistance value is controlled by a current. It offers larger dynamic range

compared to the approach in [34] and high-frequency operation. The defuzzifier in [40] is implemented by a multiplier, a divider, three integrators, an I-V converter, an attenuator and a division control unit. To avoid the nonlinearity of the multiplier for signals greater than 0.5-V, the attenuator is used. An I-V converter is needed because the multiplier block is based on a voltage-mode integrator. A division control unit gets rid of very small signals to be applied to the denominator.

Programmable analog fuzzy chips have also been developed over the last couple of decades. Continuous, fuzzy, and multi-valued logic circuits are realized using a general-purpose Field Programmable Analog Array (FPAA) in [43]. The FPAA is based on an array of current-mode processing cells, operates from  $\pm 3.3$  V or  $\pm 5$  V power supplies, and works with frequencies up to several hundred MHz. In [44], a similar field programmable analog fuzzy processor is proposed supporting fifteen rules, three inputs and one output. The architecture is split into an analog core and a digital part allowing field programmability. The digital segment relies on a software tool to compute the programming values. The chip area is 32 mm<sup>2</sup> using a CMOS 0.7-µm n-well technology with the analog core occupying only 7%. The settling time for a step response is reported to be < 0.6 µs.

Miki and Yamakawa [46] proposed an analog fuzzy processor with an inference engine of over 1 MFLIPS excluding defuzzification. To have a flexible system configuration, inferences and defuzzification are handled by two separate chips. The executed rule can be changed dynamically from one rule set to the other stored in the on-chip rule memory. The chip in [47] occupies an area of 17.9 mm<sup>2</sup> and processes up to 131072 rules, 4096 inputs and 1024 outputs with different membership functions. Fuzzification of four 12-bit inputs, inference of 80 rules, and COG defuzzification for a 16-bit output takes 16  $\mu$ s, translating to a processing speed of 62.5 KFLIPS. Baturone *et al.* [48] designed general-purpose fuzzy chips allowing fully-parallel analog rule processing and optimized digital circuitry for programmability. The analog core of a two-input processor occupies a silicon area of 1 mm<sup>2</sup> and the response time is less than 2  $\mu$ s. Although analog implementations have features such as lower power consumption [23], and not having the requirement of analog-to-digital (A/D) or digital-toanalog (D/A) converters to communicate with sensors and actuators, they suffer from poor flexibility, less precision due to noise, distortion, interferences and parameter mismatch [57], and compatibility issues with other digital systems [52].

### **2.3.2 Digital Implementations**

There are many different ways to implement fuzzy control systems in digital hardware. One approach is the use of general-purpose processors with a number of instructions dedicated to fuzzy operations. While this method [85], [86] provides features such as flexibility and automatic support of non-fuzzy computations, performance is limited [84]. A better approach in terms of speed is special-purpose processors designed only for fuzzy operations [87], [88]. However, they have poor flexibility and cannot be used as stand-alone processors to implement the control system. Most of the studies so far, therefore, have dealt with dedicated hardware tailored to a particular fuzzy application [64]. Although this scheme is not flexible at all, the advantages include very fast processing capability required for real-time systems, low cost in terms of resources, and so on [84].

Togai and Watanabe [59] [60] were the first to implement fuzzy systems in digital hardware in the mid 1980s. They developed a VLSI chip, fabricated in 2.5- $\mu$ m CMOS technology, to perform the fuzzy inference process. The rulebase is stored in Read-Only Memory (ROM) because of its faster operation and less area requirement compared to the Random Access Memory (RAM). The degree of membership functions is represented by 4 bits, so 16 discrete levels are permitted. Two circuits with serial processing capabilities are used to implement MAX and MIN operations. The chip was first demonstrated at AT&T Bell lab. It operates on a 20.8 MHz clock with a processing speed of 80 KFLIPS.

The second generation of a 1- $\mu$ m CMOS VLSI chip has been designed by Watanabe *et al.* [61] in the early 1990s. The chip consists of 688,000 transistors out of which 476,000 are used for RAM memory. Either 51 rules with 4 inputs

and 2 outputs, or 102 rules with 2 inputs and 1 output can be implemented at a speed of over 150 KFLIPS. The universe of discourse of a fuzzy set is divided into 64 elements each being a 4-bit number, therefore occupying 256 bits of memory for fuzzification table lookup. Instead of dedicating 256 bits for each fuzzy set, the membership functions for all fuzzy sets are stored in one memory area in [63]. The representations of the membership functions for each fuzzy set are overlapped. The effectiveness of this approach depends on the overlap factor of the fuzzy sets. For a factor of 2, it only requires half of the memory space compared to that of [61]. To speed up the inference process, the defuzzification operations are pre-computed and partial results are stored for runtime access. To save memory, a different way to implement membership functions is described in [62]. It makes use of three memory spaces to store the fuzzification information. Each fuzzy set is assigned a 3-bit number in the first space; the other two spaces keep track of the values that the membership functions possess for any pair of active fuzzy sets for a particular input.

A custom designed hardware fuzzy logic controller with on-line adaptability is described in [65], [66]. Look-up tables are used for fuzzification with 4-bit resolution. To avoid division in defuzzification, all possible division outputs are pre-calculated and stored in a look-up table with concatenated numerator and denominator values being used as addresses to access the table contents. To facilitate on-line adaptation, six extra SRAMs (Static Random Access Memory) are used to store input membership functions along with 6 others for normal operations. A fully pipelined version can obtain a speed up to 9 MFLIPS. A similar design approach [58] achieves 3.3 MFLIPS operational speed, while a multilevel systolic approach [67] goes up to 10 MFLIPS with the use of 30,000 gates and 3 KB memory. An adaptive fuzzy controller oriented to ASICs is presented in [75]. Adaptation algorithm works by updating the parameters of membership functions and rules based on new input data. During each cycle, the rules with more firing strength are reinforced while others are ignored depending on the degree of their strength. The circuit is fabricated in 0.7 µm CMOS technology with 35,000 gates.

A general-purpose hardware system called KAFA (KAist Fuzzy Accelerator) to provide various fuzzy inference methods and fuzzy set operations is presented in [54], [69]. Fuzzy Processing Elements (FPEs) are separate from the main controller. Each FPE is connected to its next neighbor, while the first and last ones are connected to the main controller to form a ring topology. The first prototype of KAFA is implemented on an FPGA with 128 FPE's. An FPE unit consists of a Fuzzy Arithmetic Logic Unit (FALU), a memory space to store 8-bit membership values, a register file containing nine registers and a communication With 11 basic instructions, FALU implements 8 fuzzy set operations, link. namely - logical product, logical sum, algebraic product, algebraic sum, bounded product, bounded sum, drastic product and drastic sum. KAFA also provides 3 defuzzification methods - maximum criterion, mean-of-maxima, and modified center of area – with the first two dealing with the problem of finding the FPE containing the largest membership value in a list of FPEs. A similar hardware board named Future Board [72], [73] to process fuzzy set operations is proposed by Tokunaga. It consists of 4 fuzzy set processors (FSPs) to concurrently execute four streams of fuzzy operations on 8-bit data. Lee and Bien [74] developed a flexible fuzzy control system called FLEXi. For 8 inputs, 4 outputs and 256 rules with 16 MHz clock, it operates approximately at 20 KFLIPS.

Sánchez-Solano *et al.* [70] described two programmable fuzzy controllers that provide low resource usage and relatively high operational speed by adopting some restrictions on the degree of overlapping of antecedent membership functions and by using simplified defuzzification methods employing singleton consequents. Inference time is reduced by identifying active rules [71] defined as such rules for which all the antecedent membership grades are non-zero. The prototypes are implemented in a 1- $\mu$ m CMOS technology, and they consist of 3 inputs and 1 output using 8 membership functions with an overlapping degree of 2. A memory space of 64 x 15 bits is used for membership functions of each input. They achieve an inference speed of 3 MFLIPS.

Ascia *et al.* [79] presented a VLSI fuzzy processor with 3 inputs, 1 output and 32 rules, which achieved 5.2 MFLIPS for a clock frequency of 66 MHz. A fuzzy processor [80] with four 7-bit inputs, one 7-bit output, 7 input membership functions, 8 output membership functions and 127 rules is implemented in 1  $\mu$ m CMOS technology. It is used in a trigger system in High Energy Physics Experiments, and has a speed of 50 MFLIPS. It uses the active rule selector approach presented in [71].

An asynchronous computational approach to the hardware design of a fuzzy controller is described in [68]. The controller is designed as a large asynchronous pipeline in which most of the hardwired delays are replaced by self-timed combinational logic controlled by handshaking signals rather than a global clock. This scheme is useful for low-power embedded applications.

Due to the significant advances in the digital field during the last few decades, digital approach for fuzzy hardware realization is now easier to design, more precise, and more flexible in comparison to analog implementation [58].

### **2.3.3 Fast Defuzzification**

Defuzzification has always been a bottleneck for faster implementation of fuzzy systems. Therefore a number of techniques have been proposed in the literature to avoid computationally expensive multiplication and division operations. In [89], a heuristic approach based on adapting any fuzzy output shape into one single triangle and estimating the centroid position is presented. The processing time for this approach is reported to be 23 times less than that for COG defuzzification. Runkler and Glesner [92] proposed a centroid approximation algorithm (CADE) to decrease the computation cost for defuzzification. Further reduction in computation is achieved by another algorithm (DECADE) which avoids multiplication and division operations involved in the previous method. The maximum error is reported to be about 7% for DECADE.

Eisele *et al.* [91] presented a fast defuzzification method for hardware implementation of fuzzy inference algorithms. This approach optimizes the COG