National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

## NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effect has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1 A 0N4

The author has granted an irrevocable nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-55527-0

#### THE UNIVERSITY OF ALBERTA

# A HIGH ACCURACY DIGITAL SAMPLING WATTMETER FOR DISTORTED AND VARYING FREQUENCY SIGNALS

by

#### DAVID JECTY NYARKO

#### A THESIS

SUBMITTED TO THE FACULTY OF GRADUATE STUDIES AND RESEARCH

IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE

OF MASTER OF SCIENCE

DEPARTMENT OF ELECTRICAL ENGINEERING

EDMONTON, ALBERTA

FALL 1989

#### THE UNIVERSITY OF ALBERTA

#### RELEASE FORM

NAME OF AUTHOR: DAVID JECTY NYARKO

TITLE OF THESIS: A HIGH ACCURACY DIGITAL

SAMPLING WATTMETER FOR

DISTORTED AND VARYING

FREQUENCY SIGNALS

DEGREE: MASTER OF SCIENCE

YEAR THIS DEGREE GRANTED: FALL, 1989

Permission is hereby granted to THE UNIVERSITY OF ALBERTA LIBRARY to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly or scientific research purposes only.

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.

······

(Student's signature)

Student's permanent address:

2B 8916 - 112 Street

EDMONTON, ALBERTA

T6G 2C5

Date: 31st August 1989

# THE UNIVERSITY OF ALBERTA FACULTY OF GRADUATE STUDIES AND RESEARCH

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies and Research for acceptance, a thesis entitled A HIGH ACCURACY DIGITAL SAMPLING WATTMETER FOR DISTORTED AND VARYING FREQUENCY SIGNALS submitted by DAVID JECTY NYARKO in partial fulfilment of the requirements for the degree of MASTER OF SCIENCE IN ELECTRICAL ENGINEERING.

. Kill a Stermence.....

(Supervisor)

Satr C Swinson

Date: . 11. Aug. 1989 ....

#### **ABSTRACT**

This thesis describes an approach to the implementation of digital sampling wattmeters. A numerical integration algorithm employing a trapezoidal rule with an end correction, is shown to considerably improve the accuracy of such instruments. This results in a more precise measurement of distorted and varying frequency waveforms. This approach is employed in the design of a digital sampling wattmeter design primarily intended for power system measurements.

The stand-alone system based on an 8Mhz 68000 microprocessor system, is capable of measuring distorted power signals with a fundamental frequency from dc to 1khz. Auxiliary functions in this GPIB compatible and keypad programmable instrument include voltage, current, power factor and frequency measurements in various modes.

#### **ACKNOWLEDGEMENT**

I would like to thank my sponsors, the Association of Universities and Colleges of Canada, for their financial support for my MSc. program. I would also like to thank my supervisor, Dr. Keith Stromsmoe, for his help and encouragement in preparing this thesis.

# TABLE OF CONTENTS

| ABST | RAC' | r        | • •  |      | •   | •    |      | •   | •   | •  | •  | •   | •   | •   | •  | •  | •  | •  | •  | i   |

|------|------|----------|------|------|-----|------|------|-----|-----|----|----|-----|-----|-----|----|----|----|----|----|-----|

| ACKN | OWL  | EDGEMENT | •    |      | •   | •    |      | •   | •   | •  | •  | •   | •   | •   | •  | •  | •  | •  |    | V   |

| LIST | OF   | FIGURES  | •    |      | •   | •    |      | •   | •   | •  | •  | •   | •   | •   | •  | •  | •  | •  | •  | >   |

| LIST | OF   | SYMBOLS  | •    |      |     | •    |      |     | •   | •  | •  | •   | •   | •   | •  | •  |    |    | •  | xiv |

| 1.   | I    | TRODUCT  | ON   |      | •   | •    |      | •   | •   | •  | •  |     |     | •   | •  | •  | n  | •  | •  | 1   |

| 2.   | ТН   | EORY .   |      |      | •   | •    |      | •   |     | •  | •  | •   |     |     |    |    | •  | •  | •  | 3   |

|      | 2.1  | Analy    | sis  | of   | sa  | ımp. | led  | wa  | ve  | fo | rm | s   |     | •   |    |    | •  | •  | •  | 5   |

|      | 2.2  | Error    | Det  | eri  | nir | at:  | ion  | •   | •   |    | •  | •   |     |     |    |    |    |    |    | 6   |

|      | 2.3  | Err      | or   | ехр  | res | ssi  | ons  | f   | or  | v  | ar | ic  | us  |     | pr | oc | es | si | ng |     |

|      |      | method   | s    |      |     | •    |      | •   |     |    |    |     |     |     |    |    | •  |    |    | 8   |

|      |      | 2.3.1    | Ave  | eraç | је  | of   | san  | npl | es  |    |    |     |     |     |    |    |    |    |    | 10  |

|      |      | 2.3.2    | Tra  | pez  | zoi | .da] | l Ru | ıle |     |    |    |     |     | •   |    |    |    |    |    | 12  |

|      |      | 2.3.3    | NBS  | aŗ   | ppr | oac  | ch   |     |     |    |    |     |     |     |    |    |    | •  |    | 14  |

|      |      | 2.3.4    | Mod  | lifi | ied | Т    | ape  | ezo | ida | al | Ap | gg  | roa | ac. | h  |    |    | •  |    | 15  |

|      | 2.4  | Deter    | mina | tic  | on  | of   | del  | lta |     | •  |    |     |     |     | •  |    |    |    |    | 17  |

|      | 2.5  | Compu    | tati | .on  | of  | tr   | ne d | les | ir  | ed | pa | ara | ame | et. | er | s  |    |    |    | 18  |

|      | 2.6  | Summa    | ry c | of r | :es | ult  | s    |     |     |    |    |     |     |     |    |    |    |    | _  | 20  |

| 3. | DIC | ITAL SAMPLING WATTMETER HARDWARE                                                                                                               | 5 |

|----|-----|------------------------------------------------------------------------------------------------------------------------------------------------|---|

|    | 3.1 | CPU module                                                                                                                                     | 5 |

|    |     | 3.1.1 Microprocessor circuitry 3                                                                                                               | 6 |

|    |     | 3.1.2 Memory circuitry                                                                                                                         | 7 |

|    |     | 3.1.3 Interrupt and Watchdog timer                                                                                                             |   |

|    |     | circuitry                                                                                                                                      | 7 |

|    | 3.2 | I/O module                                                                                                                                     | 8 |

|    | 3.3 | Timing Controller module                                                                                                                       | 0 |

|    | 3.4 | Analog-to-Digital interface module 4                                                                                                           | 2 |

|    | 3.5 | Input-conditioning circuitry 4                                                                                                                 | 3 |

|    |     | 3.5.1 Phase 1 circuitry                                                                                                                        | 3 |

|    |     | 3.5.2 Phase 2 circuitry                                                                                                                        | 4 |

|    |     | 3.5.3 Analog switches circuitry 4                                                                                                              | 4 |

|    |     | 3.5.4 Trigger circuitry 4                                                                                                                      | 5 |

|    |     |                                                                                                                                                |   |

| 4. | DIG | ITAL SAMPLING WATTMETER SOFTWARE 5                                                                                                             | 9 |

|    | 4.1 | Software Overview                                                                                                                              | 9 |

|    | 4.2 | Initialization and Memory test 9                                                                                                               | 9 |

|    | 4.3 | The main program 6                                                                                                                             | 1 |

|    |     | 4.3.2 Command preprocessor $\dots \dots \dots$ | 1 |

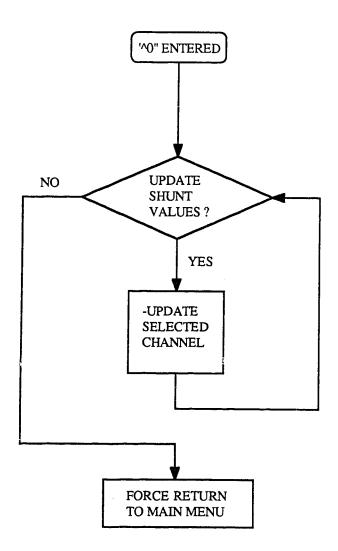

|    |     | 4.3.3 Module 0 6                                                                                                                               | 3 |

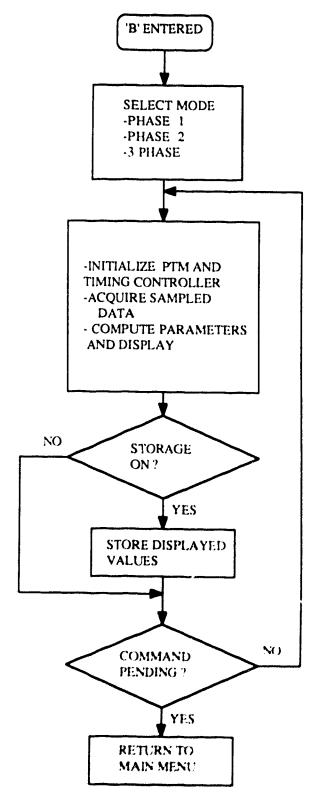

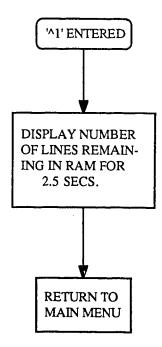

|    |     | 4.3.4 Module 1 6                                                                                                                               | 3 |

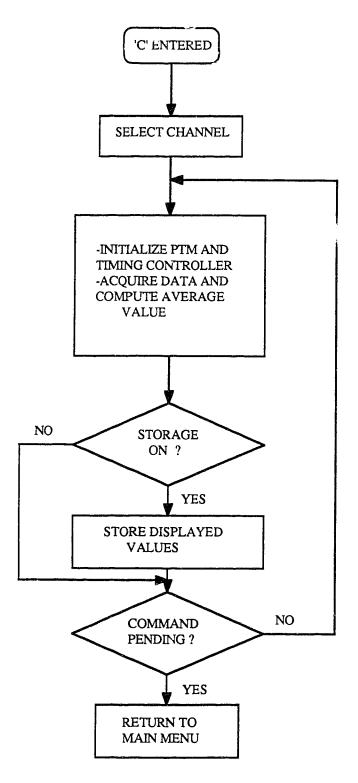

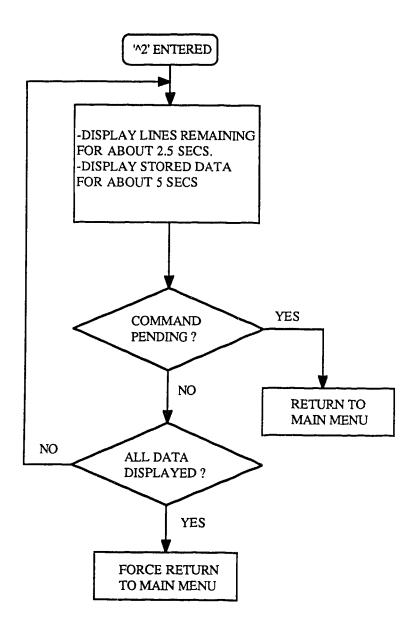

|    |     | 4.3.5 Module 2 6                                                                                                                               | 3 |

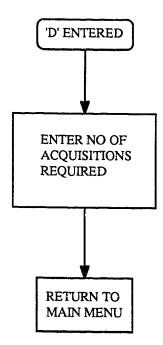

|    |     | 4.3.6 Module 3                                                                                                                                 | 4 |

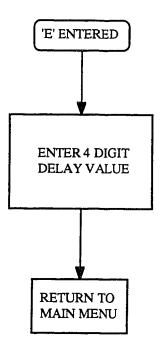

|    |     | 4.3.7 Module 4                                                                                                                                 | 4 |

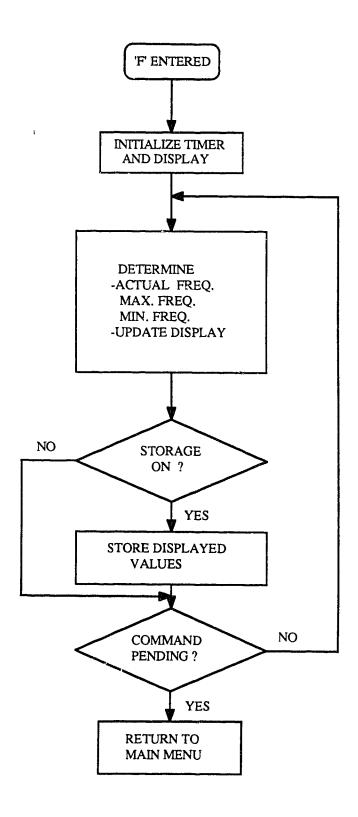

| 4.3.8  | Module   | 5   | • | • | , | • | • | •   | •   | •   | •   | •   | • | • |   |   | • | 65  |

|--------|----------|-----|---|---|---|---|---|-----|-----|-----|-----|-----|---|---|---|---|---|-----|

| 4.3.9  | Module   | 6   | • | • |   | • | • | •   | •   |     |     | •   | • |   |   | • | • | 66  |

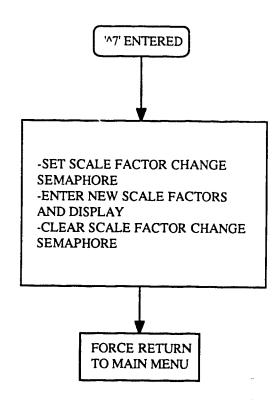

| 4.3.10 | Module   | ∍ 7 | • | • | • |   | • |     | •   |     | •   |     |   |   |   |   |   | 66  |

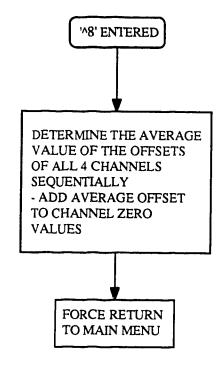

| 4.3.11 | Module   | 8 = | • |   | • | • | • | •   | •   |     | •   | • • |   | • |   |   | • | 67  |

| 4.3.12 | Module   | 9   |   | • | • | • |   |     | •   |     | • , |     | • | • |   |   |   | 67  |

| 4.3.13 | Module   | 10  |   |   | • | • | , | •   | •   | •   | • • |     |   |   | • |   |   | 68  |

| 4.3.14 | Module   | 11  |   |   | • | • | , | •   |     | • • |     | •   |   | • | • |   |   | 69  |

| 4.3.15 | Module   | 12  |   | • | • | • | • | , , | • . | • • | •   |     |   |   |   | • |   | 70  |

| 4.3.16 | Module   | 13  |   |   | • |   | • |     |     |     | •   | •   |   |   | • | • |   | 71  |

| 4.3.17 | Module   | 14  |   |   | • | • | • |     | •   |     | •   |     |   |   |   | • |   | 71  |

| 4.3.18 | Module   | 15  |   | • | • | • | • |     |     | •   |     |     | • |   |   |   |   | 72  |

| 4.3.19 | Module   | 16  |   | • | • | • | • | •   |     |     | •   | •   |   |   |   | • |   | 72  |

| 4.3.20 | Module   | 17  |   | • | • |   | • | •   | •   | •   | •   |     |   |   | • |   |   | 73  |

| 4.3.21 | Module   | 18  |   | • | • | • | • | •   | •   | •   | •   | •   |   |   | • |   |   | 73  |

| 4.3.22 | Module   | 19  |   | • | • | • | • | •   | •   |     | •   | •   |   |   |   |   |   | 74  |

| 4.3.23 | Module   | 20  |   | • | • | • | • | •   | •   |     | •   | •   |   |   |   |   |   | 74  |

| 4.3.24 | Module   | 21  | , | • | • | • | • | •   |     | •   | •   | •   | • | • | • |   | • | 75  |

| 4.3.25 | Module   | 22  |   | • |   | • | • | •   | •   | •   | •   |     |   |   | • |   |   | 75  |

| 4.3.26 | Module   | 23  | • | , | • |   | • | •   | •   |     | •   |     |   | • |   |   |   | 75  |

| 4.3.27 | Module   | 24  | • |   | • | • | • | •   |     | •   |     | •   |   | • | • |   | • | 76  |

| 4.3.28 | Module   | 25  | • |   | • |   | • | •   | •   | •   | •   |     |   |   | • | , |   | 76  |

| 4.3.29 | Module   | 26  | • |   | • |   | • | ٠   | •   |     |     |     |   | • | • |   | , | 77  |

| 4.3.30 | Module   | 27  | • |   | • | • | • | •   | •   |     | •   | •   | • | • |   |   |   | 77  |

| 4.3.31 | Module   | 28  | • | • | • | • | • | •   |     | •   | •   |     | • | • |   |   |   | 77  |

| 1.3.32 | Module : | 29  | _ |   |   |   |   |     |     |     |     |     |   |   |   |   |   | 7.0 |

| 5.   | SYSI   | TEM ROUTINES                                    | 0 8 |

|------|--------|-------------------------------------------------|-----|

|      | 5.1    | Acquisition routines                            | 0 8 |

|      | 5.2    | Computational routines                          | 1 ( |

|      | 5.3    | Utility routines                                | 1 1 |

| 6.   | SYSTE  | EM OPERATION, PERFORMANCE AND SPECIFICATIONS 1: | 2 ( |

|      | 6.1    | Calibration                                     | 2 ( |

|      | 6.2    | Scale factor calculations                       | 2 2 |

|      | 6.3    | Performance checks                              | 2 J |

|      | 6.4    | Sources of error                                | 3.8 |

|      | 6.5    | Specifications                                  | 8 : |

|      | 6.6    | Suggestions for improvements                    | ? 9 |

| 7.   | CONCL  | LUSION                                          | 3 O |

| REFE | RENCES | 3                                               | ! 1 |

| APPE | NDIX   | A WATTMETER CIRCUIT DIAGRAMS                    | ; 3 |

| ADDE | א אותא | COPTUBER ITEMENO                                |     |

# LIST OF FIGURES

| Figure | Description                                  | Page |

|--------|----------------------------------------------|------|

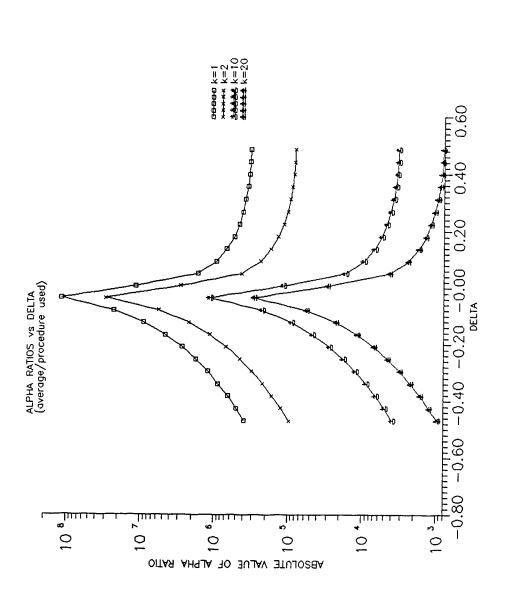

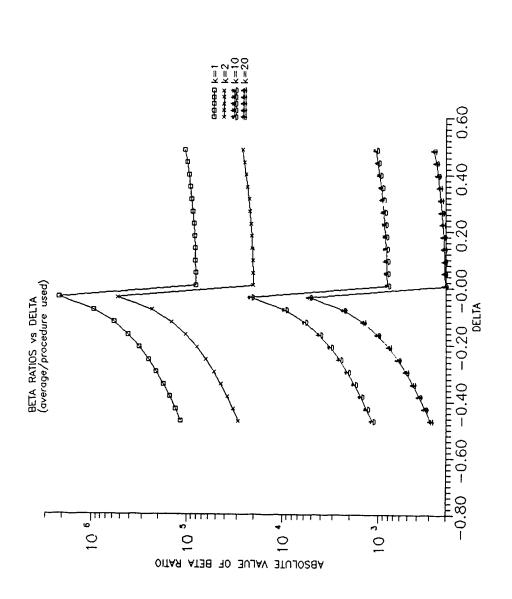

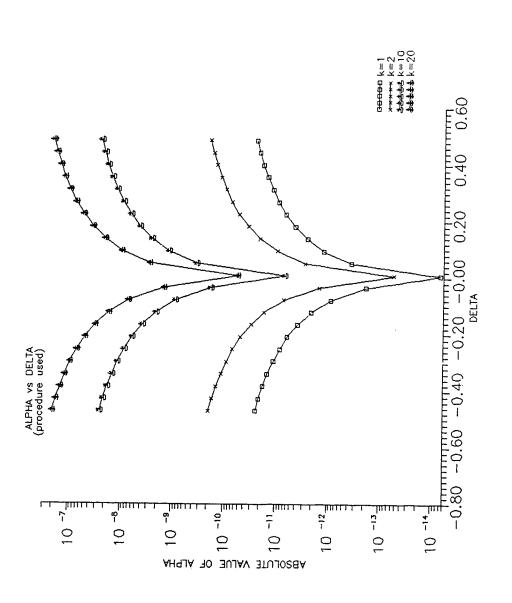

| 2.1    | Graph of alpha ratios vs del                 | ta   |

|        | (average/procedure used)                     | . 22 |

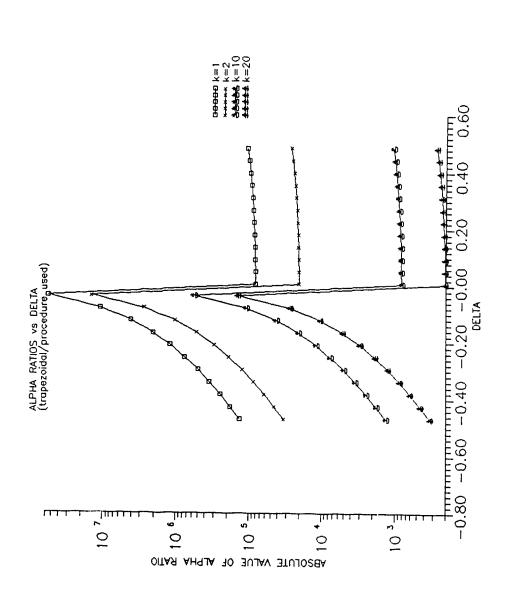

| 2.2    | Graph of alpha ratios vs del                 | ta   |

|        | (trapezoidal/procedure used)                 | . 23 |

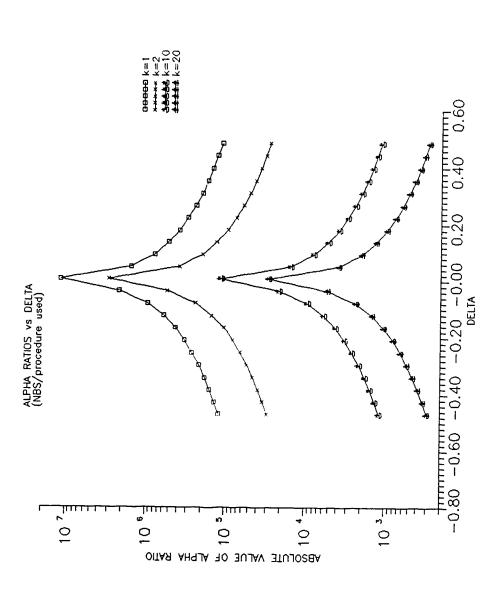

| 2.3    | Graph of alpha ratios vs delta (NBS/procedu  | re   |

|        | used)                                        | . 24 |

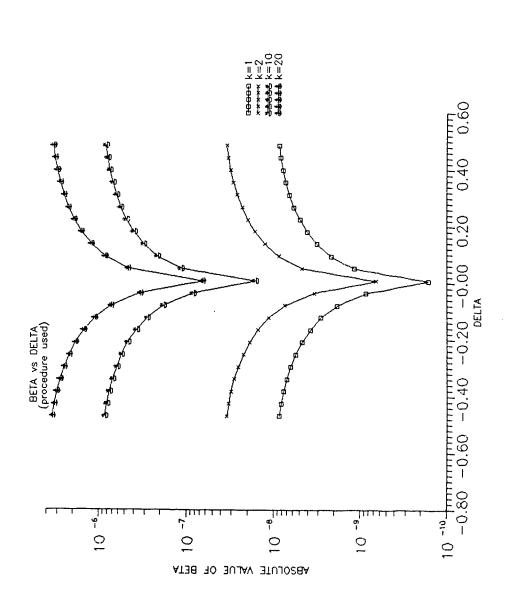

| 2.4    | Graph of beta ratios vs dela                 | ta   |

|        | (average/procedure used)                     | . 25 |

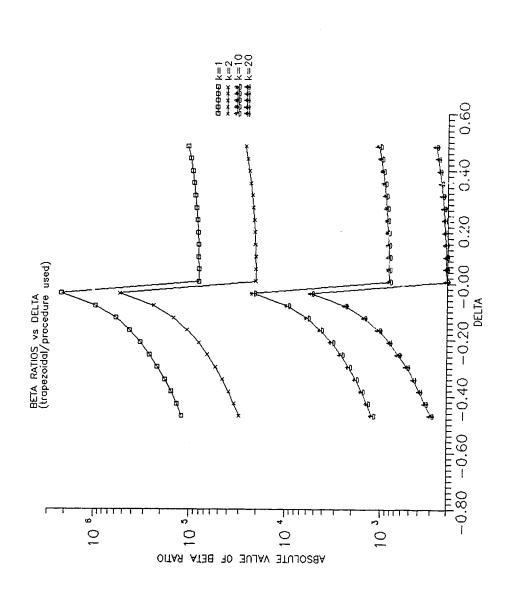

| 2.5    | Graph of beta ratios vs delt                 | ta   |

|        | (trapezoidal/procedure used)                 | . 26 |

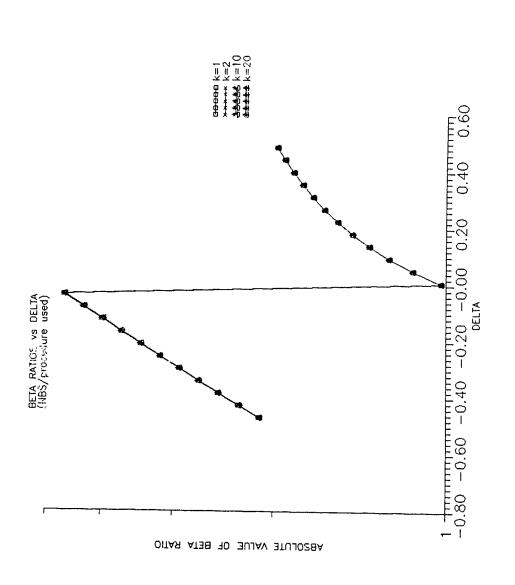

| 2.6    | Graph of beta ratios vs delta (NBS/procedur  | re   |

|        | used)                                        | . 27 |

| 2.7    | Graph of alpha vs delta for the procedur     | ce   |

|        | used                                         | . 28 |

| 2.8    | Graph of beta vs delta for the procedur      | re   |

|        | used                                         | . 29 |

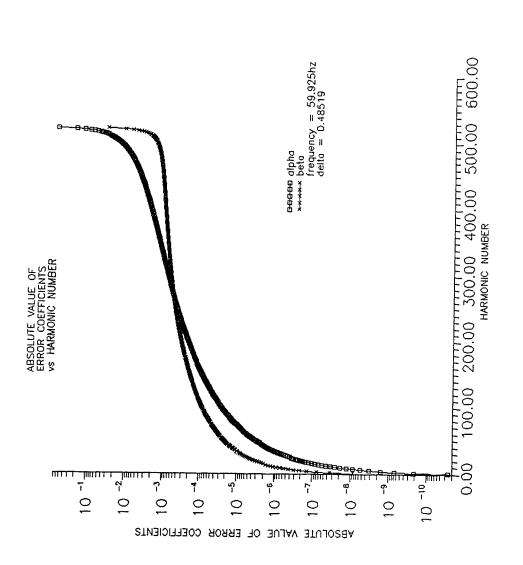

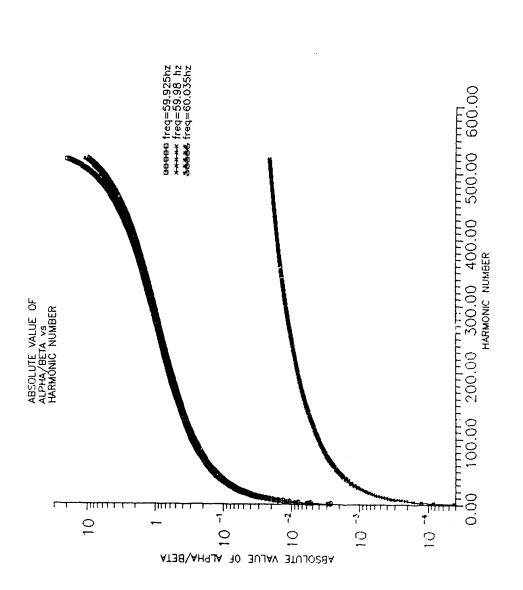

| 2.9    | Graph of absolute value of error coefficient | :s   |

|        | vs harmonic number for a frequency of 59.92  | :5   |

|        | hz                                           | . 30 |

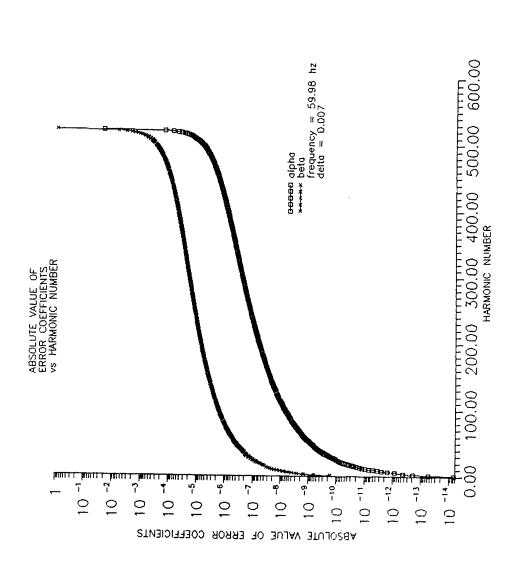

| 2.10   | Graph of absolute value of error coefficient | .s   |

|        | vs harmonic number for a frequency of 59.9   | 8    |

|        | hz                                           | 31   |

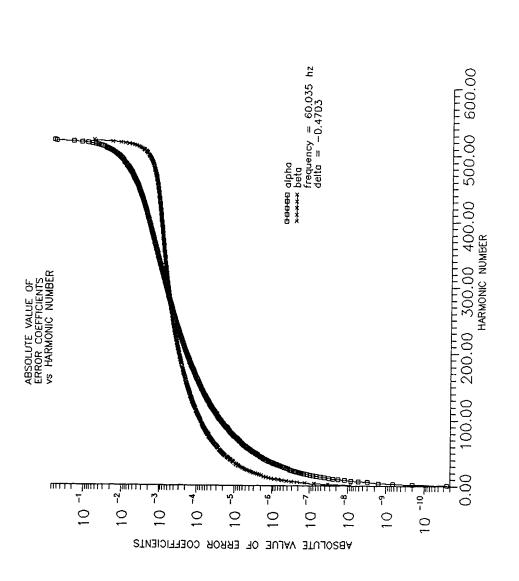

| 2.11   | Graph of absolute value of error coefficient | S    |

|      | vs harmonic number for a frequency of 60.035    |            |

|------|-------------------------------------------------|------------|

|      | hz                                              | 32         |

| 2.12 | Graph of absolute value of the ratio alpha/beta |            |

|      | vs harmonic number                              | 33         |

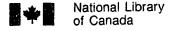

| 3.1  | Block diagram of wattmeter                      | 46         |

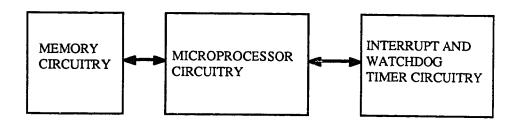

| 3.2  | Block diagram of CPU module                     | 46         |

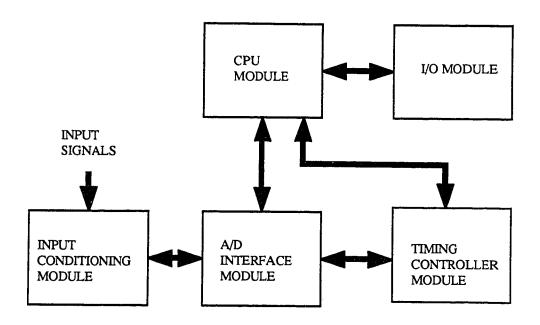

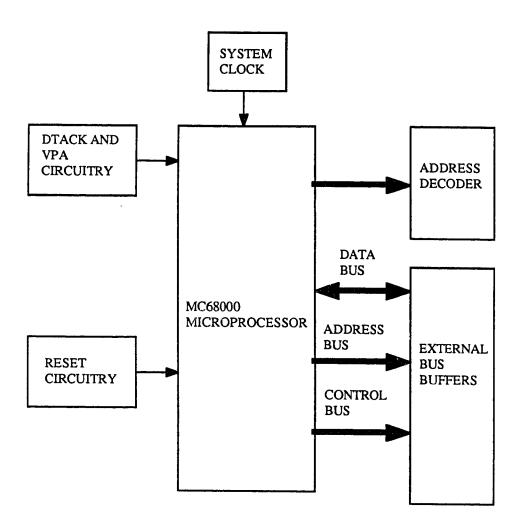

| 3.3  | Block diagram of microprocessor circuitry .     | 47         |

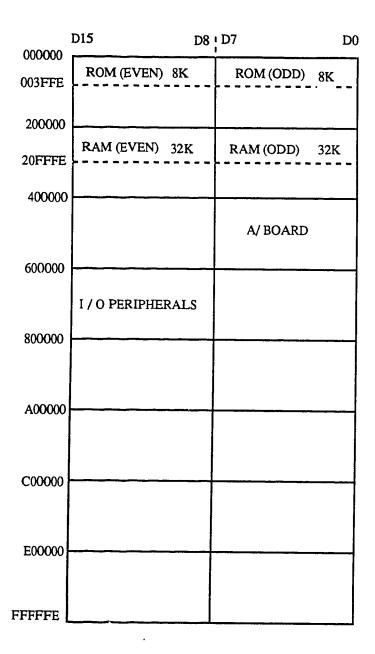

| 3.4  | System memory map                               | 48         |

| 3.5  | Detailed memory map of I/O peripherals and      |            |

|      | A/Board                                         | 49         |

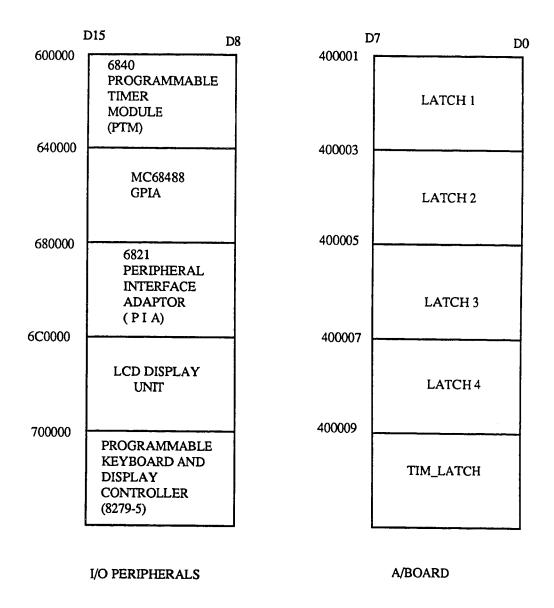

| 3.6  | Block diagram of memory circuitry               | 50         |

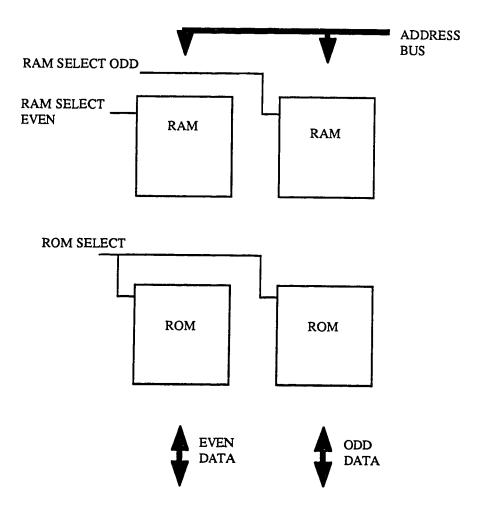

| 3.7  | Block diagram of interrupt and watchdog timer   |            |

|      | circuitry                                       | 51         |

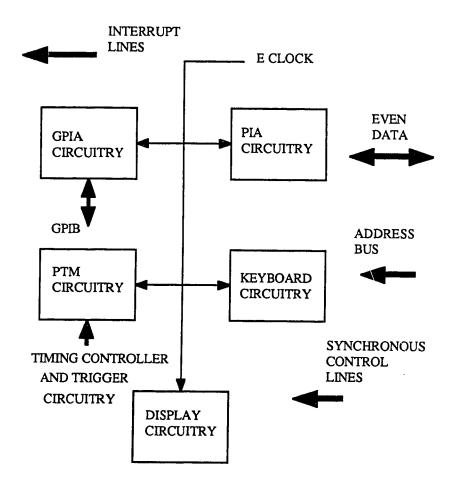

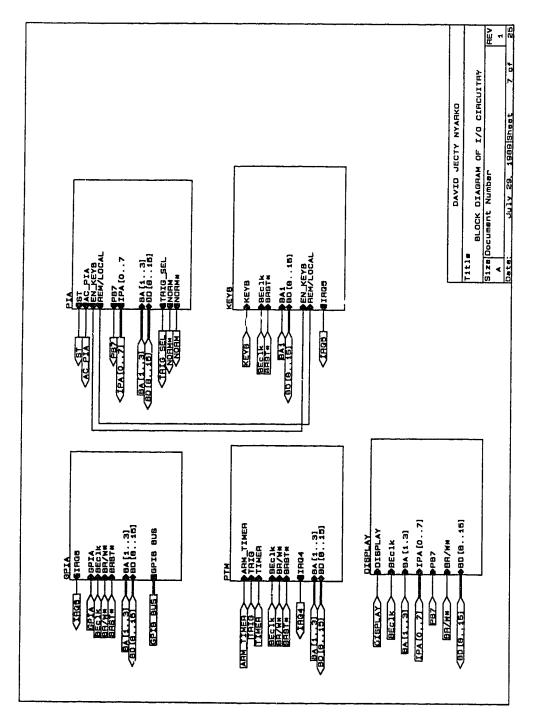

| 3.8  | Block diagram of I/O module                     | 52         |

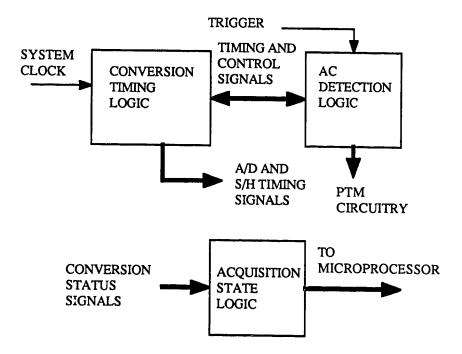

| 3.9  | Block diagram of the timing controller          |            |

|      | module                                          | 53         |

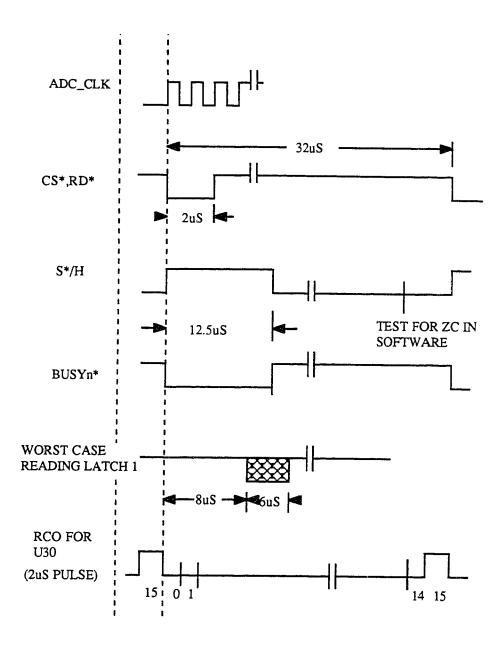

| 3.10 | A/D Interface timing diagram                    | 44         |

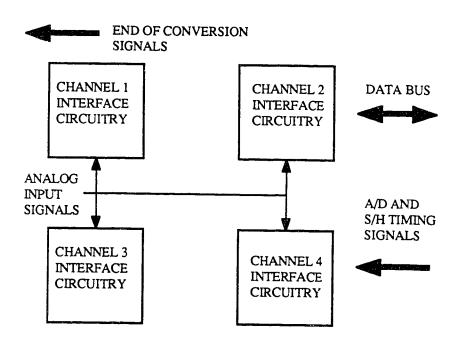

| 3.11 | Block diagram of the Analog-to-Digital          |            |

|      | interface module                                | 1,1,       |

| 3.12 | Block diagram of the input conditioning         |            |

|      | module                                          | 56         |

| 3.13 | Block diagram of the phase 1 circuitry          | 56         |

| 3.14 | Block diagram of the phase 2 circuitry          | 57         |

| 3.15 | Block diagram of the analog switches            |            |

|      | circuitry                                       | <b>.</b> , |

| 3.16 | Block diagram of the trigger circuit | try | •  | •   | •  | 58  |

|------|--------------------------------------|-----|----|-----|----|-----|

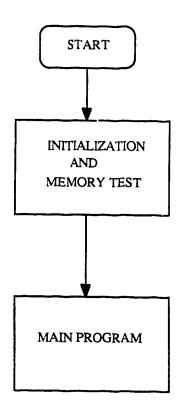

| 4.1  | Flowchart of the system software .   |     | •  |     | •  | 79  |

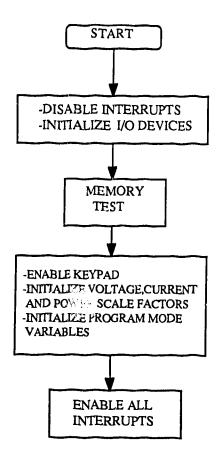

| 4.2  | Flowchart of the initialization a    | nd  | me | emc | ry |     |

|      | test                                 |     | •  | •   | •  | 80  |

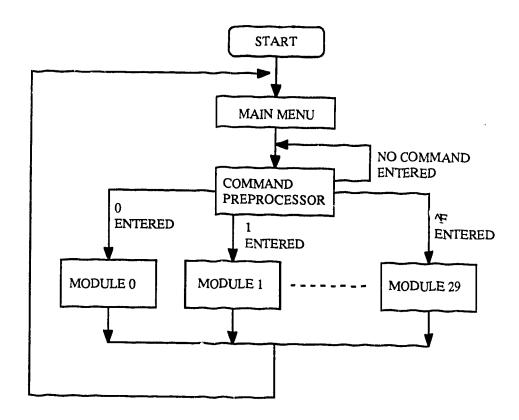

| 4.3  | Flowchart of the main program        |     | •  |     | •  | 81  |

| 4.4  | Detailed main menu displays          |     |    | •   |    | 82  |

| 4.5  | Flowchart of module 0                |     |    |     | •  | 83  |

| 4.6  | Flowchart of module 1                |     | •  |     | •  | 84  |

| 4.7  | Flowchart of module 2                |     | •  | •   | •  | 85  |

| 4.8  | Flowchart of module 3                |     | •  | •   | •  | 86  |

| 4.9  | Flowchart of module 4                |     |    | •   | •  | 87  |

| 4.10 | Flowchart of module 5                |     | •  | •   |    | 88  |

| 4.11 | Channel selection sub-menu           |     | •  | ٠   |    | 89  |

| 4.12 | Flowchart of module 6                |     | •  |     |    | 89  |

| 4.13 | Flowchart of module 7                | • • | •  |     | •  | 90  |

| 4.14 | Flowchart of module 8                |     | •  | •   | •  | 91  |

| 4.15 | Flowchart of module 9                |     | •  |     | •  | 92  |

| 4.16 | Flowchart of module 10               |     | •  |     |    | 93  |

| 4.17 | Flowchart of module 11               |     | •  |     |    | 94  |

| 4.18 | Flowchart of module 12               |     | •  | •   | •  | 95  |

| 4.19 | Flowchart of module 13               |     |    |     | •  | 96  |

| 4.20 | Flowchart of module 14               |     | •  | •   |    | 97  |

| 4.21 | Flowchart of module 15               |     |    | •   |    | 98  |

| 4.22 | Flowchart of module 16               |     |    |     | •  | 99  |

| 4.23 | Flowchart of module 17               |     |    |     |    | 100 |

| 4.24 | Flowchart of module 18 10                       | 01         |

|------|-------------------------------------------------|------------|

| 4.25 | Flowchart of module 19 10                       | 02         |

| 4.26 | Flowchart of module 20 10                       | 02         |

| 4.27 | Flowchart of module 21                          | 3          |

| 4.28 | Flowchart of module 22                          | 3          |

| 4.29 | Flowchart of module 23 10                       | <b>)</b> 4 |

| 4.30 | Flowchart of module 24                          | )5         |

| 4.31 | Flowchart of module 25                          | )5         |

| 4.32 | Flowchart of module 26                          | )6         |

| 4.33 | Flowchart of module 27                          | )6         |

| 4.34 | Flowchart of module 28                          | )7         |

| 4.35 | Flowchart of module 29                          | )7         |

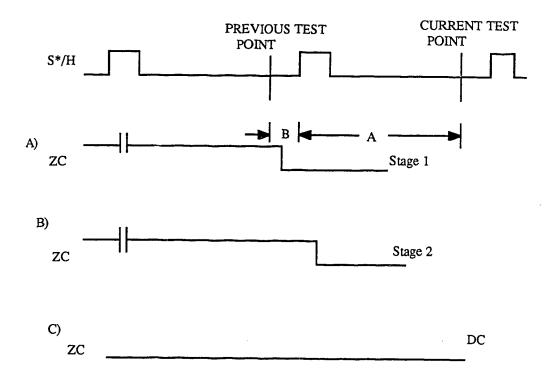

| 5.1  | Crossing detector timing diagram 1 11           | L 7        |

| 5.2  | Crossing detector timing diagram 2 11           | L <b>7</b> |

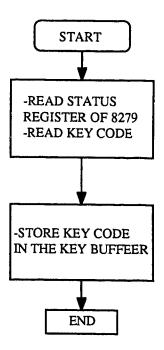

| 5.3  | Flowchart of the input routine 11               | L 8        |

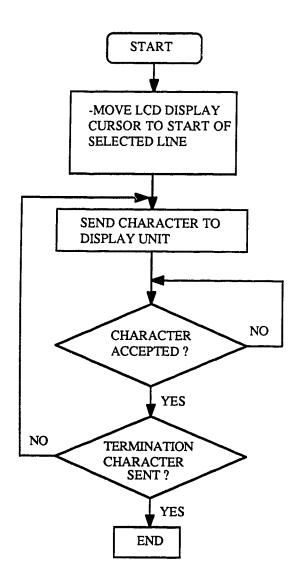

| 5.4  | Flowchart of the LCD display routine 11         | ١9         |

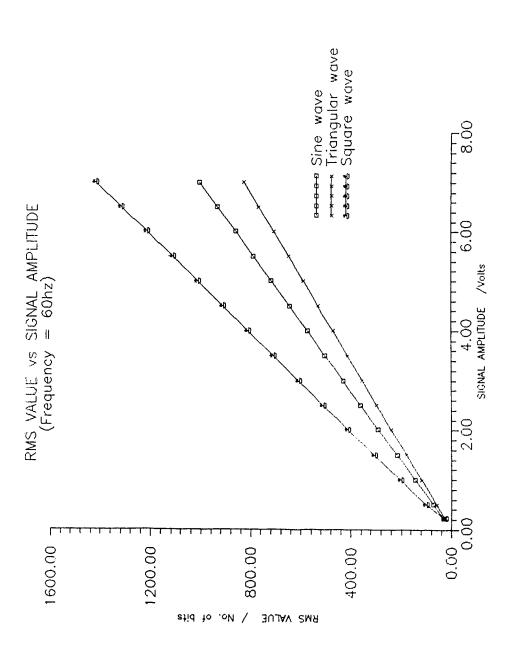

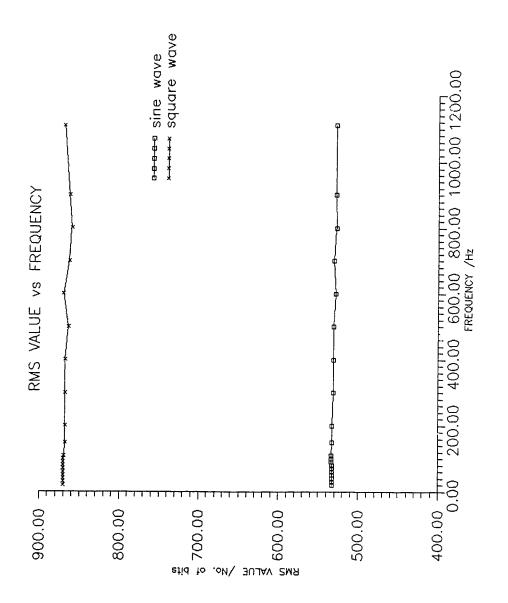

| 6.1  | Graph of rms value vs signal frequency (60      |            |

|      | hz)                                             | <u> 4</u>  |

| 6.2  | Graph of rms value vs frequency 12              | 25         |

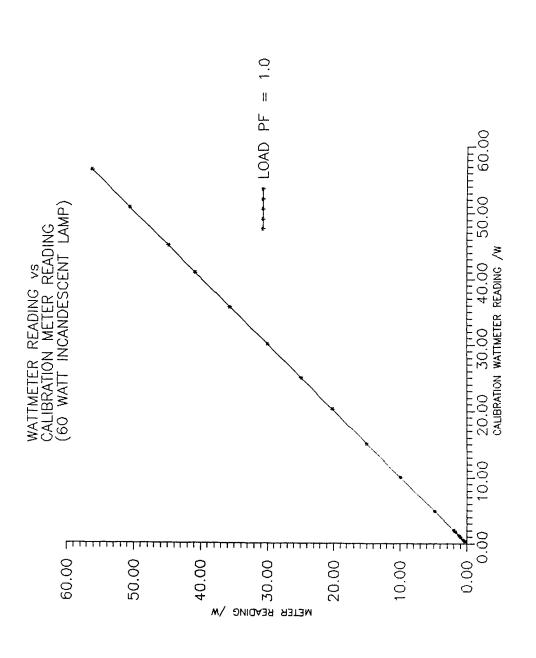

| 6.3  | Graph of wattmeter reading vs calibration meter |            |

|      | reading ( 60 Watt Incandescent lamp ) 12        | 26         |

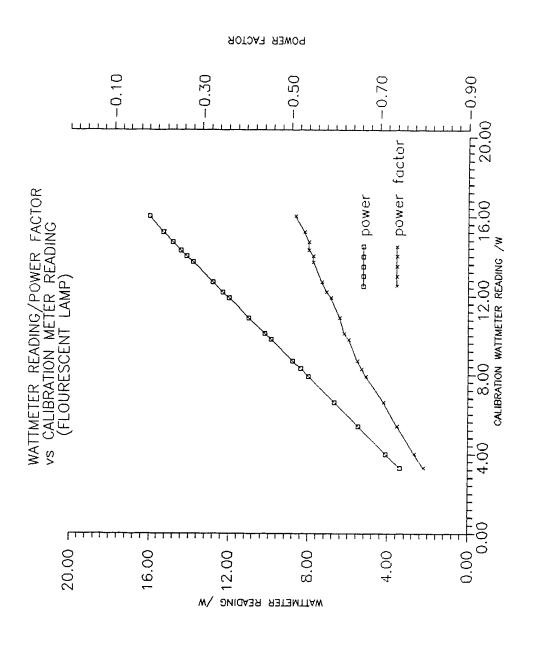

| 6.4  | Graph of wattmeter reading vs calibration meter |            |

|      | reading (Fluorescent lamp)                      | 7          |

#### LIST OF SYMBOLS

| Symbol                   | Description                                        |  |  |  |  |  |  |  |  |

|--------------------------|----------------------------------------------------|--|--|--|--|--|--|--|--|

| $\alpha_{\mathbf{k}}$    | The kth harmonic sine term error coefficient       |  |  |  |  |  |  |  |  |

| $\boldsymbol{\beta}_{k}$ | The kth harmonic cosine term error coefficient     |  |  |  |  |  |  |  |  |

| f                        | Frequency                                          |  |  |  |  |  |  |  |  |

| i                        | Current                                            |  |  |  |  |  |  |  |  |

| j                        | Sample number                                      |  |  |  |  |  |  |  |  |

| k                        | Harmonic number                                    |  |  |  |  |  |  |  |  |

| I <sub>rms</sub>         | Root-mean-square current                           |  |  |  |  |  |  |  |  |

| h                        | Sampling interval (angular measurement in radians) |  |  |  |  |  |  |  |  |

| P <sub>ac</sub>          | Active electrical power (AC)                       |  |  |  |  |  |  |  |  |

| $P_{dc}$                 | Electrical power (DC)                              |  |  |  |  |  |  |  |  |

| t                        | Time                                               |  |  |  |  |  |  |  |  |

| T                        | Period                                             |  |  |  |  |  |  |  |  |

| v                        | Voltage                                            |  |  |  |  |  |  |  |  |

| $V_{\sf rms}$            | Root-mean-square voltage                           |  |  |  |  |  |  |  |  |

#### 1. INTRODUCTION

The widespread development and use of electric power systems with highly distorted waveforms has rendered the use of the relatively commonplace instruments, particularly the analog type, inappropriate. Basically, two classes of instruments exist [5], based on the computational method employed; the analog and the digital types. Hybrid instruments employing both techniques are also in existence.

Analog instruments although relatively inexpensive with regard to their digital counterparts, suffer from numerous deficiencies. The analog computation approach suffers from amplifier gain bandwidth limitations, matching of analog components as well as a low dynamic range and sensitivity. Furthermore, calibration is not easily carried out.

The alternative digital approach, used in digital sampling meters, entails sampling the input voltage and current signals and employing fully digital arithmetic procedures to compute the required parameters. This results in very precise results. It is also easily effected in digital stored-program systems such as microprocessor-based implementations.

Two distinct approaches to wattmeter sampling timing exist. In the synchronous approach, the sample timing and the waveform frequency are synchronised so that a block of samples represents an integral number of periods.

Alternatively, an asynchronous technique is employed, which sampling is at a fixed rate independent of the waveform frequency. The first-mentioned approach has been widely employed and analyzed [1],[10],[13]. This approach, although easy to implement, results in accurate meters only if the signal frequency under consideration is stable. The computation of electrical power, voltage and current on systems operated from the electrical mains require an asynchronus technique for an adequate degree of accuracy. This approach is employed in the National Bureau of Standards calibration wattmeters [12]. Since the blocks of samples processed in this approach do not generally represent an integer number of periods, an allowance must be made for the ends of the block. The approach utilized, the modified trapezoidal approach, unlike other processing methods employed, uses all the samples obtained, computing the required integral.

The device was developed to meet the following objectives.

- Peak input voltage, current and maximum power of 350v, 10A and 3500W respectively.

- 2) Input signal frequency from dc to 1khz.

- 3) Frequency measurement range; 12 1000hz.

- 4) A user-friendly software interface.

- 5) An easy to maintain hardware.

#### 2 THEORY

The determination of electrical power, voltage and current entails the computation of appropriately scaled integrals. Digital sampling meters utilize values from a discrete set approximating continuous signal values. The application of numerical integration techniques to the sample set results in an approximation to the signal parameters desired.

The fundamental equations for calculating the electrical dc power, the dc voltage, the dc current, the electrical ac power, and the root-mean-square voltage and current are respectively;

$$P_{dc} = \frac{1}{A} \int_{0}^{A} v i dt$$

(2.1)

$$V_{dc} = \frac{1}{B} \int_{0}^{B} v dt$$

(2.2)

$$I_{dc} = \frac{1}{C} \int_{0}^{C} i dt \qquad (2.3)$$

$$P_{ac} = \frac{1}{T} \int_{0}^{T} v i dt$$

(2.4)

$$V_{rms} = \sqrt{\frac{1}{T} \int_{0}^{T} v^{2} dt} \qquad (2.5)$$

$$I_{rms} = \sqrt{\frac{1}{T} \int_{0}^{T} i^{2} dt}$$

(2.6)

where A,B,C are arbitrary time intervals,

T is the period

v is the instantaneous voltage

and i is the instantaneous current

Equations 2.1 to 2.6 involve parameters which are functions of the average of integrals. In general, these equations can be represented as;

$$x = F[I(y(t))] \qquad (2.7)$$

where x is the parameter required

y(t) is the corresponding variable

I is an averaging function dependent on the integral of y(t)

and the function F, represents any extra processing required to compute the parameter.

For example, relating the above equation to equation 2.5;

$$x(t) = V_{rms}$$

$$y(t) = v^{2}$$

$$I\{y(t)\} = \frac{1}{T} \int_{0}^{T} v^{2} dt$$

and F is the square-root function.

# 2.1 Analysis of sampled waveforms

A convenient approach to the analysis of the periodic signals encountered in the measurement of the system parameters is the Fourier series technique.

A Fourier series expansion for a periodic signal y(t) is:

$$y(t) = a_0 + \sum_{k=1}^{\infty} a_k \sin\left(\frac{2\pi kt}{T}\right) + \sum_{k=1}^{\infty} b_k \cos\left(\frac{2\pi kt}{T}\right) \quad (2.8)$$

where T = the fundamental period

t = time

Sampling the above signal at regularly spaced intervals of length h radians, produces sampled values  $y_j$  which can be expressed as:

$$y_{j} = a_{0} + \sum_{k=1}^{\infty} a_{k} \sin(kjh) + \sum_{k=1}^{\infty} b_{k} \cos(kjh) \qquad (2.9)$$

j = 0,1,2,...,n for a signal sampled at n+1 points

The above representation of an ac signal can also be used to represent the power signal which exists as a result of the microprocessor computations on the sampled values of voltage and current. This is due to the simultaneous sampling of the sinusoidal voltage and current signals.

#### 2.2 Error Determination

The basic principle involved in the determination of the root mean square values of the voltage and current as well as the average power, is the application of a linear averagi , operator A to the product of sampled values  $\mathbf{v}_j^2$ ,  $\mathbf{i}_j^2$  and  $\mathbf{v}_j\mathbf{i}_j$  respectively. This operator computes the mean-value of an integral. It is thus the discrete equivalent of the continuous data averaging function I in equation 2.7. The existence of numerous algorithms for computing the integral of a discrete data set, thus result in a variety of expressions for A. These expressions for A are referred to in this thesis, as the processing methods. The error in any processing method indicates the deviation of the parameters obtained using that method to that obtained by computing the mean value of the integral with continuous signals.

Two schemes for the error determination exist: time domain and frequency domain analysis. The former is suitable for synchronous sampling implementations but difficult to interpret for asynchronous sampling schemes. The latter approach [14] however covers both sampling schemes easily, and is easily interpreted. This is due to the fact that the error coefficients are related directly to the signal harmonics. This approach is used in the subsequent equations.

Let y represent the products of the instantaneous values of the relevant continuous signals, and  $y_i$  represent

the products of the sampled values. The error  ${\bf E}$  resulting from the application of the linear averaging operator  ${\bf A}$  on  ${\bf y}_j$  is:

$$E = Ay_j - \frac{1}{T} \int_0^T y(t) dt$$

(2.10)

$$= \lambda \sum_{k=1}^{\infty} a_k \sin(kjh) + \lambda \sum_{k=1}^{\infty} b_k \cos(kjh)$$

(2.11)

since  $Aa_0 = a_0$

$$= \sum_{k=1}^{\infty} a_k \operatorname{Asin}(kjh) + \sum_{k=1}^{\infty} b_k \operatorname{Acos}(kjh)$$

(2.12)

$$= \sum_{k=1}^{\infty} a_k \alpha_k + \sum_{k=1}^{\infty} b_k \beta_k \qquad (2.13)$$

The error coefficients  $\alpha_k$  (alpha) and  $\beta_k$  (beta) are thus dependent on the processing method. The equation further indicates the dependence of the error on the Fourier series coefficients and hence the start of the sampling process.

For n+1 regularly spaced samples spanning n intervals of duration h, the following expression is obtained

$$(n + \Delta)h = 2m\pi$$

(2.14)

where n,m are integers

and  $\Delta$  (delta) is a dimensionless quantity.

# 2.3 Error expressions for various processing methods

Two distinct cases should be analyzed in the determination of the error expressions.

- a)  $kh = 2\pi p$  where p is a positive integer

- b)  $kh \neq 2\pi p$  where p is a positive integer

#### a) $kh = 2\pi p$

In this case, a general error expression can be obtained for all processing methods which satisfy the relation;  $\mathbf{A}\mathbf{a}_0 = \mathbf{a}_0$ .

$$\alpha_{k} = A \sin(jkh)$$

$$= A \sin(j2\pi p)$$

$$= 0$$

$$\beta_{k} = A \cos(jkh)$$

$$= A \cos(j2\pi p)$$

$$= 1$$

It should be noted that the error expressions obtained for  $\alpha_k$  and  $\beta_k$  above, are applicable to a synchronous sampling scheme provided the following conditions are satisfied.

a) n+1 samples covering m periods where m and n are coprime.

b)

$$k = p\left(\frac{n}{m}\right)$$

.

For example if 521 samples are taken in a period of a waveform, only the 520th ,1040th etc. harmonics will contribute to the error in measurement of the required

parameter.

#### b) $kh \neq 2\pi p$

In this instance, the error is dependent on the processing scheme. Four existing processing schemes will be considered; the average of samples, the trapezoidal rule, the NBS approach and the processing method used in this thesis.

In the average of samples approach the integral is approximated by a series of rectangles of height equal to the sampled values. This approach does not take into account the last sampled value. No correction is made to account for cases in which the total sampling interval does not cover an integral number of cycles. It is however the most widely used approach. The trapezoidal rule approximates the integral using a series trapezoids. All the samples are used in the computation of the integral. Like the average method, no correction is made for the sampling interval. The NBS method is simply an average method including an end correction range [0-1]. Finally, the approach used in this thesis is simply a trapezoidal rule with an end correction. Unlike the NBS method, the end correction  $\Delta$  is restricted to the range [-0.5,0.5] by adjusting the sample size accordingly. This method will be referred to as the trapezoidal approach.

#### 2.3.1 Average of samples

The average value for n+1 samples [2],[6],[8] is given by;

$$Ay_{j} = \frac{1}{n} \sum_{j=0}^{n-1} Y_{j}$$

( 2.15 )

The corresponding error coefficient relating to the sine term of the error expression is:

$$\begin{split} & \underset{k}{\mathbf{A}} = \mathbf{A} \sin(j\mathbf{k}\mathbf{h}) \\ & = \mathbf{A} \left[ \mathrm{Im} \left( \mathbf{e}^{ij\mathbf{k}\mathbf{h}} \right) \right] \\ & = \mathbf{A} \left[ \mathrm{Im} \left( \mathbf{e}^{ij\theta} \right) \right] \\ & = \mathbf{A} \left[ \mathrm{Im} \left( \mathbf{e}^{ij\theta} \right) \right] \\ & = \frac{1}{n} \sum_{j=0}^{n-1} \mathrm{Im} \left( \mathbf{e}^{ij\theta} \right) \\ & = \frac{1}{n} \mathrm{Im} \left( \frac{1 - \mathbf{e}^{i\mathbf{n}\theta}}{1 - \mathbf{e}^{i\theta}} \right) \\ & = \frac{1}{n} \mathrm{Im} \left[ \frac{1 - \cos(n\theta) - i\sin(n\theta)}{1 - \cos\theta - i\sin(n\theta)} \right] \left( \frac{1 - \cos\theta + i\sin\theta}{1 - \cos\theta + i\sin\theta} \right) \right] \\ & = \frac{1}{n} \left[ \frac{\sin\theta \left( 1 - \cos(n\theta) \right) - \sin(n\theta) \left( 1 - \cos\theta \right)}{\left( 1 - \cos\theta \right)^2 + \sin^2\theta} \right] \end{split}$$

now

$$(n + \Delta)h = 2m\pi$$

=>  $(n + \Delta)kh = 2mk\pi$

$nkh = 2mk\pi - \Delta kh$

=>  $n\theta = 2mk\pi - \Delta kh$

=>  $sin(n\theta) = -sin(\Delta kh)$

and  $cos(n\theta) = cos(\Delta kh)$

hence;

$$\alpha_{k}^{A} = \frac{1}{n} \left[ \frac{\sin\theta (1-\cos(\Delta\theta)) + \sin(\Delta\theta) (1-\cos\theta)}{2(1-\cos\theta)} \right]$$

$$= \frac{1}{n} \left[ \cot\left(\frac{k h}{2}\right) \sin^{2}\left(\frac{\Delta k h}{2}\right) + \frac{\sin(\Delta k h)}{2} \right]$$

The corresponding error coefficient relating to the cosine term of the error expression is:

$$\beta_{k} = A \cos(jkh)$$

$$= A \left[ Re \left( e^{ijkh} \right) \right]$$

$$= A \left[ Re \left( e^{ij\theta} \right) \right] \qquad \text{where } \theta = kh$$

$$= \frac{1}{n} \sum_{j=0}^{n-1} Re \left( e^{ij\theta} \right)$$

$$= \frac{1}{n} Re \left( \frac{1 - e^{in\theta}}{1 - e^{i\theta}} \right)$$

$$= \frac{1}{n} Re \left[ \left( \frac{1 - \cos(n\theta) - i\sin(n\theta)}{1 - \cos\theta + i\sin\theta} \right) \right]$$

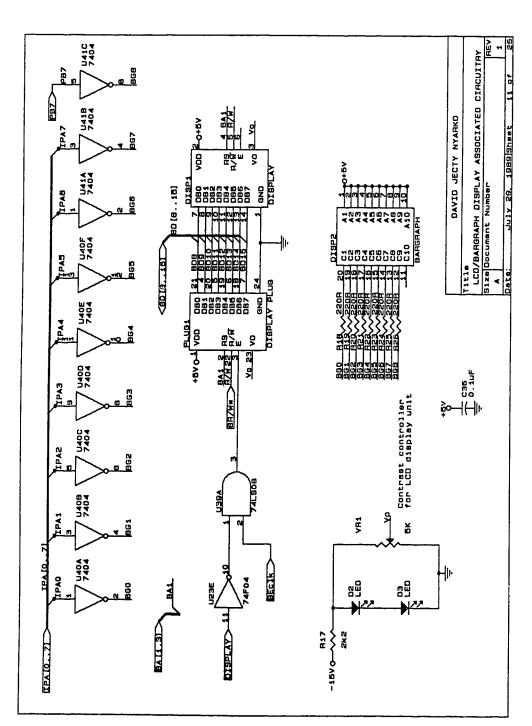

facility results in simple LCD display routines. The LCD unit also performs the refreshing of the display thus freeing up the microprocessor for other tasks. A further advantage in using this device is the possibility of writing to any of the 80 locations on the screen independently of the others. The 4 line LCD places a limitation on the number of items that can be displayed on the screen at a time. The bargraph display segments indicate the system as well as the program status. Enabling or disabling individual display segments is effected through the PIA. The detailed circuit diagram of this section is shown if Fig. A.11.

The GPIA circuitry provides the interface required to implement the IEEE-488 bus (GPIB) protocol. The heart of this subunit, the Motorola MC68488 GPIA IC, facilitates the implementation of the bus protocol. This circuitry together with the associated software enables the instrument to implement the following IEEE-488 standard features: talker, listener, complete source and acceptor handshake, serial and parallel poll, device trigger, device clear and the remote/local procedure. The detailed circuit diagram of this circuitry is shown in Fig. A.12.

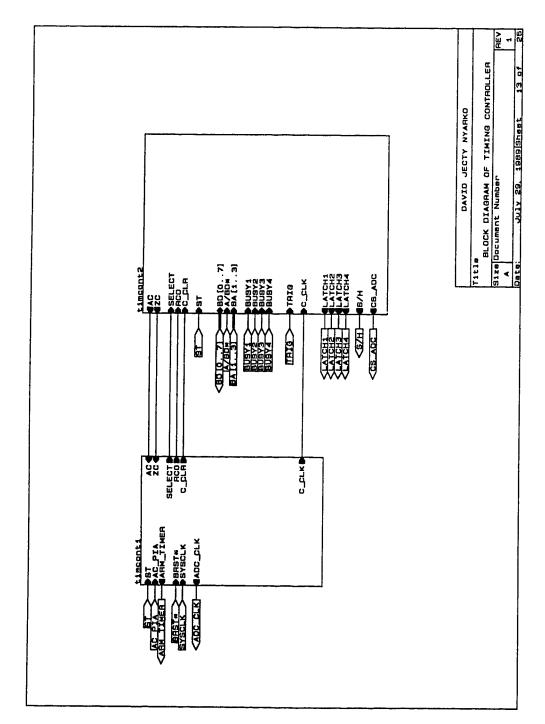

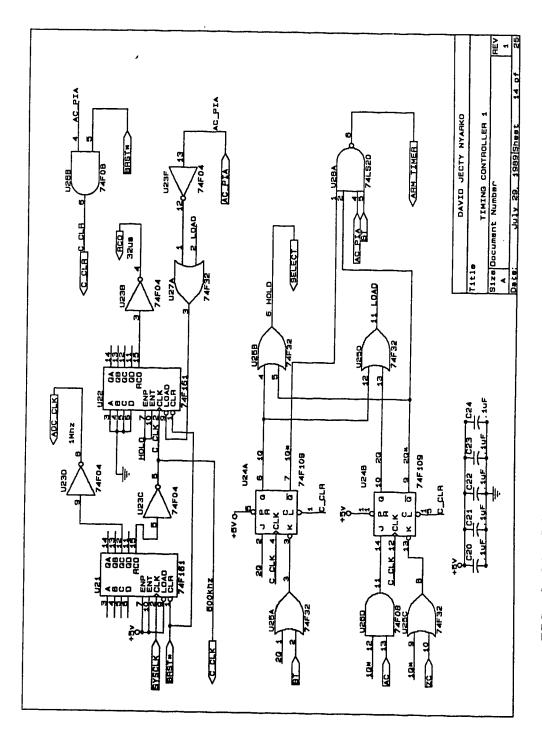

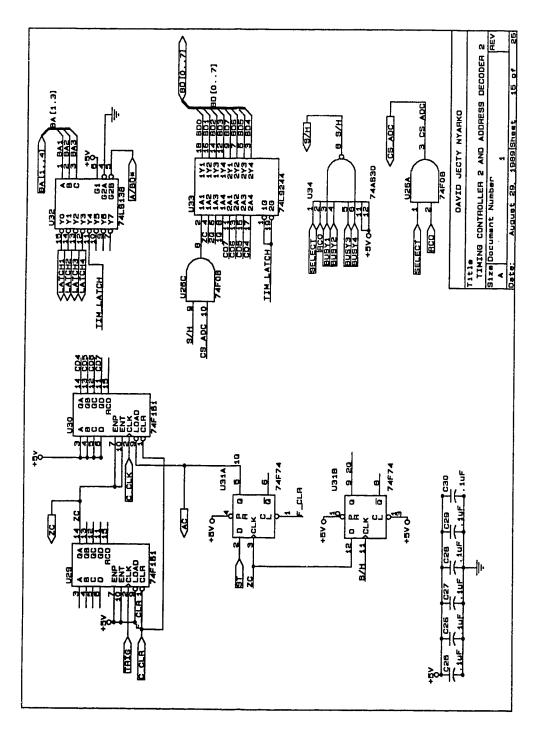

#### 3.3 Timing Controller module

The block diagram of this module is shown in Fig. 3.9 (page 53). This subunit comprises the conversion timing

logic, the AC detection logic and the acquisition state logic. A more detailed block diagram showing the control signal interconnections is shown in the appendix as Fig. A.13.

The conversion timing logic produces the signals required for the analog-to-digital (A/D) converters and the sample-and-hold amplifiers. The use of Fairchild Advanced Schottky TTL (FAST) logic as well as the derivation of the various timing signals from the 8 Mhz system clock results in minimal jitter as well as precise timing signals. The A/D converter signals are the 1Mhz analog-to-digital (A/D) converters clock signal and the  $2\mu$ s start of conversion signal. The primary sample-and-hold amplifier signal is that of the  $32\mu$ s sampling interval. Some relevant timing signals generated by this logic and their relationship to the analog-to-digital interface circuitry is indicated in Fig. 3.10 (page 54).

The AC detection logic provides the automatic AC or DC mode detection required for the wattmeter operation.

The acquisition state logic provides the status signals employed by the software in determining the state of the current acquisition cycle. This circuit also determines the end correction required following an acquisition cycle involving an AC signal.

The detailed circuitry of this subunit is shown in Figs. A.14 and A.15.

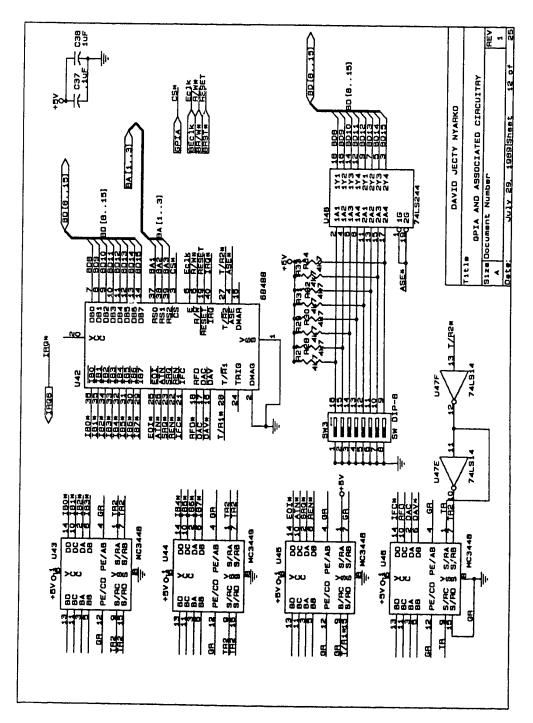

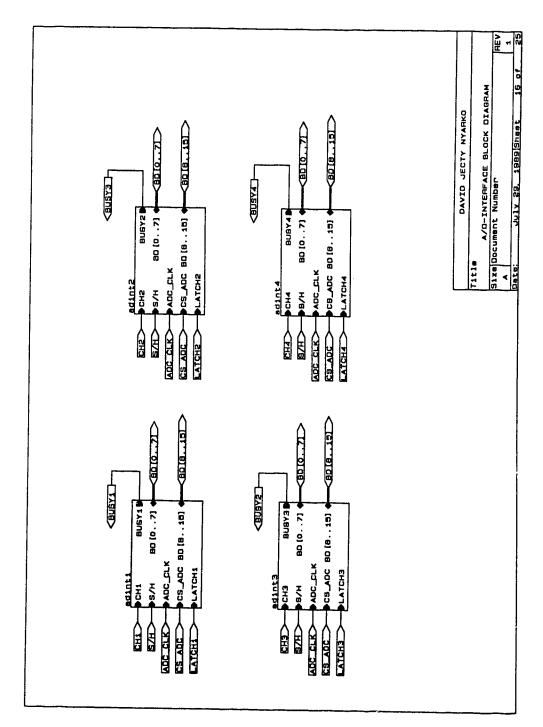

#### 3.4 Analog-to-Digital interface module

The block diagram of this module is shown in Fig. 3.11 (page 55). A more detailed block diagram showing the various signal interconnections is shown in the appendix as Fig. A.16.

The purpose of this section is to provide a digital equivalent of the analog input signal after the required input conditioning has been performed. This comprises 4 similar channel interface sections representing each of the input channels. Each section has as its main devices, a voltage scaling and translation section, a sample-and-hold amplifier, a 12-bit analog-to-digital (A/D) converter, as well as an output latch for the temporary storage of the converted values. An input signal in the range -10v to +10v applied to the respective voltage scaling and translation section produces a 0-5v output. The latter voltage is applied to the corresponding sample-andhold amplifier and subsequently converted to a 12-bit value in the respective A/D converter. The acquisition scheme employed, results in the sampling and conversion of signals on all 4 channels being performed simultaneously. The circuit logic is set up so that the results of the previous conversions are stored in the latches while the current conversion is taking place. This scheme results in 30 µs of the  $32\mu s$  sampling interval being available for use by the

microprocessor.

The detailed circuit diagram of this subunit is shown if Figs. A.17 - A.20.

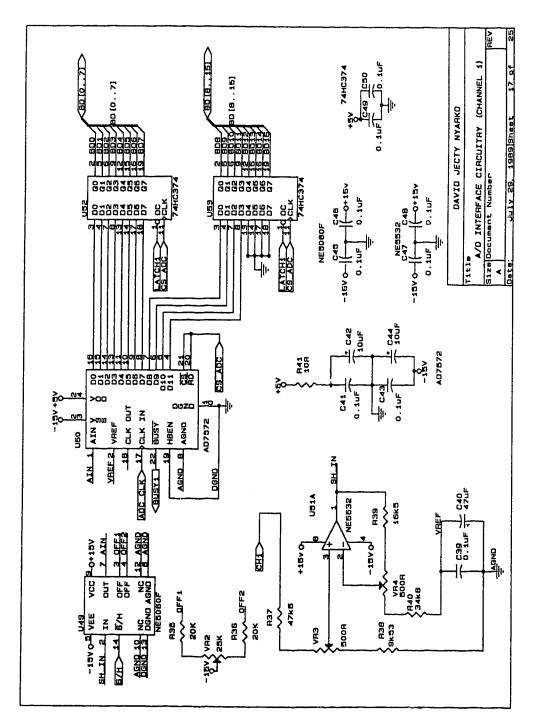

# 3.5 Input-conditioning circuitry

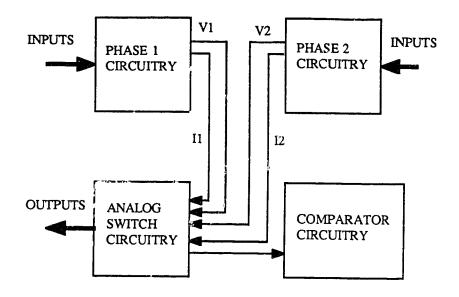

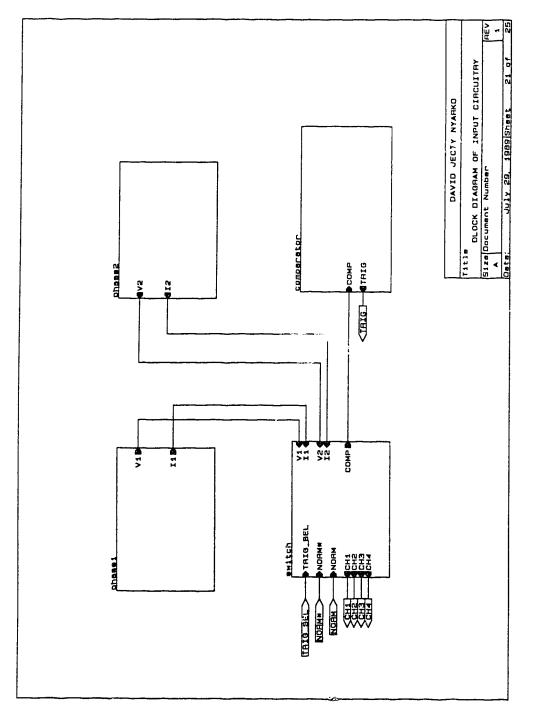

Fig. 3.12 (page 56) shows the block diagram of this module. The four sections making up this module are; the Phase 1 circuitry, the Phase 2 circuitry, the analog switches circuitry and the trigger circuitry. A more detailed block diagram showing the various signal interconnections is shown in the appendix as Fig. A.21.

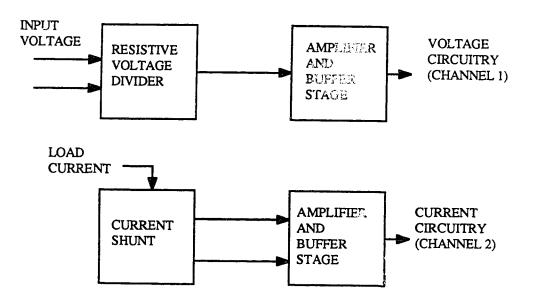

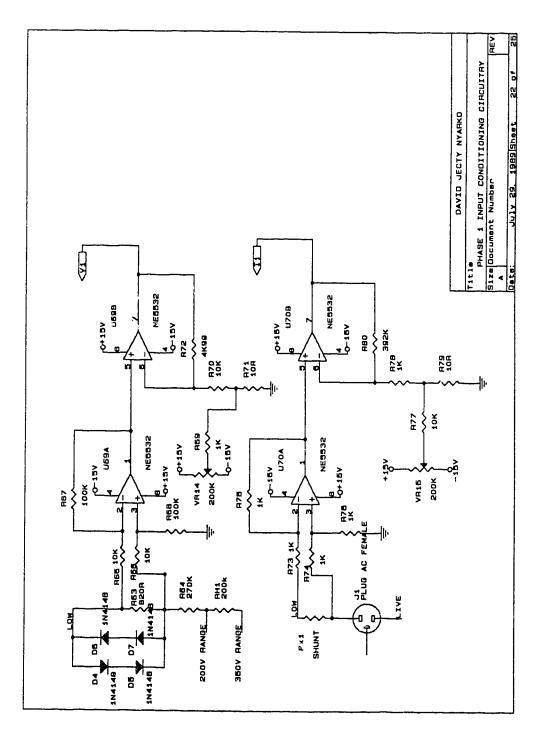

# 3.5.1 Phase 1 circuitry

The block diagram of the Phase 1 circuitry is shown in Fig. 3.13 (page 56). This section consists of a voltage circuitry and a current circuitry. The voltage circuitry also referred to as the channel 1 circuitry, provides the interface between the digital wattmeter and the input voltage source. This circuitry is employed for single phase measurements or as the first phase in three-phase system measurements. Two input voltage ranges of 200V and 350V peak are provided. Initial signal attenuation is provided by the resistive voltage divider stage. Further buffering and amplification to the -10v to +10v required for the subsequent A/D interface stage is provided by the amplifier and buffer stage [4]. The current circuitry also referred

to as the channel 2 circuitry, provides the interface between the digital wattmeter and the input current source. This circuitry is employed for single phase measurements or as the first phase in three-phase system measurements. A current shunt is employed for current measurement. The voltage generated across the shunt, is amplified by the subsequent amplifier and buffer stage circuitry to the -10v to +10v range required for the subsequent A/D interface stage. The detailed circuit diagram of this stage is shown in Fig. A.22.

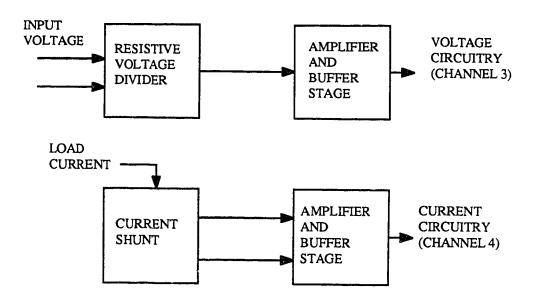

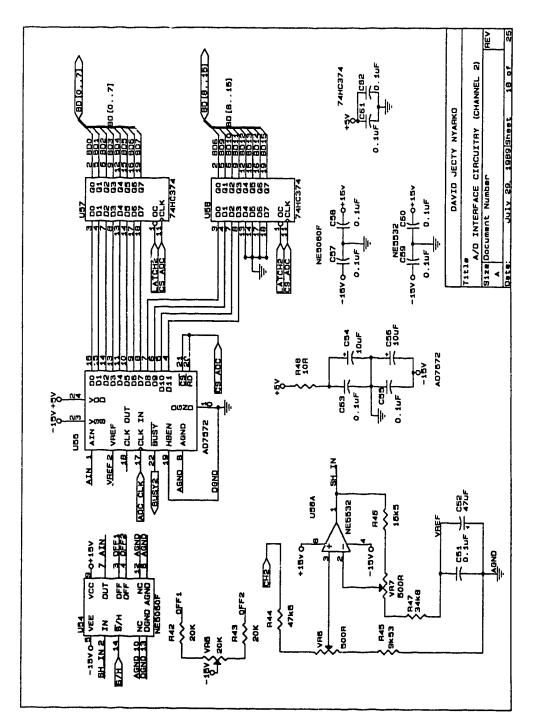

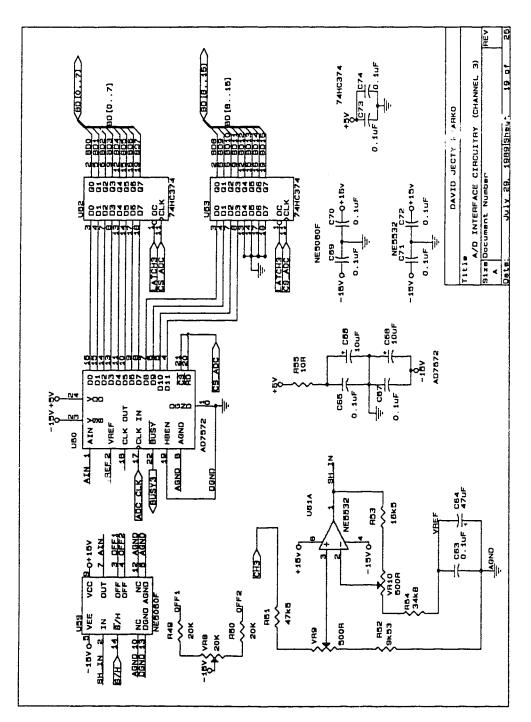

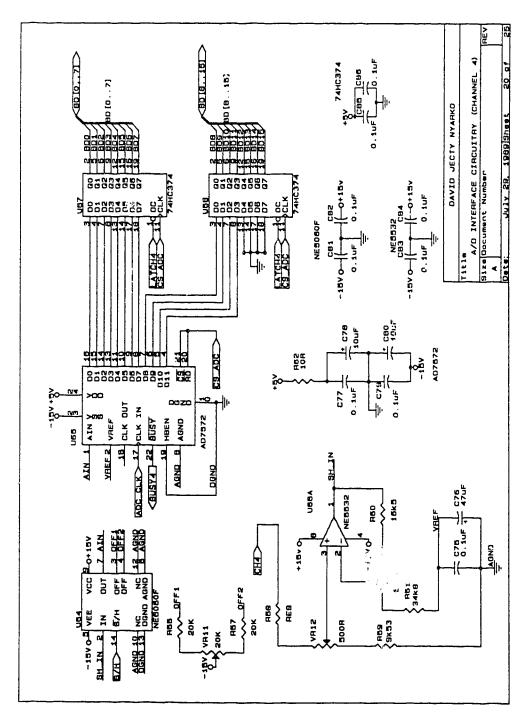

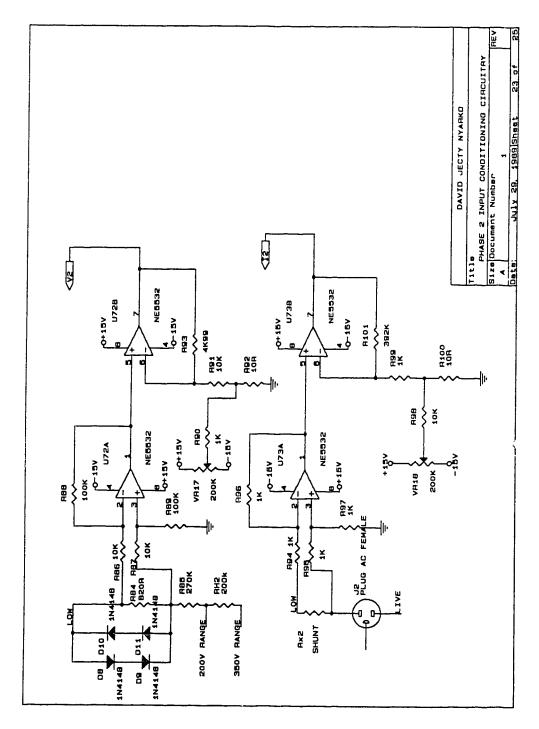

#### 3.5.2 Phase 2 circuitry

The block diagram of the Phase 2 circuitry is shown in Fig. 3.14 (page 57). This circuitry is identical to the Phase 1 circuitry and used in three-phase measurements or measurements of a second setup. This section comprises a voltage circuitry also referred to as the channel 3 circuitry and a current section referred to as the channel 4 circuitry. The detailed circuit diagram of this stage is shown in Fig. A.23.

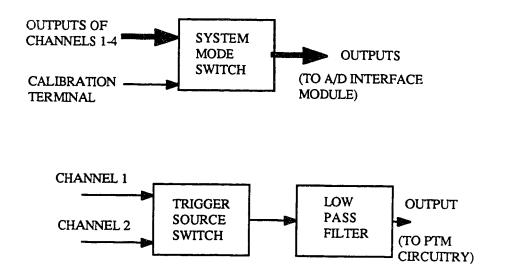

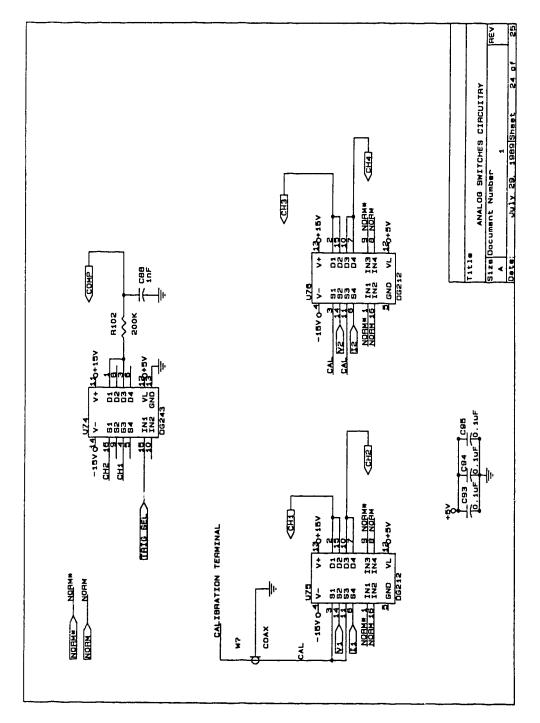

#### 3.5.3 Analog switches circuitry

The block diagram of this section is shown in Fig. 3.15 (page 57). This section consists of two main blocks; the trigger source switching circuitry and the system mode switch circuitry. Both switching circuits are controlled

through the PIA. The trigger source input selects the output of either channel 1 or 2 as the trigger source. Filtering of the output of this stage is provided by the low-pass filter before subsequent processing. The system mode switch selects the input to the A/D interface stage. Two options are available for the above-mentioned stage. These are; the calibration terminal or the input-conditioning subunit. The analog switches are controlled by the 6821 PIA IC. This approach enables the selection of the specified sources under software control. The detailed circuit diagram of this circuit is shown in Fig. A.24.

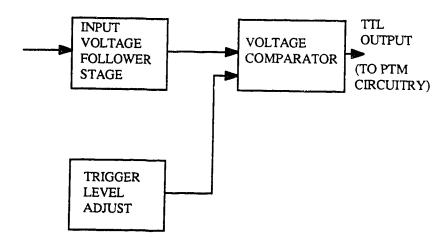

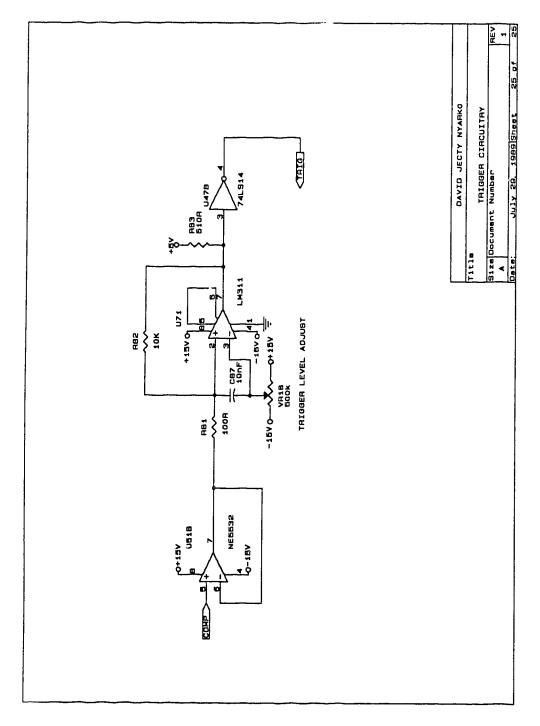

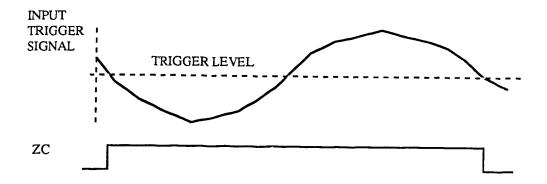

#### 3.5.4 Trigger circuitry

Fig. 3.16 (page 58) shows the block diagram of this circuitry. This circuit is basically that of a variable threshold voltage level detector. The triggering level adjust resistor provides the input switching threshold voltage of the voltage comparator. The comparator includes logic to generate a TTL compatible output signal. The detailed circuitry for this section is shown if Fig. A.25.

Fig. 3.1 Block diagram of wattmeter

Fig. 3.2 Block diagram of CPU module

Fig. 3.3 Block diagram of microprocessor circuitry

Fig. 3.4 System memory map

Fig. 3.5 Detailed memory map of I/O peripherals and A/Board

Fig. 3.6 Block diagram of memory circuitry

Fig. 3.7 Block diagram of interrupt and watchdog timer circuitry

Fig. 3.8 Block diagram of I/O module

Fig. 3.9 Block diagram of the timing controller module

Fig. 3.10 A/D Interface timing diagram

Fig. 3.11 Block diagram of the Analog-to-Digital interface module

Fig. 3.12 Block diagram of the input conditioning module

Fig. 3.13 Block diagram of the phase 1 circuitry

Fig. 3.14 Block diagram of the Phase 2 circuitry

Fig. 3.15 Block diagram of the analog switches circuitry

Fig. 3.16 Block diagram of the trigger circuitry

## 4. DIGITAL SAMPLING WATTMETER SOFTWARE

The software structure is geared towards the efficient and speedy implementation of the necessary mathematical manipulations and wattmeter functions required. This ties in suitably with the design goal of implementing a very accurate system using reasonably priced off-the-shelf components.

The hardware and software marriage is effectively achieved with 'idle' periods such as occur during sampling intervals being utilized for program code execution by the microprocessor.

With the ease of use and maintenance in mind, a user-friendly software interface is provided, as well as routines to simplify the system calibration and maintenance. The wattmeter program source code is included in Appendix B.

## 4.1 Software Overview

The flowchart in Fig. 4.1 (page 79) indicates the program flow of the digital sampling wattmeter.

On power-up or following a system reset, the system initialization and memory test are performed. This is followed by the execution of the main program.

# 4.2 Initialization and Memory test

The flow diagram of this section is shown in Fig. 4.2

(page 80). Initially, all system interrupts are disabled. Subsequently, the flip-flops and timing controller are initialized. This is followed by the initialization of the microprocessor peripheral devices namely; the 6821 PIA, the 8279 programmable keyboard and display controller, the 6840 PTM, the MC68488 GPIA ICs as well as the LCD display.

On successful completion of the above procedure, the memory test is performed. This test exponsively checks all 64 kilobyte locations in the system static RAMS. A static ram test [3] with 5 data backgrounds is used. An indication of the current data background (0-4) being used is reflected on the corresponding LED of the bargraph display. A failure of this test results in the processor displaying the failing address. In the last-mentioned mode, a system reset is the only option available to the user in restarting the system.

The ensuing program code enables the keypad and performs the second initialization. In this initialization stage the voltage, current and power scale factors are stored in the static RAMS. Next, the program mode variables are initialized and all interrupts are enabled. Subsequently, the analog-to-digital interface module has its inputs switched to the outputs of channels 1 to 4. All microprocessor interrupts are enabled.

# 4.3 The main program

The flow diagram of this module is indicated in Fig. 4.3 (page 81). The program code interacts directly with the hardware in accepting user inputs as well as computing and displaying results as required through an interaction of system routines.

# 4.3.1 The main menus

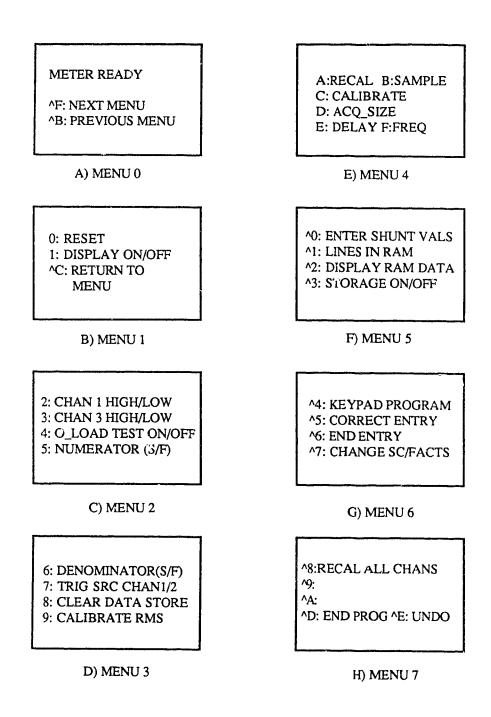

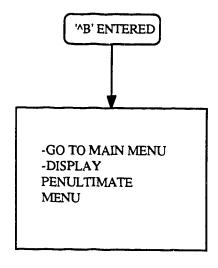

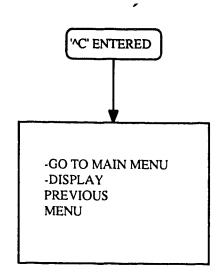

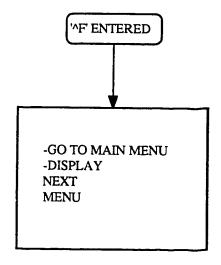

The routines used in this stage are the input and LCD string display routines. The limitations of the LCD mentioned earlier prevent the display of the description of all the 32 possible keypad commands on the LCD display simultaneously. As a result the command summary is divided into 8 menus denoted menu 0 to menu 7. The screen display of these menus are indicated in Fig. 4.4 (page 82). The display of the next menu is always performed using the 'F command. The display of the previous menu being performed using the 'B command. A program command having a caret prefix indicates the simultaneous enabling of the control switch and the corresponding keypad character. Following the execution of a particular keypad command, the previous main menu displayed is always entered.

### 4.3.2 Command preprocessor

This section of the main program is always entered following the display of a particular main menu. The main

routine used is the input routine. The purpose of the command preprocessor is to determine the command entered and transfer program control to the required module. On entering a non-defined command, or in the absence of any command, the software simply loops through the command look-up table. The commands required by the program are passed through the byte-wide key buffer. The contents of the latter memory location is used by the command preprocessor software in transferring program control to the required module. The system hardware interacts with the key buffer either through the keypad or externally through the IEEE-488 bus (GPIB). Both sources operate in an interrupt mode.

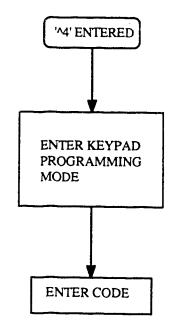

The keypad can be operated in either the normal or the keypad programming mode. In the normal mode, commands are entered in response to the displayed menu messages. The command entered is duplicated in the key buffer by the interrupt service routine executed when a key closure occurs. The keypad programming mode is basically an emulation of the GPIB bus programming mode. In the GPIB bus programming mode, the user enters a programming code string through an active talker on the bus. This latter string, comprising the key code commands entered in the preferred order of execution, is stored in the 128 byte programming code buffer. The programming mode semaphore is also set in this mode. This enables the loading of the next program

byte from the program code string into the key buffer during the ensuing program execution.

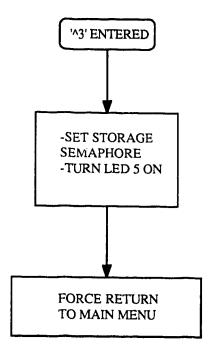

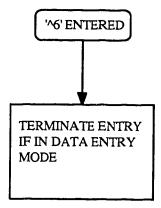

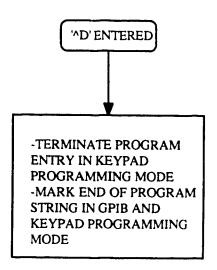

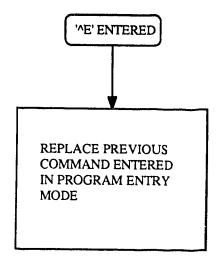

The GPIB program commands are; 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F, G, H, I, J, K, L, M, N, O, P, Q, R, S, T, U and V. The corresponding keypad commands are; 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F, ^0, ^1, ^2, ^3, ^4, ^5, ^6, ^7, ^8, ^9, ^A, ^B, ^C, ^D, ^E and ^F respectively.

#### 4.3.3 Module 0

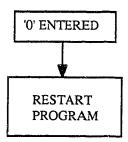

The flow diagram of this module is shown in Fig. 4.5 (page 83). This module is executed when a '0' is processed by the command preprocessor. This module restarts the wattmeter.

### 4.3.4 Module 1

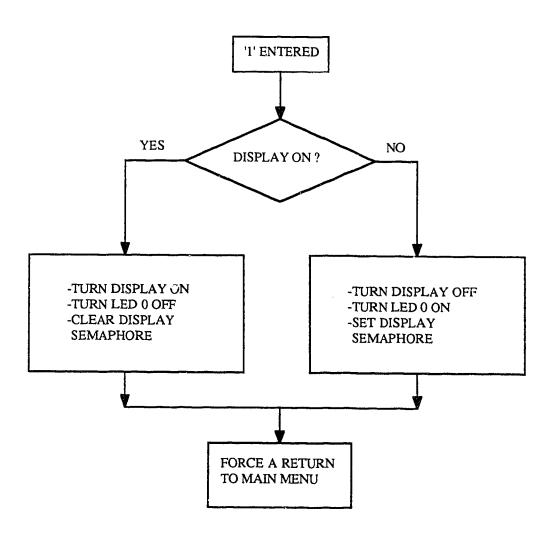

The flow diagram of this module is shown in Fig. 4.6 (page 84). This module is executed when a '1' is processed by the command preprocessor. The routines used are the LCD and bargraph display routines. The function of this module is to toggle the display between the on and off states. The status of the display is reflected on LED 0 of the bargraph display using a bit in a byte-wide memory location. The bit manipulation instructions of the 68000 microprocessor enable the ease of implementation of the bargraph display.

### 4.3.5 Module 2

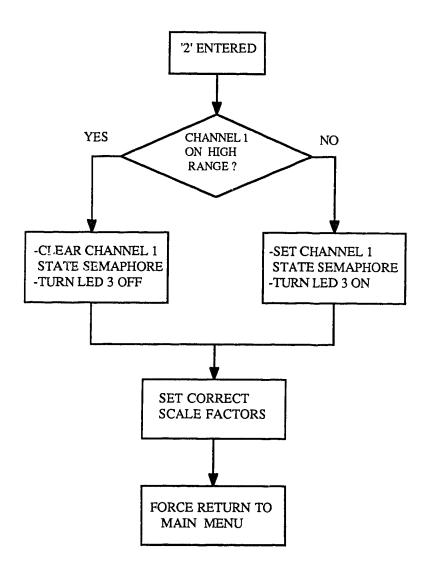

The flow diagram of this module is shown in Fig. 4.7 (page 85). This module is executed when a '2' is processed by the command preprocessor and uses the display and scale factor routines. The purpose of this module is to set the correct scale factors for the computation of the system parameters when either the 200v or the 350v range on channel 1 is being used. Following a system power-up, the 200v range is used. The range used is reflected on LED 3 of the bargraph display. Subsequently, the required current and power scale factors are computed voltage, using the scale factor routines. Following the latter procedure, the hex value FF is loaded into the key buffer. The hex value FF does not correspond to any key code. Hence, the transfer of program control to a particular module after a return to the command preprocessor module via the main menu, can only be effected when a new command is entered.

#### 4.3.6 Module 3

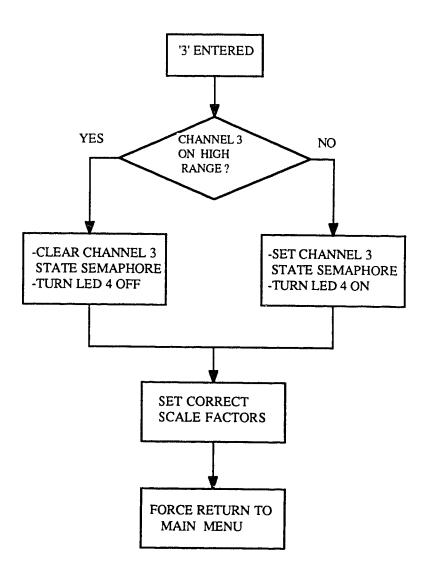

The flow diagram of this module is shown in Fig. 4.8 (page 86). This module is executed when a '3' is processed by the command preprocessor. The function of this module is similar to that of module 2. However in this case the range indication refers to channel 3. In addition, the range status is indicated on LED 4.

### 4.3.7 Module 4

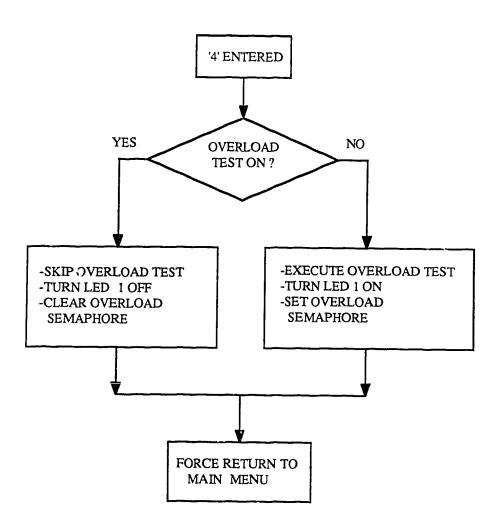

The flow diagram of this module is shown in Fig. 4.9 (page 87). This module is executed when a '4' is processed by the command preprocessor. This module uses the bargraph display routine and one of the utility routines namely; the overload test routine. The purpose of this module is to cause an execution of the overload routine or cause the program to skip over this routine following the execution of the acquisition routine. The software uses the state of the overload semaphore in determining the execution or otherwise of the overload routine. The program default mode following a system power-up or reset, is the execution of the overload test. This module is relevant during a system calibration or maintenance. The system status regarding the execution of the overload test is reflected on LED 1 of the bargraph display. Following the latter procedure, the hex value FF is loaded into the key buffer. The latter approach forces a return to the main menu and also prevents the reexecution of this module following the return.

### 4.3.8 Module 5

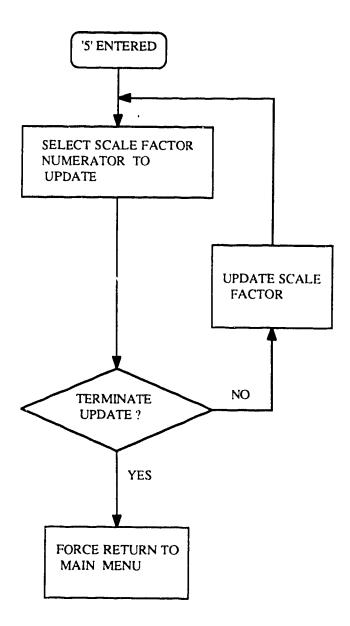

The flow diagram of this module is shown in Fig. 4.10 (page 88). This module is executed when a '5' is processed by the command preprocessor and uses the LCD display routine. The primary use of this module is the changing of the numerator of the voltage or current scale factors. This module is relevant when new scale factors need to be

programmed as a result of the replacement or aging of components. Following the execution of a '5', the sub-menu in Fig. 4.11 (page 89) is displayed. After selecting the appropriate channel, the user selects 'F', 'B' or '6 to increment, decrement or terminate scale factor updating respectively. Subsequently, the hex value FF is loaded into the key buffer.

#### 4.3.9 Module 6

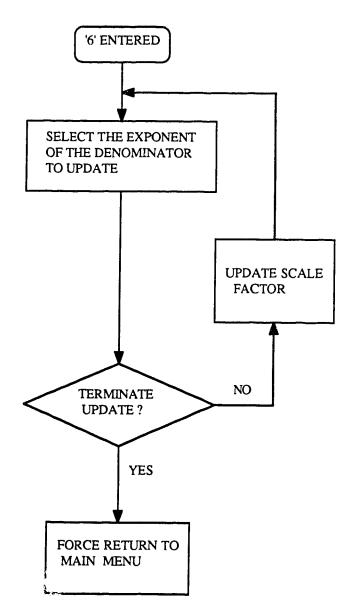

The flow diagram of this module is shown in Fig. 4.12 (page 88). This module is executed when a '6' is processed by the command preprocessor. This module uses the LCD display routine and is similar to module 5. However, the primary use of this module is the changing of the exponent of the denominator of the voltage or current scale factors. The denominators of each scale factor have a mantissa of 2.

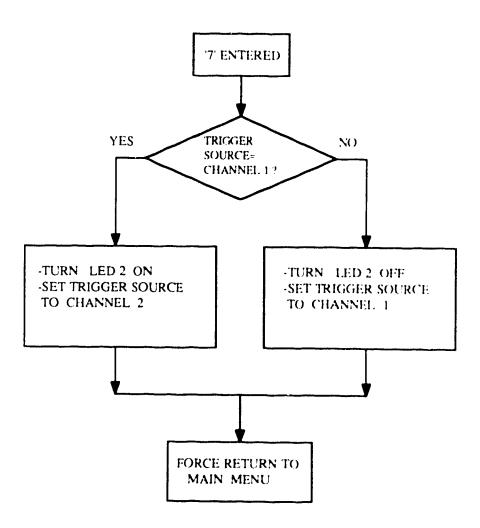

## 4.3.10 Module 7

The flow diagram of this module is shown in Fig. 4.13 (page 90). This module is executed when a '7' is processed by the command preprocessor. This module uses the bargraph display routine. Under software control using the PIA, the trigger source switch is employed in selecting either channel 1 or channel 2 as the system trigger source. The trigger source status is indicated on LED 1 of the bargraph display. Following a system power-up or reset, channel 1 is

used as the system trigger source. The hex value FF is loaded into the key buffer prior to exiting this module.

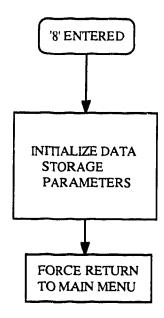

## 4.3.11 Module 8

The flow diagram of this module is shown in Fig. 4.14 (page 91). This module is executed when a '8' is processed by the command preprocessor. This module reinitializes the data storage parameters. This module sets the size of the data stored in RAM to zero in addition to setting the data pointer to the base of the RAM location. The data pointer points to the next free memory location for the storage of the LCD display data. Following the execution of this module, a return to the main menu is performed.

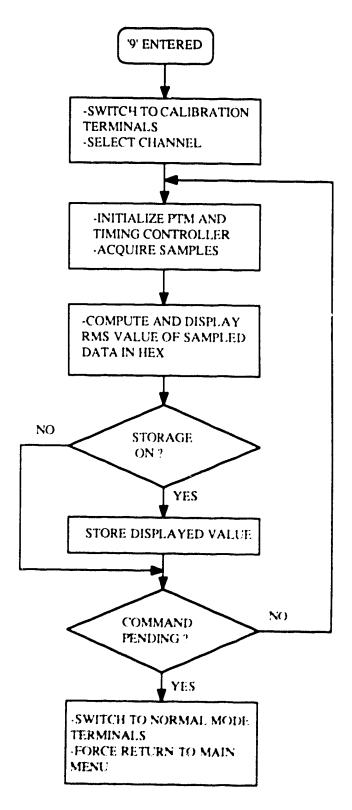

## 4.3.12 Module 9

The flow diagram of this module is shown in Fig. 4.15 (page 92). This module is executed when a '9' is processed by the command preprocessor. This module uses the AC acquisition, display and AC computation routines. The AC acquisition routine enables the acquisition of samples for a single cycle of the input signal. The AC computation routines utilize the procedure mentioned in section 2.3.4. The purpose of this module is to compute and display the rms value of the sampled data in the presence of an AC signal on the calibration terminal. On entering this module, the system mode switch is switched over to the

$$= \frac{1}{n} \left[ \frac{(1-\cos(n\theta))(1-\cos\theta) + \sin\theta\sin(n\theta)}{(1-\cos\theta)^2 + \sin^2\theta} \right]$$

now

$$(n + \Delta)h = 2m\pi$$

=>  $(n + \Delta)kh = 2mk\pi$

$nkh = 2mk\pi - \Delta kh$

=>  $n\theta = 2mk\pi - \Delta kh$

=>  $sin(n\theta) = -sin(\Delta kh)$

and  $cos(n\theta) = cos(\Delta kh)$

hence;

$$\beta_{k}^{A} = \frac{1}{n} \left[ \frac{(1 - \cos(\Delta\theta))(1 - \cos\theta) - \sin\theta\sin(\Delta\theta)}{2(1 - \cos\theta)} \right]$$

$$= \frac{1}{n} \left[ \sin^{2}\left(\frac{\Delta kh}{2}\right) - \frac{1}{2}\cot\left(\frac{kh}{2}\right)\sin(\Delta kh) \right]$$

## 2.3.2 Trapezoidal rule

The expression for n+1 samples using the trapezoidal rule is:

$$\mathbf{A}\mathbf{y}_{j} = \frac{1}{n} \left[ 0.5\mathbf{y}_{0} + \sum_{j=1}^{n-1} \mathbf{y}_{j} + 0.5\mathbf{y}_{n} \right]$$

$$= \frac{1}{n} \left[ \sum_{j=0}^{n-1} \mathbf{y}_{j} - 0.5\mathbf{y}_{0} + 0.5\mathbf{y}_{n} \right]$$

(2.16)

The corresponding error coefficient relating to the sine term of the error expression is:

$$=> \alpha_{k}^{T} = \lambda \sin(jkh)$$

$$= \frac{1}{n} \left[ \cot\left(\frac{k h}{2}\right) \sin^{2}\left(\frac{\Delta k h}{2}\right) + \frac{\sin(\Delta k h)}{2} - \frac{\sin 0}{2} + \frac{\sin(nkh)}{2} \right]$$

$$= \frac{1}{n} \left[ \cot\left(\frac{k h}{2}\right) \sin^{2}\left(\frac{\Delta k h}{2}\right) + \frac{\sin(\Delta k h)}{2} - \frac{\sin 0}{2} - \frac{\sin(\Delta k h)}{2} \right]$$

$$= \frac{1}{n} \left[ \cot\left(\frac{k h}{2}\right) \sin^{2}\left(\frac{\Delta k h}{2}\right) \right]$$

The corresponding error coefficient relating to the cosine term of the error expression is:

$$\beta_{k}^{T} = A \cos(jkh)$$

$$= \frac{1}{n} \left[ \sin^{2} \left( \frac{\Delta kh}{2} \right) - \frac{1}{2} \cot \left( \frac{k h}{2} \right) \sin(\Delta kh) - \frac{\cos 0}{2} + \frac{\cos(nkh)}{2} \right]$$

$$= \frac{1}{n} \left[ \sin^2 \left( \frac{\Delta kh}{2} \right) - \frac{1}{2} \cot \left( \frac{k h}{2} \right) \sin(\Delta kh) - \frac{\cos 0}{2} + \frac{\cos(\Delta kh)}{2} \right]$$

$$= -\frac{1}{2n} \left[ \cot \left( \frac{k h}{2} \right) \sin(\Delta kh) \right]$$

## 2.3.3 NBS approach

The expression for n+1 samples using the NBS approach [12] is:

$$Ay_{j} = \frac{1}{n + \Delta} \left( \sum_{j=0}^{n-1} y_{j} + \Delta * y_{n} \right)$$

(2.17)

The corresponding error coefficient relating to the cosine term of the error expression is:

$$= \frac{1}{n + \Delta} \left( \cot \left( \frac{k h}{2} \right) \sin^2 \left( \frac{\Delta k h}{2} \right) + \frac{\sin(\Delta k h)}{2} + \Delta \sin(nkh) \right)$$

$$= \frac{1}{n + \Delta} \left[ \cot \left( \frac{k h}{2} \right) \sin^2 \left( \frac{\Delta k h}{2} \right) + \frac{\sin(\Delta k h)}{2} \right]$$

$$- \Delta \sin(\Delta k h)$$

$$= \frac{1}{n + \Delta} \left[ \cot \left( \frac{k h}{2} \right) \sin^2 \left( \frac{\Delta k h}{2} \right) + \frac{1}{2} (1 - 2 * \Delta) \sin(\Delta k h) \right]$$

The corresponding error coefficient relating to the cosine term of the error expression is:

$$= \frac{1}{n + \Delta} \left[ \sin^2 \left( \frac{\Delta kh}{2} \right) - \frac{1}{2} \cot \left( \frac{k h}{2} \right) \sin(\Delta kh) \right]$$

$$+ \Delta \cos(nkh)$$

$$= \frac{1}{n + \Delta} \left[ \sin^2 \left( \frac{\Delta kh}{2} \right) + \Delta \cos(\Delta kh) \right]$$

$$- \frac{1}{2} \cot \left( \frac{k h}{2} \right) \sin(\Delta kh)$$

# 2.3.4. Mc led Trapezoidal Approach

The expression for n+1 samples for an approach proposed by Zu-Liang [11] and referred to in the Modified

Trapezoidal Method (MTM) is:

$$\mathbf{A}\mathbf{y}_{j} = \frac{1}{n+\Delta} \left[ 0.5\mathbf{y}_{0} + \sum_{j=1}^{n-1} \mathbf{y}_{j} + 0.5\mathbf{y}_{n} + \frac{\Delta}{2} (\mathbf{y}_{n} + \mathbf{y}_{n+\Delta}) \right] (2.18)$$

$$= \frac{1}{n+\Delta} \left[ \sum_{j=1}^{n-1} \mathbf{y}_{j} + 0.5 (1+\Delta) (\mathbf{y}_{0} + \mathbf{y}_{n}) \right] (2.19)$$

since  $y_0 = y_{n+\Delta}$  for a measurement interval covering of an integral number of signal cycles.

The corresponding error coefficient relating to the sine term of the error expression is:

$$\alpha_{k}^{N} = \mathbf{A} \sin(jkh)$$

$$= \frac{1}{n+\Delta} \left[ \cot\left(\frac{kh}{2}\right) \sin^{2}\left(\frac{\Delta kh}{2}\right) - \frac{\Delta}{2} \left(\sin(nkh) + \sin(0)\right) \right]$$

$$= \frac{1}{n+\Delta} \left[ \cot\left(\frac{kh}{2}\right) \sin^{2}\left(\frac{\Delta kh}{2}\right) - \frac{\Delta}{2} \sin(\Delta kh) \right]$$

The corresponding error coefficient relating to the cosine term of the error expression is:

$$\beta_{k}^{N} = A \cos(jkh)$$

$$= \frac{1}{n+\Delta} \left[ -\frac{1}{2} \cot\left(\frac{k h}{2}\right) \sin(\Delta kh) + \frac{\Delta}{2} \left(\cos(nkh) + \cos(0)\right) \right]$$

$$= \frac{1}{n+\Delta} \left[ -\frac{1}{2} \cot\left(\frac{k h}{2}\right) \sin(\Delta kh) + \frac{\Delta}{2} \left(\cos(\Delta kh) + 1\right) \right]$$

$$= \frac{1}{n+\Delta} \left[ -\frac{1}{2} \cot\left(\frac{k h}{2}\right) \sin(\Delta kh) + \Delta\cos^{2}\left(\frac{\Delta kh}{2}\right) \right]$$

$$= \frac{1}{n+\Delta} \left[ \Delta\cos^{2}\left(\frac{\Delta kh}{2}\right) - \frac{1}{2} \cot\left(\frac{k h}{2}\right) \sin(\Delta kh) \right]$$

# 2.4 Determination of delta

Delta ( $\Delta$ ) is determined by employing a hardware scheme which resolves each sampling interval into 16 discrete sub-intervals. The sub-interval in which the end of a period occurs, is divided by 16 to obtain delta. Delta can thus obtained to the nearest one-sixteenth.

This scheme results in a more precise estimate of delta as opposed to the interpolation schemes suggested in the implementation of precision digital sampling meters [12] [14].

In order to minimize the errors resulting from a

deviation of the computed interpolated value  $\Delta$  and the actual value of  $\Delta,$  the sample size is adjusted so that  $|\Delta|$   $\leq$  0.5 .

# 2.5 Computation of the desired parameters

The DC parameters of voltage, current and power are computed using the trapezoidal rule, while the corresponding AC parameters are computed using the processing method outlined in section 2.3.4.

The relationship between the parameters required, the value of  $y_j$  in equation 2.8 ,and the further computations required after applying the required processing method, are summarized below.

| Parameter  | Yj                 | Further computations |

|------------|--------------------|----------------------|

| required   |                    | required             |

| AC voltage | $(v_j)^2$          | compute square-root  |

| AC current | (i <sub>j</sub> )² | compute square-root  |

| AC power   | $v_{j}^{i}$        | ·                    |

| DC voltage | $\mathbf{v}_{j}$   |                      |

| DC current | i <sub>j</sub>     |                      |

| DC power   | $v_{j}i_{j}$       |                      |

$\boldsymbol{v}_{j}$  and  $\boldsymbol{i}_{j}$  are the respective sampled values of voltage and current.

Due to the use of fixed point arithmetic for the computation of most of the AC parameters, the following modified formula is used.

$$\mathbf{A}\mathbf{y}_{j} = \frac{1}{16n + 16\Delta} \left( 16 \sum_{j=1}^{n-1} \mathbf{y}_{j} + 0.5(16+16\Delta) (\mathbf{y}_{0} + \mathbf{y}_{n}) \right) \quad (2.20)$$

The above equation is used in the determination of power.

The determination of the rms values however, includes a correction for any dc terms present. The resulting expression is thus;

RMS value =

$$\sqrt{A(y_i^2) - (Ay_i)^2}$$

(2.21)

where  $y_j$  is  $v_j$  or  $i_j$  depending on the parameter required.

and A is the processing method used

Another parameter, the power factor (P.F) [11] for sinusoidal signals, is determined as follows:

a) A Single-phase system

$$P.F. = \frac{POWER}{V_{im} i_{im}}$$

(2.22)

b) A Balanced three-phase three-wire system

P.F. =

$$\left[ \frac{(P1 + P2)^2}{(P1+P2)^2 + 3(P2-P1)^2} \right]^{\frac{1}{2}}$$

(2.23)

where  $v_{jm}$  is the maximum sampled voltage value  $i_{jm}$  is the maximum sampled current value P1 and P2 are the phase powers, with P2 being the larger value.

# 2.6 Summary of results

The relationships obtained for the various processing methods in section 2.3.4., are compared using the relevant parameters employed in the practical implementation of the meter. The error values thus obtained would have been obtained if error-free analog input devices as well as a perfect analog-to-digital conversion process occurred in the meter.

From the equations obtained in section 2.3.4, it is observed that the error coefficients are functions of  $\Delta$ (delta), k (the harmonic number), h (the sampling interval in radians) and n the number of samples processed. In the actual meter implementation, a fixed sampling interval of  $32\mu s$  and an acquisition cycle of one period of the input signal cycle are used. In addition, for the processing method used, the sample size is adjusted to ensure  $|\Delta| \leq 0.5$ . Frequencies around the nominal power line frequency of 60 hz which result in values of delta which satisfy the following relation are used.

$$\{ 0 < |\Delta| \le 0.5 \}$$

The frequencies employed range from 59.925 hz to 60.035 hz

in increments of 0.005 hz.

Graphical representations of the results deduced in section 2.3.4 and the relationships between the various processing method and the approach employed, are indicated in figs. 2.1 - 2.12. The  $32\mu s$  sampling interval used in the instrument is employed for these representations.

Figs. 2.1 - 2.8 are plotted for signal harmonics of 1 ( the fundamental), 2, 10 and 20. In figs. 2.9 - 2.12, harmonics from 1 to the number of samples processed in a cycle (521 in the cases analyzed) are used. Figs. 2.1 - 2.6 indicate the relationship between the ratios of the error coefficients of the average, trapezoidal and NBS approach to that of the procedure used in this work. Figs 2.1 - 2.3 refer to the alpha ratios while figs. 2.4 - 2.6 are for the beta ratios. Figs 2.7 and 2.8 indicate the relationship between the values of error coefficients  $\alpha_k^N$  and  $\beta_k^N$  respectively for signal harmonics of 1 (fundamental), 2, 10 and 20.

Figs. 2.1 - 2.5 indicate a general decrease in the error ratios with increasing harmonic number. The processing method used in this work results in an improvement of the alpha error coefficient of the signal fundamental frequency component by a factor of about 10<sup>5</sup> compared with the component calculated from the average, trapezoidal and NBS methods. The beta error coefficients that result from using the average and trapezoidal methods are identical, with an improvement of about 10<sup>5</sup> being

GRAPH OF ALPHA RATIOS VS DELTA (AVERAGE/APPROACH USED) FIG. 2.1

GRAPH OF ALPHA RATIOS VS DELTA (TRAPEZOIDAL/PROCEDURE USED) FIG. 2.2

GRAPH OF ALPHA RATIOS VS DELTA (NBS/PROCEDURE USED) FIG. 2.3

GRAPH OF BETA RATIOS VS DELTA (AVERAGE/PROCEDURE USED) FIG. 2.4

GRAPH OF BETA RATIOS VS DELTA (TRAPEZOIDAL/PROCEDURE USED) 2.5 FIG.

FIG. 2.6 GRAPH OF BETA RATIOS VS DELTA (NBS/PROCEDURE USED)

FIG. 2.7 GRAPH OF ALPHA VS DELTA FOR THE PROCEDURE USED (MTM)

GRAPH OF BETA VS DELTA FOR THE PROCEDURE USED (MTM) FIG. 2.8

FIG. 2.9 GRAPH OF ABSOLUTE VALUE OF ERROR COEFFICIENTS VS HARMONIC NUMBER FOR A FREQUENCY OF 59.925 hz

2.10 GRAPH OF ABSOLUTE VALUE OF ERROR COEFFICIENTS VS HARMONIC NUMBER FOR A FREQUENCY OF 59.98 hz FIG.

FIG. 2.11 GRAPH OF ABSOLUTE VALUE OF ERROR COEFFICIENTS VS HARMONIC NUMBER FOR A FREQUENCY OF 60.035 hz

GRAPH OF ABSOLUTE VALUE OF THE RATIO ALPHA/BETA VS HARMONIC NUMBER FIG. 2.12

obtained with the processing method used in this work. From fig. 2.6, it is observed that the beta error ratios are approximately equal irrespective of the order of the harmonic. Figs. 2.9 - 2.12 relate to the processing method used. The absolute values of alpha and beta (figs. 2.9 - 2.11) as well as their ratios (fig. 2.12), are obtained for harmonics from 1 to 521. The choice of frequencies of 59.925 hz, 59.98hz and 60.035 hz was made because they result in delta values close to 0.5, 0 and -0.5 respectively. Fig 2.12 indicates the absolute values of the ratios of alpha and beta obtained in figs. 2.9 - 2.11.

In determining the error contribution to a meter reading for a particular harmonic term, the worst case contribution will correspond to the largest value of either alpha or beta at that harmonic. As outlined previously, if the starting point of the acquisition cycle could be varied, then in principle the error term due to a particular harmonic could be minimized.

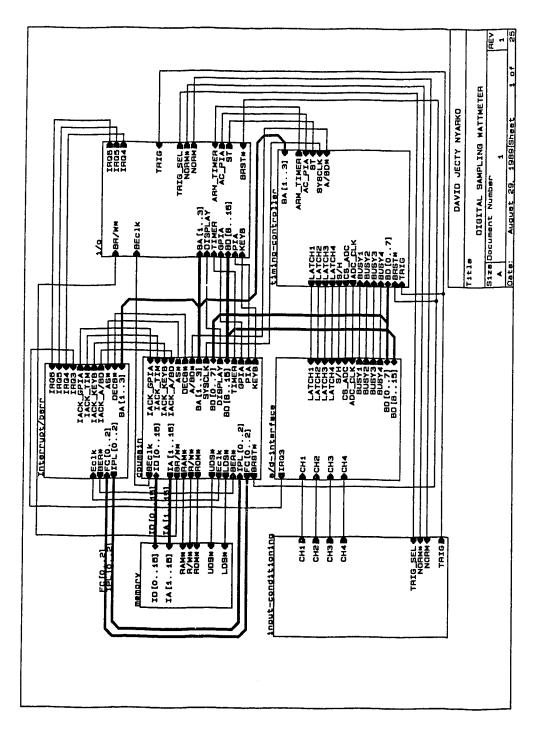

## 3. DIGITAL SAMPLING WATTMETER HARDWARE

The choice of the system hardware is governed by the following design considerations:

- (a) A highly accurate system using off-the-shelf components.

- (b) Adequate speed in handling 12-bit values and the mathematical manipulations to be performed on the latter.

An 8 Mhz zero-wait state 68000 microprocessor based system is employed for the current design. The instruction set of this processor incorporates various data manipulation instructions suitable for the mathematical computations involved. The hardware also facilitates the incorporation of debugging support which simplifies system maintenance.

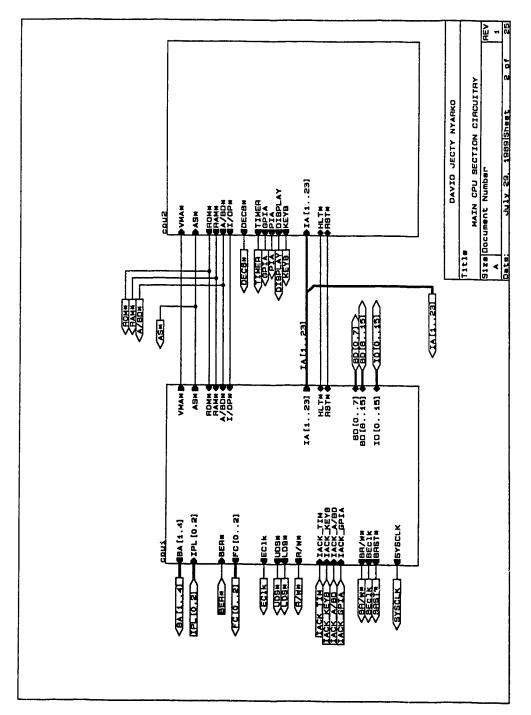

A block diagram of the system hardware is shown in Fig. 3.1 (page 46). The system sub-units are; the CPU module, the I/O module, the timing controller module, the analog-to-digital interface module and the input-conditioning module. A more detailed block diagram showing the interconnecting signal lines are given in Fig. A.1.

#### 3.1 CPU module

The block diagram of this module is shown in Fig. 3.2 (page 46). This circuit consists of the following:

a) the microprocessor circuit,

- b) the memory circuit,

- c) the interrupt and watchdog timer circuitry.

A more detailed block diagram showing the control signal

interconnections is shown in the appendix as Fig. A.2.

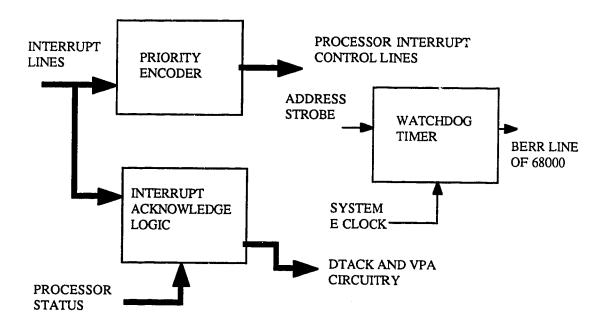

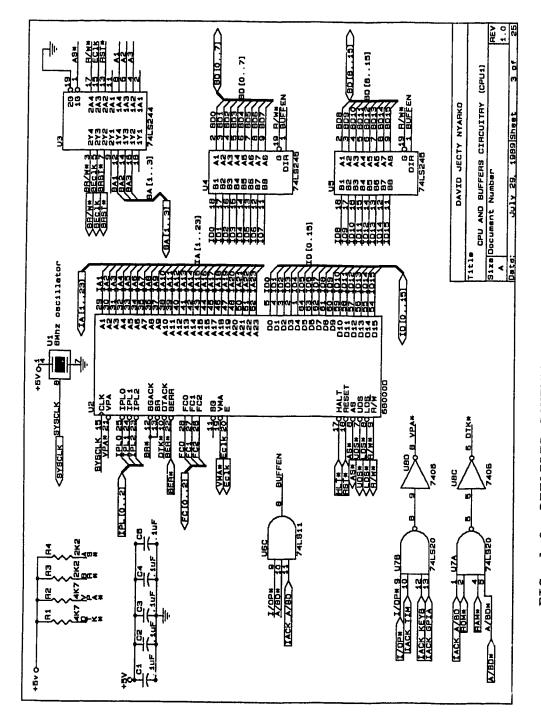

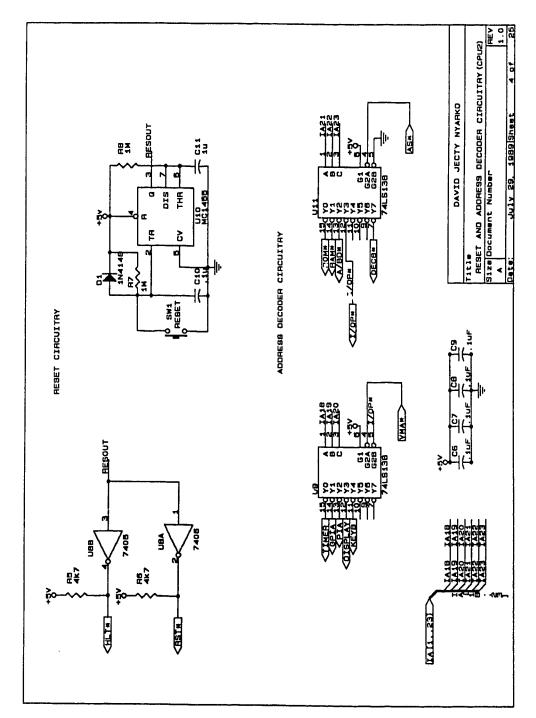

# 3.1.1 Microprocessor circuitry

The block diagram of this circuit is shown in Fig. 3.3 (page 47). The heart of this circuitry is a 68000 microprocessor clocked by an 8 Mhz system clock [9]. The reset circuitry generates the required reset signal on power-up or following the assertion of the externally provided reset switch.

The system memory map shown in Fig. 3.4 (page 48), indicates a partial decoding of the 16 megabyte direct address space. This scheme results in a simple implementation of the decoding scheme required for the microprocessor peripheral devices. The I/O and A/board address spaces are further decoded as indicated in Fig. 3.5 (page 49).

The DTACK and VPA generation circuitry generate the required data transfer acknowledgement signals for asynchronous and synchronous data transfers respectively, between the microprocessor and external devices.

Data, address and control line buffers are provided for communication external to the microprocessor circuitry.

The detailed schematic of this circuitry is shown in

Fig. A.3 and Fig. A.4.

# 3.1.2 Memory circuitry

The block diagram of this circuitry is shown in Fig. 3.6 (page 50). The 16-bit data bus of the microprocessor necessitates the use of a pair of byte-wide memory devices. Two 8 kB byte-wide EPROMs having a maximum access time of 200ns, as well as a pair of 32 kB byte-wide static RAMs having a maximum access time of 150ns are used. The EPROMs store the program code and permanent data. The latter devices are decoded at a base address of 000000 hex. This scheme results in a simplified reset and interrupt circuitry thus further simplifying the system design. The static rams are decoded at a base address of 200000 hex. The RAMS are employed for the storage of sampled data values as well as temporary variables. 8k words are allocated for the storage of the sampled data values. The detailed circuitry of this sub-unit is indicated in Fig. A.5.

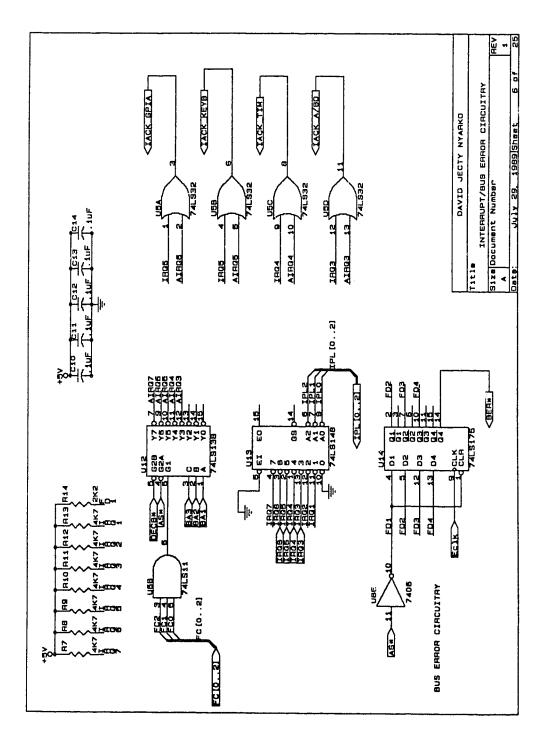

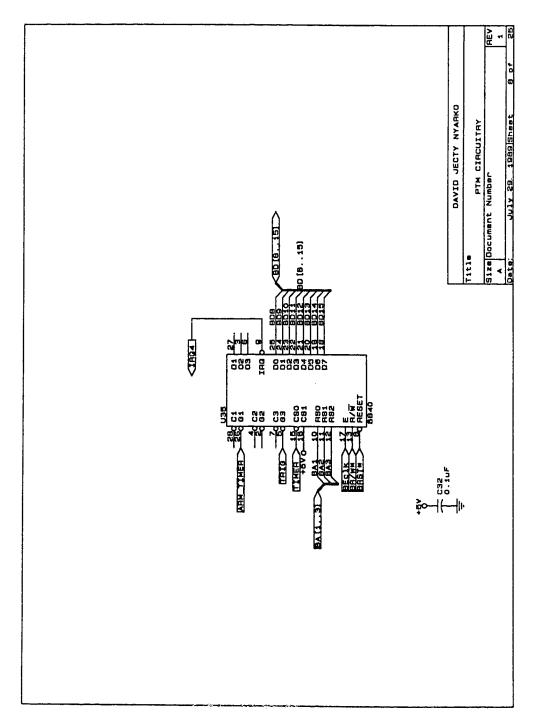

# 3.1.3 Interrupt and Watchdog timer circuitry

The block diagram of this circuitry is shown in Fig. 3.7 (page 51). This circuitry encodes the interrupt signals and also generates the required interrupt acknowledgement signals. The interrupt encoding scheme results in the following priority scheme for the servicing of interrupts:

the GPIA circuitry, the keyboard controller circuitry and the PTM circuitry.

The watchdog timer asserts the microprocessor bus error line following the absence of a data transfer acknowledge signal. The assertion of the bus error line occurs 40 system clock cycles following the start of a data transfer sequence.

The detailed circuit diagram is shown in Fig. A.6.

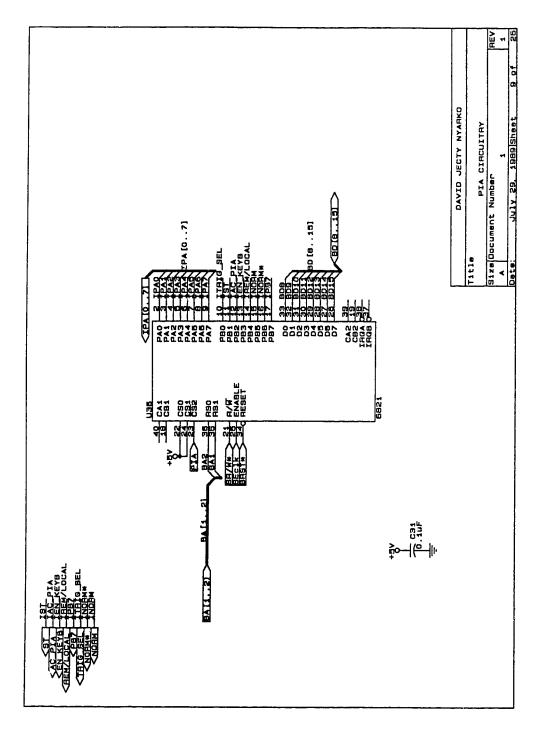

## 3.2 I/O module

This section consists of five individual subunits as indicated in the block diagram of Fig. 3.8 (page 52). The microprocessor peripherals in this section interface with the 68000 microprocessor via the synchronous control signal lines. A more detailed block diagram showing the control signal interconnections is shown in the appendix as Fig. A.7.

The PTM subunit is centered around the 6840 programmable timer module. This unit serves two main functions. It is employed in the detection of the presence of an AC or DC signal on the trigger input line. This simple scheme enables the use of an interrupt approach through a device geared towards the efficient generation of interrupts. Secondly, the timer module is employed in the determination of the trigger input line signal frequency. The detailed circuit diagram of this circuit is

shown in Fig. A.8.

The PIA circuitry is centered around the 6821 peripheral interface adapter IC. Both peripheral ports of the latter device are configured as outputs. In essence, this circuitry functions as a microprocessor controlled output latch. The detailed circuit diagram of this circuitry is shown in Fig. A.9

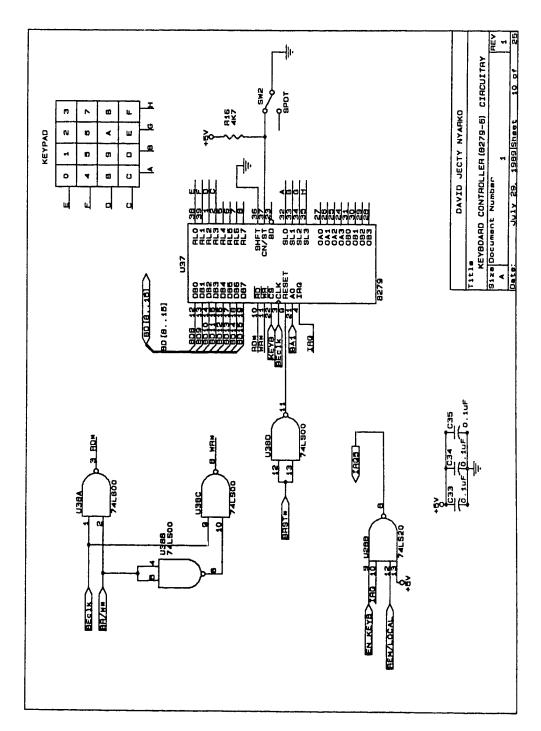

The keyboard circuitry is centered around the Intel 8279 programmable keyboard and display controller IC [7]. The main function of this circuitry is to provide the necessary interface between the microprocessor and the input terminal. This circuit also decodes and debounces the keypad switches. The 4 by 4 keypad matrix and a single pole double throw switch result in 32 unique keypad combinations for the various wattmeter functions. An interrupt driven scheme is employed in determining a key closure. The detailed circuit diagram of this section is shown in Fig. A.10.

The display circuitry uses 2 devices for display of the program results as well as the system status. The primary unit is a 4 line by 20 column LCD display. In addition, a 10 segment tri-colour bargraph is also used. The various segments of the latter device being labelled 0 to 9. The LCD display is connected to the microprocessor as a memory mapped device at address 6C0000 hex. The LCD display unit includes an onboard character generator ROM. The latter

calibration terminals under software control. The sub-menu of Fig. 4.11. is next displayed. The user next selects the required channel. This is followed by the initialization the PTM as well as the timing controller. acquisition routine is next executed. Prior to the execution of the acquisition routine, the keypad is disabled through the PIA and enabled following the completion of the data acquisition. The multiplication, summation and square-root computation routines are then employed in determining the root-mean-square value of the acquired data. The results are subsequently displayed on the LCD display unit. The displayed values are then stored in the storage location in ram provided the storage of data previously been enabled. The above procedure is executed until another command is entered. Following that, the system mode switch is connected to channels 1 to 4 and program execution returns to the main menu.

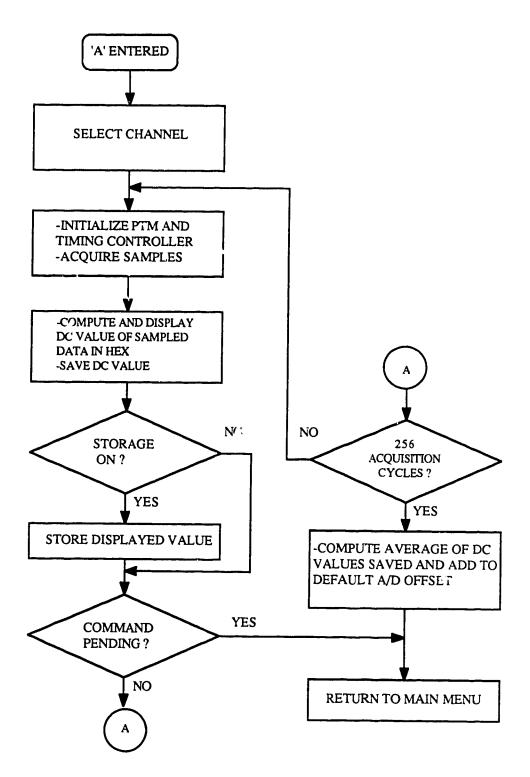

## 4.3.13 Module 10

The flow diagram of this module is shown in Fig. 4.16 (page 93). This module is executed when an 'A' is processed by the command preprocessor. This module uses the DC acquisition, display and DC computation routines. The DC acquisition routine results in the acquisition of 1024 samples. The DC computation routines utilize the trapezoidal rule procedure mentioned in section 2.3.2. The