#### Design, Analysis, and Control of the Modular Multilevel DC/DC Converter for Medium- and High-Voltage DC Grids

By

Ramin Razani

A thesis submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Energy System

Department of Electrical and Computer Engineering University of Alberta

© Ramin Razani, 2022

## Abstract

Nowadays, renewable energy sources have gained escalating importance due to environmental and economic reasons. However, these energy sources are primarily located in remote areas and distant from load centers. High-voltage dc (HVDC) and medium-voltage dc (MVDC) systems have been proposed in the last decades for efficient and reliable integration of renewable energy resources. To date, a noticeable number of these dc systems are established around the world. Recently, researchers have proposed the concept of "DC grids," which can be realized by connecting the existing point-to-point dc systems. This structure can improve the efficiency and stability of the power system. However, one of the most concerning challenges related to this concept is the interconnection of already built dc systems. Because existing dc systems are built through time, they possibly have different voltage levels and grounding systems. To address this challenge, the dc/dc modular multilevel converter (MMC) is proposed in the literature as one of the most promising solutions. This converter offers the advantages of modularity, scalability, and high efficiency.

Few studies have been conducted on the modeling and control of the dc/dc MMC. The literature falls short in several aspects, such as improved design, analysis of operation limits, fault-tolerant operation, converter analysis under uncertainty, and development of advanced controllers and efficient fault-blocking capability. This research aims to 1) develop an augmented design approach that considers both control and hardware aspects of the converter, 2) investigate the operation limit of the hybrid dc/dc MMC caused by the capacitors voltages unbalance, 3) develop a tailored fault-tolerant operation strategy without additional submodules (SMs), 4) analyze the unsymmetrical operation of the dc/dc MMC caused by

parametric uncertainty, 5) develop an advanced controller based on the model predictive control for the dc/dc MMC, and 6) realize an efficient fault-blocking capability by proper selection of SMs.

The first study in this thesis facilitates the dc/dc MMC design with a smaller number of SMs and higher efficiency. Unlike the previous literature, the analytical results of the second study show that the capacitors voltages balance in the hybrid dc/dc MMC limits the operation range of the converter. In the third study, first, the unique features of the dc/dc MMC are investigated. These features make the fault-tolerant operation possible without the need for additional SMs. Then, utilizing these features, a tailored fault-tolerant operation strategy is developed to cope with several SMs failures. When the parametric uncertainty comes into action, it can force the converter to work in unsymmetrical conditions. The fourth study develops steady-state models representing the behavior of the converter in unsymmetrical conditions, and then the maximum tolerable variation of parameters is found in different practical cases. An advanced controller based on the model predictive control is developed in the fifth study to improve the steadystate and transient performances of the dc/dc MMC. Finally, an efficient fault-blocking capability is realized by adequately selecting the number and type of SMs. Detailed timedomain simulations under the MATLAB/Simulink environment validate the analytical results. This research contributed to the fundamental understanding of the dc/dc MMC operation and significantly improved the converter efficiency, reliability, and steady-state and dynamic performances.

# Preface

This thesis is an original work by Ramin Razani. As detailed in the following, some chapters of this thesis have been published or submitted for publication as scholarly articles in which Professor Yasser Abdel-Rady I. Mohamed was the supervisory author and has contributed to concepts formation and the manuscript composition.

Chapter 3 has been published as R. Razani and Y. A-R. I. Mohamed, "Augmented Design of DC/DC Modular Multilevel Converter Improving Efficiency and Reducing Number of SMs," in *IEEE Transactions on Power Delivery*, vol. 35, no. 6, pp. 2905-2915, Dec. 2020.

Chapter 4 has been published as R. Razani and Y. A-R. I. Mohamed, "Operation Limits of the Hybrid DC/DC Modular Multilevel Converter for HVdc Grids Connections," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 9, no. 4, pp. 4459-4469, Aug. 2021.

Chapter 5 has been published as R. Razani and Y. A-R. I. Mohamed, "Fault-Tolerant Operation of the DC/DC Modular Multilevel Converter Under Submodule Failure," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 9, no. 5, pp. 6139-6151, Oct. 2021.

Chapter 6 has been published as R. Razani and Y. A-R. I. Mohamed, "Analysis of the Unsymmetrical Operation of the DC/DC MMC Considering the DC-Link Impedance," in *IEEE Transactions on Power Delivery*, vol. 37, no. 3, pp. 1723-1733, June 2022.

Chapter 7 has been published as R. Razani and Y. A-R. I. Mohamed, "Model Predictive Control of Non-Isolated DC/DC Modular Multilevel Converter Improving the Dynamic Response," in *IEEE Open Journal of Power Electronics*, vol. 3, pp. 303-316, 2022.

# Acknowledgment

I would like to thank my supervisor, Professor Yasser Abdel-Rady I. Mohamed, for his invaluable guidance and endless support throughout this work. Without his guidance and encouragement, I could not have completed this work.

I also wish to express my thanks to the members of the thesis examination committee: Prof. Ali Mehrizi-Sani, Prof. Greg Kish, Prof. Hao Liang, and Prof. Yunwei (Ryan) Li. The valuable feedback provided by the committee members was much appreciated.

I would like to gratefully acknowledge the financial support provided by the Alberta Innovates– Technology Futures Scholarships. I am truly honored and thankful to receive this prestigious scholarship.

# Contents

| Abstract  | ii                                                                 |

|-----------|--------------------------------------------------------------------|

| Preface   | iv                                                                 |

| Acknowle  | edgmentv                                                           |

| Contents. | vi                                                                 |

| Figures   | xi                                                                 |

| Tables    | xvi                                                                |

| Chapter 1 | Introduction1                                                      |

| 1.1 I     | Research Motivations1                                              |

| 1.2 I     | Research Objectives                                                |

| 1.3 I     | Research Methodology                                               |

| 1.4 I     | Research Contributions4                                            |

| 1.5       | Thesis Organization4                                               |

| Chapter 2 | Literature Survey                                                  |

| 2.1 I     | solated Topologies6                                                |

| 2.1.1     | Dual Active Bridge (DAB) Topologies6                               |

| 2.1.2     | Flyback/Forward Based Topologies                                   |

| 2.2       | Non-Isolated Topologies8                                           |

| 2.2.1     | DC Autotransformer                                                 |

| 2.2.2     | Resonant Converter                                                 |

| 2.2.3     | DC Modular Multilevel Converter9                                   |

| 2.2.4     | DC/DC MMC10                                                        |

| Chapter 3 | Augmented Design of the DC/DC MMC16                                |

| 3.1       | Fopology and Mathematical Modeling of the Conventional DC/DC MMC16 |

| 3.1.1     | Topology16                                                         |

| 3.1.2                                               | Mathematical Modeling                                                                                                                                                                                                                                                     | 17                         |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 3.2 Pro                                             | pposed Augmented Design                                                                                                                                                                                                                                                   | 19                         |

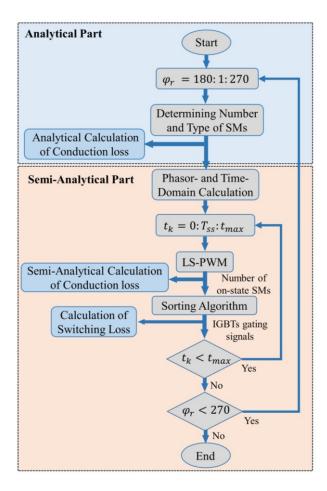

| 3.2.1                                               | Analytical Part                                                                                                                                                                                                                                                           | 20                         |

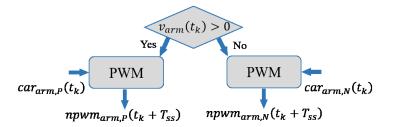

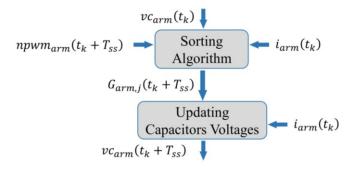

| 3.2.2                                               | Semi-Analytical Part                                                                                                                                                                                                                                                      | 23                         |

| 3.3 De                                              | sign Example 1: 20 MW DC/DC MMC                                                                                                                                                                                                                                           | 26                         |

| 3.3.1                                               | Optimum Converter Design Using the Augmented Method                                                                                                                                                                                                                       | 26                         |

| 3.3.2                                               | Simulation Results of the Designed Converter                                                                                                                                                                                                                              | 27                         |

| 3.3.3<br>Augme                                      | Comparison between Calculated Losses by Simulation and the Proposed<br>ented Design                                                                                                                                                                                       | 32                         |

| 3.4 De                                              | sign Example 2: 300 MW DC/DC MMC                                                                                                                                                                                                                                          | 33                         |

| 3.4.1                                               | Effect of DC-Link Voltage Ratio                                                                                                                                                                                                                                           | 34                         |

| 3.4.2                                               | Effect of Arm Inductance                                                                                                                                                                                                                                                  | 37                         |

| 3.5 Su                                              | mmary                                                                                                                                                                                                                                                                     | 39                         |

| Chapter 4                                           | Operation Limits of the Hybrid DC/DC MMC                                                                                                                                                                                                                                  | 40                         |

| 4.1 Hy                                              | brid DC/DC MMC                                                                                                                                                                                                                                                            | 40                         |

| 4.1.1                                               | Structure                                                                                                                                                                                                                                                                 | 40                         |

| 4.1.2                                               | Mathematical Modeling                                                                                                                                                                                                                                                     | 41                         |

| 4.1.3                                               | Determining the Number of HBSMs and FBSMs                                                                                                                                                                                                                                 | 42                         |

|                                                     | 2                                                                                                                                                                                                                                                                         | 43                         |

| 4.2 Ca                                              | pacitors Voltages Balance Analysis of the Hybrid DC/DC MMC                                                                                                                                                                                                                |                            |

| 4.2 Ca<br>4.2.1                                     |                                                                                                                                                                                                                                                                           | 45                         |

|                                                     | pacitors Voltages Balance Analysis of the Hybrid DC/DC MMC                                                                                                                                                                                                                | 45<br>46                   |

| 4.2.1                                               | pacitors Voltages Balance Analysis of the Hybrid DC/DC MMC<br>DC Component of Arm Current Higher Than the AC Component                                                                                                                                                    | 45<br>46<br>47             |

| <ul><li>4.2.1</li><li>4.2.2</li><li>4.2.3</li></ul> | pacitors Voltages Balance Analysis of the Hybrid DC/DC MMC<br>DC Component of Arm Current Higher Than the AC Component<br>DC Component of Arm Current Smaller Than the AC Component                                                                                       | 45<br>46<br>47<br>52       |

| <ul><li>4.2.1</li><li>4.2.2</li><li>4.2.3</li></ul> | pacitors Voltages Balance Analysis of the Hybrid DC/DC MMC<br>DC Component of Arm Current Higher Than the AC Component<br>DC Component of Arm Current Smaller Than the AC Component<br>Finding the Minimum Feasible Phase Difference                                      | 45<br>46<br>47<br>52<br>54 |

| 4.2.1<br>4.2.2<br>4.2.3<br>4.3 Ve                   | pacitors Voltages Balance Analysis of the Hybrid DC/DC MMC<br>DC Component of Arm Current Higher Than the AC Component<br>DC Component of Arm Current Smaller Than the AC Component<br>Finding the Minimum Feasible Phase Difference<br>rification of the Proposed Method | 45<br>46<br>47<br>52<br>54 |

| 4.4     | 4.1 | Transmitted Power                                                  | 59 |

|---------|-----|--------------------------------------------------------------------|----|

| 4.4     | 1.2 | Conversion Ratio                                                   | 60 |

| 4.4     | 4.3 | Arm Inductance                                                     | 62 |

| 4.5     | Sun | nmary                                                              | 63 |

| Chapter | : 5 | Fault-Tolerant Operation of the DC/DC MMC                          | 64 |

| 5.1     | SM  | Fault Analysis                                                     | 64 |

| 5.2     | Fau | lt-Tolerant Operation of the DC/DC MMC                             | 65 |

| 5.2     | 2.1 | Fault-Tolerant Operation Using the Inherent Redundant SMs          | 66 |

| 5.2     | 2.2 | Fault-Tolerant Operation with Reduced Arm AC Voltage               | 69 |

| 5.2     | 2.3 | Fault-Tolerant Operation with Reduced Power Transmission           | 73 |

| 5.2     | 2.4 | Fault-Tolerant Operation Considering the Arm Peak Current Limit    | 74 |

| 5.2     | 2.5 | The Proposed Fault-Tolerant Operation Strategy                     | 76 |

| 5.2     | 2.6 | Closed-Loop Controller Beside the Proposed Fault-Tolerant Approach | 78 |

| 5.3     | Sim | ulation Studies                                                    | 79 |

| 5.3     | 3.1 | Case I: Fixed Power Transmission                                   | 80 |

| 5.3     | 3.2 | Case II: Limited AC Circulating Current                            | 83 |

| 5.3     | 3.3 | Case III: Reduced Power Transmission                               | 85 |

| 5.4     | Sun | nmary                                                              | 87 |

| Chapter | : 6 | Unsymmetrical Operation of the DC/DC MMC                           | 89 |

| 6.1     | Det | ailed Steady-State Model of the DC/DC MMC                          | 89 |

| 6.1     | .1  | Average Model of the Phase-leg                                     | 89 |

| 6.1     | .2  | Arms Currents                                                      | 91 |

| 6.1     | .3  | First Harmonic of the Sum of Capacitors Voltages                   | 95 |

| 6.1     | .4  | Internal Stability Condition                                       | 96 |

| 6.2     | Sim | plified Model and Unsymmetrical Operation of the DC/DC MMC         | 97 |

| 6.2     | 2.1 | Simplified Model                                                   | 97 |

| 6.2.2     | Simplified Model for a DC/DC MMC with N-Phase-Legs           | 99  |

|-----------|--------------------------------------------------------------|-----|

| 6.2.3     | Symmetrical Operation                                        | 99  |

| 6.2.4     | Unsymmetrical Operation                                      | 99  |

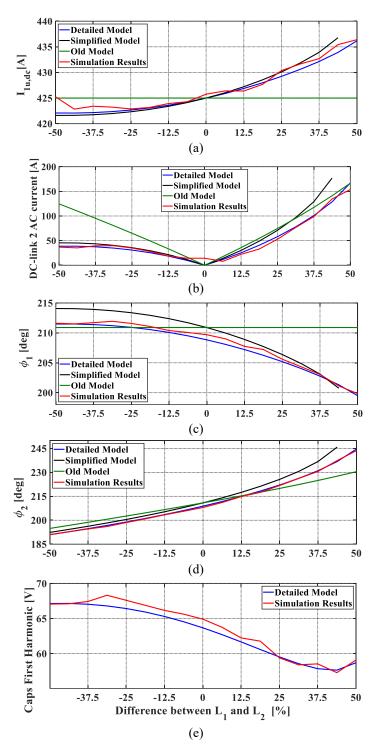

| 6.3 Ve    | rification of the Developed Steady-State Models              | 100 |

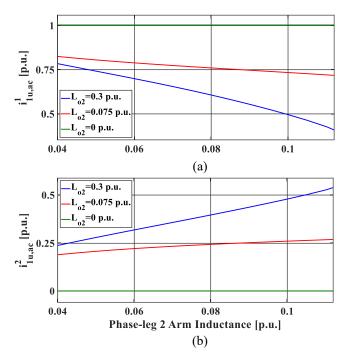

| 6.3.1     | Unsymmetrical Operation: Variation in Arm Inductances        | 101 |

| 6.3.2     | Unsymmetrical Operation: Variation in Arm AC Voltage         | 103 |

| 6.3.3     | Maximum Tolerable Variation of the Parameters                | 103 |

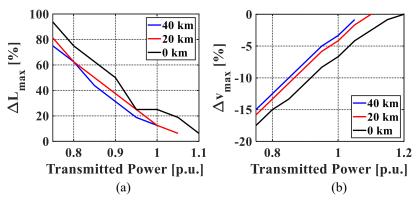

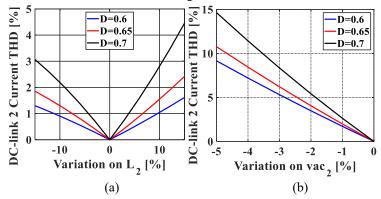

| 6.4 Ef    | fect of the System Parameters on the Unsymmetrical Operation | 106 |

| 6.4.1     | DC-Link 2 Length                                             | 106 |

| 6.4.2     | Transmitted Power                                            | 107 |

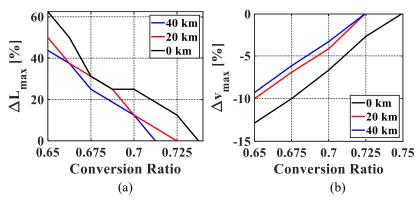

| 6.4.3     | Conversion Ratio                                             | 107 |

| 6.5 Su    | mmary                                                        |     |

| Chapter 7 | Model Predictive Control of the DC/DC MMC                    | 111 |

| 7.1 Dy    | namic Model                                                  | 111 |

| 7.1.1     | Currents and Voltages                                        | 111 |

| 7.1.2     | SMs Energies                                                 | 113 |

| 7.2 Pro   | oposed MPC Method for the DC/DC MMC                          | 116 |

| 7.2.1     | Output Current                                               | 116 |

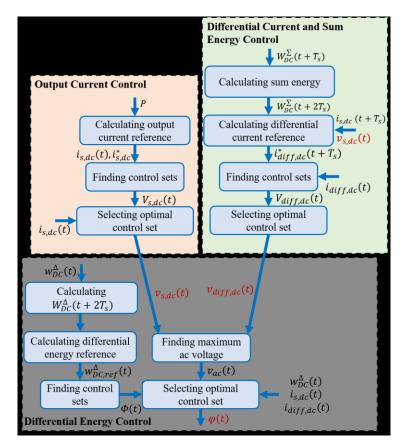

| 7.2.2     | Differential Current and Sum Energy                          | 117 |

| 7.2.3     | Differential Energy                                          | 120 |

| 7.2.4     | Overall Control Diagram                                      | 121 |

| 7.2.5     | Time-Delay Compensation                                      | 123 |

| 7.2.6     | Calculation Time [63-65]                                     | 123 |

| 7.3 Sir   | nulation Studies                                             | 125 |

| 7.3.1     | Case Study I: Steady-State                                   | 126 |

| 7.3.2     | Case Study II: Transient Mode Performance                    |     |

| 7.3      | .3   | Case Study III: Parametric Uncertainty                |

|----------|------|-------------------------------------------------------|

| 7.4      | Sum  | 13:                                                   |

| Chapter  | 8    | Realization of an Efficient Fault-Blocking Capability |

| 8.1      | DC   | Fault Analysis                                        |

| 8.2      | Prop | bosed Efficient Topology138                           |

| 8.2      | .1   | Fault-Current Blocking Requirements                   |

| 8.3      | Imp  | roving the Efficiency139                              |

| 8.4      | Sim  | ulation Studies                                       |

| 8.4      | .1   | Load Transient Operation                              |

| 8.4      | .2   | Steady-State Operation                                |

| 8.4      | .3   | Fault Analysis                                        |

| 8.5      | Sun  | 148 nmary                                             |

| Chapter  | 9    | Conclusion and Future Work                            |

| 9.1      | Con  | clusion149                                            |

| 9.2      | Futu | re Work                                               |

| Appendi  | x    |                                                       |

| Bibliogr | aphy |                                                       |

# Figures

| Figure 1-1 Organization of the thesis                                                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-1 Two-level high-voltage DAB [3]6                                                                                                                                                                                                                                  |

| Figure 2-2 Modular Multilevel DAB [3]7                                                                                                                                                                                                                                      |

| Figure 2-3 a) Modular dc/dc converter based on flyback/forward, b) dc/dc converter based on                                                                                                                                                                                 |

| the flyback/forward with centralized coupled inductor [4]8                                                                                                                                                                                                                  |

| Figure 2-4 DC autotransformer [4]9                                                                                                                                                                                                                                          |

| Figure 2-5 Single-stage resonant converter [15]9                                                                                                                                                                                                                            |

| Figure 2-6 dc modular multilevel, a) ac current filtering with filter, b) ac current filtering by control actions [3]10                                                                                                                                                     |

| Figure 3-1 Conventional topology of the dc/dc MMC17                                                                                                                                                                                                                         |

| Figure 3-2 Flowchart of the proposed augmented design                                                                                                                                                                                                                       |

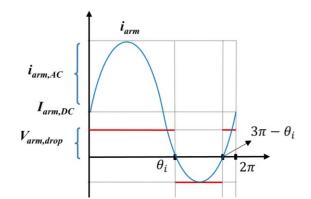

| Figure 3-3 Arm current and voltage drop due to arms semiconductor switches                                                                                                                                                                                                  |

| Figure 3-4 Implementation of the PWM in the semi-analytical approach23                                                                                                                                                                                                      |

| Figure 3-5 Sorting algorithm and updating capacitors voltages in the semi-analytical approach                                                                                                                                                                               |

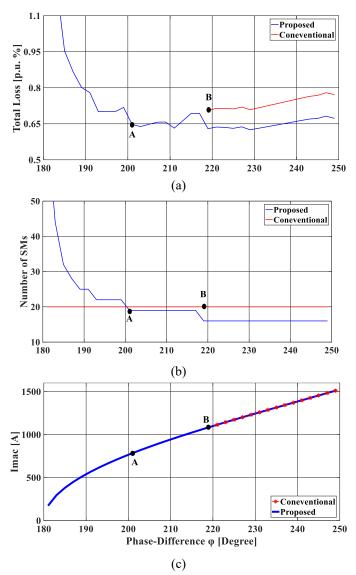

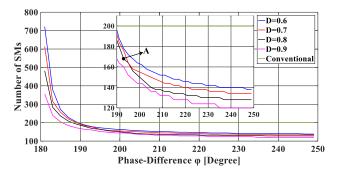

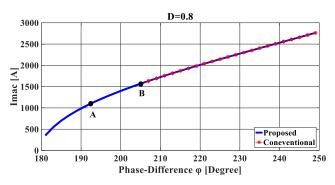

| Figure 3-6 (a) Total loss comparison (b) Number of SMs (c) Amplitude of ac circulating current                                                                                                                                                                              |

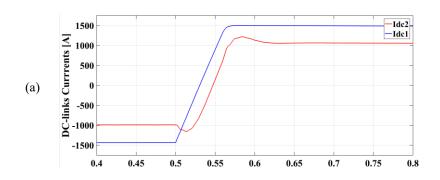

| Figure 3-7 Simulation results of the 20 MW converter designed by the proposed augmented method, (a) DC links currents, (b) Arms current, (c) Capacitors voltages of HBSMs in the upper arm, (d) Capacitor voltage of FBSM in the upper arm, (e) Phase difference between ac |

| voltage of upper and lower arms                                                                                                                                                                                                                                             |

| Figure 3-8 Zoomed in results of the designed converter, (a) The arms voltages, (b) The arms currents, (c) The upper arm HBSMs voltages, (d) The upper arm HBSMs capacitor voltages.                                                                                         |

|                                                                                                                                                                                                                                                                             |

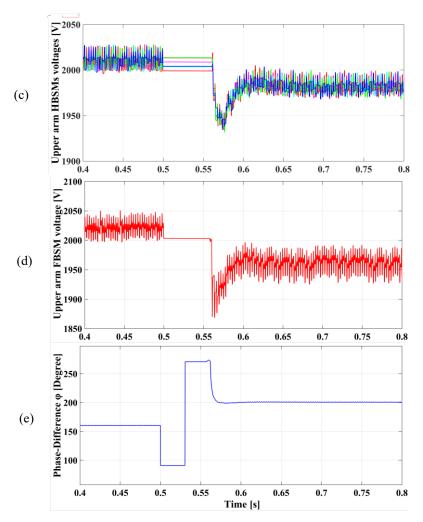

| Figure 3-9 Total losses at each operation point for the conventional topology and the                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| converters designed by the proposed augmented method, (a) DC-link voltage ratio D=0.6, (b)                                                                                                                                                                                                                                                                             |

| D= 0.7, (c) D=0.8, (d) D=0.935                                                                                                                                                                                                                                                                                                                                         |

| Figure 3-10 Number of SMs at each operation point for the conventional topology and the converter designed by the proposed augmented method                                                                                                                                                                                                                            |

| Figure 3-11 Amplitude of the ac circulating current when <i>D</i> =0.8                                                                                                                                                                                                                                                                                                 |

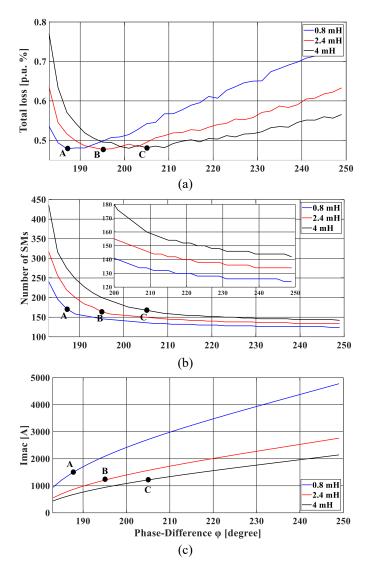

| Figure 3-12 Effect analysis of the arm inductance on the converter performance, (a) Total loss in p.u., (b) required number of SMs at each phase difference and (c) Amplitude of ac circulating current                                                                                                                                                                |

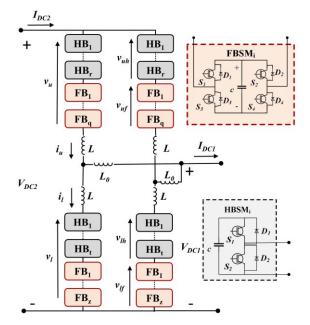

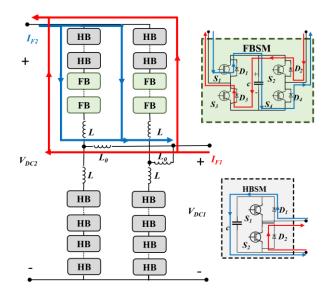

| Figure 4-1 Structure of the hybrid dc/dc MMC40                                                                                                                                                                                                                                                                                                                         |

| Figure 4-2 Phasor diagram of (a) upper and lower arms when the lower arm voltage is the reference (b) lower arm when the lower arm voltage is the reference (c) upper arm when the upper arm voltage is the reference                                                                                                                                                  |

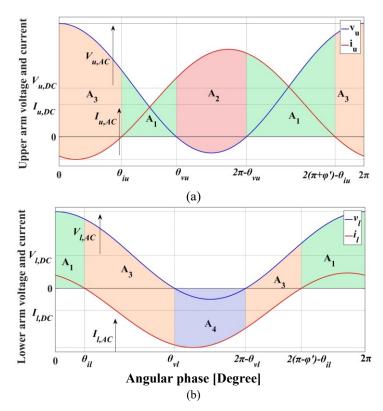

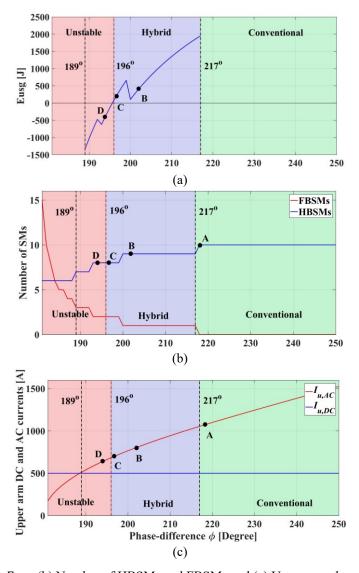

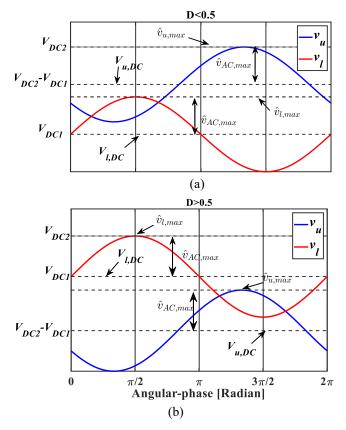

| Figure 4-3 Voltage and current of (a) Upper arm and (b) Lower arm, when the dc component of arm current is higher than the ac component                                                                                                                                                                                                                                |

| Figure 4-4 Voltage and current of (a) Upper arm and (b) Lower arm, when the ac component of arm current is higher than the dc component                                                                                                                                                                                                                                |

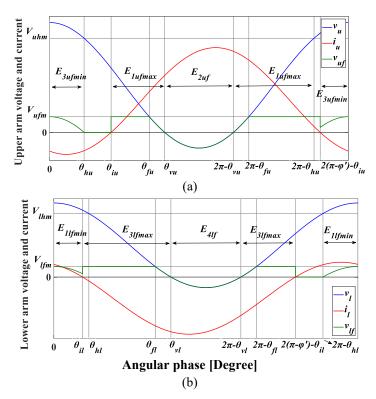

| Figure 4-5 Voltage, current and FBSMs equivalent voltage of (a) Upper arm and (b) Lower arm                                                                                                                                                                                                                                                                            |

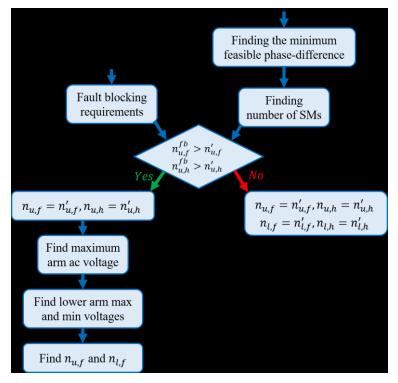

| Figure 4-6 The overall procedure of finding stable operating points                                                                                                                                                                                                                                                                                                    |

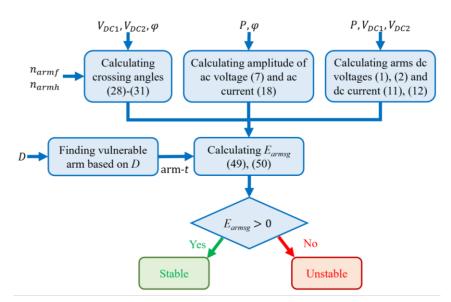

| Figure 4-7 (a) <i>Eusg</i> , (b) Number of HBSMs and FBSMs and (c) Upper arm dc and ac currents                                                                                                                                                                                                                                                                        |

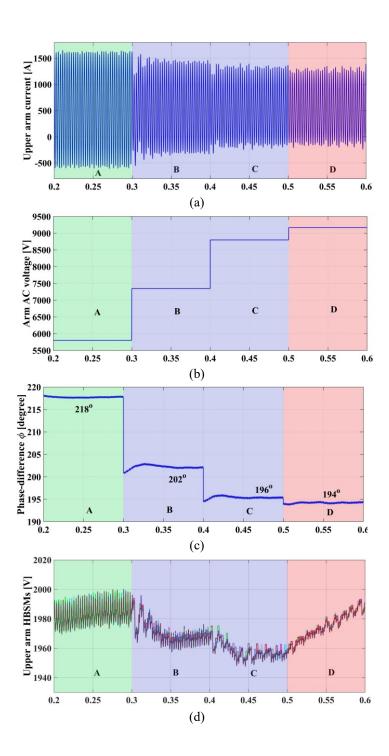

| <ul><li>Figure 4-8 Simulation results, (a) Upper arm current, (b) Arm ac voltage, (c) Phase</li><li>difference between upper and lower arms AC voltages., (d) Voltages of upper arm HBSMs,</li><li>(e) Voltages of upper arm FBSMs and (f) Voltages of lower arm HBSMs</li></ul>                                                                                       |

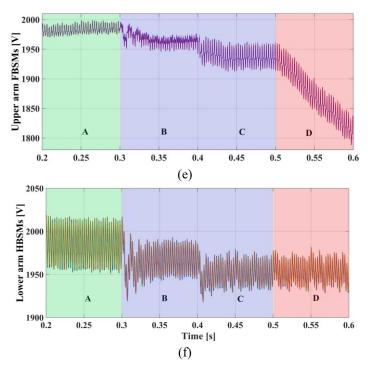

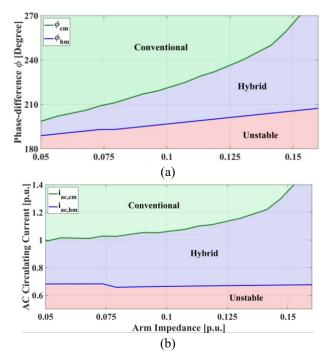

| Figure 4-9 Analytical studies results, (a) The minimum feasible phase difference of the conventional ( $\varphi cm$ ) and hybrid ( $\varphi hm$ ) topologies, (b) The minimum amplitude of ac circulating current in the conventional ( <i>iac</i> , <i>cm</i> ) and hybrid ( <i>iac</i> , <i>hm</i> ) topologies, when the transmitted power changes between [0.5, 2] |

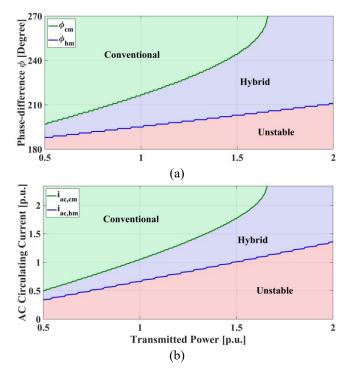

| Figure 4-10 Analytical studies results, (a) The minimum feasible phase difference of the conventional ( $\varphi cm$ ) and hybrid ( $\varphi hm$ ) topologies, (b) The minimum amplitude of ac circulating current in the conventional ( <i>iac</i> , <i>cm</i> ) and hybrid ( <i>iac</i> , <i>hm</i> ) topologies, when the conversion ratio changes between [0.5, 0.85] |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4-11 Analytical studies results, (a) The minimum feasible phase difference of the conventional ( $\varphi cm$ ) and hybrid ( $\varphi hm$ ) topologies, (b) The minimum amplitude of ac circulating current in the conventional ( <i>iac</i> , <i>cm</i> ) and hybrid ( <i>iac</i> , <i>hm</i> ) topologies, when the arm inductance varies between [0.05, 0.16]   |

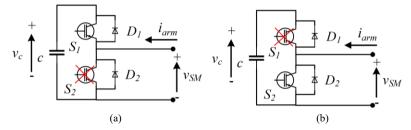

| Figure 5-1 Half-bridge-based SM under open-circuit faults, a) $S_2$ fault and b) $S_1$ fault                                                                                                                                                                                                                                                                              |

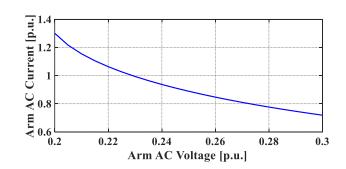

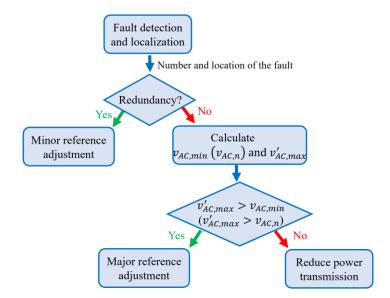

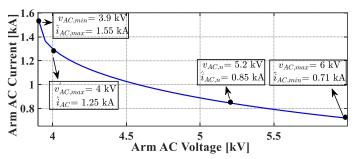

| Figure 5-3 The minimum allowable arm ac voltage with respect to the transmitted power in p.u                                                                                                                                                                                                                                                                              |

| Figure 5-4 The arm ac current with respect to the arm ac voltage in p.u.76Figure 5-5 Flowchart of the proposed fault-tolerant operation.77                                                                                                                                                                                                                                |

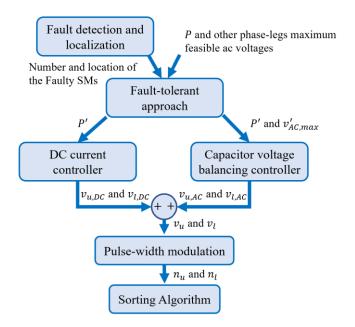

| Figure 5-6 One phase-leg controller including the proposed fault tolerant approach                                                                                                                                                                                                                                                                                        |

| Figure 5-8 The arm ac circulating current with respect to the arm ac voltage for the dc/dc MMC                                                                                                                                                                                                                                                                            |

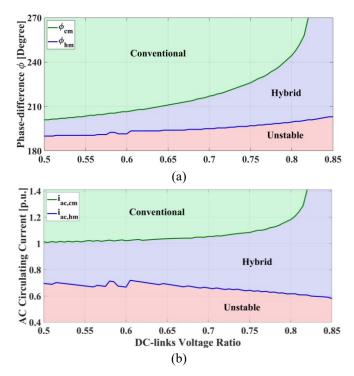

| Figure 5-9 Simulation results of case II, (a) the dc links currents, (b) the upper and lower arms current, (c) the upper and lower arms voltages, (d) the capacitors voltages of HBSMs in the upper arm, (e) the capacitor voltage of HBSM in the lower arm                                                                                                               |

| Figure 5-10 Simulation results of case III, (a) the dc links currents, (b) the upper and lower arms current, (c) the upper and lower arms voltages, (d) the capacitors voltages of HBSMs in the upper arm, (e) the capacitors voltages of HBSMs in the lower arm                                                                                                          |

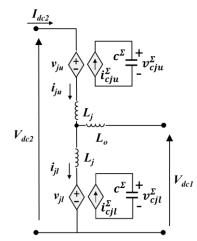

| Figure 6-1 Averaged model of phase-leg- <i>t</i> in the dc/dc MMC89                                                                                                                                                                                                                                                                                                       |

| Figure 6-2 (a) ac equivalent circuit of a dc/dc MMC with two phase-legs considering the dc-<br>link 2 inductance, (b) Simplified ac circuit, (c) ac circuit ignoring the ac voltage sources of<br>phase-leg 2, (d) ac circuit ignoring the ac voltage sources of phase-leg 1                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

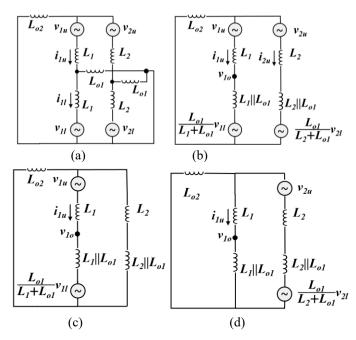

| Figure 6-3 The ac current of the upper arm in the phase-leg 1 induced by the arms ac voltages of phase-leg 1 (self-induced), (b) The ac current of the upper arm in the phase-leg 1 induced by the arms ac voltages of phase-leg 2 (cross-coupling)                                                                                        |

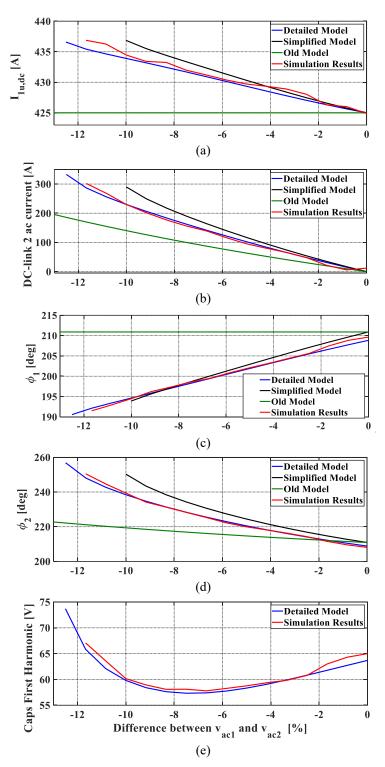

| Figure 6-4 Simulation results of unsymmetrical operation of the dc/dc MMC with different<br>arm inductances, (a) the upper arm dc component, (b) the leaked ac current into dc-link 2, (c)<br>the phase-difference of phase-leg 1, (d) the phase-difference of phase-leg 2, (e) the first order<br>harmonic of sum capacitors voltages     |

| Figure 6-5 Simulation results of unsymmetrical operation of the dc/dc MMC with different<br>arm voltages, (a) the upper arm dc component, (b) the leaked ac current into dc-link 2, (c) the<br>phase-difference of phase-leg 1, (d) the phase-difference of phase-leg 2, (e) the first-order<br>harmonic of the sum of capacitors voltages |

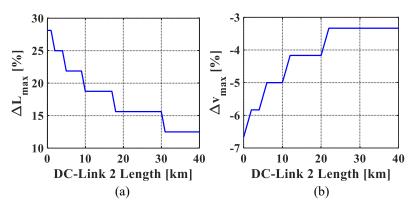

| Figure 6-6 The maximum tolerable variation of (a) the arm inductance and (b) the arm ac voltage, when the dc-link 2 length changes from 0 to 200 km                                                                                                                                                                                        |

| Figure 6-7 The dc-link 2 current THD (a) when variation of <i>L</i> 2 is between -15% to 15%, (b) when variation of <i>vac</i> 2 is between -5% to 0%, for the dc-link 2 lengths of 0 km and 10 km.                                                                                                                                        |

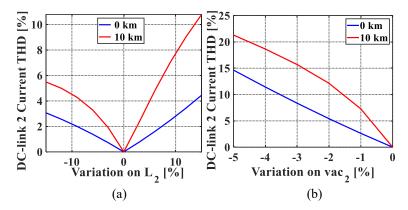

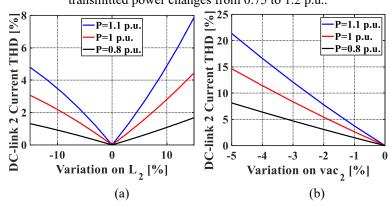

| Figure 6-8 The maximum tolerable variation of (a) the arm inductance and (b) the arm ac voltage, when the transmitted power changes from 0.75 to 1.2 p.u                                                                                                                                                                                   |

| Figure 6-9 The dc-link 2 current THD (a) when variation of <i>L</i> 2 is between -15% to 15%, (b) when variation of <i>vac</i> 2 is between -5% to 0%, for the transmitted powers of 1.1 p.u., 1 p.u. and 0.8 p.u                                                                                                                          |

| Figure 6-10 The maximum tolerable variation of (a) the arm inductance and (b) the arm ac voltage, when the conversion ratio changes from 0.65 to 0.75109                                                                                                                                                                                   |

| Figure 6-11 The dc-link 2 current THD (a) when variation of $L2$ is between -15% to 15%, (b) when variation of <i>vac2</i> is between -5% to 0%, for conversion ratios of 0.6, 0.65 and 0.7109                                                                                                                                             |

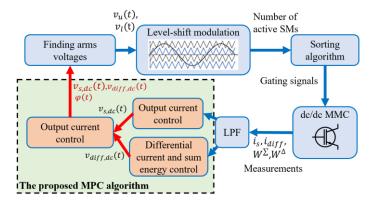

| Figure 7-1 Overall flow chart of the proposed MPC of the dc/dc MMC                                                                                                                                                                                                                                                                         |

| Figure 7-2 Overall control of the dc/dc MMC123                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 7-3 The steady-state operation of the proposed MPC approach, (a) the dc-links currents and the phase-leg 1 current, (b) the arms currents, (c) arms voltages, (d) the SMs voltages of the upper arm, (e) the SMs voltages of the lower arm |

| Figure 7-4 PI-based controller in transient mode, (a) dc-links currents and the phase-leg 1 current, (b) arms currents, (c) arms voltages, (d) the SMs voltages of the upper arm, (e) the SMs voltages of the lower arm                           |

| Figure 7-5 The proposed MPC in transient mode, (a) the dc-links currents and the phase-leg 1 current, (b) the arms currents, (c) arms voltages, (d) the SMs voltages of the upper arm, (e) the SMs voltages of the lower arm                      |

| Figure 7-6 Sensitivity analysis, (a) THD of dc-link 1 current, (b) Average voltage of upper arm capacitors, (c) Average voltage of lower arm capacitors                                                                                           |

| Figure 7-7 The proposed MPC approach in transient mode under parametric uncertainty, (a) dc-links currents and the phase-leg 1 current, (b) the SMs voltages of the upper arm, (c) the SMs voltages of the lower arm                              |

| Figure 7-8 Conventional PI-based controller in transient mode under parametric uncertainty,<br>(a) dc-links currents and the phase-leg 1 current, (b) the SMs voltages of the upper arm, (c)<br>the SMs voltages of the lower arm                 |

| Figure 8-1 The dc/dc MMC and fault currents paths                                                                                                                                                                                                 |

| Figure 8-3 Load transient operation, (a) the dc-links currents and the phase-leg 1 current, (b) the arms currents, (c) the SMs voltages of the upper arm, (d) the SMs voltages of the lower arm                                                   |

| Figure 8-4 Low-voltage side short-circuit, (a) the dc-links currents and the phase-leg 1<br>current, (b) the arms currents, (c) the arms voltages, (d) the SMs voltages of the upper arm,<br>(e) the SMs voltages of the lower arm                |

| Figure 8-5 High-voltage side short-circuit, (a) the dc-links currents and the phase-leg 1 current, (b) the arms currents, (c) the arms voltages, (d) the SMs voltages of the upper arm, (e) the SMs voltages of the lower arm                     |

|                                                                                                                                                                                                                                                   |

# Tables

| Table 3-I Main Parameters of the Simulated Converter                               | 29     |

|------------------------------------------------------------------------------------|--------|

| Table 3-II Comparison of the Conventional Topology at Operating Points A and the   |        |

| Designed Converter at Operating Point B (Design Example 1)                         | 32     |

| Table 3-III Main Parameters of Analyzed Large-Scale DC/DC MMC                      | 34     |

| Table 3-IV Comparison of Operating Points A and C (Design Example 2)               | 37     |

| Table 4-I Exchanged Energy by the Arm and Associated Areas                         | 45     |

| Table 4-II Main Parameters of the Simulated Converter                              | 54     |

| Table 5-I Behaviour of Half-Bridge SM Fault Under S1 and S2 Fault                  | 65     |

| Table 5-II Main Parameters of the Simulated Converter                              | 80     |

| Table 5-III A Brief Illustration of Simulation Case-Studies                        | 80     |

| Table 6-I Main Parameters of the Simulated System                                  | 100    |

| Table 6-II The Maximum Tolerable Variation of Parameters                           | 105    |

| Table 7-I calculation Time of the Basic Mathematical Operations                    | 124    |

| Table 7-II Comparison of calculation Time                                          | 124    |

| Table 7-III Parameters of the Simulated DC/DC MMC                                  | 125    |

| Table 7-IV Comparison of the PI controller and the Presented MPC Approach in the S | teady- |

| State                                                                              | 128    |

| Table 8-I Main Parameters of the Simulated Converter                               | 141    |

| Table 8-II Steady-State Comparison of the Proposed Modified Topology and the       |        |

| Conventional Topology                                                              | 144    |

# **Chapter 1** Introduction

New clean and renewable energy resources, such as wind, photovoltaic, and energy storage systems will be significant parts of close-future grids. For example, in Alberta, more than 5000 MW of new wind power generation is already contracted or under development, whereas windbased generation is going to be 20% of the total power generation capacity in Canada by 2025 [1], [2]. The renewable energy resources are mostly far located from load centers, and, therefore, the generated power must travel long distances to reach consumers. In this regard, high-voltage dc (HVDC) and medium voltage dc (MVDC) systems are introduced to transmit harvested power from renewable resources with better stability and reliability as compared to the conventional high-voltage ac (HVAC) transmission systems. To date, a considerable number of point-to-point dc systems have been installed around the world, which has inspired researchers to introduce a new concept of "DC grids" [3]. One of the main challenges of the dc grid is to interconnect two already installed point-to-point dc systems, which might have different voltage levels and grounding systems. To address this problem, different types of high voltage/power dc/dc converters were proposed in the literature [4]. These converters will play a significant role in interfacing and integrating renewable resources into power grids [4]. One of the most promising topologies, which is inspired by the renowned dc/ac modular multilevel converter (MMC) [5], [6] is the dc/dc MMC [7]. This newly emerged dc/dc converter inherited the prominent advantages of the well-known dc/ac MMC, such as high reliability, high efficiency, and scalability [8]. However, several challenges related to this converter still need to be addressed.

#### **1.1 Research Motivations**

The available literature on the dc/dc MMC falls short in the following aspects:

• The dc/dc MMC can work in different operating points while transmitting a fixed amount of power. However, the operation at each operating point requires a different

number of submodules (SMs) in each arm. Moreover, the ac circulating current is different at each operating point. This will affect the initial cost and efficiency of the converter. As a result, it is crucial to find the proper operating point.

- The operation and control of the hybrid dc/dc MMC are investigated in the literature. Previous results showed that the hybrid dc/dc MMC could limitlessly extend the power transfer capability. However, analytical and simulation results show that the operation of this converter is limited by the capacitors voltages unbalance. Therefore, this phenomenon needs to be studied thoroughly.

- In general, MMCs are susceptible to SM failures. As a result, it is critical to develop a fault-tolerant operation strategy for the dc/dc MMC. To date, the fault-tolerant operation of the dc/dc MMC under SM failure is not investigated in the literature.

- The dc/dc MMC operation is not studied in the unsymmetrical condition. The unsymmetrical condition is referred to the situation in which the phase-legs operate at different operating points because of varying system parameters.

- The development of an advanced controller based on the model predictive control (MPC) for the dc/dc MMC is still lacking in the literature. Several studies showed that this control method improved the steady-state and transient operation of power electronic converters.

- To date, only the hybrid dc/dc MMC with full-bridge-based SMs in the upper arm is introduced for fault-blocking. However, this topology has very high semiconductor losses due to the large number of switches in the upper arm. A topology that offers the fault-blocking capability and high-efficiency operation is still missing.

## **1.2 Research Objectives**

The following objectives are identified for this research work to address the difficulties mentioned above:

- Develop an augmented design approach considering the control aspects (different operating points) and the hardware aspects (number of SMs) of the dc/dc MMC. This approach results in a more efficient and cheaper converter compared to the conventional topology.

- Study the effect of capacitors voltages unbalance on the hybrid dc/dc MMC operation limit, and develop a systematic approach to determine the maximum power that the hybrid dc/dc MMC can transfer.

- Develop a tailored fault-tolerant operation strategy that does not require any redundant SMs and only utilizes the unique characteristics of the dc/dc MMC.

- Study the unsymmetrical operation of the dc/dc MMC to facilitate converter analysis and modeling in the presence of parametric uncertainty.

- Develop a decoupled discrete-time dynamic model of the dc/dc MMC, and design an advanced controller based on the MPC method.

- Find a straightforward process to determine the number and type of SMs in the dc/dc MMC to yield the bidirectional fault-blocking capability and high-efficiency operation.

## **1.3 Research Methodology**

First, using the available phasor-domain model of the dc/dc MMC, the number of needed SMs and conduction and switching losses are found at different operating points. The results are used to build a new design approach that yields a more efficient converter. Second, by conducting analytical studies, the capacitors voltages of the hybrid dc/dc MMC in the steady-state are investigated, and the maximum transmitted power for which the capacitors voltages can be balanced is found. Third, by conducting analytical studies, it is shown that the fault-

tolerant operation with the same transmitted power is possible without the need for additional SMs. Furthermore, the required arms voltages are calculated based on the transmitted power to prove that, in severe SMs faults conditions, the converter can continue its operation with reduced power transmission. Fourth, by considering dc-links impedance, new detailed and simplified models are developed to study the behavior of the dc/dc MMC in the presence of parametric uncertainty. The maximum tolerable variation of the parameters is found using the developed models. Fifth, by decoupling and discretizing the dynamic model of the dc/dc MMC using the forward Euler method, the first controller based on the MPC method is proposed to control the dc/dc MMC. Finally, the appropriate number and type of SMs are selected by analytical studies to satisfy the fault-blocking requirements and high-efficiency operation.

### **1.4 Research Contributions**

The main contributions of this research work are the development of

- A new design approach that reduces the number of active components and power losses and extends the operating range of the dc/dc MMC [9],

- An analytical method to determine the operation limit of the hybrid dc/dc MMC caused by the capacitors voltages unbalance [10],

- A fault-tolerant approach that uses the dc/dc MMC's unique characteristics without the need for redundant SMs [11],

- 4) Detailed and simplified models that can express the behavior of the dc/dc MMC in the presence of parametric uncertainty [12], and

- 5) A model predictive control of the dc/dc MMC that improves both the steady-state operation and dynamic response of the converter.

- 6) An efficient hybrid dc/dc MMC topology with bidirectional fault-blocking capability.

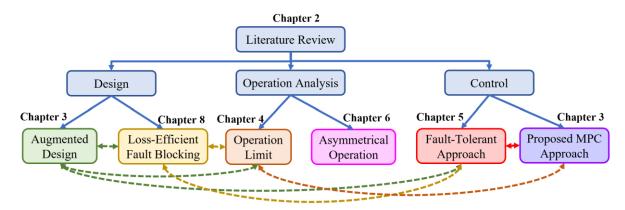

## **1.5** Thesis Organization

This thesis focuses on the design, analysis, and control of the dc/dc MMC. It is organized as shown in Figure 1.1. In Chapter 2, different topologies of the dc/dc converters and a literature

survey on the dc/dc MMC are presented. In Chapter 3, the proposed augmented design of the dc/dc MMC is presented. The operation limit of the hybrid dc/dc MMC is investigated in Chapter 4. The proposed SM fault-tolerant operation is elaborated in Chapter 5. Chapter 6 studies the dc/dc MMC operation in the unsymmetrical condition. The developed MPC controller for the dc/dc MMC is presented in Chapter 7. The proposed efficient topology with fault current blocking capability is introduced in Chapter 8. Finally, Chapter 9 concludes the thesis and provides directions for future works.

Figure 1-1 Organization of the thesis.

# **Chapter 2** Literature Survey

This chapter presents an overview of different topologies of the dc/dc converters for mediumand high-voltage applications and a detailed literature survey on the dc/dc MMC.

## 2.1 Isolated Topologies

The isolated topologies are based on two stages of the ac-dc conversion. The galvanic isolation is achieved by the ac transformer or coupled inductors. Safety and grounding are the main reasons for the isolation. These topologies make it possible to have different grounding systems on both sides of the converter. Furthermore, a high conversion ratio can be easily achieved by proper design of the ac transformer, and it provides inherent dc-fault block capability. The isolated topologies can be categorized as the different variations of the dual active bridge (DAB) and those operating based on flyback/forward converter principles.

#### 2.1.1 Dual Active Bridge (DAB) Topologies

Two-level high-voltage DAB and modular multilevel DAB are the most common types of DAB topologies. In the following, the advantages and disadvantages of these topologies are explained.

Figure 2-1 Two-level high-voltage DAB [3].

Figure 2-2 Modular Multilevel DAB [3].

## 2.1.1.1 Two-Level High-Voltage DAB

As shown in Figure 2-1, this topology is based on two two-level voltage-source converters (VSC) interconnected via an ac transformer. In HVDC applications, this topology has multiple downsides. The most important of them is the insulation and the electromagnetic interference (EMI) caused by high dv/dt in this topology [3].

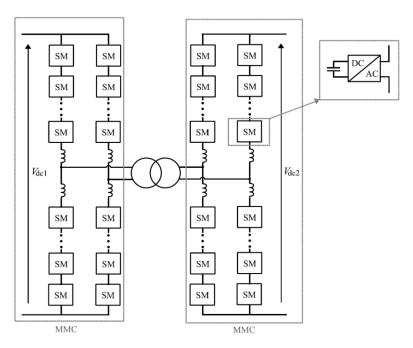

#### 2.1.1.2 Modular Multilevel DAB

The modular multilevel DAB consists of two ac/dc modular multilevel converters (MMCs) connected via an ac transformer, as depicted in Figure 2-2. The transferred power is controlled by applying an appropriate ac waveform at the terminals of the transformer [13]. The challenge of this topology is to design a high-voltage/power transformer operating at medium frequency. This challenge can be addressed by making a tradeoff between the size of the transformer and the switching losses of the MMCs [14]. As the modular multilevel DAB requires two fully rated MMCs, the overall size and cost of the system are significant. The main advantages of this topology are reliability, modularity, and scalability, making it an excellent solution for high-power/voltage applications at small conversion ratios [15].

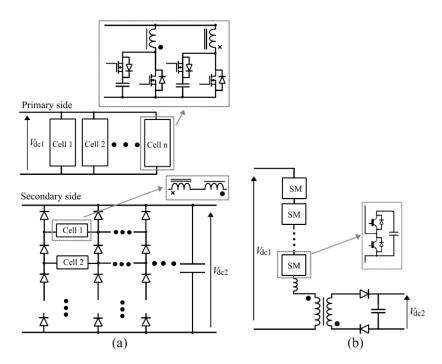

Figure 2-3 a) Modular dc/dc converter based on flyback/forward, b) dc/dc converter based on the flyback/forward with centralized coupled inductor [4].

#### 2.1.2 Flyback/Forward Based Topologies

For high-voltage levels, some circuits are designed based on one coupled inductor and a string of SMs. Others use multiple coupled inductors in an isolated modular structure [16]. These two types are illustrated in Figure 2-3. These structures are suitable for high conversion ratios. However, having a high current in the centralized inductor and insulation requirements in the modular structure limits the application of these topologies to low-power cases [17].

## 2.2 Non-Isolated Topologies

There exist many types of non-isolated dc/dc converters, categorized as dc autotransformer, resonant converter, and dc modular multilevel.

#### 2.2.1 DC Autotransformer

This topology consists of two high-voltage dc/ac converters connected in series on the dc ports and connected via an ac transformer on the ac side, as shown in Figure 2-4. The difference

Figure 2-4 DC autotransformer [4].

Figure 2-5 Single-stage resonant converter [15].

between this topology and DAB topologies is that only part of the transmitted power is processed by the ac transformer, reducing overall losses and the transformer rating. Moreover, the rating of the dc/ac converters is decreased because of their series connection. The advantages of this topology disappear when the conversion ratio increases; hence it is suitable for medium and low conversion ratios [15].

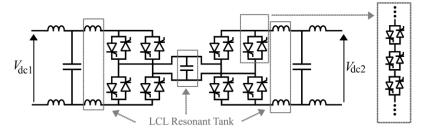

#### 2.2.2 Resonant Converter

The idea behind this topology is to use the resonance to step up the voltage and achieve soft switching. As illustrated in Figure 2-5, the dc-dc conversion is accomplished using a dc-ac-dc chain. This topology offers a high conversion ratio. However, the passive components must tolerate high electrical stresses, and since all the power passes through the resonant elements, their current and voltage ratings are very high. These downsides limit this converter to medium power application at a medium conversion ratio [18].

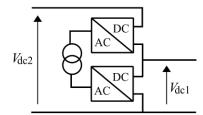

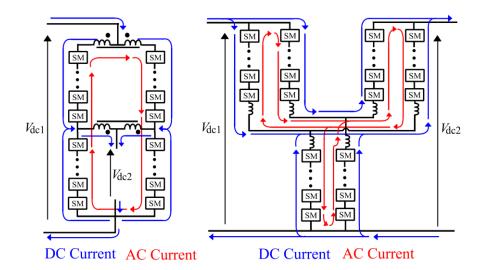

#### 2.2.3 DC Modular Multilevel Converter

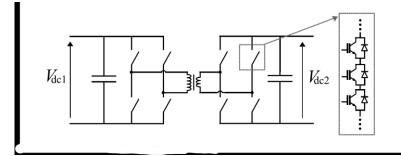

This topology uses the main idea of the dc/ac MMC to generate voltages and currents at different frequencies. As shown in Figure 2-6, two different current loops exist, dc and ac loops. The dc current is responsible for the exchange of power between dc-links. The ac current is

Figure 2-6 dc modular multilevel, a) ac current filtering with filter, b) ac current filtering by control actions [3]. generated to neutralize the dc power flow and make the average absorbed power by the arms zero [19]. To prevent the ac current from leaking into dc-link, two approaches can be used 1) use of passive filters [19], [7]. 2) control actions [20]. These two approaches are depicted in Figure 2-6. The size of passive components can be reduced by increasing the switching frequency. The dc modular multilevel has the advantages of scalability, modularity, and high reliability. However, the need for high ac circulating current in applications with high conversion ratios limits its operation to low or medium conversion ratios [3].

#### **2.2.4 DC/DC MMC**

The dc/dc MMC with passive filters has the lowest number of components and the simplest structure compared to the other MMC-based dc/dc converters (like the modular multilevel DAB and the dc MMC without the passive components). Therefore, it is selected as the focus of this study. From now on, the dc modular multilevel converter with passive filters is called the dc/dc MMC. The literature on the dc/dc MMC is reviewed from different perspectives in the following subsection.

#### 2.2.4.1 Design

Different control methods were proposed for the dc/dc MMC [21-24], which tried to reduce the ac circulating current. The minimization of the ac circulating current is one common interest among researchers because it increases converter losses and the current rating of electrical components. However, there exists a serious limitation in the conventional topology of the dc/dc MMC (i.e., the dc/dc MMC proposed in [7], which uses an equal and fixed number of half-bridge based submodules (HBSMs) in each arm) which prevents further reduction of the ac circulating current as explained in the following. In [25], it was shown that as the phase difference gets closer to 180°, the amplitude of the circulating current reduces; however, a higher ac voltage is required to be generated by the arms. In [23], it was stated that because the required amplitude of the arm ac voltage increases when the phase-difference approaches 180°, the number of feasible operation points in the conventional topology of the dc/dc MMC is limited. This is because, at some operating points, the generation of the required maximum and minimum voltages of the arms is not feasible by the conventional topology of the dc/dc MMC. Two major limitations of the conventional topology of the dc/dc MMC are

- Due to the fixed number of HBSMs in the conventional dc/dc MMC, the number of feasible operating points is limited, especially those located near a phase difference of 180°. This problem becomes more severe when the conversion ratio is near 1. This problem imposes higher conduction losses and current rating in the converter.

- 2. In each operating point, arms are required to generate a specific range of voltages which are not equal for upper and lower arms. Therefore, each arm needs a different number and even types of submodules (SMs) (e.g., half-bridge or full-bridge). However, the inefficient design of the conventional topology assumes the use of an equal number of HBSMs in both arms which increases the total number of SMs and the conduction losses.

Motivated by the aforementioned problems, an augmented design method for the dc/dc MMC that considers both the control (the phase-difference between arms ac voltages) and the hardware (type and number of SMs) aspects of the converter needs to be developed.

#### **2.2.4.2 Operation of the Hybrid DC/DC MMC**

To bring more functionality to the dc/dc MMC, the concept of hybrid topologies was proposed in [7, 9, 23, 26]. A typical hybrid topology of the dc/dc MMC employs a combination of fullbridge-based submodules (FBSMs) and HBSMs. In [7], it was shown that when the conversion ratio is close to unity, a combination of the FBSMs and HBSMs is needed for the converter to operate properly. The authors in [26] proposed a hybrid dc/dc MMC with FBSMs in the upper arm and HBSMs in the lower arm to provide fault-blocking capability and step-up operation. To increase the power transfer capability and attenuate the ac circulating current in the dc/dc MMC, a hybrid topology with a combination of HBSMs and FBSMs in each arm was presented in [23]. Adding FBSMs enables the arms to generate negative voltages, which is the key to extend the swing range of arms voltages. In [9], an augmented design of the dc/dc MMC, which tries to remove the limitations of the conventional topology, was proposed. This is realized by selecting the number of HBSMs and FBSMs based on the minimum and maximum arms voltages. The previous studies did not determine any limitation on reducing the ac circulating current and increasing the power transmission in the hybrid dc/dc MMC. They assumed that each arm voltage could be generated by having enough HBSMs and FBSMs. However, the simulation studies show that the operation of the hybrid dc/dc MMC is limited by the capacitors voltages unbalance. An analytical study of the capacitors voltages balance of the hybrid dc/dc MMC is missing in the literature.

#### 2.2.4.3 Fault-Tolerant Operation

The dc/dc MMC and the dc/ac MMC benefit from a modular structure that contains many semiconductor switches. In such topologies, switch failure is a common issue which is referred to as SM fault. As these converters usually transmit a large amount of power, they should remain operational in the event of SM failure. Fault-tolerant operation of the dc/ac MMC was investigated in [5, 27-33]. Adding redundant SMs to the converter was proposed in [27-29]. In this strategy, all the SMs are treated equally in normal operation. When one of the SMs fails, it can be bypassed without harming the converter operation because there already exist additional SMs. The authors of [30] proposed an optimized version of the redundant SMs strategy, which reduces SM capacitor voltage, decreases switching frequency in normal operation, and provides a fast fault restoration in the case of SM fault. In [31], a resilient framework is realized by adding a new SM to each arm to smooth the transient mode and handle multiple SMs faults. A dc/ac MMC based on a novel SM circuit is proposed in [32], which guarantees the operation of the converter despite multiple SM faults. The authors of [33]

attempted to remove the need for communication systems in fault-tolerant operation by using only arms electrical parameters without knowing the number of faulty SMs. In [5], a fullbridge-based SM with half of the voltage rating of the half-bridge-based SMs is added to each arm to suppress the excessive ac circulating current in 2N+1 modulation and provide faulttolerant operation which can only handle a few SMs failure in the arm.

Research on the dc/dc MMC is limited to the converter modeling [9, 10, 25, 34, 35] and different converter control methods [21-24]. However, the fault-tolerant operation of this converter has not been studied yet. Although the dc/dc MMC is similar to the dc/ac MMC, its operation principle is mostly different. Therefore, the fault-tolerant operation of dc/dc MMC needs to be studied separately.

#### 2.2.4.4 Asymmetrical Operation

In power systems, parameters of different components may have  $\pm 5\%$  tolerance, and it could increase to  $\pm 30\%$  worst-case tolerance due to aging, temperature stresses, field stress, radiation, and distorted operation [34], [35]. Moreover, because of control malfunctioning and components failure [11], the generated voltages by the dc/dc MMC might deviate from the reference value by a few percent. With these uncertainties, the dc/ac and the dc/dc MMC can be forced to operate in an unsymmetrical condition. This condition means that the impactful parameters like the generated ac voltage and/or the arm inductance are not equal in different phase-legs, and each phase-leg operates at different operating points. Some studies investigated the operation of the dc/ac MMC in the unsymmetrical condition. Authors in [36] designed a robust controller based on an optimum guaranteed cost control theory to ensure the safe operation of the dc/ac MMC in unsymmetrical conditions. In [37], modeling and design of the dc/ac MMC with parametric uncertainties were discussed. However, with the available steadystate models of the dc/dc MMC [21, 22, 25], the unsymmetrical operation of this converter cannot be studied. This is because the connection between the operation of different phase-legs is lost by ignoring the dc-link impedance. It means changes in the operating point of one phaseleg would not affect the other ones. As a result, a steady-state model that, unlike the previous models, can show the dc/dc MMC behavior in the unsymmetrical condition is demanded.

#### **2.2.4.5 Control**

Recently, design [25], [9], and modeling [12, 38, 39] aspects of the dc/dc MMC have been studied. The control aspect of the dc/dc MMC is studied in [21-24]. In [24], a capacitor voltage balancing strategy that reduces the circulating current was proposed. The operation principle of the hybrid dc/dc MMC was explained in [23], where the power transfer capability is improved by utilizing the elevated capacitors voltages. In [22], the full-state regulation of the dc/dc MMC was proposed to minimize the ac circulating current. Authors in [21] introduced a new closed-loop control of the dc/dc MMC to ensure energy balancing in the load transient and steady-state. To date, all the suggested control approaches are based on proportional-integral (PI) controllers. This type of controller suffers from the complexity of handling multiple control objectives and poor transient performance. As the number of control objectives grows, the number of needed PI loops increases resulting in the complexity of the overall control structure and the difficulty of PI parameters tuning.

In the previous literature, to overcome the disadvantages of the PI-based controllers, researchers widely used the model predictive control (MPC) for the control of the dc/ac MMC [40-45]. In [40], the computational burden of the MPC was reduced by decoupling the capacitors voltage balancing from the MPC algorithm. This task was realized in a separate sorting algorithm. By solving the Diophantine equations, the online optimization and presence of the weighting factors were avoided in [41], which resulted in a lower computational burden and enhanced reliability. A new modulated MPC for the dc/ac MMC was proposed in [44], where it used two predetermined voltage levels to build the voltage reference. To improve the computational burden and steady-state performance and eliminate the need for weighting factors, a new MPC approach, called the sliding-discrete control set, was introduced in [45]. To date, a few studies [46, 47] developed MPC methods for the isolated dc/dc MMC. In general, this topology is built of two dc/ac MMCs which are connected via an ac transformer. In [46], a modulated MPC approach was proposed for the inductor-less MVDC MMC, which reduces the computational burden by reformulating the underlying optimization problem. The author in [47] proposed a Finite Control Set MPC to regulate the output voltage. This is

achieved by defining a cost function, including the output voltage, which yields the optimum number of SMs in the next control period.

Despite extensive studies on the application of the MPC method in the control of the MMCbased converters, the MPC method has never been used for the control of the dc/dc MMC introduced in [7]. Although these converters, the dc/dc and the other MMC-based converters, share a similar topology, crucial differences exist in the operation principle. Moreover, the control objectives and the control variables of these two converters are different. Therefore, the developed MPC methods for the other MMC-based converters cannot be used directly for the dc/dc MMC. Therefore, developing a tailored MPC approach for the dc/dc MMC would be beneficial to improve the dynamic performance.

#### 2.2.4.6 Fault-Blocking Capability

Fault-blocking capability is an important feature that should be realized in the dc/dc MMC. This feature allows the dc/dc MMC to block the fault current from both dc sides. The past literature [7, 21, 26] proposed that using FBSMs in the upper arm of the dc/dc MMC would provide the bidirectional fault-blocking capability. However, replacing the HBSMs with the FBSMs will increase the losses significantly; this is because FBSMs have twice the number of semiconductor switches compared to the HBSMs. Moreover, in these studies, the FBSMs are treated as HBSMs in the normal operation mode, while they can generate negative voltages, unlike the HBSMS. Therefore, realizing an efficient fault-blocking capability is still missing in the literature.

# **Chapter 3** Augmented Design of the DC/DC MMC

In this chapter, first, the operation principle and the mathematical model of the conventional dc/dc MMC are presented. Then the proposed augmented design is explained in detail. This approach includes two main parts, analytical and semi-analytical, which are elaborated in this report. In the end, two different case studies are presented to verify the effectiveness of the proposed method. In the first case study, a medium voltage dc/dc MMC is designed by the proposed augmented approach. The results from the analytical and semi-analytical parts are compared with the results from the simulation study. In the second case study, the impact of system parameters on the converter performance is studied.

# **3.1** Topology and Mathematical Modeling of the Conventional DC/DC MMC

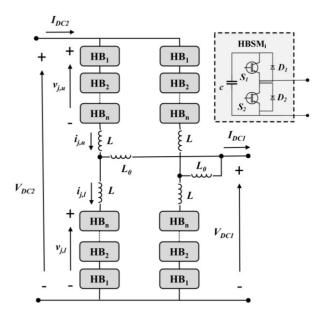

#### 3.1.1 Topology

The circuit of a dc/dc MMC with two phase-legs is illustrated in Figure 3-1. Each phase-leg includes two arms consisting stack of HBSMs and an arm inductor L, which is necessary for injecting an ac circulating current. The voltage of dc-link 2  $V_{DC2}$  (input side) is assumed to be greater than that of dc-link 1  $V_{DC1}$  (output side). The midpoints of the phase-legs are connected to the output dc-link via a large inductor  $L_0$ , which acts as a filter and prevents the leakage of the ac circulating current into the output side. The dc-link currents are denoted by  $I_{DC1}$  and  $I_{DC2}$ . The voltages generated by the upper and lower arms of phase-leg-*j* are denoted by  $v_{j,u}$  and  $v_{j,l}$ , and arms current are denoted by  $i_{j,u}$  and  $i_{j,l}$ . In the rest of the chapter, superscripts related to the phase-leg are removed, and due to similarity, the operation of one phase-leg is analyzed.

Figure 3-1 Conventional topology of the dc/dc MMC.

#### 3.1.2 Mathematical Modeling

Assuming that the converter transmits the nominal power P from dc-link 2 to dc-link 1, each arm processes an equal portion of power  $P_{DC}$  which can be calculated as follows:

$$P_{DC} = \frac{1 - D}{M} \cdot P, D = \frac{V_{DC1}}{V_{DC2}}$$

(3-1)

where *M* is the number of phase-legs, and *D* is the dc-links voltage ratio. In the dc/dc MMC, to neutralize the effect of the dc power flow, the upper and lower arms of each phase-leg should exchange active ac power  $P_{AC}$ . To stabilize the capacitors voltages of each arm, the summation of  $P_{DC}$  and  $P_{AC}$  must be zero. The exchange of an active ac power can be possible by adding an ac voltage to the arms reference voltage generating an ac circulating current, which ideally only flows through the arms and does not penetrate the dc links. The arm ac voltage could have any frequency. Higher frequencies decrease the size of passive components, and on the other hand, increase the switching frequency and losses. The exchanged active ac power between arms can be calculated as

$$P_{AC} = -P_{DC} \tag{3-2}$$

$$P_{AC} = \frac{X_{L0}}{2(X_L^2 + 2X_L X_{L0})} \hat{v}_{u,AC} \cdot \hat{v}_{l,AC} \cdot \sin(\varphi)$$

(3-3)

where  $\hat{v}_{u,AC}$  and  $\hat{v}_{l,AC}$  are the amplitudes of the upper and lower arms ac voltages, respectively; and  $X_L$  and  $X_{L0}$  are the reactances of the inductors L and  $L_0$ , respectively. To enable the exchange of active ac power, there should be a phase difference  $\varphi$  between the arms ac voltages. When P is positive, it could change between  $\pi$  to  $3\pi/2$ ; and when P is negative, it could vary from  $\pi/2$  to  $\pi$  creating different operating points [24]. Changing the phase difference  $\varphi$  while the converter transmits the same amount of power can affect the converter performance significantly.

The arms reference voltages in the time-domain are shown in (3-4) and (3-5).

$$v_u(t) = (V_{DC2} - V_{DC1}) + \hat{v}_{u,AC} \cos(\omega t + \varphi)$$

(3-4)

$$v_l(t) = V_{DC1} + \hat{v}_{l,AC} \cos(\omega t) \tag{3-5}$$