**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI

films the text directly from the original or copy submitted. Thus, some

thesis and dissertation copies are in typewriter face, while others may be

from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality

illustrations and photographs, print bleedthrough, substandard margins,

and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete

manuscript and there are missing pages, these will be noted. Also, if

unauthorized copyright material had to be removed, a note will indicate

the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and

continuing from left to right in equal sections with small overlaps. Each

original is also photographed in one exposure and is included in reduced

form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations

appearing in this copy for an additional charge. Contact UMI directly to

order.

IIMI

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor MI 48106-1346 USA 313/761-4700 800/521-0600

#### University of Alberta

# ERROR IDENTIFICATION AND DATA RECOVERY IN MISR-BASED DATA COMPACTION

by

Wes A. Tutak

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of **Master of Science**.

Department of Electrical and Computer Engineering

Edmonton, Alberta Fall 1997

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-22683-2

University of Alberta

Library Release Form

Name of Author: Wes A. Tutak

Title of Thesis: Error Identification and Data Recovery in MISR-based Data Com-

paction

Degree: Master of Science

Year this Degree Granted: 1997

Permission is hereby granted to the University of Alberta Library to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly or scientific research purposes only.

The author reserves all other publication and other rights in association with the copyright in the thesis, and except as hereinbefore provided, neither the thesis nor any substantial portion thereof may be printed or otherwise reproduced in any material form whatever without the author's prior written permission.

Wes A. Tutak

16207 56 Street

Edmonton, AB

Canada, T5Y 2V1

Date: Aug. 28, 1997.

#### University of Alberta

#### Faculty of Graduate Studies and Research

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies and Research for acceptance, a thesis entitled Error Identification and Data Recovery in MISR-based Data Compaction submitted by Wes A. Tutak in partial fulfillment of the requirements for the degree of Master of Science.

Dr. Yisoling Sun

Sum Tiading

Dr. Bruce Cockburn

Br. Jonathan Schaeffer

Date: Aug. 28, 1997.

## **Abstract**

This thesis presents a new data recovery scheme for use in fault diagnosis in a STUMPS-based testing environment. The proposed scheme transfers partially compacted data from the CUT to the tester and uses analytical methods off-line to recover the information lost during signature compaction. Our proposed data recovery scheme significantly reduces the amount of data transferred from the CUT to the tester and can reduce the tester time used for data retrieval.

Two alternatives to the primary data recovery scheme are presented. The first alternative enhances the error identification resolutions by increasing the amount of partially compacted information obtained from the CUT. The second alternative significantly reduces the testing time and tester complexity by eliminating intermediate signature comparison.

Extensive computer simulations are described that illustrate the merits and feasibility of the new data recovery schemes using pseudorandomly generated circuit responses and ISCAS85 benchmark circuits.

# Acknowledgements

I would like to thank my supervisor, Dr. Xiaoling Sun, for her guidance and patience throughout this research project. Her investment of extra time and effort on my behalf is gratefully acknowledged. My thanks also go to the members of my supervisory committee, Dr. Bruce Cockburn and Dr. Jonathan Schaeffer, for their valuable comments. Most importantly, I would like to thank my wife, Darlene, for her support and understanding during the course of my studies.

# Contents

| 1 | Inti                             | roduct               | ion                                                       | ]  |

|---|----------------------------------|----------------------|-----------------------------------------------------------|----|

| 2 | Background and Literature Review |                      |                                                           | 8  |

|   | 2.1                              | Signature Analysis   |                                                           | 8  |

|   |                                  | 2.1.1                | Serial Data Compaction and Pseudorandom Test Generation . | ć  |

|   |                                  | 2.1.2                | Parallel Data Compaction                                  | 10 |

|   | 2.2                              | The S                | TUMPS Testing Environment                                 | 11 |

|   |                                  | ng Diagnosis Methods | 1:3                                                       |    |

|   |                                  | 2.3.1                | Simulation-based Methods                                  | 13 |

|   |                                  | 2.3.2                | Signature Analysis-based Methods                          | 14 |

|   |                                  | 2.3.3                | Error Control Code Method                                 | 15 |

|   | 2.4                              | Fault                | Diagnosis in a STUMPS Environment                         | 16 |

| 3 | Data Recovery Schemes            |                      |                                                           |    |

|   | 3.1                              | New I                | Data Recovery Scheme                                      | 20 |

|   |                                  | 3.1.1                | Modelling of Parallel Data Compaction                     | 21 |

|   |                                  | 3.1.2                | Construction of Space Compaction Sequences                | 22 |

|   |                                  | 3.1.3                | The Primary Data Recovery Scheme                          | 25 |

|   | 3.2                              | Defini               | tions and Declarations                                    | 26 |

|   | 3.3                              | Two-k                | nown-stream Error Identification Algorithm                | 30 |

|   |                                  | 3.3.1                | Algorithm                                                 | 33 |

|   |                                  | 3.3.2                | Error Identification Example                              | 37 |

|   |                                  | 3.3.3                | Complexity Analysis                                       | 39 |

|                           | 3.4                        | Two-u  | inknown-stream Error Identification Algorithm         | 41  |

|---------------------------|----------------------------|--------|-------------------------------------------------------|-----|

|                           |                            | 3.4.1  | Algorithm                                             | 4:3 |

|                           |                            | 3.4.2  | Error Identification Example                          | 45  |

|                           |                            | 3.4.3  | Complexity Analysis                                   | 46  |

|                           | 3.5                        | Altern | native Data Recovery Schemes                          | 47  |

|                           |                            | 3.5.1  | With Non-overlapping Response Vectors                 | 47  |

|                           |                            | 3.5.2  | With Simplified Testing Procedure                     | 50  |

| 4                         | Exp                        | erime  | ntal Results                                          | 52  |

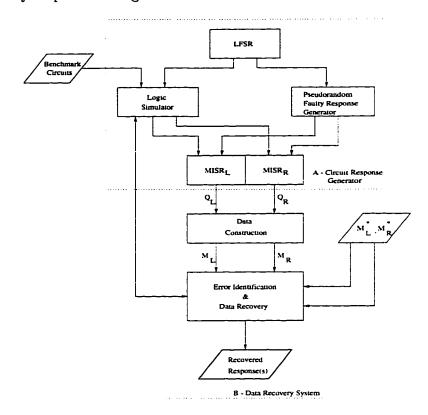

|                           | 4.1                        | Syster | m Overview                                            | 52  |

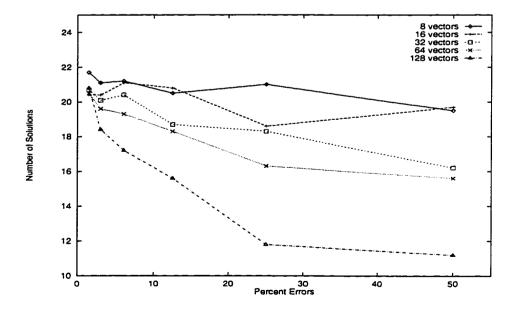

|                           | 4.2                        | Data   | Recovery in Pseudorandomly Generated Response Vectors | 54  |

|                           |                            | 4.2.1  | Simulation Environment                                | 55  |

|                           |                            | 4.2.2  | Results for Overlapping Vectors                       | 56  |

|                           |                            | 4.2.3  | Results for Non-overlapping Vectors                   | 59  |

|                           | 4.3                        | Data   | Recovery in Benchmark Circuits                        | 68  |

|                           |                            | 4.3.1  | Simulation Environment                                | 68  |

|                           |                            | 4.3.2  | Results                                               | 70  |

|                           | 4.4                        | Softwa | are Implementation                                    | 71  |

| 5                         | Con                        | clusio | n                                                     | 78  |

| Bi                        | Bibliography               |        |                                                       | 82  |

| $\mathbf{A}_{\mathrm{j}}$ | Appendices                 |        |                                                       | 85  |

| ${f A}$                   | A DR User Reference Manual |        |                                                       |     |

# List of Figures

| 1.1 | General testing environment                          | :}  |

|-----|------------------------------------------------------|-----|

| 1.2 | Signature analysis testing environment               | 4   |

| 2.1 | An LFSR with $P(x) = x^3 + x^2 + 1$                  | 9   |

| 2.2 | A MISR with $P(x) = x^3 + x^2 + 1$                   | 10  |

| 2.3 | The STUMPS architecture                              | 12  |

| 3.1 | Modified STUMPS architecture                         | 21  |

| 3.2 | Modelling MISR as concurrent compactions             | 22  |

| 3.3 | Data construction system                             | 23  |

| 3.4 | Data recovery scheme                                 | 25  |

| 4.1 | Software system block diagram                        | 53  |

| 4.2 | Graphical results for vector size 1024 × 16, 1 block | 58  |

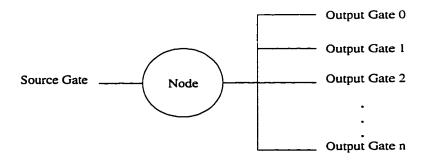

| 4.3 | Node object                                          | 73  |

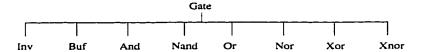

| 4.4 | Gate class hierarchy                                 | 73  |

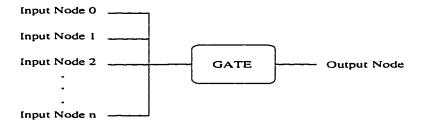

| 4.5 | Gate object                                          | 7:3 |

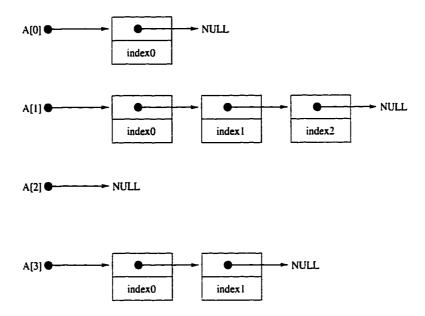

| 4.6 | A sample SparseMatrix $A[][]$                        | 76  |

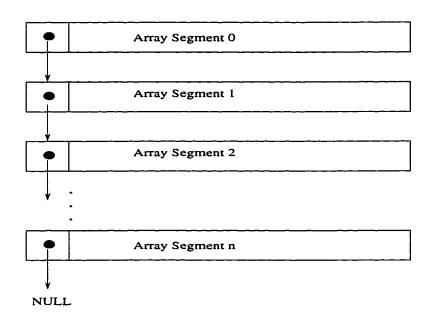

| 4.7 | The DynamicArray structure                           | 77  |

# List of Tables

| 3.1  | Left shifting MISR space compaction                              | 28  |

|------|------------------------------------------------------------------|-----|

| 3.2  | Right shifting MISR space compaction                             | 29  |

| 3.3  | Equations derived for vector $(v = 1)$                           | 38  |

| 3.4  | Equations derived for vector $(v = 2)$                           | 39  |

| 3.5  | Equations derived for vector $(v = 3)$                           | 40  |

| 3.6  | Error cancellations in the left compaction stream                | 4:  |

| 3.7  | Error cancellations in the right compaction stream               | 4-  |

| 3.8  | Non-overlapping left shifting MISR space compaction              | 48  |

| 4.1  | Results for vector size 128×16, 1 block (overlapped vectors)     | 60  |

| 4.2  | Results for vector size 128×16, 2 blocks (overlapped vectors)    | 60  |

| 4.3  | Results for vector size 256×16, 1 block (overlapped vectors)     | 61  |

| 4.4  | Results for vector size 256×16, 2 blocks (overlapped vectors)    | 61  |

| 4.5  | Results for vector size 512×16, 1 block (overlapped vectors)     | 62  |

| 4.6  | Results for vector size 512×16, 2 blocks (overlapped vectors)    | 62  |

| 4.7  | Results for vector size 1024×16, 1 block (overlapped vectors)    | 63  |

| 4.8  | Results for vector size 1024×16, 2 blocks (overlapped vectors)   | 63  |

| 4.9  | Results for vector size 128×16, 1 block (nonoverlapped vectors)  | 64  |

| 4.10 | Results for vector size 128×16, 2 blocks (nonoverlapped vectors) | 6-1 |

| 4.11 | Results for vector size 256×16, 1 block (nonoverlapped vectors)  | 65  |

| 4.12 | Results for vector size 256×16, 2 blocks (nonoverlapped vectors) | 65  |

| 4.13 | Results for vector size 512×16, 1 block (nonoverlapped vectors)  | 66  |

| 4.14 | Results for vector size 512×16, 2 blocks (nonoverlapped vectors) | 66  |

| 4.15 | Results for vector size $1024 \times 16$ , 1 block (nonoverlapped vectors)  | 67 |

|------|-----------------------------------------------------------------------------|----|

| 4.16 | Results for vector size $1024 \times 16$ , 2 blocks (nonoverlapped vectors) | 67 |

| 4.17 | Characteristics of ISCAS85 benchmark circuits                               | 69 |

| 4.18 | Results of data recovery in standard benchmark circuits                     | 71 |

|      |                                                                             |    |

# Chapter 1

### Introduction

The economic problems of digital testing and fault diagnosis are some of the main concerns in designing and manufacturing digital systems. Digital testing seeks to determine whether a system is functioning correctly. Fault diagnosis attempts to locate the failing components or silicon areas responsible for the malfunction if the system has failed a test [2]. With *integrated circuits* (ICs) rapidly increasing in complexity and decreasing in size, fault diagnosis is essential for IC manufacturing. It is used in the early production phase to identify design and process errors in order to effect design corrections and yield improvements. In addition, it is used to analyze devices that subsequently fail in the field to improve quality and minimize future failures. Improvements to the fault diagnosis methods can impact the overall testing and production cost.

Testing can be broadly categorized into voltage testing and parametric testing. Voltage testing is concerned with the logic values of circuit outputs (voltage levels) generated by input stimuli as compared with the logic values generated by a reference circuit for the same stimuli. Parametric testing is concerned with the measured values of circuit parameters, such as current. propagation delay or power consumption. and whether they fall within predetermined thresholds. This thesis focuses strictly on voltage testing and henceforth, the term testing shall mean voltage testing.

Testing can be either external or internal. External testing relies exclusively on an external tester to supply stimuli to the circuit under test (CUT), and to capture and evaluate the circuit responses. Its chief drawbacks are the expense of the complex, high-speed testing equipment (multi-million dollars): and the large volume of data managed by the tester, resulting in long testing times. Internal testing, such as built-in self-test (BIST), reduces the need for complex, expensive testing equipment by including testing circuitry on-chip. As circuit packing density doubles every 18 months, an increasing amount of silicon area (normally < 10%) can be used for BIST. By staying on-chip, BIST can proceed at higher internal circuit speeds making effective testing of larger, more dense ICs practical. Internal testing has become an indispensable technique for testing deep sub-micron ICs.

The last distinction between testing methods is off-line versus on-line testing. A test is characterized as off-line when the CUT must be taken out of normal operation to be tested. On-line testing methods perform board-level or chip-level testing during normal system operation. On-line testing is necessarily internal as a tester cannot be utilized during the normal system operation. Due to design complexity and high cost, on-line testing is mainly found in safety-critical systems.

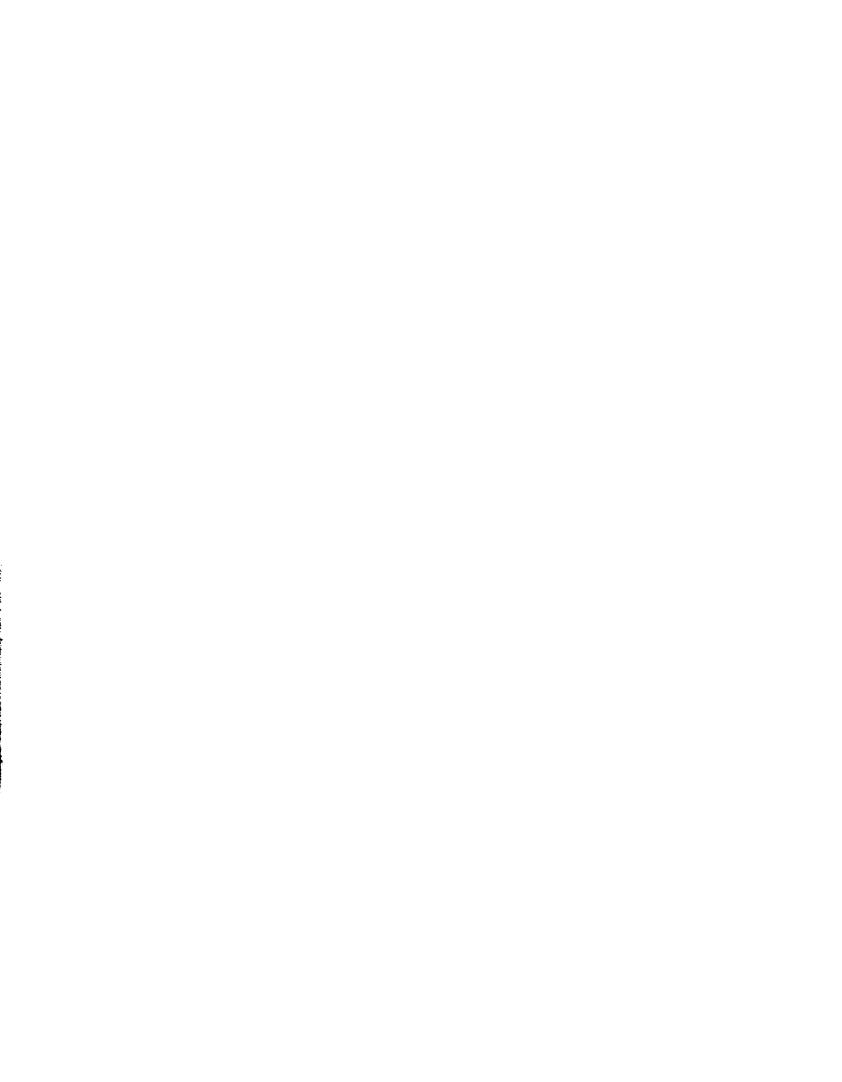

Figure 1.1 shows a typical off-line testing environment. The testing process in this environment consists of: (1) applying many stimuli to the CUT: (2) capturing the generated circuit responses; and (3) comparing the responses from the CUT to reference good circuit values to render a "pass/fail" judgement. Two basic components are needed for testing, whether external or internal: a mechanism to provide input stimuli to the CUT, and a mechanism to evaluate the generated circuit responses. In external testing these mechanisms are wholly contained within the tester, while in BIST some mechanisms are implemented on-chip.

In an ideal testing environment, every CUT would be exposed to all possible input stimuli during testing, termed exhaustive testing. Due to time and storage constraints. exhaustive testing is only practical for small circuits. For example, to exhaustively test a 100-input circuit with a test system able to apply 1 billion test patterns per second would require approximately  $4 \times 10^{13}$  years, i.e. several orders of magnitude greater than the age of the universe. To keep testing costs low, the test of a single IC should be accomplished in mere seconds. A practical solution to this problem is the random test [6]. A random test consists of a large, random selection of test patterns used to expose the CUT to a sample of its input space. A truly random selection of test patterns is undesirable for testing purposes since it is not repeatable (unless stored).

Figure 1.1: General testing environment

Repeatability is necessary to simplify the comparison of circuit responses. Instead. a pseudorandom test is used to approximate a random test. It has the properties of a random test but is fully repeatable. A pseudorandom pattern generator (PRPG) is a mechanism for generating repeatable sequences of pseudorandom test patterns. PRPGs can be realized directly in hardware for BIST applications.

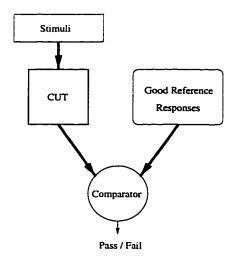

After applying an input stimulus, randomly generated or otherwise, it is necessary to compare the circuit response with a good reference. The obvious approach would be a direct bit-by-bit comparison of each response with its reference. This is impractical, however, due to the time required to compare numerous circuit responses in the test and the high storage demands of many reference responses. A more practical approach, suitable for BIST, is data compaction. Data compaction is destructive data compression with the primary objective of distinguishing different data streams. Data compaction is performed on the sequence of responses generated by the CUT. The final result is termed the signature of the CUT. This signature is compared to a precomputed good circuit signature to render a judgment on the CUT. Thus, only a single comparison is performed involving a small quantity of data (typically 16 - 32 bits) permitting short testing times, minimal storage needs, and high test quality. Several data compaction methods exist, including parity checking, transition counting and ones counting [6]. In practice, the mostly commonly used data compaction method is signature analysis [6]. Figure 1.2 presents a general signature

analysis-based testing environment.

Figure 1.2: Signature analysis testing environment

This thesis addresses issues in BIST employing PRPGs and signature analysis. Specifically, the problem of performing fault diagnosis in this testing environment is investigated. Pass/fail testing is an integral part of IC manufacturing: each fabricated part is placed on a tester for several seconds to determine whether it is functioning correctly. Those ICs that fail the test may require further tester time to gather diagnostic information to identify the defect(s) responsible. Economic constraints only allow mere seconds of tester time per IC. Thus improved methods of performing fault diagnosis can impact the total manufacturing cost of ICs. This thesis explores alternative diagnosis methods for ICs.

When the test of a CUT produces a "fail" result, post-testing diagnosis attempts to identify the physical defect or defects responsible. A very large scale integrated (VLSI) circuit may contain millions of transistors. A "fail" in a pass/fail test of an IC does not reveal which of the millions of transistors is defective. Therefore, no design corrections/improvements can be made to eliminate the failure causing problem; hence there is a need for post-testing diagnosis. Diagnosis of a CUT starts from errors observed during testing and attempts to identify the faults responsible. Errors are circuit responses inconsistent with reference responses. Faults are models

of physical defects within a circuit that may manifest as errors under specific input stimuli. While knowledge of circuit errors reveals the presence of defects in the CUT. knowledge of the faults reveals the location of potential defects in the circuit. This knowledge can be used to correct design problems or make design improvements to enhance fabrication yield.

Signature analysis, while a boon to pass/fail testing, presents unique challenges for fault diagnosis. Diagnosis requires a knowledge of the specific errors produced in the circuit responses. Signature analysis, however, loses this information during compaction toward the final signature of the CUT (typically 16 - 32 bits). Nevertheless, it is a widely used testing method due to advantages in testing speed and ready application in BIST systems. Instead, to fulfill the needs of fault diagnosis. special methods are needed to overcome the extreme data loss and obtain the lost stimulus/faulty response pairs. Ideally, this should be done with restricted built-in hardware, at-speed testing and least possible dependence on an external tester.

STUMPS<sup>1</sup> is a BIST architecture utilizing signature analysis first proposed by Bardell and McAnney [5] (STUMPS is introduced in detail in chapter 2). Although originally proposed for board-level testing, STUMPS has gained in popularity for IC-level testing [12]. It consists of a PRPG to provide test patterns and a parallel compactor to compact internal circuit responses. Test pattern generation and response compaction occur internal to the STUMPS-equipped device. The tester initiates the test and at its completion obtains and evaluates the final signature from the CUT. All circuit responses are lost during compaction and the final signature contains very little information for diagnosis.

A fault diagnosis scheme for use in a STUMPS environment is given by Waicukauski and Lindbloom [20]. This method partitions long circuit response sequences into short blocks (256 test vectors), and compares the intermediate signatures of each block with precomputed fault-free counterparts to identify blocks of responses that contain errors. If a discrepancy occurs, the circuit responses in the faulty block are scanned out in serial and stored for use in fault diagnosis. This method retrieves the uncompacted erroneous circuit responses in the CUT and stores them on the tester. It has

<sup>&</sup>lt;sup>1</sup>Self-Test Using MISR/Parallel SRSG (shift-register sequence generator)

been shown that often only a few faulty blocks of circuit responses are necessary for successful fault diagnosis.

Following data retrieval, actual fault diagnosis is a two-step process. Structural analysis of the CUT and subsequent fault simulation are used to derive the fault(s) responsible for the observed responses. First, structural analysis of the CUT is performed to create a list of faults that may cause the erroneous circuit responses obtained from the CUT. Each fault in the list is then simulated and the resulting responses are compared with the retrieved responses. If they are equal, the fault is considered as a possible explanation of the observed erroneous behavior, otherwise it is rejected. The final result of the fault diagnosis process is one or more faults modelling potential defects within the CUT.

The objective of this thesis is to explore alternative solutions to the data retrieval method used in Waicukauski's diagnosis scheme [19, 20]. The subsequent fault diagnosis procedures remain unchanged. In our solution, we propose to transfer partially compacted data from the CUT to the tester, and to use analytical methods off-line to recover the information lost during signature compaction.

Our proposed data recovery scheme significantly reduces the amount of data transferred from the CUT to the tester (typically by a factor of 8), and can eliminate the need for decision making by the tester on every intermediate signature. As a result, the tester time used for data retrieval for fault diagnosis can be significantly decreased, while employing a less expensive tester to perform the task. Since a state-of-the-art tester costs millions of dollars, our methods allow significant savings in the overall testing and production cost.

Our simulation results show that we can achieve comparable fault diagnostic resolution as that of Waicukauski. It further validates the feasibility of our proposed data recovery schemes. The remainder of this thesis is organized as follows.

Chapter 2 provides background information and literature review. Data compaction theory is discussed as a basis for the proposed data recovery scheme. The STUMPS testing architecture is then presented in detail. Past diagnosis efforts are reviewed. And lastly, fault diagnosis in the STUMPS environment is treated separately.

Chapter 3 presents the new data recovery scheme. Two error identification algo-

rithms used in the scheme are explained and stated with detailed examples of their operation. Complexity analysis of the two algorithms is given. Lastly, alternatives of the primary data recovery scheme are proposed with their advantages and disadvantages.

Chapter 4 describes the experiments performed to test the performance and feasibility of the data recovery schemes. The details of the simulation environments and justifications are given. The experimental results are presented along with analysis. Lastly, the software system used to perform the simulations is described.

Chapter 5 draws conclusions about the achieved results and summarizes the thesis.

## Chapter 2

## Background and Literature Review

This chapter presents the background topics relating to testing and diagnosis. Section 2.1 reviews the signature analysis-based data compaction technique. Section 2.2 discusses the STUMPS testing architecture, which is the basis of our new data recovery schemes. Section 2.3 presents a literature review of existing fault diagnosis methods, including simulation-based methods, signature analysis-based methods, and the recent error control code method. Lastly, section 2.4 presents the current STUMPS fault diagnosis scheme.

### 2.1 Signature Analysis

As introduced in chapter 1, signature analysis is a widely used data compaction technique for the purposes of testing complex VLSI circuits [2]. It transforms the generated response of a CUT into a compact signature (typically 16 - 32 bits). The evaluation of the CUT is then simply the comparison of the obtained signature with a precomputed reference signature; if the two are equal the CUT is judged "good". otherwise it is judged "faulty". The compaction process can be automated and realized in hardware as a linear feedback shift register (LFSR) to perform serial compaction or a multiple-input shift register (MISR) to perform parallel compaction. This section deals in detail with the operation of these two compactors.

# 2.1.1 Serial Data Compaction and Pseudorandom Test Generation

Signature analysis is based on the concept of cyclic redundancy checking (CRC), and is implemented in hardware with an LFSR [6]. A shift register is a collection of connected storage elements such that the state of each element is shifted to the next in response to a clock signal. An LFSR is a shift register with a linear feedback network of XOR gates feeding certain storage elements. The next state of a storage element is determined by its source network of XOR gates. To function as a data compactor, the input of the LFSR is supplied the response of the CUT in serial. This perturbs the state of the LFSR according to the feedback network. The signature is the final state of the LFSR following the completion of the test.

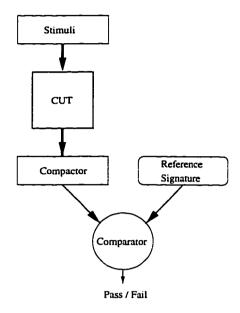

The data compaction process performed by an LFSR is equivalent to polynomial division over GF(2) [14]. A binary bit stream can be represented as a polynomial by associating each bit of the stream with the coefficient of a unique power of a dummy variable of the polynomial. For example, the bit stream  $b_n b_{n-1} \cdots b_0$  is represented by the polynomial  $b_n x^n + b_{n-1} x^{n-1} + \cdots + b_0 x^0$ . The LFSR itself can be represented by a polynomial, P(x), with the feedback connections indicated by non-zero terms of the polynomial [6]. Figure 2.1 shows a sample LFSR with polynomial  $P(x) = x^3 + x^2 + 1$ .

Figure 2.1: An LFSR with  $P(x) = x^3 + x^2 + 1$

The compaction process viewed as polynomial division is as follows. The serial input sequence to be compacted is the numerator polynomial, M(x); the LFSR performing the division is the denominator or divisor polynomial, P(x); the serial output of the LFSR is the quotient polynomial, Q(x); and the final state of the LFSR is the remainder polynomial or signature, S(x). Mathematically, signature compaction is formulated as:

$$Q(x) = \frac{M(x)}{P(x)} + S(x).$$

To perform the polynomial division, the LFSR is initialized to an all-zero state and the serial input sequence, M(x), is presented to the LFSR input, high-order bit first. The quotient bit sequence, Q(x), is shifted out of the LFSR output, high-order bit first, and the final state of the LFSR following compaction is the signature, S(x).

As well as serving as data compactors, LFSRs can be used for test pattern generation. An LFSR, initialized to a non-zero state, will cycle through a pseudorandom sequence of states with successive applications of a clock signal. The sequence of states is determined by the polynomial of the LFSR. An LFSR that generates the maximum length sequence of non-repeating states is termed a primitive LFSR. A primitive m-bit LFSR will generate all states corresponding to the possible combination of m bits but for the all-zero state. The maximum length sequence of states of an m-bit primitive LFSR is thus  $(2^m - 1)$  states.

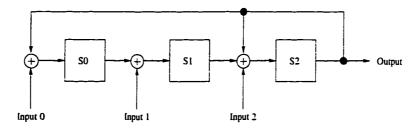

### 2.1.2 Parallel Data Compaction

A drawback of employing LFSRs for data compaction is the single data input which only permits the compaction of a serial data stream. To compact multiple data streams in parallel, an LFSR can be modified into a MISR [6] by adding an input and an XOR gate between every two adjacent register cells, retaining the same feedback connections as the original LFSR. An m-bit MISR is able to compact m bits of data per clock cycle. Figure 2.2 shows an example MISR with  $P(x) = x^3 + x^2 + 1$ .

Figure 2.2: A MISR with  $P(x) = x^3 + x^2 + 1$

For notational convenience, a polynomial can be represented by a binary sequence where each non-zero coefficient corresponds to a "1", and "0", otherwise. As an example, the polynomial,  $P(x) = x^3 + x^2 + 1$ , can be represented by the binary sequence, 1101.

### 2.2 The STUMPS Testing Environment

Many off-line BIST architectures employ signature analysis along with other techniques such as scan testing and partitioning [2] to increase the testability of a circuit. The goal of scan testing is to transform a sequential circuit into a purely combinational circuit for testing purposes. The response of the circuit is then solely dependent on the current stimulus, not past stimuli. To achieve this goal requires access to the internal circuit storage elements where normally no such outside access exists. To that end, scan testing replaces all memory elements with special scan registers connected to form scan chains. A scan register is a dual-mode memory element: in normal mode data is loaded from the data input line; in scan-mode data is loaded from a separate scan-in port. The scan-in and scan-out ports of a scan chain are made externally accessible, permitting data to be serially scanned in or out of the internal memory elements. The other testing technique of circuit partitioning attempts to divide a circuit into many sub-circuits that can be tested separately. Partitioning can be realized with scan testing by creating many separate scan chains to divide a circuit.

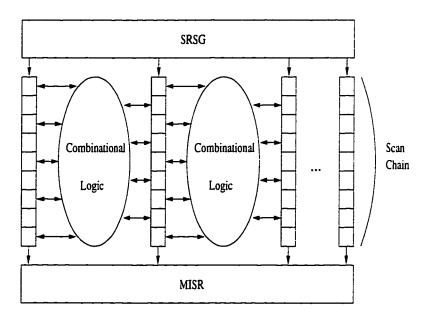

An off-line BIST architecture incorporating scan testing and partitioning is the self-test using MISR/parallel SRSG<sup>1</sup> (STUMPS) testing architecture [5]. It was originally proposed to test multichip modules at the board-level. A special testing chip implements the SRSG and MISR components of STUMPS which, respectively, generate test patterns for the other chips on the board and compact in parallel their output responses.

Each chip to be tested must utilize scan-based flip-flops [5], configured into scan chains (or data streams). A number of scan chains, per board, are formed by directly connecting the scan-in and scan-out ports of individual chips. The scan chains are supplied pseudorandom test patterns in parallel from the SRSG. By scanning in known test patterns into the scan chains, a sequential circuit is converted into a combinational circuit during testing. Combinational circuits are easier to test as their response depends only upon the current input vector, not on past inputs.

The scan chains provide the inputs to the combinational logic blocks and capture the generated responses. Normal circuit operation is governed by a system clock or

<sup>&</sup>lt;sup>1</sup>Acronym of shift-register sequence generator.

clocks. Scan testing also introduces a separate test clock to govern the serial flow of data within scan chains. With multiple applications of the test clock, data from the SRSG is scanned into the scan chains, loading test patterns into the chips to be tested. The regular system clock is then asserted once to capture the responses from the chips back into the scan chains. The subsequent test patterns are then scanned in, while simultaneously, the circuit responses are being scanned out to the test chip where they are compacted by the MISR. After the application of many test patterns, the final signature is scanned out of the test chip and compared with a error-free signature to determine whether response errors were detected.

STUMPS has since become a standard IC-level BIST architecture [12]. Memory elements are realized as scan registers connected to form scan chains. The functions of the test chip are implemented directly within the IC as dedicated BIST resources. Figure 2.3 shows the IC-level STUMPS architecture showing the configuration of scan chains, SRSG and MISR.

Figure 2.3: The STUMPS architecture

### 2.3 Existing Diagnosis Methods

Testing and diagnosis have different purposes and conflicting requirements. Testing should be fast, comprehensive and inexpensive since it is performed on every device manufactured. Techniques used to speed testing, such as signature analysis, severely hamper fault diagnosis by compacting, and losing, the circuit responses necessary for diagnosis. Diagnosis is only performed on devices that fail testing, thus the primary requirements are of diagnostic accuracy and detail. The results of diagnosis must be accurate and specific to focus attention on the location of the defect so that it can be quickly corrected. To reduce cost, it is desirable to perform diagnosis with existing testing methods and with minimal tester support.

A circuit may have countless possible physical defects that can produce faulty behavior. Diagnosis employs fault models to systematically characterize the majority of the potential defects. A fault model is a set of rules and assumptions which describe the effects that defects have on digital circuits [2]. The results of fault diagnosis are one or more faults (or fault classes) in the adopted fault model. Many fault models have been proposed to describe various defects, including: briding faults, transition faults, delay faults, and stuck-open faults. The most common is the *stuck-at* fault model, it assumes fault-free logic gates with defects causing signal lines between gates to be permanently stuck at either logic 1 or logic 0, regardless of stimulus [2]. Much of the early work in fault diagnosis has been based on the assumption of the stuck-at fault model. This section reviews published literature as a history of fault diagnosis.

#### 2.3.1 Simulation-based Methods

Early diagnosis approaches attempt to enumerate the behavior of faults in the assumed fault model [1]. A fault dictionary is compiled by simulating the CUT with every fault and recording the corresponding circuit response. Diagnosis then consists of the simple task of locating the observed response of the CUT in the fault dictionary and noting the corresponding fault(s). Disadvantages of this technique are set by the limits of the adopted fault model and the inability to diagnose multiple faults.

#### 2.3.2 Signature Analysis-based Methods

Signature analysis based methods attempt to solve the problem of response data loss inherent with data compaction. Considerable effort has been made in identifying and locating errors in the uncompacted circuit responses based on the observed signature [6, 8, 9, 11, 13, 19, 20, 21]. There are three types of signature analysis-based fault location techniques: fault dictionary, algebraic analysis and intermediate signatures.

#### Fault Dictionary

The fault dictionary-based method constructs a look-up table containing the modeled faults and their corresponding faulty signatures [6]. Diagnosis consists of locating the observed faulty signature in the dictionary. The small size of a signature makes this method limited at discriminating individual faults as many faults may produce the same signature.

#### Algebraic Analysis

Algebraic analysis methods attempt to compute the erroneous circuit response from the faulty signature obtained from testing.

The first such method was given by McAnney and Savir [11]. It uses an LFSR that is the reciprocal of the LFSR used for compaction. The reciprocal LFSR is initialized with the faulty signature obtained from the CUT then clocked to reverse the compaction and compute where the error was introduced. This method constrains the test length to be no greater than the state space of the LFSR. At most two errors in the test sequence can then be identified.

A similar method by Chan and Abraham [8] is applicable to both serial and parallel compactors. It uses state transition matrices to describe the compaction process. An analytical formulation is given to calculate the error location in the test sequence. The method is limited to identifying which compaction step introduced the errors or the channel(s) containing the errors.

A method employing a number of cyclic registers to perform compaction was presented by Savir and McAnney [13]. Utilizing multiple cycling registers, the errors in the test sequence are computed from the signatures remaining in the registers. The

number of errors that can be effectively identified is approximately half the length of the shortest register. Three cycling registers of relatively prime lengths (i.e. sharing no common divisors) can identify up to 50 errors in a sequence of 2<sup>20</sup> bits using a 300-bit signature. Disadvantages include the physical size of the long cycling registers and the added storage for a fault dictionary of 300-bit signatures.

In [9], a partitioning scheme to decompose a final error signature into partial error signatures is presented. Existing methods are then used to derive the error sequence for each partial error signature. The final error sequence is given as the product of the partial error sequences. Although this scheme can identify multiple errors. a particular disadvantage is the time and space complexity of the partitioning algorithm for significant numbers of errors.

#### Intermediate Signatures

Intermediate signature methods are based on signatures obtained at regular intervals during testing. For diagnostic purposes, circuit responses are partitioned into short blocks. An intermediate signature is obtained after the compaction of each block of responses. The intermediate signatures are compared with error-free counterparts to target failing blocks for diagnosis.

Waicukauski's intermediate signature method [19, 20] is described in chapter 1 on page 5. Intermediate signatures are computed every block of 256 test vectors. Blocks with faulty signatures are targeted for data retrieval and subsequent fault diagnosis. This method is treated further in section 2.4.

An alternative approach is employed at Northern Telecom [21]. In this method intermediate signatures are computed after every test vector. Data retrieval is not performed. Instead, fault simulation is used to locate the fault or faults that produce the observed intermediate signatures.

#### 2.3.3 Error Control Code Method

The diagnosis method in [22] uses a special programmable MISR (PMISR) to perform compaction. A set of equation based on Reed-Solomon codes [10] are obtained from the faulty signatures and solved to identify the error-capturing frames. Each scan

chain is then retested to locate the actual erroneous flip-flops. Drawbacks of this method include the need to retest the CUT with different configurations of the PMISR and the computational expense necessary to solve the system of equations.

### 2.4 Fault Diagnosis in a STUMPS Environment

Fault diagnosis is an important process in the design of IC chips with sub-micron technologies. As well as helping to correct design errors, it can be used to improve yield and increase circuit reliability. Fault diagnosis is the opposite of fault simulation: it starts with a stimulus and observed faulty circuit response, and then determines the fault set that can produce the faulty response given the same stimulus. To reduce the fault set, many stimulus/faulty response pairs must be considered. Knowledge of the fault(s) potentially responsible for the observed behavior is then used by the designer to correct design problems or improve yield.

Fault diagnosis requires that many stimulus/faulty response pairs be obtained from a CUT. However, this is at odds with current internal testing methods. The necessity of testing increasingly dense ICs has led to the innovation of BIST. One form of BIST is STUMPS which is both an aid and a hindrance to fault diagnosis. It is an aid since it permits the observation of many internal circuit nodes, aiding diagnostic resolution. However, it is a hindrance, as during testing these observation points are inaccessible from off-chip. Additional, post-testing time must be expended to scan out this internal circuit information where it can be used for fault diagnosis.

Once initialized, the testing of a STUMPS equipped IC occurs mainly on-chip. The result obtained is a final signature (typically 16 - 32 bits long) which is the compacted response of the CUT for the entire test set. This signature is then compared off-chip by the tester with the good signature (obtained through logic simulation of the good circuit) to produce a pass/fail judgment of the IC. By staying mainly on-chip, testing can proceed at much higher speeds.

The final signature is suitable for rendering a pass/fail judgment of a CUT, however on its own it is grossly inadequate for fault diagnosis. Consider a STUMPS implementation consisting of 16 data streams, each of 1024 bits and a test length of 100.000 patterns. Each circuit response consists of (16 × 1024) bits or 2 Kbytes of information; while the entire test consists of 200 Mbytes of information. The circuit response information lost during data compaction is unrecoverable from a final signature of several bytes. This makes IC-level fault diagnosis a difficult and costly task.

Data retrieval is one method for obtaining the lost circuit response information [20]. Recall that in STUMPS, access to all data streams is only available through two ports, a scan-in port for input and a scan-out port for output. Data retrieval in STUMPS is the process of scanning out in serial the contents of all data streams to obtain the response of the CUT.

To perform fault diagnosis, many stimulus/faulty response pairs must be scanned out from the CUT. However, scanning out the entire circuit response for every stimulus in the test set is time-consuming and unnecessary. Not every circuit response will be faulty, certain stimuli may not induce errors in circuit responses, producing the same responses as the good circuit. Fault-free circuit responses can be determined through circuit simulation, thus it is desirable to only scan out the faulty circuit responses.

For the purposes of data retrieval, the test set is divided into discrete intervals of one or more test patterns. Each interval has an *intermediate signature* computed by logic simulation of the good circuit. This is the intermediate result of compacting all responses up to and including the responses from the current testing interval. All such signatures are compiled into a dictionary of intermediate signatures. During data retrieval, the intermediate signatures obtained from the CUT are compared with their counterparts in the dictionary. A discrepancy indicates that the preceding test interval must contain at least one faulty response, whereupon all responses in the present interval are scanned out to be used for fault diagnosis.

Consider a system with intervals consisting of 100 test patterns, the specific steps of the data retrieval process are [6]:

- **Step 1:** Initialize the BIST circuitry in the CUT to the beginning of the test sequence.

- Step 2: Apply the next 100 test patterns to the CUT.

- Step 3: Scan out the intermediate signature from the CUT.

Step 4: Compare the signature with the counterpart in the dictionary. If the signatures are the same, the state of the BIST circuitry in the CUT is restored to the state before the signature was scanned out. Otherwise, if the signatures differ, the BIST circuitry in the CUT is restored to the state at the start of the current interval. The 100 test patterns are then re-applied, but instead of being compacted each response is scanned out and stored for further fault diagnosis. Once all responses in the interval have been scanned out, the BIST circuitry in the CUT is restored to that of the good circuit at the end of the current test interval.

Step 5: If there are more intervals in the test set, go to Step 2.

**Step 6:** The stored responses are transferred from the tester to a workstation where fault diagnosis can proceed off-line.

After data retrieval is complete, fault diagnosis [20] is performed to determine the fault class(es) responsible for the observed faulty responses. In addition to the faulty responses, the following data and systems are necessary to perform fault diagnosis: (1) a structural description of the CUT, (2) a fault simulator, and (3) a PRPG to generate the test patterns in the test. The first step of fault diagnosis involves the structural analysis of the circuit to create a minimal fault list. Subsequently, each fault in the list is simulated with the generated stimuli and the resulting responses are compared with the retrieved responses. If the simulated responses match all retrieved responses, the fault is accepted. Otherwise, the fault is rejected as it does not reproduce all observed responses. The final result of fault diagnosis is a set of faults that can reproduce the observed faulty behavior and thus are potentially responsible for the defect(s) in the CUT.

As can be seen from the previous steps, data retrieval is a complex, lengthy process as compared with pass/fail testing. A pass/fail judgment of a CUT involves a single, uninterrupted application of the test set followed by the scan-out and comparison of the final signature. The only tester-CUT interaction is at the start to initiate the test, and at the end to scan-out the final signature. Data retrieval, on the other hand, demands many more interactions between the tester and the CUT. Each test

interval is initiated and halted, the intermediate signatures are scanned out. the BIST circuitry is reset, and ultimately the circuit responses are scanned out. Data retrieval occupies an expensive testing system for an extended length of time that can otherwise be used to verify many more newly fabricated ICs. It transfers more data from the CUT than may be necessary to accomplish fault diagnosis.

The data recovery schemes presented in the following chapter attempt to address these shortcomings. The new schemes obtain the faulty circuit responses from partially compacted information transferred from the CUT and exploit analytical methods implemented off-line.

# Chapter 3

# **Data Recovery Schemes**

In this chapter we present a new scheme for data recovery in MISR-based data compaction. The primary data recovery scheme [16] is introduced in section 3.1. New terms with examples, are defined in section 3.2. Two new error identification algorithms, central to the data recovery scheme, are presented in sections 3.3 and 3.4. respectively, along with detailed examples of their operation and analysis of their computational complexity. The first algorithm is able to perfectly identify all errors confined to any two known data streams. The second algorithm generalizes this approach to unknown data streams, permitting the identification of errors in any two data streams. Lastly, alternatives to the primary data recovery scheme are proposed in section 3.5. The alternatives enhance the primary scheme by increasing the amount of information available for error identification and by significantly reducing testing time.

### 3.1 New Data Recovery Scheme

The proposed data recovery scheme consists of both a hardware and software component. The hardware component is an additional BIST resource in the form of a second MISR added to the STUMPS architecture. The software component implements error identification algorithms that compute the erroneous data bits in the uncompacted circuit responses. The erroneous data bits are combined with the good circuit responses obtained by simulation to produce the uncompacted circuit responses. The

new scheme replaces the data retrieval method presented in chapter 2. It requires additional BIST hardware and off-line computation in exchange for the elimination of extra tester-CUT interactions and reduction of the volume of data transferred between tester and CUT.

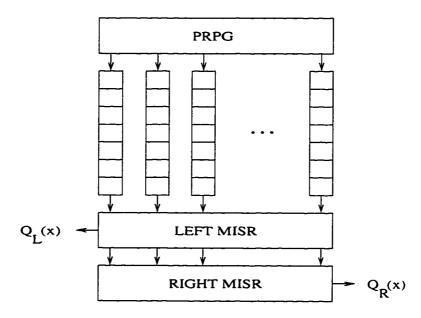

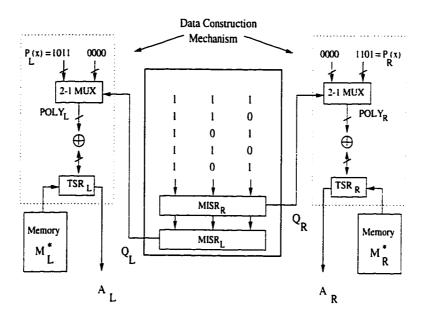

Recall from chapter 2 that the traditional STUMPS architecture has a single MISR that compacts the circuit response. The necessary hardware support for the data recovery scheme consists of the standard STUMPS architecture with the addition of a left shifting MISR and a corresponding scan-out port, as shown in figure 3.1. With two MISRs, one shifting left and another shifting right, two different quotient sequences,  $Q_L$  and  $Q_R$ , can be obtained from the MISRs. The quotient sequences are the only information obtained from the CUT for data recovery. The proposed data recovery scheme uses analytical techniques to compute the circuit responses lost during the data compaction based on the quotient sequences.

Figure 3.1: Modified STUMPS architecture

### 3.1.1 Modelling of Parallel Data Compaction

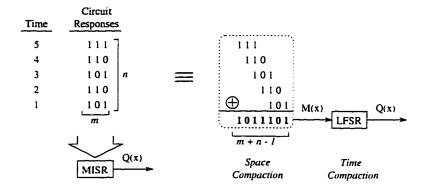

The signature compaction process in a MISR can be considered as two concurrent compaction processes [23]. The first process is space compaction which transforms n, m-bit words into a serial stream of (n + m - 1) bits, which is termed the space

compaction sequence. The second process is time compaction which performs polynomial division of the space-compacted stream by an LFSR with the same feedback polynomial as the MISR. An example of the two processes is shown in figure 3.2. This dual view of MISR-based data compaction permits the construction of the space compaction sequence from the quotient sequence and the signature. The space compaction sequence can then be used to identify errors in the uncompacted circuit response. In figure 3.2 it can be seen that each bit of the space compaction sequence is the modulo-2 sum of at most three response bits. Thus, errors in these response bits are localized to this one bit of the space compaction sequence. No such localization of errors exists in the quotient sequences, however: the first introduced error bit will perturb many subsequent bits in the quotient sequence.

Figure 3.2: Modelling MISR as concurrent compactions

### 3.1.2 Construction of Space Compaction Sequences

We term the reverse of signature compaction data construction. Thus, equation

$$M(x) = P(x)Q(x) + S(x)$$

can be considered as the process of constructing the input sequence, M(x), from the given quotient sequence, Q(x), divisor polynomial, P(x), and signature, S(x).

Consider a data block of  $(n \times m)$  bits, where n and m are the numbers of rows and columns of the data block, respectively. Let M(x) be the (n+m-1)-bit serial stream space compacted by an m-bit MISR. We assume that the bits which made up Q(x) are collected during the data compaction. By linearity, the process of constructing

M(x) from the given P(x), Q(x) and S(x) can be considered as:

$$M(x) = M_1(x) + M_2(x) + \cdots + M_n(x) + S(x),$$

where  $M_k(x) = Q_k(x)P(x)$ , and  $Q_k(x)$  equals the quotient, Q(x), with all bits except the k-th bit set to 0. During compaction, a Q(x) bit is shifted out of the MISR at each clock cycle. This bit can then be used to build one subsequence,  $M_k(x)$ , and to complete the construction of one bit of M(x).

**Example 3.1** Consider the MISR in figure 2.2, with P(x)=1101, and the data block and the space compaction stream, M(x)=1011101, in figure 3.2. The Q(x) collected during time compaction is 11000, and the signature, S(x), is 001. According to the partial construction method described above, we have:

$$M_1(x)=1101000; M_2(x)=0110100; M_3(x)=0000000; M_4(x)=00000000:$$

$$M_5(x)=0000000, \text{ and}$$

$$M(x)=M_1(x)+M_2(x)+M_3(x)+M_4(x)+M_5(x)+S(x)=1011101.$$

Figure 3.3: Data construction system

Figure 3.3 depicts an implementation of the data construction technique developed by Dr. Sun et al. [15, 17], which can be realized in either hardware or software. The system consists of the following components.  $MISR_R$  and  $MISR_L$  implement the divisor polynomial,  $P_R(x)=1101$ , and its reciprocal,  $P_L(x)=1011$ , respectively.  $Q_L(x)$  and  $Q_R(x)$  are the quotient sequences obtained during the data compaction in real time. The memory contains the predetermined error-free space compaction sequences,  $M_L^*(x)$  and  $M_R^*(x)$ .  $TSR_L$  and  $TSR_R$  are (m+1)-bit left and right shift registers, respectively.  $POLY_L$  and  $POLY_R$  are 2-1 MUXs.  $Q_L$  and  $Q_R$  serve as the MUX Select signals to construct  $M_L(x)$  and  $M_R(x)$ , respectively. The binary representations of the polynomials of the MISRs are chosen when Select=1: otherwise all zeros are chosen. The output of the system is the compaction sequence error masks.

$$A_L = M_L \oplus M_L^*$$

$$A_R = M_R \oplus M_R^* ,$$

generated in real-time during testing of the CUT. The proposed data recovery system then uses the  $A_L$  and  $A_R$  sequences to recover the information bits lost during data compaction.

We explain the right shifting operation of the system using the data in figure 3.2. where m=3, n=5,  $M_R(x) = M_R^*(x)=1011101$  and  $Q_R(x)=11000$ . The operation of the left shifting process is symmetric.

- 1. The most significant (m+1) bits of  $M_R^*(x)$ , 1011, are loaded into  $TSR_R$ .

- 2. The first 3-bits of the  $(3 \times 5)$  circuit response, 101, are fed into and compacted by the two MISRs simultaneously. The first 1 output bit of  $Q_R(x)$  from  $MISR_R$  causes 1101 to be selected by  $POLY_R$ . In the case of a 0 output bit of  $Q_R(x)$ . 0000 is selected.

- 3. The contents of  $TSR_R$  are XORed with that of  $POLY_R$  producing 0110, which is then stored back to  $TSR_R$ .

- 4. The contents of  $TSR_R$  are shifted 1-bit to the left and 1-bit of the remaining  $M_R^*(x)$  in memory is simultaneously shifted into  $TSR_R$ . The bit  $\mathbf{0}$  of  $TSR_R$  is shifted out. A  $\mathbf{0}$  indicates "no error" in the last bit of the space compaction sequence, and a  $\mathbf{1}$  indicates "an error".

- 5. Repeat steps 2 to 4 until the end of the data compaction process.

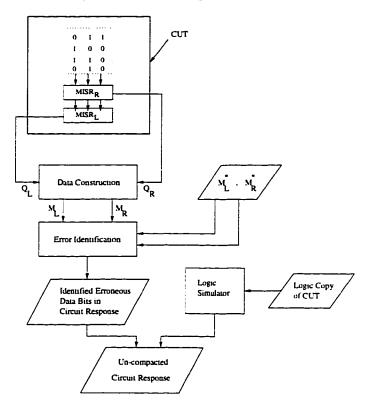

#### 3.1.3 The Primary Data Recovery Scheme

The newly proposed data recovery scheme takes as input the left and right quotient sequences and produces as output the uncompacted circuit responses. Figure 3.4 shows a block diagram of the data recovery scheme. The first step entails the construction of the left and right space compaction sequences,  $M_L$  and  $M_R$ , from the quotient sequences,  $Q_L$  and  $Q_R$ , obtained from the CUT. The space compaction sequences with their precomputed error-free counterparts,  $M_L^*$  and  $M_R^*$ , are used to compute the compaction sequence error masks,  $A_L$  and  $A_R$ . These are used by the error identification algorithms to compute the errors present in the original uncompacted circuit responses. Finally, the identified errors are combined with the good circuit responses. obtained by simulation, to produce the complete uncompacted circuit responses.

Figure 3.4: Data recovery scheme

The new data recovery process proceeds as follows:

Step 1: Initialize the BIST circuitry in the CUT.

**Step 2:** Capture the  $Q_L$  and  $Q_R$  sequences from the left and right shifting MISRs

after a faulty block is identified by the comparison of intermediate signatures during a test.

- Step 3: Reconstruct the left and right space compaction sequences.  $M_L$  and  $M_R$ . from the  $Q_L$  and  $Q_R$  sequences, respectively.

- Step 4: Invoke the analytical error identification algorithms to compute the set of erroneous circuit response bits that produced the  $M_L$  and  $M_R$  sequences.

- Step 5: Combine the results of step 4 with the good circuit responses obtained via logic simulation to obtain the faulty circuit responses.

- Step 6: Proceed with further fault diagnosis to locate defective components/areas based on the recovered erroneous circuit responses obtained in step 5.

The following section formally defines the terminology used. The subsequent sections present the error identification algorithms required by the data recovery process (step 4).

## 3.2 Definitions and Declarations

The basic entity used in the discussion of the error identification algorithms is the response vector, which is the response of the CUT to one stimulus. In a STUMPS environment, the response vector can be viewed as an  $(n \times m)$  data block, where n is the length of each data stream (assuming all data streams are of equal length), and m is the number of data streams compacted in parallel by the m-bit MISRs. Further, assume that V such response vectors were generated by V test patterns or test vectors.

Our data recovery scheme employs two MISRs during data compaction, one shifting to the left and another shifting to the right. In our model of MISR-based compaction, the circuit responses can be viewed as both a left and right space compaction that produce the left and right space compaction sequences, respectively.

**Definition 3.1** A response vector is an  $(n \times m)$  collection of data bits generated by the CUT from the application of one test pattern.

**Definition 3.2** The *left space compaction sequence*, denoted as  $M_L(x)$ , is the sequence of bits resulting from the space compaction performed by the left shifting MISR. Further,  $M_L^*(x)$ , denotes the error-free left space compaction sequence obtained by simulation of the good circuit. Analogously, for the right-space compaction, we have  $M_R(x)$  and  $M_R^*(x)$ .

Any data bit in a response vector can be identified by the row and columns indices. i, j respectively, indexing into an  $(n \times m)$  data block. A test set will consist of some number V compacted response vectors. Elements are further discriminated according to their respective response vector. v.

**Definition 3.3** An *element* is a data bit in one  $(n \times m)$  response vector. For a test length of V vectors, any element, written  $E_{i,j}^v$ , can be uniquely identified by the tuple (v, i, j), where v is the vector  $(1 \le v \le V)$ , i is the data row  $(1 \le i \le n)$ , and j is the data column or data stream  $(1 \le j \le m)$ .

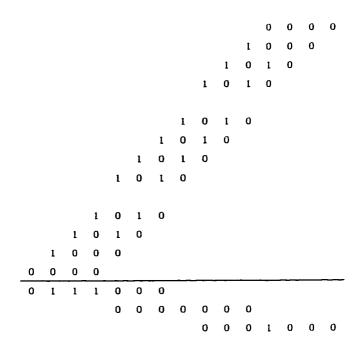

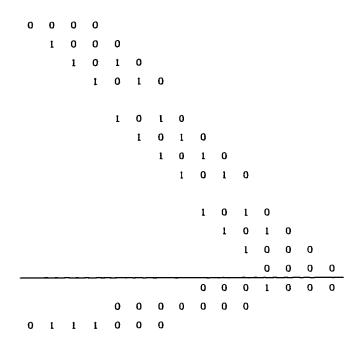

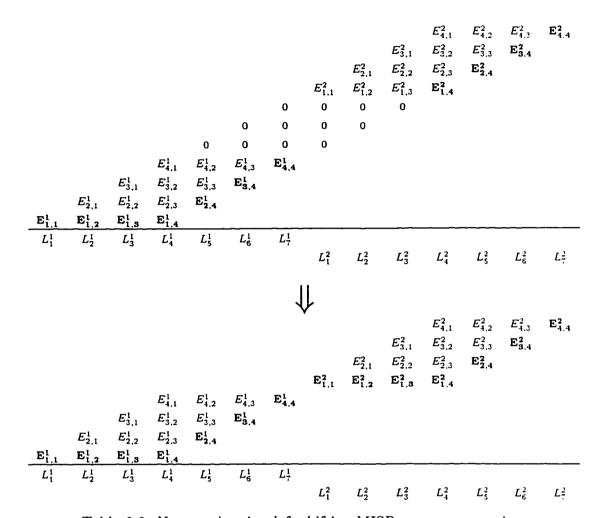

Elements in the left or right compaction are grouped into left and right space compaction columns, respectively. The left space compaction columns of response vector v, are labeled from left to right as  $L_1^v$ ,  $L_2^v$ , ...,  $L_{n+m-1}^v$ . Similarly the right space compaction columns of response vector v, are labeled from right to left as  $R_1^v$ ,  $R_2^v$ , ...,  $R_{n+m-1}^v$ . As with individual elements, space compaction columns are identified as to their corresponding vector, v. Associated with each space compaction column is a unique key element which is used to construct all member elements of the column. Tables 3.1 and 3.2 show the left and right response vector configurations for (V=3, n=4, m=4).

**Definition 3.4** A space compaction column is the set of data bits whose modulo-2 sum forms one bit of a space compaction sequence.

Tables 3.1 and 3.2 show a three vector configuration. A specific feature of note is the *overlapping* compaction columns between individual response vectors. Specifically, every two consecutive response vectors share (m-1) compaction columns. A compaction column can have elements from two consecutive vectors.

Table 3.1: Left shifting MISR space compaction

**Example 3.2** In table 3.1, compaction columns  $L_1^2$ ,  $L_2^2$ ,  $L_3^2$  overlap columns  $L_5^1$ ,  $L_6^1$ ,  $L_7^1$ , respectively; likewise, columns  $L_1^3$ ,  $L_2^3$ ,  $L_3^3$  overlap columns  $L_5^2$ ,  $L_6^2$ ,  $L_7^2$ .

**Definition 3.5** The *key elements* of the left space compaction columns are  $E_{1,1}^1$ ,  $E_{1,2}^1$ , ...,  $E_{1,m}^1$ , and  $E_{i,m}^v$ , where i = 1, 2, 3, ..., n and v = 1, 2, 3, ..., V.

**Definition 3.6** The *key elements* of the right space compaction are  $E_{1,1}^1, E_{1,2}^1, \ldots$   $E_{1,m}^1$ , and  $E_{i,1}^v$ , where  $i=1,2,3,\ldots,n$  and  $v=1,2,3,\ldots,V$ .

**Example 3.3** The key elements of the response vectors in tables 3.1 and 3.2 are shown in bold. For instance, the key element of column  $L_7^2$  is  $E_{4,4}^2$  (table 3.1), and that of  $R_4^2$  is  $E_{1,1}^2$  (table 3.2).

**Definition 3.7** Given a key element,  $E_{i,j}^v$ , the column members are the elements in the corresponding space compaction column.

**Example 3.4** For key element  $E_{1,1}^2$  in table 3.2, the members of the space compaction column in the right compaction are:  $\{E_{1,1}^2, E_{2,2}^2, E_{3,3}^2, E_{4,4}^2\}$ .

Table 3.2: Right shifting MISR space compaction

**Definition 3.8** The *left* and *right space compaction sequence error masks*, denoted as  $A_L(x)$  and  $A_R(x)$  are defined as:

$$A_L(x) = M_L(x) \oplus M_L^*(x)$$

$$A_R(x) = M_R(x) \oplus M_R^*(x).$$

$A_L(x)$  and  $A_R(x)$  are the left and right space compaction sequence error mask for the entire test length V; the subsequences of  $A_L(x)$  and  $A_R(x)$ , denoted respectively as  $A_L^v(x)$  and  $A_R^v(x)$  ( $1 \le v \le V$ ), are the left and right space compaction sequence of vector v.

An individual subsequences  $A_L^v(x)$  is extracted from  $A_L(x)$  by right shifting  $A_L(x)$   $((v-1)\times m)$  times and considering the least significant (n+m-1) bits. Likewise,  $A_R^v(x)$  can be extracted from  $A_R(x)$ .

Having extracted the subsequences, there is a direct relation between bits in a space compaction subsequences and the value of space compaction columns, as follows:

$$L_i^v = A_L^v[i],$$

$$R_i^v = A_R^v[i].$$

**Example 3.5** Consider tables 3.1 and 3.2. They depict a scenario with three  $(4 \times 4)$  response vectors. If the left and right space compaction sequence error masks are. respectively,  $A_L(x) = 0001110010001011$  and  $A_R(x) = 001100100000010$ . the corresponding subsequences are:

$$A_L^1(x) = 1000101, \ A_R^1(x) = 0000010$$

$A_L^2(x) = 1100100, \ A_R^2(x) = 0010000$   $A_L^3(x) = 0001110, \ A_R^3(x) = 0011001.$

The following definitions pertain specifically to entities used by the error identification algorithms.

**Definition 3.9** The *Boolean equation set* is the set of equations formulated from the left and right space compaction columns of a response vector. The equations in the set can be solved simultaneous to establish the values of elements in the vector.

**Definition 3.10** The solution set is a set of equations with each equation consisting of an element equal to a bit value. This set is the result of simultaneously solving a set of Boolean equations.

**Definition 3.11** An *inconsistent* set of equations is a set with two or more equations that imply contradictory values for one or more variables.

**Example 3.6** The set  $B = \{ E_{1,1}^1 = 1, E_{1,1}^1 \oplus E_{4,4}^1 = 0, E_{4,4}^1 = 0 \}$  is inconsistent since both  $E_{1,1}^1 = 1$  and  $E_{1,1}^1 = 0$  are implied.

# 3.3 Two-known-stream Error Identification Algorithm

The proposed algorithm is able to identify all erroneous bits in a  $(n \times m)$  response vector under the following constraints: (a) the m input data streams to the MISRs are independent, i.e. the errors in one stream do not affect the others. (b) errors are

localized in at most two data streams, and (c) the data streams containing errors are known.

As previously defined, a compaction column is a set of data bits whose modulo-2 sum forms one bit of a space compaction sequence. Thus each column can be written as a Boolean sum of up to m elements (the unknowns) equal to the respective bit in a space compaction sequence. For example, in table 3.2, assuming compaction column  $R_6^1$  corresponds to a bit value of 1 in a space compaction sequence, the resulting equation would be:  $(E_{3,1}^1 \oplus E_{4,2}^1 \oplus E_{1,3}^2 \oplus E_{2,4}^2 = 1)$ . Given a set of such equations, they could be solved simultaneously to obtain the value of each element.

The total number of elements in a response vector, and hence the number of unknowns, is  $(n \times m)$ . The number of possible equations per  $(n \times m)$  response vector is the number of compaction columns in the left and right space compaction. i.e. (2(n+m-1)). This system of equations cannot uniquely determine  $(n \times m)$  unknowns. Thus the larger problem of uniquely determining the entire  $(n \times m)$  vector is impossible given only the information contained in the two space compaction sequences. Instead we reduce the problem and require that all erroneous data bits occur in at most two known data streams (assumptions (b) and (c) above).

By limiting the focus to at most two erroneous data streams, the number of unknown elements is at most  $(2 \times n)$ . The values of the other  $((m-2) \times n)$  elements can be computed by logic simulation of the good circuit, i.e. the error-free values. The number of equations per vector remains the same at (2(n+m-1)). Next, consider the error masks of the data bits, instead of the actual values, as follows:

$$E_{error-mask} = E_{error-free} \oplus E_{erroneous}$$

.

The  $((m-2) \times n)$  non-erroneous elements then attain a value of 0 and can be dropped from the equations. Likewise, the space compaction sequence error masks must be used in the equations instead of the space compaction sequences. Thus we have a system of (2(n+m-1)) equations in  $(2 \times n)$  unknowns. This system can be solved simultaneously to uniquely determine the error mask value of each unknown element. The actual value of each element can then be computed as:

$$E_{actual-value} = E_{error-mask} \oplus E_{error-free}$$

To summarize, for the case (V = 1), error bits in a  $(n \times m)$  vector are to be identified. The vector can be viewed as a left and right space compaction, respectively divided into left and right space compaction columns.

Each space compaction column has a value provided by a bit in the respective left or right space compaction error mask. The following points illustrate the error identification method:

- 1. There are at most  $(2 \times n)$  elements in the erroneous data streams.

- 2. The left and right compaction columns form a set of (2(n+m-1)) Boolean equations in  $(2 \times n)$  unknowns (the elements in the erroneous data streams).

- 3. The value of each equation is the corresponding bit of the left or right space compaction sequence error mask.

- 4. The set of equations can be solved simultaneously to obtain unique error mask values for each of the  $(2 \times n)$  elements.

- 5. The actual value of each element is:  $E_{actual-value} = E_{error-mask} \oplus E_{error-free}$ .

The above method holds for one vector in isolation, i.e. (V = 1). However, for (V > 1), a compaction column can have member elements from two adjacent vectors, see tables 3.1 and 3.2. The number of equations for each vector is always (2(n+m-1)). However, the number of elements, and thus unknowns, is no longer  $(2 \times n)$ .

For response vector v where (v = 1 or v = V), there is one adjacent vector. The number of elements from vector v is  $(2 \times n)$ . Additionally, the left compaction can contribute at most (m-1) elements from the adjacent vector and likewise the right compaction, for an extra (2(m-1)) elements. Thus, the total number of elements, and hence unknowns, is  $(2 \times n + 2(m-1) = 2(n+m-1))$ . These can be uniquely determined by (2(n+m-1)) equations.

For each vector v where (1 < v < V), there are two adjacent response vectors. (v-1) and (v+1). The two adjacent vectors can contribute a maximum of (2(m-1)) elements per space compaction for a total of

$$2 \times n + 2(2(m-1)) = 2(n + 2(m-1))$$

elements. These cannot be uniquely determined by only (2(n+m-1)) equations. However, if vector (v-1) was previously solved, the values of all elements in this vector are established. The solution equations for elements in vector (v-1) that appear in the equations for vector v, numbering at most (2(m-1)), can be added to the set of (2(n+m-1)) equations for a total of (2(n+2(m-1))) equations. This enhanced set can uniquely determine the (2(n+2(m-1))) elements. Since vector (v=1) can be successfully solved on its own, this method has a starting point, and all subsequent vectors can be solved in succession.

Error identification proceeds one response vector at a time. Although the complete set of equations for multiple response vectors can be written and solved simultaneously, this becomes infeasible with large test lengths consisting of several thousands of test vectors. Instead, each vector is solved individually. The left and right space compaction sequence error masks for the entire test length are respectively.  $A_L$  and  $A_R$ . To perform error identification, individual subsequences.  $A_L^v$  and  $A_R^v$ , for vector v must be extracted from  $A_L$  and  $A_R$ , respectively.  $A_L^v$  is simply the (n+m-1) least significant bits of  $A_L$  right-shifted  $((v-1) \times n)$  times;  $A_R^v$  is likewise obtained from  $A_R$ .

# 3.3.1 Algorithm

In the following algorithm,  $c_1$  and  $c_2$  are the erroneous data streams with  $(1 \le c_1 < c_2 \le m)$ , B is the set of Boolean equations, and  $Solution^{v-1}$  and  $Solution^v$  are the solution sets for response vectors (v-1) and v, respectively. The subfunctions. LKE(). RKE(), LCM() and RCM(), compute the left and right key elements and column membership, respectively. They are defined following algorithm Identify2Known().

```

Function Identify2Known(A_L^v, A_R^v, c_1, c_2, Solution^{v-1})

/* computes the values of elements in data streams c_1 and c_2 of vector v^*

/* with compaction sequence error masks A_L^v and A_R^v

/* Solution^{v-1} is the solution set for the previous vector */

B \leftarrow \text{extract equations from } Solution^{v-1}

for k = 1 to (n + m - 1) do

```

```

KeyElement_L \leftarrow LKE(L_k^v)

Column_L \leftarrow LCM(KeyElement_L)

B \leftarrow B \cup Equation(Column_L, c_1, c_2, A_L^v[k])

KeyElement_R \leftarrow RKE(R_k^v)

Column_R \leftarrow RCM(KeyElement_R)

B \leftarrow B \cup Equation(Column_R, c_1, c_2, A_R^v[k])

Solution^v \leftarrow solve B

/* an inconsistent set of equations is indicated via a flag */

return Solution or inconsistent flag

end . /* Identify2Known() */

Function LKE(L_k^v)

/* computes the key element of the left compaction column L_k^v */

if (v == 1) then

if (k \leq m) then

return E_{1,k}^v

else

return E_{k-m+1,m}^v

else

if (k < m) then

return LKE(L_{n+k}^{v-1})

else

return E_{k-m+1,m}^v

end . /* LKE() */

Function RKE(R_k^v)

/* computes the key element of the right compaction column R_k^v */

if (v == 1) then

if (k \leq m) then

```

```

return E^v_{1,m-k+1} else return E^v_{k-m+1,1} else if (k < m) then return RKE(R^{v-1}_{n+k}) else return E^v_{k-m+1,1} end . /* RKE() */

```

The quantity, LastVector, in the following two functions, is the number of the last response vector to be recovered. For example, in a failing block of 256 response vectors, LastVector = 256.

```

Function LCM(E_{i,j}^v)

/* computes the set of column members of the left compaction */

/* column given by key element E_{i,j}^{v} */

s \leftarrow i; \, t \leftarrow j; \, C \leftarrow \emptyset

if (v == LastVector) then

while ((s \le n) \text{ AND } (t \ge 1))

C \leftarrow C \cup E_{s,t}^v

s \leftarrow s + 1

t \leftarrow t - 1

else

while (t \ge 1)

if (s \le n) then

C \leftarrow C \cup E_{s,t}^v

else

3 \leftarrow s \mod n

C \leftarrow C \cup E_{3,t}^{v+1}

```

```

s \leftarrow s + 1

t \leftarrow t - 1

/* C is the set of column elements */

return C

end . /* LCM() */

Function RCM(E_{i,j}^v)

/* computes the set of column members of the right compaction */

/* column given by key element E_{i,j}^{v} */

s \leftarrow i; t \leftarrow j; C \leftarrow \emptyset

if (v == LastVector) then

while ((s \le n) \text{ AND } (t \le m))

C \leftarrow C \cup E_{s,t}^v

s \leftarrow s + 1

t \leftarrow t + 1

else

while (t \leq m)

if (s \leq n) then

C \leftarrow C \cup E_{s,t}^v

else

\beta \leftarrow s \bmod n

C \leftarrow C \cup E_{\beta,t}^{v+1}

s \leftarrow s + 1

t \leftarrow t + 1

/* C is the set of column elements */

return C

end . /* RCM()*/

```

Function  $Equation(C. c_1. c_2. value)$

```

/* formulates the Boolean equation for a compaction column */

/* C is a set of member elements of a compaction column */

/* c_1, c_2 are the erroneous data streams /*

/* value is a bit-value of a space compaction sequence */

/* the function returns the formulated Boolean equation */

if (E_{a,c_1}^{v_1} \in C \text{ AND } E_{b,c_1}^{v_2} \in C) then

return \{E_{a,c_1}^{v_1} \oplus E_{b,c_2}^{v_2} = value\}

else if (E_{a,c_1}^{v_1} \in C) then

return \{E_{a,c_1}^{v_1} = value\}

else if (E_{b,c_2}^{v_2} \in C) then

return \{E_{b,c_2}^{v_2} = value\}

else

return \{0 = value\}

end . /* E_{a,c_1}^{v_2} = value

```

## 3.3.2 Error Identification Example