### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

UM®

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

.

.

#### University of Alberta

CODE AND DATA OUTLINING

by

Peng Zhao

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of **Doctor of Philosophy**.

Department of Computing Science

Edmonton, Alberta

.

Fall 2005

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence ISBN: Our file Notre retérence ISBN:

#### NOTICE:

The author has granted a nonexclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or noncommercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadiennesur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manguant.

To Fang,

without a doubt

.

.

...

## Abstract

In this dissertation we investigate compiler techniques to address the performance problems caused by heterogeneous execution frequency of code in the same function and heterogeneous access pattern of fields in the same data structure. These heterogeneous characteristics are bad for performance. On one hand, it is frequent that instructions in the same function have very different execution frequencies. There is often infrequently referenced *cold* code, such as exception handlers, intertwined in frequently invoked *hot* functions. Cold code in hot functions not only degrades instruction cache efficiency but also makes host functions too large to be inlined. On the other hand, programmers organize their data layout in a semantically meaningful way that often does not match the runtime access pattern well. This data organization causes inefficient data cache utilization.

We use compiler outlining techniques to address these performance problems that are difficult to handle by programmers. For programs with heterogeneous execution frequency, we use function outlining to split cold code out of the host function. Function outlining makes the host function smaller and more amenable for inlining optimization because the compiler is then able to do partial inlining, *i.e.* inline only the hot parts of a callee. To address the heterogeneous data pattern issue, we use data outlining or reshaping, which splits large data structures into smaller ones, to improve the efficiency of data cache.

We describe in detail the necessary analysis and transformations needed to preserve correct program behavior in code and data outlining. In both function outlining and data outlining, we conduct a study of possible strategies. Our study shows that, although function outlining can be used to reduce function sizes (by up to 97%) and partial inlining improves performance by up to 5.75%, partial inlining has very limited effect on enabling more aggressive inlining for SPEC2000 benchmarks. The major benefits of partial inlining are actually the benefits of function outlining, which become more pronouncing when inlining is enabled. We also found that data reshaping could improve performance dramatically: one of the benchmarks studied achieves 2.1 times speedup with proper reshaping strategy. Detailed analysis explains these performance results.

## Acknowledgements

I want to heartedly thank everybody who generously offered me help during my quest of Ph.D degree.

First of all, I am indebted to my advisor, Dr. José Nelson Amaral, for his numerous valuable discussions and suggestions. It is he who introduced me to the field of compiler research. I also appreciate his patience and support throughout my entire project.

Thanks also go to the other members of my Ph.D. exam committee members, Dr. Bruce Cockburn, Dr. David Padua, Dr. Jonathan Schaeffer, Dr. Lorna Stewart, and Dr. Duane Szafron. I thank them for agreeing to serve in my candidacy exam committee and for their time and energy spent on reviewing my proposal and thesis. Especially, their discussions during my candidate exam made me start to think about the possibility of data outlining, which is the second part of this thesis.

I thank Sun C. Chan and Shin-ming Liu for their insightful discussions on function outlining. I also thank Dr. Yaoqing Gao, Shimin Cui and Raúl Silvera for their discussions and cooperation on my data-outlining work at IBM. I got much help from the mailing lists for Open64, ORC, Pfmon, and Pro64 when I picked up my experimentation platforms. Here I specially thank Kaiyu Chen, Buqi Cheng, Jim Dehnert, Stephane Eranian, Lixia Liu, Michael Murphy, Chandrasekhar Murthy, Chengyong Wu, Shuxin Yang, Qingyu Zhao, and Shukang Zhou. My project would have been much more difficult without their kind help.

Last, but not least, this dissertation would not be possible without the help from my family. I thank my parents, Weigui Zhao and Yueqing Zhao, for their moral support throughout this five-year journey. My wife, Fang Liu, has demonstrated her unconditional love by numerous encouragements when I felt frustrated and by sacrificing the living standards that she has long deserved to be with me.

Financial support for this dissertation was provided by the Natural Sciences and Engineering Research Council (NSERC) of Canada. I also thank Intel Corp. and IBM Corp. for the internship opportunities that allowed me to expand my work on function outlining and data outlining, respectively.

# **Table of Contents**

| 1 | Intr     | roduction 1                                            |

|---|----------|--------------------------------------------------------|

|   | 1.1      | Research Goal                                          |

|   | 1.2      | Contributions                                          |

|   | 1.3      | Dissertation Organization                              |

| 2 | Bac      | kground 6                                              |

|   | 2.1      | Inter-Procedural Optimization (IPO) 6                  |

|   |          | 2.1.1 Tractable IPO                                    |

|   | 2.2      | Profiling-guided IPO 10                                |

|   | 2.3      | IPO Case Study                                         |

|   |          | 2.3.1 ORC without IPO                                  |

|   |          | 2.3.2 ORC with IPO                                     |

| 3 | Inli     | ning Tuning 16                                         |

| Ŭ | 3.1      | Introduction                                           |

|   | 3.2      | Overview of ORC Inlining                               |

|   | 3.3      | Inlining Tuning                                        |

|   | 0.0      | 3.3.1 Adaptive Inlining                                |

|   |          | 3.3.2 Cycle Density                                    |

|   | 3.4      | Results                                                |

|   | 0.4      | 3.4.1 Experimental Environment                         |

|   |          | 3.4.2 Performance Analysis                             |

|   |          | 3.4.3 Compilation Time and Executable Size Analysis 28 |

|   |          | 3.4.4 Motivation for Partial Inlining                  |

|   | 3.5      | Related Work                                           |

| 4 | <b>T</b> | ction Outlining 33                                     |

| 4 |          |                                                        |

|   | 4.1      |                                                        |

|   | 4.2      | Background                                             |

|   |          | 4.2.1 WHIRL Tree Introduction                          |

|   |          | 4.2.2 Region                                           |

|   | 4.3      | Function Outlining 38                                  |

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

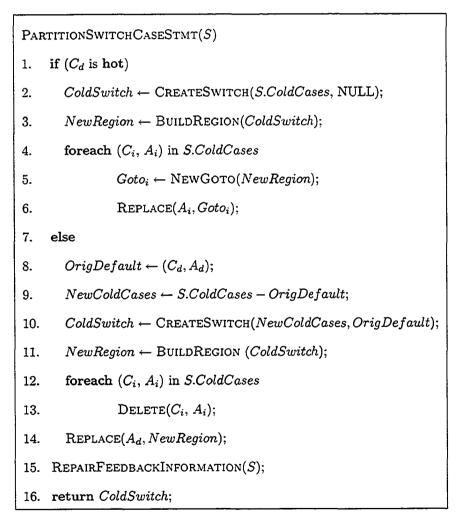

|    |      | 4.3.1   | Reorganize a Switch Statement                | 39 |

|----|------|---------|----------------------------------------------|----|

|    |      | 4.3.2   | Handling Frequent Early Returns (ER)         | 45 |

|    |      | 4.3.3   | Outlining Candidate Identification           | 45 |

|    |      | 4.3.4   | Function Splitting and Patching              | 48 |

|    |      | 4.3.5   | Performance Tuning                           | 55 |

|    | 4.4  | Result  | ts                                           | 56 |

|    |      | 4.4.1   | Experiment Configuration                     | 56 |

|    |      | 4.4.2   | Function Outlining Performance               | 56 |

|    |      | 4.4.3   | Outlining Statistics                         | 57 |

|    |      | 4.4.4   | Partial Inlining                             | 59 |

|    |      | 4.4.5   | Aggressive Partial Inlining                  | 60 |

|    | 4.5  | Relate  | ed Work                                      | 60 |

|    |      | 4.5.1   | Function Splitting                           | 61 |

|    |      | 4.5.2   | Region Formation Algorithm                   | 62 |

|    |      | 4.5.3   | Preservation of Semantics in Splitting       | 63 |

|    |      | 4.5.4   | Code Layout                                  | 63 |

| 5  | Dat  | a Out   | lining or Reshaping                          | 64 |

|    | 5.1  | Introd  | luction                                      | 64 |

|    | 5.2  | Data    | Reshaping                                    | 66 |

|    |      | 5.2.1   | Overview                                     | 66 |

|    |      | 5.2.2   | Data Shape Analysis                          | 67 |

|    |      | 5.2.3   | Structure Partition Plan and Array Reshaping | 70 |

|    |      | 5.2.4   | Array Reshaping                              | 73 |

|    | 5.3  | Exper   | imental Study                                | 76 |

|    |      | 5.3.1   | Experimental Platform                        | 77 |

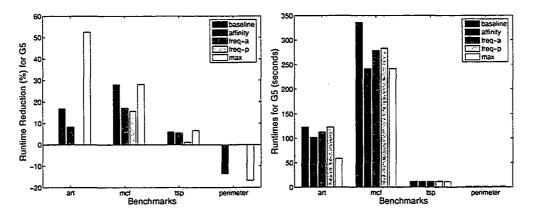

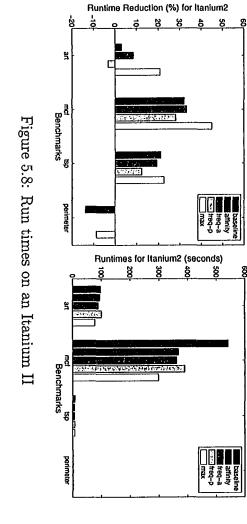

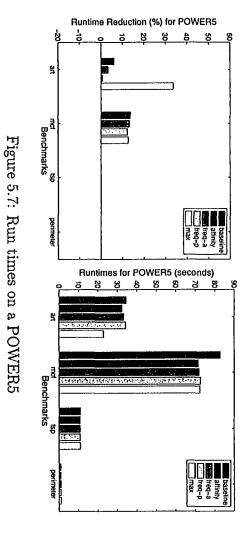

|    |      | 5.3.2   | Run Time Improvement                         | 78 |

|    |      | 5.3.3   | Micro-architecture Performance Study         | 81 |

|    | 5.4  | Relate  | ed Work                                      | 85 |

|    |      | 5.4.1   | Data Layout Optimization                     | 85 |

|    |      | 5.4.2   | Loop Restructuring                           | 86 |

|    |      | 5.4.3   | Data Prefetching                             | 86 |

| 6  | Cor  | nclusio | ons and Future Work                          | 88 |

|    | 6.1  | Concl   | usions                                       | 88 |

|    | 6.2  |         | re Work                                      | 89 |

|    |      |         | Further Inlining                             | 89 |

|    |      |         | Extension of Forma Data Outlining Framework  | 89 |

|    |      | 6.2.3   | Automatic Heuristics Tuning                  | 90 |

| Bi | blio | graphy  | 7                                            | 91 |

# List of Tables

| 3.1 | Impact of <i>cycle_density</i> on executable size and compilation time | 29 |

|-----|------------------------------------------------------------------------|----|

| 4.1 | Variable patching rule                                                 | 53 |

| 4.2 | Semantics of <i>ReturnFlag</i> on the return of the new PU             | 54 |

| 4.3 | Strategy combinations                                                  | 57 |

| 4.4 | Statistics of outlining                                                | 58 |

| 5.1 | Address-arithmetic-based reshaping                                     | 74 |

| 5.2 | Pointer-based reshaping                                                | 74 |

| 5.3 | Characteristics of the experimental platforms, memory and page         |    |

|     | sizes given in bytes (†: DCache+ICache, $\ddagger$ : off-die)          | 77 |

| 5.4 | Compiler versions in the performance study                             | 78 |

|     |                                                                        |    |

# List of Figures

| 2.1  | The procedure barrier against compiler optimization                 | 7  |

|------|---------------------------------------------------------------------|----|

| 2.2  | Inter-procedural constant propagation on variable $a$               | 7  |

| 2.3  | Inter-procedural constant propagation enables function special-     |    |

|      | ization and dead store elimination                                  | 8  |

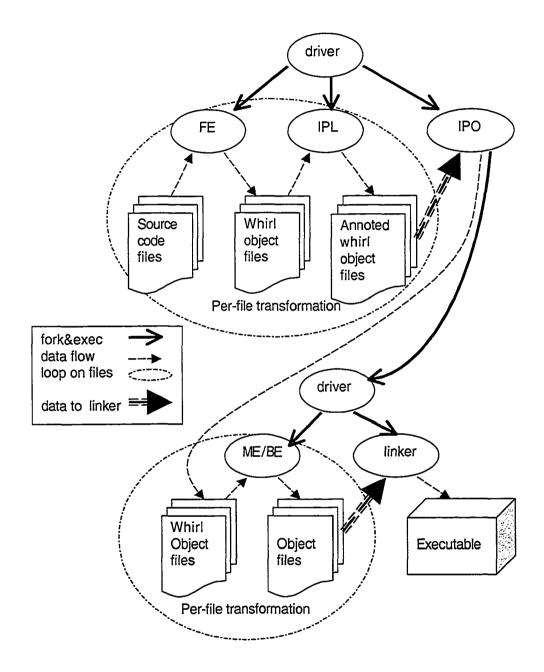

| 2.4  | ORC compilation without IPO                                         | 12 |

| 2.5  | IPO-involved ORC compilation                                        | 14 |

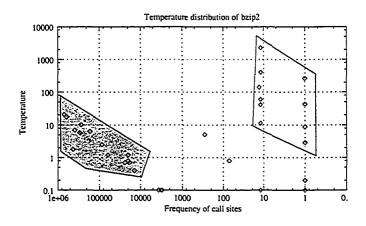

| 3.1  | Temperature distribution of bzip2                                   | 20 |

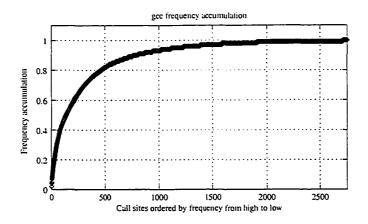

| 3.2  | Frequency accumulation of gcc (the top 2,750 of all 19,000 call     |    |

|      | sites are plotted)                                                  | 21 |

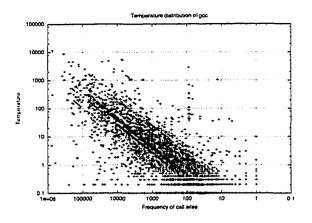

| 3.3  | Temperature distribution of gcc                                     | 23 |

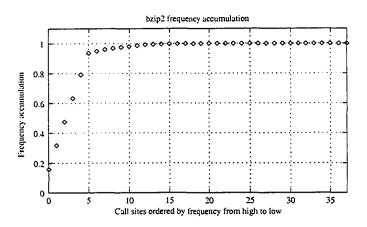

| 3.4  | Frequency accumulation of bzip2 (the top 38 of all 239 call sites   |    |

|      | are plotted)                                                        | 24 |

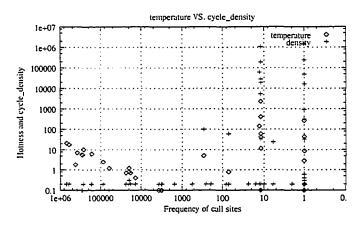

| 3.5  | Cycle density vs. temperature (bzip2)                               | 25 |

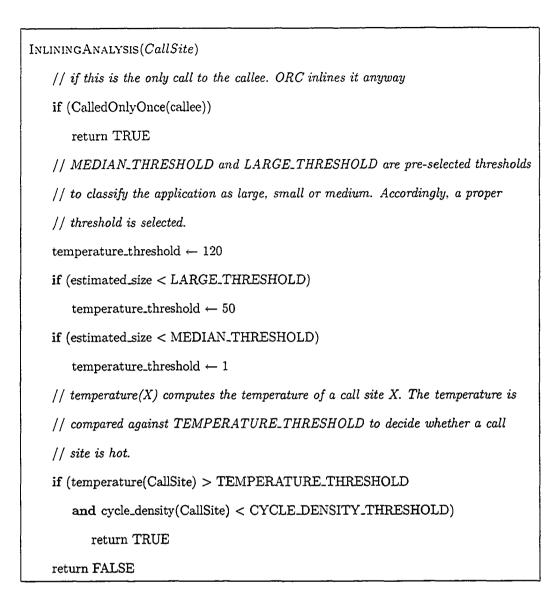

| 3.6  | Adaptive inlining in ORC                                            | 26 |

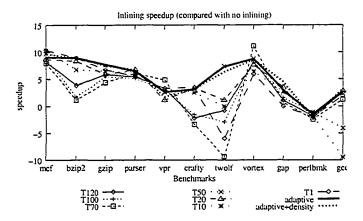

| 3.7  | Overall performance comparison                                      | 27 |

| 3.8  | Final performance comparison                                        | 28 |

| 3.9  | Call sites breakdown                                                | 30 |

| 4.1  | Example source code & WHIRL tree                                    | 36 |

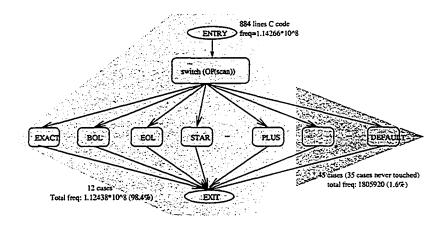

| 4.2  | Annotated control flow graph of function <i>regmatch</i> in perlbmk | 39 |

| 4.3  | Partitioning regmatch in perlbmk                                    | 40 |

| 4.4  | Case clustering                                                     | 42 |

| 4.5  | Partition benefit analysis                                          | 43 |

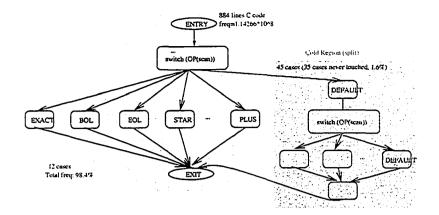

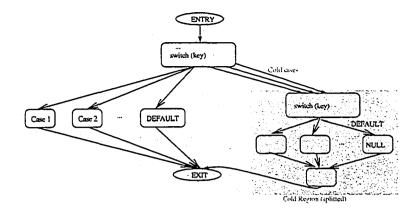

| 4.6  | Partitioning a <i>switch</i> with hot default cases                 | 44 |

| 4.7  | Partition and split switch                                          | 44 |

| 4.8  | Handling early exits                                                | 46 |

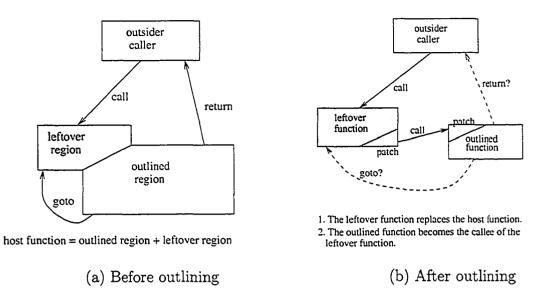

| 4.9  | Outlining transformation                                            | 49 |

| 4.10 | Function foo before function splitting                              | 50 |

| 4.11 | The original <i>foo</i> function after function splitting           | 51 |

| 4.12 | The new <i>fooNEW1</i> function after function splitting            | 51 |

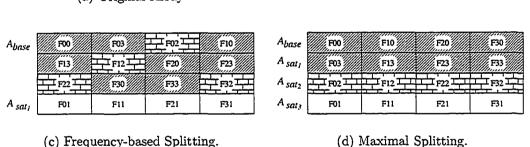

| 4.13 | Different outlining strategies (shaded code is cold)                | 55 |

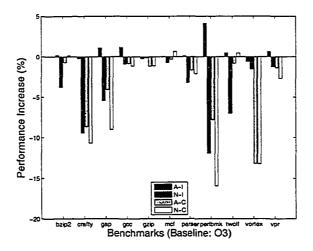

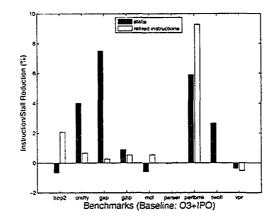

| 4.14 | Performance of Function Outlining                                   | 57 |

|      |                                                                     |    |

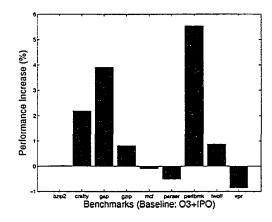

| 4.15 | Performance of Partial Inlining            | 59 |

|------|--------------------------------------------|----|

| 4.16 | Effects on Stalls and Instructions         | 60 |

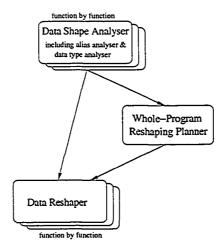

| 5.1  | The Forma data reshaping framework         | 66 |

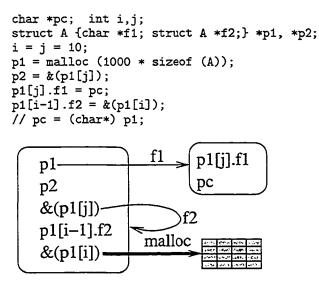

| 5.2  | Field-sensitive Steensgaard alias analysis | 67 |

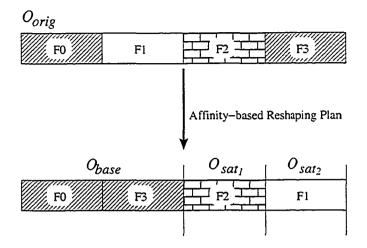

| 5.3  | Reshaping planning (affinity-based)        | 71 |

| 5.4  | Different reshaping planning strategies    | 71 |

| 5.5  | Run times on a G5                          | 78 |

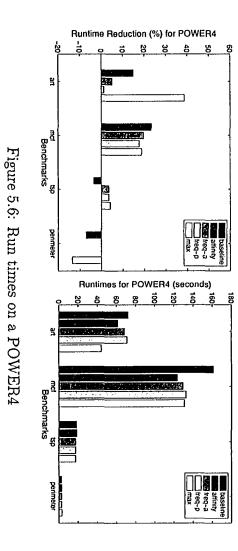

| 5.6  | Run times on a POWER4                      | 79 |

| 5.7  | Run times on a POWER5                      | 79 |

| 5.8  | Run times on an Itanium II                 | 79 |

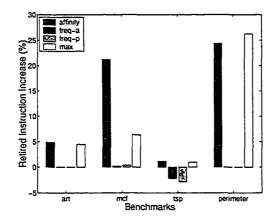

| 5.9  | Retired instructions on Itanium-II         | 81 |

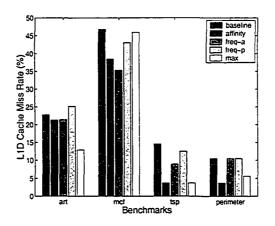

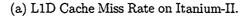

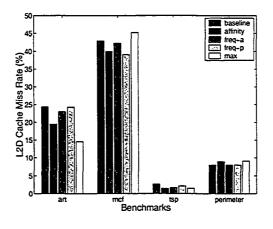

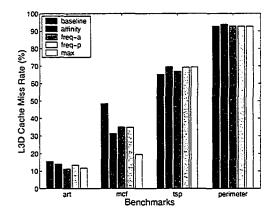

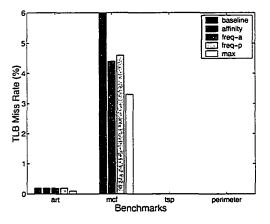

| 5.10 | Data cache (levels 1 and 2) efficiency     | 82 |

| 5.11 | Data cache (level 3) and TLB efficiency    | 83 |

## Chapter 1

## Introduction

### 1.1 Research Goal

Over the past four decades, we have been witnessing the ever-increasing speed of modern microprocessors due to advances in semiconductor fabrication and architectural innovation. On the other hand, people are working hard to improve programmer productivity by adopting software engineering techniques that emphasize modularity, code reuse, and maintainability. There is a gap between performance engineering and software engineering. Software productivity is often emphasized and the programs produced with advanced software engineering techniques are often suboptimal in performance because they cannot fully utilize the resources or architectural features of the underlying hardwares. This gap is still widening. A good compiler should bridge this gap by transforming high-level applications into hardware-friendly binaries.

In this dissertation, we deal with two specific problems arising from the semantic gap between software engineering and performance engineering. The first problem stems from the heterogeneous frequency<sup>1</sup> of code in a single function. When writing a program, programmers tend to place semantically-related code together in a function, even though the execution frequencies of these codes might differ significantly. A good example is error and exception handling code. As a consequence, there are often many cold (*i.e.* infrequently-executed) code segments in a hot function. Putting code segments with heterogeneous execution frequencies together deteriorates instruction cache effi-

<sup>&</sup>lt;sup>1</sup>In this thesis, we call the number of occurences of executing a piece of code the execution frequency of the code. Similarly, the number of times a piece of data is accessed is its access frequency. Heterogeneous frequency is a conceptual term. When two frequencies are very different (*e.g.* 0 versus 100000), we say they are heterogeneous.

ciency, interferes with a compiler's goal of focusing its resources and time on frequently-executed code, and, more importantly, makes host functions too large to be inlined.

The second problem studied in this thesis is the performance penalty due to a semantics-oriented data layout. In high-level programming languages, programmers use aggregate data structures, such as structs and classes, to organize their data. All the features of a given object are put together in the same aggregate data structure, without consideration of runtime access patterns. This data layout also prevents better performance for several reasons. First, the frequency of access to fields in the same data type may vary significantly with *hot fields* accessed very frequently and *cold fields* seldom referenced. Placing fields with very different access frequencies together in memory hurts performance because the cold fields pollute the data cache and waste memory bandwidth. Second, the runtime data access pattern might not be consistent with the access frequency distribution. In other words, hot fields are not necessarily accessed together. This means that the temporal locality of certain hot fields is degraded by other hot fields.

During preliminary investigation toward this thesis, we spotted the abovementioned problems in some popular benchmarks. This motivated us to investigate the performance potential of compiler techniques to address these problems. Since the performance setback of heterogeneous characteristics in both instruction and data were unclear at the start of our study, we decided to study both.

Generally, the unifying technique of this thesis, outlining, consists of removing a cold part from a hot host function or data structure. To handle the cold code segments in a hot function, we use function outlining to split them out of their host functions and generate new functions to hold these split code segments. The original code segments in the host functions are replaced by function calls to the new functions. Function outlining separates hot code from cold code and makes the original hot function smaller and therefore more amenable to inlining optimization. Because only the hot portions in a function are inlined after function outlining, we call it *partial inlining*. To make the data layout more friendly to the underlying hardware, we split an object into two or more smaller objects. Each smaller object holds fields that have high access affinity. Accordingly, we split arrays that contain aggregate data structures into multiple smaller arrays. The result of the data outlining is a data layout that has a smaller memory footprint, has better locality and is more amenable to hardware data prefetching.

Important research questions include:

• Would function outlining followed by partial inlining yield performance improvements in industry-standard benchmarks? To achieve partial inlining, we need region identification algorithms to find the cold code segments in a hot function. Sometimes the cold code in a function is not well organized. Therefore, we need some transformations to reorganize the codes so that they are easier to split. Regions that are split out of the host function might cause extra runtime function calls. We could suffer serious performance degradation if hot codes are split out of a host function. To gain performance by partial inlining, the performance degradation of function outlining itself must be kept strictly under control. Hence, function outlining must achieve a balance between reduced host function sizes and potential increase in runtime function calls. Finally, to make function outlining safe, we also need to preserve correct program behavior when splitting code out of a function.

• Can data outlining be made safe to be integrated into a productionlevel compiler? The transformed program must retain its original semantics. Because of the prevailing usage of pointers and type casting in the C/C++ programming languages, transforming data accesses is not a trivial task. If two data accesses are aliased with each other, transforming one of them means that we must also update the other one. Also, data outlining should be avoided if a memory location is referenced through multiple views; it is dangerous to do transformation without a consistent starting point. If the safety problem is solved, does data outlining results in performance improvements?

### 1.2 Contributions

The primary contributions in this dissertation include:

- By carefully tuning the inlining framework in the Open Research Compiler (ORC), we found that large function bodies are among the major impediments to beneficial inlining. This suggests an opportunity for function outlining and partial inlining.

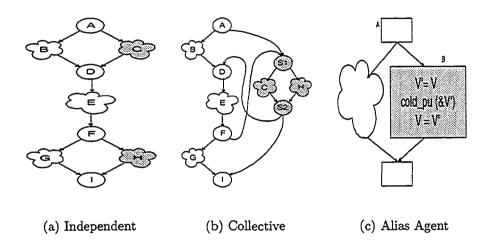

- In our function outlining work, we propose a region formation algorithm based on an abstract syntax tree. Our region formation algorithm efficiently exploits high-level control flow structures, and their associated feedback information, to identify candidate regions for outlining. We formulate the *Optimal Outlining Problem* and argue that it is NP-hard. Then we devise an effective heuristic to analyze the benefits of outlining a region. This heuristic decision weighs the benefit of reducing the host function size against the execution frequency of the extra function calls introduced. We describe how to patch the control flow and the data flow to preserve the program semantics in outlining. Because outlining is an early code transformation, it may negatively impact existing downstream optimizations. Our experiments show that complex alias relationships

created by outlining parameters have a major impact on downstream optimizations and may result in the introduction of substantial memory spills. To handle this problem, we propose a novel technique, called *alias agent*, to disambiguate parameters created to pass references to outlined functions. Finally, we study two orthogonal function splitting strategies: (1) *collective* versus *independent* splitting; and (2) splitting with versus without alias agent. This study shows that selecting the correct strategy is crucial. Independent splitting with alias agent reduces function sizes significantly while minimizing the performance penalty of outlining. Based on our function outlining work, we report the performance results of partial inlining.

• We build Forma, a practical data outlining (or data reshaping) framework that can be used to automatically analyze and transform C/C++ programs. Forma consists of a data shape analysis, including both alias analysis and data type analysis, structure partition planing and array reshaping transformations. Forma has been integrated into the IBM XL C/C++ V7.0 compiler. We also conduct an empirical study of two orthogonal reshaping decisions: frequency-based object partition × affinity-based object partition × maximum object partition; and address-arithmetic-based × pointer-based array splitting. Some important, but subtle, insights on data reshaping are exposed by a thorough analysis and empirical study. We found that data reshaping could improve performance significantly. Experimental results also suggest that the combination of address-arithmetic-based array splitting and the seemingly naive maximal object splitting achieves the best or close-to-best performance on the studied benchmarks.

## 1.3 Dissertation Organization

Both function outlining and data outlining are inter-procedural optimizations that require runtime profiling information to estimate optimization benefits. Therefore, as a background introduction, Chapter 2 describes important concepts that are directly relevant to this thesis. We first introduce interprocedural optimization (IPO) and profiling-guided optimization. Then we use the Open Research Compiler (ORC) as an example to demonstrate how a compiler's behavior changes when IPO is involved. Chapter 3 investigates the inlining trade-offs and identifies the partial inlining opportunities in the SPEC INT2000 benchmarks. Chapter 4 proposes function outlining and discusses its design and implementation. We also report our results of partial inlining in Chapter 4. Chapter 5 handles the data layout problem and presents *Forma*, a data outlining framework that is safe and automatic. We conclude this dissertation in Chapter 6 by summarizing our contributions and by presenting some extension opportunities.

## Chapter 2

## Background

This section introduces the background for this dissertation. The research in this dissertation consists of two inter-procedural optimizations (IPO): function outlining and data outlining. Both of them require inter-procedural analysis (IPA) and runtime feedback information. Therefore, in this section we discuss inter-procedural optimizations and profiling-guided compiler optimizations. We use the Open Research Compiler (ORC) [1], one of our research platforms, as an example to demonstrate how a compiler's behavior changes when IPO is involved.

## 2.1 Inter-Procedural Optimization (IPO)

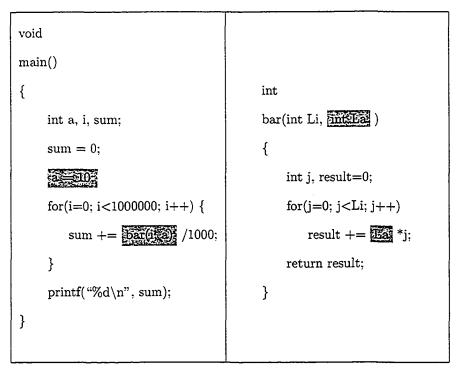

The placement of related program segments into separate procedures hides useful information, limits the scope of compiler analysis, and prevents the aggressive application of compiler optimizations. Classic optimizations, such as common sub-expression elimination, constant propagation, alias analysis, code scheduling, and register allocation, cannot be easily applied across procedure boundaries. In an intra-procedure compilation framework, the boundaries of procedures are barriers that prevent compiler optimization. In the example shown in Figure 2.1, assume that there is only one place in the entire program that calls **bar**. A compiler that has no cross-boundary information about **main** and **bar** has to conservatively assume that the values of the parameters passed to **bar** are only known at runtime.

However the second parameter to the invocation of bar, variable a in main is a constant that can be propagated from main to bar, as shown in Figure 2.2

After the constant propagation, the second parameter to bar is not needed anymore and can be eliminated. Also, the definition of variable a in main is

Figure 2.1: The procedure barrier against compiler optimization

Figure 2.2: Inter-procedural constant propagation on variable a

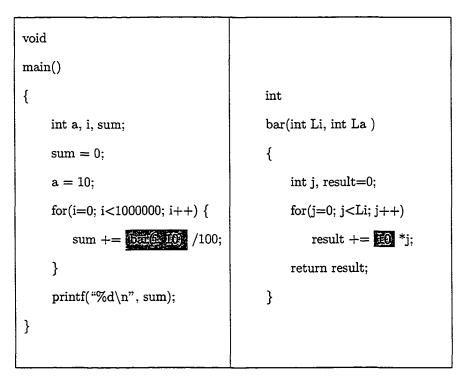

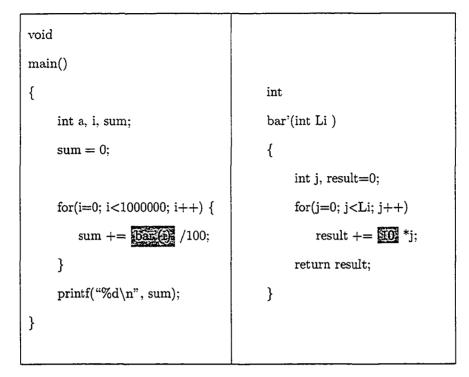

no longer used, and therefore can be eliminated by dead code elimination. These transformations produce the code shown in Figure 2.3. To find these optimization opportunities, a compiler must analyze the data and control flow both in the caller and in the callee.

Figure 2.3: Inter-procedural constant propagation enables function specialization and dead store elimination

Inter-Procedural Optimization (IPO), also called cross-module optimization or whole-program optimization, improves the performance of programs by exploring optimization opportunities across procedure boundaries. By taking advantage of these opportunities, IPO eliminates the performance penalty associated with small program units, and thus enables programmers to take advantage of software modularity. IPO has been implemented in most modern industry-strength compilers and has proved to be a very effective optimization technique. For instance, in the HP-UX 10.20 compiler, Ayers *et al.* demonstrated a performance improvement of 32% for the SPECint95 benchmark on a PA8000-based workstation [7]. Later, they reported that IPO can speed up independent software vendor's applications, with as many as 5 million lines of source code, by as much as 71% [8].

To be employed in commercial compilers, IPO must be carefully designed. First of all, IPO requires that the compiler be able to analyze and optimize code throughout the application. Usually compilers have access to the whole program only during the linking phase, when all the relocatable object files are read and linked together to create an executable file. Thus, inter-procedural optimizations are often implemented in the linker [65, 66]. We call these interprocedural optimizations *link-phase IPOs* or *low-level IPOs*. The input to low-level IPOs consists of relocatable instructions. Implementing IPO in the link phase has two major advantages. First, link-phase IPO has access to the whole application because static library code is available in the link-phase but is not easily available in earlier phases. The second advantage is that link-phase optimizations have access to low-level information. Examples of low-level information includes register usage, register availability, function layout, and procedure sizes. Some low-level IPOs, such as inter-procedural register allocation and code placement, can only be performed in the link phase.

However, important IPOs cannot be applied in the link phase because binary instructions in object files have lost required high-level information. A good example is type and aggregate data construct information that is essential for the efficiency of inter-procedural alias analysis. Another important drawback of low-level IPO is that the link phase takes place at the very end of the compilation process, which means that some optimization opportunities originated by IPO have little chance to be explored. Therefore it is also desirable that some inter-procedural optimizations be performed on higher level language representations of the program. We call these inter-procedural optimizations *high-level IPOs*.

A high-level IPO method consists of introducing a fake linker early in the compilation. This fake link phase reads and analyzes all the available source code. However, instead of relocatable binaries, the input and output of the fake linker are both high-level intermediate representations. Hence, after the fake high-level IPO, other classic optimization techniques can be applied efficiently on the high-level intermediate representation.

Many modern compilers, including the MIPSPro compiler [48], the Open Research Compiler, the HP-UX compiler [8], and the IBM XL compiler [24], implement high-level IPO with a fake linking phase.

#### 2.1.1 Tractable IPO

An obstacle to IPO is that, when applied to large applications, it might result in excessive compilation time and excessive memory space requirements for the compiler. Earlier IPO experiences suggest that a naive IPO design cannot be used for large applications. For example, the IPO-enabled compiler in HP-UX9.0 requires, on average, 1.7KB of memory for each line of source code [8], which makes even the compilation of some moderate-sized benchmarks very memory-demanding and time-consuming. The problem is even worse for commercial software with millions of lines of source code. There are several ways to address the IPO scalability issue. First, the data structures in the compiler must be carefully designed. Complex data management techniques might be employed to schedule the loading of information into memory when it is needed and swapping it out to external storage or discard it according to its expected future use. Second, IPO can be selectively applied to the most important units of the program. The 80-20 rule predicts that usually only a very small portion (20%) of the code consumes most of the execution time (80%) [15]. Thus the compiler should focus its optimization efforts on the most executed program units, which consist of only a small portion of the whole application. The selection of the optimization target can be guided by programmer intervention or by profiling information.

### 2.2 Profiling-guided IPO

Whole program analysis and optimization is often impractical because of its excessive time and memory requirements. Given the large variance in the potential benefit of analyzing and optimizing each call site, IPO must optimize call sites selectively. IPO may increase the size of some procedures through inlining or code duplication and cause longer compilation times. In some cases, IPO may even produce slower programs because of unexpected adverse effects in instruction caches and register usage. Thus, compilers must select call sites that are amenable to inter-procedural optimization. This selection is often informed by profiling information.

Profiling-guided compilation requires more than one compilation and execution of the application before the final executable code is generated. The simplest profiling-guided compilation requires three steps: two rounds of compilation and one round of execution taking place between the compilations. First, the compiler inserts counters to collect run-time statistics. These counters may be inserted either in the original source code or in an intermediate representation of the program. Runtime statistics collected include call site frequencies, the frequency in which each branch is taken or not taken, the number of iterations executed by each loop, and so on. We call this phase the instrumentation phase. The second phase is the instrumented execu*tion* of the instrumented program with a training data input. The counters inserted in the code collect runtime statistics and save these statistics in a formatted file that can be interpreted by a later compilation. Finally, the runtime statistics gathered during the instrumented execution are used to guide the second compilation. The action of associating the source code, or the intermediate representation, with its respective frequency information is called annotation.

Feedback information is beneficial for optimization when the training data set is representative of typical input data sets. However, profiling-guided compilation comes at a cost. The need for preliminary compilation and for a training execution is inconvenient and time-consuming. Often, the instrumented program needs much more time to compile and to execute. Experiments show that instrumented programs slow down by 30-1,000% when compared with their non-instrumented versions [5, 14, 17, 20, 34]. Thus, efficient profiling has concerned several researchers [6, 11, 13]. An alternative to instrumentation and feedback information is to use an estimation of the execution frequency distribution in an application through static program analysis [12, 19, 29, 40, 90, 97].

Another drawback of profiling-based optimization is that its effectiveness depends on the training input set. The training input must be representative of the actual input at runtime to generate appropriate feedback information. However, research shows that the representativeness is not a big problem in real profiling-based optimizations [32, 90]. Our work is based on profiling information.

### 2.3 IPO Case Study

In this dissertation, function outlining is conducted using the Open Research Compiler (ORC) and data outlining is conducted using the Toronto Portable Optimizer (TPO). Both compilers handle IPO in a similar fashion. We will use ORC as an example to show how IPO-involved compilation is different from compilation without IPO. ORC is an open-source compiler that is adapted from the SGI MIPSPro compiler. ORC generates executables for Itanium Processor Family (IPF) processors. ORC inherits from the MIPSPro compiler a mature compilation infrastructure, a rich optimization set including IPO, and complete program analysis support. This excellent pedigree makes ORC a very good platform for experimenting with novel research ideas.

#### 2.3.1 ORC without IPO

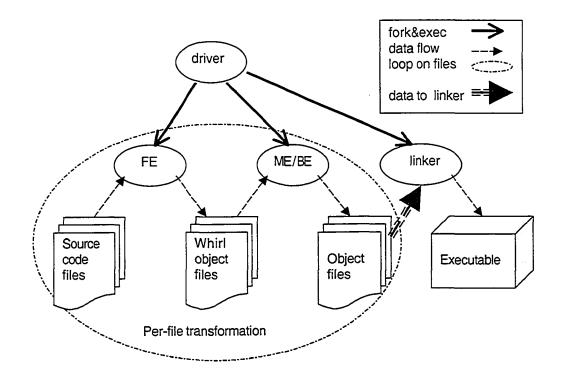

When IPO is not invoked, ORC works like a traditional compiler as shown in Figure 2.4. ORC transforms source code into executable in two phases. The first phase, shown inside the dotted ellipse in Figure 2.4, is the modular compilation of each source code file to generate a corresponding object code files. The second phase is the linking of the object files into the final executable.

During the first phase, each source code file is first translated by the compiler *front-end* (FE) into its intermediate representation called WHIRL (Winning Hierarchical Intermediate Representation Language). The WHIRL object file is then transformed by the compiler *middle-end* (ME) and *back-end*(BE) into a relocatable object file. The WHIRL transformation iterates on all the program units (PUs) in a source code file.

Figure 2.4: ORC compilation without IPO

#### WHIRL Transformation Levels

The compiler gradually translates the source code from high-level language constructs to low-level machine instructions. As more and more optimization techniques are added into ORC, the robustness and maintainability of the compiler itself becomes an important concern. To address this issue, the WHIRL transformation is further divided into several phases, resulting in several WHIRL levels. The higher the WHIRL level, the closer the WHIRL representation is to the original source code. When the program is transformed from the very high-level WHIRL to the very low-level WHIRL, the hierarchical constructs from the high-level programming language are gradually *lowered* to flat instruction-like constructs.

Optimizations have to be orchestrated carefully so that they take place at the proper WHIRL levels. There might be several reasons for some optimizations to occur at higher levels of WHIRL representation. First, at the higher levels, the compiler can access more accurate information, such as control flow constructs and complex data types, from the original program. For example, some programming language operations are represented by a single high-level WHIRL statement. Thus, it is easy to find redundant operations by testing if the operator and the operands are the same or not. However, once these highlevel constructs are lowered to several low-level WHIRL statements, it is more difficult to detect the redundant operations. Moreover, high-level transformations are more efficient and easier to implement because a high-level WHIRL representation typically contains fewer, but more expressive, statements.

On the other hand, some optimizations can only take place on a lowlevel intermediate representation. For example, register allocation has to be conducted at the end of the compilation because only at that time can the compiler access all the variables, including the original variables in the program and the temporary variables generated by earlier compiler transformations.

Some optimizations, such as dead store elimination and copy propagation, need to be repeated several times throughout the compilation. One reason is that the opportunities for these optimizations appear after other transformations are performed. Moreover, these optimizations, in turn, might enable further optimizations. Another important reason to perform some optimizations multiple times is that, when applied early, they help make the WHIRL representation more concise and more tractable for downstream transformations.

#### Middle-end and Back-end Optimizations

A large repertoire of code optimizations takes place along with WHIRL transformations. Some of these optimizations are machine-independent while others are very sensitive to the low-level micro-architectural organization. Machineindependent optimizations usually take place before machine-dependent ones. Thus WHIRL transformations are also divided into two phases. The earlier phase is formed by the machine-independent *middle-end* optimizations. Middle-end optimizations include the incremental *lowering* of the intermediate representation of the program, the high-level loop optimizations, and other traditional optimizations. The later phase performs the *back-end* optimizations, which are machine-dependent. Back-end optimizations include register allocation, code scheduling, *etc*.

#### 2.3.2 ORC with IPO

ORC implements a complete IPO facility. Figure 2.5 shows the compilation process in ORC when IPO is invoked. IPO creates opportunities for other middle-end and back-end code optimizations. Therefore IPO must be performed before such optimizations.

Source-code files are fed into the front-end for the generation of intermediate representation in the form of WHIRL-object files. Then Inter-Procedural Lowering  $(IPL)^1$  reads the WHIRL object files and the feedback information, analyzes them one-by-one, and writes the frequencies, estimated size, and estimated number of cycles executed in each procedure into the original WHIRL

<sup>&</sup>lt;sup>1</sup>IPL is a preparation phase for IPO. Probably ORC uses this term for historical reasons.

Figure 2.5: IPO-involved ORC compilation

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

objects into files. IPO takes these annotated intermediate representations as input to inlining and other inter-procedural optimizations. After IPO, the procedures are fed to the traditional optimizer to generate relocatable objects. Finally, the linker is invoked to generate the executable.

From Figure 2.5, we can see that, compared with the front-end, with the back-end, and with the IPL, the operation of IPO is more similar to a linker. The IPO reads all the available WHIRL object files and analyzes them together. This is necessary to enable the compiler to access the whole application instead of a single procedure or source file. By analyzing the information about all the source files, the compiler can perform inlining across the boundaries of different source files. This wider scope for optimization is important for performance because closely-related callers and callees do not always reside in the same source file.

## Chapter 3

## Inlining Tuning

### 3.1 Introduction

Function inlining is a very important optimization technique that replaces a function call with the body of the function [7, 22, 25, 26, 27, 30, 47, 59, 87]. One advantage of inlining is that it eliminates the overhead resulting from a function call. The savings are especially pronounced for applications where only a few call sites are responsible for the bulk of the run-time function invocations; inlining those call sites significantly reduces the function invocation overhead. For example, mcf (one of the SPEC2000 benchmarks) contains 34 call sites. Among these call sites, there are 5 that are executed more than 10 million times and 4 call sites that are executed more than 1 million times in a standard SPEC2000 training execution. These 9 call sites account for 99.85% of all the function invocations in mcf. Our experiments show that inlining the 15 most frequent call sites can reduce the running time of mcf by more than 9%.

Inlining also expands the context of static analysis. This wider-scoped analysis creates opportunities for other optimizations. Because the body of the callee is now available at the call site, conservative assumptions that the compiler would previously make about the call site are no longer required.

Another advantage of inlining is the improvement of cache efficiency. From the point of view of the data cache (D-cache), after inlining there is no need to create parameters to pass the caller's variables that are referenced by the callee. Thus, a variable that previously had separate representations in the caller and in the callee can now be reduced to a single memory location or even promoted to a register. This storage consolidation reduces the data access footprint of the application and improves the use of the memory hierarchy. A similar advantage also exists for the instruction cache (I-cache). After inlining, closely related segments of code are placed together, reducing the chances of instruction cache conflicts [72].

However, inlining can have negative effects. One problem with inlining is the growth of the code, also known as *code bloat*. Because a procedure may be called from multiple call sites, it is often not possible to eliminate a procedure after inlining a single call site. Thus, the final executable file must contain several copies of the procedure: the original one and the inlined copies. With the growth of functions because of inlining, the compilation time and the compiler memory space requirement may become intolerable because some of the algorithms used for static analysis have super-linear complexity.

Besides of the compilation time and memory resource cost, inlining might also have the adverse effect of increasing the execution time of the application. After inlining, the register pressure may become a limitation because the caller now contains more code, more variables, and more intermediate values. This additional storage requirement may not fit in the register set available in the machine. Thus, if the register allocator cannot do a good job, inlining may increase the number of register spills resulting in a larger number of load and store instructions executed at runtime.

The above discussion of the benefits and drawbacks of inlining leads to an intuitive criterion to decide which call sites are good candidates for profitable inlining. The value of the benefits of inlining, such as eliminating function-call overhead, enabling more optimization opportunities, and improving cache efficiency, depend on the execution frequency of the call site. The more frequently a call site is invoked, the more promising is the inlining of the site. If the call site is invoked only a couple of hundred times in a long execution, inlining it is unlikely to produce any improvement.

On the other hand, the negative effects of inlining relate to the size of the caller and the size of the callee. Larger functions tend to have worse cache behavior and higher register pressure. Inlining large callees results in more serious code bloat, and, probably, performance degradation due to additional *memory spills.*<sup>1</sup>

Thus, we have two basic guidelines for inlining. First, the call site must be very frequent, and, second, neither the callee nor the caller should be too large. Most of the papers that address inlining take these two factors into consideration in their inlining analysis.

In this chapter we describe our experience in tuning the inlining heuristics for the Open Research Compiler (ORC). The main contributions of this chapter are:

<sup>1</sup>A memory spill occurs when the register allocation algorithm is not able to fit all live values into registers. In this case, some values must be written temporarily (*spilled*) to memory.

- We propose *adaptive inlining* to enable aggressive inlining for small benchmarks. Usually, small benchmarks are amenable to aggressive inlining as shown in Section 3.4. Adaptive inlining becomes conservative for large benchmarks such as gcc because the negative effects of aggressive inlining are often more pronounced in such benchmarks.

- We introduce the concept of *cycle\_density* to control code bloat and compilation-time increase.

- Our detailed experimental results show the potential of inlining. We investigate the impediments to beneficial inlining and motivate function outlining and partial inlining.

The rest of this chapter is organized as follows: Section 3.2 describes the existing inlining analysis in ORC and its limitations. Section 3.3 describes our enhancements to the inlining analysis (adaptive inlining and *cycle\_density* heuristics) and Section 3.4 studies performance, finds the impediments for inlining frequent call sites, and motivates function outlining and partial inlining. Section 3.5 reviews related work. The findings presented in this chapter were published in [99].

## 3.2 Overview of ORC Inlining

To control the negative effects of inlining, we should inline selectively. How do we determine whether a call site is suitable for inlining? The performance effect of inlining an edge of the call graph depends on two factors: the execution frequency of the site and the size of the callee. The problem of selecting the most beneficial call sites while satisfying the code bloat constraints can be mapped to the *knapsack* problem, which has been shown to be NP-complete [37, 79]. Thus, heuristics are often used to estimate the gains and the costs of each potential inlining. ORC uses profiling information to calculate the *temperature* of a call site to approximate the potential benefit of inlining an edge  $E_i(p,q)$ that represents a call site in a function p that calls a function q.<sup>2</sup>

$$temperature_{E_i(p,q)} = \frac{cycle\_ratio_{E_i(p,q)}}{size\_ratio_q}$$

(3.1)

where:

$$cycle\_ratio_{E_i(p,q)} = \frac{freq_{E_i(p,q)}}{freq_q} \times \frac{cycle\_count_q}{Total\_cycle\_count}$$

(3.2)

<sup>&</sup>lt;sup>2</sup>Because function p may call q at different call sites, the pair (p,q) does not define an unique call site. Thus, we add the subscript i to uniquely identify the  $i^{th}$  call site from p to q.

$$size_ratio_q = \frac{size_q}{Total\_application\_size}$$

(3.3)

where  $freq_{E_i(p,q)}$  is the frequency of the edge  $E_i(p,q)$ ;  $freq_q$  is the overall execution frequency of function q in the training execution;  $Total_application_size$  is the estimated size of the application which is the sum of the estimated sizes of all its functions;  $size_q$  is the estimated size of the function q.

Total\_cycle\_count is the estimated total execution time of the application:

$$Total\_cycle\_count = \sum_{k \in PUset} cycle\_count_k$$

(3.4)

where PUset is the set of all program units (*i.e.* functions) in the program,  $cycle\_count_k$  is the estimated number of cycles spent on function k.

$$cycle\_count_k = \sum_{i \in stmts_k} freq_i$$

(3.5)

where  $stmts_k$  is the set of all statements of function k,  $freq_i$  is the frequency of execution of statement i in the training run.

The overall frequency of execution of the callee q is computed by:

$$freq_q = \sum_{k \in callers_q} freq_{E_i(k,q)}$$

(3.6)

where  $callers_q$  is the set of all functions that contain a call to q.

Essentially, cycle\_ratio is the contribution of a call graph edge to the execution time of the whole application. A function's cycle count is the execution time spent in that function, including all its invocations.  $(\frac{freq_{E_i}(p,q)}{freq_q} * cycle\_count_q)$  is the number of cycles contributed by the callee q invoked by the edge  $E_i(p,q)$ . Thus,  $cycle\_ratio_{E_i(p,q)}$  is the contribution of the cycles resulting from the call site  $E_i(p,q)$  to the application's total cycle count. The larger the  $cycle\_ratio_{E_i(p,q)}$  is, the more important the call graph edge.

The estimated size of the function q,  $size_q$ , is computed by:

$$size_q = 5 * BB\_count_q + STMT\_count_q + CALL\_count_q$$

(3.7)

where  $BB\_count_q$  is the number of basic blocks<sup>3</sup> in function q and reflects the complexity of the control flow in the PU,  $STMT\_count_q$  is the number of statements in q, excluding labels, parameters, and pragmas.  $CALL\_count_q$  is the number of call sites in q.

The  $size_ratio_q$  is the callee q's contribution to the whole application's size.

$<sup>^{3}</sup>$ A basic block is a straight-line piece of code which contains neither branch instructions nor branch targets in the middle.

Finally, the *Total\_application\_size* is given by:

$$Total\_application\_size = \sum_{k \in PUset} size_k$$

(3.8)

The intuition for the temperature heuristic is that edges with high temperature are call-sites that are invoked frequently and whose callee is small compared to the entire application. With careful selection of a threshold on temperature, ORC can find cycle-heavy calling edges whose callee is small compared to the whole application.

Figure 3.1 shows the distribution of the temperature for the bzip2 benchmark.<sup>4</sup> The horizontal axis shows the calling frequency and the vertical axis the temperature. Each dot in the graph represents an edge in the call graph. The temperature varies in a wide range: from 0 to 3000. The calling frequency is shown in reverse order, the most frequently called edges appear on the left side of the graph and the least-frequently-called edges are toward the right side. From left to right, the temperature decreases as the frequency of the call sites also decreases. It is reasonable that the temperature does not go straight down because besides the call-site frequency, the temperature heuristic also takes the callee's size into consideration. Procedure size negatively influences the temperature. Thus, frequently invoked call sites might be "cold" simply because they are too large.

Figure 3.1: Temperature distribution of bzip2

In the original ORC inlining heuristic, a call site is rejected for inlining if its temperature is less than a specified threshold. However, this temperature heuristic may lead to the inlining of edges with high temperature but very low frequency. For instance, we highlighted two clusters of edges in the

$<sup>^{4}</sup>$ To make it easy to read, the two axes of the graphs are drawn using a log scale. Thus some call sites whose frequencies or temperatures are 0 are not shown in the graph. The same situation exists in Figure 3.3.

Figure 3.2: Frequency accumulation of gcc (the top 2,750 of all 19,000 call sites are plotted)

temperature×frequency graph for bzip2 in Figure 3.1. The cluster on the right side of the graph has higher temperature but much lower frequency than the cluster on the left side of the graph. Inlining infrequently invoked call sites should always be avoided because it does not help performance. To improve this heuristic, we created a new mechanism to cooperate with the temperature heuristic to prevent the inlining of hot but infrequently invoked call sites. We describe our solution in Section 3.3.

### 3.3 Inlining Tuning

We improve the inlining heuristics of ORC in two ways. First, adaptive inlining is employed to make the inlining heuristics more flexible. Second, a new *cycle\_density* heuristic is introduced to restrict the inlining of hot but infrequent procedures.

### 3.3.1 Adaptive Inlining

The original inlining heuristic in ORC used a fixed-temperature threshold (120) for inlining decisions. This threshold was chosen as a trade-off among compilation time, executable size, and performance results for different benchmarks. However, a fixed threshold turns out to be inflexible for applications with very different characteristics. For example, a high threshold (*e.g.* 120) is reasonable for large benchmarks because they are more vulnerable to the negative effects of code size increase resulting from inlining. However, the same

threshold might not be good for small applications such as mcf, bzip2, and gzip. We will use gcc, which is a typical large application, and bzip2, which is a representative small application, to illustrate this problem.

Figure 3.2 shows the frequency accumulation for the gcc benchmark and Figure 3.3 shows its temperature distribution. In Figure 3.2, the X-axis represents the call sites sorted by invocation frequency from high to low. The  $i^{th}$  point numbered from left to right in the figure represents the accumulated percentage of the *i* most frequent call sites.

gcc has a complex function call hierarchy and the function invocations are distributed amongst a large number of call sites: there are more than 19,000 call sites in gcc. In the standard SPEC2000 training execution of gcc, there are more than 42,000,000 function invocations, and the most frequent call site is called no more than 800,000 times. Figure 3.2 shows that the top 10% (about 2,000) most frequently invoked call sites account for more than 95% of all the function calls. Inlining these 2,000 call sites would result in unbearable compilation cost and substantial code bloat.

In Figure 3.3, according to the frequency of execution, we should inline the call sites on the left hand side of the graph and we should avoid inlining the call sites on the right-hand side. Notice that several call sites on the right-hand side are hot, and thus are inlined by the original heuristics of ORC.

For large applications, the improvement from inlining is usually very limited (as we will see in the Section 3.4). On one hand, it is impossible to eliminate most of the function overheads without wholesale inlining. On the other hand, if we use the same temperature threshold as for small benchmarks, we might end up with the problem of *over-inlining*, *i.e.* too many procedures are inlined and the negative effects of inlining are more pronounced than the positive ones. For example, if the temperature threshold is set to 1, there will be more than 1,700 call sites inlined in gcc. Such aggressive inlining makes the compilation time much longer without performance improvement as our experiments show.

The high temperature threshold (120) in the original ORC was chosen to avoid over-inlining in large applications. However, this conservative strategy impedes aggressive inlining for small benchmarks where code bloat is not as prominent. For instance, Figure 3.1 and Figure 3.4 show the temperature distribution and frequency accumulation of the bzip2 benchmark. There are only 239 call sites and about 3,900 lines of C code in bzip2. This implies that the program is quite small when compared with more than 19,000 call sites and 190,000 lines of C code in the gcc benchmark. Moreover, in bzip2 the top ten most frequently invoked call sites, which comprise about 4.2% of the total number of call sites, accounts for nearly 97% of all the function calls shown in Figure 3.4.

As we will see in the Section 3.4, aggressive inlining is good for small benchmarks such as bzip2. Inlining the 10 most frequently invoked call sites

Figure 3.3: Temperature distribution of gcc

in bzip2 eliminates almost all its runtime function calls.

However, the inflexible temperature threshold often prevents the inlining of the most frequent call sites because their temperatures are lower than the fixed threshold (120). Thus, it is desirable that the temperature threshold for small benchmarks be lowered because many of the call sites that have performance potential do not reach the conservative temperature threshold used to prevent code bloat in large applications.

The contradiction between the threshold distributions of large benchmarks and small ones naturally motivates adaptive inlining: we use a high temperature threshold for large applications because they tend to have many hot call sites; and we enable more aggressive inlining for small applications by lowering the temperature threshold for them.

Adapting the inlining temperature threshold according to application size is pretty simple in ORC. Because the estimated size of each procedure in ORC is available in the IPO phase, their sum is the estimated size of the application.<sup>5</sup> We classify applications into three categories: large applications, medium applications and small applications. In the compilation, we utilize proper temperature threshold according to the estimated application size. If an application is a large application, its temperature threshold is 120. If it is a medium application, its temperature threshold is 50. Otherwise, the temperature threshold is lowered to 1. The threshold values were obtained by a detailed empirical study of the SPEC2000 benchmarks. This division of applications into three categories produces better results than any single threshold applied to all benchmarks.

<sup>&</sup>lt;sup>5</sup>We ignore library functions and dynamic shared-objects because we cannot acquire this information at compilation time.

Figure 3.4: Frequency accumulation of bzip2 (the top 38 of all 239 call sites are plotted)

### 3.3.2 Cycle Density

The intuition behind the definition of temperature is that hot procedures should be frequently invoked and not too large. However, as we have seen in Figure 3.3 and Figure 3.1, some of the procedures with high temperature are not actually hot, *i.e.* some infrequently invoked call sites also have high temperatures. These call sites are represented by the points in the top-right part of the graphs and correspond to functions that are not called frequently, but contain high-trip count loops that contribute to their high *cycle\_ratio*, which results in a high temperature (see Equation 3.2). We call the functions that are called infrequently but have high temperatures *heavy functions*.

Inlining heavy functions results in little performance improvement. First, very few runtime function calls are eliminated. Second, the path from the caller to a heavy function is not a hot path at all, and thus will not benefit from post-inlining optimization. Third, inlining heavy functions might prevent frequent edges from being inlined if the code growth budget is spent. To handle this problem, we introduce *cycle\_density* to filter out heavy functions.

$$cycle\_density_q = \frac{cycle\_count_q}{frequency_q}$$

(3.9)

where  $cycle\_count_q$  is the number of cycles spent on procedure q and  $frequency_q$  is the number of times that the procedure q is invoked.

When a call site fulfills the temperature threshold, the *cycle\_density* of the callee is computed. If the callee has a large cycle count but small frequency, *i.e.* its *cycle\_density* is high, it must contain loops with a high trip count. These heavy procedures are not inlined. *cycle\_density* has little impact on the performance because it only filters out infrequent call sites. However,

using *cycle\_density* as a filter can significantly reduce the compilation time and executable sizes, which is important in some application contexts, such as embedded computing.

Figure 3.5: Cycle density vs. temperature (bzip2)

Figure 3.5 compares the temperature against the *cycle\_density* for each call site in bzip2. For call sites that are actually hot, the temperature is indeed high while the *cycle\_density* is low (for bzip2 they are always less than 0.5). These call sites are the ones that will benefit from inlining.

Infrequently-invoked call sites fall into two categories according to their temperatures. Infrequently-invoked call sites with low temperature are eliminated by the temperature threshold. Infrequently-invoked call sites with high temperature always have very high *cycle\_density*. Thus we can prevent the inlining of these sites by choosing a proper *cycle\_density* threshold. In our tuning, we use a fixed *cycle\_density* threshold of 10 that works well for the SPEC2000 benchmarks as we will see in the next section.

We implemented this enhanced inlining decision criteria and contributed it to the ORC-2.0 release. Figure 3.6 shows the C-style pseudo code for the improved inlining analysis in the ORC. Notice that a procedure that has a single call site in the entire application will always be inlined. The reasoning is that the inlining of that single call site will render the callee dead, and will allow the elimination of the callee. Therefore this inlining will save function invocations without causing code growth.

Figure 3.6: Adaptive inlining in ORC

# 3.4 Results

# 3.4.1 Experimental Environment

We investigate the effects of adaptive inlining and of the introduction of the *cycle\_density* heuristic on performance, compilation time, and the final executable size of SPEC INT2000 benchmarks. We use a cross-compilation method: we run ORC on an IA32 machine (an SMP machine with 2 Pentium-III 600MHz processors and 512MB memory) to generate an IA64 executable which is run on an Itanium machine (733MHz Itanium-I processor, 1GB memory). Thus our performance comparison is conducted on the IA64 systems and

our compilation time comparison is conducted on the IA32 system.

# 3.4.2 Performance Analysis

Figure 3.7: Overall performance comparison

Figure 3.7 shows the performance improvement when different inlining strategies are used. T120 represents a fixed temperature threshold of 120, T1 is a fixed temperature threshold of 1, similarly for the other T labels. In adaptive the temperature threshold varies according to the *adaptation* heuristic described in Section 3.2. In the adaptive+density compiler both the adaptation and the *cycle\_density* heuristics are used.

Except for perlbmk, in all benchmarks the adaptation heuristic results in positive speedup for inlining. These results suggest that our adaptive temperature threshold is properly selected. In some cases the difference between a fixed threshold and the threshold chosen with adaptation is very significant (see bzip2 and twolf). Note also that the addition of *cycle\_density* to adaptation does not produce much effect on performance. This result is explained by the fact that *cycle\_density* only prevents heavy and infrequently invoked functions from inlining.

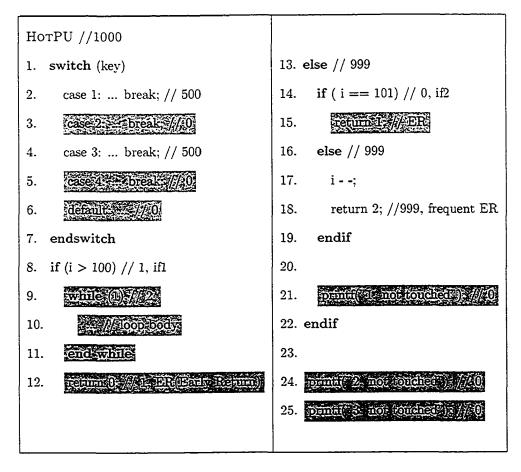

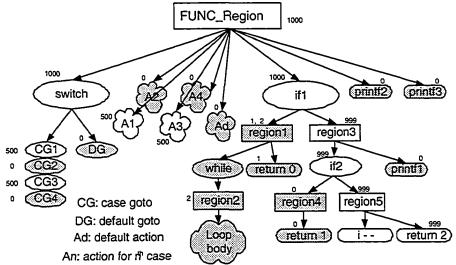

We arranged the benchmarks in Figure 3.7 according to their sizes with the smaller benchmarks on the left and the larger ones on the right. Comparatively, in general, inlining yields better speedups for small benchmarks than for large benchmarks. This observation can be made by examining the maximum performance improvement from all the strategies. Excluding twolf and vortex, the maximum performance improvement decreases from left to right (from small benchmark to large benchmarks). This trend suggests a loose correlation between the application size and potential performance improvements that can be obtained from inlining.

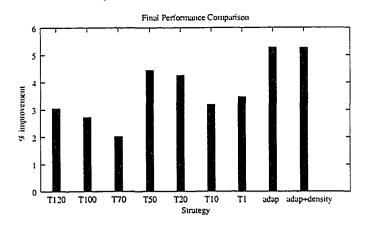

Figure 3.8: Final performance comparison

Figure 3.8 compares the performance improvements of different strategies more explicitly. We first calculate the performance speedup for each benchmark. The baseline is the performance of the 11 benchmarks compiled without inlining. Each bar in Figure 3.8 represents the arithmetic average performance speedup for the 11 benchmarks studied. Finally, the two rightmost bars are for adaptive inlining without and with *cycle\_density* heuristics. The adaptive inlining strategy speeds up the benchmarks by 5.28%, while the best average performance gain of all other strategies is 4.45% when the temperature threshold is 50. Notice also that the performance influence of *cycle\_density* heuristics is negligible.

## 3.4.3 Compilation Time and Executable Size Analysis

In this section, we study the effect of the *cycle\_density* heuristics on the compilation time and on the executable size. Because *cycle\_density* filters procedures that have high temperatures but are infrequently invoked call sites, we expected that their use should reduce both the compilation time and the final executable size.

Table 3.1 shows some statistics collected from different optimization configurations. In the table, "N" means no inlining is used, "A" means adaptive inlining is used and "A-D" means using adaptive inlining plus *cycle\_density*. The table first shows the executable size, measured in bytes, and the compilation time, measured in seconds, for all benchmarks when no inlining is performed. Then for the compiler with adaptive inlining and the compiler with adaptive inlining plus *cycle\_density*, the table displays the percentage increase in the executable size and compilation time. The table also shows, under the "calls" columns, the number of call sites that were inlined in each

|         |         | Compi                                      | ompilation Time |          |         |         |       |      |

|---------|---------|--------------------------------------------|-----------------|----------|---------|---------|-------|------|

| Program | Ν       | А                                          |                 | A-       | D       | Ν       | А     | A-D  |

|         | (Bytes) | $(8) \ \% \ inc \ call \ \% \ inc \ calls$ |                 | (Secs)   | %inc    | %inc    |       |      |

| bzip2   | 116295  | 54.1                                       | 89              | 26.9     | 88      | 70.356  | 117.8 | 71.3 |

| gcc     | 4397983 | 4.4                                        | 919             | 4.4 919  |         | 4194.54 | 6.0   | 4.0  |

| crafty  | 635855  | 20.1                                       | 204             | 20.1 204 |         | 440.687 | 30.9  | 30.9 |

| gap     | 1977644 | 9.7                                        | 345             | 7.3      | 7.3 343 |         | 9.1   | 2.7  |

| gzip    | 147417  | 67.6                                       | 62              | 28.0     | 54      | 109.457 | 93.8  | 41.2 |

| mcf     | 48241   | -0.5                                       | 19              | -6.3     | 17      | 41.832  | 9.3   | 8.5  |

| parser  | 340223  | 18.1                                       | 239             | 16.4     | 224     | 274.868 | 17.1  | 12.9 |

| perlbmk | 2163047 | 7.5                                        | 419             | 7.5      | 419     | 1518.37 | 10.6  | 8.9  |

| twolf   | 823832  | 10.6                                       | 147             | 10.6     | 147     | 646.769 | 19.8  | 20.5 |

| vortex  | 1170014 | 31.4                                       | 210             | 31.1     | 208     | 1162.27 | 33.0  | 36.5 |

| vpr     | 532912  | 17.5                                       | 141             | 16.4 139 |         | 293.683 | 30.2  | 26.2 |

| average |         | 21.9                                       |                 | 14.8     |         |         | 34.3  | 24.0 |

Table 3.1: Impact of cycle\_density on executable size and compilation time

case.

The cycle\_density heuristic significantly reduces the code bloat and compilation time problem. On average, adaptive inlining increases the code size by 21.9% and the compilation time by 34.3%. When cycle\_density is used to screen out heavy procedures, these numbers reduce to 14.8% and 24%, respectively. It is also interesting to compare the actual number of inlined call sites: the cycle\_density heuristic only eliminates a few call sites. Except for gzip and parser, cycle\_density prevents the inlining of no more than 2 call sites in each benchmark. Table 3.1 also shows some curious results. Although cycle\_density prevents the inlining of a single call site for bzip2, the code growth reduces from 54.1% to 26.9%. A close examination of bzip2 reveals that the procedure doReversibleTransformation calls sortIt infrequently (only 22 times in the standard training run). However ORC performs a bottom-up inlining, in which the edges in the bottom of the call graph are analyzed and inlined first. In the bzip2 case, sortIt absorbs many functions and becomes very large and *heavy* before it is analyzed as the callee. When ORC analyzes the sites that call sortIt, the estimated cycle number spent in sortIt is huge, which contributes to its high temperature. However, sortIt is called infrequently and its inlining does not produce measurable performance benefits.  $cycle_density$  filters these heavy functions successfully.

Finally, *cycle\_density* only eliminates a few call sites because it is not applied to callees that are only called at one call site in the entire application (see Figure 3.6).

## 3.4.4 Motivation for Partial Inlining

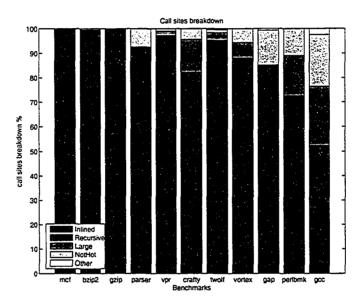

Figure 3.9: Call sites breakdown

Figure 3.9 shows how many dynamic function calls can be eliminated using our adaptive inlining technique. We divided the function calls into five different categories:

- Inlined Call sites that can be inlined with our adaptive inlining technique. These call sites have high temperature and low cycle\_density.

- NotHot Call sites that are not frequently invoked. It brings no benefit to inline these call sites.

**Recursive** ORC does not inline call sites that are in a cycle in the call graph.

- Large Call sites that have high temperature but cannot be inlined because either the callee, the caller or its combination is too large. gcc, perlbmk, crafty and gap have some large call sites.

- Other Call sites that cannot be inlined due to other reasons. For example, the actual parameters to the call sites do not match the formal parameters of the callee. As Figure 3.9 shows, these call sites are very rare.

With our enhanced inlining framework, we were able to eliminate most of the dynamic function calls for small benchmarks such as mcf, bzip2, and gzip. However, we only eliminated about 30% dynamic function invocations for gcc and 57% for perlbmk. Examining the graph in Figure 3.9, to obtain further benefits from inlining we need to address inlining in these large benchmarks. The categories that are the most promising are the recursive function calls and call sites with large callers or callees.

Figure 3.9 shows that for some large benchmarks (parser, perlbmk, and gcc) a significant portion of the function invocations that are not inlined are recursive functions.

Among the two problems, we are particularly interested in using the idea of code splitting to reduce the sizes of the frequently invoked large functions, which is discussed in Chapter 4.

# 3.5 Related Work

In this chapter we presented improvements to the inlining heuristics in the Open Research Compiler (ORC). Several researchers have investigated inlining. However, very few of them produced a detailed empirical study using an industry-strength compiler infrastructure based on industry-standard benchmarks such as the one that we present in this thesis.

Ayers et al. [7] and Chang et al. [22, 47] studied aggressive inlining and cloning. Their inlining facility is very much like that in ORC: the inlining happens on high-level intermediate representation, using feedback information and cross-module analysis. Both of them use a budget to control code bloat: inlining a call site consumes code-growth budget. Ayers et al. use an estimated 100% compilation-time increase as their budget for inlining. ORC uses an estimated 100% code-size increase for the inlining budget. In our experiments, inlining in ORC never uses up this budget.