## Hardware-Efficient Approximate Arithmetic Circuits for Deep Learning and Other Computation-Intensive Applications

by

Mohammad Saeed Ansari

A thesis submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in

Integrated Circuits and Systems

Department of Electrical and Computer Engineering

University of Alberta

© Mohammad Saeed Ansari, 2019

#### Abstract

Approximate computing (AC) is an emerging paradigm that leverages the inherent error tolerance of many applications—such as image recognition, multimedia processing, and machine learning (ML)—to allow some accuracy to be traded off to save energy consumption. AC techniques can be applied at both the circuit and/or architecture levels, possibly in coordination with software-level techniques.

Multiplication is one of the most resource- and power-hungry operations in many error-tolerant computing applications, such as image processing, neural networks (NN), and digital signal processing (DSP). In this research project, we focus on the design and implementation of hardware-efficient approximate computing circuits, aiming to simplify the multiplication operation and/or to reduce the number of required multiplications.

Two  $4\times4$  approximate multiplier designs are proposed in which approximation is employed in the partial product reduction tree, the most expensive part of the design of a multiplier. The two proposed designs are then used to construct larger approximate multipliers.

Multiplication is the computational bottleneck in NNs. For the first time, we attempt to find the critical features in an approximate multiplier that make it superior to others for use in a NN. Inspired by the insight that adding small amounts of noise can improve the performance of NNs, we replaced the exact multipliers in two representative NNs with 600 approximate multipliers and then experimentally measured the effect on classification accuracy. In-

terestingly, some approximate multipliers improved the performance of NNs. Insight into which features of an approximate multiplier make it superior to others in the NN applications was gained by training a statistical predictor that anticipates how well a given approximate multiplier is likely to work in a NN application.

In the logarithmic number system (LNS) the multiplication operation is converted into simple shift and addition operations. We have proposed a novel exact leading-one detector (LOD) to speed up the calculation of the base-2 logarithm of the input operands to a logarithmic multiplier. In addition, since the logarithmic multipliers that use LODs always underestimate the actual multiplication product, a nearest-one detector (NOD) is proposed for a logarithmic multiplier that has a double-sided error distribution. Additionally, a logarithmic squaring circuit is proposed that uses a linear approximation for calculating the base-2 logarithm of the input operand.

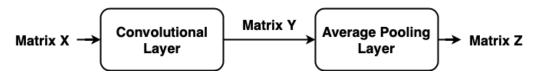

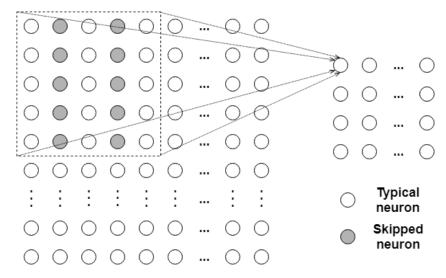

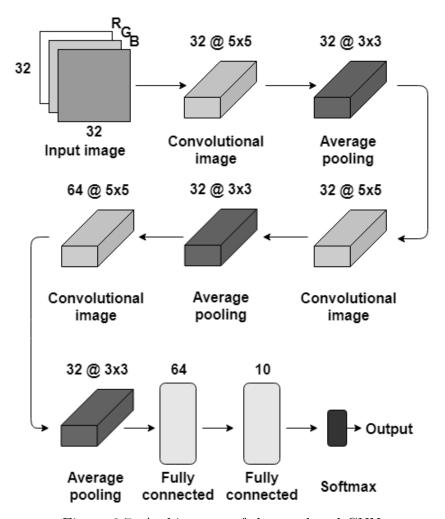

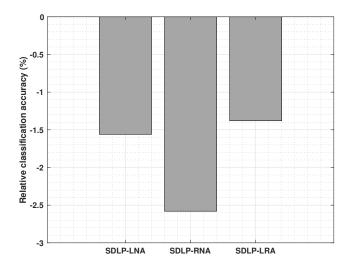

Finally, we investigate the design of multiply-accumulate (MAC) units. An approximate logarithmic MAC (LMAC) unit is proposed for the first time. Furthermore, a soft-dropping low-power (SDLP) architecture is specifically designed for convolutional neural networks (CNNs) that, unlike the existing accelerators that simplify the multiplication/addition operations, reduces the number of required multiplications. The SDLP takes advantage of the spatial dependence between the input image pixels and skips some of the multiplications during the convolution operation and, thereby, reduces the energy consumption of the CNN inference calculation.

#### **Preface**

This dissertation presents the original work in the field of approximate computing (AC) by Mohammad Saeed Ansari.

In Chapter 3, we propose two 4×4 low-power approximate multipliers using encoded partial products and approximate compressors. These two multipliers are then used to build larger multipliers. This work has been published as M. S. Ansari, H. Jiang, B. F. Cockburn, and J. Han, "Low-Power Approximate Multipliers Using Encoded Partial Products and Approximate Compressors," *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, Vol. 8, No. 3. pp. 404-416. I developed the circuit design and H. Jiang provided the hardware description language (HDL) code for some of the existing designs in the literature for comparison purposes. Dr. J. Han and Dr. B. F. Cockburn provided technical suggestions and revised the manuscript.

The use of approximate multipliers in neural networks (NNs) is investigated in Chapter 4, by replacing the exact multipliers in two NN benchmarks and evaluating the resulting NN's classification accuracy. A statistical analysis is then carried out to identify the critical features in an approximate multiplier that tend to improve its performance in NNs. This work has been accepted for publication as M. S. Ansari, V. Mrazek, B. F. Cockburn, L. Sekanina, Z. Vasicek, and J. Han, "Improving the Accuracy and Hardware Efficiency of Neural Networks Using Approximate Multipliers," *IEEE Transactions on Very Large Scale (VLSI) Systems*. I provided the HDL code for some approximate multipliers. V. Mrazek added my codes to his and evaluated the performance of all of the approximate multipliers in two NN benchmarks. Based on his results, I ran some statistical analysis to identify the critical features. Finally, I developed the classifiers that anticipate how well an approximate multiplier

would work in a NN. Drs. B. F. Cockburn, L. Sekanina, Z. Vasicek, and J. Han provided technical suggestions and improved the flow of the manuscript by their comments.

Chapter 5 presents a new leading-one detector (LOD) design, which has been submitted IET Computers and Digital Techniques as M. S. Ansari, S. Gandhi, B. F. Cockburn, and J. Han, "Approximate Leading One Detector Design for a Hardware-Efficient Mitchell Multiplier". I developed the main idea and did the software level simulations and S. Gandhi helped with the HDL coding. Drs. J. Han and B. F. Cockburn provided constructive suggestions on improving the quality of the manuscript. An improved logarithmic multiplier (ILM) is also proposed in this chapter that uses a nearest-one detector instead of the conventional LOD. This work has been submitted to IEEE Transactions on Computers as M. S. Ansari, B. F. Cockburn, and J. Han, "An Improved Logarithmic Multiplier for Energy-Efficient Neural Computing". I developed the main idea and performed the required simulations. Drs. J. Han and B. F. Cockburn contributed by providing technical suggestions that significantly improved the quality of the manuscript. Finally, a low-error squaring function (LESF) is proposed in this chapter. This work has been submitted to IEEE Transactions on Emerging Topics in Computing as M. S. Ansari, B. F. Cockburn, and J. Han, "Low-Power Approximate Logarithmic Squaring Circuit Design for DSP Applications". Drs. Han and Cockburn provided suggestions to the research and helped revising the manuscript.

A logarithmic multiply-accumulate (MAC) unit is proposed in Chapter 6. This work has been submitted to *IEEE Transactions on Very Large Scale* (VLSI) Systems as M. S. Ansari, B. F. Cockburn, and J. Han, "Design of a Fast and Energy-Efficient Approximate Logarithmic Multiply-Accumulate Unit". I developed the idea and ran all the required simulations. Drs. Han and Cockburn provided technical suggestions to improve the quality of the manuscript. A soft-dropping low-power (SDLP) accelerator is also presented for convolutional neural networks (CNNs). This work is drafted as M. S. Ansari, B. F. Cockburn, and J. Han, "Approximate Accelerators for CNN-based Image Classifiers that Rely on Pixel Spatial Dependence". I carried out all of the simu-

lations and Drs. Han and Cockburn provided valuable suggestions to improve the structure as well as the technical content of the manuscript.

## Contents

| 1 | Intr<br>1.1<br>1.2<br>1.3<br>1.4 | Motivation                                                    | 1<br>3<br>4<br>5 |

|---|----------------------------------|---------------------------------------------------------------|------------------|

| 2 |                                  | nputation-Intensive Applications and Approximate Arith-       |                  |

|   |                                  | ic Circuits                                                   | 7                |

|   | 2.1                              | Computation-intensive applications                            | 7                |

|   |                                  | 2.1.1 Image and digital signal processing                     | 7<br>9           |

|   |                                  | 2.1.2 Multiple-input multiple-output (MIMO) systems           | 11               |

|   | 2.2                              | Approximate arithmetic for computation-intensive applications | 15               |

|   |                                  | 2.2.1 Approximate adders                                      | 15               |

|   |                                  | 2.2.2 Approximate multipliers                                 | 16               |

| 3 | Low                              | y-power approximate multipliers using encoded partial prod    |                  |

| J |                                  | s and approximate multipliers using encoded partial prodes    | 21               |

|   | 3.1                              | Proposed Multiplier Designs                                   | $\frac{1}{22}$   |

|   |                                  | 3.1.1 Modified approximate 4:2 compressor                     | 22               |

|   |                                  | 3.1.2 Two approximate $4 \times 4$ multipliers                | 25               |

|   |                                  | 3.1.3 Scaling up to larger multipliers                        | 27               |

|   | 2.0                              | 3.1.4 Extension to signed Booth multipliers                   | 31               |

|   | 3.2                              | Performance Evaluation                                        | 31<br>31         |

|   |                                  | 3.2.1 Accuracy analysis                                       | 33               |

|   | 3.3                              | Example Applications                                          | 34               |

|   | 0.0                              | 3.3.1 Image sharpening                                        | 34               |

|   |                                  | 3.3.2 JPEG image compression                                  | 36               |

|   |                                  | 3.3.3 Multiple-input multiple-output wireless systems         | 36               |

|   | 3.4                              | Summary                                                       | 40               |

| 4 | Imp                              | proving the Accuracy and Hardware Efficiency of Neural        |                  |

|   | Net                              | works Using Approximate Multipliers                           | <b>42</b>        |

|   | 4.1                              | Evaluation of Approximate Multipliers in Neural Networks      | 43               |

|   |                                  | 4.1.1 Application-independent metrics                         | 43               |

|   |                                  | 4.1.2 Application-dependent metrics                           | 45               |

|   | 4.0                              | 4.1.3 Overfitting                                             | 46               |

|   | 4.2                              | Critical Features of Multipliers for NNs                      | 49<br>50         |

|   |                                  | 4.2.1 Feature selection                                       | $\frac{50}{52}$  |

|   | 4.3                              | Error and Hardware Analysis of Approximate Multipliers        | 57               |

|   | 1.0                              | 4.3.1 Error analysis                                          | 57               |

|         | 4.4<br>4.5                               | 4.3.2 Hardware analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 57<br>60<br>63                                                  |

|---------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| 5       |                                          | arithmic Multiplier and Squaring Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 65                                                              |

|         | 5.1                                      | Fast and Low-Power Leading-One Detector for More Energy-<br>Efficient Logarithmic Multipliers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 65                                                              |

|         |                                          | 5.1.1 The proposed LOD design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 66                                                              |

|         | 5.2                                      | 5.1.2 Hardware analysis of the proposed LOD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 67                                                              |

|         | 0.2                                      | ral Computing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 68                                                              |

|         |                                          | 5.2.1 Proposed approximation approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 68                                                              |

|         |                                          | 5.2.2 Improved logarithmic multiplier design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 70<br>75                                                        |

|         |                                          | 5.2.4 Example application: neural networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 79                                                              |

|         | 5.3                                      | Low-Power Approximate Logarithmic Squaring Circuit Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 83                                                              |

|         |                                          | for DSP Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 83<br>83                                                        |

|         |                                          | 5.3.2 Performance evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 88                                                              |

|         | 5.4                                      | 5.3.3 Example application: square law detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 91<br>92                                                        |

|         |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                 |

|         | 0.1                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 02                                                              |

| 6       | $\operatorname{Log}$                     | arithmic Multiply-Accumulate Unit and Accelerators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 94                                                              |

| 6       |                                          | carithmic Multiply-Accumulate Unit and Accelerators Design of a Fast and Energy-Efficient Approximate Logarithmic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 94                                                              |

| 6       | $\operatorname{Log}$                     | rarithmic Multiply-Accumulate Unit and Accelerators  Design of a Fast and Energy-Efficient Approximate Logarithmic  MAC Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 94<br>95<br>95                                                  |

| 6       | $\operatorname{Log}$                     | parithmic Multiply-Accumulate Unit and Accelerators  Design of a Fast and Energy-Efficient Approximate Logarithmic MAC Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 94<br>95<br>95<br>100                                           |

| 6       | $\operatorname{Log}$                     | arithmic Multiply-Accumulate Unit and Accelerators  Design of a Fast and Energy-Efficient Approximate Logarithmic  MAC Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 94<br>95<br>95                                                  |

| 6       | <b>Log</b> 6.1                           | rarithmic Multiply-Accumulate Unit and Accelerators  Design of a Fast and Energy-Efficient Approximate Logarithmic MAC Unit  6.1.1 Proposed logarithmic MAC (LMAC)  6.1.2 Evaluation of the LMAC  6.1.3 Example application: image sharpening  Approximate Accelerators for CNN-based Image Classifiers that Rely on Pixel Spatial Dependence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 94<br>95<br>95<br>100<br>102                                    |

| 6       | <b>Log</b> 6.1                           | rarithmic Multiply-Accumulate Unit and Accelerators  Design of a Fast and Energy-Efficient Approximate Logarithmic MAC Unit  6.1.1 Proposed logarithmic MAC (LMAC)  6.1.2 Evaluation of the LMAC  6.1.3 Example application: image sharpening  Approximate Accelerators for CNN-based Image Classifiers that Rely on Pixel Spatial Dependence  6.2.1 Proposed approximate accelerators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 94<br>95<br>95<br>100<br>102<br>103<br>106                      |

| 6       | <b>Log</b> 6.1                           | rarithmic Multiply-Accumulate Unit and Accelerators  Design of a Fast and Energy-Efficient Approximate Logarithmic MAC Unit  6.1.1 Proposed logarithmic MAC (LMAC)  6.1.2 Evaluation of the LMAC  6.1.3 Example application: image sharpening  Approximate Accelerators for CNN-based Image Classifiers that Rely on Pixel Spatial Dependence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 94<br>95<br>95<br>100<br>102                                    |

|         | Log 6.1 6.2 6.3                          | Parithmic Multiply-Accumulate Unit and Accelerators  Design of a Fast and Energy-Efficient Approximate Logarithmic MAC Unit  6.1.1 Proposed logarithmic MAC (LMAC)  6.1.2 Evaluation of the LMAC  6.1.3 Example application: image sharpening  Approximate Accelerators for CNN-based Image Classifiers that Rely on Pixel Spatial Dependence  6.2.1 Proposed approximate accelerators  6.2.2 Evaluation of the SDLP Accelerators  Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 94<br>95<br>95<br>100<br>102<br>103<br>106<br>113<br>116        |

| 6<br>7  | Log 6.1 6.2 6.3 Cor 7.1                  | Parithmic Multiply-Accumulate Unit and Accelerators  Design of a Fast and Energy-Efficient Approximate Logarithmic MAC Unit  6.1.1 Proposed logarithmic MAC (LMAC)  6.1.2 Evaluation of the LMAC  6.1.3 Example application: image sharpening  Approximate Accelerators for CNN-based Image Classifiers that Rely on Pixel Spatial Dependence  6.2.1 Proposed approximate accelerators  6.2.2 Evaluation of the SDLP Accelerators  Summary  Conclusions and Future Work  Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 94 95 95 100 102 103 106 113 116 118                            |

|         | Log 6.1 6.2 6.3 Cor                      | Parithmic Multiply-Accumulate Unit and Accelerators  Design of a Fast and Energy-Efficient Approximate Logarithmic MAC Unit  6.1.1 Proposed logarithmic MAC (LMAC)  6.1.2 Evaluation of the LMAC  6.1.3 Example application: image sharpening  Approximate Accelerators for CNN-based Image Classifiers that Rely on Pixel Spatial Dependence  6.2.1 Proposed approximate accelerators  6.2.2 Evaluation of the SDLP Accelerators  Summary  Columnary  C | 94<br>95<br>95<br>100<br>102<br>103<br>106<br>113<br>116        |

| 7       | Log 6.1 6.2 6.3 Cor 7.1                  | Tarithmic Multiply-Accumulate Unit and Accelerators  Design of a Fast and Energy-Efficient Approximate Logarithmic MAC Unit  6.1.1 Proposed logarithmic MAC (LMAC)  6.1.2 Evaluation of the LMAC  6.1.3 Example application: image sharpening  Approximate Accelerators for CNN-based Image Classifiers that Rely on Pixel Spatial Dependence  6.2.1 Proposed approximate accelerators  6.2.2 Evaluation of the SDLP Accelerators  Summary  Acclusions and Future Work  Conclusions  Future work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 94 95 95 100 102 103 106 113 116 118                            |

| 7<br>Re | 6.2<br>6.3<br>Cor<br>7.1<br>7.2<br>efere | Tarithmic Multiply-Accumulate Unit and Accelerators  Design of a Fast and Energy-Efficient Approximate Logarithmic MAC Unit  6.1.1 Proposed logarithmic MAC (LMAC)  6.1.2 Evaluation of the LMAC  6.1.3 Example application: image sharpening  Approximate Accelerators for CNN-based Image Classifiers that Rely on Pixel Spatial Dependence  6.2.1 Proposed approximate accelerators  6.2.2 Evaluation of the SDLP Accelerators  Summary  Acclusions and Future Work  Conclusions  Future work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 94<br>95<br>95<br>100<br>102<br>103<br>106<br>113<br>118<br>120 |

## List of Tables

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10 | Truth table of the proposed approximate compressor Truth table of the proposed approximate compressor Truth table for the Stage 2 compressor | 21<br>23<br>24<br>25<br>27<br>30<br>32<br>33<br>34<br>37 |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7                       | Considered features of the output error function                                                                                             | 44<br>52<br>54<br>56<br>62<br>62<br>63                   |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10 | Hardware metrics of five different logarithmic squaring functions. The proposed vs. the conventional full adder                              | 67<br>74<br>74<br>77<br>78<br>78<br>82<br>90<br>90<br>92 |

| <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                       | Average PSNR of reconstructed images by using approximate pixel values                                                                       | 102<br>107<br>113                                        |

| 6.4 | Comparison of the hardware cost between the exact and the | 116 |

|-----|-----------------------------------------------------------|-----|

|     | approximate variants of the SDLP accelerators             | 110 |

## List of Figures

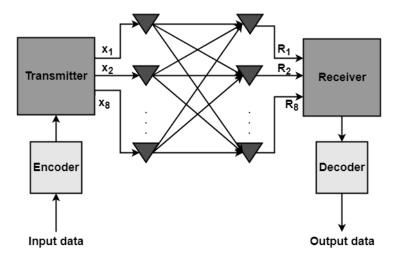

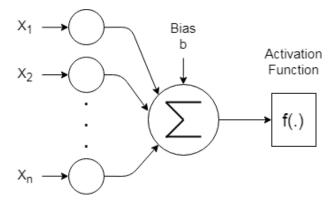

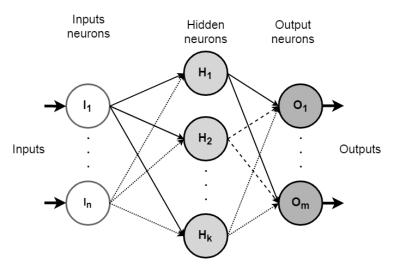

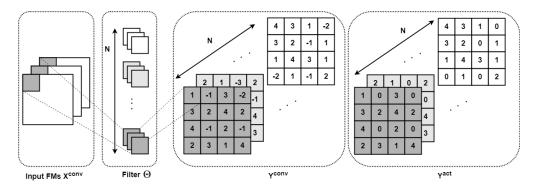

| 2.1<br>2.2<br>2.3<br>2.4                                                    | Block diagram of an 8×8 MIMO system.  Model of an artificial neuron.  Structure of a feed-forward NN.  Feed-forward propagation in convolutional and activation layers.                                                                                                                                     | 11<br>12<br>13<br>15                               |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

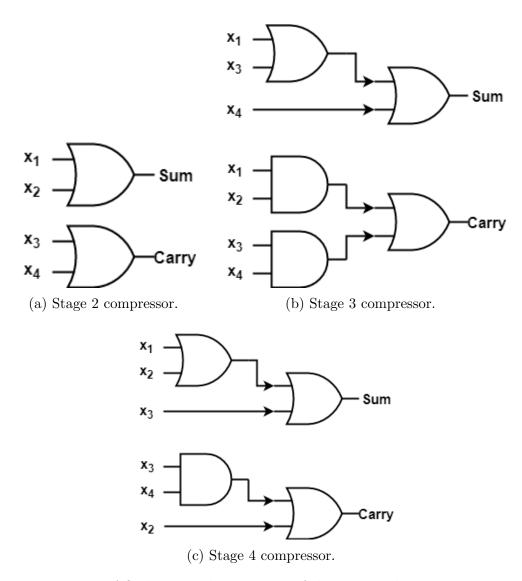

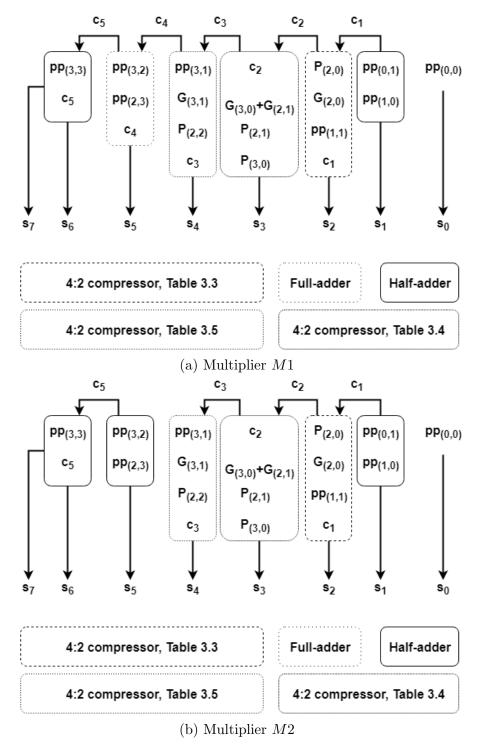

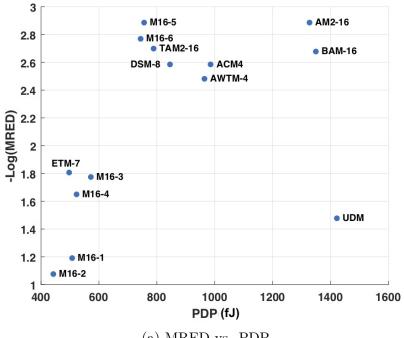

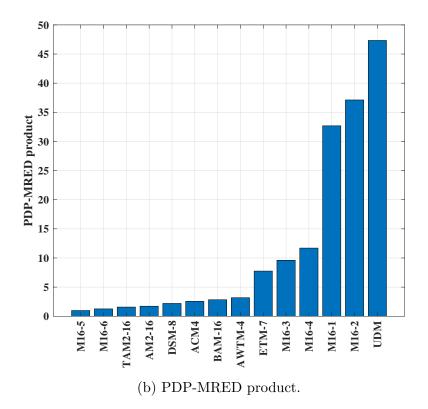

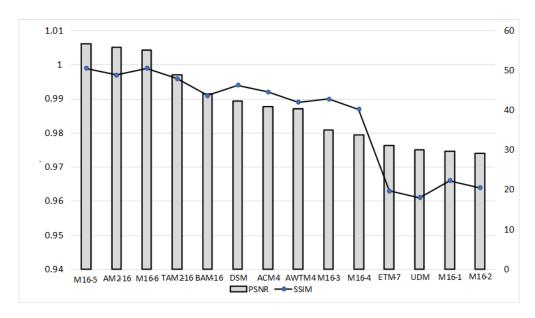

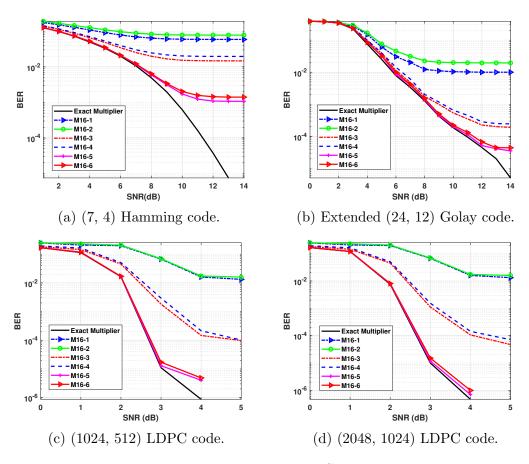

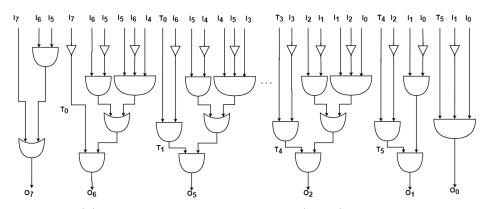

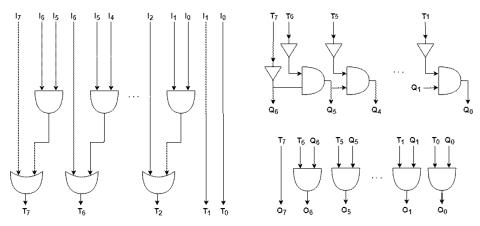

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6                                      | AOI logic implementation of the proposed compressors Partial product reduction in multipliers (a) $M1$ and (b) $M2$ . Building $2n \times 2n$ multipliers using $n \times n$ multipliers MRED and PDP of the approximate multipliers PSNR and SSIM values for the image sharpening application. BER vs. SNR | 26<br>28<br>29<br>35<br>36<br>39                   |

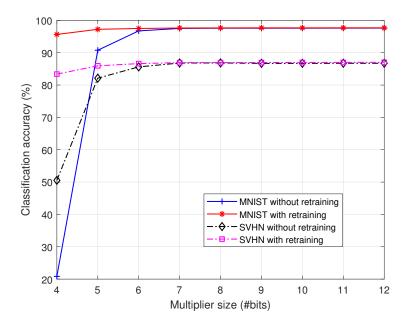

| 4.1<br>4.2                                                                  | Effects of multiplier size on classification accuracy                                                                                                                                                                                                                                                       | 45<br>49                                           |

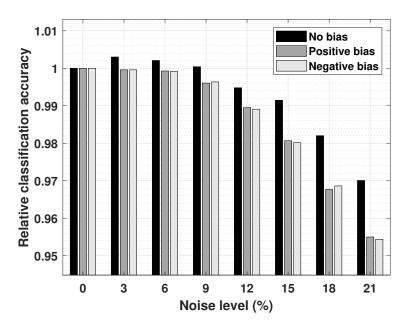

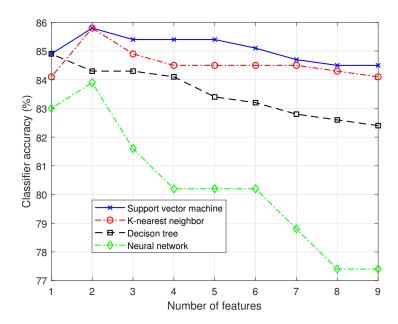

| 4.3                                                                         | tive Gaussian noise                                                                                                                                                                                                                                                                                         | 55                                                 |

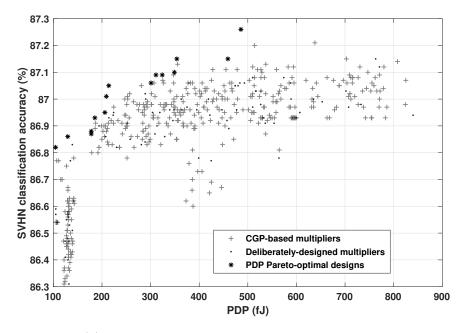

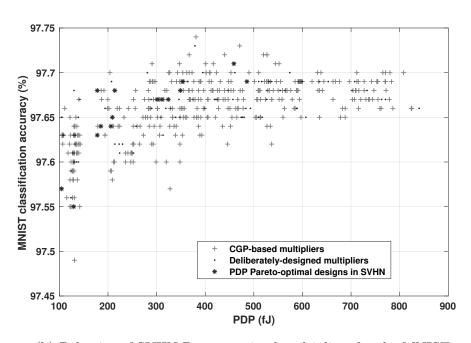

| 4.4                                                                         | Neural network accuracy using the same approximate multipliers for different datasets                                                                                                                                                                                                                       | 58                                                 |

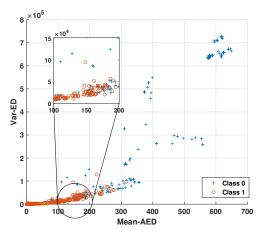

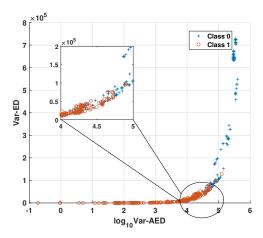

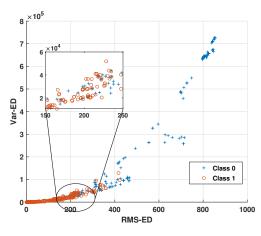

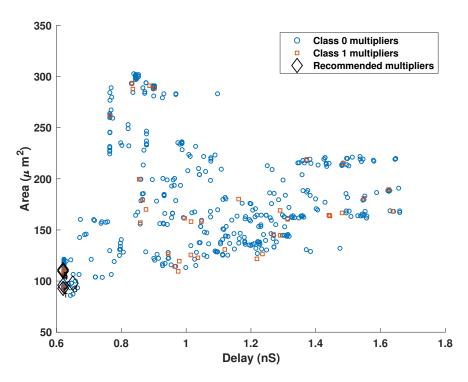

| 4.5                                                                         | Classification of Class 0 and Class 1 multipliers based on the most important features                                                                                                                                                                                                                      | 59                                                 |

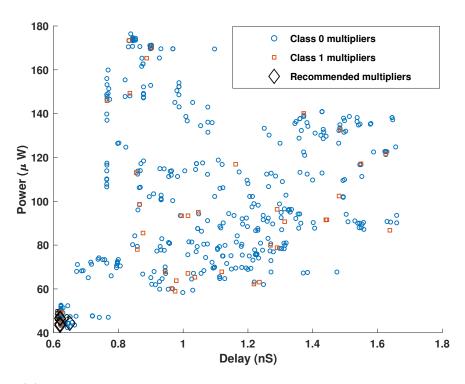

| 4.6                                                                         | Hardware comparison between Class 0 and Class 1 approximate multipliers                                                                                                                                                                                                                                     | 61                                                 |

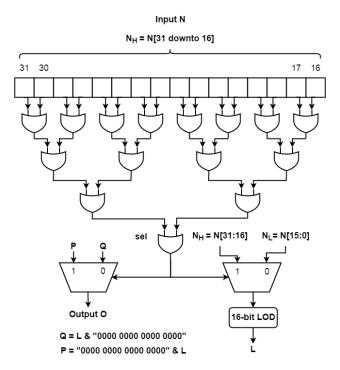

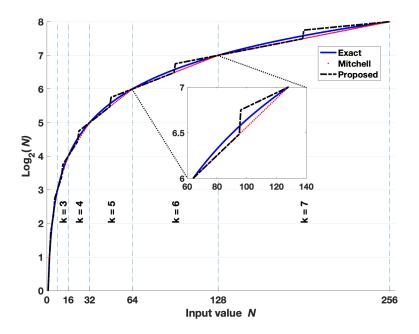

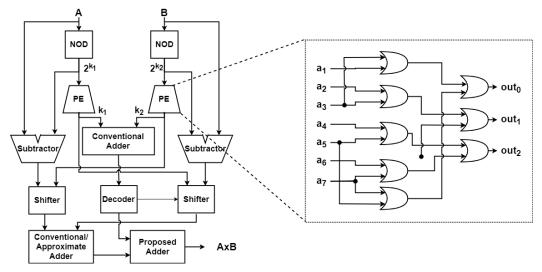

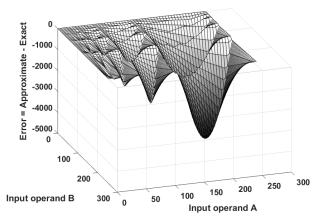

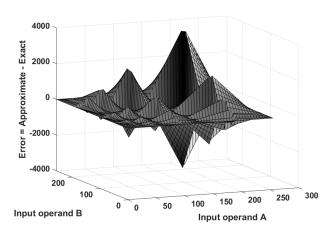

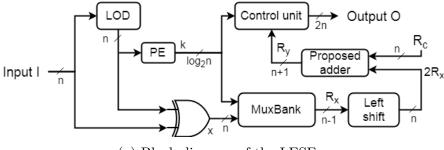

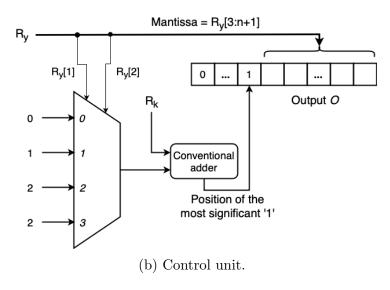

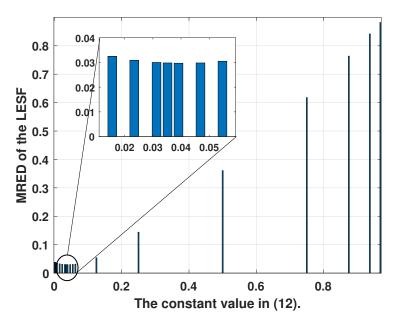

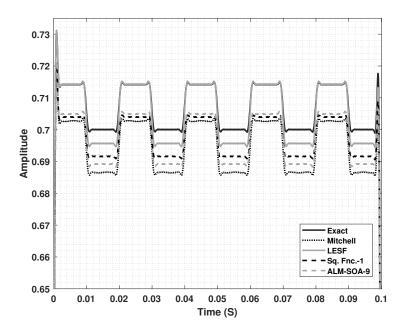

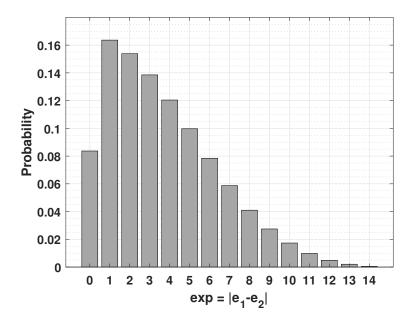

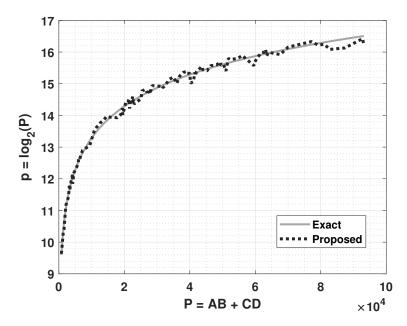

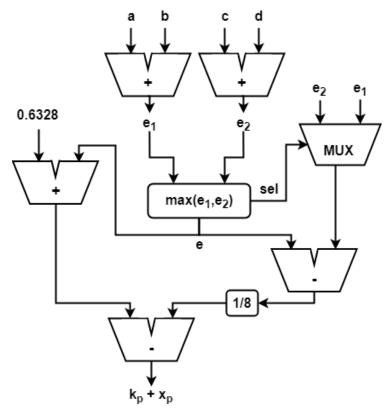

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11 | Using a 16-bit LOD to find the position of the leading one in a 32-bit number                                                                                                                                                                                                                               | 67<br>69<br>72<br>76<br>80<br>81<br>85<br>86<br>89 |

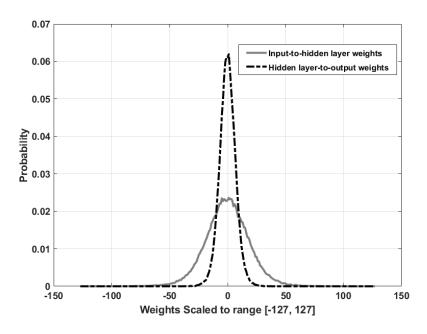

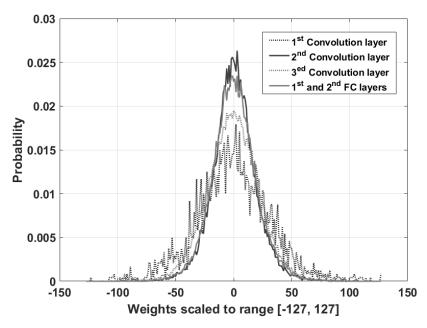

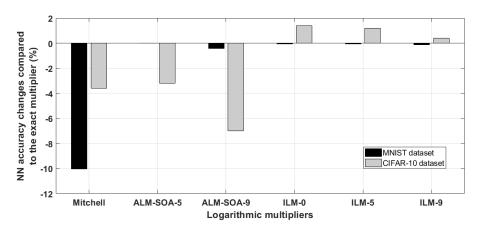

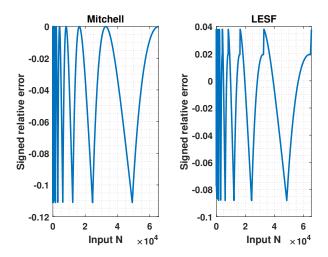

| <i>C</i> 1                                                                  | logarithmic squaring functions.                                                                                                                                                                                                                                                                             | 92                                                 |