National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Service

Services des thèses canadiennes

Ottawa, Canada K1A 0N4

# CANADIAN THESES

# THÈSES CANADIENNES

# NOTICE

The quality of this microfiche is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree,

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Previously copyrighted materials (journal articles, published tests, etc.) are not filmed.

Reproduction in full or in part of this film is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30.

La qualité de cette microfiche dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

Les documents qui font déjà l'objet d'un droit d'auteur (articles de revue, examens publiés, etc.) ne sont pas microfilmés.

Là reproduction, même partielle, de ce microfilm est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30.

THIS DISSERTATION HAS BEEN MICROFILMED **EXACTLY AS RECEIVED**

LA THÈSE A ÉTÉ MICROFILMÉE TELLE QUE NOUS L'AVONS REÇUE

# THE UNIVERSITY OF ALBERTA

Compensation Techniques for Internal CMOS Operational Amplifiers

BY

Guy Fortier

# A THESIS

SUBMITTED TO THE FACULTY OF GRADUATE STUDIES AND RESEARCH

IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE

OF MASTER OF SCIENCE

DEPARTMENT OF ELECTRICAL ENGINEERING

EDMONTON, ALBERTA

SPRING 1987

Permission has been granted to the National Library of Canada to microfilm this thesis and to lend of sell copies of the film.

The author (copyright owner) has reserved other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without his/her written permission.

L'autorisation a été accordée à la Bibliothèque nationale du Canada de microfilmer cette thèse et de prêter ou de vendre des exemplaires du film.

L'auteur (titulaire du droit d'auteur) se réserve les autres droits de publication; ni la thèse ni de longs extraits de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation écrite.

ISBN 0-315-37744-5

# THE UNIVERSITY OF ALBERTA .

# RELEASE FORM

NAME OF AUTHOR: Guy Fortier

TITLE OF THESIS: Compensation Techniques for Internal

CMOS Operational Amplifiers

DEGREE: Master of Science

YEAR THIS DEGREE GRANTED: SPRING 1987

Permission is hereby granted to THE UNIVERSITY OF ALBERTA LIBRARY to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly or scientific research purposes only.

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.

9012 - 135 Avenue Edmonton, Alberta Canada, T5E 1N4

Date: January 30, 1987

# THE UNIVERSITY OF ALBERTA

# FACULTY OF GRADUATE STUDIES AND RESEARCH

The undersigned certify that they thave read, and recommend to the Faculty of Graduate Studies and Research for acceptance, a thesis entitled Compensation Techniques for Internal CMOS Operational Amplifiers submitted by Guy Fortier in partial fulfilment of the requirements for the degree of Master of Science.

(Supervisor)

January 30, 1987

# **ABSTRACT**

A novel compensation technique for internal two-stage CMOS op amps Instead of connecting the compensation capacitor across is presented. the output stage for the Miller multiplication effect, a separate matched 'compensation' stage is used. The RHP zero is eliminated and the nondominant pole becomes independent of the load capacitance resulting in a 200 improvement in the phase margin for the same power dissipation. The achievable performance for this type of compensation in propas such as power dissipation, settling time, phase margin, die supply rejection is compared with the other power compensation schemes found in the literature. Designs based on a set of specifications were generated using the different The step response of the unity gain compensation techniques. was studied using SPICE simulations. configuration capacitor compensation and the separate stage compensation designs were The measurements for a sample of 5 chips are given. integrated. meral design of internal two-stage CMOS op amps is discussed and a systematic design method is presented.

# ACKNOWLEDGEMENTS

The author wishes to extend his sincere thanks to

- the Canadian Microelectronic Corporation whose services permitted the fabrication of the integrated circuits

- Bell Northern Research and the Alberta Microelectronics

Corporation for their financial support

- his supervisor Prof. I.M. Filanovsky for his guidance and encouragement

- his wife Marjo and his typist Colleen for all the work which went into preparing the manuscript

- his friend Ganesh Kothapalli for his moral support.

|         | TABLE OF CONTENTS                                                                                              |      |

|---------|----------------------------------------------------------------------------------------------------------------|------|

| ,       |                                                                                                                |      |

| CHAPTER |                                                                                                                | PAGE |

| 1.0 IN  | TRODUCTION                                                                                                     | - ,  |

|         |                                                                                                                | 1    |

| 1.      | 1 Applications of op amps                                                                                      | 1    |

| i,      | 2 CMOS realization of op amps                                                                                  | 2    |

| 1.      | 3 Two categories of op amp                                                                                     | 3    |

| ι.      | Stability and compensation of op amps                                                                          | 3    |

| 1.      | Thesis content                                                                                                 | 6    |

| •       |                                                                                                                |      |

| 2.0 OP  | AMP DESIGN                                                                                                     | 10   |

|         | $\lambda_{\alpha}$                                                                                             | . :  |

| 2       | Basic Two-stage Architecture                                                                                   | 10   |

| 2.2     | Performance Parameters                                                                                         | 10   |

| *       | *2.2.1 Gain (Av(0))                                                                                            | 10   |

|         | 2.2.2 Gain bandwidth product (GBW or w <sub>u</sub> )                                                          | 12   |

| •       | 2.2.3 Phase margin (PM)                                                                                        | 14   |

|         | 2.2.4 Slew rate (SR)                                                                                           | 15   |

|         | 2.2.5 Settling time (t <sub>S</sub> )                                                                          | 18   |

|         | 2.2.6 Input common mode range (ICMR) and                                                                       |      |

| •       | output swing (OS)                                                                                              | 20   |

| P       | 2.2.7 Power supply rejection ratio (PSRR)                                                                      | 21   |

|         | 2.2.8 Common mode rejection ratio (CMRR)                                                                       | 25   |

|         | 2.2.9 Offset (Vos) and noise (Vn)                                                                              | 27   |

| 2.3     | rangan kanggan | 31   |

|         |                                                                                                                | 31   |

|         |                                                                                                                | 31   |

|         |                                                                                                                | DT.  |

| TABLE OF CONTENTS (continued)                          |            |

|--------------------------------------------------------|------------|

|                                                        |            |

| CHAPTER                                                | PAGE       |

|                                                        |            |

| 2.4.2 Example                                          | . 36       |

| 2.4.3 Evaluating tradeoffs                             | r - *      |

|                                                        |            |

|                                                        | . 46       |

| 2.5 Effect of Different Architectures                  |            |

| 2.5.1 Variations of the two-stage                      | . 49       |

| 2.5.2 Single stage op amps                             | . 49       |

| 2.5.3 Architectures for low power applications         | . 51       |

| 2.5.4 Circuit techniques for reducing offset and noise | .53        |

|                                                        | •          |

| 3.0 INTERNAL COMPENSATION TECHNIQUES                   | 55         |

| 3.1 General Considerations                             | 55         |

| 3.1.1 Second order system model                        | 55         |

| 3.1.2 Validity of second order assumption              | 59         |

| 3.2 Series Buffer Compensation                         | 61         |

| 3.2.1 Description                                      | 61         |

| 3.2.2 Choosing Ro                                      | 64         |

| 3.2.3 Power dissipation                                |            |

| 3.2.4 Lower limit on g <sub>m2</sub>                   | 66         |

| 3.2.5 Choosing C                                       | . 66       |

|                                                        | 67         |

| 3.2.6 Factors affecting the step response              | 6 <b>9</b> |

| - Imprecise pole/zero cancellation                     | 68         |

| - Nonlinear second stage                               | '70        |

| 3.2.7 SPICE results                                    | 73         |

|                                                        | ~          |

| vii                                                    |            |

# / TABLE OF CONTENTS (continued)

| CHAPTER                                   | PAGE   |

|-------------------------------------------|--------|

|                                           |        |

| 3.3 Series Resistor Compensation          | 76     |

| 3.3.1 Description                         | 76     |

| 3,3.2 Choosing R                          | , 78   |

| 3.3.3 Slew rate limitations               | 79     |

| 3.3.4 Choosing C                          | 4      |

| 3.3.5 Factors affecting the step response | 80     |

| 3.3.6 SPICE results                       | 80     |

| 3.4 Separate Stage Compensation           | 83     |

| 3.4/1 Small signal analysis               | . 83   |

| 3.4.2 Phase margin                        | 85     |

| 3.4.3 Power dissipation                   | .,. 85 |

| 3.4.4 Settling time                       | 86     |

| .4.5 Matching requirements                | 87     |

| 3.4.6 Power supply rejection              | 88     |

| 3.4.7 SPICE results                       | 90     |

|                                           |        |

| 4.0 EXPERIMENTAL RESULTS                  | 95     |

| 4.1 Op Amp Implementation                 | 95     |

| 4.2 Open Loop DC Measurements             | 98     |

| 4.3 Closed Loop DC Measurements           | 98     |

| 4.4 Slew Rate Measurements                | . 102  |

| 4.5 Settling Time Measurements            | 103    |

| 4.6 Phase Margin and Unity Gain Frequency | 107    |

|                                           |        |

|                                           |        |

# TABLE OF CONTENTS (continued)

| CHAP    | TER       |                                                        | PAGE         |

|---------|-----------|--------------------------------------------------------|--------------|

|         | ,         |                                                        |              |

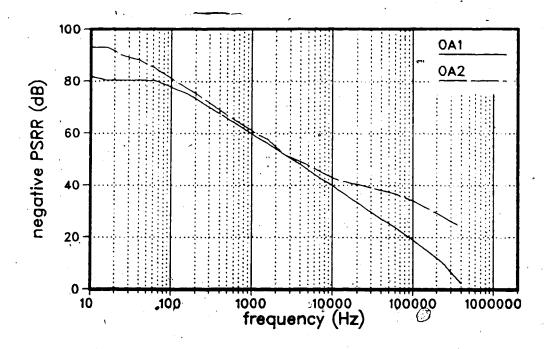

| •       | 4.7       | Negative PSRR Measurement                              | 107          |

|         | 4.8       | Positive PSRR and CMRR Measurements                    | 108          |

|         | 4.9       | Discussion of Results                                  | 111          |

|         | * .       |                                                        |              |

| 5.0     | CONC      | CLUSIONS AND DISCUSSION                                | 114          |

|         | 5,1       | General Design of Two-stage Amplifiers                 | L <b>1</b> 4 |

| هد درون | 5.2       | Realization in Different Technologies                  | 116          |

| ,       | 5 3       | Effects of Compensation Techniques on OA Performance 1 | 117          |

|         | 5.4       | Separate Stage Compensation                            | 119          |

|         | 5.5       | Concluding Remarks and Future Research                 | l21          |

|         | , A. BIBL | <b>TOGRAPHY</b>                                        | 123          |

|         |           |                                                        |              |

|         | Appe      | ndix 1 Estimation of SR and GBW for a given ts         | 125          |

| -/.     | Appe      | ndix 2 ICMR and OS Requirements                        | [ <b>2</b> 8 |

| /       | Appe      | ndix 3 SPICE File for Design Example                   | 30           |

| _     | LIST OF TABLES                                                                          |

|-------|-----------------------------------------------------------------------------------------|

| TABLE | PA                                                                                      |

|       |                                                                                         |

| 2.1   | Typical performance specifications for a 2-stage CMOS op amp (PMOS input configuration) |

| 2.2   | Design equations 3                                                                      |

| 2.3   | Specifications for the design example                                                   |

| 2.4   | Relationships between gct and performance parameters 45                                 |

| 2.5   | Comparison of NMOS vs PMOS input configurations                                         |

| 3.1   | Results of simulations on designs using series buffer compensation                      |

| 3.2   | Simulation results for series resistor compensation designs 81                          |

| 3.3   | Separate stage and conventional compensation design circuit parameters                  |

| 3.4   | Simulation results for separate stage compensation 92                                   |

| 4.1   | OAl measurement results                                                                 |

| 4.2   | OA2 measurement results                                                                 |

|       | LIST OF FIGURES                                                                |        |

|-------|--------------------------------------------------------------------------------|--------|

| FIGUE | RE                                                                             | PAGE   |

|       |                                                                                |        |

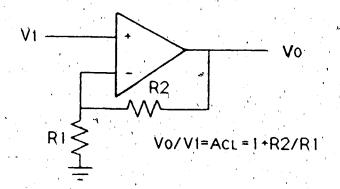

| 1.1   | Typical closed-loop frequency response for non-inverting amplifier application | . 5    |

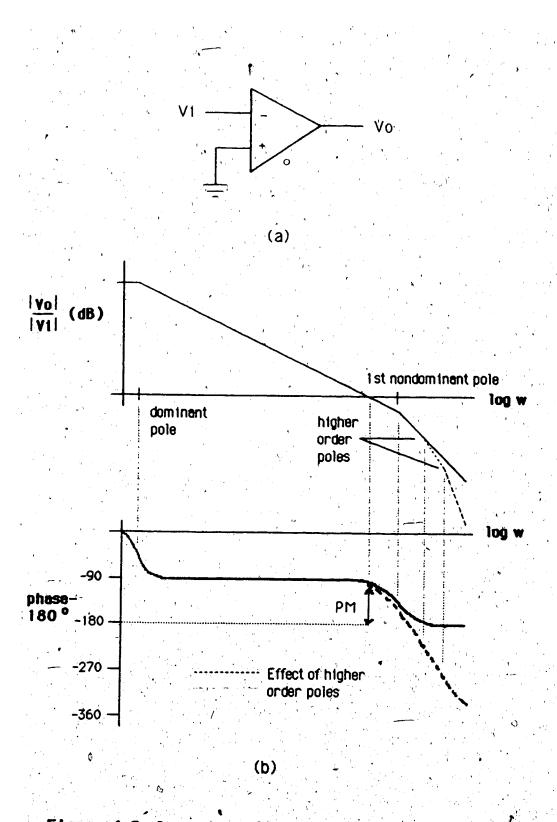

| 1.2   | Open loop frequency response                                                   | . 7    |

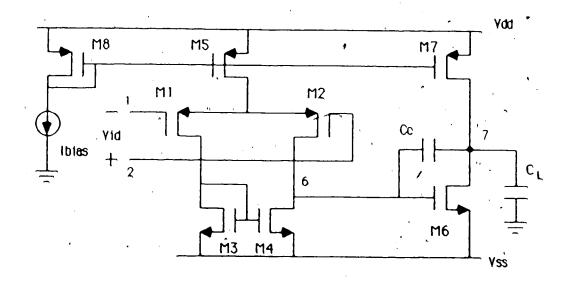

| 2.1   | Two stage architecture                                                         | 11     |

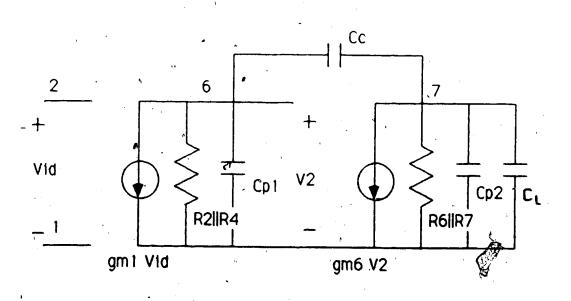

| 2.2   | Small signal model of two stage OA                                             | . 11   |

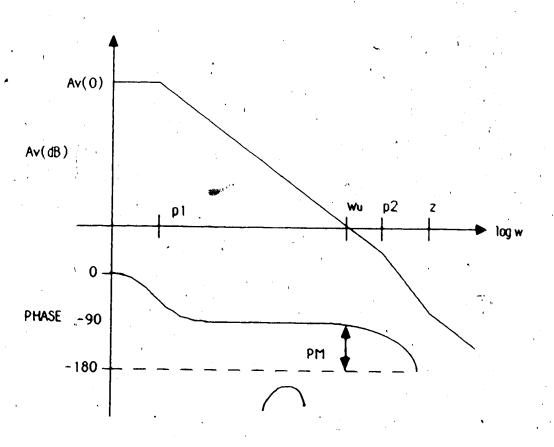

| 2.3   | Frequency response                                                             | . 13   |

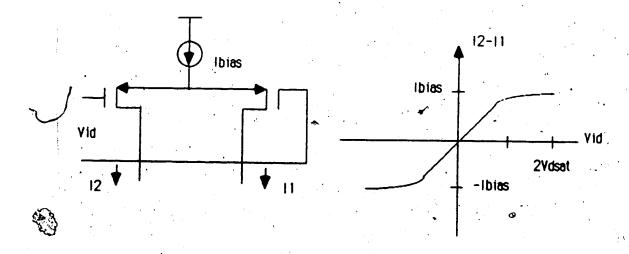

| 2.4   | Differential pair transfer function                                            | . 13 🚭 |

| 2.5   | Effect of transconductance ratio on required nondominant pole location         | 16     |

| 2.6   | Model for calculating SR                                                       | 17     |

| 2,7   | Circuit configuration for testing PSRR                                         | . 17 , |

| 2.8   | Required GBW and SR for a given settling time ts                               | 19     |

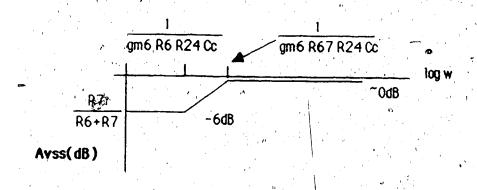

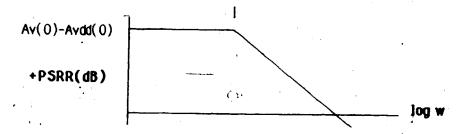

| 2.9   | Model for -PSRR calculations                                                   | 23     |

| 2.10  | Frequency response from negative supply                                        | 23     |

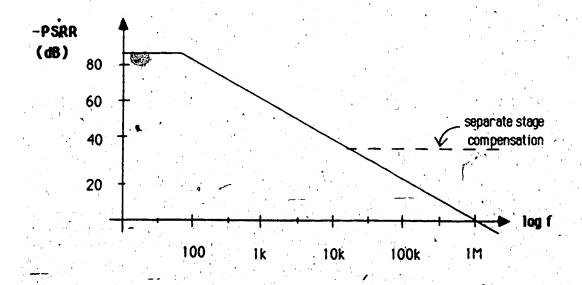

| 2.11  | Negative PSRR                                                                  | 23     |

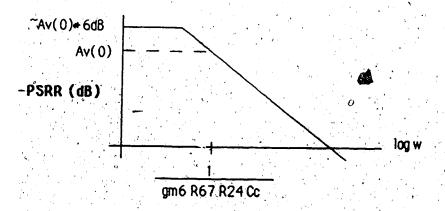

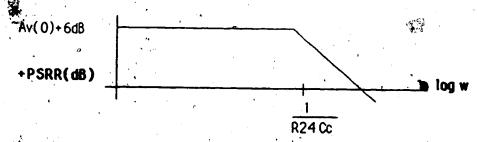

| 2.12  | del for +PSRR calculations                                                     | . 24   |

| 2.13  | Gain from positive supply                                                      | . 24   |

| 2.14  | +PSRR(w)                                                                       | 24     |

| 2.15  | +PSRR(w) assuming infinite first stage rejection                               | . 24   |

| 2.16  | Model for CMRR calculation                                                     | . 26   |

| 2.17  | Common mode gain frequency response                                            | . 26   |

| 2.18  | CMRR frequency response                                                        | . 26   |

| 2.19  | Representation of offset voltage and noise                                     | . 28   |

| 2.20  | Second stage operating point                                                   | . 28   |

# LIST OF FIGURES (continued)

| FIGUR | E                                                                    | PAGE |

|-------|----------------------------------------------------------------------|------|

| 1     |                                                                      |      |

| 2.21  | Spectral noise density example                                       | 28   |

| 2,22  | Design flowchart                                                     | 34   |

| 2.23  | Transistor dimensions for 5 micron rules                             | 42   |

| 2,24  | Two stage op amp with NMOS imputs                                    | 42   |

| 2.25  | Final circuit for design example                                     | 43   |

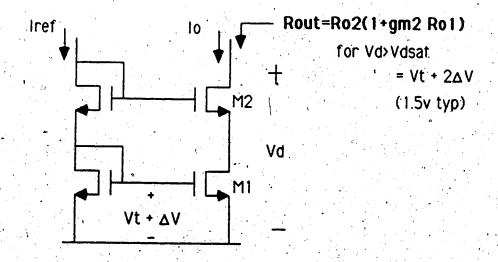

| 2,26  | Cascoded transistor configuration                                    | 43   |

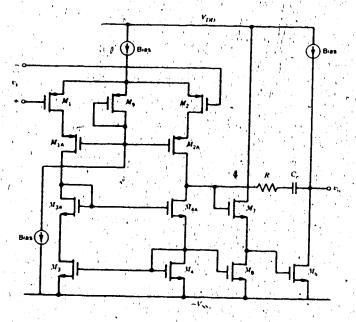

| 2.27  | Op amp with cascoded first stage                                     | 50   |

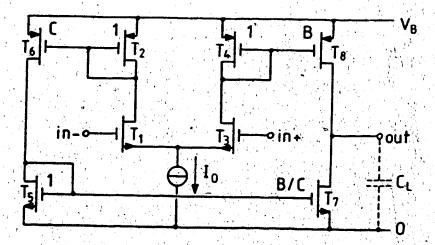

| 2.28  | Operational transconductance amp                                     | 50   |

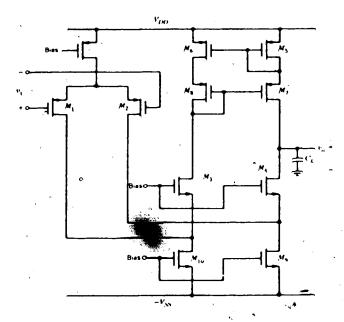

| 2.29  | Folded cascode amp                                                   | 52   |

| 2.30  | Circuit illustrating class AB second stage                           | 52   |

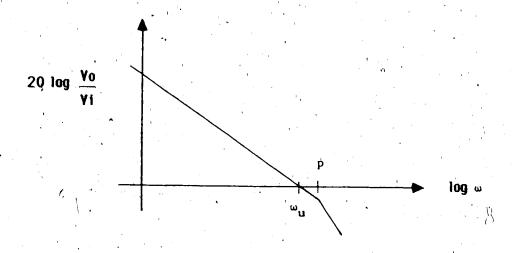

| 3.1   | Simplified OA open loop frequency response                           | 57   |

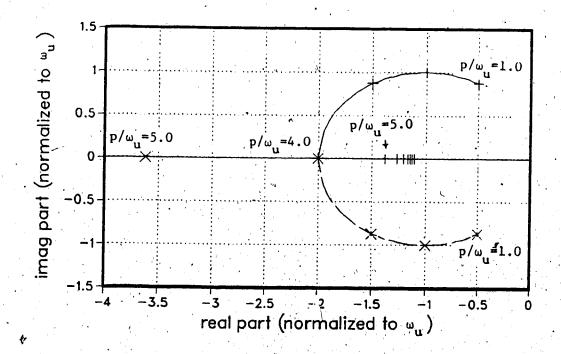

| 3,2   | Root locus for 2nd order system                                      | 57   |

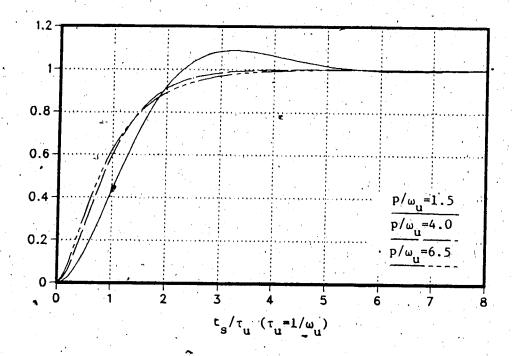

| 3.3   | Step response for 2nd order system                                   | 58 " |

| 3.4   | Phase margin vs open loop pole location for 2nd order system         | 58   |

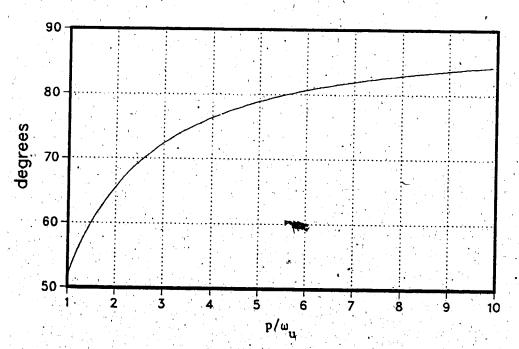

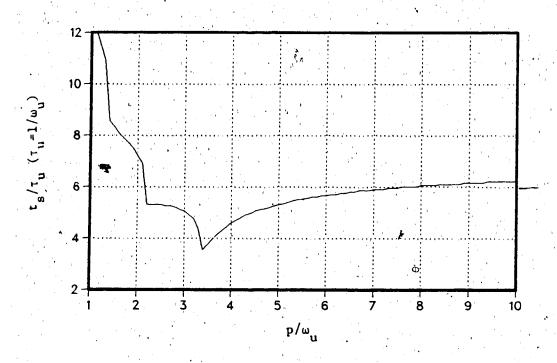

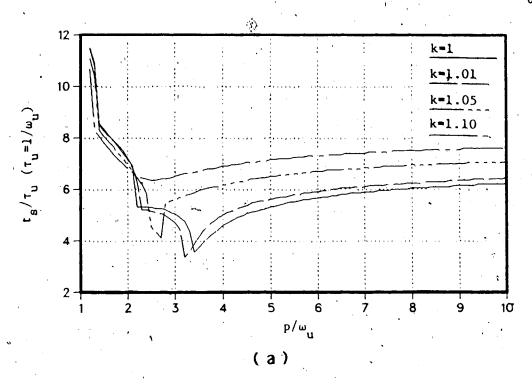

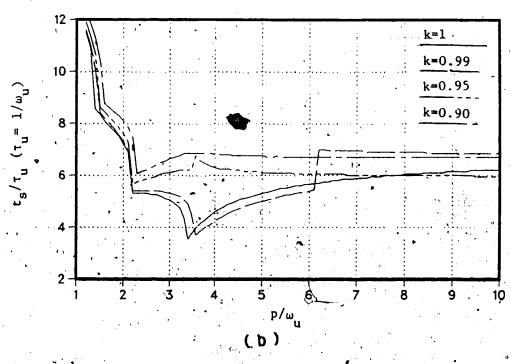

| 3.5   | 0.1% settling time for 2nd order system                              | 60   |

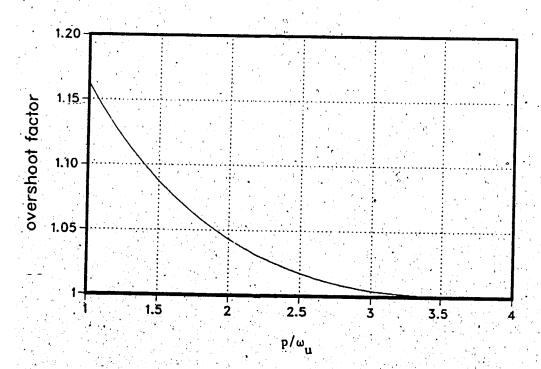

| 3.6   | Overshoot for 2nd order system                                       | 60   |

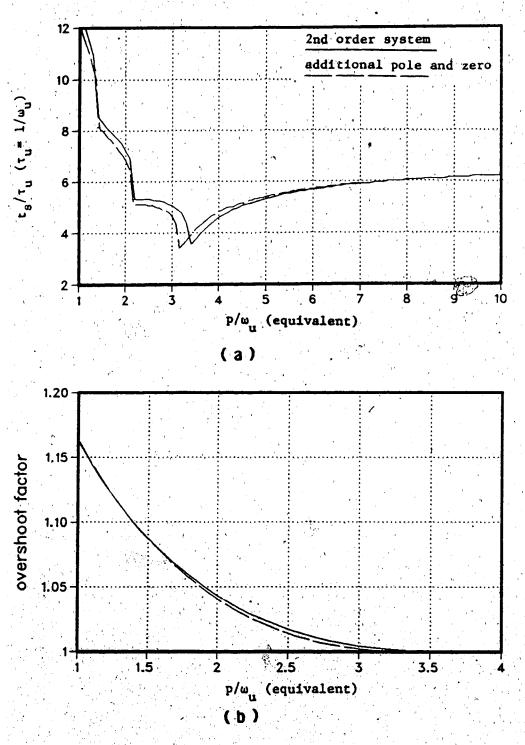

| 3.7   | Accuracy of 2nd order assumption with pole and zero at 10 and 20 MHz | 62   |

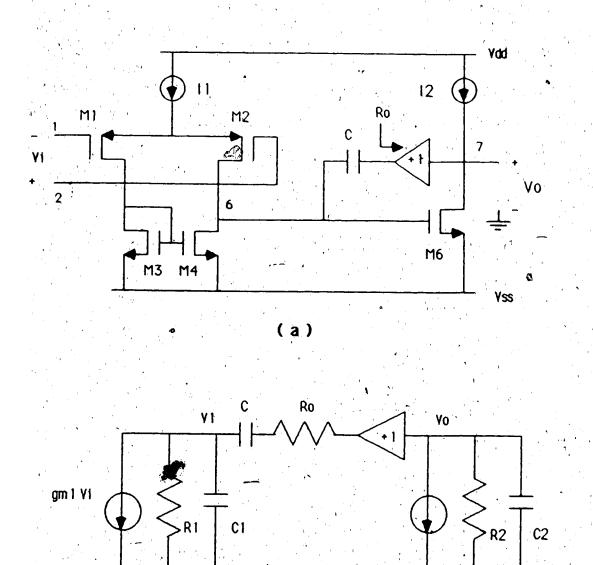

| 3.8   | Compensation with a series buffer                                    | 63   |

| 3.9   | 0.1% settling times with doublet at wu                               | 69   |

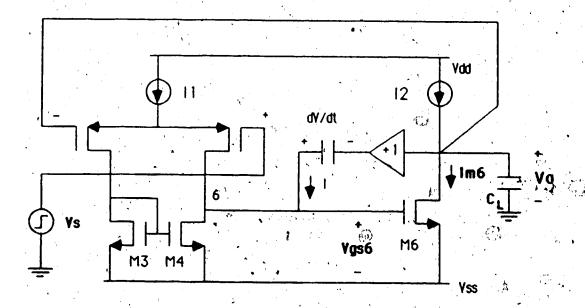

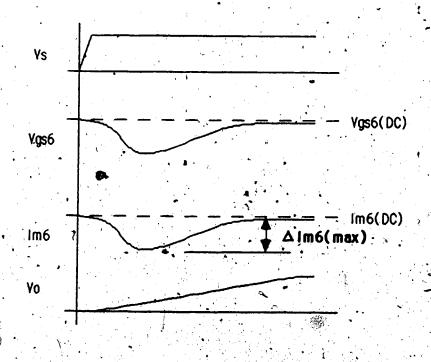

| 3.10  | Waveforms for a positive step input                                  | 71   |

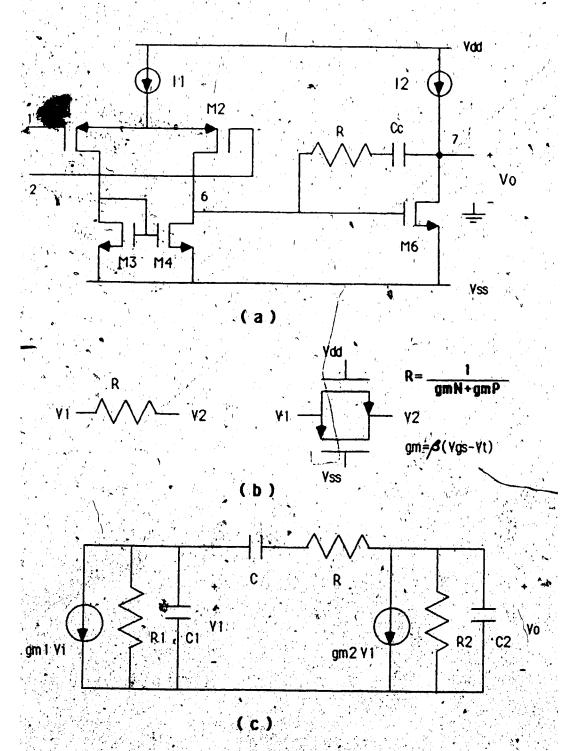

| 3.11  | Compensation with a series resistor                                  | 77-  |

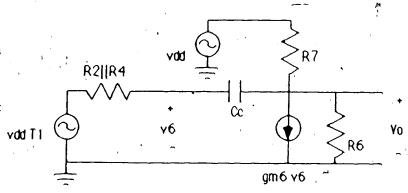

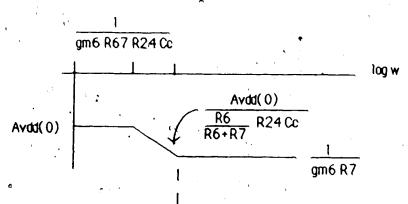

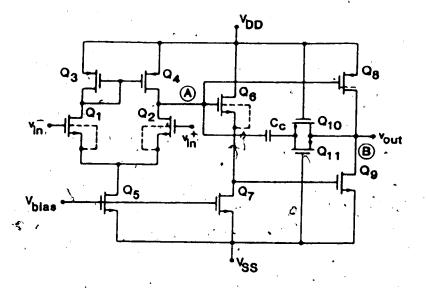

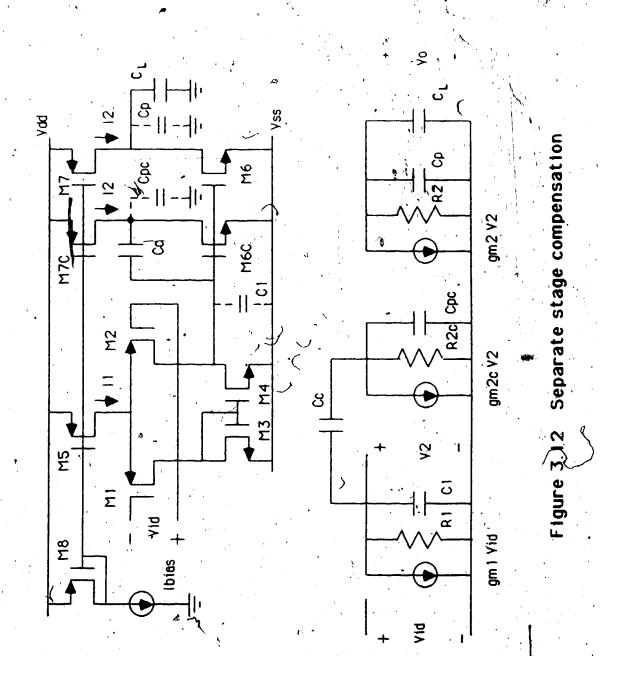

| 3.12  | Separate stage compensation                                          | 84   |

# LIST OF FIGURES (continued)

| FIGURE |                                                                               | PAGE  |

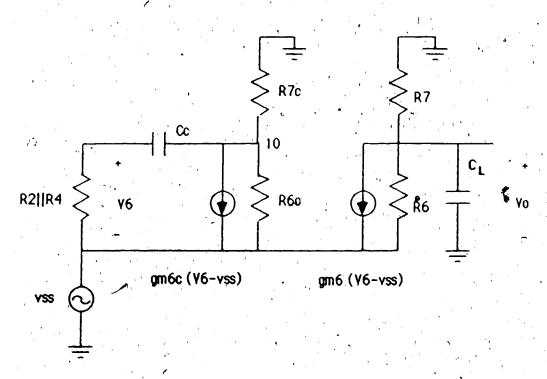

|--------|-------------------------------------------------------------------------------|-------|

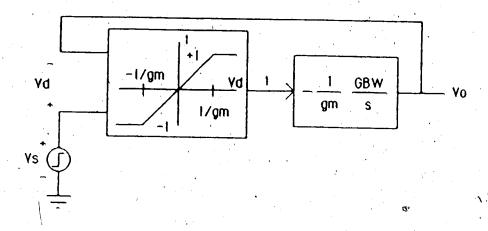

| 3,13   | Model for calculating negative PSRR                                           | 89    |

| 3,14   | Negative PSRR for separate stage and conventional compensation design         | 89    |

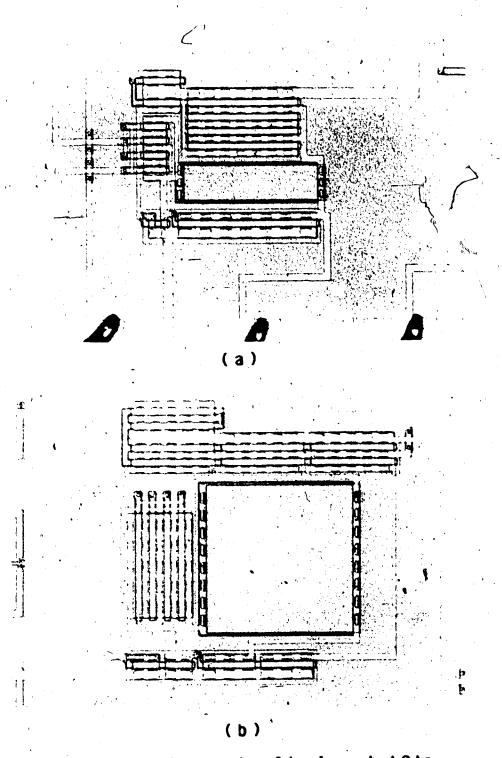

| 4.1    | Photomicrographs of implemented OAs                                           | 96    |

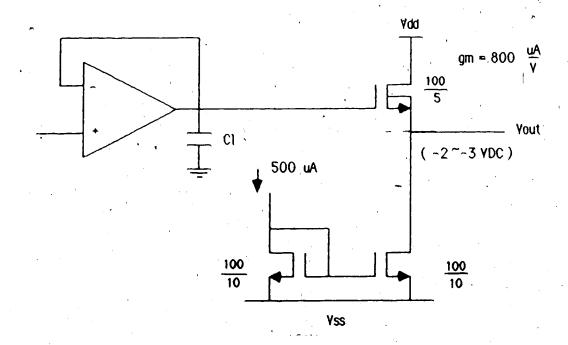

| 4.2    | Buffered version of implemented OAs                                           | 97    |

| 4,3    | Open loop measurement on semiconductor parameter analyser.                    | 97    |

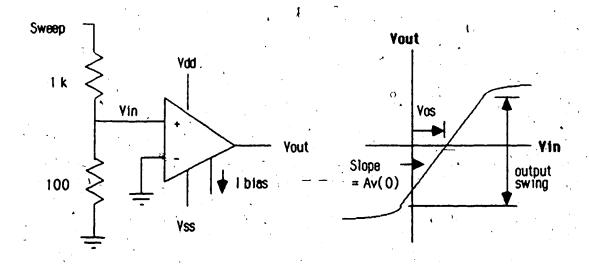

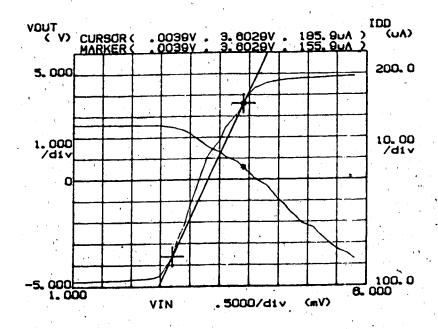

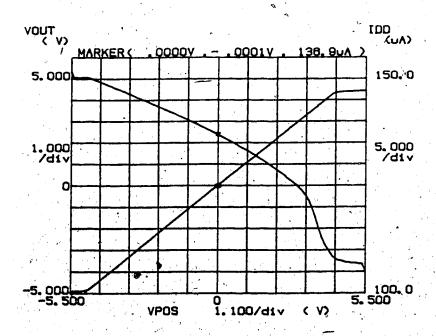

| 4,4    | Open loop transfer characteristic                                             | 101 " |

| 4.5    | Closed loop transfer characteristic                                           | 101   |

| 4,6    | 3 V step response of OAl                                                      | 104   |

| 4,7    | 1 V step response                                                             | 104   |

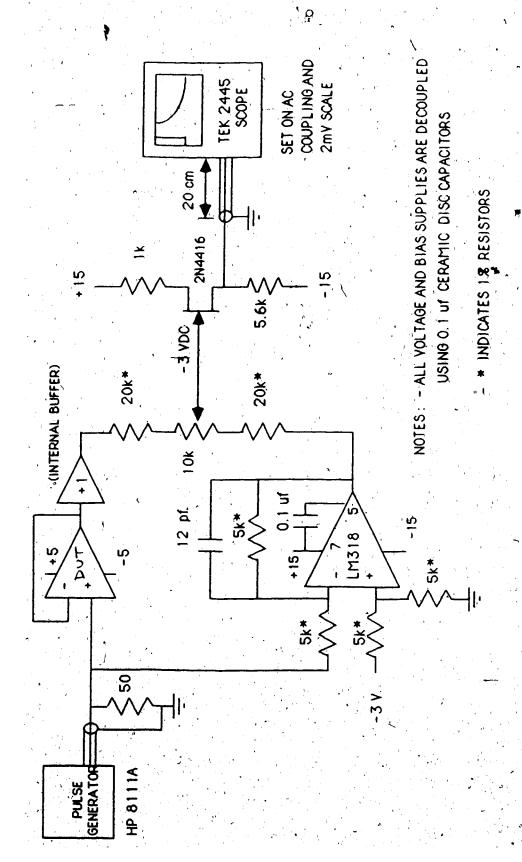

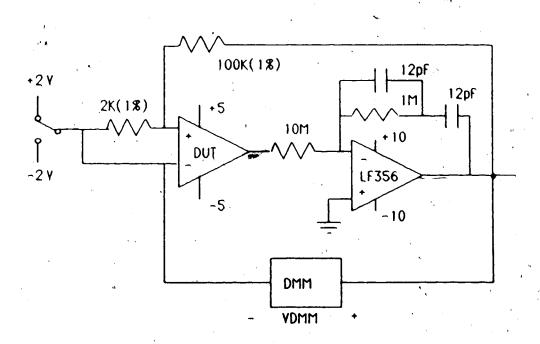

| 4.8    | Circuit used to make settling time measurement                                | 105   |

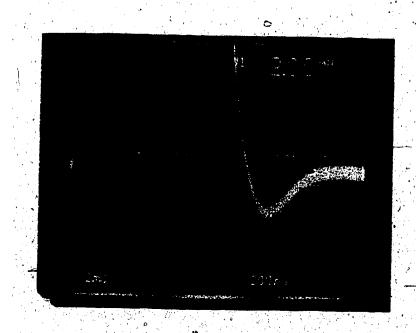

| 4,9'   | Input pulse and spike waveforms seen at center of divider in settling circuit | 106   |

| 4.10   | Middle spike of fig. 4.9 as seen on most sensitive scale .                    | 106   |

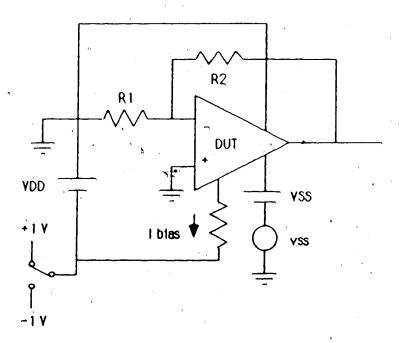

| 4.11   | Configuration for measuring PSRR                                              | 109   |

| 4.12   | Negative PSRR                                                                 | 109   |

| 4.13   | Configuration for measuring CMRR                                              | 110   |

| 4.14   | OA2 settling time waveform showing 'long tail' due to pole-zero mismatch \    | 110   |

| Al.1   | Simplified model of the OA in the non-inverting unity gain configuration      | 126   |

| A1.2   | Step response for the circuit of fig Al.1                                     | 126   |

|        |                                                                               |       |

|                                    | LIST OF SYMBOLS                                             |

|------------------------------------|-------------------------------------------------------------|

| •                                  |                                                             |

| . A <sub>1</sub>                   | differential input voltage gain (open loop) at doublet      |

|                                    | frequency                                                   |

| Acm                                | common mode input voltage gain                              |

| Av(0)                              | differential input voltage gain (open loop) at DC           |

| Av,A <sub>OL</sub>                 | differential input voltage gain (open loop)                 |

| Av <sub>DD</sub> , Av <sub>S</sub> | voltage gain from power supplies to output                  |

| Ce                                 | compensation capacitor                                      |

| -c <sub>L</sub>                    | load capacitor                                              |

| CMRR                               | common mode rejection ratio                                 |

| Cox                                | gate oxide capacitance                                      |

| c <sub>p</sub>                     | parasitic capacitance                                       |

| $\mathbf{f_u}$                     | op amp unity gain frequency                                 |

| f <sub>T</sub>                     | transistor unity current gain frequency                     |

| GBW                                | gain-bandwidth product                                      |

| e <sub>m</sub>                     | transistor transconductance                                 |

| g <sub>mb</sub>                    | transistor transconductance from substrate                  |

| 1,                                 | op amp first stage bias current                             |

| 12                                 | op amp second stage bias current                            |

| ICMR                               | input common mode range                                     |

| I <sub>M6</sub>                    | second stage driver current                                 |

| Itot                               | op amp total bias current                                   |

| k                                  | ratio of doublet pole and zero                              |

| k <sub>B</sub>                     | Boltzmann's constant 1.38 x 10 <sup>-23</sup> J/K           |

| K                                  | factor describing ratio of transconductances of first stage |

|                                    | input pair and mirror load transistors                      |

# LIST OF SYMBOLS (continued)

-  $\mu$ Cox (intrinsic transconductance parameter) K' KF flicker noise coefficient L, transistor device length peak percentage overshoot in step response Мp QΑ operational amplifier os output swing Laplace transfer function pole frequency p' p/w<sub>u</sub> (normalized pole location) power dissipation Pdiss · PM phase margin **PSRR** power supply rejection ratio Řο buffer output resistance SPICE analog circuit simulation software package slew rate step response settling time t<sub>s</sub> Vcm DC common mode input voltage small signal AC component of common mode input voltage v<sub>cm</sub> Vdmm. DC voltage measured on digital multimeter VDS transistor drain-source voltage VDSAT transistor drain-source saturation voltage  $v_{GS}$ transistor gate-source voltage Vi, Vo input and output voltages small signal AC component of input and output voltages rms noise voltage mean of normalized noise power

# LIST OF SYMBOLS (continued)

| Vos                               | offset voltage                                       |

|-----------------------------------|------------------------------------------------------|

|                                   | _                                                    |

| Vo <sup>+</sup> , Vo <sup>-</sup> | positive and negative output voltages                |

| $v_s$                             | voltage stepsize                                     |

| v <sub>s,B</sub>                  | transistor source-body voltage                       |

| v <sub>ss</sub> ,v <sub>DD</sub>  | DC power supply voltages                             |

| vss,vdd                           | AC small signal component of power supply voltages   |

| v <sub>t</sub>                    | transistor threshold voltage                         |

| v <sub>to</sub>                   | transistor threshold voltage with $V_{SB} - 0$       |

| w <sub>u</sub>                    | op amp unity gain frequency (radians/sec)            |

| w <sub>z</sub>                    | doublet zero frequency (radians/sec) '               |

| w                                 | transistor device width                              |

| $\mathbf{x}_{\mathbf{d}}$         | width of depletion region between transistor channel |

|                                   | pinch-off point and drain                            |

| β                                 | - μCox(W/L) (transconductance parameter)             |

| € .                               | step response error band factor                      |

| 7                                 | body effect parameter [1]                            |

| λ .                               | transistor output resistance parameter [1]           |

| $\mu$                             | electron (hole) mobility                             |

| $\phi_{\mathbf{F}}$               | Fermi level [1]                                      |

| $\tau_{\mathbf{u}}$               | - 1/w <sub>u</sub> (time constant)                   |

| r <sub>z</sub>                    | - 1/w <sub>Z</sub> (time constant)                   |

# 1.0 INTRODUCTION

# 1.1 Applications of op amps

Since their introduction in the mid-60's, monolithic operational amplifiers (or 'op amps') have become the most widely used type of analog integrated circuit [16]. The op amp is a general purpose amplifying device which is used in a closed feedback loop. The op amb together with its external feedback components forms an 'operational circuit' [12]. Part of the appeal of the op amp lies in the fact that such that the input-output characteristics. are ideally. relationship for the operational circuit becomes solely dependent on the external feedback components. Hence the transfer function becomes insensitive to integrated circuit process tolerances which result in variation of the op amp parameters. This desirable behaviour is most closely achieved as the op amp approaches the ideal of having infinite bandwidth, infinite input resistance and zero output and resis ince. By only varying the external feedback components then, the operational circuit can be made to perform various analog signal processing functions such as precision gain, inversion, addition, subtraction, integration, differentiation and even nonlinear operations such as exponentiation. This, together with its low cost and small size due to integration, have brought the op amp into use in countless applications [17].

Because of the economic advantages of implementing both digital and analog functions on the same chip, it is desirable to realize op amps in CMOS. CMOS is the technology of choice for digital circuits, resulting in lower power dissipation and higher circuit densities compared to both NMOS and bipolar implementations [20]. Analog functions requiring op amps are often needed for interfacing digital systems to the outside world. Some of these functions include filtering, voltage comparison, generation of reference voltages and the sample and hold function. Improvements in process technology now allow these analog functions to be implemented on the same chip as the digital circuitry resulting in more cost effective products [13]. Examples of subsystems in which this has occurred are A/D converters, digital signal processors and PCM voice encoders.

Using CMOS for analog circuits instead of the traditional bipolar implementation shows both advantages and disadvantages. The disadvantages are the lack of a floating diode structure, higher low-frequency noise, and lower transistor transconductance by typically an order of magnitude for the same bias current [18]. This last fact results in order of magnitude higher DC offsets, increased temperature sensitivity and lower gain. The typical CMOS op amp gain is 5000. Versus a minimum of 50,000 for the common '\( \mu A741 \) bipolar op amp.

Some of the advantages of CMOS are its greater circuit density (op amps are 3-5x smaller in area [18]), its ability to implement a good switch and the very high input resistance of its transistors. The latter two facts allow the use of switched capacitor techniques for

reducing the high noise and offset levels of op amps [13]. Switched capacitors can also simulate large resistance values which doubt normally be integrated due to area constraints. Because of this, switched capacitor filters are a common application for CMOS op amps [13].

1.3 Two categories of op amp

Because CMOS op amps are usually used within integrated systems, their loads are often well-defined and purely capacitive with a value of only a few picofarads. Hence these 'internal' op amps [1] do not require the usual additional stage which provides a low output resistance. In contrast, a stand-alone op amp [1] needs an output stage because it is required to drive variable loads with capacitance of up to several hundred picofarad and resistance as low as a few thousand ohms. Thus, the output resistance of the internal CMOS op amp is typically several hundred thousand ohms while that of a stand-alone op amp such as the  $\mu$ A741 is 75 ohms.

1.4 Stability and compensation of op amps

It is essential that the op amp be capable of stable operation in a closed-loop feedback configuration. In the time domain this translates into a desirable transient response such as a step response with little overshoot or ringing and fast settling. In the frequency domain stability implies a flat passband with little peaking of the frequency characteristic (assuming the most simple application as an amplifier -

see figure 1.1) [19]. Op amp compensation aims at shaping the open-loop frequency response such that in the closed-loop feedback configuration the desired stability is achieved. Basic feedback theory [14] indicates that the total phase shift of the signal through the loop (i.e. the amplifier with its feedback circuit) must not exceed 180° for frequencies where the loop gain is still greater than unity. (Note here that the additional 180° due to inversion within the op amp is not included). A measure of the degree of stability is given by the 'phase margin' which is the amount by which the phase shift falls short of the 180° limit at the unity gain frequency. Generally, a higher phase margin results in less overshoot and ringing of the closed-loop transient response and less peaking of the frequency response.

The frequency response of the uncompensated op amp has closely spaced poles introduced by parasitics in each stage [19]. Each pole contributes a gradually increasing phase shift of up to 90° for frequencies above approximately ten times the pole frequency. The closed-loop feedback circuit with an uncompensated op amp is unstable because the op amp's closely spaced poles cause its phase shift to reach the 180° limit for greater than unity gain. The role of the compensation is to introduce a dominant pole at low frequency to roll off the gain characteristic such that the unity gain frequency occurs at a frequency lower than the next nondominant pole. A positive phase margin is then assured (see figure 1.2).

The correspondence between phase margin and closed-loop response is based on the assumption of a single nondominant pole. For this simple case the nondominant pole location determines the closed-loop frequency

AcL(f)

(in dB)

AcL(0)

fu

log f

(a)

Figure 1.1 Typical closed-loop frequency response for non-inverting amplifier application.

(þ)

(a) circuit configuration (b) frequency response

margin itself can be used to predict the closed-loop responses. However, the actual op amp usually has additional poles and zeros at higher frequency which affect the open-loop response as shown in figure 1.2. In this case the correspondence between phase margin and closed-loop response is only an approximation. The accuracy of the approximation improves as the higher order poles and zeros are located further from the second pole (see section 3.1.2).

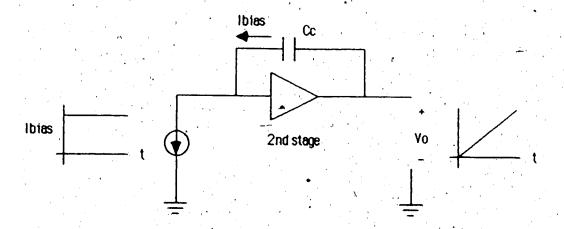

The most basic compensation method for internal CMOS op amps is achieved by a capacitor placed across the input and output of the second gain stage [1]. The Miller multiplication effect results in a large shunt capacitance at the first stage output which, together with the high output resistance gives the required dominant pole for compensation. This simple technique works better in bipolar implementations than in CMOS. The phase margin is degraded due to the parallel signal path to the output through the compensation capacitor and this effect is more evident in CMOS due to the lower device transconductance. Using a buffer or resistor in series with the capacitor are techniques which have appeared in the literature [4,5] for solving this problem.

# 1.5 Thesis content

This thesis investigates four compensation techniques used in internal CMOS op amps. The four techniques are:

- 1) Susing a single Miller capacitors

- 2) using a series buffer with the capacitor;

Figure 1.2 Open-loop frequency response

(a) circuit configuration

(b) magnitude and phase response

- 3) using a series resistor with the capacitor; and

- 4) using a single Miller capacitor on a separate compensation stage.

While the first three methods are widely reported in the literature, the fourth method is new to the author's knowledge. Instead of the compensation capacitor being placed across the second stage for the Miller multiplication effect, it is placed across a separate matched 'compensation' stage. Because the compensation capacitor is isolated from the output node the signal feedthrough problem is not observed. Also, as opposed to the simple capacitor compensation, the nondominant pole location becomes independent of the load capacitance. These facts result in superior compensation.

It was desired to evaluate the different compensation techniques as to their achievable performance. Partly due to the different size of compensation capacitor required and partly due to the different circuit architecture, the noise power dissipation, power supply rejection and required die area can differ for a given transient response depending on the technique which was used. The simple capacitor compensation was used as a benchmark against which the other techniques were compared. The compensation was aimed at obtaining a desirable transient response and especially a reduction of the settling time (op amp settling time is one of the factors which limits the input frequency range of switched capacitor filters). Only 100% feedback resulting in unity gain was considered because this configuration presents the most stringent compensation requirement.

Designs based on a common set of design specifications were generated using all four techniques. The results of SPICE simulations

on these designs are given. The simple capacitor compensation and the separate stage compensation designs were integrated and measurements on a sample of 5 chips are given.

One chapter is devoted to the general design of internal CMOS op amps. Seeking an optimum design can become quite a complicated matter as there are approximately twelve specifications which may have to be met and about the same number of independent circuit parameters which can be adjusted. The performance areas are often interrelated which can result in conflicting design requirements. A systematic design method is presented with the aim of providing the details of the design procedure which most texts fail to include. It is hoped that the information will be of use to other graduate students requiring the implementation of op amps in their research.

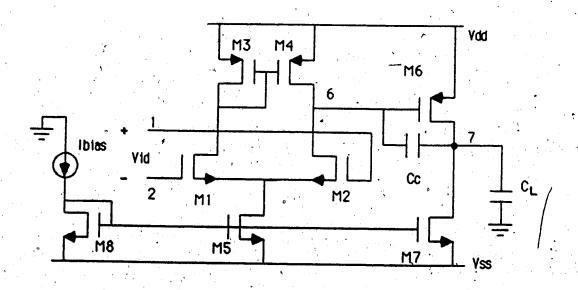

# OP AMP DESIGN

2. Basic two-stage architecture

The design methods of this chapter are based on the two-stage architecture of figure 2.1. The first stage consists of the differential input pair M1/M2 driving the current mirror load M3/M4 with M5 providing a constant current bias. As well as giving gain, this stage provides differential to single-ended conversion with good rejection of common mode signals. The second gain stage consists of M6 in a common source configuration with M7 as a constant current source load. The compensation capacitor Cc is used to provide the necessary gain rolloff for stability and is connected across the second stage for the Miller multiplication effect. (For a discussion of the basic blocks which make up the amplifier see [1]).

# 2.2 Performance parameters

The op amp is designed to meet a number of performance specifications. The following section defines these parameters, describes their significance and gives their design equations corresponding to the two stage architecture.

# 2.2.1 Gain

As mentioned in chapter 1 the op amp connected in a negative feedback configuration offers many advantageous characteristics. It is important that the gain of the op amp is high as these characteristics

Figure 2.1 Two stage architecture

Figure 2.2 Small signal model of two stage OA

will more closely approach the ideal as the gain increases. The small signal model of figure 2.2 can be used for calculating the DC gain to be [1, p. 742]:

$$Av(0) - (g_{m1} R_{24}) (g_{m6} R_{67})$$

(2.1)

where the subscripts refer to the transistor designations of figure 2.1 and  $R_{24} - R_2 || R_4$ ,  $R_{67} - R_6 || R_7$ . The output impedance of each transistor is dependent on bias current I and device length [1] i.e.

$$R = \frac{1}{I\lambda} \quad \text{where } \lambda = \frac{1}{L_{\text{eff}}} \quad \frac{dX_d}{dV_{DS}}$$

(2.2)

and  $\frac{dX_d}{dV_{DS}}$  is a factor dependent on  $V_{DS}$ . ( $\lambda$  is typically 0.01 V<sup>-1</sup> for

for NMOS and  $0.03 \text{ V}^{-1}$  for PMOS).

# 2.2.2 Gain-Bandwidth product (GBW)

Figure 2.3 shows the op amp's frequency response characteristic based on the small signal model of figure 2.2. This characteristic is close to the usually required fully compensated OA characteristic. The dominant pole  $p_1$  can be shown  $\{1, p. 549\}$  to be set by the compensation capacitor as follows:

$$p_1 = -\frac{1}{\chi_{g_{m6} R_{67}) Cc R_{24}}}$$

(2.3)

the second stage, is seen in parallel with the first stage output impedance. The gain thus rolls off by 3dB at p<sub>1</sub> and continues to roll off at a -20dB/decade rate for higher frequencies. It can be shown [12] that the gain-bandwidth product for a noninverting feedback configuration is equal to the GBW of the op amp itself. Hence this

Figure 2.3 Frequency Response

Figure 2.4 Differential pair transfer function

figure of merit is useful for calculating the bandwidth of the feedback circuit depending on the overall gain. From (2.2) and (2.3) the GBW of the two stage op amp is seen to be:

GBW - Av(0)p<sub>1</sub> -

$$\frac{g_{m1}}{Cc}$$

(2.4)

It should also be noted that in the interval where the op amp gain rolls off at 20dB/decade its gain-frequency product is constant. Hence the unity gain-frequency  $\mathbf{w}_{\mathbf{u}}$  is equal to the GBW.

# 2.2.3 Phase margin (PM)

For stable operation in a feedback configuration the phase shift of the op amp must be sufficiently less than  $180^{\circ}$  at the unity gain frequency. This phase margin is indicated on figure 2.3 and is usually required to be at least  $^{\circ}45^{\circ}$  (preferably  $60^{\circ}$ ) to avoid excessive ringing and provide acceptable settling times. The phase margin is degraded by the nondominant pole  $p_2$  and the right hand plane zero z. From the small signal model of figure 2.2  $p_2$  and z are derived as [1, p. 549]:

$$p_2 = \frac{g_{m6}}{C_T} \tag{2.5}$$

$$z = \frac{g_{\text{m6}}}{Cc} \tag{2.6}$$

(under the assumptions Cc,  ${

m C}_{L}>>{

m Cp}_{1}$ ).

From (2.6) and (2.4), the location of the zero relative to  $\mathbf{w}_{\mathbf{u}}$  is given by

$$\frac{z}{w_{11}} = \frac{g_{m6}}{g_{m1}} \tag{2.7}$$

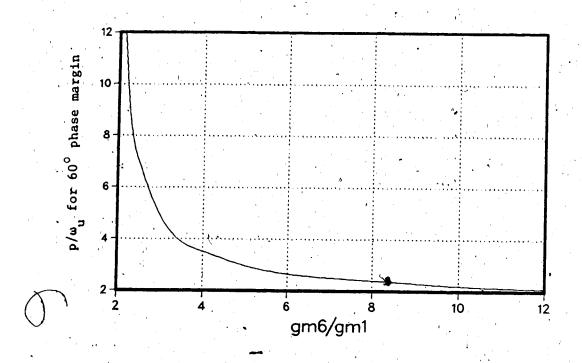

Thus the phase margin degradation due to the RHP zero is dependent on this transconductance ratio. Taking this into account, for a  $60^{\circ}$  phase margin the required location of  $p_2$  relative to  $w_u$  can be approximated by:

$$\frac{|P_2|}{w_u} = \frac{1}{\tan[30 - \tan^{-1}(\frac{g_{m1}}{g_{m6}})]}$$

(2.8)

This is plotted in figure 2.5. From the figure, one sees that with

$$\frac{|\mathbf{p}_2|}{|\mathbf{w}_1|} = 3 \tag{2.9}$$

a  $60^{\circ}$  phase margin should be guaranteed for values of  $\frac{g_{m6}}{g_{m1}} \ge 6$ . However, this required value of  $|p_2|/w_u$  may have to be increased in order to account for additional phase shift introduced by parasitics in the first stage which have not been considered in the approximate analysis.

# 2.2.4 Slew Rate (SR)

The slew rate limit of the op amp is the maximum rate of change of its output voltage. For large input signals the input differential stage leaves its linear operating region and appears as a constant current source of value Ibias (see figure 2.4). As shown in figure 2.6, the second stage with compensation capacitor will integrate this current and result in a varying output voltage of slope

$$\frac{dV_0}{dt} - \frac{Ibias}{Cc} - SR \qquad (2.10)$$

The slew rate must be high enough to ensure a fast settling response to large input steps when the op amp is used in pulse mode. Also, the slew rate will limit the maximum output amplitude of a sine wave for a given frequency [21].

Figure 2.5 Effect of transconductance ratio on required nondominant pole location

Figure 2.6 Model for calculating SR

Figure 2.7 Circuit configuration for testing PSSR

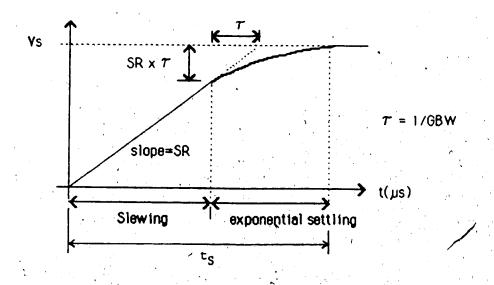

# 2.2.5 Settling time $(t_S)$

The settling time refers to the time required for the op amp in a feedback configuration to settle to within a certain error band of its final output level in response to a step input. Settling times referred to in this thesis will be for a unity gain noninverting feedback configuration and an error band of 0.1%. This is the level of accuracy deemed suitable for switched capacitor signal processing applications [2]. Fast settling is very important for this application as it will set the limit on the upper frequency range of the signals to be processed.

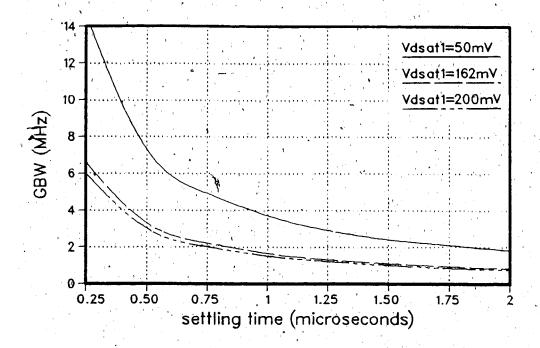

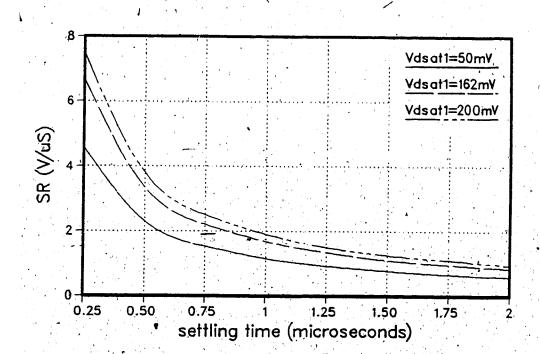

The step response for a feedback configuration will start with a slewing period and end with the op amp in linear operation. Hence both the GBW and SR will have an effect on the settling time. Under the assumption of an OA with an integrator frequency response, the period of linear operation gives exponential settling. Under these conditions, an estimate of the GBW and SR requirements for a given t<sub>S</sub> and voltage step can be derived (see appendix 1).

The results for a one volt step are summarized on the graphs of figure 2.8. The different curves correspond with different values of  $V_{DSAT}$  for the input transistor pair (note that  $V_{DSAT}$  must be kept low for low offset - see section 2.2.9). For a 1.V step, the exponential settling model shows the optimum value of  $V_{DSAT}$  to be, about 162 mV.

The actual settling time will be longer than predicted by the model due to the ringing caused by the nondominant pole and zero. For an OA with  $60^{\circ}$  phase margin the settling time for a 1 V step has been seen to be typically 20% longer than predicted (see table 3.1).

Figure 2.8 Required GBW and SR for a given settling time ts.

## 2.2.6 Input common mode range (ICMR) and output swing (OS)

Both these specifications define the operating range of the op amp, outside of which its characteristics become degraded. As a common mode input signal approaches  $V_{SS}$ , M1 and M2 will eventually leave pinchoff causing the gain to drop. Similarly, as the output voltage approaches  $V_{SS}$ , M6 will eventually leave pinchoff with the same result. It can be shown (appendix 2) that the -ICMR and -OS specs set upper limits on  $V_{DSAT3}$  as follows:

$$(-ICMR): V_{DSAT3} \le (Vi_{min} - V_{SS}) - |V_{t3}| + |V_{t1}|$$

(2.11)

$$(-0S): V_{DSAT3} \le (Vo_{min} - V_{SS})$$

(2.12)

The output swing requirement will normally take precedent as body effect causes  $|V_{t1}| > |V_{t3}|$  by 1 V typically. (2.11) can thus easily be met with  $Vi_{min} - V_{SS}$  i.e. -ICMR extends to  $V_{SS}$ . The aspect ratio of M3 and M4 is then:

$$(W/L)_{3} \geq \frac{I_{5}}{K_{D}' (V_{DSAT3max})^{2}}$$

(2.13)

A positive going common mode input eventually causes M5 to leave pinchoff causing first stage bias current to roll off and the SR to be degraded. A positive going output signal eventually causes M7 to leave pinchoff. Now +ICMR and +OS set limits on VDSAT5 as follows (appendix 2):

$$(+ICMR): V_{DSAT5} \leq (V_{DD} - V_{max}) - |V_{GS1}|$$

$$\leq (V_{DD} - V_{max}) - \left[\sqrt{\frac{I_5}{kp'(W/L)_1}} + |V_{t1}|\right]$$

$$(2.14)$$

$$(+OS): V_{DSAT5} \leq (V_{DD}-V_{o_{max}})$$

(2.15)

Once V<sub>DSAT5max</sub> is decided (W/L)<sub>5</sub> is found:

$$(W/L)_{5} \ge \frac{2 I_{5}}{K_{p'}(V_{DSAT5max})^{2}}$$

(2.16)

From (2.14) above, it is seen that the +ICMR falls short of  $V_{DD}$  by at least  $V_{GS1}$ , (~ 1.2 V typically for  $V_{\rm t}$  = 0.9 V). Also, to avoid an unreasonably large value of (W/L)<sub>5</sub>,  $V_{DSAT5}$  cannot be chosen too small. Thus +ICMR can only be within 1.5 - 2 V of  $V_{DD}$ .

## 2.2.7 Power supply rejection ratio (PSRR)

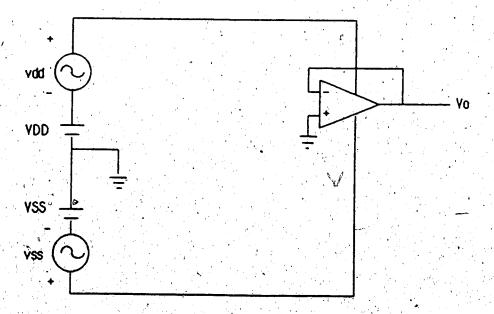

The PSRR is a measure of the ability of the op amp connected in a feedback configuration to reject signals on the power supplies. This parameter is quite important for CMOS op amps since they are likely to operate in a system which combines both analog and digital circuitry on the same chip. For a configuration such as in figure 2.7 the component of Vo due to either vdd or vss (ripple on the power supply lines, say) can be shown [15] to be given by:

$$\frac{\text{vo}}{\text{vdd}} = \frac{\text{Av}_{\text{DD}}}{\text{Av}} \qquad \frac{\text{vo}}{\text{vss}} = \frac{\text{Av}_{\text{SS}}}{\text{Av}}$$

(2.17)

for frequencies up to the unity gain frequency. Here  $\mathrm{Av}_{\mathrm{DD}}$  and  $\mathrm{Av}_{\mathrm{SS}}$  are the gains to the output from the power supplies. Hence the rejection ratios are defined as:

+PSRR(f) =

$$\frac{Av(f)}{Av_{DD}(f)}$$

and -PSRR(f) =  $\frac{Av(f)}{Av_{SS}(f)}$  (2.18)

For the two-stage architecture of figure 2.1 the +PSRR will typically be much higher (say 20dB) than the -PSRR. Also it remains flat out to higher frequencies before beginning to roll off. The explanation follows.

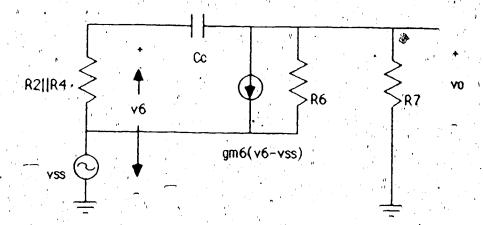

Because the diode connected transistor M3 is biased at a constant current, its drain will track  $V_{SS}$ . Since the currents in M3 and M4 are equal and their gate voltages are equal, their drain voltages must also be equal hence the first stage output will also track  $V_{SS}$ . The model of figure 2.9 can then be used to derive  $Av_{SS}(w)$  shown in figure 2.10. At low frequencies, the circuit simplifies to the voltage divider  $R_6$  and  $R_7$ . As the frequency approaches the dominant pole of the OA, the compensation capacitor acts as a short, M6 looks like a diode connected transistor and the supply signal appears almost undiminished at the output. The result is that -PSRR(w) follows Av(w) quite closely, as shown in figure 2.11.

The +PSRR can be calculated using the model of figure 2.12. The DC gain from the positive supply can be shown to be

$$Av_{DD}(0) = \frac{R_6}{R_6 + R_7} - g_{m6} (R_6 | | R_7) T_1$$

(2.19)

where  $T_1$  is the transfer function to the output of the first stage and can be shown to be approximately:

$$T_1 \approx \frac{1}{2 g_{m3} R_5}$$

(2.20)

(2.19) shows that the output of the first stage actually helps to cancel the output component due to the resistance divider  $R_6$  and  $R_7$ . Hence the noninfinite rejection of the first stage can cause +PSRR(0) to be much higher than -PSRR(0). However (2.20) does not take into account 1st stage device mismatches and in fact  $T_1$  can be much larger than expected. Hence the second component of (2.19) may predominate causing the +PSRR to be degraded.

AvDD(w) as shown in figure 2.13 can be derived from the model of.

Figure 2.9 Model for -PSSR calculations

Figure 2.10 Frequency response from negative supply

Figure 2.11 Negative PSRR

Ġ,

Figure 2.12 Model for +PSSR calculations

Figure 2.13 Gain from positive supply

Figure 2.14 +PSRR(w)

Figure 2.15 +PSRR(w) assuming infinite first stage rejection.

figure 2.12. At high frequencies Cc appears as a short causing the dominant output component to be due to the resistance divider consisting of the diode connected transistor  $(1/g_{m6})$  and  $R_7$ . The frequency of which this occurs is seen to be greater than the dominant pole of the op amp. +PSRR(w) is then as shown in figure 2.14. From (2.19) it is seen that if the first stage had infinite rejection +PSRR would be approximately equal to -PSRR at low frequencies. However it would remain flat to much higher frequencies as shown in figure 2.15.

In summary, then, the +PSRR is superior to the -PSRR mainly because as the frequency increases and Cc makes M6 appear as a diode connected transistor, the gain from the positive supply will roll off while the gain from the negative supply increases. If the complementary architecture with NMOS inputs were used the -PSRR would be superior as the diode connected transistor would then be the one connected to the positive supply.

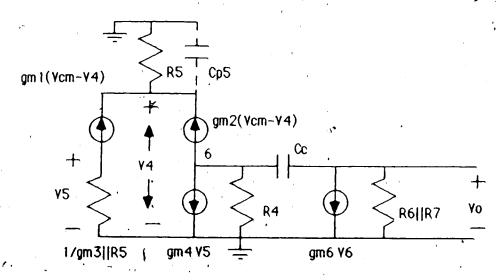

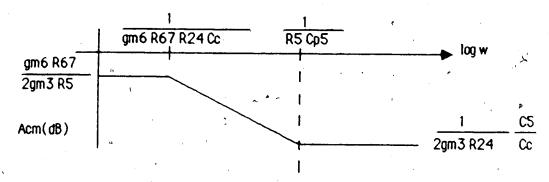

## 2.2.8 Common mode rejection ratio (CMRR)

The CMRR is defined as:

$$\begin{array}{c}

\text{CMRR} - \underline{\text{Av}} \\

\underline{\text{Acm}}

\end{array} \tag{2.21}$$

where Acm is the gain for a common mode signal at the op amp inputs. This parameter is especially relevant to applications involving a noninverting feedback configuration. A unity gain buffer, for example, with input  $v_{\rm cm}$  has an output error:

$$\frac{\mathbf{v_o} - \mathbf{v_{cm}}}{\mathbf{v_{cm}}} \simeq \frac{1}{\mathsf{CMRR}} - \frac{1}{\mathsf{Av}}$$

(2.22)

hence the importance of the high CMRR.

Figure 2.16 Model for CMRR calculation

Figure 2.17 Common mode gain frequency response

Figure 2.18 CMRR frequency response .

The model of figure 2.16 can be used to calculate the CMRR of the 2 stage architecture. The DC transfer functions to the first stage output can be shown to be:

$$\frac{\mathbf{v}_6}{\mathbf{v}_{cm}} \approx \frac{1}{2g_{m3}R_5} \tag{2.23}$$

and the overall common mode gain at DC;

$$Acm(0) = \frac{v_7}{v_{cm}} = \frac{g_{m6}R_{67}}{2g_{m3}R_5}$$

(2.24)

which can be typically -6dB.

The overall rejection can be improved by increasing the transconductance of the current mirror load and by increasing the length of M5.

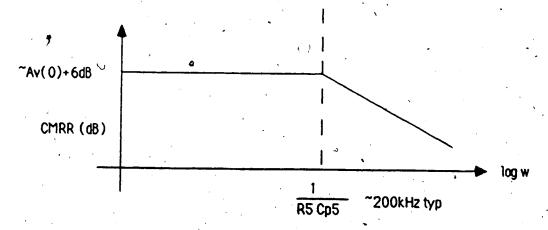

The frequency response of Acm is set by Cc which introduces a low frequency pole, and the parasitic Cp<sub>5</sub> associated with source-substrate capacitance which by shunting M5 introduces a high frequency zero. The result is as shown in figure 2.17. Because Acm rolls off at the dominant pole frequency of the op amp, the CMRR will stay flat out to quite high frequency (see figure 2.18).

### 2.2.9 Voltage offset and noise

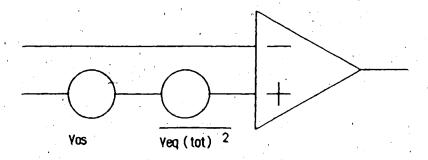

with no input signal, a voltage offset and noise appear at the op amp output. The voltage offset can be considered a type of low frequency noise as it drifts with time (aging), temperature or supply voltage. The effect of these additive error sources on an operational circuit can be modelled by using equivalent input sources in series with the terminals of a noiseless and offset-free op amp as shown in figure 2.19.

Figure 2.19 Representation of offset voltage and noise

Figure 2.20 Second stage operating point

Figure 2.21 Spectral noise density example

Vos is defined as the differential input voltage (with zero common mode voltage) required to force the output voltage to be zero. For the two stage architecture, the offset can be divided into systematic and random contributions. The systematic contribution results from an imbalance in the bias currents of M6 and M7. Roughly speaking the gate voltage of M6 must be set such that the current of M6 takes up all the current of M7. This sets the following requirement on the W/L ratios:

$$\frac{(W/L)_{6}}{(W/L)_{3}} - 2 \frac{(W/L)_{7}}{(W/L)_{5}}$$

(2.25)

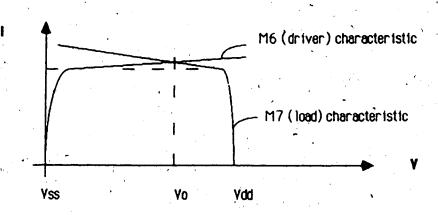

In actual fact this will still result in some imbalance due to the different output impedances of PMOS (M7) and NMOS (M6) devices. Figure 2.20 shows the output voltage as the intersection of the characteristic curves of the output devices. It can be seen from the figure that because the PMOS device has typically 1/3 the output impedance of the NMOS device either the M6 characteristic must be raised or the M7 characteristic lowered to bring Vo midway between VDD and VSS. This corresponds to slightly increasing (W/L)6 relative to (W/L)3 or decreasing (W/L)7 relative to (W/L)5. These adjustments can be made during computer simulation. In practical terms the adjustment is usually not required as the resulting input offset is typically less than 1 mV.

The random offset component is due to threshold mismatches or W/L mismatches and is usually on the order of several mV. It can be shown [1, p. 745] to be given by:

Vos =

$$\Delta V_{t(1-2)} + \Delta V_{t(3-4)} \frac{g_{m3}}{g_{m1}}$$

(2.26)

+  $\left(\frac{I}{g_{M}}\right)_{(1-2)} \left[\left(-\frac{\Delta W/L}{W/L}\right)_{(1-2)} - \left(\frac{\Delta W/L}{W/L}\right)_{(3-4)}\right]$

The contribution due to the threshold mismatch of the current mirror load is minimized by having a small  $g_{m3}/g_{m1}$ . The W/L mismatch contribution is reduced by having a small  $I/g_M$  ratio. This is ensured by operating the input transistors with  $(V_{GS}-V_r) \simeq 50-200$  mV.

The equivalent input noise voltage Vn can also be shown  $\{1, p. 750\}$  to be predominantly due to the inherent noise of the input pair if  $g_{m1}$  is made 2 or more times greater than  $g_{m3}$  and  $g_{m3}$  and  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  and  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  and  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made 2 or more times greater than  $g_{m3}$  is made

$$\frac{\overline{v_N^2}}{\Delta f} = \frac{2KF_p}{fW_1L_1Cox} + 4kT\left(\frac{4}{3g_{m1}}\right)$$

(2.27)

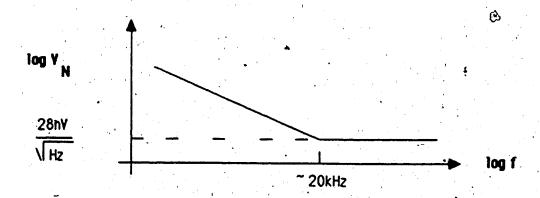

The first component is the 1/f or flicker noise and can be minimized by increasing the device area. The noise coefficient KF is strongly process dependent and is typically 2 or 3 times smaller for the PMOS as opposed to the NMOS device. The second component is due to thermal fibise and can be reduced by increasing  $g_{ml}$ .

A typical value for KF<sub>p</sub> might be 3 x  $10^{-12}$  V<sup>2</sup>pF [1]. Figure 2.21 then shows the spectral noise density for an 80 x 10 micron device (see design example) assuming KF<sub>p</sub>  $\simeq 3 \text{x} 10^{-12}$  V<sup>2</sup>pF, Cox  $\simeq$  .4 fF/ $\mu$ m<sup>2</sup>, I  $\simeq$  5  $\mu$ A, and K<sub>p</sub>' = 10  $\mu$ A/V<sup>2</sup>. Note that the flicker noise is dominant up to about 20 kHz.

To palculate the total equivalent input noise voltage for an operational circuit requires integration of the spectral density function (2.27) over the frequency range. For the above example, if the op amp is connected as a unity gain buffer and  $f_u \simeq 1$  MHz the total noise voltage is calculated to be Vn  $\simeq$  40  $\mu$ V. This sets

the lower limit on the minimum signal size which can be applied to the circuit.

#### 2.3 Typical Performance Parameters

Table 2.1 gives the expected performance specifications for a two-stage -CMOS internal op amp with PMOS inputs. Achievable performance in the areas of GBW, SR, die area and  $P_{diss}$  is highly dependent on  $C_{\rm I}$ . This will be further appreciated in the design example.

#### 2.4 Design

#### 2.4.1 Procedure

For simplicity, the op amp is designed to meet the following set of "primary" design specifications: PM, SR, GBW,  $\pm$ ICMR,  $\pm$ OS. The "secondary" specifications of Av(0), CMRR, PSRR, t<sub>S</sub> and P<sub>diss</sub> are then checked (usually by computer simulations) to see if they are acceptable. If they are not acceptable, it may be that the primary set of specifications is incompatible and needs to be revised. For instance, it can be shown [13, p. 225] that Av(0) and CMRR are fully determined by the GBW and SR. Similarly, t<sub>S</sub> and P<sub>diss</sub> are both determined by SR, GBW and PM.

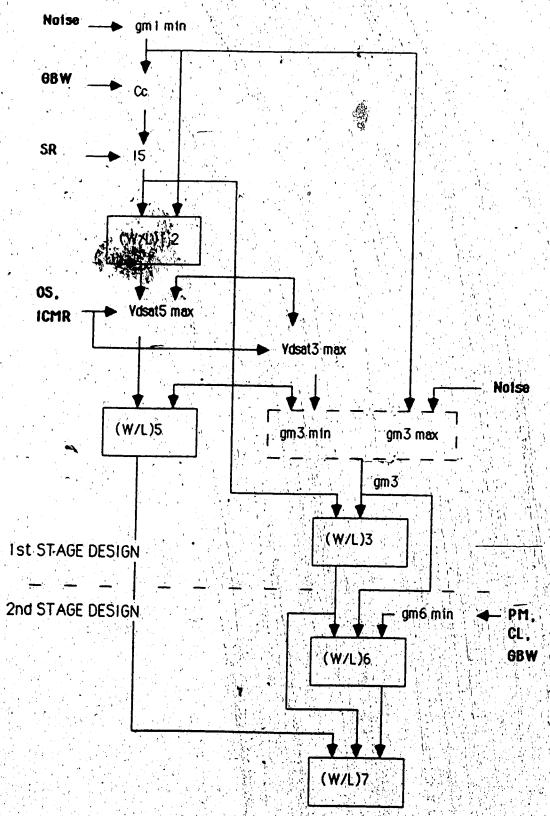

The list of design equations corresponding to the architecture of figure 2.1 is given in table 2.2. The order of calculations is summarized in the flowchart of figure 2.22. Bold items indicate performance parameters while items in square boxes are the final circuit values.

| SPEC                     | TYPICAL VALUES                                                 |

|--------------------------|----------------------------------------------------------------|

| Av(0)                    | $10^3 \sim 10^4$                                               |

| GBW                      | 1 - 10 MHz                                                     |

| SR                       | 2 - 20 V/μs                                                    |

| PM                       | 60°                                                            |

| t <sub>S</sub>           | $\leq 1 \ \mu s \ (0.18, 1 \ V \ step, C_L=5 \ pF)$            |

| +ICMR<br>-ICMR           | $v_{DD}$ -1.5 $v$ $v_{SS}$                                     |

| +0S<br>-0S               | V <sub>DD</sub> -0.5 V<br>V <sub>SS</sub> +0.5 V               |

| +PSRR (DC)<br>-PSRR (DC) | 100 dB<br>80 dB                                                |

| CMRR (DC)                | 80 dB                                                          |

| OFFSET                   | ≤ 10 mV                                                        |

| NOISE                    | $\leq \frac{100 \text{ nV}}{\sqrt{\text{Hz}}} \text{ @ 1 kHz}$ |

| Pdiss                    | 0.5 - 10 mW                                                    |

| DIE AREA                 | ≤ 100,000 micron <sup>2</sup>                                  |

| LOAD                     | 1 - 100 pF                                                     |

Table 2.1 Typical performance specifications for a 2-stage CMOS op amp (PMOS input configuration)

| Performance<br>parameter | Design equations                                                                              |

|--------------------------|-----------------------------------------------------------------------------------------------|

| PM ≥ 60°                 | $\frac{g_{m6}}{C_L} \ge 3 w_u^*$                                                              |

| SR                       | I <sub>5</sub> - SR C <sub>L</sub>                                                            |

| GBW                      | $g_{m1}$ - GBW $C_L$                                                                          |

| -ICMR                    | $V_{DSAT3} \leq (Vi_{min} - V_{SS}) -  V_{t3}  +  V_{t1} $                                    |

| -os                      | V <sub>DSAT3</sub> ≤ Vo <sub>min</sub> - V <sub>SS</sub>                                      |

| +ICMR                    | $V_{DSATS} \le (V_{DD} - Vi_{max}) - \left( \sqrt{\frac{I_5}{Kp'(W/L)_1}} +  V_{t1}  \right)$ |

| +OS                      | V <sub>DSAT5</sub> ≤ V <sub>DD</sub> - Vo <sub>max</sub>                                      |

| Noise<br>and             | $g_{m3} \leq 1/2 g_{m1}$                                                                      |

| Offset                   | $L_3 \ge 2 L_1$                                                                               |

Table 2.2 Design Equations

<sup>\*</sup> see notes of section 2.4.1

Figure 2.22 Design flowchart

Note the following:

1. It is advantageous to choose  $g_{ml}$  at the lowest limit set by thermal noise (see equation (2.27)). From (2.4) it is seen that for a given GBW, this results in the smallest value for Cc and hence reduced area requirements. Also, it means reduced  $P_{diss}$  and higher gain since a smaller first stage current is required for a given SR.

The smaller value of  $g_{m1}$  also results in a higher frequency RHP zero. Since  $g_{m6}$  is fixed by the PM requirement (see (2.5)), a smaller  $g_{m1}$  means a larger transconductance ratio. From (2.7) then, it is seen that the RHP zero moves further from  $w_u$  resulting in an improved phase margin.

If a large  $g_{ml}$  is required giving  $g_{m6}/g_{ml} < 6$ ,  $p/w_u-3$  will be insufficient for a  $60^{\circ}$  phase margin (see figure 2.4). A compensation technique from the next chapter should be used since otherwise a large  $p/w_u$  ratio may be required resulting in much larger second stage current (see next point). An indication that  $g_{m6}/g_{m1} < 6$  is given by  $Cc > C_L/2$  since from (2.5) and (2.4) it can be written

$$\frac{g_{\text{mb}}}{g_{\text{m1}}} = 3 \frac{c_{\text{L}}}{c_{\text{C}}}$$

$$(2.28)$$

3. For minimum second stage current the ratio g<sub>m3</sub>/g<sub>m1</sub> should be as large as possible. Because M3, M4 and M6 have a common gate voltage we can write:

Hence from (2.29) the larger  $g_{m3}/g_{m1}$  the smaller  $I_6$ . As indicated in the design flowchart,  $g_{m3}$  usually has an upper limit of  $g_{m3} - g_{m1}/2$  to prevent excess noise and offset. However if the lower limit set by ICMR and OS exceeds this there will necessarily be some performance tradeoff. If the noise limit for  $g_{m3}$  is used and  $p/w_{u}-3$  (2.29) becomes  $I_6 - 3$  SR  $C_1$

4. From (2.2) it is seen that transister output resistance is directly proportional to the device length. Hence the gain requirement usually sets a lower limit on the length.

L ≥ 10 micron is suggested. The length of matched devices should be equal for best matching.

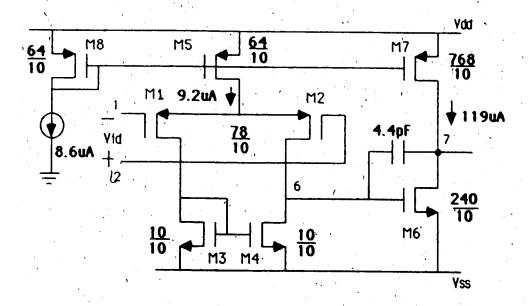

#### 2.4.2 Example

The following design example is for a conventional two stage op amp which was submitted for fabrication using Northern Telecom's 5 micron process. Test results on this op amp are given in chapter 4. Its performance was used as a benchmark against which other designs appearing in this thesis were compared. The chosen design specifications are given in table 2.3. Note that a larger than typical load capacitance was chosen because of the requirement that the op amp would have to drive off chip loads for testing.

The calculations follow the design flow of figure 2.22. Northern Telecom's process parameters were taken from [3]. All device lengths were taken as 10 micron for adequate gain and best matching. Note that to avoid accumulation of error, whenever a transistor dimension is

| GBW              | 1 MHz                  |

|------------------|------------------------|

| SR               | 2 V/μs                 |

| PM .             | ≥ 60°                  |

| $c_{\mathbf{L}}$ | 20 pF                  |

| +ICMR            | v <sub>DD</sub> - 2 v  |

| -ICMR            | v <sub>ss</sub>        |

| +os              | v <sub>DD</sub> -0.5 v |

| -0 <b>S</b>      | V <sub>SS</sub> +0.5 V |

| Av(0)            | ≥ 5000                 |

|                  |                        |

Table 2.3 Specifications for the design example

rounded off to the nearest micron, the aspect ratio is recalculated for use in later calculations,

1. Phase margin requirement:

$$8_{m6(min)} = {}^{3C_{L}} w_{u}$$

(2.31)

- 3 (20 pF) (2 1 MHz) - 377  $\mu$ A/V

$g_{\rm m6}$  = 355  $\mu A/V$  was used in the implemented design and so is chosen here.

### 2. Noise requirement:

A transconductance ratio of about 10 was deemed as resulting in a satisfactory noise level. Hence  $g_{\rm m1}=27.6~\mu A/V$  corresponding with  $g_{\rm m6}/g_{\rm m1}=12.86$  was chosen.

3. Gain-Bandwidth requirement:

Cc -

$$\frac{g_{m1}}{GBW}$$

-  $\frac{27.6 \ \mu A/V}{2\pi}$  - 4.4 pF (2.32)

4. Slew rate requirement:

$$I_5$$

- Cc SR - 4.4 pF (2 V/ $\mu$ s) - 8.8  $\mu$ A (2.33)

$$(W/E)_1 - \frac{g_{m1}^2}{I_5 K_p} - \frac{(27.6)^2}{8.8 (9.75)} - 8.88$$

(2.34)

$L_1$  (DRAWN) - 10  $\mu$ m

L<sub>1</sub> (ACTUAL) = (10 - 1.2)

$$\mu$$

m = 8.8  $\mu$ m

()

W<sub>1</sub> (DRAWN) = 8.88 (8.8  $\mu$ m) = 78.14 = 78  $\mu$ m

So final values are

$$(W/L)_1 - \frac{78}{8.8} - 8.86$$

(2.35)

and

$$g_{m1} - \sqrt{2IK_p'(W/L)_1} - \sqrt{8.8 (9.75) \frac{78}{8.8}} - 27.6 \mu A/V$$

Note that to have an acceptable level of 1/f noise,  $W_1$  and  $L_1$  may have to be scaled up, to get a larger transistor area (see section 2.2.9).

Negative going ICMR and OS requirement:

(-ICMR):

$$v_{DSAT3} \le (v_{in_{(min)}} - v_{SS}) - v_{c3} + |v_{c1}|_{max}$$

(2.36)

where

$$V_{cl(max)} = V_{c0} + \gamma(\sqrt{2\phi_F} + V_{SB} - \sqrt{2\phi_F})$$

(2.37)

= 0.9 + 0.634 ( $\sqrt{.612 + 9} - \sqrt{.612}$ ) = 2.4 V

' (here  $V_{SB}$  is estimated)

so

$$V_{DSAT3} \le 0 - 0.9 + 2.4 - 1.5 V$$

(-05):

$$V_{DSAT3} \le Vo^{*}_{(max)} - V_{SS} = 0.5 \text{ V}$$

(2.38)

Hence the output swing requirement on  $V_{\mbox{DSAT3}}$  overrides and

$$(W/L)_3 \ge \frac{I_5}{K_n'(V_{DSAT3})^2} - \frac{8.8}{30(0.5)^2} - 1.17$$

(2.39)

choose L<sub>3</sub> (DRAWN) -  $10 \mu m$

so

$$L_3$$

(ACTUAL) - 10 - 1.4 - 8.6  $\mu$ m

and W<sub>3</sub> (DRAWN) - 1.17 (8.6) - 10.06  $\mu$ m, say 10  $\mu$ m

this gives

$$g_{m3} - \sqrt{2I_3 K_n' (W/L)_3}$$

(2.40)

-  $\sqrt{2 (4.4) 30 (1.163)} - 17.5 \mu A/V$

and

$$\frac{g_{m3}}{g_{m1}} - \frac{17.5}{27.6} - 0.63$$

For noise and offset considerations this ratio should not be increased (see (2.26)) so  $(W/L)_3$  cannot be increased further. (Also, in retrospect,  $L_3$  should have been chosen  $L_3 \geq 2L_1$  for reduced 1/f noise contribution from M3 and M4 [1, p. 750]. This is overlooked here in order to be in agreement with the dimensions of the circuit submitted for fabrication.

6. Knowing  $g_{m6}$ ,  $g_{m3}$  and  $(W/L)_3$ ,  $(W/L)_6$  can be derived from the fact that M3 and M6 have a common gate voltage. Hence

$$\frac{g_{m6}}{g_{m3}} - \frac{\beta_6}{\beta_3} \frac{V_{DSAT}}{V_{DSAT}} - \frac{W_6}{W_3}$$

(2.41)

if  $L_6$  -  $L_3$  - 10  $\mu m$

therefore  $W_6 - 10 = \frac{355}{17.5} = 203 \ \mu m$

Positive going ICMR and OS:

(+ICMR):

$$V_{DSAT5} \leq (V_{DD} - V_{1(max)}) - \left(\sqrt{\frac{I_{5}}{Kp'(W/L)_{1}}} + V_{c1(min)}\right)$$

(2.42)

where

$$V_{tl(min)} - V_{tl(0)} + \gamma (\sqrt{2\phi_F + V_{SB}} - \sqrt{2\phi_F})$$

(2.43)

$$= 0.9 + 0.634(\sqrt{.612 + .5} - \sqrt{.612})$$

$$= 1.07$$

(note: here  $V_{SB}$  is estimated)

hence

$$V_{DSAT5} \le 2 - \left( \sqrt{\frac{8.8}{9.75(8.86)}} + 1.07 \right)$$

$\le 2 - 1.39$   $\le 0.6$

(+OS):

$$V_{DSAT5} \le V_{DD} - Vo^{+}_{(max)} = 0.5 \text{ V}$$

(2.44)

Hence the output swing requirement on  $\mathbf{V}_{\mathbf{DSAT5}}$  overrides.

`So

$$(W/L)_5 \ge \frac{2 I_5}{Kp'(V_{DSAT5})^2} - \frac{2(8.8)}{9.75(0.5)^2} - 7.22$$

(2.45)

Choose

$$L_5$$

(DRAWN) - 10  $\mu$ m

then L<sub>5</sub> (ACTUAL) = 10 - 1.2 = 8.8

$$\mu$$

m and W<sub>5</sub> (DRAWN) = 7.22 (8.8  $\mu$ m) = 63.54  $\approx$  64  $\mu$ m. So the final ratio is (W/L)<sub>5</sub> = 64/8.8 = 7.273

## 8. Systematic offset requirement:

Choose  $L_7$  -  $L_5$  - 10  $\mu m$ . Then because  $L_6$  -  $L_3$ , (2.25) can be written

$$w_7 - w_5 \cdot \frac{1}{2} \cdot \frac{w_6}{w_3}$$

(2.46)

In order to get a round number,  $W_6$  is altered to 205 microns, then:

$$W_7 - \frac{64}{2} \frac{205}{10} - 656 \mu m$$

### 9 Power dissipation request:

From (2.30) and (2.10) the total bias current can be estimated as

Ibias =

$$SR C + 3 SR C_{L}$$

(2.47)

From (2.28) this can be rewritten:

Ibias

$$\approx 3 \text{ SR C}_{L} (g_{m1}/g_{m6} + 1)$$

(2.48)

For this design then, Ibias is

Ibias

$$\approx 3 (2 \text{ V/}\mu\text{s})(20 \text{ pF})(1/12.9 + 1)$$

- 129  $\mu\text{A}$

Hence with  $\pm$  5V supplies the expected power dissipation is 1.29 mW.

#### Simulations

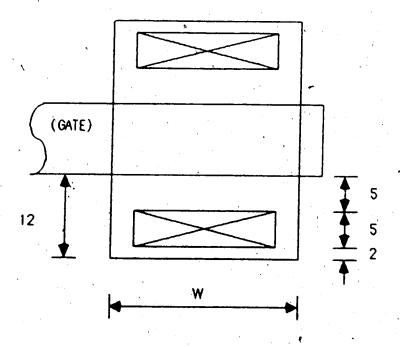

The gain, CMRR and PSRR are difficult to predict due to the inaccuracy of estimating transistor output resistance. Hence it is best to use the more accurate SPICE [22] level 2 models in order to check that these performance areas are acceptable. Also, the simulations verify that the primary design specifications are met. Appendix 3 shows the basic SPICE file which was used. Transistor source and drain areas and peripheries were estimated from Northern Telecom's 5 micron design rules as shown in figure 2.23. As a result of the simulation process, the end values for the second stage

Figure 2.23 Transistor dimensions for 5 micron rules

Figure 2.24 Two stage op-amp with NMOS inputs

Figure 2.25 Final circuit for design example

Figure 2.26 Cascoded transistor configuration

transistor sizes differs from the above design values. The final circuit is shown in figure 2.25. During the simulations, it was observed that the more accurate MOSFET model resulted in lower values of  $V_{\rm DSAT}$  than expected. Although this meant that ICMR and OS were better than expected, it also resulted in the need to increase  $(W/L)_6$  in order to obtain the desired transconductance.  $(W/L)_7$  consequently also had to be increased to prevent systematic offset. A summary of all the simulation results can be found in table 3.4. Measurements of the actual circuit implementation are given in chapter 4.

#### 2.4.3 Evaluating tradeoffs

If during the simulation phase the op amp performance is seen to be deficient in some area it will be necessary to make some circuit adjustments. To help in this process, table 2.4 shows the general relationship between the circuit parameters and the performance parameters. From the table one can see that for a given circuit change, performance in one area may improve while in another it may degrade. The designer can then choose the approach which results in the most acceptable tradeoff.

As an example of the use of the table, consider that the first stage current is increased. From the table it is seen that SR, GBW and the thermal noise level should improve. However, Av(0), ICMR, OS, PSRR, CMRR and offset will degrade. Looking across the table, though, shows that increasing the aspect ratios of M1, M2, M3, M4 and M5 will counteract these degradations while maintaining the improvements in SR, GBW and noise.

Table 2.4 Relationships between cct and performance parameters

| Set notes       | ٩       | lst<br>stage  | M1 and M2      | M3 and M4    | <b>9</b>                              | 7 W    | MS             | 8             |               |

|-----------------|---------|---------------|----------------|--------------|---------------------------------------|--------|----------------|---------------|---------------|