### Compiler-Driven Performance on Heterogeneous Computing Platforms

by

Artem Chikin

A thesis submitted in partial fulfillment of the requirements for the degree of

Master of Science

Department of Computing Science

University of Alberta

© Artem Chikin, 2019

### Abstract

Modern parallel programming languages such as Open Multi-Processing (OpenMP) provide simple, portable programming models that support of-floading of computation to various accelerator devices. Coupled with the increasing prevalence of heterogeneous computing platforms and the battle for supremacy in the co-processor space, gives rise to additional challenges placed on compiler/runtime vendors to handle the increasing complexity and diversity of shared-memory parallel platforms.

To start, this thesis presents three kernel re-structuring ideas that focus on improving the execution of high-level parallel code in Graphics Processing Unit (GPU) devices. The first addresses programs that include multiple parallel blocks within a single region of GPU code. A proposed compiler transformation can split such regions into multiple regions, leading to the launching of multiple kernels, one for each parallel region. Second, is a code transformation that sets up a pipeline of kernel execution and asynchronous data transfers. This transformation enables the overlap of communication and computation. The third idea is that the selection of a grid geometry for the execution of a parallel region must balance the GPU occupancy with the potential saturation of the memory throughput in the GPU. Adding this additional parameter to the geometry selection heuristic can often yield better performance at lower occupancy levels.

This thesis next describes the Iteration Point Difference Analysis — a new static-analysis framework that can be used to determine the memory coalescing

characteristics of parallel loops that target GPU offloading and to ascertain safety and profitability of loop transformations with the goal of improving their memory-access characteristics. GPU kernel execution time across the Polybench suite is improved by up to  $25.5\times$  on an Nvidia P100 with benchmark overall improvement of up to  $3.2\times$ . An opportunity detected in a SPEC ACCEL benchmark yields kernel speedup of  $86.5\times$  with a benchmark improvement of  $3.4\times$ , and a kernel speedup of  $111.1\times$  with a benchmark improvement of  $2.3\times$  on an Nvidia P100 and V100, respectively.

The task of modelling performance takes on an ever increasing importance as systems must make automated decisions on the most suitable offloading target. The third contribution of this thesis motivates the need with a study of cross-architectural changes in profitability of kernel offloading to GPU versus host CPU execution, and presents a prototype design for a hybrid computing device selection framework.

### **Preface**

Chapter 3 of this thesis has been published as A. Chikin, T. Gobran. J.N. Amaral, "OpenMP Code Offloading: Splitting GPU Kernels, Pipelining Communication and Computation, and Selecting Better Grid Geometries", Proceedings of the Fifth Workshop on Accelerator Programming Using Directives, in November 2018. This work was presented at the workshop during the Supercomputing 2018 conference in Dallas, TX, on November 11, 2018, by the author. My role on the project was to formulate the research project, introduce ideas for compiler transformations that the project evaluated, and form the experimental methodology to evaluate these ideas. I was also responsible for supervision of the undergraduate student working on the project, educating him about the subject and guiding the execution of the ideas. T. Gobran was responsible for carrying out the manual prototyping of the proposed code transformations, performing the experimental evaluation, reporting the results to myself and J.N. Amaral and drafting the manuscript. J.N. Amaral was the supervisory member of the research project team and contributed to the overall structure, direction of the resulting manuscript and to manuscript edits.

Chapter 4 of this thesis has been submitted for publication as **A. Chikin**, T. Lloyd, J.N. Amaral, E. Tiotto, M. Usman, "Memory-access-aware safety and profitability analysis for transformation of accelerator-bound OpenMP loops". The contents of this chapter fall under a patent filed with the U.S. Patent Office as **A. Chikin**, T. Lloyd, J. N. Amaral, E. Tiotto "Compiler for Restructuring Code Using Iteration-Point Algebraic Difference Analysis", Patent Reference: P201706298US01, filed on March 12, 2018. I was responsible for designing, building, and experimentally evaluating the analysis framework (within the IBM XL Compiler), the loop dependence test, and the associated

safety/profitability analyses that are used to guide relevant automated compiler transformations. T. Lloyd contributed many technical discussions and advice that helped evolve the ideas developed during this research, the work also directly extends T. Lloyd's prior work. J.N. Amaral was the supervisory author and contributed to guiding the experimental evaluation and editing the resulting manuscript. E. Tiotto was the IBM collaborator, and participated in technical discussions. M. Usman contributed the formal mathematical formulation for the algorithms presented in this work.

Chapter 5 of this thesis has been submitted for publication as **A. Chikin**, J.N. Amaral, K. Ali, E. Tiotto, "Towards Hybrid Execution Target Selection Through Analytical Performance Modeling". The contents of this chapter cover ideas that fall under a patent filed with the U.S. Patent Office as **A. Chikin**, J.N. Amaral, K. Ali, E. Tiotto, "Hybrid Compute Device Selection Analysis", Patent Reference: P201803063US01, filed on August 31, 2018. I was responsible for conceiving the research project idea, constructing the architecture of the hybrid analysis, prototyping its components, and experimentally evaluating its efficacy. J.N. Amaral and K. Ali were supervisory authors and contributed to the focus of the project and edits to the resulting manuscript. E. Tiotto was the IBM collaborator, and participated in technical discussions.

Another research result, which is not part of this thesis, but was completed during my M.Sc program at the University of Alberta is a research project published as T. Lloyd, A. Chikin, E. Ochoa, K. Ali, J.N. Amaral, "A Case for Better Integration of Host and Target Compilation When Using OpenCL for FPGAs", *Proceedings of Fourth International Workshop on FPGAs for Software Programmers*, in October 2017. This work introduced a series of interconnected compiler transformations aimed at improving performance of Field-Programmable Gate Array (FPGA) programs generated through high-level synthesis of Open Compute Language (OpenCL). My roles on the project included implementing the reduction dependence elimination transformation and participating in guiding the overall direction of the research.

### To my Mom and Dad

For all the sacrifices they have made, endless love, support and inspiration.

## Acknowledgements

I would like to thank my supervisor, Dr. J Nelson Amaral, for his continuing support through guidance, advice and direction over the years that I have had the privilege of working with and learning from him.

I would also like to thank the many people working at, and visiting, the University of Alberta systems laboratory, for insightful conversations, technical arguments, and moments of whimsy. I have learned so much from each and every one of you.

This research has been funded by IBM Center for Advanced Studies (CAS) Canada and by the National Science and Engineering Research Council (NSERC) of Canada through their Collaborative Research and Development (CRD) program and through the Undergraduate Student Research Awards (USRA) program.

## Contents

| 1 | Intr                 | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                        |

|---|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 2 | Bac 2.1 2.2 2.3      | kground GPU Architecture, Programming Model, and Execution Platform 2.1.1 Memory Coalescing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3<br>3<br>5<br>5<br>7<br>9                               |

| 3 | Con                  | enMP Code Offloading: Splitting GPU Kernels, Pipelining munication and Computation, and Selecting Better Grid ometries  Fission of Multiple-Parallel-Region Target Regions Overlapping Data Transfer and Split Kernel Execution Pipelining Data Transfer and Parallel Loop Execution                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11<br>14<br>16<br>20<br>23<br>26<br>27<br>30<br>31<br>34 |

| 4 | Men form 4.1 4.2 4.3 | mory-access-aware safety and profitability analysis for transmation of accelerator-bound OpenMP loops  Loop Iteration Point Algebraic Differences  4.1.1 Focusing on Loop-Specific Analysis Demands  Symbolic Representation  4.2.1 Algebraic Simplification  4.2.2 Algebraic Difference Cancellation  Data Dependence Graph Pruning with Iteration Point Differences  4.3.1 Single-Loop Dependence Checking  4.3.2 Loop-Nest Dependence Checking  4.3.3 Symbolic Differences of Control-Dependent Expressions  Improve Dependence Testing  4.3.4 Prototype Implementation Demonstrates That the Iteration Point Difference Analysis (IPDA) Test is Essential  For Safety Analysis  IPDA GPU Global Memory Coalescing | 35<br>37<br>39<br>39<br>40<br>41<br>42<br>43<br>45<br>47 |

|   | 4.5                  | Analysis on parallel OpenMP loops                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49<br>52<br>53                                           |

| R | References 9                            |                                                                                                                                                                                                                                                                                                                                                                                                     |                                              |  |  |

|---|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|--|

| 7 | Con                                     | clusion                                                                                                                                                                                                                                                                                                                                                                                             | 93                                           |  |  |

| 6 | Rela<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5 | Ated Work  Overlapping GPU Computation and Memory Transfers GPU Occupancy / Grid Geometry                                                                                                                                                                                                                                                                                                           | 86<br>86<br>87<br>89<br>89                   |  |  |

|   | 5.2                                     | Change Across GPU Generations 5.1.1 Generational Performance Gaps Require Fine-Tuned Performance Estimates A New Hybrid Analysis Framework for Deciding the profitability of GPU Offloading 5.2.1 OpenMP CPU Performance Model 5.2.2 GPU Performance Model 5.2.3 GPU Memory Access Pattern: Improved Coalescing Detection 5.2.4 Putting It All Together 5.2.5 Evaluation Discussion and Future Work | 71<br>72<br>74<br>76<br>79<br>80<br>82<br>85 |  |  |

| 5 | cal                                     | rard Hybrid Execution Target Selection Through Analyti-<br>Performance Modeling<br>Comparative Offloading Performance                                                                                                                                                                                                                                                                               | 67                                           |  |  |

|   | 4.6                                     | Evaluation                                                                                                                                                                                                                                                                                                                                                                                          | 58<br>58<br>61<br>63                         |  |  |

|   | 4.0                                     | 4.5.2 Loop Interchange                                                                                                                                                                                                                                                                                                                                                                              | 56                                           |  |  |

## List of Tables

| 3.1 | Optimal occupancy for a massively parallel memory-bound kernel at varying numbers of uncoalesced memory accesses with tripcount 5000                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26<br>28 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.1 | Benchmark execution time speedup with automatic loop interchange and collapse enabled compared to the default codegeneration scheme.                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 65       |

| 4.2 | Loop collapse clauses were removed from benchmarks which contain them. This table shows the portion of the loop collapses re-discovered to be benefitial and automatically applied by the compiler. Execution ratio columns show the performance of the code stripped of collapse clauses versus the code with collapse clauses present. GPU code is executed on an Nvidia P100. The MIC (Many Integrated Core) relative execution column compares the performance of the same two versions of the kernel executed on an Intel Xeon Phi 7250 Processor, compiled with ICC ver. 17.0.2 | 66       |

| 5.1 | Cross-architectural changes in GPU sffloading speedup vs. host execution.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 70       |

| 5.2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 76       |

| 5.3 | GPU device/bus parameters as used in the execution model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 78       |

# List of Figures

| 2.1<br>2.2<br>2.3 | Example topology of a heterogeneous computing environment Example vector addition OpenMP 4.x accelerator code Visualization of the cooperative threading OpenMP 4 GPU code-generation scheme. (Adapted from similar figure in [24])                                                                                | 4<br>6<br>8                              |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| 3.1               | Example OpenMP GPU code with multiple parallel loops in a target region                                                                                                                                                                                                                                            | 12                                       |

| 3.2<br>3.3        | Example OpenMP code following kernel splitting Two kernel GPU code structure before asynchronous memory                                                                                                                                                                                                            | 14                                       |

| 3.4               | transfer                                                                                                                                                                                                                                                                                                           | 17                                       |

| 3.5               | Transfer                                                                                                                                                                                                                                                                                                           | 17<br>18                                 |

| 3.6               | Run time cost of allocating and freeing memory with the three                                                                                                                                                                                                                                                      | 19                                       |

| 3.7               | methods                                                                                                                                                                                                                                                                                                            | 20                                       |

| 3.8               | A GPU parallel regions structure after being broken up into 4 tiles.                                                                                                                                                                                                                                               | 21                                       |

| 3.9<br>3.10       | First parallel region in ATAX before pipelining                                                                                                                                                                                                                                                                    | 22<br>22<br>22                           |

| 3.10              | Runtime results by occupancy of SYRK at tripcount 4000                                                                                                                                                                                                                                                             | 24                                       |

|                   | Runtime results by occupancy of FDTD-2D at tripcount 15000. The speedup ratio over the baseline for each experiment evaluation of the applicable Polybench and Rodinia benchmarks run at a tripcount set to 9600. SRAD executes on a 512by512 image with the encompassing iteration loop performed 9600 times. LUD | 26                                       |

| 3.14              | operates on a 9600by9600 matrix                                                                                                                                                                                                                                                                                    | 29                                       |

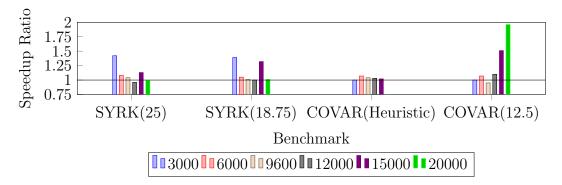

| 3.15              | Heuristic refers to that by Lloyd et al. [37]                                                                                                                                                                                                                                                                      | 31                                       |

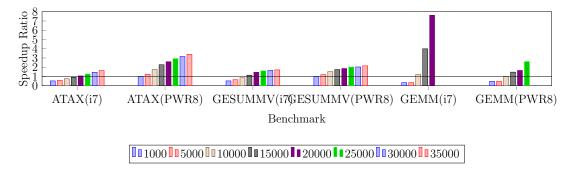

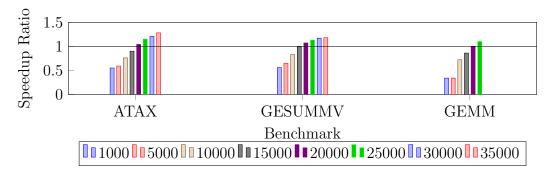

| 3.16              | applicable Polybench benchmarks at varying tripcounts. GEMM is missing sizes due to time constraints                                                                                                                                                                                                               | 32                                       |

|                   | Intel i7 machine at varying tripcounts with optimal occupancy applied to all kernels                                                                                                                                                                                                                               | 33                                       |

| 4.1               | Example loop to be analyzed by IPDA with a conditionally-defined indexing expression                                                                                                                                                                                                                               | 37                                       |

| 4.2<br>4.3<br>4.4 | Example loop array access with a potential dependence Example n-degree loop nest with a potential loop dependence. Example Loop Nest at various stages of compilation/optimization.                                                                                                                                | $\begin{array}{c} 42\\46\\48\end{array}$ |

| 4.5               | Computing the number of coalesced accesses                                                                                                                                                                                                                                                                         | 50                                       |

| 4.6 | Example target region from GEMM benchmark                                                                                   | 52      |

|-----|-----------------------------------------------------------------------------------------------------------------------------|---------|

| 4.7 | Pictorial representation of a parallel loop nest's iteration space.  — Loop iterations comprising units of parallel work.   |         |

|     | Loop Iterations executed sequentially.                                                                                      | 53      |

| 4.8 | Pictorial representation of a parallel loop nest's memory access                                                            | 00      |

|     | pattern                                                                                                                     | 56      |

| 4.9 | Excerpt from a target region in 557.pcsp                                                                                    | 63      |

| 5.1 | Example compilation and execution flow of an offloading decision                                                            |         |

|     | compiler/runtime framework                                                                                                  | 72      |

| 5.2 | Equations of Cost Model for OpenMP from [33]                                                                                | 74      |

| 5.3 | Hong and Kim performance model program exection predic-                                                                     |         |

|     | tion [20]. Highlighted is the additional factor that describes the                                                          |         |

|     | side-effects of OpenMP thread-loop-iteration scheduling                                                                     | 77      |

| 5.4 | Equations of Memory-Warp and Compute-Warp Parallelism                                                                       | 0.4     |

|     | used in GPU execution Cost Model from [20]                                                                                  | 81      |

| 5.5 | Actual versus predicted GPU offloading speedup for test kernel                                                              | 0.1     |

| T C | execution mode versus a host using 4 threads                                                                                | 81      |

| 5.6 | Actual versus predicted GPU offloading speedup for benchmark                                                                | 99      |

| 5.7 | kernel execution mode versus a host using 4 threads                                                                         | 82      |

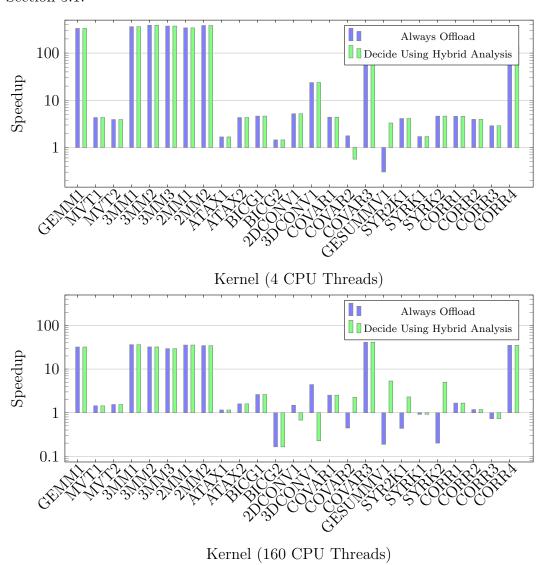

| 5.7 | Speedup achieved by always offloading to GPU versus offloading when determined profitable by the analytical hybrid decision |         |

|     | model. Benchmarks executed in <i>Benchmark</i> mode                                                                         | 83      |

|     | model. Denominants executed in Denominant mode                                                                              | $\circ$ |

## List of Acronyms

**ACF** Arithmetic Control Form.

**DDG** Data Dependence Graph.

FPGA Field-Programmable Gate Array.

**GPU** Graphics Processing Unit.

**HPC** High-Performance Computing.

IPDA Iteration Point Difference Analysis.

IR Intermediate Representation.

**LLVM** Low-Level Virtual Machine.

MIC Many Integrated Core.

**OpenACC** Open Accelerators.

OpenCL Open Compute Language.

OpenMP Open Multi-Processing.

SIMD Single Instruction, Multiple Data.

**SIMT** Single Instruction, Multiple Thread.

**SM** Streaming Multiprocessor.

**VEG** Value Evolution Graph.

## Chapter 1

### Introduction

Heterogeneous computing platforms are increasingly commonplace across all major application domains. Accelerator devices can be found in systems that vary from mobile phones to supercomputers. In the most recent Top500 list [59], 7 out of the top 10 machines use accelerator devices. The two fastest computers in the USA, the Summit supercomputer at the Oak Ridge National Laboratory and the Sierra supercomputer at the Lawrence Livermore National Laboratory rely heavily on accelerators for their computation. Summit has more than 25,000 NVIDIA V100 GPUs coupled with 9,200 IBM POWER 9 CPUs [56]. The Cray XC40 Trinity supercomputer, at the Los Alamos National Laboratory, achieves 41.5 petaflops of peak performance with a different heterogeneous architecture that uses Many Integrated Core (MIC) Xeon Phi co-processors [60]. Various competing accelerator platforms co-exist, often within the same host machine, as each has its own strengths, weaknesses, and corresponding favorable application domains. Moreover, different accelerator architectures place different, often opposing, demands on attributes of computer programs. Such demands must be met in order to achieve acceptable levels of performance.

Proliferation of heterogeneous computing has spurred development of programming models that allow developers to write applications that target execution on accelerator devices. High-level programming models such as OpenMP [13] and Open Accelerators (OpenACC) [58] provide the means to write architecture-agnostic accelerator code. Programs written using such high-level programming models are meant to be written once in a generic

fashion and to run on a variety of computational devices from general-purpose CPUs to GPU, FPGA, and MIC co-processors. Target-agnostic programming abstracts the details of accelerator architecture from the developer and makes it the prerogative of the compiler/runtime to handle architecture-specific code generation, optimization, and parameter tuning, within the limits allowed by the programming model. Furthermore, programming models like OpenMP are shifting towards being more descriptive, rather than prescriptive, with the next iteration of the standard poised to introduce constructs that allow compilers most freedom yet on how to generate code and where it should execute (e.g. #pragma loop).

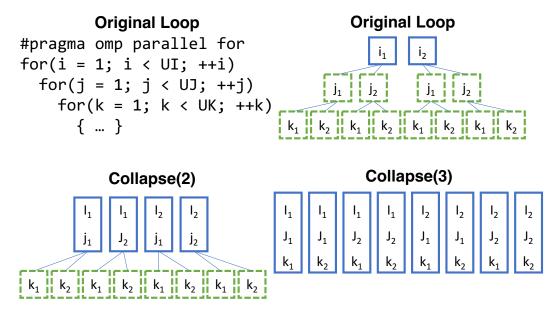

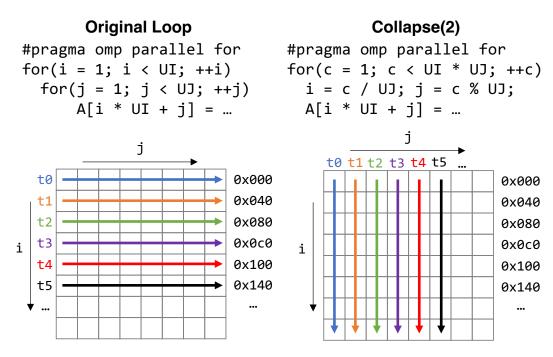

The notion of performance portability is a core tenet behind the design of high-level parallel programming models. OpenMP promises a model that allows users to write programs that seamlessly scale from workstation PCs to supercomputers. Yet, performance portability is extremely difficult to achieve because compiler heuristics and analyses struggle to keep up with advancements in micro-architecture. To compensate, the OpenMP language specification has, over time, accumulated hints that developers may provide to the compiler to increase performance for a specific target. For instance, the collapse clause instructs the compiler to collapse the iteration-space of multiple nested loops in a prescribed manner. The resulting code exhibits memory access patterns that favour a specific architecture's memory subsystem. Such hints detract from portability. More capable compilers should be able to generate the same higher-performing code without portability-reducing annotations.

### Chapter 2

## Background

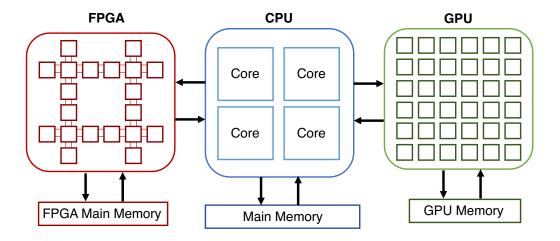

A typical heterogeneous system consists of a host machine that operates using an ordinary CPU and contains main memory modules. Attached to the host machine, via a data-transfer bus, are one or more accelerator devices. An example topology of a host computer with two accelerator devices attached is shown in Figure 2.1. The host — a general-purpose CPU machine — is responsible for the overall system's operation, memory management and control of execution among attached devices. During execution of a program that contains an accelerator kernel — a piece of computation specified to be offloaded to an accelerator — the host machine schedules execution of the kernel on a given computing device and performs the necessary data transfers to and from the computing device. A fallback scenario may occur in which the required accelerator device is unavailable or busy, in which case the host may instead schedule execution of the accelerator kernel on the host machine's CPU. If the programming model allows it, the host may elect to schedule kernel execution either on the host itself or any of the available accelerators.

# 2.1 GPU Architecture, Programming Model, and Execution Platform

GPUs are composed of a large number of Streaming Multiprocessors (SMs), each capable of executing thousands of threads in parallel. Such massive parallelism requires a strict Single Instruction, Multiple Thread (SIMT) dataparallel programming model in order to achieve performance. The Nvidia V100

Figure 2.1: Example topology of a heterogeneous computing environment

is a state-of-the-art Nvidia GPU for high-performance computing composed of 80 SMs. Each SM can issue an instruction for 128 threads per cycle [44]. The V100 has enough resources to maintain the state of thousands of threads, which gives each SM the ability to context switch between threads with zero penalty—a key instruction-latency hiding mechanism. GPU threads are grouped into warps: all the threads that comprise a warp execute either the same instruction in lock-step or no instruction at all. Lock-step execution reduces the overhead of scheduling work across a large number of threads. Threads are further grouped into thread blocks or Cooperative Thread Arrays (CTA). All threads within a thread block must execute on a single SM. They can both share intermediate results via access to SM's shared memory banks and synchronize their execution. Threads from different thread blocks have no means of direct communication or synchronization. The number of threads per thread block and the number of thread blocks comprise the GPU grid geometry.<sup>1</sup>

$<sup>^1\</sup>mathrm{NVIDIA}$ -specific terms such as warp and SM are used throughout this thesis for the sake of clarity and consistency.

#### 2.1.1 Memory Coalescing

In a typical data-parallel kernel, thread identifiers are used in memory-access addressing expressions to load/store the data items for each thread. The number of memory requests issued by a warp in a given cycle can be as large as the number of threads in a warp (32 in current architectures) because the threads belonging to it execute the same instruction simultaneously. The GPU global memory subsystem has a limited amount of bandwidth available. As a means to reduce the overall number of requests, the GPU coalesces multiple same-cycle accesses to memory within the same cache line into a single request. Coalescing memory accesses into fewer requests can dramatically improve memory throughput because no thread in a warp can continue execution until the memory accesses of all threads have completed. The number of requests necessary to satisfy all the accesses in a warp of threads is equal to the number of distinct cache lines that are accessed. Each global memory request requires hundreds of cycles to be completed; thus, structuring GPU programs to avoid non-coalesced memory accesses is paramount for performance [1].

### 2.2 OpenMP and Accelerator Programming

Programming in CUDA or OpenCL is a painstaking process that requires developers to have thorough working knowledge of the accelerator architecture being targeted. An alternative are high-level directive-based parallel programming models such as OpenMP that support offloading of code regions to accelerators. These models reduce the amount of effort required to write accelerator code by abstracting the accelerator hardware specifics from the developer. Being platform-agnostic, these models promise code portability across existing and future accelerators. Figure 2.2 shows an example parallel loop written using OpenMP 4.x with accelerator offloading. The programmer specifies a target region, directing the compiler to offload the region to an accelerator device. The target region directive is annotated with data-transfer map clauses that indicate which arrays must be transferred to and from the device data environment. Full assortment of OpenMP parallelism constructs are supported inside target re-

```

void vecAdd(double *a, double *b, double *c, int n)

{

#pragma omp target map(to: a[:n], b[:n]) map(from: c[:n])

#pragma omp teams distribute parallel for

for (int i = 0; i < n; i++)

c[i] = a[i] + b[i];

}</pre>

```

Figure 2.2: Example vector addition OpenMP 4.x accelerator code

gions; however, task-level parallelism maps poorly to data-parallel devices such as GPUs. Thus, performance considerations limit the expression of parallelism in OpenMP for execution in GPUs to parallel and loop constructs.

Moreover, GPUs' reliance on a SIMT execution model has implications on the compiler implementations that generate GPU code from OpenMP. Where possible, parallel constructs must be mapped to data-parallel structures in order to achieve good performance. Other aspects of the accelerator architecture must be taken into account in for efficient hardware utilization, such as the selection of a grid geometry. In contrast with low-level languages — such as CUDA and OpenCL — where the selection of program runtime parameters such as grid geometry is the prerogative of the programmer, OpenMP assigns this task to the compiler/runtime-system designers. On one hand the rigid execution model that must be followed when generating GPU code makes the compiler designer's task challenging. On the other hand it affords considerable freedom for code generation from high-level descriptive models. Grid geometry selection in the OpenMP context was one of the research projects pursued as a component of this thesis by the author, in collaboration with T. Lloyd. [37].

OpenMP can express three levels of parallelism inside a target region: the teams construct declares a region of code to be executed by a league of threads, the parallel construct declares a task to be executed in parallel by threads within a league, and the simd construct declares vector-based execution of a loop. The first two provide a natural mapping to the GPU's notions of thread blocks and threads, respectively. Both teams and parallel constructs have associated loop work-distribution clauses: teams distribute and parallel

for. teams distribute distributes iterations of the associated loop into equal-sized partitions spread among teams, and parallel for distributes loop iterations within a chunk to individual threads. Combined constructs are often used to capture all of the above levels of parallelism for a given loop into one prescription, such as teams distribute parallel for construct in Figure 2.2.

### 2.2.1 OpenMP 4.x GPU Code Generation

As implemented in OpenMP 4.x for LLVM/Clang as well as in the IBM XL C/C++/Fortran compilers, target regions are outlined into separate procedures. The outlined procedure is cloned into two versions: a device version and a host fallback version. CPU code is generated for the fallback variant. A kernel suitable for GPU execution is generated for the device version. To best take advantage of the GPU, data-parallel code is generated in place of parallel loops. However, full breadth of the OpenMP specification must be supported by a compliant compiler implementation. Thus, the GPU code generator must be able to handle a multitude of constructs that contain both serial and parallel code that may be nested or adjacent within a target region.

The compilers used in this work employ a cooperative threading model that utilizes the technique of warp specialization to generate data-parallel GPU code from parallel OpenMP regions [24]. Parallel work is performed by a collection of worker warps and coordinated by a single master warp (selected to be the last warp in a CTA). The coordination between warps is done through the use of a CTA-level synchronization primitive that allows for named barriers that apply to a compiler-specified number of warps to participate in the barrier (bar.sync \$0 \$1). When the master encounters a parallel region, it activates the required number of worker warps and suspends its own execution. Figure 2.3 shows a visualization of the process described above.

The resulting device kernel is translated into Nvidia's *Parallel Thread Execution*(PTX) pseudo-assembly language, using Nvidia's proprietary PTXAS assembler. The host code that previously contained the target region is rewritten to invoke the outlined device kernel through a runtime method call.

Figure 2.3: Visualization of the cooperative threading OpenMP 4 GPU codegeneration scheme. (Adapted from similar figure in [24])

The runtime performs the required setup and data-transfer. Finally, the GPU runtime compiles the PTX code into machine instructions and launches kernel execution.

#### Warp Specialization Elision

While necessary to support the full breadth of possible OpenMP constructs that can occur in target regions, as well as serial code sections and sibling parallel regions, warp specialization code-generation scheme incurs a significant amount of runtime overhead that can be avoided in select special cases. Not all kernels require the full machinery of the cooperative code-generation scheme. For

target regions that are comprised solely of a single parallel loop with no nested OpenMP constructs, and no serial code, the compiler optimizes the generated code by eliding the warp specialization and runtime-managed sections of the code. This optimization results in dramatically simpler generated data-parallel code that eliminates the mentioned overheads.

Elision of the cooperative code-generation scheme and its incurred synchronization points is enabled by target region splitting. Jacob et al. describe how this elision is handled automatically by the Clang compiler, and present a performance study of elision [24].

# 2.3 Symbolic Static Analysis: Arithmetic Control Form

The Arithmetic Control Form (ACF) static analysis framework, introduced by Lloyd et. al., is a way to capture linear and non-linear relationships between program statements [36]. ACF's main approach is to combine data and control flow by computing symbolic values for expressions of interest. Similarly to the work by Ferriere and Stoutchinin on  $\phi$ -nodes [55] and prior efforts in if-conversion [39], ACF converts conditionally-executed statements into predicated statements, capturing definitions across all potential traces through the program. Resulting ACF expressions consist of binary operations on constants and symbols representing compile-time unknowns.

In the context of data-parallel programs, ACF's key strength lies in its ability to compute an algebraic difference on the symbolic representation of a statement. For instance, consider a statement  $\mathcal{S}$  that is executed by different threads, and assume that  $\mathcal{S}$  contains an addressing expression A[f(i)], where i is the identifier of a thread executing the code. ACF constructs an algebraic expression for the difference between the symbolic value of the function f computed by two distinct threads. Then, by substituting actual constant thread identifiers into symbolic expressions, ACF can determine the memory-access stride between threads by solving the difference to a constant.

ACF replaces variable references with their dominating definitions wherever

possible during the construction of symbolic expressions. ACF can perform this replacement without any additional considerations for potential performance impact of this replacement because ACF expressions are symbolic and are not actual Intermediate Representation (IR) of the program that will undergo transformation and code-generation.

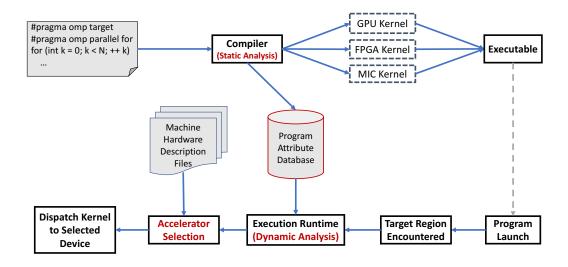

The rest of this thesis builds on these core topics. Chapter 3 outlines several compiler transformations that aim at re-structuring OpenMP parallelism constructs to better suit the GPU architecture. Chapter 4 posits a static analysis framework for detecting memory access patterns of GPU-bound parallel loops and using it to power safety and profitability analyses guiding performance-improving loop transformations. Chapter 5 re-approaches the topic of accelerator offloading in high-level parallel programming models, detailing a hybrid-analysis decision framework for selecting a target processing element out of a plurality present in a heterogeneous compute node. Chapter 6 records the state-of-the-art related work in the relevant areas of study. Chapter 7 concludes this thesis.

## Chapter 3

## OpenMP Code Offloading: Splitting GPU Kernels, Pipelining Communication and Computation, and Selecting Better Grid Geometries

A natural way for an experienced OpenMP CPU programmer to write OpenMP GPU code is to offload to an accelerator sections of code that contain various parallelism-specifying constructs, that are often adjacent. However, this programming style generally leads to unnecessary overheads that are not apparent to programmers unfamiliar with GPU programming and mapping of high-level OpenMP code to GPUs. Experienced GPU Programmers will instead create a common device data environment and operate on data by invoking separate kernels for each required parallel operation. This technique results in more efficient code and often reduces the overall amount of host-device data transfer, as our work will demonstrate. The main goal of this investigation is to deliver better performance for the code written by experienced OpenMP programmers that are not necessarily GPU programming experts.

When an OpenMP target region contains a combination of parallel and serial work to be executed in a GPU, the compiler must map these computations to the GPU's native SIMT programming model. One approach is through a technique called warp specialization [3]. When specializing warps, the compiler

Figure 3.1: Example OpenMP GPU code with multiple parallel loops in a target region.

designates one warp as the master warp and all others as a pool of worker warps. In the Clang-YKT compiler OpenMP 4 implementation, the master warp is responsible both for executing serial code and for organization and synchronization of parallel sections [24] [23]. The synchronization between parallel and serial work is implemented through named warp barriers and an emulated stack in GPU global memory for the worker warps to access the master threads state. To handle activation and deactivation of worker warps, synchronization constructs are added to the target region.

Figure 3.1 is an example of OpenMP 4 code. The pragma in line 1 establishes that the following region of code will run on the default target accelerator — assumed to be a GPU in this work, and ensures that the data specified in map clauses is transferred to and from the GPU, respective to the (to,from) specifiers. The pragmas in lines 2 and 6 establish the associated work as parallel within the enclosing target region. There is an implicit synchronization point at the end of each parallel region.

Warp specialization introduces substantial overhead because the master and worker warps must synchronize execution when parallel region execution starts and finishes. Even when there is no sequential code between parallel regions, synchronization is required between the completion of one parallel region and the start of another.

The Clang-YKT compiler performs a transformation called *elision* that

removes the warp specialization code, the master-thread stack emulation and the synchronization code, thus eliminating unnecessary overhead [24]. To be candidate for elision, a target region must contain only one parallel loop and this loop must not contain calls to the OpenMP runtime. A research question posed by our work is: what would be the performance effect of transforming an OpenMP 4 target region that contains multiple parallel regions, with or without serial code, into multiple target regions, each with a single parallel region. The goal is to enable the compiler to perform the elision transformation. Special care must be taken to avoid increasing the amount of data transfer between the host and device memory.

This chapter explores two additional transformation opportunities, both applicable to any OpenMP code where parallel loops are isolated into their own target regions. The first is the overlapping of data transfer and GPU kernel execution for multiple adjacent target regions. The target regions are wrapped in a common device data environment and through memory-use analysis, a compiler can determine which data is and is not needed until or after a certain point. The second opportunity is to overlap computation with data-transfer by pipelining the loop within a single-loop parallel region in a fashion similar to iterative modulo scheduling [49]. The loop iteration space can be divided into multiple tiles, each resulting in a separate kernel launch, execution of which happens asynchronously with the data transfer for the next tile.

Finally, this target region format allows for better selection of grid geometry tailored to the contained parallel loop. Grid geometry is the number of Cooperative Thread Arrays (CTAs), also known as thread blocks, and the number of threads per CTA that the GPU uses. Grid geometry strongly affects the overall occupancy of the GPU. Tailoring this selection to a specific parallel region can have a significant effect on the performance of that region. However, a single grid geometry must be selected for an entire target region. Therefore, multiple parallel regions in the same target region cannot have individually specialized geometry for each parallel region.

In the remainder of this chatper, Section 2.2.1 describes how kernel splitting enables the elision of runtime calls and barrier synchronization. Section 3.1

```

#pragma omp target data map(to: B[:S]) map(tofrom: A[:S], C[:S]) {

#pragma omp target teams distribute parallel for

for () {

... // Parallel work involving A and B

}

#pragma omp target teams distribute parallel for

for () {

... //Parallel work involving B and C

}

}

```

Figure 3.2: Example OpenMP code following kernel splitting.

presents a sample code to demonstrate how kernel splitting is performed. Section 3.2 describes the implementation of asynchronous memory transfers and presents a study of their performance implications. Section 3.3 explains how these transfers can be used to establish a pipeline between computation and data transfers. Section 3.4 shows that custom grid geometry must take into consideration the potential saturation of memory bandwidth in the GPU. Section 3.5 presents the performance study that can be used to predict the potential benefits of the proposed transformations.

### 3.1 Fission of Multiple-Parallel-Region Target Regions

When a target region is separated into two target regions, as shown in Figure 3.2, each target region is then executed as a separate kernel on the GPU and therefore data transferred for the first region is no longer present for the second region to utilize as is the case when both exist in a single-target region. Figure 3.2 shows how the single-target region spanning lines 1–10 in Figure 3.1 can be split into two separate target regions, one spanning lines 2–5 and the other lines 6–9. The parallel region directives (lines 2 and 6 of Figure 3.1) are combined with the target directives (lines 2 and 6 of Figure 3.2), transforming each parallel region into a stand-alone target construct. To avoid extra data transfers, the newly formed target regions are enclosed in a common device data environment containing all the implicit and explicit mappings of data

from the original single-target region. Only the data items specified in the data environment persist in GPU global memory across multiple target regions. The motivation for this transformation to be performed by a compiler is further reinforced by the design of the kernels OpenACC construct [57]. kernels construct definition states: "The compiler will split the code in the kernels region into a sequence of accelerator kernels", as deemed appropriate by the implementation. This design makes a strong argument for implementing the proposed transformation at the OpenMP level to further the efforts towards performance portability.

Furthermore, with a common device data environment, it is possible to overlap memory transfers with computation by analyzing when each data element is needed or produced. In our hand-implemented prototype for the transformation the OpenMP target update directive is used for these transfers, with the additional nowait clause added to allow for asynchronous memory transfers.

Safety measures must be taken when performing target fission, mainly to handle the presence of serial sections within the original single-target region. One concern to address is the possibility of variables being declared for the scope of the original single-target region. These variables reside in GPU memory and exist for the duration of the target region that is their scope, as a result the compiler must ensure that splitting does not interfere with any usages of them. One approach, if possible, is to move the variable declaration onto the CPU and map it to the common device data environment with an alloc map clause. Additional care must be taken to then mark such variables as teams private, to replicate the semantics of original code. Another approach is to limit the fission transformation such that all code from the declaration of the variable to its final usage resides within a single target region, though this can prevent elision.

A mitigating factor for this concern is that any such interfering declaration within the original single-target region scope must reside in a serial region at the target region scope. Variables declared inside parallel regions are assumed to be thread-local and expire when the parallel code block goes out of scope.

Another safety concern is that of serial code operating on data objects that are modified by previous parallel regions or are utilized by later parallel regions. The compiler must ensure that an updated variable is used by both the serial code and any later parallel regions on the GPU as would be the case with a single-target region wherein all code operates on the same GPU memory. One solution is to place serial code segments on the GPU in their own target regions. A drawback is paying the cost of additional kernel launch to execute serial code. An alternative approach is to execute the serial code on the CPU, with compiler analysis ensuring that any data object used in parallel regions are transferred to and from the device as needed for correctness. These transfers can become costly if they occur frequently, but in some cases run time can be improved significantly by executing serial code on the CPU.

Therefore the kernel splitting method should be applied with caution when the original single-target region has serial code or target region scoped local variables. Such scenarios did not appear in any of the benchmarks tested and likely do not represent a large portion of OpenMP code that can benefit from splitting.

### 3.2 Overlapping Data Transfer and Split Kernel Execution

Overlapping data transfer with computation can be an effective strategy to increase performance. Opportunities to benefit from asynchronous data transfers may arise from the splitting of a multi-parallel-region target into multiple single-parallel region targets. To enable the pipelining of data transfers and computation, the compiler must determine the first point of use of data and also when the computation of results is completed and the data is no longer used in the target. After such analysis, a schedule can be created for the pipelining with the overlapping effectively hiding the memory transfer time.

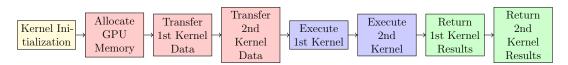

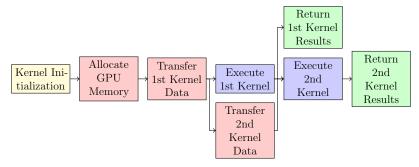

Figures 3.3 and 3.4 illustrate how this pipelining, enabled by asynchronous memory transfers, can reduce the overall execution time. In this example, if the runtime of the two kernels are long enough, this transformation results in

Figure 3.3: Two kernel GPU code structure before asynchronous memory transfer.

Figure 3.4: Two kernel GPU code structure with Asynchronous Memory Transfer.

the costs of the asynchronous memory transfers being entirely hidden.

Execution of asynchronous memory transfers and their synchronization with kernel execution can be specified manually by a programmer, using two OpenMP 4.5 clauses: depend and nowait. An OpenMP command with a depend clause with an out attribute must finish before any command with a depend clause with an in attribute with the same value. The nowait clause states that the specified OpenMP task can be run asynchronously with other tasks, thus allowing the update memory transfer to occur while a target region is executing. The combination of these clauses allows for the construction of GPU code that has asynchronous memory transfers to and from the GPU while also maintaining correct computation through clearly established task dependence relations by which these asynchronous transfers must finish.

Figure 3.5 is an example of split target region code with asynchronous memory transfers within a common device data environment. In this example the data element C is not needed until the target region at line 9, thus its mapping in the target data region in line 2 is only to return to the host after all work finishes. The transfer to the GPU for C instead begins on line 3 where it is declared asynchronous by the nowait clause. With the pair of depend clauses in lines 3 and 9 ensuring the transfer must be completed before any computation on the target region in line 9 can begin. Furthermore the array A

```

1 int a;

#pragma omp targe data map(to: A[:S], B[:S]) map(from: C[:S]) {

#pragma omp target update to(C[:S]) depend(out: a) nowait

3

#pragma omp target teams distribute parallel for

for () {

... // Parallel work involving A and B

6

7

#pragma omp target update from(A[:S]) nowait

9

#pragma omp target teams distribute parallel for depend(in: a)

for () {

10

... //Parallel work involving B and C

11

12

13 }

```

Figure 3.5: The split OpenMP GPU code with asynchronous memory transfers.

can be transferred back to the host memory asynchronously as it is not used in the second target region. Thus the memory transfer of A back to the host is moved to line 8, after the first target region computation and it is declared to be asynchronous.

As per vendor specification, asynchronous memory transfers require that the transferred data be page-locked i.e. *pinned* on the host. A pinned page cannot be swapped out to disk and enables DMA transfers via the memory controller, bypassing the CPU. To enable asynchronous transfers, the pinning must be done through the CUDA API to allocate/free pinned memory or to pin pre-allocated heap memory. The invocation of these API functions and the actual pinning of the memory introduce additional overheads but also leads to faster memory transfers. Memory capacity constraints of the target device are not affected by the transformed kernel. The amount of data required to be present on the device at a given time is reduced in the best case, and is left unaffected in the worst.

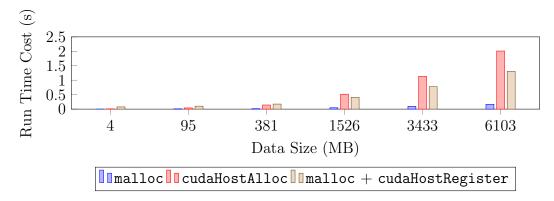

The experimental results shown in Figure 3.6 illustrate the cost of pinning memory using the CUDA API. As a point of comparison, the time taken to allocate non-pinned memory with a call to malloc and release with free is provided. cudaHostAlloc measurements include releasing memory with cudaHostFree. Finally, the cudaHostRegister results include the cost

Figure 3.6: Run time cost of allocating and freeing memory with the three methods.

of allocating with malloc, pinning with cudaHostRegister, unpinning with cudaHostFree and releasing with free. Allocating and freeing non-pinned memory takes far less time compared to the same with pinned memory for both methods that the CUDA API provides at all data sizes. However the cost of the cudaHostAlloc method grows considerably with greater data sizes while the cost of the cudaHostRegister method grows less in comparison, overtaking the other in performance. This is, in part due to cudaHostRegister not zeroing the data it pins, unlike cudaHostAlloc which does.

We use the cudaHostRegister API to pin user-allocated memory in our experiments. The main trade-off to consider when implementing kernel asynchronous data transfers is to offset the overhead of pinning memory through faster transfers enabled by pinned memory and overlapping transfer with computation. Pinning memory also has the effect of reducing the overall memory available on the host for other processes, which can possibly stifle host computation. An important factor to consider when pinning memory is the operating system's default page size. We have found that pinning the same amount of memory was up to 10× faster on a POWER8 host with 64KB pages than on a x86 Haswell host with 4KB pages.

A synthetic experiment to illustrate the balancing of the costs and benefits of asynchronous memory transfer was designed with three simple GPU kernels  $(k_1, k_2, k_3)$  that execute within a shared data environment;  $k_2$  modifies one data object from the CPU whose results must be returned, the object is not

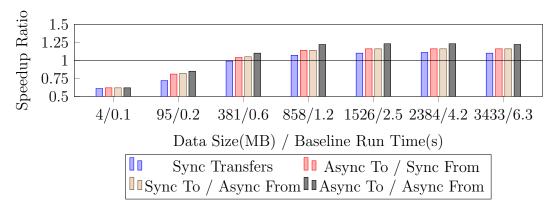

Figure 3.7: Speedup of the four versions pinning memory over the baseline version.

used by the first or third kernel. Thus, asynchronous transfer is possible both to transfer this data object to the GPU and back to the CPU. Furthermore,  $k_1$ and k<sub>3</sub> both have enough computation to fully hide the asynchronous memory transfers. The experiment's results with a varying size of the object modified by k<sub>2</sub> are shown in Figure 3.7. The baseline version uses unpinned memory and synchronous transfers. Four versions using pinned memory were constructed for comparison: (1) sync transfers; (2) async to/sync from; (3) sync to/async from; (4) async to/async from. The run time measured includes the time needed to allocate and free memory. The graph outlines the speedup ratio in total execution time for each of the four pinned memory versions compared to the baseline version. The horizontal axis shows both the size of the object transferred and the baseline run time measured in seconds. The results show that as the size of the transferred object increases, the additional cost of pinning memory becomes less relevant. For larger objects, even though simply pinning the memory pages yields performance gains, asynchronous memory transfers produce additional benefits.

### 3.3 Pipelining Data Transfer and Parallel Loop Execution

A more ambitious code transformation that utilizes the faster transfer to/from pinned memory and asynchronous communication and computation consists of

Figure 3.8: A GPU parallel regions structure after being broken up into 4 tiles.

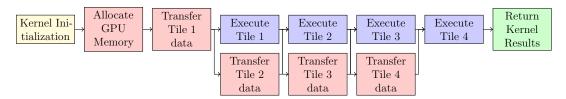

breaking a singular parallel loop into multiple loops. Known as *tiling* in compiler literature, this transformation produces multiple sub-loops (tiles) which are then placed in separate target regions. After this transformation the data transfer required for the original loop may be split into several asynchronous data transfers for data elements required by the respective tiles. Ideally, each tile should use different, contiguous, large chunks of data. The goal is to overlap the transfer with computation. In the evaluation prototype OpenMP depend clauses are used to ensure that each data transfer is finished before the corresponding tile executes. Transmission of tile results back to the host can also be added to this pipeline. Pipelining can greatly improve the run-time performance of programs with large data transfers, when the execution time of the split loop is long enough to compensate for the overhead of setting up data transfers and pinning memory.

Figure 3.8 illustrates how the execution of a parallel region can be pipelined to overlap memory transfers with computation. The single parallel-loop GPU kernel is split into four tiles which allows the memory transfers required for the latter three tiles to be hidden underneath the previous tiles' execution with asynchronous transfers. Furthermore if the execution of the tiles are long enough to cover the runtime of the memory transfers then the total cost of the transfers may be as low as 1/4 of the original cost.

The Polybench benchmark ATAX is a good candidate to benefit from this transformation. The original benchmark's first parallel region, shown in Figure 3.9, has the majority of its runtime dependent on the memory transfer of the data object A to the GPU in line 1.

Figure 3.10 shows the code after the loop is divided into four tiles and the transfer of A split into four OpenMP target update calls. The first

```

#pragma omp target teams distribute parallel for map(to: A[:NX*NY

], x[:NY]) map(from: tmp[:NX]) {

for(int i = 0; i < NX; i++) {

tmp[i] = 0;

for(int j = 0; j < NY; j++)

tmp[i] = tmp[i] + A[i*NY+j] * x[j];

}

}</pre>

```

Figure 3.9: First parallel region in ATAX before pipelining.

call in line 2 is not asynchronous as it must be done before the first tile execution starts. The remaining three transfers in line 6 are asynchronous and start before the preceding tile execution to overlap communication and computation. The depend clauses in the asynchronous transfers are needed to synchronize the end of the data transmission with the execution of the corresponding tile. Figure 3.10 shows a proof-of-concept manually implemented code change. A sufficiently-capable compiler should be able to apply a similar code transformation when equipped with memory access-pattern analysis to be able to separate tile data chunks, among other code safety analyses.

```

1 int S[4];

#pragma omp target update to(A[0:(NX/4)*NY])

3 | for(int s = 0; s < 4; s++)

4 {

if (s < 3)

5

#pragma omp target update to(A[((s+1)*NX/4)*NY:((s+2)*NX/4)*NY)

]) depend(out: S[s+1]) nowait

#pragma omp target teams distribute parallel for depend(in: S[s

7

])

for(int i = (s*NX/4); i < ((s+1)*NX/4); i++) {

8

tmp[i] = 0;

9

for(int j = 0; j < NY; j++)

10

tmp[i] = tmp[i] + A[i*NY+j] * x[j];

11

}

12

13 }

```

Figure 3.10: ATAX region after being broken up into four tiles for pipelining.

### 3.4 Custom Grid Geometry

A grid geometry defines the number of CTAs and the number of threads per CTA assigned to execute a GPU kernel. A typical GPU has a number of Streaming Multiprocessor (SM) cores that can each issue instructions for two groups of 32 threads (warps) in each cycle. An SM can maintain the state of thousands of threads in-flight, and thus can context switch execution from a warp waiting on data accesses to other warps in order to hide memory-access latency.

Each SM has a fixed-size register file, giving each CTA a register budget. At any given time the number of CTAs that can be scheduled is limited by the size of the register file. Similarly, each SM has a fixed amount of shared memory which is shared by all CTAs running on the SM. Thus, the number of CTAs simultaneously executing on an SM is also constrained by the individual CTA's shared memory use. Additional CTAs that cannot be scheduled due to these and other hardware resource limitations are queued for later execution. GPU occupancy is the percentage of available GPU threads that are used by a given kernel.

Some parallel regions with relatively low parallelism perform better when not using all available threads. A compiler can analyze parallel loops in a target region to select the most performant grid geometry. However, a single grid geometry has to be selected for an entire target region leading to a compromise that performs relatively well for all the loop nests in the region. Grid geometry specialized to each individual parallel loop, made possible by target region fission, can lead to significant performance improvements.

Lloyd et al. propose a compiler heuristic, based on static analysis and runtime loop tripcount data, for the selection of a grid geometry calculated by the amount of parallelism in each loop nest [37]. The heuristic takes into account the usage of registers and shared memory for each thread and CTA as it seeks to maximize the GPU occupancy. However, maximizing occupancy can often lead to far worse performance because it leads to saturation of other hardware resource, such as the memory subsystem in heavily memory-bound

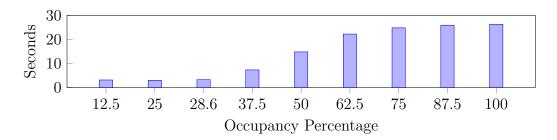

Figure 3.11: Runtime results by occupancy of SYRK at tripcount 4000.

codes. An example of this effect occurs in the SYRK benchmark shown in Figure 3.11. At a tripcount of 4000 the best performance is achieved around 25% occupancy which is close to the Clang-YKT default of roughly 28.6% (128 CTAs on this GPU). For this case the heuristic proposed by Lloyd makes a poor choice of geometry because in seeking to maximize occupancy it does not consider memory-bandwidth saturation. Maximum occupancy produces a Unified Cache throughput of 19.742 GB/s compared to a throughput of 183.001 GB/s at the optimal occupancy of 25%; moreover, the observed Global Load Throughput of 751.8 GB/s at optimal occupancy versus 81.5 GB/s at maximal, and the respective Global Store Throughput is 91.5 and 9.9 GB/s. These metrics support the intuition that memory bus saturation can severely limit performance at high occupancy.

This exception to the grid geometry formula led to the formulation of an improved grid-geometry selection strategy for the cases where the optimal occupancy is lower than the maximum. These cases fall into the broad category of parallel regions with a high amount of parallelism exposed by the program (high parallel-loop tripcounts) and result from memory-bandwidth saturation due to a large number of memory requests. The results of this performance study allows for the classification of these cases of massively parallel memory-bound kernels into two subcategories:

Uncoalesced Kernels are highly memory-bound due to uncoalesced memory accesses in large tripcount parallel loops. Uncoalesced memory accesses being loads and stores to global memory where data locations accessed by adjacent threads in a warp are not grouped together closely enough, hence the warp must perform several memory accesses to satisfy all the threads in a warp. This subcategory includes the benchmarks SYRK with tripcount of 1000 or higher and COVAR with tripcounts of 12000 or higher. SYRK falls into this subcategory due to the two high tripcount outer loops of its longest running parallel region being collapsed for high parallelism and an innermost loop containing an uncoalesced memory access which is performed sequentially by each thread. COVAR has a similar structure except without a collapse of the two outer loops and two uncoalesced memory accesses instead of one inside the inner loop. A close examination of the execution of the SYRK benchmark in the Nvidia Visual Profiler, reveals that the best performance is observed when the ratio between attempted memory transaction count and the memory throughput is the lowest — when the most data is transferred with the fewest requests. The grid geometry affects this ratio because more warps generate more requests when memory accesses are not coalesced.

The SYRK performance study shown in Figure 3.11 indicates that there is an opportunity to improve the grid-geometry selection by taking into consideration memory-bandwidth saturation. In a supplementary performance study we altered the ratio of requests/memory throughput in SYRK by adding and removing dummy uncoalesced memory accesses. This study yielded a pattern of optimal occupancy halving roughly when the number of uncoalesced memory accesses double. This insight can be used to predict the optimal occupancy for a parallel region. To analyze this pattern further a synthetic experiment was designed in which a more generalized program similar to SYRK was created consisting of a simple summation of the rows of k different  $N \times N$  matrices to produce a single matrix. The summation statement is performed within a triple-nested loop with each tripcount being 5000 and the summation involves exclusively uncoalesced memory accesses (row-major matrix accesses). The experiment was then performed with different numbers of uncoalesced memory

| Number of Accesses   1  | 2     | 3    | 4    | 5    | 6    | 7    | 8    | 9    | 10   |

|-------------------------|-------|------|------|------|------|------|------|------|------|

| Optimal Occupancy   25% | 12.5% | 6.3% | 6.3% | 6.3% | 6.3% | 6.3% | 4.0% | 4.0% | 3.1% |

Table 3.1: Optimal occupancy for a massively parallel memory-bound kernel at varying numbers of uncoalesced memory accesses with tripcount 5000.

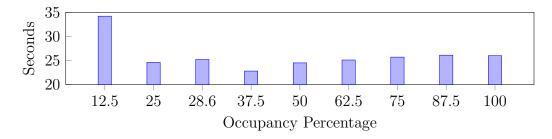

Figure 3.12: Runtime results by occupancy of FDTD-2D at tripcount 15000.

accesses to find the optimal occupancy for each. The results of the experiment in Table 3.1 show the similar optimal occupancy pattern that was found in the study of SYRK, indicating a general pattern. This study and experiment indicates that the heuristic for grid-geometry selection introduced by Lloyd et al should be augmented to account for memory-request saturation [37].

Coalesced Kernels have high memory utilization because of parallel loops with very large tripcounts and several memory accesses. Coalesced memory accesses are the opposite of uncoalesced and require only one access to bring over all data required by a warp of threads. This category includes the benchmarks FDTD-2D and LUD at high tripcounts. Lower occupancy results in better performance but the effect is less significant as shown in the results for the experiment study of FDTD-2D in Figure 3.12. This category should also be taken into consideration in an augmented version of the grid-geometry-selection heuristic.

# 3.5 Estimating Potential Benefits of Transformations

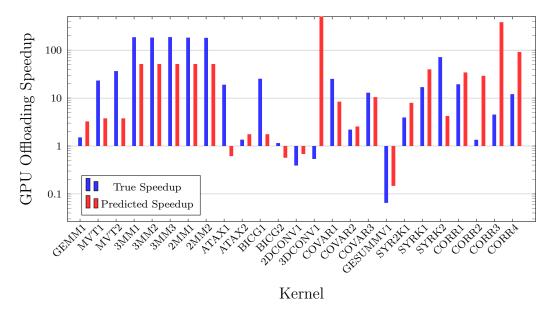

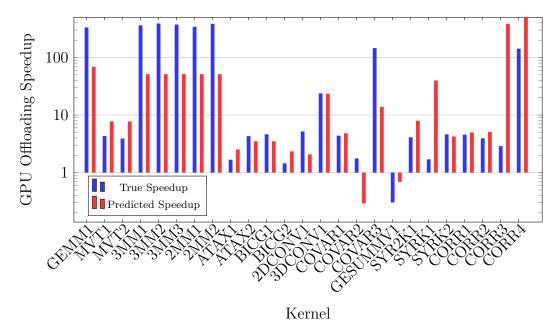

The goal of this experimental evaluation is to estimate the potential performance benefits of the proposed transformations to inform a design-team's decision to include them in a compiler. The results in this section are based