**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films

the text directly from the original or copy submitted. Thus, some thesis and

dissertation copies are in typewriter face, while others may be from any type of

computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality illustrations

and photographs, print bleedthrough, substandard margins, and improper

alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript

and there are missing pages, these will be noted. Also, if unauthorized

copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and continuing

from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations appearing

in this copy for an additional charge. Contact UMI directly to order.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

**UMI**°

# **NOTE TO USERS**

This reproduction is the best copy available.

**UMI**

# **University of Alberta**

# Design, Implementation and Testing of a Multilevel DRAM with Adjustable Cell Capacity

by

Yunan Xiang (C)

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Master of Science

Department of Electrical & Computer Engineering

Edmonton, Alberta Spring 2002

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Otawa ON K1A 0N4 Canada

Your Sto Yours rélérance

Our ille Nate nillimen

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-69779-7

**University of Alberta**

**Library Release Form**

Name of Author: Yunan Xiang

Title of Thesis: Design, Implementation and Testing of a Multilevel DRAM with

Adjustable Cell Capacity

Degree: Master of Science

Year this Degree Granted: 2002

Permission is hereby granted to the University of Alberta Library to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly or scientific

research purposes only.

The author reserves all other publication and other rights in association with the copyright in the thesis, and except as herein before provided, neither the thesis nor any substantial portion thereof may be printed or otherwise reproduced in any

material form whatever without the author's prior written permission.

Yunan Xiang

Ting Show

Apt. 507, 11147-82 Ave.

Edmonton, AB T6G 0T5

Apr. 15, 2002

# **University of Alberta**

# **Faculty of Graduate Studies and Research**

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies and Research for acceptance, a thesis entitled *Design*, *Implementation and Testing of a Multilevel DRAM with Adjustable Cell Capacity* by *Yunan Xiang* in partial fulfillment of the requirements for the degree of Master of Science.

Supervisor: Dr. Bruce F. Cockburn

Supervisor: Dr. Duncan G. Elliott

A & Ellist

Professor: Dr. Xiaoling Sun

Professor: Dr. Douglas M. Gingrich

Date Date

### **ABSTRACT**

By storing more than one bit per memory cell, MultiLevel Dynamic Random-Access Memory (MLDRAM) explores an additional dimension to increase the percell storage capacity over conventional two-level DRAM. A well-balanced and robust MLDRAM scheme was proposed previously by Birk, Elliott and Cockburn. We designed and implemented a test chip for this MLDRAM in TSMC's 0.18-micron CMOS technology. The test chip has an adjustable cell capacity that can be selected from 2, 3, 4 and 6 levels per cell, corresponding to 1, 1.5, 2 and 2.5 bits per cell. Prototypes of the test chip were verified using an Agilent 81200 digital IC tester. Most of the cells in operational chips were found to work. However, small voltage offsets affecting the signal and reference cells cause read errors for some cells. A follow-up project would be to characterize the offset problem in greater detail and to design an improved test chip.

### **ACKNOWLEDGEMENTS**

This research was supported by Micronet R&D, MOSAID Technologies Inc., ATMOS Corporation, the Canadian Microelectronics Corporation, the Natural Sciences and Engineering Research Council of Canada, and the University of Alberta. I would like to thank everybody who offered technical support and helpful suggestions for this project. Especially, I would like to express my great gratitude to my supervisors Bruce Cockburn and Duncan Elliott for providing me with this opportunity to study memories and for all they have taught me. Also, I would like to thank John Koob and Tyler Brandon for helping me with the workstations and the CAD tools. The test chip layout design and the evaluation of the silicon prototypes were both teamwork in the VLSI lab at the University of Alberta. Participants in the chip design and layout were Tyler Brandon, Dan Leder, and Julien Lamoureux. Participants in the chip prototype testing were Michael Hume, Tyler Brandon, Dan Leder, Craig Joly and Michael Redeker.

# **Table of Contents**

| Chapte | r 1 Introduction                             | 1  |

|--------|----------------------------------------------|----|

| 1.1 S  | Semiconductor Memory                         | 1  |

| 1.2 D  | DRAM Technology                              | 3  |

| 1.3 N  | MLDRAM Technology                            | 6  |

| 1.4 T  | Thesis Outline                               | 9  |

| Chapte | er 2 Previous Work                           | 11 |

| 2.1 B  | Basic DRAM Circuits                          | 11 |

| 2.1.1  | The DRAM Cell Array                          | 12 |

| 2.1.   | .1.1 Rows and Columns                        | 12 |

| 2.1.   | .1.2 Folded Bitlines and Twisted Bitlines    | 13 |

| 2.1.   | .1.3 Friendly Cells and Dummy Cells          | 15 |

| 2.1.2  | The DRAM Core                                | 16 |

| 2.1.   | .2.1 The Sense Amplifier                     | 17 |

| 2.1.   | .2.2 Data Buses                              | 20 |

| 2.1.3  | The DRAM Periphery                           | 21 |

| 2.1.4  | DRAM Floorplanning                           | 22 |

| 2.2 D  | DRAM Operations                              | 23 |

| 2.3 E  | Embedded DRAMs                               | 26 |

| 2.4 N  | MLDRAM Circuits and Techniques               | 27 |

| 2.4.1  | Furuyama's MLDRAM                            | 28 |

| 2.4.2  | Gillingham's MLDRAM                          | 31 |

| 2.4.3  | Birk's MLDRAM                                | 35 |

| 2.4.   | .3.1 Circuitry                               | 35 |

| 2.4.   | 3.2 Operations                               | 37 |

| 2.4.   | 3.3.3 Increasing the Number of Signal Levels | 41 |

| 2.4.   | .3.4 Advantages and Disadvantages            | 42 |

| Chapter 3  | Test Chip Design                                         | 44         |

|------------|----------------------------------------------------------|------------|

| 3.1 Test   | Chip Design Overview                                     | 4          |

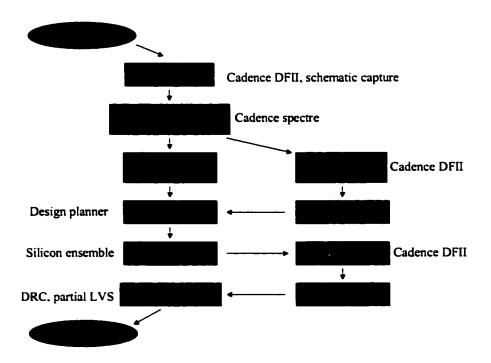

| 3.2 The I  | Design Flow                                              | 4          |

| 3.3 Deta   | iled Design                                              | 5          |

| 3.3.1      | The Core                                                 | 5          |

| 3.3.1.1    | The Memory Cells                                         | 5          |

| 3.3.1.2    | Friendly Cells and Dummy Cells                           | 5          |

| 3.3.1.3    | The Sense Amplifiers and Sub-bitline Connections         | 5          |

| 3.3.1.4    | Boost Circuits                                           | 5          |

| 3.3.1.5    | Row and Column Address Scrambling                        | 50         |

| 3.3.2      | The Periphery                                            | 5          |

| 3.3.2.1    | Row Access                                               | 58         |

| 3.3.2.2    | Column Access                                            | 60         |

| 3.3.2.3    | Data IO                                                  | 60         |

| 3.3.2.4    | Chip Pads                                                | 6          |

| 3.4 Chip   | Packaging and Fixturing                                  | 6          |

| Chapter 4  | Design Verification and Simulation                       | on 65      |

| 4.4        | and Manufff and Tour                                     | •          |

|            | gn Verification                                          |            |

|            | ematic Simulation Results  Circuit Simulation Background |            |

|            | ·                                                        |            |

| 4.2.2      | Simulation Results                                       | 6          |

| 4.2.2.1    | Simulations for 6-levels-per-cell Operation              | 6          |

| 4.2.2.2    | Simulations for 4-levels-per-cell and 3-levels-per-cell  | Operation7 |

| 4.2.2.3    | Simulations for 2-levels-per-cell Operation              | 8          |

| 4.2.3      | Discussion                                               | 8          |

| <b>-</b> • |                                                          | _          |

| Chapter 5  | Test Chip Evaluation                                     | 9          |

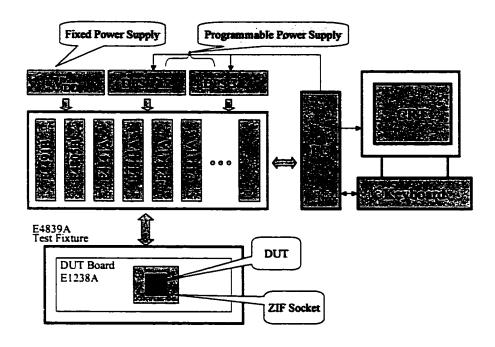

| 5.1 The    | Tester and the DUT Board Interface                       | 0          |

| 5.2  | Test Re  | esults                   | 94  |

|------|----------|--------------------------|-----|

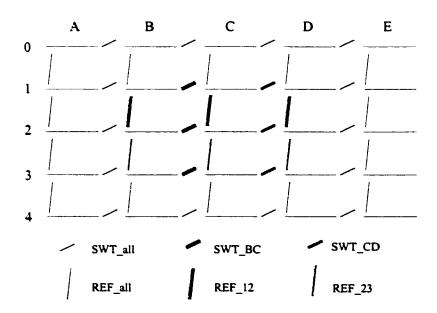

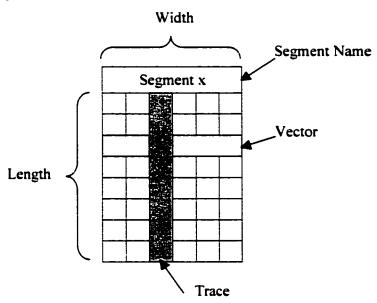

| 5.2  | .1 Tes   | st Vector Generation     | 95  |

| 5.2  | .2 A B   | Basic Functional Test    | 97  |

| 5.2  | .3 A C   | Cell Retention Time Test | 99  |

| 5.3  | Conclu   | sions                    | 101 |

| Chap | ter 6    | Conclusions              | 102 |

| 6.1  | Chip De  | esign and Simulation     | 102 |

| 6.2  | Chip Ev  | valuation                | 103 |

| 6.3  | Future ' | Work                     | 103 |

| Refe | rences   | ••••••                   | 105 |

| Appe | endix A  | Test Results for Chip 2  | 107 |

| Appe | endix B  | Test Chip Bitmaps        | 113 |

# **List of Tables**

| Table 2-1. Data conversion table                                           | 30 |

|----------------------------------------------------------------------------|----|

| Table 2-2. Restore voltage conversion                                      | 35 |

| Table 2-3. Reference generation for Birk's MLDRAM                          | 40 |

| Table 2-4. Reference generation for a 5-levels-per-cell MLDRAM             | 42 |

| Table 3-1. Cell capacities using cell pairs                                | 44 |

| Table 3-2. Configuration of the VDC reference generation voltage sources   | 45 |

| Table 3-3. Assignment of waveforms to the reference and generate wordlines | 59 |

| Table 3-4. Column and data bus decoding in one section                     | 61 |

| Table 3-5. Chip pads                                                       | 63 |

| Table 4-1. Comparison of voltage signals for 4-levels-per-cell operation   | 87 |

| Table 4-2. Output data conversion table                                    | 89 |

| Table 5-1, ML5 pin list                                                    | 93 |

| Table 5-2. Percentage of good cells                                        | 99 |

# **List of Figures**

| Figure 1-1. A 1T-1C DRAM cell                                                  | 3  |

|--------------------------------------------------------------------------------|----|

| Figure 1-2. DRAM charge sharing                                                | 4  |

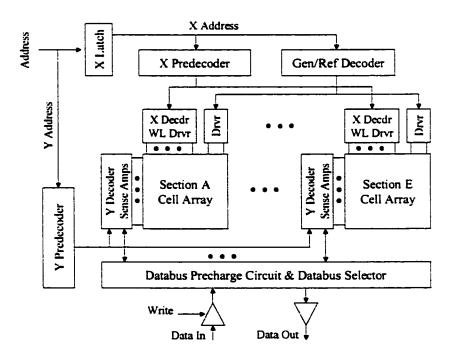

| Figure 1-3. A DRAM block                                                       | 6  |

| Figure 1-4. A two-bit-per-cell storage scheme                                  | 8  |

| Figure 2-1. A DRAM cell array                                                  | 12 |

| Figure 2-2. Open-bitline and folded-bitline array architectures                | 13 |

| Figure 2-3. Bitline twisting schemes                                           | 14 |

| Figure 2-4. DRAM core circuitry                                                | 16 |

| Figure 2-5. Standard sense amplifier block                                     | 18 |

| Figure 2-6. I/O transistor connections                                         | 19 |

| Figure 2-7. The basic sense amplifier                                          | 19 |

| Figure 2-8. Wordline driver from ATMOS Corporation                             | 21 |

| Figure 2-9. Floorplan of a 256-Mb DDR-SDRAM                                    | 23 |

| Figure 2-10. Schematic of a DRAM bitline pair                                  | 24 |

| Figure 2-11. Basic read/write timing diagram for the DRAM core                 | 25 |

| Figure 2-12. The schematic and layout of ATMOS' SoC-RAM cell                   | 27 |

| Figure 2-13. Furuyama's basic sub-bitline block design                         | 28 |

| Figure 2-14. The sensing operation in Furuyama's scheme                        | 29 |

| Figure 2-15. Timing diagram for Furuyama's MLDRAM scheme                       | 30 |

| Figure 2-16. Schematic of Gillingham's MLDRAM                                  | 32 |

| Figure 2-17. Timing diagram for Gillingham's MLDRAM                            | 33 |

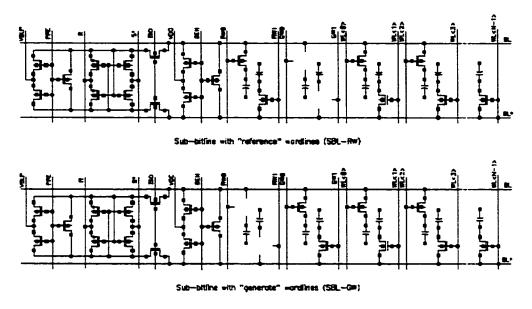

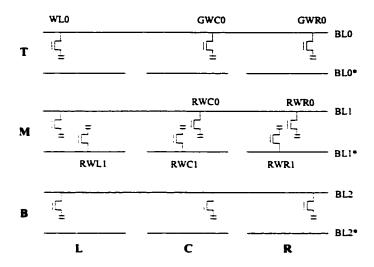

| Figure 2-18. Sub-bitline designs for Birk's MLDRAM                             | 36 |

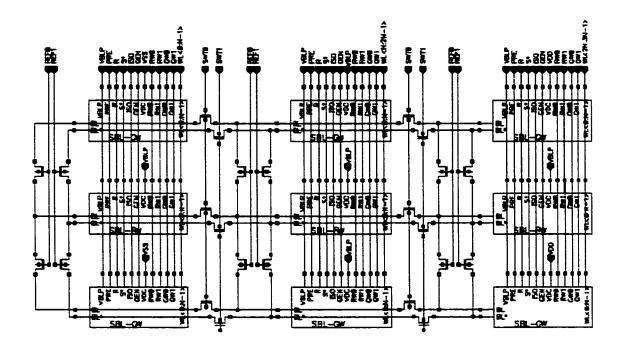

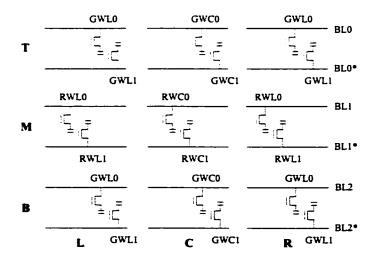

| Figure 2-19. Schematic of Birk's MLDRAM                                        | 37 |

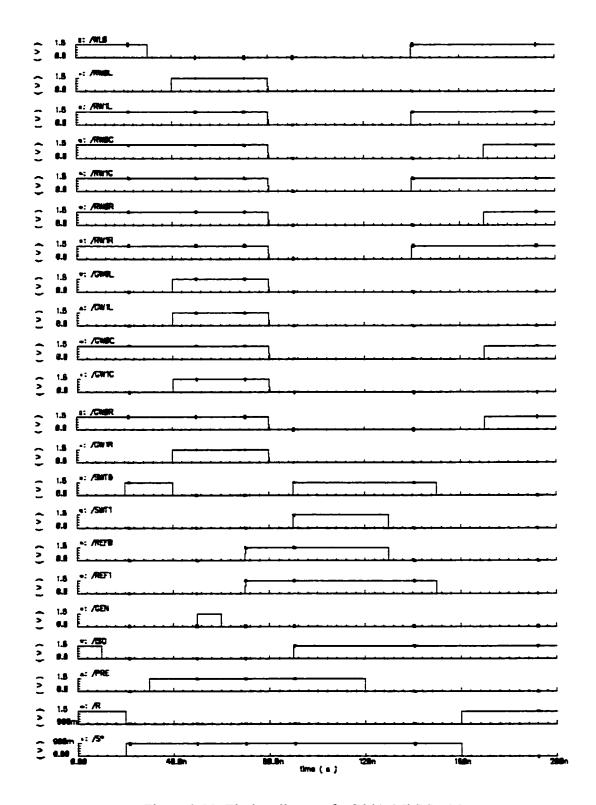

| Figure 2-20. Timing diagram for Birk's MLDRAM                                  | 38 |

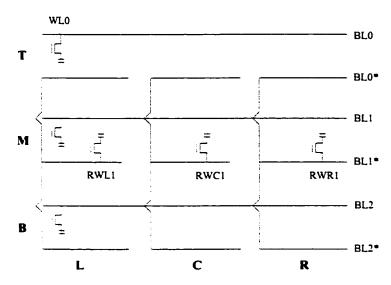

| Figure 2-21. Sub-bitlines with memory cells connected for restoring            | 39 |

| Figure 2-22. Sub-bitlines with memory cells connected for reference generation | 39 |

| Figure 2-23. Sub-bitlines with memory cells connected for sensing              | 41 |

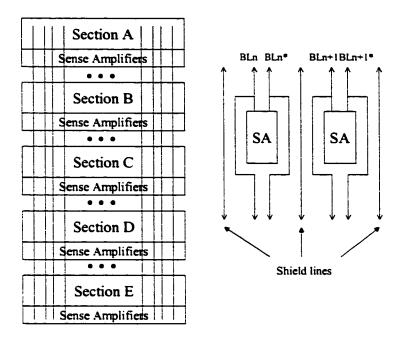

| Figure 3-1. The basic 5-by-5 sub-bitline array of the test chip                | 46 |

| Figure 3-2. Simplified test chip architecture                                  | 47 |

| Figure 3-3. Test chip design flow                                              | 48 |

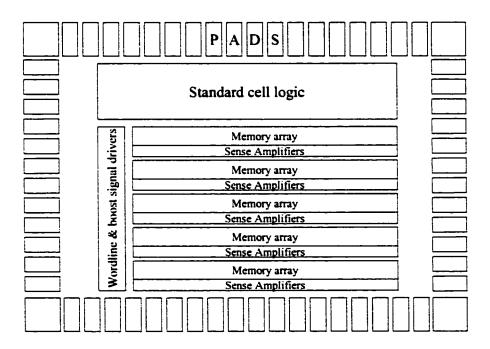

| Figure 3-4. Test chip floorplan                                                | 50 |

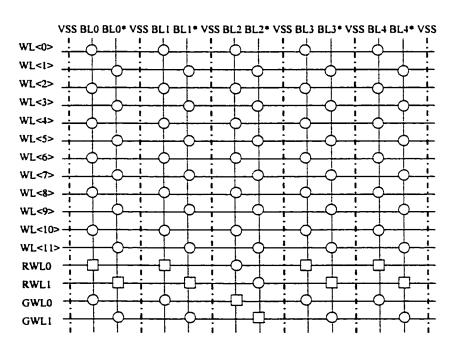

| Figure 3-5. Friendly cells in a memory array                              | 53  |

|---------------------------------------------------------------------------|-----|

| Figure 3-6. Sub-bitline connections between memory arrays                 | 55  |

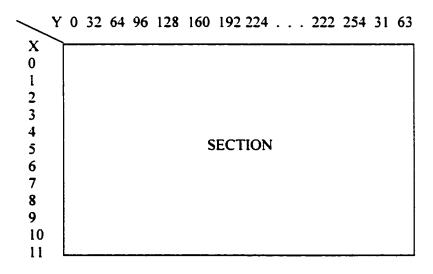

| Figure 3-7. Row and column address mapping in one section                 | 56  |

| Figure 3-8. Cell layout in one section                                    | 57  |

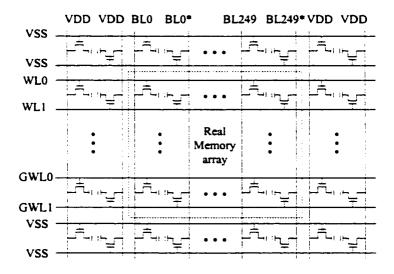

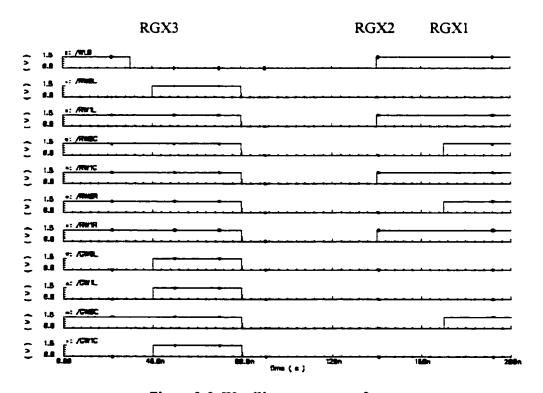

| Figure 3-9. Wordline access waveforms                                     | 58  |

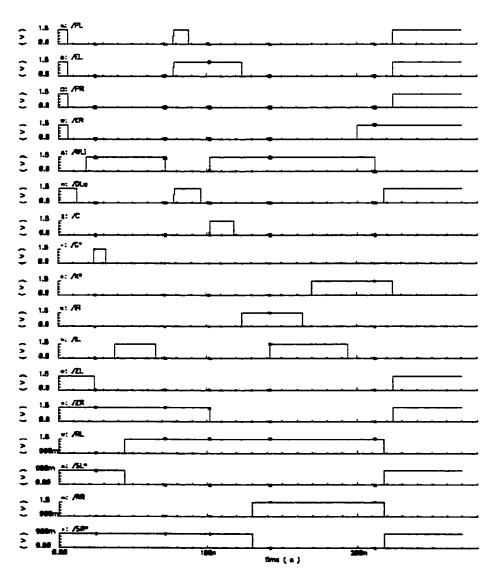

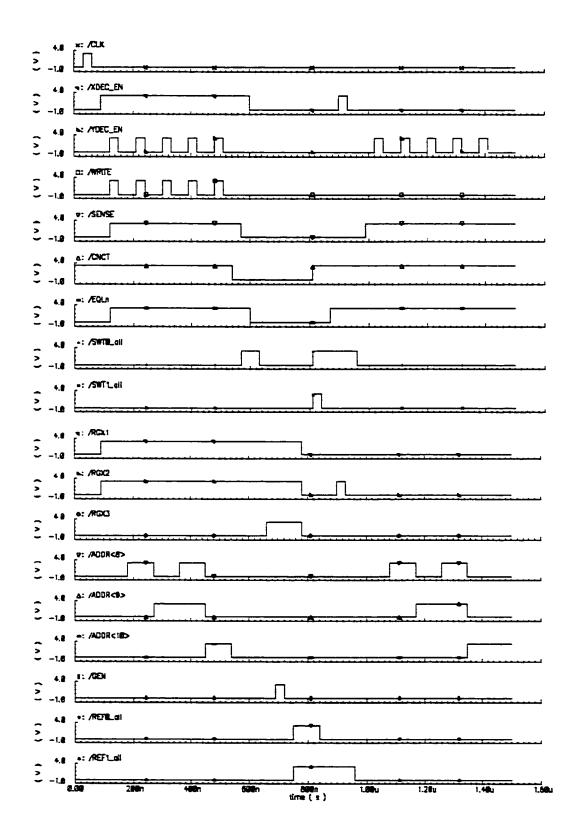

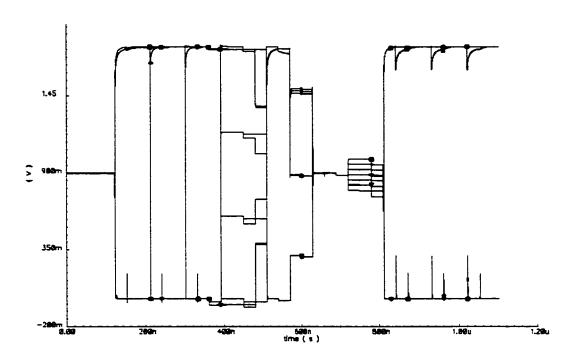

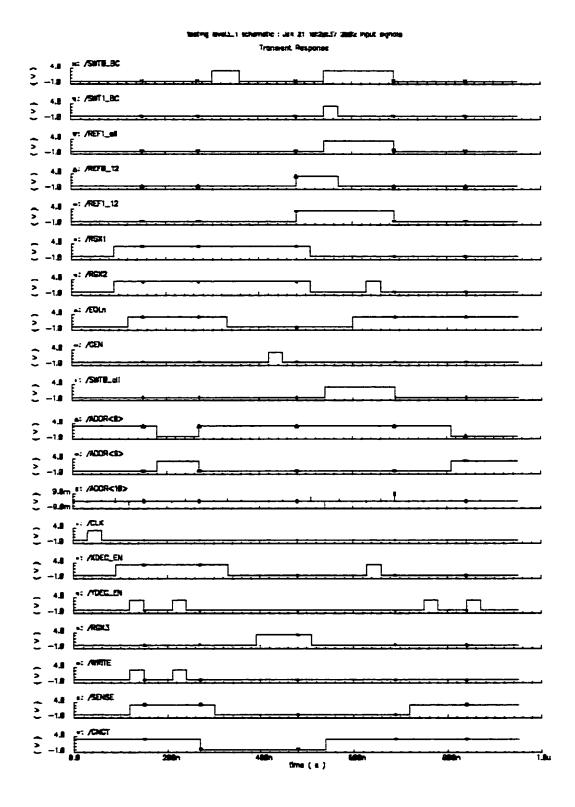

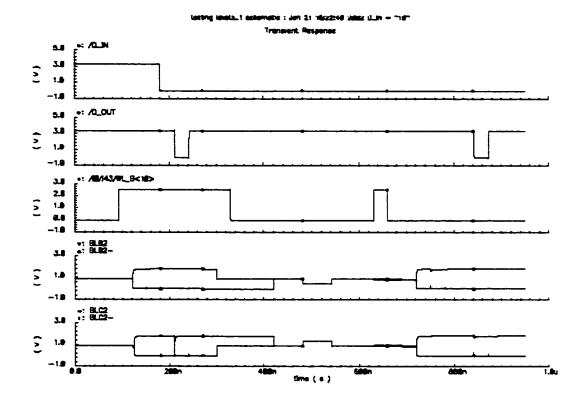

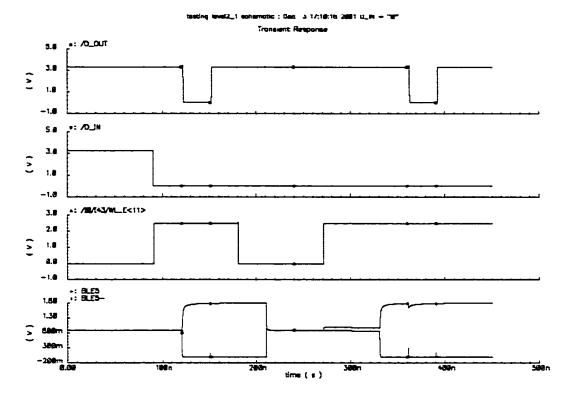

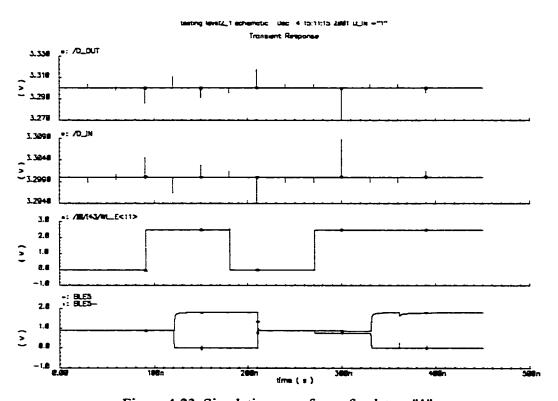

| Figure 4-1. Stimulus waveforms for 6-levels-per-cell operation            | 68  |

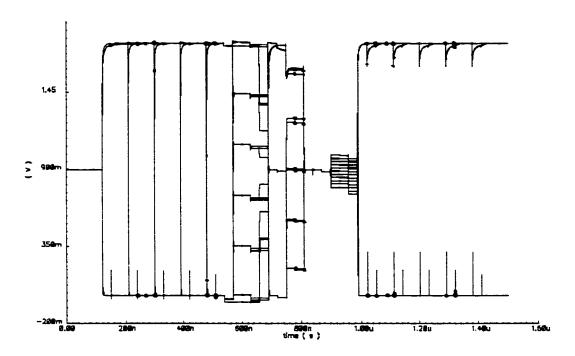

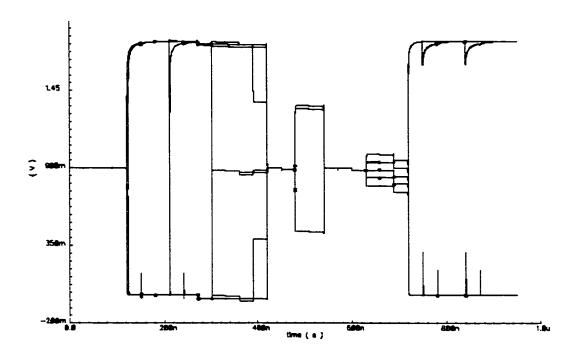

| Figure 4-2. Bitline and reference signals in 6-levels-per-cell operation  | 72  |

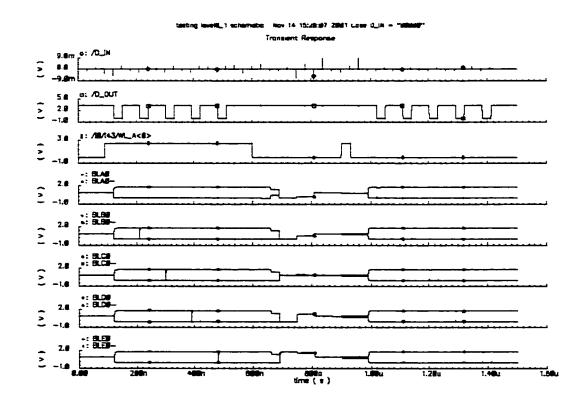

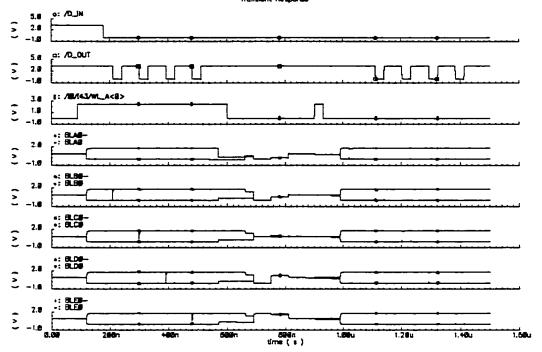

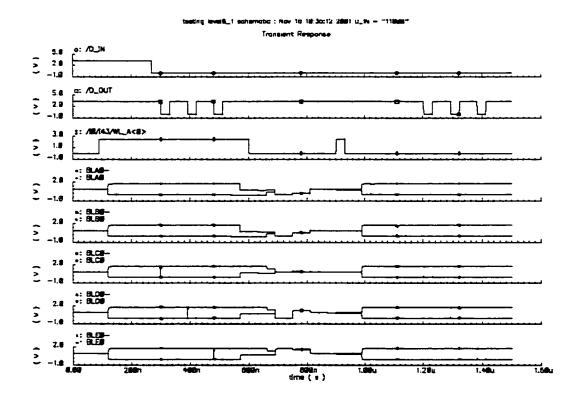

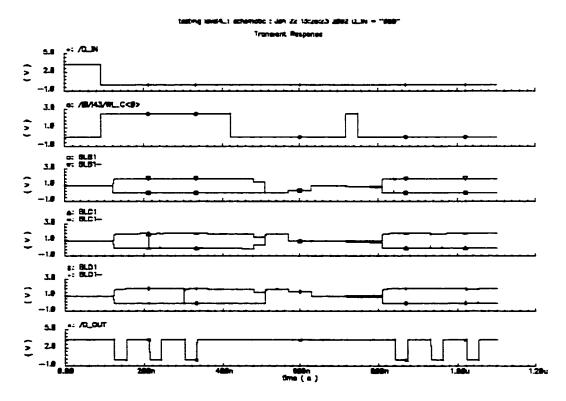

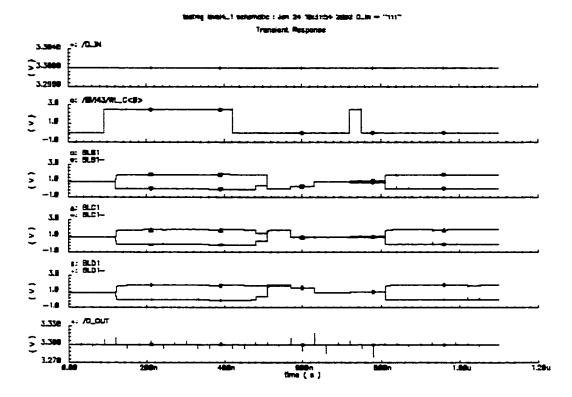

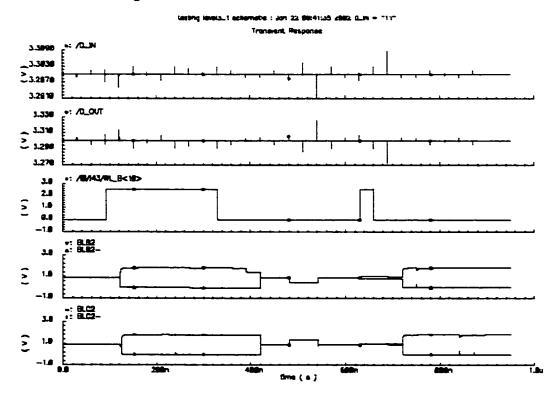

| Figure 4-3. Simulation waveforms for data = "00000"                       | 72  |

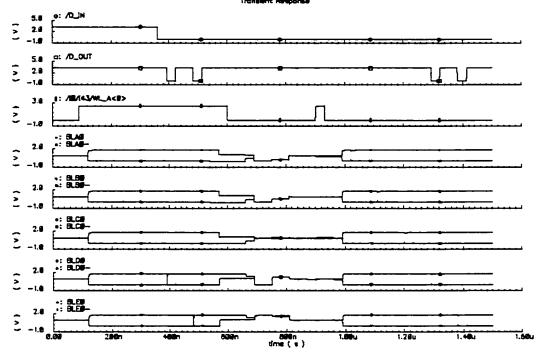

| Figure 4-4. Simulation waveforms for data = "10000"                       | 73  |

| Figure 4-5. Simulation waveforms for data = "11000"                       | 73  |

| Figure 4-6. Simulation waveforms for data = "11100"                       | 74  |

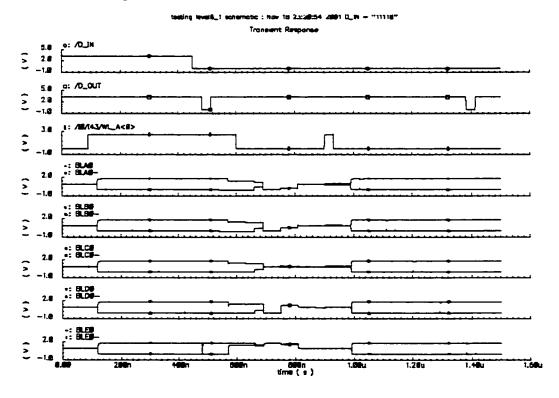

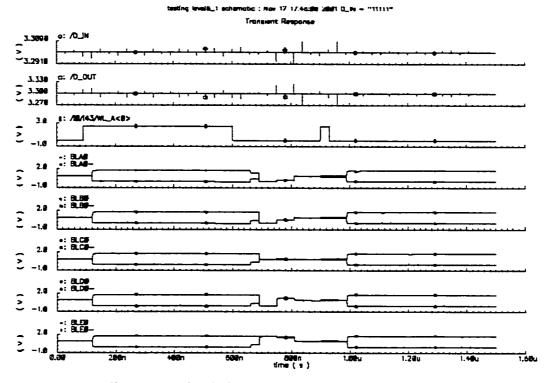

| Figure 4-7. Simulation waveforms for data = "11110"                       | 74  |

| Figure 4-8. Simulation waveforms for data = "11111"                       | 75  |

| Figure 4-9. Stimulus waveforms for 4-levels-per-cell operation            | 77  |

| Figure 4-10. Bitline and reference signals in 4-levels-per-cell operation | 78  |

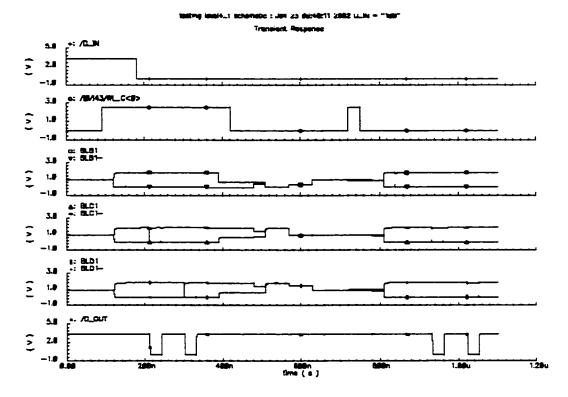

| Figure 4-11. Simulation waveforms for data = "000"                        | 78  |

| Figure 4-12. Simulation waveforms for data = "100"                        | 79  |

| Figure 4-13. Simulation waveforms for data = "110"                        | 79  |

| Figure 4-14. Simulation waveforms for data = "111"                        | 80  |

| Figure 4-15. Stimulus waveforms for 3-levels-per-cell operation           | 81  |

| Figure 4-16. Bitline and reference signals in 3-levels-per-cell operation | 82  |

| Figure 4-17. Simulation waveforms for data = "00"                         | 82  |

| Figure 4-18. Simulation waveforms for data = "10"                         | 83  |

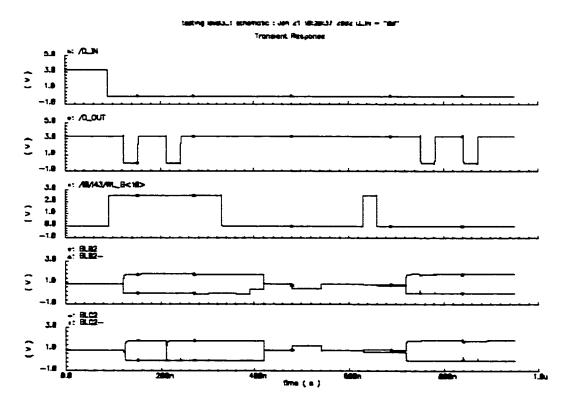

| Figure 4-19. Simulation waveforms for data = "11"                         | 83  |

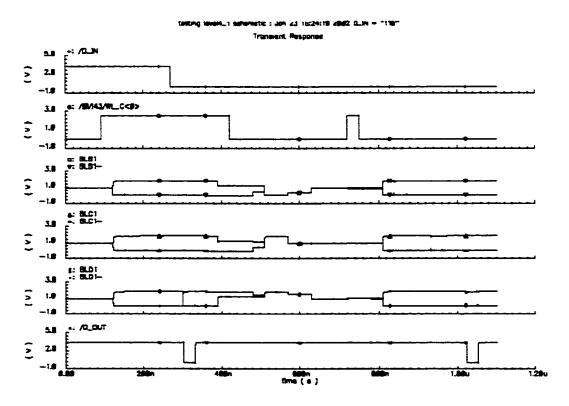

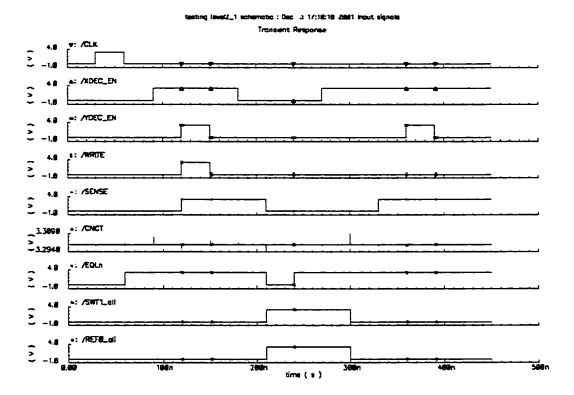

| Figure 4-20. Stimulus waveforms for 2-levels-per-cell operation           | 85  |

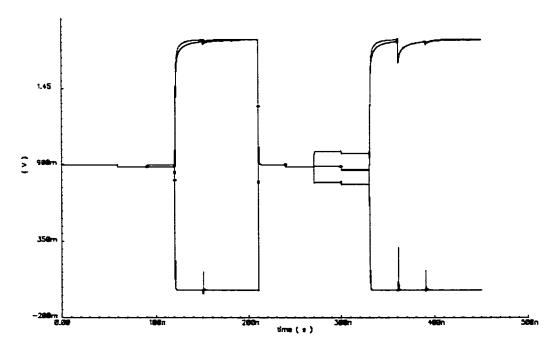

| Figure 4-21. Bitline and reference signals in 2-levels-per-cell operation | 85  |

| Figure 4-22. Simulation waveforms for data = "0"                          | 86  |

| Figure 4-23. Simulation waveforms for data = "1"                          | 86  |

| Figure 5-1. Agilent 81200 tester configuration                            | 91  |

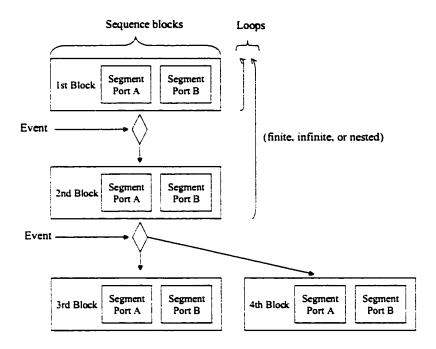

| Figure 5-2. Data segment structure                                        | 95  |

| Figure 5-3. Data sequence, blocks and segments                            | 96  |

| Figure 5-4. Basic functional test for 6-levels-per-cell operation         | 97  |

| Figure 5-5. A gray-scale bitmap for section A in chip 2                   | 98  |

| Figure 5-6. Diagram of cell leakage currents                              | 100 |

|                                                                           |     |

| 113 |

|-----|

| 113 |

| 114 |

| 114 |

| 114 |

| 115 |

| 115 |

| 115 |

| 116 |

|     |

#### **List of Abbreviations**

ASIC Application-Specific Integrated Circuit.

BL Bitline in a memory array.

C<sub>b</sub> Bitline parasitic capacitance.

C<sub>c</sub> Cell capacitance of a DRAM cell.

CMC Canadian Microelectronics Corporation.

CMOS Complementary Metal Oxide Semiconductor. Refers to a MOS process

or circuit which consists of both n-type and p-type MOS transistors.

DDR Double Data Rate, e.g. DDR DRAM.

DRAM Dynamic Random-Access Memory.

DRC Design Rules Check.

DUT Device Under Test.

EEPROM Electrically-Erasable Programmable Read-Only Memory.

EPROM Erasable-Programmable Read-Only Memory.

FeRAM Ferroelectric Random-Access Memory.

GW Generate Wordline.

HDRAM An embedded DRAM design from MOSAID Technologies Inc. that

used a pure logic process.

IC Integrated Circuit.

IP Intellectual Property.

LSB Least Significant Bit.

LVS Layout Versus Schematic.

MLDRAM MultiLevel Dynamic Random-Access Memory.

MSB Most Significant Bit.

NMOS N-type Metal Oxide Semiconductor transistor type.

PMOS P-type Metal Oxide Semiconductor transistor type.

PROM Programmable Read-Only Memory.

RAM Random-Access Memory.

ROM Read-Only Memory.

RW Reference Wordline.

SA Sense Amplifier.

SDRAM Synchronous DRAM.

SRAM Static Random-Access Memory.

SoC-RAM System-on-a-Chip Random-Access Memory, an embedded DRAM

design from ATMOS Corporation.

TSMC Taiwan Semiconductor Manufacturing Corporation.

UVEPROM Erasable-Programmable Read-Only Memory that uses Ultraviolet light

to erase the memory.

V<sub>BB</sub> Back Bias Voltage for memory array substrate.

V<sub>BLP</sub> Bitline Precharge Voltage.

V<sub>CP</sub> Ceil Plate Voltage.

V<sub>DD</sub> Power Supply Voltage.

V<sub>SS</sub> A common ground voltage, usually set to 0 V.

V<sub>signal</sub> Differential signal voltage seen by the SA during sensing operation.

V<sub>cell</sub> Initial cell storage voltage in a DRAM cell.

WL Wordline in a memory array.

### **Chapter 1** Introduction

Semiconductor memories are a vital microelectronic component in digital logic systems. From computers to microprocessor-based applications, from stand-alone memory chips to embedded intellectual property (IP) blocks in application-specific integrated circuit (ASIC) designs, memory allows data and other digital information to be stored and later retrieved. By using only one access transistor and one cell capacitor to form each storage cell, DRAM is often the most cost-effective solution for high-density semiconductor storage and is, in fact, the most widely used semiconductor memory type. DRAM revenue was \$11.2 billon in 2001. The major applications for DRAMs include main memory in computers, consumer products such as mobile systems, video and games (multimedia), communication systems and industrial applications such as medical systems and embedded controllers. Tremendous advances in DRAM process technology have reduced the minimum feature size dramatically. Indeed, the storage density of DRAM chips has been approximately quadrupling every three years for the past 30 years [1]. Currently available DRAM capacity is up to 512 Mb. 1 Gb DRAM has been introduced by some DRAM manufacturers and should be available soon.

Multilevel DRAM differs from conventional DRAM by storing more than one bit per storage cell. In this chapter, we will give a basic introduction to semiconductor memories, including both conventional DRAM and multilevel DRAM. This thesis explores the architecture and circuit design, as well as chip design, implementation and testing of an MLDRAM with adjustable cell capacity, which was intended to facilitate the characterization of a promising MLDRAM scheme that was developed as part of Gershom Birk's M.Sc. thesis research [2].

# 1.1 Semiconductor Memory

Semiconductor memory devices are generally categorized into two types: volatile memories and nonvolatile memories. Memories that retain stored data only when the power is applied are called *volatile memories* and those memories that retain data even when the power is turned off are called *nonvolatile memories* [1].

Nonvolatile memory technologies include mask-programmable read-only memories (ROM) in which the data are written permanently during manufacturing; user-programmable ROMs (PROMs) in which data can be written only once; and erasable and programmable ROMs in which stored data is erasable and reprogrammable (EPROM). UVEPROMs (or EPROMs) are erased by removing the memories from the target system and exposing the upper silicon surface to ultraviolet light. Electrically-erasable PROMs (EEPROMs) are electrically erasable to permit incircuit programming. Flash memory is another kind of electrically erasable and reprogrammable nonvolatile memory technology in which the contents of blocks of cells can be erased simultaneously through the use of an electrical erase signal. Flash memory is also two to three times denser than EEPROM. Ferroelectric memory (FeRAM) is a relatively new type of non-volatile memory to watch. It uses ferroelectric material to build cell capacitors. A ferroelectric material has the property that a remnant electric dipole polarization is imprinted in the crystal structure. The polarization can be changed by applying a sufficiently strong electric field. FeRAM potentially has many advantages such lower power consumption and higher writing speed than flash memory, but it is currently handicapped by relatively low cell density and many challenges related to processing [3].

Volatile memories are usually called random-access memories (RAMs). Data can be read from and written to any specific memory location in the same amount of time and without affecting any other stored data. Static random-access memories (SRAMs) store data into a cell by setting the state of a bi-stable flip-flop. As long as the power is applied and no write signals are received, data are retained. Dynamic randomaccess memories (DRAMs), however, store data by charging a capacitor to one of two possible voltages. The electrical charges stored on the capacitors have to be refreshed periodically to prevent loss of data due to leakage current from the storage capacitors to their surroundings. Because of the active drive capability of SRAM cells, SRAMs are inherently faster than DRAMs. SRAM is normally used to provide cache memory or embedded memory in high-performance applications. DRAMs, with only a capacitor for data storage in each cell, require roughly four to six times less silicon area per cell than SRAMs and are the cheapest and densest semiconductor memory. They have the largest sales volumes among memories and are widely used as computer system main memory as well as in graphics systems, consumer products, communication systems, and industrial applications. Historically, DRAMs have been the major technology driving force for the semiconductor industry in many aspects from process development, to production improvement, to reliability control and improvement. DRAM's role as technology pioneer is now less prominent, however, as DRAM processes have increasingly diverged from mainstream logic processes.

### 1.2 DRAM Technology

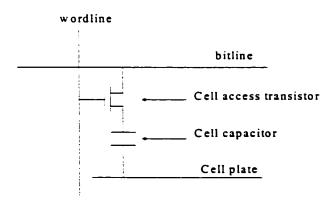

Conventional DRAM stores one bit of data, either logic 0 or logic 1, in each memory cell. The two possible values of one bit of binary data correspond to two analog voltage levels, which are usually called V<sub>SS</sub> (ground) and V<sub>DD</sub> (power supply voltage). A modern DRAM memory cell, shown in Figure 1-1, contains only one transistor and one capacitor, and is thus referred to as a 1T-1C cell. The transistor operates as a switch in between the bitline and cell capacitor, whose state is controlled by the wordline signal. This transistor is usually called the cell access transistor and it can be of either NMOS or PMOS type. When the cell access transistor turns on, charge can be transferred between the bitline and the capacitor as the voltages equalize. The side of the capacitor connected to the drain of the cell access transistor is called the storage node; the other capacitor node, which is shared by all memory cell capacitors, is called the cell plate (CP). The capacitance of the cell capacitor ranges from 20 fF to 60 fF in a typical DRAM process technology [4].

Figure 1-1. A 1T-1C DRAM cell

Digital information is encoded as analog cell voltages into two possible ways. In the positive logic encoding, logical 0s and 1s are stored as  $V_{SS}$  and  $V_{DD}$ , respectively.

In the *negative logic encoding*, logical 0s and 1s are stored as  $V_{DD}$  and  $V_{SS}$ . Depending on the analog voltage data on the bitline, the charge stored in the cell capacitor is given by either

$$Q = (V_{DD} - V_{CP}) \bullet C, \text{ or}$$

$$Q = (V_{SS} - V_{CP}) \bullet C, \qquad (1.1)$$

where C is the cell capacitance in Farads,  $V_{DD}$  and  $V_{SS}$  are the two possible driven analog voltage levels on the bitline, and  $V_{CP}$  is the cell plate voltage. After the cell capacitor has been isolated from the bitline, the charge stored in it depletes slowly due to the various leakage paths from the storage node. In order to restore the strength of the charge in the capacitor and thus maintain the stored data, sufficiently frequent refresh (i.e. re-write) operations are necessary. Because refresh operations are required, DRAM is called a dynamic memory technology, as opposed to a static one.

To write data into the memory cell, the bitline is driven to the corresponding analog voltage by a write driver buffer (not shown in Figure 1-1) and the wordline is asserted to turn on the cell access transistor. The cell storage node is therefore connected to the bitline and is rapidly driven to the bitline voltage. Then the wordline is de-asserted to turn off the cell access transistor, disconnecting the bitline and the cell storage node and trapping the desired voltage-encoded data on the cell capacitor.

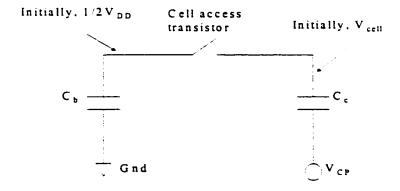

Figure 1-2. DRAM charge sharing

To read the data from the memory cell, the bitline is first precharged to a voltage midway between the two data signal voltages. The midway voltage, which is  $1/2 V_{DD}$  if  $V_{SS} = 0$ , is called the *bitline precharge voltage* ( $V_{BLP}$ ). With the bitline floating at the precharge voltage, the wordline is asserted and the cell access transistor turns on

to connect the cell capacitor to the bitline, causing charge sharing to occur between the cell capacitor and the bitline parasitic capacitance, as shown in Figure 1-2. In a DRAM cell array, one bitline is connected to a multitude of memory cells. Because of the large number (e.g. 128, 256 or 512) of cell transistors connected to the bitline, as well as its physical length and its proximity to other nearby conductors, the bitline is highly capacitive. Typically, the bitline parasitic capacitance  $C_b$  is about eight to ten times the memory cell capacitance  $C_c$  [1]. Therefore, the cell signal voltage will be greatly attenuated and thus the bitline voltage changes only slightly about  $V_{BLP}$ . Because the cell signal is lost, the read operation in a DRAM is called a destructive read. The voltage signal on the bitline (with respect to  $V_{BLP}$ ) can be calculated according to the following equation, which is implied by conservation of charge:

$$V_{signal} = (V_{cell} - \frac{V_{DD}}{2}) \bullet \frac{C_c}{C_b + C_c}$$

(1.2)

For 0.18-µm technology, the typical power supply voltage is 1.8 V [5]. Assuming the bitline parasitic capacitance to cell capacitance ratio is roughly 9, the bitline signal is only 90 mV with respect to  $V_{BLP}$ . The differential voltage between the bitline holding the attenuated cell voltage and a second bitline holding a reference voltage of  $V_{BLP}$  is amplified to the power rails by a sense amplifier and written back to the memory cell. The wordline can then be de-asserted and the destructive read and restore operation finishes.

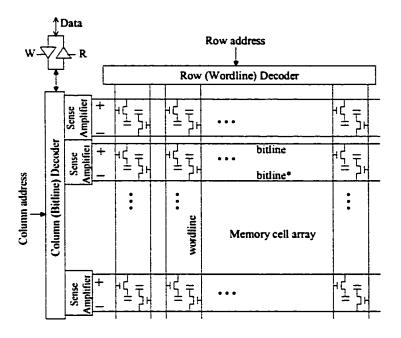

Figure 1-3 shows the high-level organization of a DRAM block. The center part is the memory array formed by a two-dimensional matrix of memory cells, as shown in Figure 1-1. Wordlines decoded from a row decoder run vertically and each wordline is connected to the gates of the access transistors in a row of memory cells. Bitlines run horizontally and each of them is connected to the sources of access transistors in a column of memory cells. True bitlines are connected to the "+" terminals of their sense-amplifiers, while complement bitlines are connected to the "-" terminals. Notice that a "folded bitline" architecture is used, as is typically the case in modern DRAM memory arrays. Thus the true bitline (bitline) and the complement bitline (bitline\*, where "\*" denotes the complement signal) are folded together at the sense amplifier to form one column (a bitline pair) that is selected by the column decoder for the same column address.

Figure 1-3. A DRAM block [6]

Sensing and restoring techniques in conventional two-level DRAM are described in [1] and [4] in considerable detail. When a wordline is asserted from  $V_{SS}$  to  $V_{DD}$ , all cell access transistors connected the wordline turn on. For sensing, the charge stored in a memory cell is shared with one bitline of a bitline pair while the other bitline continues to hold the precharge voltage to be used as a reference voltage. The sense amplifiers behave as differential amplifiers that compare the voltages on the two adjacent bitlines to determine the data from the activated memory cell. They amplify the two bitline signals to the point that they reach the array supply voltages, i.e.,  $V_{DD}$  and ground. For writing new data into a cell, the state of sense amplifier is overwritten by a low-impedance write driver (shown at the top left corner in Figure 1-3). This ensures that the new data is written back into the memory cell.

# 1.3 MLDRAM Technology

By shrinking the feature size of the transistors and adopting complex threedimensional cell capacitor structures, DRAM manufacturers have kept increasing the storage density of DRAM and lowering the per-bit cost. However, density innovations in DRAM are approaching economic limits in terms of the cost of manufacturing. It is more and more difficult to further increase the memory density cost-effectively. Multilevel DRAM, by storing more than one bit per memory cell, explores an additional dimension to further increase the storage density without requiring changes in the DRAM process.

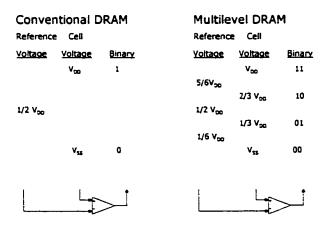

In a conventional two-level DRAM cell, the cell voltage corresponding to one bit of data can be defined as one of two possible values as follows [6]:

$$V_{cell} \in \{a_0 V_{DD}, a_1 V_{DD}\}, \text{ where } a_0 = 0 \text{ and } a_1 = 1$$

(1.3)

For a multilevel DRAM that stores N analog voltage levels per cell, the cell voltage can be one of the following voltage levels between V<sub>DD</sub> and V<sub>SS</sub>:

$$V_{cell} \in \left\{ a_0, a_1, a_2, ..., a_{N-1} \right\} V_{DD} \tag{1.4}$$

In order to maximize the noise margins between possible signals, these voltage levels are equally spaced. So equation (1.4) can be rewritten as (1.5):

$$V_{cell} \in \left\{0, 1, 2, ..., N-1\right\} \frac{V_{DD}}{N-1}$$

(1.5)

To reliably sense these N possible analog voltages, N-1 reference voltages are needed to compare with the cell voltages. These reference voltages are positioned midway between each pair of adjacent cell voltage levels to maximize the worst-case noise margin seen by the sense amplifier. The reference voltage levels are given in equation (1.6):

$$V_{REF} \in \{1, 3, 5, ..., 2N - 3\} \frac{V_{DD}}{2(N-1)}$$

(1.6)

Note that n bits can have  $2^n$  possible joint states. Therefore one cell with N possible analog signal levels can be used to encode  $[\log_2 N]$  whole bits. Fractional bits can be stored in a cell if groups of cells are considered together, with fractional bits combined into whole bits during data storage and retrieval. In the limit, when converting N analog voltage levels into binary data, n digital bits can be encoded according to equation (1.7):

$$n = \log_2 N \tag{1.7}$$

Figure 1-4 [6] illustrates how two bits of data can be encoded into one memory cell using four equally-spaced voltage levels from  $V_{SS}$  to  $V_{DD}$ .

The storage density of an N-level MLDRAM can be potentially increased over that of DRAM by a factor of n-1 without any changes in the DRAM process technology or

the optimized DRAM cell array. The most critical challenge for MLDRAM technology to overcome is probably the reduced noise margins, especially for the already more closely spaced power supply levels in today's deep sub-micron technology. The noise margins for an N-level MLDRAM cell are reduced by a factor of N-1 over those of a conventional DRAM cell in the same technology. As in the earlier example, in 0.18-µm technology, with a 1.8 V power supply voltage and a bitline-to-cell capacitance ratio of 9, the signal voltage for a conventional 2-levels-per-cell DRAM is 90 mV. However, the signal voltage is only 30 mV for a 4-level MLDRAM, and 18 mV for a 6-level MLDRAM. The reduced noise margins make the MLDRAM much more vulnerable to on-chip noise, cell leakage, sense amplifier offsets, and environmental ionizing radiation. Note also that the maximum retention time of the memory cell will decrease as the number of voltage levels increases and the inter signal level voltage decreases. Consequently, the refresh rate must be increased to maintain the data, and this would increase stand-by power consumption.

Figure 1-4. A two-bit-per-cell storage scheme [6]

The sensing and restoring operation for MLDRAM is also more complex than for DRAM. In MLDRAM, multiple analog voltage levels other than  $V_{SS}$  and  $V_{DD}$  are required. The voltages levels should be obtained on chip from the desired digital write data. For sensing, more reference voltage levels need to be created to compare with the cell voltages to allow the analog cell voltage to be converted back to digital form. A more complex control sequence will inevitably increase the access time as well as

the silicon area of an MLDRAM. Therefore, the theoretical gain in storage density is reduced by the additional area overhead.

Although multilevel floating-gate nonvolatile flash memory has already appeared in the market [7], there are still no commercial multilevel DRAM products due to all of these disadvantages. Whether or not MLDRAM can be commercially cost-effective is still unclear. Our research aims to help clarify the technical trade-offs.

A suitable circuit design for MLDRAM should minimize all of these disadvantages and also satisfy a number of other criteria. First, the feasibility of commercial production depends on the robustness of the circuits to a large degree. The correct operation of the MLDRAM circuits must be insensitive to the inevitable IC process variations that can cause the circuit parameters to differ from the nominal values. Second, the MLDRAM must be insensitive to the effects of on-chip noise. Noise insensitivity becomes more important for MLDRAM than DRAM due to the reduced noise margins. Great care must be taken when designing balanced circuits in MLDRAM to ensure that noise sources, such as gate to source/drain charge injection through the cell access transistors, will be cancelled as common mode noise by the differential sense amplifiers. Finally, the access time for MLDRAM should not be too slow compared with DRAM. Otherwise its performance will not meet the same operational requirements already met by DRAM and expected by customers. Much slower access time would restrict MLDRAM to file storage applications, where the random-access time is not as important.

#### 1.4 Thesis Outline

Several multilevel DRAM schemes have been described in previous papers and some of them have been implemented in experimental chips [8] [9] [10] [11] [12]. Recently, Birk et al. [6] [13] proposed a robust MLDRAM scheme that combines the speed advantages of [9] with the noise cancellation advantages of [10]. This thesis describes the design, implementation and testing of an MLDRAM test chip based on Birk's design, which has adjustable cell capacity and is more flexible than Chan's fixed 2-bits-per-cell implementation [14]. Regardless of the selected cell capacity, data storage and sensing follow the same mechanisms described in [6] and [13]. The test chip, which has an adjustable cell capacity of 1, 1.5, 2, 2.5 bit(s) per cell, should

be useful for characterizing the chip implementation and for experimentally determining the practical limits of one particularly promising MLDRAM technology.

The rest of this thesis is organized as follows:

The next chapter reviews basic concepts, useful circuit design techniques, chip architecture, as well as the read and write operations of conventional DRAM. Then, a detailed overview of several MLDRAM techniques is given. The previous MLDRAM projects at the University of Alberta are reviewed. Benefits, drawbacks and technology challenges for MLDRAM are summarized at the end.

Chapters 3 and 4 explore the design, simulation and implementation of the test chip. The test chip was designed in TSMC's 0.18-micron CMOS technology that is supported by the Canadian Microelectronics Corporation (CMC). Simulations for both a PMOS and an NMOS-based memory array demonstrated correct functionality for the four different cell capacities. A fully-customized memory core was combined with periphery logic, which was designed using cells from CMC's standard cell libraries.

Silicon verifications for five prototype chips are presented in Chapter 5. The test environment, some basic functional tests and test results are described.

Chapter 6 makes conclusions and proposes future related work.

### **Chapter 2 Previous Work**

MLDRAM technology borrows many ideas from conventional DRAM technology. Sections 2.1, 2.2 and 2.3 review basic concepts, circuit design techniques, chip architectures and operations for conventional DRAM. Several previous MLDRAM schemes are then reviewed and compared in Section 2.4. The major advantages, disadvantages and technology challenges of MLDRAM are summarized in Section 2.5.

#### 2.1 Basic DRAM Circuits

DRAMs evolved from the earliest 1 Kb generation to the imminent 1 Gb generation through advances in both integrated circuit manufacturing processes and circuit design techniques. A DRAM manufacturing process technology distinguishes itself from a logic process in that it places high density and low per-bit cost, rather than high performance, as its first concern. With continually shrinking transistor feature sizes and innovative cell capacitor structures, which evolved from the early planar capacitors to complex trench and stacked cell capacitors, DRAM has been the technology driver for semiconductor industry for over two decades.

Unlike most logic ICs, DRAMs have a very regular physical structure. Figure 1-3 in Chapter 1 shows a very simplified view of DRAM chip architecture. The memory arrays are composed of rows and columns of memory cells, which take up most of the memory chip area. The densely packed cell array and the immediately surrounding circuits are called the *memory core*. The core normally contains the sense amplifiers, bitline precharge devices, wordline drivers, and some address decoding logic. To achieve an efficiently packed layout, the core circuitry is constrained to be pitch matched to the bitlines and wordlines. The outermost circuitry of the DRAM chip, which contains address decoding logic, the power regulation circuits, the control logic and the interfacing circuitry, is referred to as the *periphery*.

### 2.1.1 The DRAM Cell Array

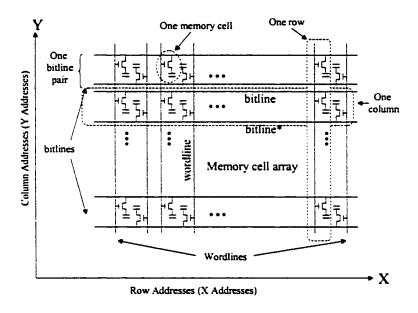

A DRAM array is a two-dimensional array of DRAM memory cells. As mentioned before, the modern 1T-1C DRAM cell includes a cell access transistor and a cell storage capacitor. Wordlines run in one direction and are connected to the gates of the cell access transistors. Bitlines run perpendicularly to the wordlines and are connected to the source/drain terminals of the cell access transistors. Figure 2-1 shows a basic DRAM cell array structure with the so-called folded bitline architecture (explained in section 2.1.1.2).

Figure 2-1. A DRAM cell array [6]

#### 2.1.1.1 Rows and Columns

As indicated in Figure 2-1, one *row* of DRAM refers to one wordline and all the memory cells connected to this wordline. One *column* of DRAM refers to one bitline and all the memory cells connected to this bitline. However, it is common practice to use the terms wordline and row, and bitline pair and column interchangeably. Given a particular wordline and bitline address, one or a few memory cell(s) can be accessed.

Note that when one wordline is addressed, the whole row of memory cells that is connected to this wordline is accessed. Standard DRAM operations, such as page mode access, take advantage of this situation by allowing fast access to cells in the currently accessed row. Depending on the memory access pattern, such a mode can improve the chip average cell access time dramatically.

#### 2.1.1.2 Folded Bitlines and Twisted Bitlines

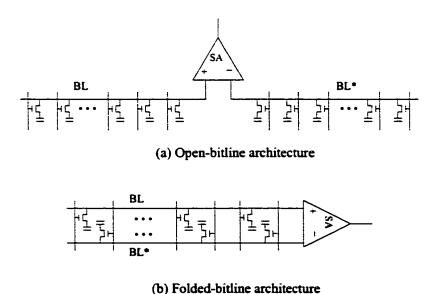

DRAM arrays prior to the 64 Kb generation (pre 1980) employed the *open bitline* array architecture as illustrated in Figure 2-2 (a). Here two bitlines are connected to the sense amplifier from two separate arrays. In this arrangement, each wordline connects to the memory cell at every bitline-wordline intersection, creating crosspoint-style arrays. Since a memory cell is present at each wordline-bitline intersection, the smallest possible area of the memory cell is between 4F<sup>2</sup> and 6F<sup>2</sup>, where the *feature size* F is the minimum realizable process dimension (that is, the half bitline pitch and the half wordline pitch). The folded bitline array architecture, shown in Figure 2-2 (b), comes from taking the complement bitline BL\* in Figure 2-2 (a) that goes into the same sense amplifier as the corresponding true bitline BL and folding it alongside BL. Since each wordline connects a crosspoint with a memory cell on only every other bitline, the minimum layout area for a memory cell in this arrangement will be 8F<sup>2</sup> [4].

Figure 2-2. Open-bitline and folded-bitline array architectures [6]

Although the open-bitline array architecture permits the greatest possible physical cell density, the folded-bitline array architecture became dominant ever since the 64 Kb generation due its greatly improved noise immunity properties. As we discussed before, bitlines are highly capacitive and normally the bitline parasitic capitance is about 8 to 10 times the memory cell capacitance. The resulting attenuated memory cell signal voltages that must be detected by the sense amplifiers are only a few hundred millivolts. Reduced power supply voltages and increasing cell capacitor leakage currents aggravate the situation by reducing the worst-case signal voltage even more. Therefore, the sensing operation is particularly vulnerable to errors caused by noise and component mismatches. In the folded bitline arrangement, by putting BL and BL\* in parallel and close to each other, electrical parameter mismatches in the bitlines due to process variations are minimized. Noise injected onto the bitlines will be tend to be common mode noise, and therefore, effectively rejected by the differential mode sense amplifier. Moreover, the folded bitline arrangement can use bitline twisting (not available in open bitlines) to further increase the noise immunity by reducing effect of the bitline-bitline capacitive coupling [4].

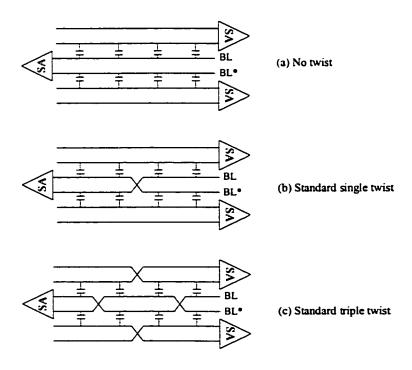

Figure 2-3. Bitline twisting schemes [4]

Bitline twisting in one or more positions of the bitline physical layout is widely used in DRAM arrays. Twisting balances the coupling capacitance to the adjacent bitline pairs so that coupling between the two columns will not be seen by the sense amplifier. Figure 2-3 (b, c) shows two standard bitline twisting schemes and illustrates how parasitic capacitive coupling will be balanced.

#### 2.1.1.3 Friendly Cells and Dummy Cells

Balanced layout is very important for small-signal analog and mixed-signal IC designs. Memory array design is actually mostly small-signal analog design despite the digital signals at the outside interfaces. The information data stored in the memory cells are held in the form of analog voltages, and the attenuated signals seen during sensing are very vulnerable to any mismatches and noises. Although process variation is inevitable in IC production, designers can still optimize their design to ensure a balanced layout and minimum variations in critical electrical parameters.

In a memory array, all memory cells are designed as much as possible to have the same size and the same physical and electrical immediate environment. So the parasitic capacitance and other electrical parameters of each memory cell should be made the same in the ideal layout design. However, for memory cells at the edges of the array, there are memory cells absent on one or two sides and this topographical discontinuity will affect the quality of the corresponding signals. A common practice to solve this problem is to add "friendly cells" all around the edge cells of the memory array [6]. Such friendly cells are usually identical to the normal ones, but they are never used for data storage. The wordline connected to the gates of their access transistors is tied permanently to the power supply voltage (V<sub>SS</sub> for NMOS and V<sub>DD</sub> for PMOS). Alternatively, the friendly cells may contain capacitors only to mimic normal cell capacitors. This approach appears to be common in embedded DRAM design.

Dummy cells, which are also called "reference cells", provide the reference voltages to be used to compare with the signal voltages from normal memory cells. Unlike friendly cells, dummy cells have wordlines that can be activated. Depending on the design, they may be identical to normal cells. It was popular to use dummy cells in early DRAMs when the bitline precharge voltage  $V_{BLP}$  was not equal to 1/2  $V_{DD}$ . This feature is no longer used for modern DRAMs, which have a 1/2  $V_{DD}$

precharge voltage that can be directly used as the reference voltage. Nevertheless, dummy cells can still be helpful for charge injection cancellation. When a wordline is activated, there will be a small amount of electrical charge injected onto the bitlines of the all accessed memory cells through the parasitic gate-to-drain capacitance of the access transistors. This small amount of charge injected onto the bitlines is very critical for the small-signal sensing, especially for multilevel DRAM designs where noise margins are even smaller. Dummy cells and dummy wordlines may be used in multilevel DRAM to store reference voltages and to cancel out charge injection.

#### 2.1.2 The DRAM Core

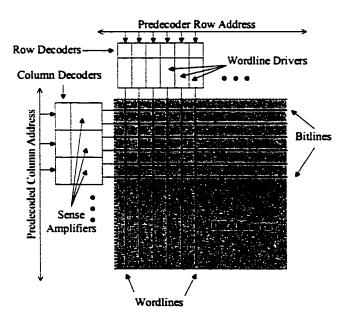

As stated earlier, the DRAM core contains the entire DRAM cell array and all the pitch-matched circuits around the array. Figure 2-4 shows a typical floorplan for the DRAM core circuitry. Row decoders and wordline drivers are laid out within wordline pitch. Column decoders and sense amplifiers are laid out within the bitline pitch. As shown in the figure, the column (but not the bitline) pitch is doubled for the folded bitline array architecture compared to that for the open bitline array architecture.

Figure 2-4. DRAM core circuitry [6]

Address decoding is normally split into hierarchical stages for layout and performance reasons. In the first stage, pre-decoders in the periphery take a group of two or three (n) address bits and produce a combination of four or eight  $(2^n)$  minterms. Those minterms are fed to the next level decoding circuits (decoders) to produce more minterms decoded from yet more address bits. Final-stage decoding circuits for the complete address of a wordline or a bitline, which logically combine minterms from the previous decoder stages, can then be more easily laid out in the very narrow pitch of a wordline or a bitline pair. Note how Figure 2-4 shows the pitch-matched final stage row and column decoders. Whatever logic style (static or dynamic) decoders or decoder trees are used, the primary objectives in decoder design are to maximize speed, minimize die area, and simplify the constraints for any pitch-matched circuits.

In commercial DRAMs, there are also redundant, fully functional columns and rows of spare memory cells at the edge of each DRAM array (not shown in Figure 2-4), which are used to improve the effective yield of sellable memories. If a defect occurs affecting a particular wordline or a bitline during manufacturing, memory cells associated with that line may not function correctly. Without the redundant rows and columns, the whole chip would have to be discarded due to less than nominal available functional capacity. With these extra rows and columns, the memory cells that do not work can be located and removed from service, and the addresses for redundant rows and/or columns can be permanently modified to replace the defective ones. The required wire reworking is usually accomplished using laser-cut fuses. Therefore many of the memory chips with physical defects and faulty cells can still be saved and sold. This technique is called *static redundancy*. Static redundancy is required to achieve economically high yields in all commercial memory chips of at least 1 Mb capacity. Extra chip area, design complexity and manufacturing time are the main additional costs of this technique.

#### 2.1.2.1 The Sense Amplifier

The term sense amplifier block refers to a collection of circuit elements (excluding memory cells) that are physically laid out within the bitline pitch. This block normally includes isolation switches, bitline precharge devices, one or more NMOS sensing transistors, one or more PMOS sensing transistors, and the input/output transistors

that connect the selected bitlines to the data buses. Figure 2-5 shows a typical DRAM sense amplifier block circuit.

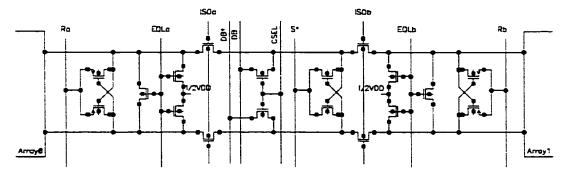

Figure 2-5. Standard sense amplifier block [4]

The precharge circuit, controlled by EQLa and EQLb in Figure 2-5, is used to precharge and equalize the bitlines to  $1/2~V_{DD}$  prior to the sensing operation. NMOS transistors with relatively large channels are used to ensure greater drivability and faster precharging. The  $1/2~V_{DD}$  precharge voltage is used in modern DRAMs because it reduces power consumption and read-write time. By applying the  $1/2~V_{DD}$  voltage to the cell plate node, rather than  $V_{DD}$  say, the electrical stress is reduced on the very thin dielectric of cell capacitors.

Isolation switches, controlled by ISOa and ISOb in Figure 2-5, allow two adjacent arrays to share the same sense amplifier block. Another benefit of isolation devices is that they provide some resistance between the low capacitance sense node of the sense amplifier and the highly capacitive bitlines. This resistance partially isolates the sensing operation from the bitlines and permits much faster sense amplifier latching.

Input/output transistors are also called column access transistors. Controlled by the decoded signals from the column decoders, which is called CSEL in Figure 2-5, they allow data to be read from and written to specific bitline pairs. These transistors must be carefully sized so that instability is not introduced in the sense amplifiers from the data bus precharge voltage or possible remnant voltages. The ratio of the size of the NMOS sense amplifier transistors over the size of the I/O transistors is referred as the beta ratio. A beta ratio of between five to eight is typical [4]. Figure 2-6 shows how two bitline pairs are selected to connect to two different data buses through four I/O transistors.

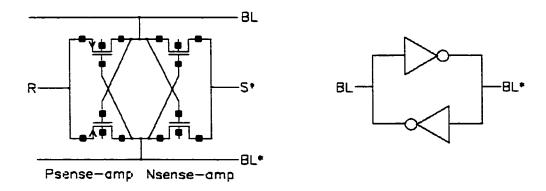

NMOS and PMOS sense amplifiers are the fundamental elements of the whole sense amplifier block. An NMOS sense amplifier consists of cross-coupled NMOS transistors which drive the lower potential bitline to ground. Conversely, a PMOS sense amplifier consists of cross-coupled PMOS transistors which drive the higher potential bitline to the positive power supply voltage.

Figure 2-6. I/O transistor connections

Figure 2-7 shows the basic *CMOS sense amplifier* where NMOS and PMOS sense amplifiers are put together. The R and S\* nodes of the sense amplifier are connected to the precharge voltage when the bitline pairs are precharged. During the sensing operation, the S and R nodes are connected to ground and VDD, respectively. When the sense amplifier is thus activated, it behaves like a feed-forward latch composed of two inverters. When powered up, it quickly drives the bitline signals to the complementary power rails in one of two possible states.

Figure 2-7. The basic sense amplifier

Because the sense amplifiers are used to detect and amplify very small differential cell signal voltages (less than 100 mV) during the sensing operation, they must be designed very carefully to ensure reliable operation. Balanced, symmetrical and duplicated circuit layout techniques are critical to a successful design [15].

Note that in the configuration of the sense amplifier block shown in Figure 2-5, the PMOS sense amplifiers are placed outside the isolation switches because the isolation switches are NMOS enhancement type and their gate control signals are not boosted. If this were not to be done, one of the bitline pairs can never be driven to a full  $V_{DD}$  because NMOS transistors can only pass an attenuated high voltage signal.

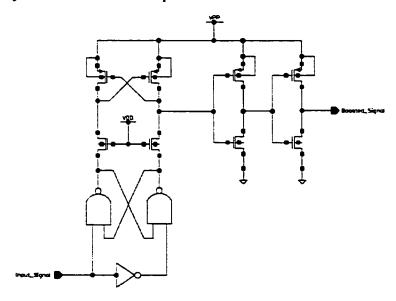

#### 2.1.2.2 Wordline Drivers

Wordlines in DRAM are highly capacitive due to the connection of a relatively large number (e.g. 128 or 256) of cell access transistors; wordlines are also highly resistive due to the relatively high resistivity of the polysilicon layer. In order to decrease the RC delay of the wordline and to improve the read-write access time, large, low-impedance wordline drivers and parallel metal straps are employed. In addition, for NMOS (PMOS) access transistors, wordline drivers are required to drive the wordline signal to at least one threshold voltage above V<sub>DD</sub> (below V<sub>SS</sub>) so that a full V<sub>DD</sub> (V<sub>SS</sub>) can be passed from the bitline to the cell storage node. This technique is called *wordline boosting*. There are many different kinds of wordline driver circuit designs. In our test chip, we used the proven wordline driver circuits from ATMOS Corporation, as shown in Figure 2-8. Wordline boosting is realized for these CMOS drivers by simply changing the power supply voltage to the boosted power supply voltage.

### 2.1.2.2 Data Buses

As illustrated in Figure 2-6, information data are read from and written to the memory core via the data buses that run over or alongside the sense amplifiers. The number of the parallel data buses determines the available data bandwidth to and from the memory core. Since data buses are long and highly capacitive, the sense amplifiers are too small to drive them to the  $V_{DD}$  and  $V_{SS}$  in a reasonable time. Therefore, just like the bitlines, data buses are precharged to 1/2  $V_{DD}$  and then left

floating at that mid voltage. For a sensing operation, when the column select signal activates the I/O transistors that connect the data buses to specific bitlines, the large data bus differential sense amplifiers will quickly detect the weak signals coming from the bitline sense amplifier and help drive the data buses to the power rails. Noise-rejection techniques, such as folded and twisted data buses, could be employed. For a write operation, the data bus voltages are driven to the intended levels by a powerful write driver and the resulting signal will overwrite the state of the comparatively small bitline sense amplifiers.

Figure 2-8. Wordline driver from ATMOS Corporation

# 2.1.3 The DRAM Periphery

The DRAM periphery contains all of the rest of the circuitry around the memory core in the memory chip. It consists of the pre-decoder logic, address buffers, data bus sense amplifiers and write drivers, circuits that control row and column redundancy, voltage regulators used to create different on-chip voltages, as well as some control logic and data output/input interface logic. For synchronous DRAM (SDRAM), the on-chip control circuitry for fast operation modes is quite complicated. Pipelining techniques and dynamic logic gates (or bipolar transistors) must typically be used in the periphery to improve speed.

## 2.1.4 DRAM Floorplanning

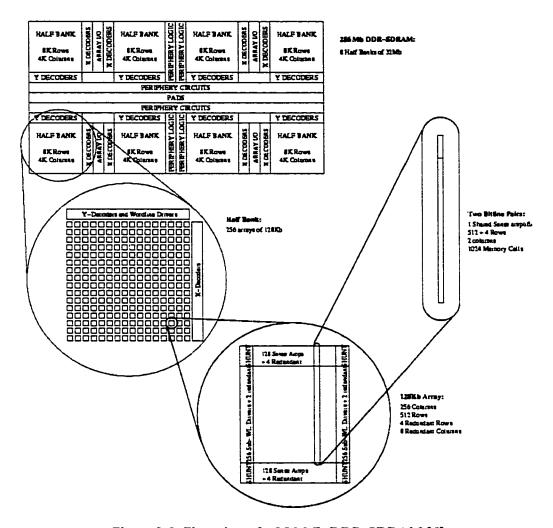

The maximum length of wordlines and bitlines is limited in practical DRAM chips. Long wordlines have large parasitic capacitance and resistance, so the RC delay of the wordlines increases and the access time becomes too long. Similarly, long bitlines have large parasitic capacitance and appreciable resistance, which means high dynamic current and power consumption, and weaker cell signals for sensing. Therefore, large capacity memory chips are always segmented into multiple smaller banks with shorter bitlines and wordlines. In each bank, there is an array of memory array blocks. For example, a 256 Mb synchronous DRAM might have 8 memory banks composed of 32 Mb memory bits each. Each bank may in turn have 8K rows and 4K columns arranged into a  $16 \times 16$  array of basic memory array blocks. Each basic memory array block may have 512 nominal rows plus 4 redundant rows and 256 nominal columns plus 8 redundant columns (512 + 16 bitlines), for a total of 128 Kb. The bank as a whole has one row decoder, major wordline drivers along the edges of the bank, and one column decoder. The major wordline drivers drive sub-wordline drivers in each basic array to activate a specific wordline. Figure 2-9 shows the floorplan of such a 256 Mb DDR-SDRAM.

Cell efficiency and die efficiency are two commonly used parameters to judge the design of a memory chip. Cell efficiency is the percentage of the die area occupied by memory cells (not including the redundant cells) over the memory core. Normally it equals the cell area divided by the core area. This parameter highly depends on the process technology and the cell layout design. The die efficiency is defined as the die area required by all of the memory cells on average of the whole chip, which can be calculated by dividing the total die area by the total silicon area occupied by the useful memory cells.

Figure 2-9. Floorplan of a 256-Mb DDR-SDRAM [6]

# 2.2 DRAM Operations

The operation modes of conventional DRAM have been continually evolved to improve chip performance. In this section, first we will discuss the basic operation of the DRAM core as background knowledge for understanding multilevel DRAM operation. Then different speed improvement operation modes will be introduced.

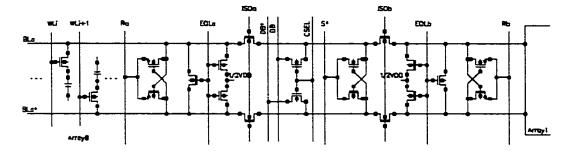

If we consider the bitline pair of the standard sense amplifier block and its associated arrays in Figure 2-5 and assume that wordline WLi in array0 is addressed, we will now obtain the column schematic shown in Figure 2-10:

Figure 2-10. Schematic of a DRAM bitline pair

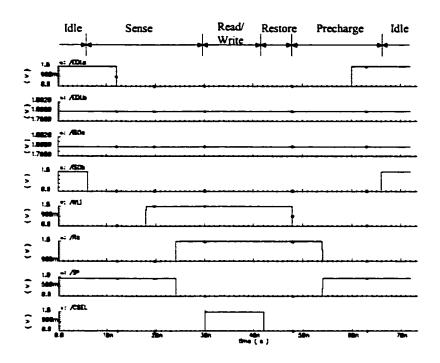

As shown in Figure 2-11, a basic read/write operation cycle starts with the idle state, where all bitlines and sense amplifier nodes are precharged to 1/2 V<sub>DD</sub>, the isolation switch signals ISOa and ISOb are switched on, and no wordlines in array0 and arrayl are activated. When a wordline in array0 is to be accessed, the isolation switch controlled by signal ISOb will disconnect arrayl from the shared sense amplifier block and leave only array0 with the complete sense amplifier block. Then the EQLa signal stops precharging the bitline pair BLa and BLa\*, leaving this bitline pair floating at the bitline precharge voltage V<sub>BLP</sub>. One specific wordline in array0, WLi, is activated by the wordline decoder and wordline driver for the given row address. All the memory cells connected to WLi are now accessed. The charge stored in each memory cell will be distributed along one bitline of the bitline pair. In our example, the voltage of the true bitline BLa will be slightly shifted by about a few hundred millivolts or less. Next, asserting signal R and S\* to the power supplies activates the PMOS and NMOS sense amplifiers. The weak differential signals on BLa and BLa\* are then amplified and driven to the power rails. The data stored in the memory cell is thus amplified and ready to be driven out over the data bus. A column select signal CSEL, decoded from the given column address, will be pulsed to connect the sense amplifier with the data bus. Depending on the operation type, the data is either read out to an external data pin or overwritten by the write driver. Then either the original data (for a read operation) or the newly written data (for a write operation) will be restored by de-asserting WLi. Finally, the sense amplifiers and bitlines are precharged back to 1/2 V<sub>DD</sub> and array1 is connected to the sense amplifier block once again by asserting the ISOb signal. The circuits are now idle again and ready for the next read/write operation.

Figure 2-11. Basic read/write timing diagram for the DRAM core

The performance of a DRAM chip can be improved by speeding up the absolute access time and/or delivering data at a faster average rate. Recall that during the normal read operation, after a specific wordline is addressed in a memory bank, a large number of data bits from all of the memory cells connected to this same wordline (collectively called a page of bits) are held on the sense amplifiers. The sense amplifiers behave like latches waiting to be selected by the column selecting signals. Many of the fast access DRAM modes that have been developed rely on the ability to rapidly access the data stored in a page without having to initiate a completely new memory cycle. Nibble mode, in which four sequential bits of data can be accessed quickly, was used in early DRAMs. Static mode, page mode, fast page mode are used to get faster access to random data in one page by eliminating the row address setup and hold time. Fast Page with Extended data out (EDO) mode (also called Hyperpage mode) and Burst Mode with EDO are operation modes that are widely available in recent DRAMs. Meanwhile, multiple parallel I/O buses and more data I/O pins are used to increase the available data bandwidth and therefore to directly increase the data transfer rate [16].

## 2.3 Embedded DRAMs

Embedded memory refers to a memory block that is integrated with other logic circuits in one chip. Embedded SRAMs have been widely used to implement cache memory in microprocessor-based system designs (SoC, system-on-a-chip) due to its fast access time and its compatibility with digital logic processes. Embedded DRAMs are also becoming more and more common in all kinds of applications. Elimination of I/O pins, lower power consumption, higher speed, wider internal data bandwidth, and more flexible data granularity make embedded DRAMs suitable for high density on chip memory in high performance systems such as graphics chips and hard disc controllers. Design and cost trade offs have to be made carefully between the DRAM process and the logic process because they have different priorities [17], [18], [19].

ATMOS' SoC-RAM<sup>TM</sup> is an embedded memory architecture developed by ATMOS Corporation for system-on-a-chip (SoC) applications [19]. SoC-RAM is delivered in the form of silicon-proven hard memory cores. It is intended to be used in the wireless, graphics, imaging and networking industries that require very large on-chip memory. It is available in both a merged DRAM-logic process and a pure logic process. The layout design of the multilevel DRAM test chip used elements of the planar logic (PL) SoC-RAM core. A brief overview of ATMOS' SoC-RAM is presented below and a detailed discussion about the MLDRAM test chip layout design will be given in Chapter 3.

The structure of ATMOS' 0.18-μm embedded SoC-RAM can be determined using their memory layout compiler. For example, the 0.18-μm, 8-Mb embedded synchronous DRAM microcell has an area of 27.3 mm<sup>2</sup> (with a height of 6000 μm and a width of 4545 μm) and a cell efficiency of 63.4%. It has 16 memory banks. Each bank has 128 pages. There are 16 words with a word width of 256 bits per page. The basic component in the memory bank is a memory block. There are 2 blocks in each bank. Each memory block has 64 rows and 4096 columns [19].

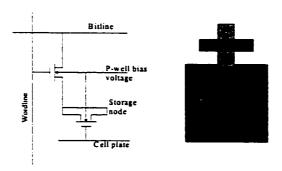

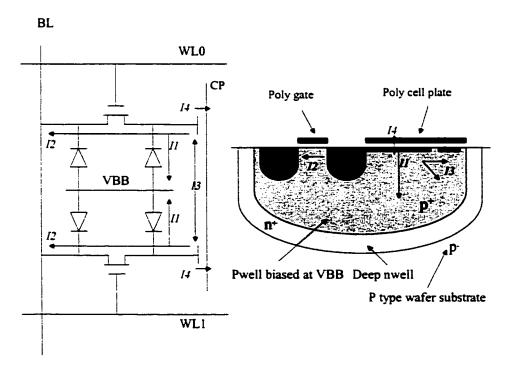

The memory cells of the SoC-RAM are NMOS-based. The cell capacitor is implemented using the parasitic channel capacitance of an NMOS transistor. The schematic and layout of a memory cell are shown in Figure 2-12. The common cell plate for the memory cells is implemented in the polyl layer. Deep n-well (from which a p-well is formed) is used to isolate the memory array from the rest of the chip.

The cell plate is biased at more than one NMOS threshold voltage  $(V_m)$  above  $V_{DD}$  in order to get linear and maximal cell capacitance. A detailed discussion about the memory cell capacitance will be given in Chapter 4.

Figure 2-12. The schematic and layout of ATMOS' SoC-RAM cell

## 2.4 MLDRAM Circuits and Techniques

Storing more than one bit per memory location to achieve higher memory density is not a new concept. D.A. Rich authored a survey of several multi-valued ROMs and RAMs that were known in 1986 [12]. Multiple states can be encoded into a ROM memory cell by varying the threshold voltage of the memory transistor or by varying the transistor's width-to-length ratio in order to change the gain current. M. Aoki et al. proposed the first 4-bit, 16-levels-per-cell DRAM in 1985 [8]. The proposed MLDRAM read and wrote the 16 states from and into the memory cell by applying a staircase waveform voltage to the addressed wordline. Since the sequential access for this scheme is too slow, it has not been pursued further although it is scalable in theory to any number of voltage levels. In 1989, T. Furuyama et al. from Toshiba Corporation designed and fabricated an experimental 1-Mb 2-bits-per-cell DRAM chip using a new technique with global reference voltages and fast parallel access [9]. In 1996, P. Gillingham from MOSAID Technologies proposed another 2-bits-per-cell multilevel DRAM sensing and restoring scheme that is robust to small parameter variations and that uses locally-generated reference voltages [10]. In 1997, Okuda et al. from NEC developed a 4-Gb 2-bits-per-cell DRAM that used a ratioed coupling capacitor to generate the reference voltages [11]. G. Birk et al. from the University of Alberta did a comparative simulation study of the three later MLDRAM techniques and proposed in [6] [13] a new scheme that combines the speed advantages of [9] and the noise cancellation advantages of [10]. A. Chan designed and implemented a test chip (ML3) based on the 2-bits-per-cell mode of Birk's new scheme in [14]. The test chip in this thesis project is also based on Birk's MLDRAM scheme, with more flexible operating modes to facilitate characterization experiments.

Although Intel has announced plans to introduce a 4-bit/cell flash device by 2003 or 2004 [7], there is still no multilevel DRAM product that has been considered promising enough to enter production.

In the following sections, we will review Furuyama's and Gillingham's MLDRAM schemes that preceded to Birk's work. Then, Birk's MLDRAM scheme will be reviewed in a full detail.

## 2.4.1 Furuyama's MLDRAM

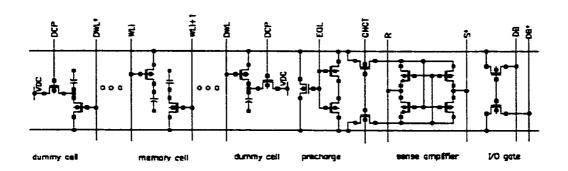

Figure 2-13 shows the basic block of Furuyama's MLDRAM scheme [9]. It consists of a pair of sub-bitlines, normal and dummy memory cells, a bitline precharge circuit, sense amplifier, and the I/O devices. Each sub-bitline has one dummy memory cell, which is used to hold the reference voltage. The reference voltage, V<sub>DC</sub>, is from a global voltage source created on chip. It is connected to the dummy cells by activating the control signal DCP. Like normal memory cells, dummy cells are connected or disconnected to the sub-bitlines by controlling the dummy wordline signals DWL and DWL\*. The sense amplifer is connected to the sub-bitline pair through two pass transistor switches controlled by signal CNCT.

Figure 2-13. Furuyama's basic sub-bitline block design

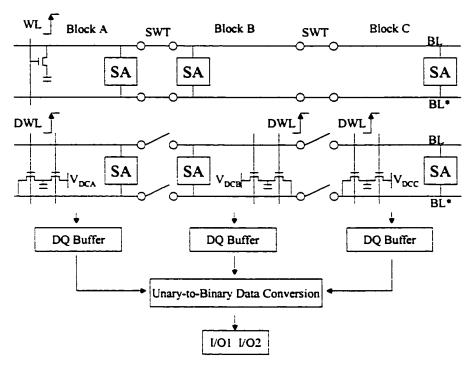

Recall from Section 1.3 that for a 2-bits-per-cell MLDRAM, one of four analog voltages stored in a memory cell must be compared with three reference voltages

during a sensing operation. In Furuyama's scheme, there are three identical basic subbitline blocks for each column, which can be connected by horizontal switches, as illustrated in the simplified block diagram in Figure 2-14. The dummy cells in each block hold one of the three reference voltages, which are V<sub>DCA</sub> for block A, V<sub>DCB</sub> for block B, and V<sub>DCC</sub> for block C.

Figure 2-14. The sensing operation in Furuyama's scheme

Figure 2-14 also illustrates the sensing operation. The timing diagram for the control signals in a sense/restore cycle is shown in Figure 2-15. When the circuits are idle, all three sections of the sub-bitlines are connected together via SWT to form one bitline and are precharged to V<sub>BLP</sub>; at the same time, the dummy cells are connected to the reference voltages via DCP (shown in Figure 2-13). A sensing operation starts with the deactivation of EQL and DCP. Following the timing diagram, a specific wordline is addressed and the charge stored in the memory cell is distributed along one full bitline, as shown in the first row of Figure 2-14. The SWT signal is then deactivated, leaving each sub-bitline in three blocks holding a copy of the attenuated signal voltage. The dummy cells on the opposite sub-bitlines are now activated and the reference voltages stored in them are redistributed along the opposite sub-bitlines. With two sub-bitlines holding the signal and reference voltages, respectively, a sense amplifier in each section is activated and the resulting digital data are latched into the

DQ buffer. Through the data conversion circuits, the 3-bit unary (also called thermometer) codeword is converted into the normal 2-bit digital data according to Table 2-1.

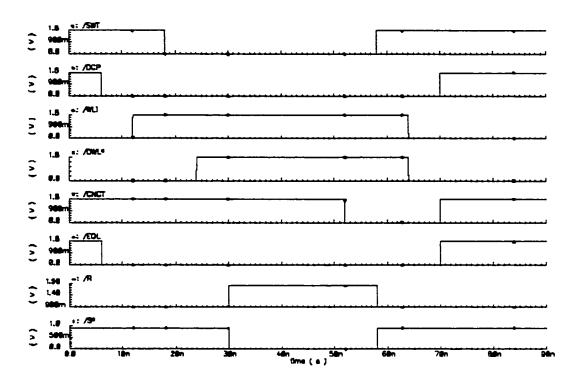

Figure 2-15. Timing diagram for Furuyama's MLDRAM scheme

Table 2-1. Data conversion table

| Cell voltage level  | Thermometer data from SAs | Two-bit binary<br>data |  |

|---------------------|---------------------------|------------------------|--|

| V <sub>DD</sub>     | 111                       | 11                     |  |

| 2/3 V <sub>DD</sub> | 110                       | 10                     |  |

| 1/3 V <sub>DD</sub> | 100                       | 01                     |  |

| V <sub>SS</sub>     | 000                       | 00                     |  |

Multilevel voltage restoration is completed by charge sharing the sub-bitlines in all three sections. First, the sense amplifiers are disconnected from the sub-bitlines. Then the floating sub-bitlines in the three blocks are connected together by activating SWT. After redistribution of charge along the full sub-bitline, the restored analog voltage is trapped back in the memory cell by deactivating the wordline. Although the three

sections are identical, there is still a minor offset error due to the bitline parasitic capacitance during the restore operation. The sub-bitline with the asserted wordline has one memory cell connected to it while the other two do not, which causes the parasitic bitline capacitance of this sub-bitline to be slightly bigger than the others.

One should note that the three global references,  $V_{DCA}$ ,  $V_{DCB}$  and  $V_{DCC}$ , are not exactly equal to the reference voltages  $V_{REF}$  because the charge in the memory cell is dumped onto three sub-bitlines while the charge in the dummy cell is only dumped onto one sub-bitline. In order to make the voltage changes caused by  $V_{DC}$  over one sub-bitline equivalent to those caused by the  $V_{REF}$  over three sub-bitlines,  $V_{DC}$  should be generated according to the following equation:

$$(V_{DC} - \frac{1}{2}V_{DD}) \bullet \frac{C_c}{C_b + C_c} = (V_{REF} - \frac{1}{2}V_{DD}) \bullet \frac{C_c}{3C_b + C_c}$$

(2.1)

$$V_{DC} = \frac{V_{REF} \bullet (C_b + C_c) + V_{DD} \bullet C_b}{3C_b + C_c}$$

(2.2)

where,

$V_{DC}$  = global reference stored in the dummy cells,  $V_{DCA}$ ,  $V_{DCB}$ , or  $V_{DCC}$

$C_c$  = cell capacitance

$C_b$  = parasitic capacitance of one sub-bitline

$V_{REF}$  = ideal reference voltages, which are 1/6  $V_{DD}$ , 1/2  $V_{DD}$  and 5/6  $V_{DD}$

The main advantages of Furuyama's MLDRAM scheme are the fast, parallel sensing and relatively simple operation. However, requiring sense amplifiers in all three sections results in greater area overhead, which reduces the potential density gain offered by the multilevel DRAM technology. The biggest disadvantage of this MLDRAM scheme is probably the use of global reference voltages, which are created on-chip, and have to be distributed across the memory array. Any slight inaccuracy in the reference voltages will cause incorrect sensing. Thus this method is vulnerable to process variations, voltage drops and offsets, and induced noise.

## 2.4.2 Gillingham's MLDRAM

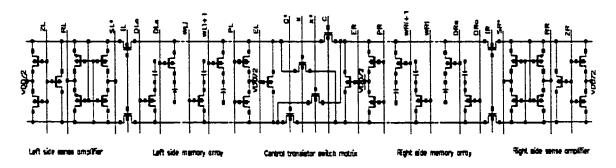

The multilevel DRAM scheme proposed by Gillingham [10] employs similar charge-sharing restore techniques as [9] and a different sequential access sensing method. The circuit schematic of a single column of Gillingham's MLDRAM is

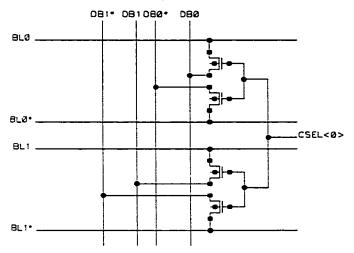

shown in Figure 2-16. Bitlines are divided into two equal sub-bitline pairs, left and right, which can be connected in six different ways by the central transistor switch matrix controlled by signals C, C\*, X, X\*, EL and ER. Each sub-bitline pair has a sense amplifier at one end, which can also be connected or disconnected by the isolation transistors. Note that there is precharge circuitry for both the sub-bitline memory array and the sense amplifiers, which means that these two sections can be precharged independently. Unlike Furuyama's scheme, the dummy cells in this scheme are not used to store the reference voltages but are used instead to cancel out the charge injection caused by the transition of the addressed wordline.

Figure 2-16. Schematic of Gillingham's MLDRAM

The associated control signal timing is illustrated in Figure 2-17. All signals ending with the letter "L" denote signals in the left side and all signals ending with the letter "R" denote signals in the right side.