#### Efficient Memory Hierarchy Utilization for Matrix Multiplication and Convolution on CPUs

| 1 |   |   |    |

|---|---|---|----|

| ľ | ٦ | ٦ | 7  |

| ĸ | , |   | γ. |

Ivan Korostelev

A thesis submitted in partial fulfillment of the requirements for the degree of

Master of Science

Department of Computing Science

University of Alberta

© Ivan Korostelev, 2022

## Abstract

Matrix multiplication is a key operation both in high-performance computing and in deep-learning applications. Generic building blocks have been introduced to abstract a matrix-multiplication operation and to enable the generation of efficient code for multiple architectures. This thesis presents three solutions to create software stacks that connect user-level code with the use of these building blocks. The first one uses pattern recognition at the intermediate representation level to discover matrix routines and replace them with efficient hand-crafted implementations that exist in numerical libraries. The second solution is a compiler-only code-generation path for matrix multiplication that targets multiple platforms. The third one is a novel convolution algorithm that replaces the traditional image-to-column data transformation with a custom cache-utilization strategy. Common to all three solutions are the use of generic building blocks that are target agnostic and the focus on making efficient use of the memory hierarchy of each machine.

The first solution, Kernelfarer, is a compiler optimization pass that searches the source code for linear algebra routines, such as matrix multiplication and rank-2 matrix update, and replaces these occurrences with efficient library implementations. Kernelfarer operates on the LLVM's intermediate representation language which makes the tool source-language agnostic and granular enough to recognize complex data dependency patterns. In comparison with other pattern matching approaches, Kernelfarer is more robust and carries less compilation time overhead.

The second solution brings the ideas for efficient matrix multiplication from high-performance libraries into a production LLVM compiler. The evaluation study shows that this approach delivers performance matching that of the high-performance libraries. This approach allows efficient linear algebra algorithms before high-performance libraries officially release them, as was the case for the IBM POWER10 $^{\text{TM}}$  architecture.

The third solution, YaConv, is a novel convolution algorithm that repurposes the building blocks for matrix multiplication from a popular high-performance library. The custom cache utilization strategy reduces the number of cache accesses by 5× and achieves mean speedup of 15% over the standard IM2CoL-based convolution. Moreover, by integrating placement of elements into cache with their use by vector instructions, the new algorithm requires only a constant buffer of the size of cache, as compared to huge memory consumption of the traditional convolution algorithms.

## **Preface**

Chapter 3 of this thesis was published as J. P. L. De Carvalho, B. Kuzma, I. Korostelev, J. N. Amaral, C. Barton, J. Moreira, and G. Araujo, "KernelFaRer: Replacing Native-Code Idioms with High-Performance Library Calls", ACM Transactions on Architecture and Code Optimization, Volume 18, Issue 3, September 2021. My role on the project was to reduce false negatives of the pattern matching tool for GEMM, extend it to SYR2K and find the cause for false negatives in matcher results from LLVM Polly. The core of the matcher design was developed by J. P. L. De Carvalho and B. Kuzma. J. N. Amaral and G.Araujo were the supervisory authors and contributed to guiding the experimental evaluation and editing the resulting manuscript. C. Barton and J. Moreira were the IBM collaborators and participated in technical discussions.

Chapter 4 of this thesis has been submitted for publication as B. Kuzma, I. Korostelev, J. P. L. De Carvalho, J. Moreira, C. Barton, G. Araujo, J. N. Amaral, "Fast Matrix Multiplication via Compiler-only Layered Data Reorganization and Intrinsic Lowering". I was responsible for developing the matrix multiplication algorithm, together with B. Kuzma, who developed the target-specific part of the code. I was also responsible for literature review and helped J. P. L. De Carvalho perform the experimental evaluation and report the results. C. Barton and J. Moreira were the IBM collaborators and participated in technical discussions. G.Araujo and J.N. Amaral were the supervisory authors and contributed to guiding the experimental evaluation and editing the resulting manuscript.

Chapter 5 of this thesis has been submitted for publication as I. Korostelev, J. P. L. De Carvalho, J. Moreira, J. N. Amaral, "YaConv: Convolution with Low Cache Footprint". I was responsible for designing and developing the algorithm,

performing the experimental evaluation, literature review and drafting the manuscript. J. P. L. De Carvalho contributed to algorithm design and the resulting manuscript. J. Moreira provided knowledge on the architectural design of IBM machines and helped with running the experiments. J.N. Amaral was the supervisory author and contributed to guiding the experimental evaluation and editing the resulting manuscript.

To my dad, for the discipline.

To my mom, for the unconditional love.

The only way to do great work is to love what you do.

– Steve Jobs

# Acknowledgements

I thank my supervisor, Dr. J Nelson Amaral, for teaching me how to speak. I appreciate the many times he has pushed me to do things the right way and not cut the corners.

I thank my friend João for the insightful conversations on computers, a gentle introduction to LLVM and many cool tips and tricks.

I thank Karolína for the support she offered during the slow-progressing periods of my thesis.

I thank my friends Cody, Batyr, Logan, Wilson, Tomas and João who have always offered a great company to relax from work.

I thank Ford Motor Company for making a great Lincoln Town Car which let me explore the Canadian Rockies and reset my mind so many times.

Thanks to everyone who joined me outdoors!

I thank my colleague Braedy Kuzma for his help with algorithm development.

I thank the IBM collaborators, José Moreira and Kit Barton, for providing their knowledge of the IBM hardware and infrastructure.

I thank Dr. Guido Araujo and Victor Ferrari for the conversations that shaped my work on convolution.

This research has been funded in part by the IBM Center for Advanced Studies (CAS) Canada and Graduate Research Assistantship Fellowship (GRAF).

# Contents

| 1 | Intr            | roduction                                                | 1                     |

|---|-----------------|----------------------------------------------------------|-----------------------|

| 2 | Bac 2.1 2.2 2.3 | Outer Product                                            | 3<br>5<br>5<br>7<br>8 |

| 3 |                 | nelFaRer: Replacing Native-Code Idioms with              | _                     |

|   |                 | h-Performance Library Calls                              | 9                     |

|   | 3.1             |                                                          | 1                     |

|   |                 |                                                          | 1                     |

|   |                 | 3.1.2 Pattern Matching in LLVM IR                        | 2                     |

|   | 2.0             |                                                          | 3                     |

|   | 3.2             |                                                          | 5                     |

|   |                 |                                                          | 6                     |

|   |                 |                                                          | 23                    |

|   | 3.3             |                                                          | 26<br>27              |

|   | ა.ა             |                                                          | 27                    |

|   |                 |                                                          | 31                    |

|   |                 | 3.3.3 Robustness of Pattern Matching                     | 32                    |

|   |                 |                                                          | 35                    |

|   |                 |                                                          | 6                     |

|   | 3.4             |                                                          | 37                    |

|   |                 |                                                          |                       |

| 4 |                 | Matrix Multiplication via Compiler-only Layered Data     |                       |

|   |                 | rganization and Intrinsic Lowering 3                     | 8                     |

|   | 4.1             |                                                          | 1                     |

|   |                 |                                                          | 13                    |

|   |                 |                                                          | 17                    |

|   |                 |                                                          | 1                     |

|   | 4.2             | 4.1.4 Arbitrary Values for nr, mr, kr and Access Order 5 | 52<br>53              |

|   | 4.2             | Experimental Evaluation                                  | Ю                     |

|   |                 | Approaches 5                                             | 6                     |

|   |                 | Approaches                                               | U                     |

|   |                 |                                                          | 69                    |

|   |                 |                                                          | 52                    |

|   | 4.3             | Additional Opportunities                                 | 34                    |

|   | 1.0             |                                                          | 54                    |

|   |                 | 4.3.2 Targetting other matrix engines                    | 55                    |

|   |                 |                                                          | _                     |

|                           | 4.4   | Concluding Remarks                                | 66 |

|---------------------------|-------|---------------------------------------------------|----|

| 5                         | YaC   | Conv: Convolution with Low Cache Footprint        | 68 |

|                           | 5.1   | Cache Inefficiencies of Previous Algorithms       | 70 |

|                           |       | 5.1.1 Convolution With im2col Transformation      | 70 |

|                           | 5.2   | YaConv                                            | 72 |

|                           |       | 5.2.1 Extra Memory Usage                          | 74 |

|                           |       | 5.2.2 Tiling and Block Sizes                      | 75 |

|                           | 5.3   |                                                   | 76 |

|                           |       | 5.3.1 Experimental Methodology                    | 77 |

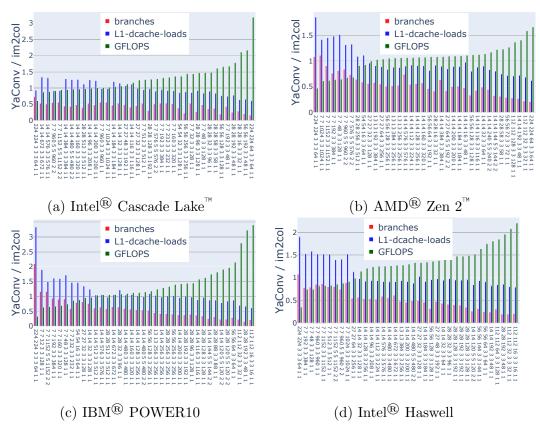

|                           |       | 5.3.2 Performance on PyTorch Layers               | 78 |

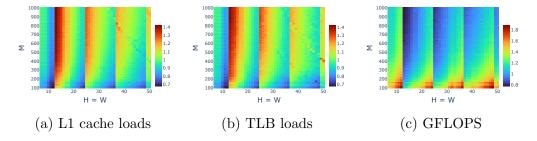

|                           |       | 5.3.3 YaConv Performance Varies with Image Sizes  | 80 |

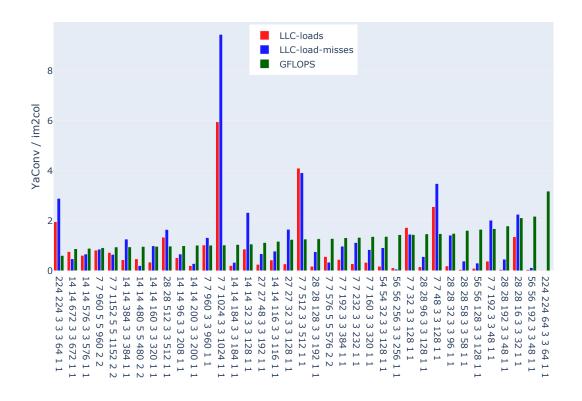

|                           |       | 5.3.4 YaConv Improves L3 Cache Performance        | 82 |

|                           | 5.4   | Concluding Remarks                                | 84 |

| 6                         | Rel   | ated Work                                         | 86 |

| _                         | 6.1   | A T                                               | 86 |

|                           | 6.2   | Compiler Approaches to Memory Access Optimization | 89 |

| _                         |       | 1 .                                               | 00 |

| 7                         | Cor   | nclusion                                          | 92 |

| $\mathbf{R}_{\mathbf{c}}$ | efere | nces                                              | 94 |

# List of Tables

| 2.1               | Matrix Math Assist (MMA) instruction summary                                                                                                                                                                                                        | 6        |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.1               | Access offset expressions for all combinations of column-major (CM) and row-major (RM) order                                                                                                                                                        | 21       |

| 3.2               | Conditions to determine the access orientation                                                                                                                                                                                                      | 22       |

| 3.3               | Machine configuration used in the evaluation.                                                                                                                                                                                                       | 27       |

| 3.4               | Comparison of pattern matching tool robustness to different patterns. Kernelfare is the presented method. Cells marked "X" indicate that the tool recognized and replaced the kernel idiom. "M" indicates instances where the tool only matched the |          |

|                   | kernel but was not able to replace it                                                                                                                                                                                                               | 33       |

| 3.5               | Comparison of time spent in LLVM passes implementing a GEMM & SYR2K detection method. Times are in milliseconds.                                                                                                                                    | 34       |

| $\frac{4.1}{4.2}$ | Machine configuration used in the evaluation                                                                                                                                                                                                        | 54<br>66 |

| 5.1               | Clockrate, cache sizes and output tile dimensions of the GEMM microkernel of the machines used for the experiments. L1 and L2 cache sizes are per core. L3 size is followed by the number of                                                        |          |

|                   | cores sharing L3 cache                                                                                                                                                                                                                              | 76       |

| 5.2               | Values for selected convolution parameters from 218 layers in                                                                                                                                                                                       |          |

|                   | PyTorch, from most to least common                                                                                                                                                                                                                  | 77       |

# List of Figures

| 2.1<br>2.2                                                          | GEMM as outer product                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4<br>8                                             |

|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 3.1                                                                 | (a) Idiom of finding the length of a string and (b) returning the minimum of 2 numbers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12                                                 |

| 3.2                                                                 | (a) Double negation example; (b) Tree representation of (a); (c) Matcher and replacement code; and (d) Pattern matched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13                                                 |

| 3.3<br>3.4                                                          | CBLAS interface for double-precision GEMM (a) Memory access of GEMM in source code; (b) colum-major access order; (c) row-major access order; (d) Simplified LLVM IR code of the innermost loop in (a) (Code in (b) and (c) is in                                                                                                                                                                                                                                                                                                                                                                                                           | 14<br>17                                           |

| 3.5                                                                 | C/C++)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 18                                                 |

| 3.6                                                                 | (a) Naïve GEMM; (b) symmetric rank-2k operations (syr2k); and (c) Multiresolution analysis kernel (doitgen)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25                                                 |

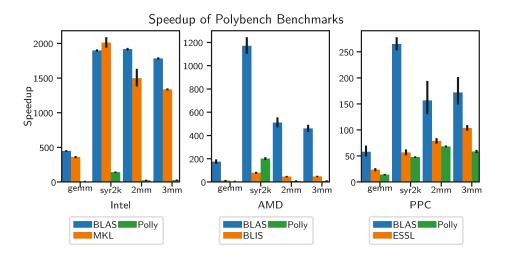

| 3.7                                                                 | The speedup of benchmarks when compared to the same benchmark run at -03 on the respective platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 30                                                 |

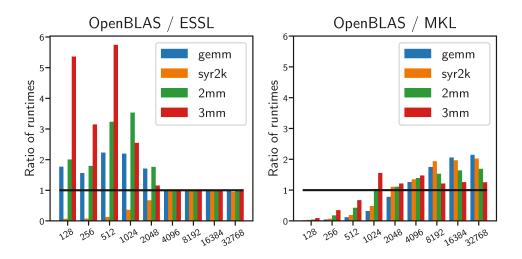

| 3.8<br>3.9                                                          | The ratio of runtimes of OpenBLAS and vendor libraries The speedup relative to each hand optimization by replacing GEMM in each platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 32<br>34                                           |

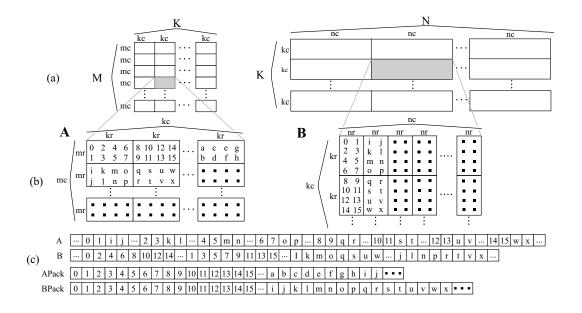

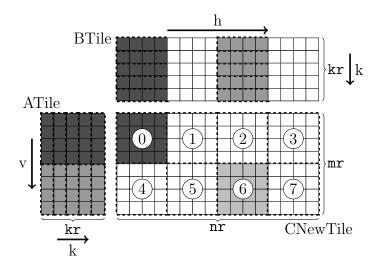

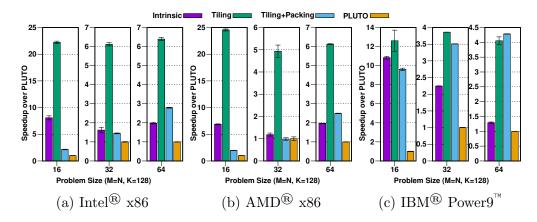

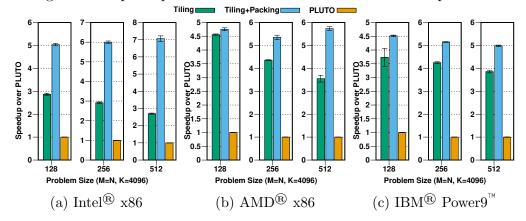

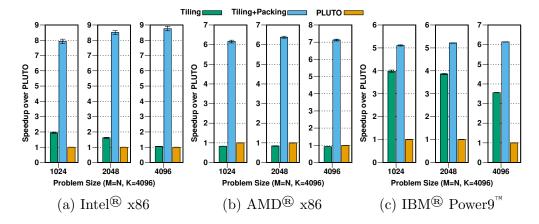

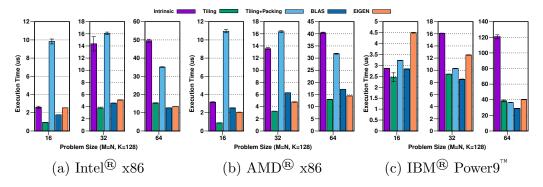

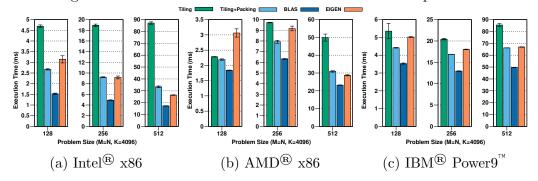

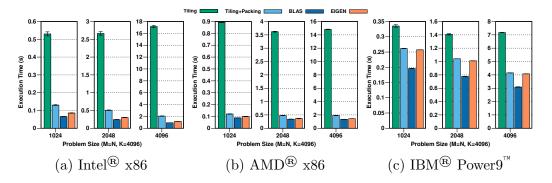

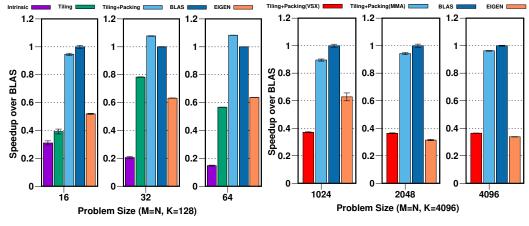

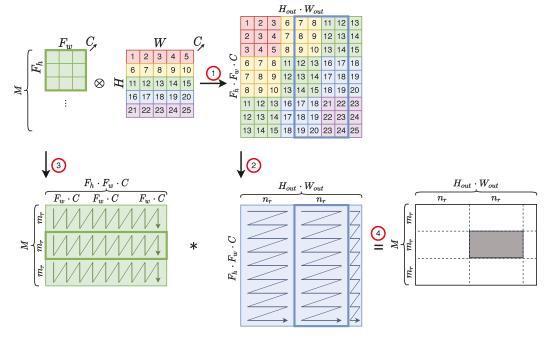

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10 | Outer-product (rank-1 update) operation.  Tiling and packing for llvm.matrix.multiply.  Division of CNewTile into MMA accumulators.  Speedup over PLuTo for small SGEMM in each platform.  Speedup over PLuTo for medium SGEMM in each platform.  Speedup over PLuTo for large SGEMM in each platform.  Execution time of small SGEMM in each platform.  Execution time of medium SGEMM in each platform.  Execution time of medium SGEMM in each platform.  Execution time of large SGEMM in each platform.  (a) Speedup over BLAS of small SGEMM on POWER10 with MMA; (b) Contrasting VSX and MMA performance of SGEMM kernel on POWER10. | 41<br>44<br>49<br>57<br>57<br>58<br>60<br>61<br>64 |

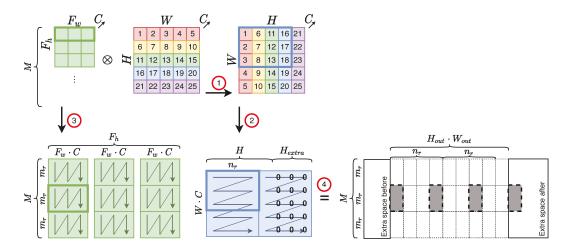

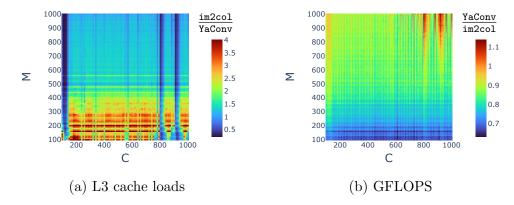

| 5.1<br>5.2<br>5.3                                                   | im2col convolution The novel YaConv algorithm Ratios for L1 cache, branches and GFLOPS between YaConv and im2col on layers from PyTorch across four machines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 71<br>73<br>79                                     |

| 5.4                                                                 | Varying image size $H = W$ and number of input channels with fixed $M = 200, F_h = F_w = 3, P_h = P_w = 1$ on Intel <sup>®</sup> Cascade Lake <sup>™</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 81                                                 |

| 5.5 | L3 cache usage and GFLOPS on PyTorch layers on Intel®                                         |    |

|-----|-----------------------------------------------------------------------------------------------|----|

|     | Cascade Lake $^{\tilde{\mathbb{M}}}$                                                          | 83 |

| 5.6 | Varying the number of input and output channels with fixed                                    |    |

|     | image and filter size on Intel <sup>®</sup> Cascade Lake <sup><math>^{\text{TM}}</math></sup> | 84 |

# List of Acronyms

AI Artificial Intelligence

**AMX** Advanced Matrix Extensions

**BLAS** Basic Linear Algebra Subprograms

CNN Convoutional Neural Network

**CPU** Central Processing Unit

**GEMM** General Matrix Multiplication

**HPC** High-Performance Computing

IR Intermediate Representation

**LLVM** Low-Level Virtual Machine

MLIR Multi-Level Intermediate Representation

MMA Matrix Math Assist

SIMD Single Instruction, Multiple Data

TLB Translation Lookaside Buffer

VSX Vector-Scalar Extension

## Chapter 1

## Introduction

The Artificial Intelligence (AI) resurgence of the last decade has increased demand for both server-grade and mobile computing power. Convoutional Neural Network (CNN) is the central algorithm for pattern recognition tasks, such as image classification, speech processing and language translation. More than 95% of the CNN training and inference time is spent in matrix multiplication of the fully-connected and convolutional layers [55]. Numerous engineering and data processing algorithms, such as matrix decomposition, Principal Component Analysis (PCA) and k-Means continue to heavily rely on matrix multiplication. To meet the surging demand, major chip vendors integrate new hardware solutions for matrix operations. IBM® POWER10 features MMA units which are intended to accelerate matrix operations on data of any type stored in vector registers [84]. Intel® introduced Advanced Matrix Extensions (AMX) designed to work on 8- or 16-bit matrix data stored in two-dimensional registers, called tiles [61]. The differences in matrix accelerator unit implementations in the hardware trickle down the software stack. With more development in specialized hardware for AI, an explosion in the number of code generation paths will require new approaches.

For several decades, efficient code for the critical computational primitives has been provided by specialized numerical libraries. With the explosion in the variety of hardware architectures available on the market, the task of writing up-to-date assembly code for each platform becomes unsurmountable. This has spurred advances in the compiler technologies with Low-Level Virtual

Machine (LLVM) being the most prominent compiler infrastructure for domainspecific applications. Polyhedral loop analysis, network graph optimizations and heterogenous hardware code generation are all now avalaible as part of LLVM. The flexibility of the project allows to add new architecture targets promptly and efficiently. Multi-Level Intermediate Representation (MLIR), a project based on the LLVM infrastructure, has already integrated Intel's recently-added Advanced Matrix Extensions and compiler developers have integrated these changes in the exisiting numerical primitives [32].

## Chapter 2

# Background

General Matrix Multiplication (GEMM) is a standard routine from Basic Linear Algebra Subprograms (BLAS) that has been optimized for over 40 years and has close to peak performance implementations in the open-source libraries such as BLIS and OpenBLAS [70], [94]. In mathematical notation, GEMM is expressed by the formula:

$$C = \beta \cdot C + \alpha \cdot A * B \tag{2.1}$$

where  $\alpha$  and  $\beta$  are scalars,  $A_{M\times K}$  and  $B_{K\times N}$  are the input matrices, and  $C_{M\times N}$  is the output matrix. Most high-performance implementations of GEMM rely on the seminal work of Goto and Geijn [35]. Peak Central Processing Unit (CPU) performance for GEMM is achieved by a loop nest that optimizes data cache and Translation Lookaside Buffer (TLB) locality and leverages an efficient GEMM microkernel. Throughout the thesis, I refer to this algorithm as the conventional GEMM algorithm.

#### 2.1 Outer Product

Matrix multiplication is often introduced as the computation of multiple inner products, as defined by the sum  $C[i][j] = \sum_{k=1}^{K} A[i][k] \cdot B[k][j]$ . Implementations of GEMM directly using this inner product form suffer from poor reuse of loaded register values. Instead, the GEMM microkernel in BLAS libraries is implemented as multiple outer product computations.

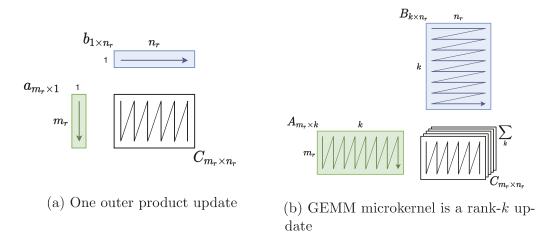

Figure 2.1: GEMM as outer product

Figure 2.1a shows one outer product update (rank-1 update) that computes partial result  $C_{m_r \times n_r} += a_{m_r \times 1} * b_{1 \times n_r}$ . In each update, elements of the vector  $a_{m_r \times 1}$  and elements of the vector  $b_{1 \times n_r}$  are loaded into vector registers. Either elements of a or b are broadcast in registers to produce an operand tile of size  $m_r \times 1$  or  $1 \times n_r$ . The values in registers are multiplied and accumulated to  $C_{m_r \times n_r}$ . To compute the full GEMM, this step is repeated for each column of  $A_{m_r \times k}$  and each row of  $B_{k \times n_r}$ , as shown in Figure 2.1b.

Unrolling the loop along k dimension and prefetching the next elements are commonly implemented to achieve better performance [35], [70], [94]. After k-loop unrolling, several columns of A and rows of B are used for each update to maximize vector-register utilization. Sizes  $m_r$  and  $n_r$  control the amount of register reuse by the outer product update [35]. These two parameters depend on the architecture and define the minimum GEMM size the microkernel will compute at peak performance. In order to utilize the microkernel for the full GEMM, a cache-aware strategy must tile the arrays into cache-sized buffers. Moreover, the elements should be placed in the buffers in the order in which they will be accessed by the outer-product updates, as shown in Figure 2.1b.

## 2.2 Accelerators With Outer and Inner Product

Matrix multiplication and other linear algebra operations can be expressed as a series of rank-k update operations. These operations compute the product of an  $m \times k$  matrix by another  $k \times n$  matrix, accumulating the result into an  $m \times n$  matrix. When k = 1, the operation reduces to an outer product of two vectors, of m and n elements, respectively as illustrated in Figure 4.1. A rank-k update can itself be decomposed to a sequence of k outer products.

#### 2.2.1 Matrix-Multiply Assist in POWER10

The MMA instructions were introduced in PowerISA 3.1 [50] as an extension of the Vector-Scalar Extension (VSX) facility. IBM's POWER10 processor is the first to implement these new instructions and functional units that perform two-dimensional matrix operations. MMA relies on 512-bit accumulator (ACC) registers to represent matrices, which can be manipulated by BLAS-like rank-k operations that consume vector registers as inputs. Each accumulator register is associated with four of the architecture's 128-bit vector-scalar registers (VSRs). While an accumulator is being used for MMA instructions, the associated VSRs are blocked from use. Up to eight of these accumulators can be use simultaneously, leaving 32 of 64 VSRs available for use as vector registers.

Outer-products have high-computational density since they are two-dimensional operations that compute mn element-wise operations from m+n input values. Therefore, they are the standard building block of high-performance linear algebra frameworks such as OpenBLAS and Eigen. In processors with one-dimensional vector instructions, the outer products are emulated using a combination of broadcasting and element-wise multiply-add instructions. MMA bypasses this emulation step by directly supporting outer product.

In the MMA rank-k update instructions, the updated matrix is stored in an ACC, while the operand vectors (or matrices) are provided through VSRs. The result matrix is either a  $4 \times 4$  matrix of 32-bit elements (floating-point or

Table 2.1: MMA instruction summary.

| Input type                  | Computation size              | Result         |

|-----------------------------|-------------------------------|----------------|

|                             | $m \times k \cdot k \times n$ | shape and type |

| 4-bit integer (i4)          | $4 \times 8 \cdot 8 \times 4$ | $4 \times 4$   |

| 8-bit integer (i8)          | $4 \times 4 \cdot 4 \times 4$ | i32            |

| 16-bit integer (i16)        | $4 \times 2 \cdot 2 \times 4$ |                |

| brain-float (bf16)          | $4 \times 2 \cdot 2 \times 4$ | $4 \times 4$   |

| IEEE half-precision (f16)   | $4 \times 2 \cdot 2 \times 4$ | f32            |

| IEEE single-precision (f32) | $4 \times 1 \cdot 1 \times 4$ |                |

| IEEE double-precision (f64) | $4 \times 1 \cdot 1 \times 2$ | $4 \times 2$   |

| TEEE double-precision (104) | 4 × 1 · 1 × 2                 | f64            |

integer) or a  $4 \times 2$  matrix of 64-bit floating point elements. The k is a function of the input data type, which can vary from 4-bit integers (k=8) to 32- or 64-bit floating-point numbers (k=1). For all input data types of 32-bit or less, the multiplying operands are represented by one VSR each. For 64-bit inputs, one operand is represented by a pair of VSRs ( $4 \times 64$ -bit elements) and the other by a single VSR ( $2 \times 64$ -bit elements). A summary of the MMA rank-k update instructions is shown in Table 2.1.

MMA can operate with several data types that have different sizes. Moreover, a single MMA instruction can accumulate multiple outer products depending on the size of the data elements. For instance, for a 32-bit data type, each 128-bit VSR contains four elements and the MMA instruction computes and accumulates a single outer product into the 512-bit accumulator that contains  $4 \times 4$  matrix elements [7]. Following BLAS terminology, such an instruction is called a rank 1 update [29]. However, for a 16-bit data type, each VSR contains eight elements and the MMA instruction computes and accumulates two outer products into the  $4 \times 4$ -element accumulator, thus computing a rank 2 update. For 8-bit data types the instruction computes rank 4 updates and for 4-bit data types it computes rank 8 updates. Table 2.1 shows the types supported by MMA. The computation size indicates the size of each operand and the rank of the update computed by an MMA instruction. For all types with up to 32 bits the result in the accumulator is 16 32-bit values organized in a  $4 \times 4$  grid. For f64 the accumulator contains  $4 \times 2$  elements of the matrix and performs a rank 1 update.

#### 2.2.2 Accelerators With Inner Product

IBM's POWER10 MMA uses outer product as a base operation, which allows for reuse of vector registers. In contrast, the Single Instruction, Multiple Data (SIMD) processing unity of IBM's Power9<sup>™</sup> VSX, and early versions, only feature inner-product operations. In the POWER10 MMA, after column elements of a matrix A and row elements of a matrix B are loaded into VSRs, each outer-product instruction computes a partial product of a piece of A × B. Each VSR lane of an MMA accumulator holds accumulated partial products of different cells of the resulting matrix C. Performing the accumulation in place in MMA eliminates the need for any additional data movement. In contrast, VSX inner product multiplies rows of matrix A by columns of matrix B which were loaded into VSRs. Each lane of the resulting inner-product VSR has an element-wise product. The final value of a cell of C is computed by adding each VSR lane together, in what is called a horizontal reduction.

Horizontal reductions are more expensive than vertical reductions<sup>1</sup> because their latency is proportional to a SIMD vector length [92]. The across-lane computation required for a horizontal reduction defeats the goal of parallel computation on each SIMD lane in vectorization. To make a better usage of vector instructions, efficient linear-algebra libraries, such as OpenBLAS [93] and Eigen [38], emulate an outer-product computation by changing how the input elements are loaded into SIMD vector lanes. This emulation technique consists in broadcasting a single column element of matrix A over all SIMD lanes of a vector register to multiply it with a vector register with row elements of B. This strategy is more performant than direct inner-product matrix multiplication. However, it wastes vector register space and reduces the utilization of the level 1 cache because neighboring elements that are already in the cache are not readily loaded into registers.

Both Intel's AMX [53] and Arm's ME only support inner-product operations. AMX computes a block of the resulting matrix C through an inner-product

<sup>&</sup>lt;sup>1</sup>Also known as element-wise reductions.

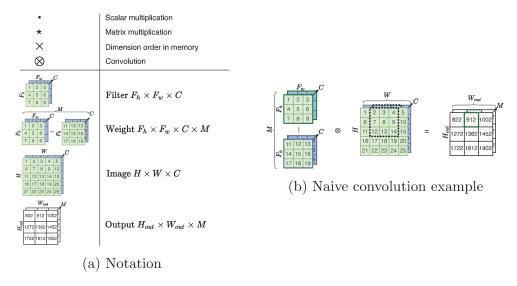

Figure 2.2: Convolution Notation and an Example of Naive Convolution

multiplication of 2D tiles of matrix A and matrix B. Arm's ME can emulate outer product using the broadcasting technique used in libraries.

#### 2.3 Convolution Notation

Convolutional neural networks consist of layers, each of which has a fixed weight tensor. Each convolutional layer can be expressed by the formula:

$$W_{F_h \times F_w \times C \times M} \otimes I_{H \times W \times C} = O_{H_{out} \times W_{out} \times M}$$

(2.2)

where  $I_{H\times W\times C}$  and  $O_{H_{out}\times W_{out}\times M}$  are the input and output tensors and  $W_{F_h\times F_w\times C\times M}$  is the weight tensor.

Figure 2.2a illustrates the tensor notation and the meaning of symbols  $\cdot$ , \*,  $\otimes$ , and  $\times$  used throughout this thesis. A variable input to each layer is the tensor  $I_{H\times W\times C}$  that contains an image of height H, width W and the number of input channels C. Shown in Figure 2.2a, a weight tensor has shape  $F_h \times F_w \times C \times M$  and consists of M filters. Each filter is a tensor of shape  $[F_h \times F_w \times C]$ , where C is the number of channels,  $F_h$  is the height of the filter, and  $F_w$  its width. The output tensor has dimensions  $[H_{out} \times W_{out} \times M]$ , where  $H_{out}$  and  $W_{out}$  are the output image height and width. Vertical and horizontal padding  $P_h$ ,  $P_w$  with zero-elements are typically applied to enlarge the input image so that the output image is of the same size  $(H_{out} = H, W_{out} = W)$ .

## Chapter 3

# KernelFaRer: Replacing Native-Code Idioms with High-Performance Library Calls

General matrix-matrix multiplication (GEMM) and symmetric rank-2k update (SYR2K) are simple to implement naively but complex when designed to optimize the memory hierarchy [35]. GEMM in particular is idiomatic because it can be succinctly expressed and it exhibits a direct relation between implementation complexity and performance [74]. Most generic compiler loop transformations fail to exploit specific features of programming idioms such as GEMM [12], [37]. This chapter reaffirms that both sophisticated programmers and compilers still do not generate code with the performance of well-tuned libraries [34]. Thus, instead of optimizing an idiom, a compiler may simply replace it with a call to a library such as the Basic Linear Algebra Subprograms (BLAS) library [9]. These expertly crafted implementations efficiently exploit the memory hierarchy and can deliver high throughput on their target platform [22], [35], [93]. This chapter argues that idiom replacement must be both robust and safe in order to be an effective solution.

Despite progress in recent research [18], [34], existing approaches for idiom identification are brittle and fail to recognize minor variants of an idiom. Existing solutions require intimate knowledge of polyhedral analysis [18] or of a new domain-specific language that describes idioms [34]. They also have high compilation time costs even when the target idiom is absent from the code

(see Section 3.3.5).

Our solution is a new optimization pass for the LLVM framework [64]. This pass combines tree matching and idiom recognition [14], [68], [74], [75] with a data dependence analysis to deliver a robust idiom recognition and a safe replacement strategy. Previously, Carvalho et al. presented a work-in-progress report of this compiler pass [15]. This solution extends tooling already present in the LLVM framework and is fully integrated in this widely used compiler framework. Therefore it will be easier to adopt, maintain and update. This chapter also introduces the first, to the best of our knowledge, formulation of an analysis that determines a GEMM matrix's access order by matching the induction variables used in the memory access (see Section 3.2.1). Access-order detection is crucial to enable transparent and correct usage of high-performance libraries.

This chapter makes the following contributions:

- A robust idiom-recognition compiler pass that identifies many variants

of the GEMM and SYR2K idioms and replaces them with optimized

library calls (see Section 3.2 and Section 3.2.3). Kernel Finder &

Replacer (KernelFaRer)<sup>1</sup> identifies both n\u00e4ive implementations and

hand-optimized variants of these idioms(see Section 3.3.3).

- 2. The first formulation of an analysis that determines a GEMM matrix's access orders by combining pattern matching and loop information analysis in LLVM **Intermidiate Representation (IR)** (see Section 3.2.1). The same strategy was employed to match SYR2K's access order.

- 3. An experimental evaluation that provides evidence that: (a) the pass is robust and identifies many more idiom variants than other approaches; (b) the addition to compilation time is significantly smaller; (c) the increase in performance is consistent across architectures and libraries (see Section 4.2).

The remainder of the chapter is organized as follows: Section 3.1 presents

<sup>&</sup>lt;sup>1</sup>Source code available at https://github.com/jaopaulolc/KernelFaRer.

background material; Section 3.2 details how LLVM IR pattern matching and optimized library call insertion are combined in KernelFarer's implementation; Section 4.2 describes the experimental setup and analyzes the performance improvements achieved by the proposed approach when compared with current solutions and manual library-based programming.

### 3.1 Pattern Matching Idioms

This section presents programming idioms in the context of pattern matchers that target idioms in LLVM IR code and reviews how the GEMM operation is typically programmed and optimized.

#### 3.1.1 Programming Idioms

Programming idioms are recurrent constructs that express a computation, can be easily recognized (by humans), and are simple to compose [74]. The introduction of the array-oriented APL language in the 1960s [54] with concise statements that exhibit high memory and high runtime complexity motivated research on idiom recognition and selection [82]. Later, recognition of idioms was used in many programming languages [14], [18], [34], [41], [44], [45], [60], [68], [75]. Existing idiom-based approaches differ mostly on:

- the program representation usually graph-based structures (e.g. data-dependence graphs, expression trees);

- the matching algorithm (e.g. depth-first traversals or solver-based);

- the normalization constraints for the matching mechanism to work (e.g. memory accesses must be affine) or to be more effective (e.g. common subexpressions elimination);

- how idioms are expressed, either through a domain-specific language (DSL) or programatically via a Visitor Pattern [72], and replaced (e.g. code generation or employment of high-performance library).

Figure 3.1: (a) Idiom of finding the length of a string and (b) returning the minimum of 2 numbers.

Idioms have concise syntax and convey common understanding of recurrent computations [54]. For example, Figure 3.1(a) shows an idiom, written in C, for finding the length of a string s. This example relies on the NULL byte at the end of well-formed strings, a false value in C that terminates the loop. Figure 3.1(b) shows how a ternary operator concisely expresses the min operation without the need for if/else control flow. This chapter identifies larger idioms that express an identifiable and well-known operation: GEMM. These idioms often account for a significant portion of the execution time of an application and their performance can be greatly improved by replacing them with calls to fine-tuned libraries.

#### 3.1.2 Pattern Matching in LLVM IR

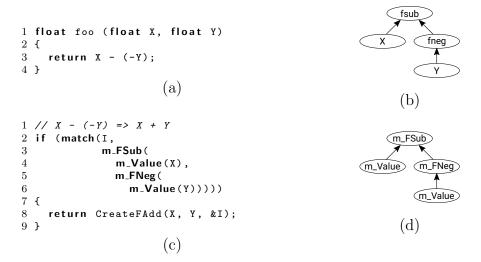

The LLVM compiler framework has a PatternMatch namespace that provides a mechanism to build simple and efficient matchers for LLVM IR [64]. PatternMatch is used for static analysis (e.g. Demanded-Bits and Instruction-Simplify analyses), code generation (e.g. Instruction Selection) and transformations (e.g. Instruction Combining). The code in Figure 3.2 illustrates how PatternMatch can simplify instructions in the LLVM InstCombine pass.

Figure 3.2(b) shows the tree representation of the expression in the return statement in line 3 of Figure 3.2(a). Figure 3.2(c) has a code excerpt from the LLVM InstCombine pass that employs PatternMatch to simplify the expression X - (-Y) into X + Y, shown as a tree in Figure 3.2(d) <sup>2</sup>. In the code of Figure 3.2(c), I references an fsub (floating-point subtract) instruction. The method match(V, P) returns true if and only if the value V matches the pattern P.

PatternMatch provides template methods that both describe IR patterns

<sup>&</sup>lt;sup>2</sup>The code in LLVM uses a visitor for fsub instructions that only matches fneg.

Figure 3.2: (a) Double negation example; (b) Tree representation of (a); (c) Matcher and replacement code; and (d) Pattern matched.

and bind values in the pattern to pass variables. For example, the m\_FSub and m\_FNeg methods shown describe the instructions fsub and fneg. The m\_Value method matches and binds the left-hand side operand of fsub to X and the single argument of fneg to Y. PatternMatch also provides flexible commutative versions of matcher methods ( $e.g.m_c$ \_FAdd<sup>3</sup>) that avoids cumbersome code describing and testing two symmetric patterns. Within a basic block, LLVM can find simple patterns used for instruction selection.

The LLVM LoopIdiomRecognize attempts to recognize two idioms — memory-set and memory-copy — to replace the loop code with the llvm.memset and llvm.memcpy intrinsics. Backends generate inline code or runtime library calls for these intrinsics. The existing LLVM PatternMatch cannot be used in the LoopIdiomRecognize pass because it is limited to the scope of a single basic block. Instead, that pass employs only Data-Flow Analyses (DFAs) [1] to identify and replace both memory idioms. KernelFarer uses PatternMatch to find loop idioms and DFAs to assess if the the transformations are legal.

## 3.1.3 General Matrix-Matrix Multiplication

General matrix-matrix multiplication (GEMM), already pervasive in linear algebra computations [46], regained attention because convolution kernels

<sup>&</sup>lt;sup>3</sup>\_c indicates that the instruction to be matched (fadd) is commutative.

```

1 void cblas_dgemm (

const CBLAS_LAYOUT Layout,

3

const CBLAS_TRANSPOSE transa,

const CBLAS_TRANSPOSE transb,

const int m, const int n, const int d,

const double alpha,

*a, // A's base address

7

const double

lda, // and leading dimension

*b, // B's base address

8

const int

9

const double

ldb, // and leading dimension

10

const int

const double

11

beta,

*c, // C's base address

12

double

ldc); // and leading dimension

13

const int

```

Figure 3.3: CBLAS interface for double-precision GEMM.

used in neural networks can be efficiently implemented using GEMM as a primitive [19]. Formally, GEMM can be defined as follows.

**Definition 1.** Let A and B be matrices of dimensions  $M \times D$  and  $D \times N$  respectively. Let  $\alpha$  and  $\beta$  be any value in  $\mathbb{R}$ . The general matrix-matrix product of A and B is a matrix C of dimensions  $M \times D$  such that:

$$C(i,j) = \beta \cdot C(i,j) + \alpha \cdot \sum_{k=1}^{D} A(i,k) \cdot B(k,j)$$

(3.1)

Although a naïve implementation of GEMM is simple, seminal work by Goto et al. shoroughly 80%ws that a fast GEMM must utilize the memory hierarchy well [35]. Their approach splits the computation into blocks to increase data reuse; and creates a matrix memory layout that increases temporal and spatial access locality, a process called *packing the matrices*. The central idea is to focus on the data movement from main memory, through caches, and into the processor's registers.

The GotoBLAS library [35] inspired other BLAS libraries. Processor-manufacturer solutions include IBM's Engineering and Scientific Subroutine Library (ESSL) [49] and Intel's Math Kernel Library (MKL) [51]. Manufacturers also contribute to OpenBLAS [70]. AMD's version is the BLAS-like Library Instantiation Software (BLIS) framework [94]. CBLAS is a unified interface to these libraries for C languages [9].

Figure 3.3 shows the interface for double-precision GEMM. The Layout specifies if the resulting matrix C is stored in row-major or column-major order. The arguments transa and transb indicate if the matrices A and B

are transposed, allowing matrices in different storage orders to be multiplied without the creation of copies. An idiom matcher (see Section 3.2) must deduce the layout of the matrices being matched to obtain these first three parameters. The matrix dimensions (m, n, and d) appear in line 5, followed by the scalar factors  $\alpha$  and  $\beta$  (lines 6 and 11), and the base address pointers (lines 7, 9, and 12). The leading dimensions (lines 8, 10, and 13) are the number of elements in the *first* dimension of each matrix.

BLAS libraries rely heavily on direct use of assembly and thus are not portable across platforms, thus the many versions of BLAS. In contrast, Eigen [38] implements BLAS routines using C++ template meta programming to hierarchically organize the decisions and the tuning for each platform. The templates encode platform-specific information that allow the compiler to choose a strategy that is tuned based on cache sizes, vectorization support and other instruction-set-architecture features (e.g. fused multiply-add support). Eigen also relies on code transformations available in modern compilers such as GNU's C/C++ Compiler (GCC) and Clang [21]. There is no routine to call to compute GEMM in Eigen because it is a header-file only library that defines builtin vector and matrix types. Computations are overloaded operations on these types. Thus, the programmer needs to include the header files providing Eigen's types and operators and write C++ expressions of the form: C = beta \* C + alpha \* A \* B as per Definition 1. Using Eigen to replace a GEMM idiom required the creation of a wrapper library encapsulating Eigen code (see Section 3.2.3).

## 3.2 An Idiom Recognition and Replacement Pass

This section presents Kernelfarer, an LLVM IR pass that performs idiomatic code rewrite and is integrated into LLVM's standard optimization pipeline. Kernelfarer is an independent IR pass that extends the LLVM PatternMatch Application Programming Interface (API) (see Section 3.1.2) with custom matchers to identify more complex idioms. Kernelfarer works

independently of other LLVM optimization frameworks like Polly, but it can be of assistance to it or other paths to code generation. The description of this pattern-matching extension is demonstrated in a GEMM case study. However, the methodology is flexible enough to capture all IR constructs and thus enables the description of many idioms. In fact, performance results with our prototype implementation of a SYR2K matcher and replacer are discussed in Section 4.2. A standard data-flow analysis is sufficient to determine if values computed in the idiom are used elsewhere in the program and thus can also be extended to other idioms.

The Kernelfarer's algorithm can be divided into three phases as follows:

- 1. Identify candidates that match the target idiom through IR matchers (see Section 3.2.1).

- 2. Check data dependences and isolate the matched code (see Section 3.2.2).

- 3. Replace the idiom with a call to a high-performance library (see Section 3.2.3).

Phase 1 uses LLVM's PatternMatch to identify IR code that matches the target idiom. The data-dependence analysis in Phase 2 determines if the replacement of the matched code with a library call is legal. This phase also determines if code transformations, such as loop distribution or loop invariant code motion, are needed to make the transformation legal.

#### 3.2.1 GEMM Pattern Matching (Phase 1)

GEMM memory access patterns can be expressed in a higher-level programming language as shown in Figure 3.4. The variables  $iv_i$ ,  $iv_j$ , and  $iv_k$  on line 1 of Figure 3.4(a) are induction variables of a level-three loop nest (or deeper). The for loop syntax in Figure 3.4(a) indicates that the three loops can be nested in any order. For any nesting order, the reduction on line 2 expresses a GEMM. Parenthesis operators are used for indexing the arrays to indicate that the elements of the array may be accessed either in column-major or in row-major order. For instance, A(i, k) means that the element on the i-th

```

1 \%41 = phi [\%53, \%40], [0, \leftrightarrow]

%25]

2 \%42 = phi [\%52, \%40], [0, \leftrightarrow]

1 for (0 <= iv_i < M; 0 <= iv_j < N;

%251

0 \le iv_k \le D

C(iv_i, iv_j) += A(iv_i, iv_k) * B(iv_k, iv_j)

3 \%43 = mul \%41, \%17

4 \%44 = add \%43, \%23

(a)

5 \%45 = getelementptr \%4, \%44

6 \%46 = load \%45

1 operator()(iv_1, iv_2) {

2 return *(addr + iv_2 * 1d + iv_1);

7 \%47 = mul \%41, \%16

8 \%48 = add \%47, \%26

9 \%49 = getelementptr \%6, \%48

(b)

10 \%50 = load \%49

1 operator()(iv_1, iv_2) {

= fmul %46, %50

11 %51

return *(addr + iv_1 * 1d + iv_2);

12 \%52 = fadd \%42, \%51

13 \%53 = add \%41, 1

(c)

14 \%55 = icmp eq \%53, \%21

15 br %55, %30, %40

```

Figure 3.4: (a) Memory access of GEMM in source code; (b) colum-major access order; (c) row-major access order; (d) Simplified LLVM IR code of the innermost loop in (a) (Code in (b) and (c) is in C/C++).

row and k-th column is accessed. The implementation of the operators for column-major order is shown in Figure 3.4(b) while the row-major access is shown in Figure 3.4(c), where addr is the base address of an array and 1d is the leading dimension of the array. The dimensions of the matrices are:  $A_{M\times D}$ ,  $B_{D\times N}$ , and  $C_{M\times N}$ .

Identifying a GEMM idiom requires the identification of its two components: the loop nest on line 1 and the reduction operation on line 2 of Figure 3.4(a). The multiply-and-add operations of the reduction idiom appear on lines 11-12 of the LLVM IR of the innermost loop nest shown in Figure 3.4(d). In this **Static Single Assignment (SSA)** representation the result of each instruction is assigned a unique value. Thus, each of the instructions in Figure 3.4(d) can be referred to by its value V. For instance, the fmul in line 11 is uniquely identified by the value %51 and the fadd in line 12 by the value %52. In general, when presenting an algorithm that iterates over all the instructions in the body of a loop L, this chapter will say "for all values V in L".

A *GEMMReduction* is a multiply-add instruction sequence that satisfies the following conditions: 1. it appears in the innermost level of a loop nest of at least depth three; 2. the operands are memory accesses to arrays; 3. the address

```

1 template <typename MatcherType>

2 auto MatchStoreOfMatrixC(MatcherType GEMMReduction, Value C, Value

Alpha, Value Beta, PHINode iv_1, PHINode iv_2, Value LDC, Value GEP)

return m_Store(

4

OneOf(ScaledVOrV(Alpha, GEMMReduction),

ScaledVOrV(Beta, m_PHI(m_Value(), GEMMReduction)),

5

6

m_c_FAdd(ScaledVOrV(Beta, m_Load(GEP)),

7

ScaledVOrV(Alpha, m_PHI(m_Value(), GEMMReduction)

))),

8

ArrayAccess(C, iv_1, iv_2, LDC));

9 }

(a)

1 inline auto GEMMReduction (Value AddLHS, Value MulLHS, Value MulRHS,

PHINode iv_1^A, PHINode iv_2^A, PHINode iv_1^B, PHINode iv_2^B, Value Alpha,

Value LDA, Value LDB) {

2

return MultiplyAdd(

3

Alpha, AddLHS, \mathbf{m}_{\text{-}}\mathbf{Load}(\mathbf{ArrayAccess}(\mathbf{MulLHS},\ iv_1^A,\ iv_2^A,\ \mathbf{LDA})),

\mathbf{m}_{-}\mathbf{Load}(\mathbf{ArrayAccess}(\mathbf{MulRHS},\ iv_1^B,\ iv_2^B,\ \mathbf{LDB}));

4

5 }

(b)

1 auto ArrayAccess(Value Op, PHINode iv_1, PHINode iv_2, Value LD) {

return OneOf (

{\tt m\_GEP} \, ({\tt m\_Load} \, ({\tt m\_GEP} \, ({\tt Op} \, , \, \, {\tt m\_PHI} \, (iv_2))) \, , \, \, {\tt m\_PHI} \, (iv_1)) \, ,

m\_GEP(m\_GEP(Op, PHITimesLD(iv_1, LD)), m\_PHI(iv_2)),

5

m\_GEP(m\_GEP(Op, m\_PHI(iv_2)), PHITimesLD(iv_1, LD)),

6

m\_GEP(Op, m\_PHI(iv_1), m\_PHI(iv_2)),

7

exttt{m\_GEP(Op, AffineFunctionOfPHI}(iv_1, iv_2, LD));

8 }

(c)

```

Figure 3.5: (a) Matcher of a store of *GEMMReduction* into matrix C; (b) *GEMMReduction* matcher; and (c) Matcher for an array access.

of the memory accesses are affine expressions of the form  $\mathtt{addr} + iv_x \times \mathtt{ld} + iv_y$ , where  $iv_x$  and  $iv_y$  are index variables in the loop nest and  $\mathtt{addr}$  is a loop-invariant expression — either the base address of a matrix or the base address or a block within the matrix; and 4. the combination of induction variables used in the address expressions is one of the combinations shown in Table 3.1.

The first component of the pattern, loop nests, are identified using LLVM's LoopInfo analysis pass. LoopInfo provides a consistent way to retrieve loop information from the IR of a program, such as the nesting level of a given loop. The second part of the pattern, *GEMMReduction*, cannot be identified with the existing LLVM PatternMatch API. Therefore, KERNELFARER extends PatternMatch by adding new matchers and new constructs for matching more complex patterns. Figure 3.5 shows the main patterns contributed by

KERNELFARER, those printed in red are the proposed extensions and those in black are the existing constructs. The main pattern that matches a store of a *GEMMReduction* to the destination matrix C is shown in Figure 3.5(a), a similar pattern was created to match SYR2K reductions.

Kernelfarer introduces the OneOf combiner construct to allow a list of multiple matchers, which usually represent subtle variations in a target pattern, to be tested in turn. OneOf only returns a successful match if one of the provided sub-matchers match the underlying piece of LLVM IR. This construct is widely used in Kernelfarer extensions to facilitate the description of variations in the target pattern. PatternMatch provides basic disjunctive and conjunctive nodes. Disjunction nodes allows the capturing of idioms with polymorphic components. Conjunction nodes allow further specification and pattern component constraints. Combining OneOf with these nodes makes Kernelfarer pattern matcher more robust. For example, ScaledVOrV(s, V) uses the disjunctive node to match either s\*V or V, where V is any value represented by a Kernelfarer & PatternMatch matcher.

Figure 3.5(b) shows the matcher that captures the GEMMReduction itself, where MultiplyAdd matches expressions of the form  $\alpha*A*B.^4$  ArrayAccess, shown in Figure 3.5(c), is the matcher that identifies accesses to arrays in different representations. Lines 3-6 are the sub-matchers representing different variants of access to 2D arrays, while in line 7 the matcher identifies flat-arrays. m\_GEP and m\_PHI match their respective IR instructions, namely getelementptr and  $\phi$ -nodes. Flat-arrays have indexing expressions that are affine functions of loop induction variables and such expressions are matched with AffineFunctionOfPHI. 2D-array accesses have an idiomatic expression that multiplies an induction variable by a matrix leading dimension. PHITimesLD captures two variants of this idiom, thus matching wether the multiplication is performed by a multiply (mul) or by a shift-left (sh1) LLVM IR instruction.

$<sup>^4\</sup>alpha$  is optionally matched by using PatternMatch's disjunctive node.

# **Algorithm 1** LLVM IR Pass to find GEMM candidates.

```

1: function FINDGEMMIRPASS(Function F, LoopInfo LI)

LoopList \leftarrow FINDINNERDEEPLOOPS(F, LI)

for all Loops L in LoopList do

3:

4:

for all Values V in L do

if GemmPattern.Match(V) then

5:

IVList \leftarrow \{iv_1^A, iv_2^A, iv_1^B, iv_2^B, iv_1^C, iv_2^C\}

6:

(OrderList, iv_i, iv_j, iv_k) \leftarrow MATRIXACCESSOR

7:

DER(IVList)

8:

(M, N, D) \leftarrow LOOPSUPPERBOUND(LI, iv_i, iv_i, iv_k)

9:

if AllGemmValuesFound() then

A \leftarrow Matrix(OrderList, M, N, D)

10:

B \leftarrow Matrix(OrderList, M, N, D)

11:

12:

C \leftarrow Matrix(OrderList, M, N, D)

13:

Gemm \leftarrow (L, IVList, A, B, C)

14:

Candidates.Insert(Gemm)

15: function MATCH(Value V, Pattern P)

return P.MATCH(V)

16:

17: interface Pattern<T>::match(Value V)

18: function Pattern<FADD>::Match(Value V)

AddOper0 \leftarrow V.GETOPERAND(0)

19:

20:

AddOper1 \leftarrow V.GETOPERAND(1)

21:

return FADD_MATCH(AddOper0, AddOper1)

```

#### Algorithm to match a GEMM

The central idea of this chapter is that the loop information provided by the compiler can be used to constrain the search for the target idiom's components to the places where it is possible for them to occur. In LLVM, the nesting level, entry, exit, and latch basic blocks for each loop are available through the LoopInfo pass. However, there are two limitations: (1) in a kernel that has been optimized through blocking, the inner loops are not in canonical form; and (2) the induction-variable information is only available for canonical loops via the LoopInfo pass [64]. Kernelfarer's solution is to combine basic-block and loop-nesting information from LoopInfo with PatternMatch. In LLVM IR, induction variables are lowered to  $\phi$  instructions with at least two incoming values: an initialization value; and a new value that comes from the loop's latch basic block. Kernelfarer's general idiom recognizer uses PatternMatch to match these  $\phi$  instructions.

Algorithm 1 uses PatternMatch and the LoopInfo pass to identify GEMM

Table 3.1: Access offset expressions for all combinations of column-major (CM) and row-major (RM) order.

| Access Order |       | rder  | Offset Expressions        |                                                                                    |                                                                                                                     |  |

|--------------|-------|-------|---------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|

| C            | A     | B     | C                         | A                                                                                  | В                                                                                                                   |  |

| RM           | RM    |       | $iv_i \times ld_C + iv_j$ | $iv_i \times ld_A + iv_k$                                                          |                                                                                                                     |  |

| CM           | IUIVI | RM    | $iv_j \times ld_C + iv_i$ | $ \iota v_i \wedge \iota u_A + \iota v_k $                                         | $ iv_k \times ld_B + iv_i $                                                                                         |  |

| RM           | CM    | ICIVI | $iv_i \times ld_C + iv_j$ | $iv_k \times ld_A + iv_i$                                                          | $\left \begin{array}{c} \iota v_k \wedge \iota u_B + \iota v_j \end{array}\right $                                  |  |

| CM           | OWI   |       | $iv_j \times ld_C + iv_i$ | $\left \begin{array}{c} \iota v_k \wedge \iota u_A + \iota v_i \end{array}\right $ |                                                                                                                     |  |

| RM           | RM    |       | $iv_i \times ld_C + iv_j$ | $iv_i \times ld_A + iv_k$                                                          |                                                                                                                     |  |

| CM           | 10101 | CM    | $iv_j \times ld_C + iv_i$ | $ \iota v_i \wedge \iota u_A + \iota v_k $                                         | $ iv_i \times ld_B + iv_k $                                                                                         |  |

| RM           | CM    | OWI   | $iv_i \times ld_C + iv_j$ | $iv_k \times ld_A + iv_i$                                                          | $\left \begin{array}{c}\iota \iota \iota_{\jmath} \wedge \iota \iota \iota_{B} + \iota \iota_{k}\end{array}\right $ |  |

| CM           |       |       | $iv_j \times ld_C + iv_i$ | $ \iota v_k \wedge \iota u_A + \iota v_i $                                         |                                                                                                                     |  |

candidates. First, using the LLVM LoopInfo pass, find all innermost loops that are nested at the third (or deeper) level and place these loops in a list (line 2). Then, iterate over all instructions (value V in line 4) inside those loops, invoking the method MATCH of a GemmPattern object on each one of them. The generic interface for MATCH is shown in line 17, where T can be any LLVM IR instruction type. Each instruction type in a pattern must have an implementation for the MATCH interface. For instance, the implementation of MATCH for FAdd for the GEMM pattern is shown on line  $18^5$ . To find the idiom, MATCH descends the IR tree matching the specified pattern.

Values from the IR are captured through matcher objects of type BINDTYPE. GemmPattern contains such objects to capture, for instance, values associated with a GEMM's induction variables and memory address instructions.

#### Determination of the Matrix Access Order

A crucial step to replace a GEMM idiom with a call to a library is to determine the access order used by the idiom for each matrix (Algorithm 1, line 7). These access orders are required by the library call that will replace the detected idiom (see Section 3.2.3). This analysis differs from the work of Wolfe et al. where the iteration domain is analyzed to identify dependencies in a loop [71].

$<sup>^5</sup>$ The FADD\_MATCH in line 21 is an algorithmic simplification of an object-oriented code structure in LLVM. It abstracts the matching of both operands of a fadd instruction referenced by V (line 18) using the FAdd\_Match object within GemmPattern.

Table 3.2: Conditions to determine the access orientation.

| Access Order |    | Equalities to derive access order of |                              |                              |  |  |  |

|--------------|----|--------------------------------------|------------------------------|------------------------------|--|--|--|

| A            | В  | A and $B$                            | (                            | C                            |  |  |  |

| Л            |    | A and D                              | RM                           | CM                           |  |  |  |

| RM           | RM | $o_A = l_B$                          | $l_C = l_A \wedge o_C = o_B$ | $l_C = o_B \wedge o_C = l_A$ |  |  |  |

| CM           | RM | $l_A = l_B$                          | $l_C = o_A \wedge o_C = o_B$ | $l_C = o_B \wedge o_C = o_A$ |  |  |  |

| RM           | CM | $o_A = o_B$                          | $l_C = l_A \wedge o_C = l_B$ | $l_C = l_B \wedge o_C = l_A$ |  |  |  |

| CM           | CM | $l_A = o_B$                          | $l_C = o_A \wedge o_C = l_B$ | $l_C = l_B \wedge o_C = o_A$ |  |  |  |

Here the goal is to identify the access order of each matrix in the target pattern.

Table 3.1 shows the offset expressions according to the access order of the matrices assuming that the index variables are  $iv_i$ ,  $iv_j$ , and  $iv_k$ . When a multiply-and-add operation that is a candidate to be a GEMM reduction is encountered, the expressions for the access into the matrices are identified as  $l_C \times ld_C + o_C$ ,  $l_A \times ld_A + o_A$ , and  $l_B \times ld_B + o_B$  where  $l_C$  is the index variable for the leading dimension of matrix C and  $o_C$  is the offset into that dimension of  $C^6$ . The same logic is applied to the matrices A and B. The access order can be deduced by examining which of the index variables are identical in the multiply-and-add idiom candidate.

Table 3.2 shows the equality conditions that determine the access order for matrices A and B. For instance, if  $o_A = l_B$ , then both matrices A and B are accessed in row-major order as shown in the first two rows of Table 3.1. Given that all the possible combinations for access orders for a GEMM are given in Table 3.1, it follows that if none of the equality constraints shown on the second column of Table 3.2 are met, then the multiply-and-add cannot be a GEMM reduction.

To illustrate how to determine the access order of C, let's examine the two top rows of Table 3.1 where both matrices A and B are accessed in row-major order. There are two cases. If  $l_C = l_A$  and  $o_C = o_B$  then C is accessed in row-major order. If  $l_C = o_B$  and  $o_C = l_A$ , then C is accessed in column-major order. If neither of these conjunctions are satisfied, then the multiply-and-add

$<sup>^6</sup>l_X$  and  $o_X$  are also known as the angular and linear coefficients of a linear function, such as those in indexing expressions used to access array elements.

is not a GEMM reduction. Similar sets of conjunctions can be written for the other three combinations of access order for A and B as shown in Table 3.2.

This strategy can also be used to detect the access order of matrices in other computational kernels (e.g., SYR2K).

## Loop Upper Bounds

The intuition to determine loop upper bounds is that the index variable of a loop must be initialized prior to starting the execution of the loop and must be updated within the loop body. Therefore, in the SSA representation there must be a  $\phi$  instruction that merges the initialization path with the update path at the first basic block of a loop. First, add all  $\phi$  instructions that are in the first basic-block of the loops and that use  $iv_i$ ,  $iv_j$ , or  $iv_k$  to a work list. Then, match each  $\phi$  instruction in this list against a pattern tree that represents the instruction sequence for the loop index update and loop comparison<sup>7</sup>. The upper bound of a loop L is the operand compared with the value defined by the  $\phi$  instruction if the pattern belongs to the latch block of L. All GEMM instances matched by GemmPattern that have a valid access order and for which loop nests upper bounds can be determined are candidates for replacement with a call to a library (see Section 3.2.3). Now, a data-flow analysis must establish the legality of the transformation.

In the triangular iteration space of SYR2K two out of tree induction variables are traversed in the same way as in GEMM and the third variable's (J) upper (lower) bound is dependent on another variable (I). To detect this pattern, Kernelfare checks for the presence of I in the  $\phi$  instruction for J. This detection method can be thwarted by the insertion of auxiliary induction variables.

## 3.2.2 Data-Dependence Analysis

Idiom replacement must preserve program behavior, including writes to memory and outputs. Also, any inner-loop code that is not part of the GEMM reduction must be safely moved out of the loop nest. A liveness and side-effects analysis

<sup>&</sup>lt;sup>7</sup>This instruction sequence is idiomatic of loop-exit conditions.

### **Algorithm 2** Data-Dependence Analysis IR Pass.

```

1: function AnalysisPass(Function F, Kernel K)

L \leftarrow K.GETASSOCIATEDLOOP()

2:

3:

for all Instructions I in L do

if I \in K. Values or I \in K. Stores then continue

4:

if I.MAYWRITETOMEMORY() then

5:

6:

return False

if I.MAYHAVESIDEEFFECTS() then

7:

return False

8:

9:

for all Users U of Instruction I do

B \leftarrow BasicBlock of I

10:

11:

if B \notin L then

12:

return False

13:

return True

```

of the use-def chains in the idiom's loop nest can be combined to determine if any intermediate value is live after the idiom or produces side-effects during the computation. This analysis differs from the loop dependence analysis of Wolfe et al. [71].

The Data-Dependence Analysis in Algorithm 2 receives the IR for a function F and a Kernel object found within F. It returns a boolean indicating if the idiom replacement is legal. At the matching stage, the algorithm gathers two data structures. (K.Values) contains matrix pointers, offsets and intermediate values; (K.Stores) contains the stores in the Kernel. These data structures afford flexible access to the Kernel parameters and enable checking that the only extra stores in the loop nest are initializations stores.

The Data-Dependence Analysis algorithm iterates over all instructions in the kernel's associated loop (line 3) skipping those that are in the kernel (line 4). If an instruction may store to memory (line 5) or produces side-effects such as throwing an exception (line 7), return False. The algorithm also checks for data flow from definitions in the kernel innermost loop to uses after the loop (lines 9 - 12).

The kernels in Figure 3.6 illustrate when instructions may or may not be moved out of a GEMM loop. Two of them, Figure 3.6(b) and (c), are from benchmarks in PolyBench [77]. In spite of its simplicity, the naïve GEMM implementation in Figure 3.6(a) cannot be directly rewritten because of the

```

1 for (long i = 0; i < M; i++)

2

for (long j = 0; j < N; j++) {

3

C[i][j] = 0.0;

1 for (long r = 0; r < R; r++)

4

for (long k = 0; k < D; k++)

for (long q = 0; q < Q; q++) {

5

C[i][j] +=

3

for (long p = 0; p < P; p++) {

alpha * A[i][k] * B[k][j];

6

4

sum[r][q][p] = 0.0;

}

7

for (long s = 0; s < P; k++)

5

(a)

sum[r][q][p] +=

7

A[r][q][s] * C4[s][p];

for (long i = 0; i < M; i++)

8

}

for (long j = 0; j < M; j++)

9

for (long p = 0; p < P; p++)

for (long k = 0; k < N; k++) {

A[r][q][p] = sum[r][q][p];

10

4

C[i][j] +=

}

5

alpha * A[i][k] * B[j][k];

6

C[i][j] +=

(c)

alpha * B[i][k] * A[j][k];

7

(b)

```

Figure 3.6: (a) Naïve GEMM; (b) symmetric rank-2k operations (syr2k); and (c) Multiresolution analysis kernel (doitgen).

initialization of matrix C. This initialization must first be moved to a separate loop because all high-performance libraries assume that matrix C is initialized prior to calling the function that implements GEMM. Another possibility is to simply delete the GEMM reduction store that is in line 5 and to insert a library call at the exit-block of the loop nest — dead code can be removed later by LLVM passes. Side effects in the initialization of the matrix C could also prevent rewrite. Kernelfarer recognizes this idiom and replaces it if no side-effects exist.