**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI

films the text directly from the original or copy submitted. Thus, some

thesis and dissertation copies are in typewriter face, while others may be

from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality

illustrations and photographs, print bleedthrough, substandard margins,

and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete

manuscript and there are missing pages, these will be noted. Also, if

unauthorized copyright material had to be removed, a note will indicate

the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and

continuing from left to right in equal sections with small overlaps. Each

original is also photographed in one exposure and is included in reduced

form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations

appearing in this copy for an additional charge. Contact UMI directly to

order.

IIMI

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor MI 48106-1346 USA 313/761-4700 800/521-0600

### THE UNIVERSITY OF ALBERTA

Simulation Models for Variable Speed Electric Drives

by

# RAJAT BHARGAVA (C

A Thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for a degree of

Master of Science

Department of Electrical and Computer Engineering

Edmonton, Alberta

Fall 1997

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-22571-2

# University of Alberta

# LIBRARY RELEASE FORM

Name of Author

: Rajat Bhargava

Title of Thesis

: Simulation Models for Variable Speed Electric Drives

Degree

: Master of Science

Year This Degree Granted: 1997

Permission is hereby granted to THE UNIVERSITY OF ALBERTA, LIBRARY to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly or scientific research purposes only.

The author reserves other publication rights, and either the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.

Rajat Bhargava

Permanent Address: 3A, 9006-112<sup>th</sup> St.

Edmonton, Alberta

T6G 2C5

Date: 16th July 1997

# **University of Alberta**

# Faculty of Graduate Studies and Research

The undersigned certify they have read, recommended to the Faculty of Graduate Studies and Research for acceptance, a thesis entitled "Simulation Models for Variable Speed Electric Drives", submitted by Rajat Bhargava in partial fulfillment of the requirements for the degree of Master of Science.

John (. Salmon

(Supervisor)

Dr. I.M. Filanovsky

Date: Ut July 1997

# To Whom it may concern

# Co-author of the papers:

- 1. SPICE3 simulation techniques in Power Electronics

- 2. SCR harmonic correction topologies for VSI drives

Dr. E. Nowicki

University of Calgary

Department of Electrical and Computer Engineering

2500 University Drive N.W.

Calgary, AB T2N 1N4

Phone: 403 220 5006

Email: nowicki@enel.ucalgary.ca

# To Whom it may concern

As a co-author of the papers titled "SPICE3 simulation techniques in Power Electronics" and ""SCR harmonic correction topologies for VSI drives", I would like to grant permission to Mr. Rajat Bhargava to include these papers in his M.Sc thesis entitled "Simulation Models for Variable Speed Electric Drives".

Mr. Emanuel Bocancea

Em /to carcoa

#### **ABSTRACT**

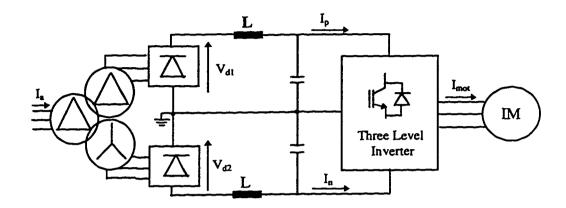

This thesis describes simulation models for assessing the performance of variable speed power electronic drive systems. Simulation models are developed for both the Voltage Source Inverter (VSI) and the Current Source Inverter (CSI) using SPICE3. A simulation model for a complete drive system is presented for a VSI drive system using a 12-pulse input rectifier and a 3-level Pulse width modulation (PWM) VSI.

Models are described for simulating the action of the input, output and load portions of both the CSI and VSI drive types. The drive systems are discussed with reference to both 6-pulse and 12-pulse rectifier stages. The 12-pulse rectifier input stage uses a  $\Delta - \Delta / \Delta - Y$  transformer. The modeling of a  $\Delta - \Delta / \Delta - Y$  transformer is done using d-q axis theory. DC Filters are used to obtain a ripple free dc voltage or current, which acts as the input to the inverter stage. Pulse width modulation (PWM) is used to control the inverter output stage of both drive systems. The induction motor acts as the load to the inverter output stage and is also modeled using d-q axis theory. Experimental results are used to verify that the simulation models are accurate and represent the real system. The simulation models are constructed using actual drive parameters obtained by performing various experimental tests. The performance of a low distortion rectifier is investigated using both simulation and experimental data, with emphasis on the current harmonics, the power factor and the total harmonic distortion. The result of this performance analysis shows that the novel rectifier topology can be used to successfully lower the total harmonic distortion of the rectifier input line current whilst achieving a unity power factor.

The various simulation techniques developed in this work are implemented using SPICE3 and lower the difficulty of simulating an entire drive topology. Fast run times are obtained as a result and convergence problems are improved. Close agreement of the simulation results with experimental ones prove the accuracy of the SPICE3 models.

### Acknowledgment

I would like to extend my special thanks to:

- the Department of Electrical and Computer Engineering for their financial and technical assistance.

- my colleague, Emanuel Bocancea for being a great coworker.

- Srinivas Padmanabhuni and Ram Maikala for their timely help.

- Shilpee for being with me when I need her most

- and most of all my supervisor, Dr. John C. Salmon for his valuable advice and encouragement throughout my work.

# TABLE OF CONTENTS

| List | of | Figures |

|------|----|---------|

| List | of | Symbols |

| Chapter 1: Introduction |                                                                           |  |

|-------------------------|---------------------------------------------------------------------------|--|

| 1.1                     | Drive topologies                                                          |  |

| 1.2                     | Simulation and Experimental results3                                      |  |

| 1.3                     | Literature Survey                                                         |  |

| 1.4                     | Organization of the Thesis                                                |  |

| Chapter 2               | : Introduction to SPICE3 simulation                                       |  |

| 2.1                     | The SPICE3 Simulator                                                      |  |

| 2.2                     | Format of Circuit Files                                                   |  |

| 2.3                     | SPICE for power electronics circuit simulation                            |  |

| 2.4                     | Troubleshooting                                                           |  |

|                         |                                                                           |  |

| Chapter 3               | : Diode Bridge Rectifier                                                  |  |

| 3.1                     | Six-pulse diode bridge rectifier                                          |  |

|                         | 3.1.1 Simulation of 6-pulse diode bridge rectifier                        |  |

|                         | 3.1.2 C dc-link filter                                                    |  |

|                         | 3.1.3 Waveforms and analysis for C filter                                 |  |

|                         | 3.1.4 Harmonic analysis for C-filter                                      |  |

|                         | 3.1.5 LC dc-link filter                                                   |  |

|                         | 3.1.6 Waveforms and analysis for LC-filter                                |  |

|                         | 3.1.7 Harmonic analysis for LC-filter                                     |  |

| 3.2                     | Twelve-pulse diode bridge rectifier                                       |  |

|                         | 3.2.1 d-q Axis Theory model for $\Delta$ - $\Delta/\Delta$ -Y transformer |  |

|                         | 3.2.2 SPICE3 model for $\Delta$ - $\Delta$ / $\Delta$ -Y transformer      |  |

|                         | 3.2.3 SPICE3 model for 12-pulse rectifier                                 |  |

|                         | 3.2.4 Waveforms and analysis for 12-pulse rectifier                       |  |

| 3.2.5 Harmonic analysis for 12-pulse rectifier        |

|-------------------------------------------------------|

|                                                       |

| Chapter 4 : Voltage Source Inverter                   |

| 4.1 6-pulse, 2-level Square Wave Inverter             |

| 4.1.1 SPICE simulation                                |

| 4.1.2 Waveform and analysis                           |

| 4.2 Pulse Width Modulated Voltage Source Inverter     |

| 4.2.1 Simulation of PWM VSI                           |

| 4.2.2 Waveforms and analysis of PWM VSI               |

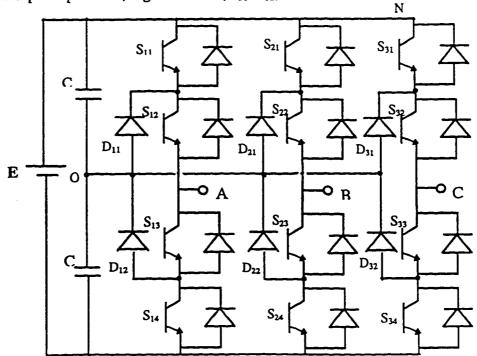

| 4.3 Three-level PWM inverter                          |

| 4.3.1 Simulation of Three-level PWM inverter          |

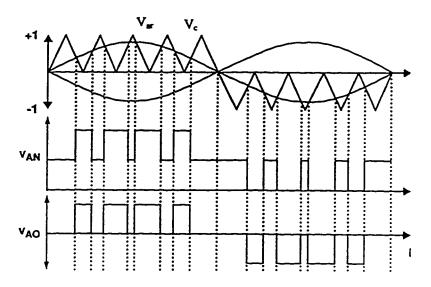

| 4.3.2 Waveform and analysis of 3-level PWM inverter51 |

|                                                       |

| Chapter 5 : Current Source Inverter                   |

| 5.1 6-pulse, 2-level PWM Current Source Inverter      |

| 5.1.1 SPICE3 Simulation                               |

| 5.1.2 Waveform and analysis                           |

| 5.1.3 Harmonic analysis                               |

| 5.2 Controlled Current Source for a CSI               |

|                                                       |

| Chapter 6: Induction Motor                            |

| 6.1 Induction motor drive                             |

| 6.1.1 Induction motor modeling                        |

| 6.1.2 SPICE3 simulation                               |

| 6.1.3 Waveforms and analysis                          |

| 6.2 Constant voltage/frequency operation              |

| 6.2.1 SPICE3 simulation of constant V/ f operation    |

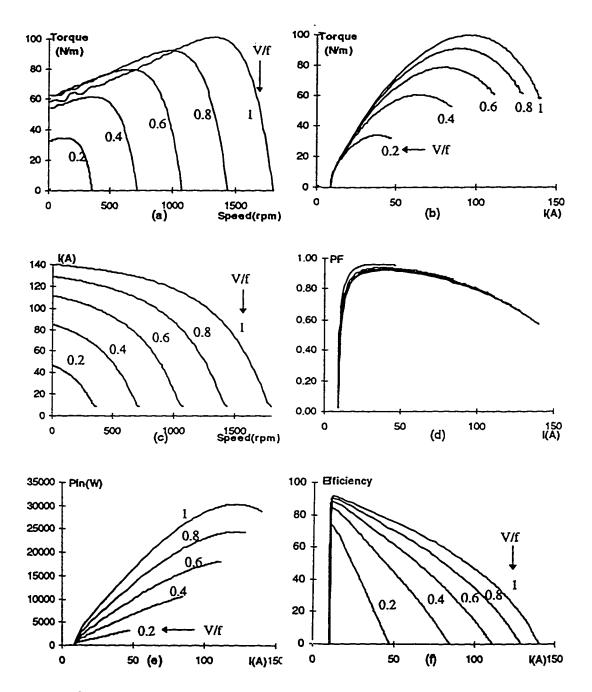

| 622 Analysis of constant Wf operation cursus 69       |

| Chapter 7: Variable S   | peed Drive72                                       |

|-------------------------|----------------------------------------------------|

| 7.1 Selecting driv      | ve components                                      |

| 7.2 VSI and CSI         | Drive Topologies                                   |

| 7.3 12-pulse, 3-le      | vel PWM VSI Drive                                  |

| 7.3.1 SPICE3            | Simulation                                         |

| 7.3.2 Wavefo            | orm and analysis                                   |

| 7.4 VSI and CSI         | Drives                                             |

| Chapter 8 : Novel Recti | fier Topology                                      |

| 8.1 Current harmo       | onics and power factor                             |

| 8.2 Rectifier topo      | ology 86                                           |

| 8.2.1 Simulat           | tion of Rectifier topology                         |

| 8.2.2 Wavefo            | orm and analysis                                   |

| 8.2.3 Simulat           | tion tools used for circuit Performance Analysis92 |

| 8.2.4 Perform           | nance Analysis and Design                          |

| Chapter 9: Conclusion   | 1                                                  |

| 9.1 SPICE3 simu         | lation                                             |

| 9.2 Drive Topolo        | egy                                                |

| 9.3 Novel Rectifi       | ier Topology 104                                   |

| 9.4 Suggestions for     | or future work                                     |

| Bibliography            |                                                    |

| Appendix                |                                                    |

| A Harmonic analy        | ysis data for 6-pulse diode bridge rectifier       |

| B Test data for Δ-      | Δ / Δ-Y transformer parameters                     |

| C Harmonic analy        | vsis data for 12-pulse diode bridge rectifier      |

| D Test data for Induction Motor parameters                           |  |

|----------------------------------------------------------------------|--|

| E Harmonic analysis for inverters                                    |  |

| F Harmonic analysis data for resonant network rectifier topology 117 |  |

| G SPICE3 Netlist files                                               |  |

| H Conference papers (CCECE'96, Calgary)                              |  |

# LIST OF FIGURES

| 1.1  | Block Diagram of Voltage Source Inverter Drive                                                | . 2  |

|------|-----------------------------------------------------------------------------------------------|------|

| 1.2  | Block Diagram of Current Source Inverter Drive                                                | .3   |

|      |                                                                                               |      |

|      | SPICE3 simulator performance curve                                                            |      |

| 2.2  | Circuit Diagram for a half wave diode rectifier                                               | .13  |

| 2.3  | SPICE3 schematic for a half wave diode rectifier                                              | .13  |

| 3.1  | Three-phase diode bridge rectifier circuit                                                    | 20   |

| 3.2  | SPICE3 model for 6-pulse rectifier bridge with C filter                                       | 21   |

| 3.3  | Simulated and experimental waveforms for 6-pulse rectifier with C-                            |      |

|      | filter                                                                                        | . 23 |

| 3.4  | Simulated and experimental waveforms for 6-pulse rectifier with LC-                           |      |

| f    | iilter                                                                                        | 25   |

| 3.5  | Block Diagram for 12-pulse diode bridge rectifier                                             | 26   |

| 3.6  | Phasor diagram for d-q transformation for $\Delta$ - $\Delta$ transformer                     | . 28 |

| 3.7  | Phasor diagram for d-q transformation of the $\Delta$ -Y transformer                          | . 29 |

| 3.8  | d-q axis theory transformer model                                                             | 30   |

| 3.9  | SPICE3 model for the 12-pulse rectifier                                                       | 31   |

| 3.10 | ) Waveforms for Δ-Δ / Δ-Y transformer                                                         | 32   |

| 3.1  | I Simulated and experimental line current waveforms for the $\Delta$ - $\Delta$ / $\Delta$ -Y |      |

|      | transformer                                                                                   | .33  |

| 3.12 | 2 Simulated and experimental output voltage waveforms for the 12-                             |      |

|      | pulse rectifier                                                                               | 35   |

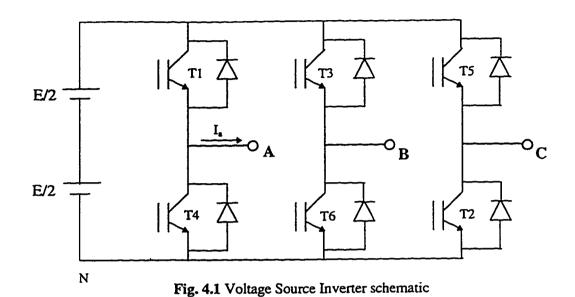

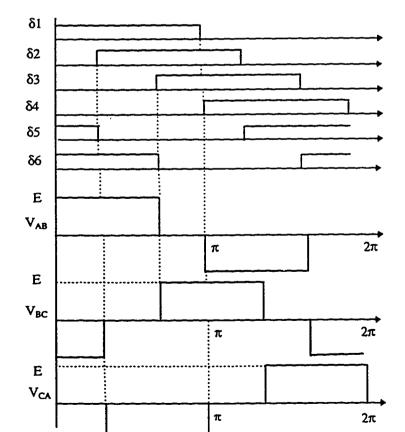

| 4.1  | Voltage Source Inverter schematic                                                             | . 37 |

| 4.2 SPICE3 model for square wave voltage source inverter                |

|-------------------------------------------------------------------------|

| 4.3 Simulated and experimental waveforms for square wave VSI            |

| 4.4 Three phase PWM waveforms                                           |

| 4.5 SPICE3 model for PWM VSI                                            |

| 4.6 PWM Sinewave generation                                             |

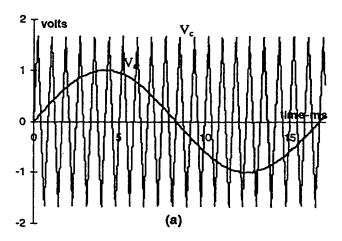

| 4.7 Simulated ref. sine wave and triangular carrier wave for PWM VSI 47 |

| 4.8 Simulated and experimental waveforms for PWM VSI 48                 |

| 4.9 Circuit for a 3-level PWM Inverter                                  |

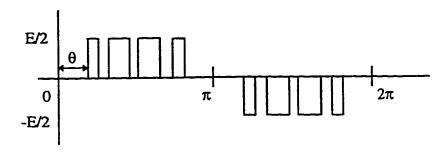

| 4.10 PWM waveform for 3-level VSI                                       |

| 4.11 Typical output waveforms for 3-level inverter                      |

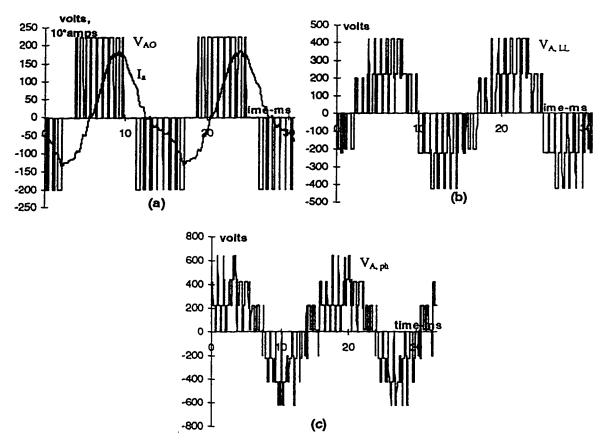

| 4.12 Simulated waveforms for 3-level PWM inverter                       |

|                                                                         |

| 5.1 Circuit diagram for Current Source Inverter                         |

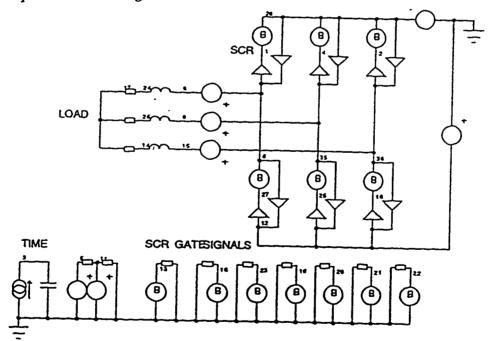

| 5.2 SPICE3 model for PWM CSI                                            |

| 5.3 Switching pattern generation for CSI over half carrier cycle 56     |

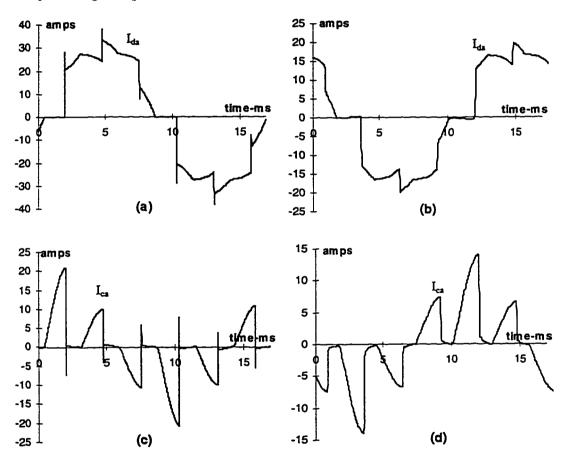

| 5.4 Simulated waveforms for CSI PWM                                     |

| 5.5 Block diagram for control scheme of the current source              |

|                                                                         |

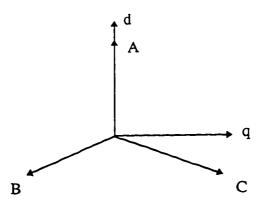

| 6.1 Stationery A-B-C to d-q axes transformation 61                      |

| 6.2 d-q Equivalent Circuits                                             |

| 6.3 Per-phase equivalent circuit for Induction Motor 64                 |

| 6.4 SPICE3 model for induction motor 64                                 |

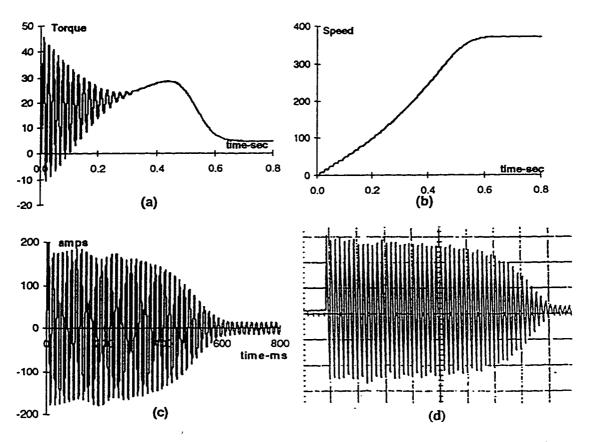

| 6.5 Simulation waveforms for Induction Motor                            |

| 6.6 Constant volts per hertz curves for Induction Machine               |

|                                                                         |

| 7.1 Simplified circuit of a motor drive                                 |

| 7.2 Block diagram for 12-pulse, 3-level PWM VSI Inverter Drive          |

| 7.3 Switching logic for dc-link current                                 |

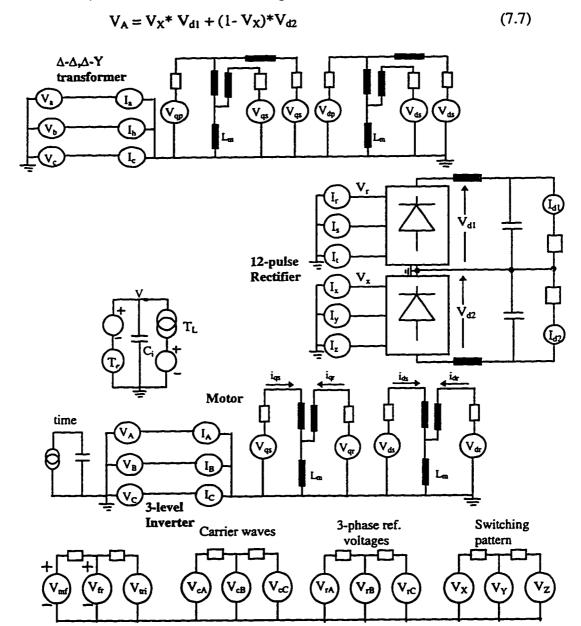

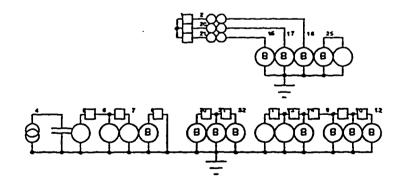

| 7.4 SPICE3 model for the 12-pulse, 3-level PWM VSI drive                |

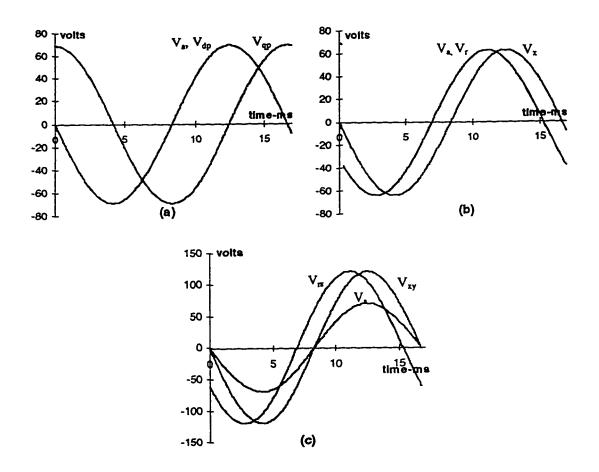

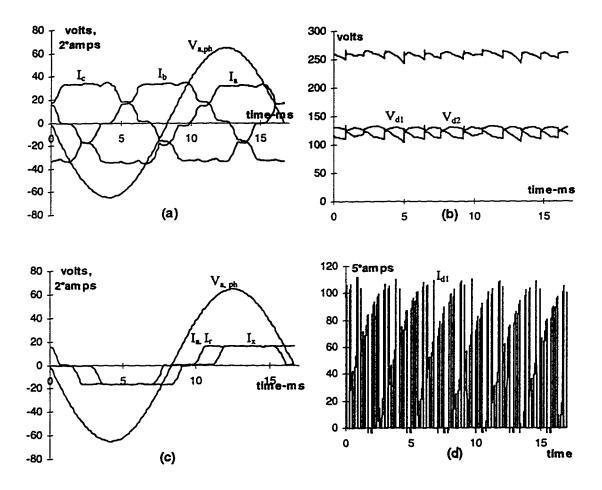

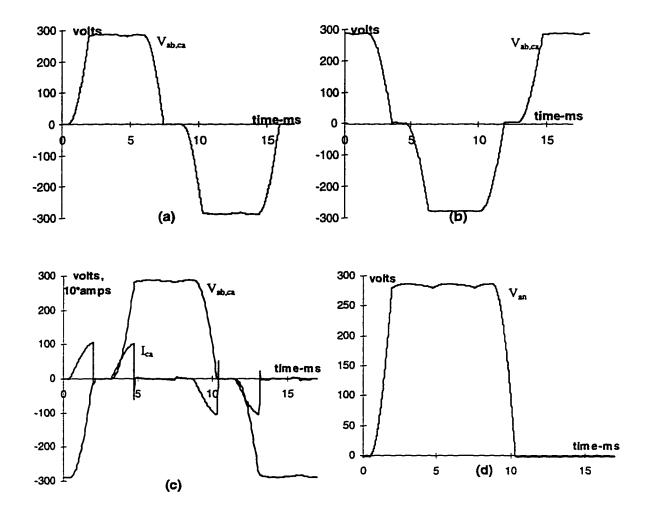

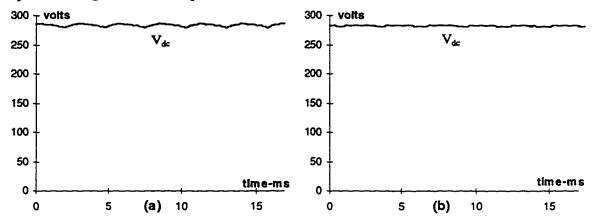

| 7.5 Simulated waveforms for 12-pulse, 3-level PWM Inverter drive 79                                 |

|-----------------------------------------------------------------------------------------------------|

| 7.6 Simulated waveforms for 12-pulse, 3-level PWM Inverter drive 80                                 |

| 7.7 Simulated switching pattern waveforms                                                           |

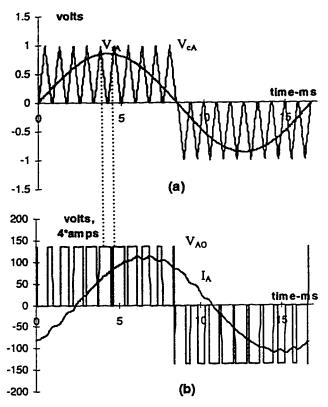

| 7.8 Simulated waveforms for 12-pulse, 3-level PWM Inverter drive 82                                 |

| 7.9 Simulated waveforms for constant volts per hertz operation of 12-                               |

| pulse, 3-level PWM Inverter drive                                                                   |

|                                                                                                     |

|                                                                                                     |

| 8.1 Utility Interface                                                                               |

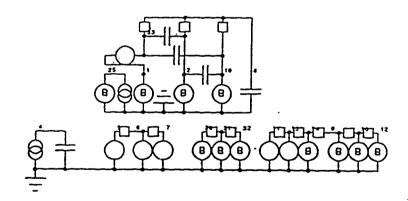

| 8.2 Resonant mode harmonic correction circuit for a 3-φ diode bridge86                              |

| 8.3 12-pulse rectifier with a resonant-mode harmonic correction topology87                          |

| 8.4 SPICE3 model for 12-pulse rectifier with resonant mode harmonic                                 |

| correction circuit                                                                                  |

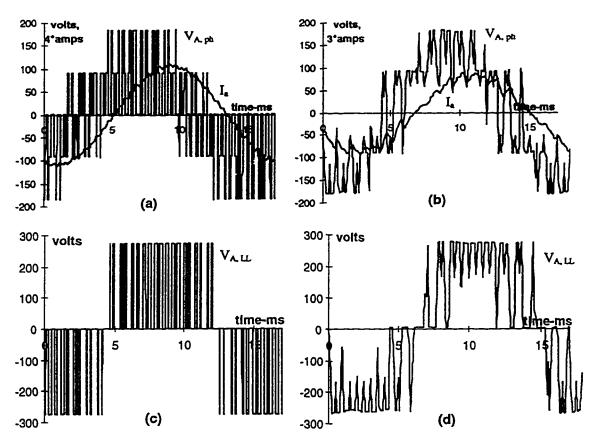

| 8.5 Waveforms for phase voltage (V <sub>ph</sub> ) and line current (I <sub>a</sub> ) for a 6-pulse |

| rectifier bridge with resonant network                                                              |

| 8.6 Simulated and experimental waveforms for 3-phase diode bridge with                              |

| resonant network90                                                                                  |

| 8.7 Waveforms for the resonant capacitors                                                           |

| 8.8 Waveforms for the 6-pulse output rectifier voltage                                              |

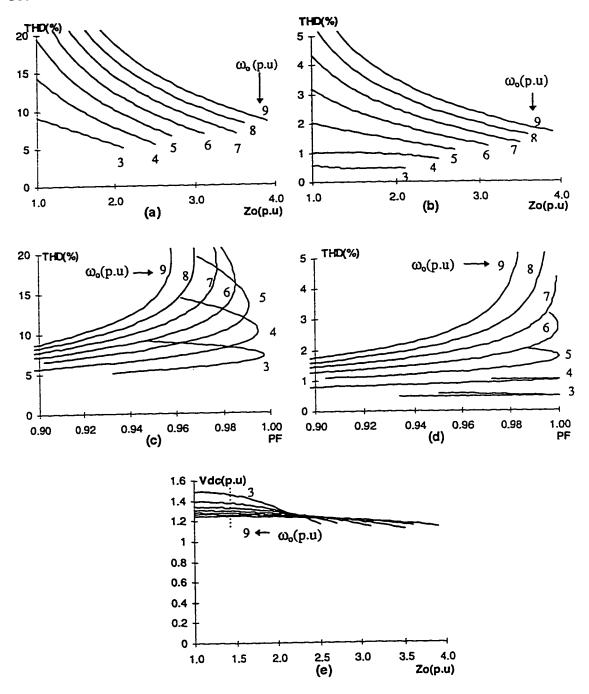

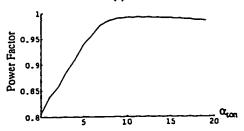

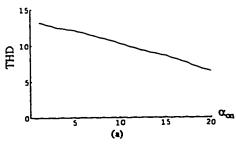

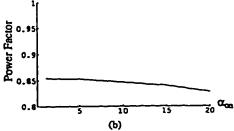

| 8.9 6-pulse and 12-pulse rectifier performance curves keeping ω <sub>o</sub> constant               |

| and varying Z <sub>0</sub> 95                                                                       |

| 8.10 6-pulse and 12-pulse rectifier performance curves keeping ω <sub>o</sub> constant              |

| and varying Z <sub>0</sub> 96                                                                       |

| 8.11 6-pulse and 12-pulse rectifier performance curves keeping Z <sub>0</sub> constant              |

| and varying $\omega_{\circ}$                                                                        |

| 8.12 6-pulse and 12-pulse rectifier performance curves keeping Z <sub>0</sub> constant              |

| and varying $\omega_0$                                                                              |

#### LIST OF SYMBOLS

SPICE Simulation Program with Integrated Circuit Emphasis

ac alternate current

VSI Voltage Source Inverter

CSI Current Source Inverter

PWM Pulse Width Modulation

DPF Displacement Power factor

THD Total Harmonic Distortion

CDF Current Distortion Factor

PF Power Factor

A Nodal admittance matrix

RELTOL Relative Tolerance

ABSTOL Absolute Tolerance

I. Phase A Current

L<sub>m</sub> Magnetizing inductance

L<sub>is</sub> Stator inductance

V<sub>a, ph</sub> Phase A Voltage

LABVIEW Laboratory Virtual Instrument Engineering Workbench

GPIB General Purpose Interface Bus

d-axis direct axis

q-axis quadrature axis

SCR Silicon Controlled Rectifier

kVA Kilovolt Amperes

GTO Gate Turn-off Thyristor

NPC Neutral Point Clamped

IM Induction Motor

ω angular frequency

I<sub>d</sub> dc-link current

V/f volts per hertz

$\psi$  induction motor flux linkage

T<sub>e</sub> electromagnetic torque

T<sub>L</sub> load torque

$\phi_{ag}$  air-gap flux

f<sub>sl</sub> slip frequency

L<sub>s</sub> source inductance

PCC Point of Common Coupling

I<sub>1</sub> fundamental current

φ phase angle

I<sub>ca</sub> Phase A capacitor current

# Chapter 1

### INTRODUCTION

The ac variable speed drive is a complex non-linear system. The computer simulation and modeling becomes essential for the analysis and design of such a system. SPICE3, which is the simulation software used in this work, has now become a widely accepted circuit simulation package for Power Electronic circuits. To develop a model for an electric drive system in SPICE3 is to widen its capabilities by simulating the whole drive system in only one simulation. This avoids complex mathematical operations for its performance analysis, making drive design more straightforward and practical.

Computer aided circuit simulation of power electronic systems offer the system designer the opportunity to explore all the various design trade-off and options and also to perform wide-ranging comparative investigation, optimization and performance analysis.

#### 1.1 Drive Topologies

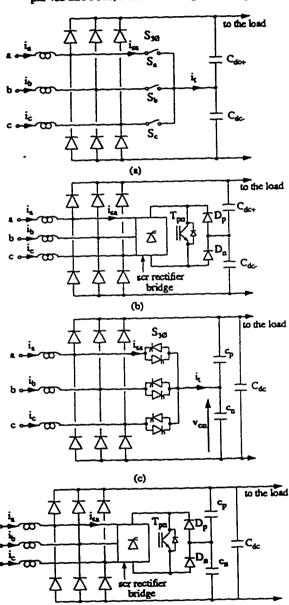

This work discusses two basic drive topologies - the Voltage Source Inverter [1]-[3] and the Current Source Inverter [4], [5]. These two drives are the most common drives used in the industry. Simulation models for these drives facilitates the comparative analysis and design of new drive topologies.

The rectifier stage of a drive is commonly either a 6-pulse diode bridge rectifier or a 12-pulse diode bridge rectifier [6], [7]. For the 12-pulse rectifier the input stage is a  $\Delta$ - $\Delta$ ,  $\Delta$ -Y transformer with the output voltages of the transformer phase shifted by 30° from each other. The series connection of two 6-pulse diode bridge rectifier connected to such a transformer gives a 12-pulse operation which is applicable for high power applications.

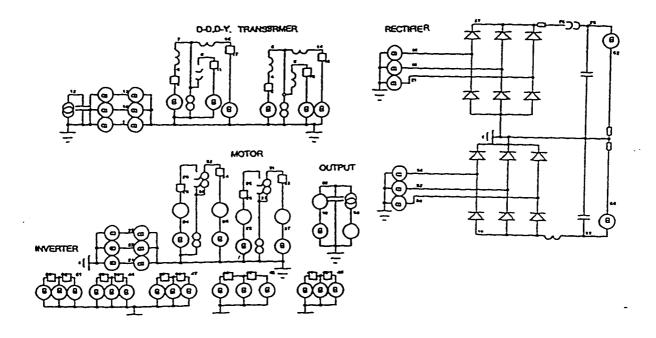

The dc-link filter stage is a large capacitor for the VSI so that the input to the

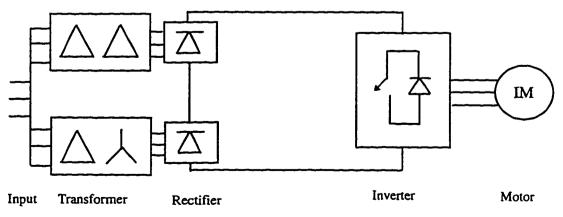

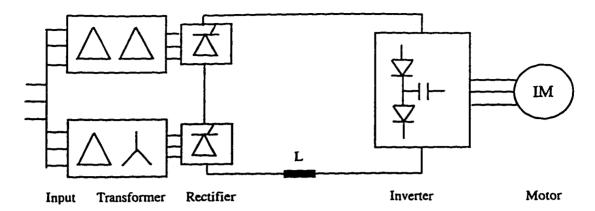

inverter is an approximately constant dc voltage. The voltage source inverter can be either a square wave inverter or a pulsewidth modulated (PWM) inverter. The rectifier stage to the square wave inverter is a phase controlled rectifier to control the input dc voltage. The PWM inverter has the provision of control of the output voltage and hence can be supplied from a fixed dc voltage, see Fig.1.1. The PWM VSI inverter uses high switching frequency to eliminate the dominant harmonics in the output line-to-line voltage. The simulation of such high frequency operation makes analysis simpler.

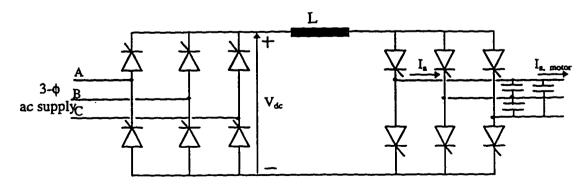

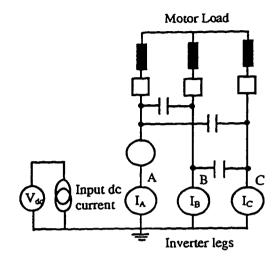

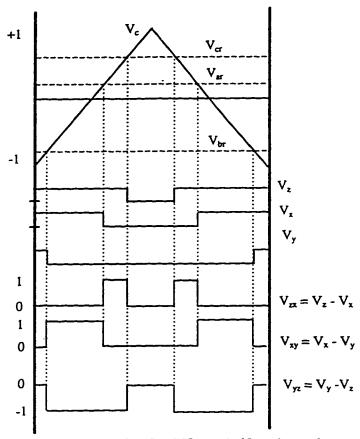

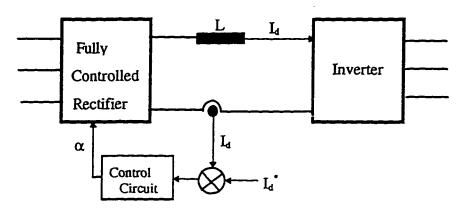

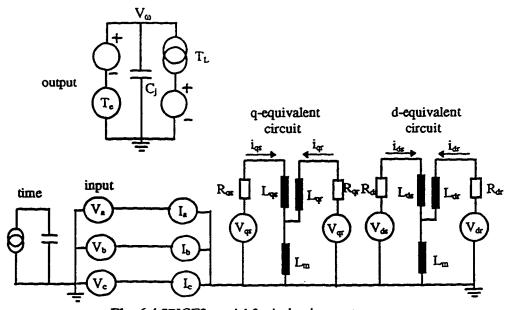

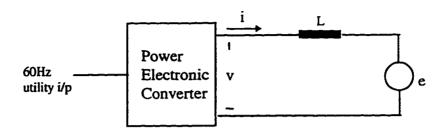

The dc-link filter for a CSI drive is a large inductor in the dc rail which results in a stiff dc current being fed to the inverter, see Fig.1.2. Current fed into the inverter is converted into three ac line currents by the appropriate PWM gating pattern of the inverter switches see section 5.1.1. Current harmonics are absorbed by the output filter so as to provide sinusoidal load current and voltage. A generalized structure of a simple controller for a current source inverter is also explained.

The output of a drive topology is the induction motor. For the control of induction motors, a fixed frequency ac supply with variable voltage or a variable frequency ac supply with variable voltage or current is required. Variable speed drives utilizing an ac motor fed with variable frequency, three-phase ac derived from an inverter, are encountered with increasing frequency [4]. A simulation model for the induction motor helps to examine both the transient and steady state.

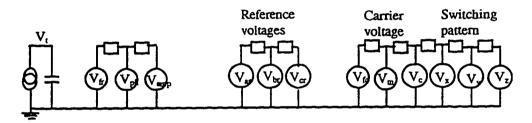

Fig. 1.1 Block diagram for PWM VSI Inverter Drive

Fig. 1.2 Block diagram for PWM CSI Inverter Drive

# 1.2 SPICE3 simulation and experimental results

SPICE is a standard circuit simulator program used by the electronic industry. This program uses non-linear physical models to simulate semiconductor components. In power electronics these micromodels are useful at the switch level of simulation wherein the commutating performance of the power switch in the circuit is of main interest. Because, at this level events occur in a very short time interval as compared with the total on or off state of the device, decoupling is usually possible. This decoupling allows a local simulation of the switches [2].

The simulation software used in this work is SPICE3 (Version 3f4). The simulator is equipped with a schematic capture input program and postprocessor for waveform analysis. The previous versions of SPICE primarily used the voltage controlled and current controlled switch for modeling and simulation [48]. In most of the models the total system ends up having a large number of switches, thus requiring larger amount of memory and long computation times. In the latest version of SPICE3 (version 3f4), the "B" and "U" statements introduced can be used to more effectively model switches and control circuit transfer functions used in power electronic drive systems. These B-statement and U-statement can be used as voltage function and current functions defining various complex equations. Thus, the flexibility and capability of SPICE as a stand alone program can be enhanced while significantly reducing run times.

The new features of SPICE3 are used very effectively for the simulation of various power electronic circuits [9]. The modeling of the  $\Delta$ - $\Delta$ ,  $\Delta$ -Y transformer is done using d-q axis theory. In this theory the time varying parameters are eliminated and the variables and parameters are expressed in orthogonal or mutually decoupled direct (d) and quadrature (q) axes. The B-statement is used to model the complex equations resulting from the transformation. The modeling of the induction machine is also done in the same manner using d-q axis theory.

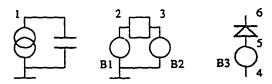

The diode rectifier topology uses the simple power diode from the SPICE3 device library. For better accuracy, such as for the simulation of the novel rectifier topology the device parameters can be altered. The switching device in the case of a square wave inverter is modeled by using a B-statement in series with a diode.

SPICE3 becomes very effective when modeling the inverter topology. At high switching frequency operations, as in the case of PWM inverters simulation has convergence problems due to fast transfer of current from one switching device to the other. The B-statement solves this problem by modeling the inverter legs by three B-statements representing the switching pattern of the six devices. This also reduces the number of switching devices.

In the present work, SPICE3 is used for generating the raw data for all the simulated waveforms and the raw data is postprocessed using Excel to obtain the waveform plots. Harmonic analysis is also done using SPICE3. In addition, SPICE3 is provided with the Interactive Interpreter that helps to monitor parameters in a single run by means of a do loop. This feature is used to generate the data for the various performance curves for the novel rectifier topology.

All the parameters values used in the SPICE3 model are the same as that used in the experimental setup. For the  $\Delta$ - $\Delta$ ,  $\Delta$ -Y transformer, the Open Circuit test and the Short Circuit test is done to determine the parameter values. Similarly, for the induction motor the Load test , the Standstill test and the Stator dc test is done. This helps in a logical comparison of the simulation and experimental results.

The data used for the experimental waveforms was generated using a data acquisition system called LABVIEW - Laboratory Virtual Instrument Engineering Workbench. The experimental measurement system consists of the following: Tektronix TDS 420 four channel oscilloscope, Power Macintosh 7100/66 computer running LABVIEW 4.0 software, GPIB card NI-488, GPIB cable, high voltage probe isolators with scaling factor of 1/500 and 1/50, clamp-on Hall-effect current probe isolator with scaling factor of 100mV/A and 10mV/A.

#### 1.3 Literature Survey

Numerous digital and analogue computer simulation studies of the performance of electrical drives have been done in the past [10]-[14]. However, because of the complexity of power electronic circuits, the vast majority of these studies have neglected the power-electronic circuit topology and assumed a zero impedance source, with the power electronic switching action represented solely by the theoretical voltages (currents) supplied to the drive motor.

Digital computer simulation studies [15],[16] which have attempted to take into account the power-electronic circuits and source impedance effects, for example input rectifier, dc link filter, inverter, etc. have all involved significant simplifying assumptions and therefore provides a very limited, albeit useful first approximation to the various interactions.

The power and flexibility of power electronic circuit simulation depends heavily on the CAD package library of power electronic devices and components available to the user. To specialize these CAD packages for PWM inverter drive system requires an additional range of library models to represent devices, components, machines and processes specific to power electronic systems to be developed [17], [18].

A PC based simulation CAD tool, PECADS is proposed in [19]. It uses real structure simulation (RSS) and digital identification for power electronic computer aided design and simulation. The simulation package follows the RSS rule that each

block has to be simulated in such a manner that the output signals will represent the same evolution as the real ones.

Another power electronic CAD package has been proposed in [19] which has been specially designed to cater for the simulation of pulse-width modulation controlled power electronic systems. This CAD package combines the features and facilities of a previously developed PWM generation and analysis package called PWLIB [20] with a circuit analysis package called BTRAP. The "equivalent-circuit" electromechanical induction motor model, which, when incorporated into the PWLIB/BTRAP package, provides the CAD facilities for developing various integrated drive systems.

A flexible method to design a complete three-phase inverter drive is to use a circuit simulator like SABER, but a serious problem is that designing a complete three-phase inverter, especially operating at low fundamental frequency and higher switching frequency, will take many hours to do, and if parameters like gate resistance, gate-drive supply and load currents are varied, optimized design is almost impossible. Among the important power electronic devices, the power diode model has been improved in [21] and the IGBT model is developed in [22]. Both component models are based on the SABER simulator. In [23], corresponding models are implemented in SPICE. Practical implementation of a proposed model of a power diode is suggested in [24] using both SPICE and SABER.

The functional definition of a switching converter is used to model three-phase VSI or CSI using PSpice [11]. Simplified device models using controlled sources have been proposed to speed up the simulation. For further simplification, each converter is simulated as a multiport network, wherein the time solution of the currents and voltages, in the input and output terminal, constitute the main objective of the analysis.

A considerable attention has been directed towards enhancing the performance of power converters. Multilevel waveforms are used to reduce the harmonic distortion and increase the power rating of high-performance inverter power supplies [25]. There has been great interest in the neutral point clamped pulse-width modulated (NPC-PWM) inverters drives. The NPC inverter's output voltage may contain fewer

harmonics than that of a conventional full bridge inverter [2] and since the imposed source voltages across the main switching devices are halve the dc source voltage it is particularly attractive in high power applications.

So far, several control schemes for NPC three-level inverters have been proposed. Reported switching pattern based on selective harmonic elimination [2], [26] did not consider the variations of the neutral point potential which is an inherent problem of NPC inverters as pointed out in [27]. Vector control schemes which consider the neutral voltage balance have been reported [28].

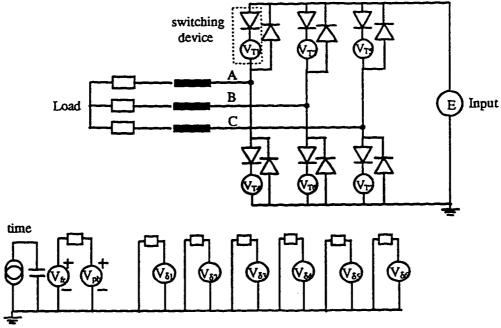

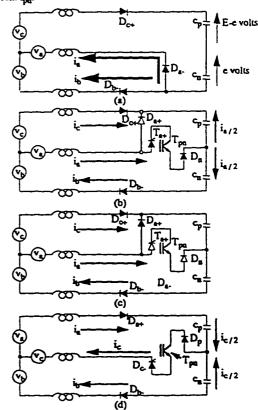

The novel rectifier topology examined in this work is an improvement upon the 3-phase Y-switch networks explored in recent articles [29],[30] with the prime application being the input stage to commercial variable speed drives. The converter topologies examined in [29] are essentially SCR harmonic correction units (HCUs) suitable as a retrofit or as a drive option. The work describes a series of techniques using thyristor switches that improve the harmonic content of diode rectifiers connected to a voltage source inverter drive.

A new active interphase reactor for 12-pulse diode rectifier is proposed in [31]. It uses a conventional 12-pulse diode rectifier which requires an interphase reactor to ensure the independent operation of the two parallel-connected three-phase diode bridge rectifiers. In this scheme, a low kVA (0.02 p.u) active current source injects a triangular current into an interphase reactor of a 12-pulse diode rectifier. The proposed system draws near sinusoidal current from the utility with less than 1% THD.

The concept of reducing harmonic distortion associated with rectifier circuits by third harmonic current injection has been reported in [32]-[34]. All the above schemes require a controllable line synchronized external third harmonic current source. Scheme [34] necessitates the use of an input isolation transformer along with the access to its neutral terminal. [32] uses tuned L-C branches in a network that injects total third-harmonic modulated current into the ac terminals of the rectifier. A modification of the scheme uses a magnetic device for current injection in a 3-phase, sinusoidal-current utility interface.

modification of the scheme uses a magnetic device for current injection in a 3-phase, sinusoidal-current utility interface.

#### 1.4 Organization of the Thesis

The thesis begins with an introduction to the SPICE software with emphasis to the latest version of SPICE3. SPICE3 has been very useful for the simulation of power electronic circuits. The introduction of the B-statement and U-statement facilitates the simulation of various complex circuitry. An overview of the SPICE simulator is discussed which is important in solving various problems during simulation.

The rectifier stages of the drive topology are then described. The 6-pulse diode bridge is discussed with emphasis to the performance with a C dc-link filter and LC dc-link filter. Two series connected 6-pulse diode bridge rectifiers give a 12-pulse operation that is very useful for high power applications. The input stage to the 12-pulse rectifier is a  $\Delta$ - $\Delta$ ,  $\Delta$ -Y transformer with their output voltages phase shifted at 30° from each other. The modeling of the  $\Delta$ - $\Delta$ ,  $\Delta$ -Y transformer is done using d-q axis theory. The use of B-statements help to simulate the transformer model very easily by decoupling the input of the rectifier from its output. The comparison of simulation results with experimental ones agree very closely.

The inverter stage can either be a Voltage Source Inverter (VSI) or a Current Source Inverter (CSI) [4], [36]. Both the square wave VSI and the pulsewidth modulated VSI is discussed. The PWM VSI inverter combines both voltage and frequency control within itself and the high switching operation eliminates the voltage harmonics from the output [37]. The inverter leg is modeled using three B-statements that represent the switching function of the six switching devices. A generalized structure of a three-level voltage source inverter is presented with its simulation waveforms. Comparison of the simulated and experimental results for the waveforms and the harmonic analysis of the output voltage are presented for each of the VSI.

The Current Source Inverter is discussed next. A variable dc link voltage is generated by phase control, which is converted to current source by connecting a

series inductance. The CSI is modeled in much the same way as the VSI with three B functions generating the PWM switching pattern. Capacitors are connected at the output of the inverter to absorb high frequency harmonics associated with the PWM inverter output current. The CSI is also viewed with reference to a constant current source inverter where the dc current fed to the inverter is kept constant using a closed loop scheme.

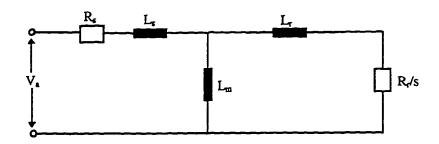

The output stage of the drive is the Induction Motor which is described next. The motor is modeled using d-q axis theory. The elimination of the time-varying components in the d-q axis theory, helps to model the motor easily using voltage functions. The simulation waveforms for the direct-on-line starting of the motor is presented. The operation of the induction motor with constant V/f is explained and various curves are obtained using SPICE3 simulation.

The general features of the variable speed drives with emphasis to the PWM inverter drives summarizes the various stages of the drive topology. A 12-pulse, 3-level PWM voltage source inverter is simulated in one single drive structure to demonstrate the capability and flexibility of SPICE3 for complex circuit simulation.

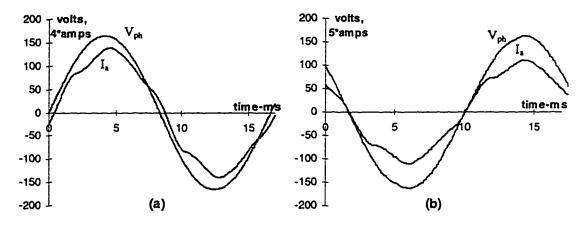

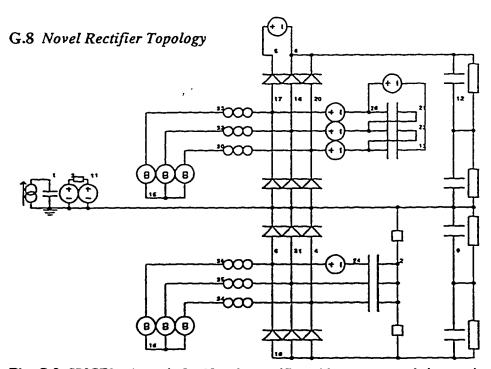

The thesis concludes by examining a novel rectifier topology that draws a line current with low total harmonic distortion at unity power factor. A resonant network is used to build up a current prior to the natural conduction of the diodes thus helping in waveshaping the line current. SPICE3 simulation waveforms are used to compare with the experimental results. The interactive interpreter, which is a new feature in SPICE3 is used to generate data for the performance analysis of the rectifier topology. The analysis and design of a new rectifier topology with the help of SPICE3 simulation tools is well established.

# Chapter 2

### INTRODUCTION TO SPICE SIMULATION

Circuit simulation is becoming an indispensable tool for circuit design in power electronic drive systems. Numerical analysis of electrical circuits appeal to the circuit designer as an alternative to tedious hand calculations. This concept facilitates the augmenting or supplanting the laboratory testing in general. This chapter introduces the SPICE3 simulator and explains the various features of circuit simulation tools. The general format of SPICE is described with emphasis to its use in power electronic applications.

#### 2.1 The SPICE Simulator

SPICE (Simulation Program with Integrated Circuit Emphasis) is a general purpose electronic circuit simulation program. Since its introduction, SPICE has gone through its own evolution. The final upgraded version of SPICE is SPICE3 which was converted from the original FORTRAN program to the C program, though the core algorithm have stayed the same. SPICE3f4 is the latest version in the long line of circuit simulators from University of California, Berkeley, which are generally known under the family name of SPICE. It evolved from the older SPICE2g6 and is gradually replacing the latter as the de facto standard among both academic and industrial SPICE simulators.

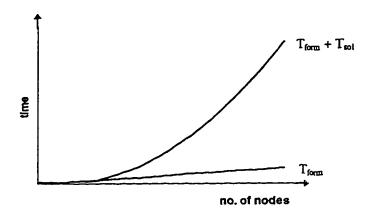

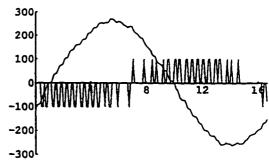

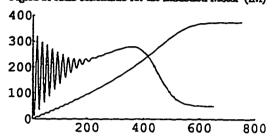

SPICE falls under the category of continuous time simulator. The time for computer solutions as shown in Fig. 2.1 for such simulators consists of two parts

T<sub>form</sub> - time to set up the modified nodal admittance matrix

T<sub>sol</sub> - time to solve the equations

Fig. 2.1 SPICE3 simulator performance curve

The time required to form the matrix is linear with the number of nodes. The time to solve the equations grows as n<sup>3</sup> [38]. In SPICE if a lot of nodes are connected to ground then we get a sparse matrix and a faster solution is obtained using the Sparse Matrix Technique, instead of the usual Gauss Elimination technique. The salient features of the Sparse Matrix Technique are

- Stores only non-zero elements

- Performs operations only on non-zero elements

- Processing order is determined, before the matrix entries are known, to minimize

"fill-ins".

With smaller number of nodes, time to form matrix is much greater than the time for the solution. SPICE primarily uses Nodal Analysis for circuit equation formulation.

Nodal Analysis uses the following methodologies for forming the nodal matrix

- Kirchoff's current law (KCL) this is the starting point

- Kirchoff's voltage law (KVL)

Once the matrix has been formed it proceed to solve the equations thus formed.

For a system of "n" equations,

$$Ax = b$$

the solution methods would be:

#### Matrix inversion

- Cramer's rule

- $x = A^{-1}b$ ,  $n^3$  operations for inversion

#### Gaussian elimination

- forward elimination to form upper triangular system and backward substitution

- $-n^3/3 + n^3 n/3$  operations

#### LU decomposition

- modified form of Gaussian elimination

- reduction of A into L and U

- forward elimination and backward substitution

It can be seen from Fig. 2.1, that the matrix solution time is significantly smaller than the device evaluation time, although the difference decreases as the circuit size increases [38].

#### 2.2 Format of circuit files

A circuit file that is read by the SPICE3 simulator is generated by the schematic capture software. The circuit file can be divided into five parts

- (1) the title describing the type of circuit or any other comment.

- (2) the circuit describing the circuit elements and set of model parameters

- (3) the analysis description which defines the type of analysis

- (4) the output description which defines the way the output is to be presented

- (5) the end of the program

A circuit is described by statements stored in the circuit file. Each statement is self contained and independent of every other statement. Each element in the circuit is connected between nodes that are assigned numbers. Node 0 is predefined as the ground. The first statement of the file is always a comment line. The value of the circuit is written after the nodes to which the element is connected. Models may be used to assign values to the various parameters of the circuit elements. Of the various types of analysis that SPICE offers, the time domain analysis, specified by the .TRAN

statement, is used in the majority of the work. The transient analysis portion of SPICE computes the transients output variables as a function of time over a user-specified time interval. The initial conditions are automatically determined by a dc analysis. All sources which are not time dependent (for example, power supplies) are set to their dc values. The last line of the circuit file terminates with the .END statement.

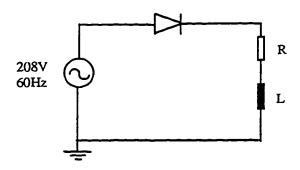

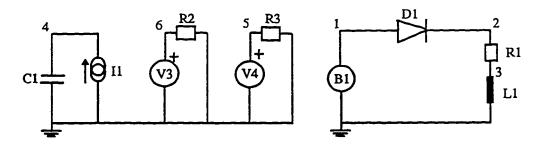

Given below in Fig. 2.2 is the circuit diagram for a simple half wave diode rectifier and Fig. 2.3, is an example of its SPICE3 schematic with its corresponding circuit file.

Fig. 2.2 Circuit diagram for Half wave diode rectifier

Fig. 2.3 SPICE3 schematic for a half wave diode rectifier

half wave diode rectifier

TRAN 20US 116.67MS 100MS 20US UIC

.OPTIONS METHOD=GEAR RELTOL=0.03 ABSTOL=1E-4

.MODEL PD D

R1231K

```

L1 3 0 2.5MH

B1 1 0 V=V(6)*SIN(V(5)*V(4)) * V = V<sub>m</sub>·sin(ω·t)

C1 4 0 1F IC = 0

V3 6 0 DC 294

R2 0 6 1K

I1 0 4 1

V4 5 0 DC 377

R3 0 5 1K

D1 1 2 PD D

.END

```

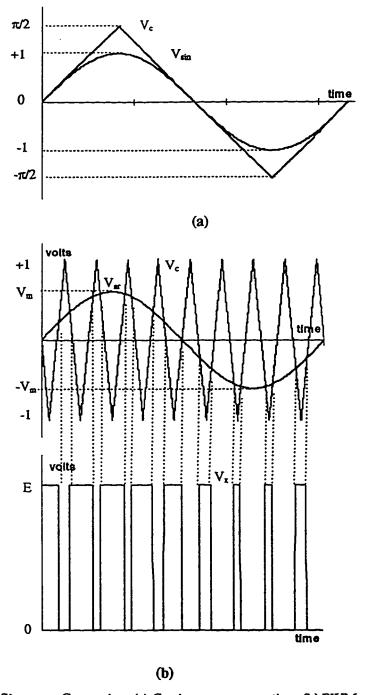

The input sinusoidal voltage to the rectifier is a B-statement which is made to be a voltage function. The amplitude of the sine function is 294V ( $208x\sqrt{2}$ ), modeled as a dc voltage source across nodes 6 and 0. Similarly the frequency of the sine wave is modeled as a dc voltage source of magnitude 60V across nodes 5 and 0 corresponding to a 60Hz frequency. The time in SPICE3 is modeled with a constant current source feeding a capacitor. The capacitor charges and ramps up linearly so that the voltage across the capacitor gives the time reference in the simulation. This kind of a model gives circuit functions access to time as a voltage for e.g. a B-statement and can be very useful for PWM circuits with repeated saw tooth functions.

Two types of numerical integration techniques are available in SPICE3f4: the Trapezoidal method and the Gear method. It has been found that using the Gear method for simulating circuits containing power diode model can reduce convergence problems [38].

#### 2.3 SPICE for power electronics circuit simulation

The switching nature of power electronic devices cause the analysis of power electronic circuits to be very difficult. SPICE simulation provides an easy solution to this. The choice of a circuit model depends upon the objective of the simulation. If the goal is to study a circuit to gain an understanding of the principle of operation,

components should be as elementary as possible. Avoiding the use of actual non-linear relationships for the device hastens the speed of simulation.

The major advantage of using SPICE in power electronics is that with the same software a particular circuit can be analyzed and designed at various system and subsystem levels, i.e. at the level of the power switch or the circuit system as a whole [12]. However, for higher levels of simulation, a much simpler model for the devices is chosen for the circuit implementation to minimize convergence problems and reduce the run times.

Power Electronic circuits are frequently coupled to Drive Systems. A variable speed AC machine connected to the rectifier-inverter system gives rise to complex stability problems. The machine is a non-linear multivariable system and interacts dynamically with the source impedance of the drive. Further complexity may arise when for instance multiple machines are fed by a single inverter or multiple rectifiers feed a single inverter. The analysis of such systems is tedious and computer simulation becomes imperative. The study of new control strategies, the effect of harmonics and the variation of system parameters are also facilitated by simulation results.

The recent updates made to SPICE at University of California, Berkley has made obsolete various simulation techniques often used for power electronic systems [9]. The B-statement and the U-statement introduced in the latest version of SPICE3 i.e. Version 3f4, has simplified the structure of control and switching functions used frequently in Power Electronics. The B-statement can be either a current or voltage function and is used to model various complex circuitry without indulging in the micromodeling and the device characteristics of the switching device. This would prevent long simulation run times and convergence problems. The U-statement is simply a comparison statement that has a value of either 1 or 0 according to its argument. Some of the features of SPICE3 used for power electronic simulation are:

OPTIONS - Various parameters of the simulations available in SPICE3 can be altered to control the accuracy, speed or default values for some devices. These parameters are changed via the .OPTIONS line. ABSTOL and RELTOL are the two most common options used. ABSTOL resets the absolute current error tolerance of the program. RELTOL resets the relative error tolerance of the program.

.TRAN - This dot command performs transient analysis of the circuit. The general form of .TRAN is

#### TRAN TSTEP TSTOP TSTART TMAX UIC

TSTEP is the plotting increment for the output. For use with the post-processor, TSTEP is the suggested computing increment. TSTOP is the final time, and TSTART is the initial time. If TSTART is omitted, it is assumed to be zero. The transient analysis always begins at time zero. TMAX is useful when one wishes to guarantee a computing interval which is smaller than the printer increment, TSTEP. This would also ensure a more accurate numerical integration.

One of the advantages of choosing a small TSTEP is that it increases the resolution of the waveforms obtained from SPICE3 simulation. This feature is made use of in cases where the experimental waveforms have a resolution that is restricted by the resolution of the oscilloscope. This is frequently seen in the simulation waveform of PWM Inverters where high switching frequency is used.

- IC The IC line is for setting the transient initial conditions. When the UIC parameter is specified on the .TRAN line, then the node voltages specified on the .IC control line are used to compute the capacitor, diode and inductor initial condition. Since no dc bias solution is compared before the transient analysis, it is important to specify all dc source voltages on the .IC control line if they are to be used to compute device initial conditions.

- PRINT The Print line helps in generating data for the vectors following the print command. Output variables can be specified for any kind of analysis such as TRAN (for transients analysis) just before the list of vectors.

.PRINT TRAN vector1 vector2 ...

- .FOUR The Four (or Fourier) line controls whether SPICE performs analysis as

a part of the transient analysis. The dc component and the first nine harmonics are

determined.

- .MODEL Some devices that are included in SPICE require many parameter values. Often, many devices in a circuit are defined by the same set of device model parameters. For these reasons, a set of device model parameters is defines on a separate .MODEL line and assigned model name. The device element lines in SPICE then refer to the model name.

In addition, SPICE3 is provided with the Interactive Interpreter that helps to monitor parameters in a single run by means of a do loop. The stand alone program is in the form of a .CONTROL file that uses simple syntax similar to C and the shell script. This feature of SPICE3 has been very useful in the performance analysis of Power Electronic circuits. Some of the features of the interactive interpreter are:

- alias: It creates an alias for a command. It can be used to cause a word to be aliased to text.

- alter: It changes a device or model parameter.

- destroy: It releases the memory holding the data for the specified run.

- echo: It prints out the given text to the screen during the simulation run.

- print: It prints the vectors described by the expression following the print statement. If the col argument is present, it prints the vectors named side by side in column format. If the line argument is given, the vectors are printed horizontally.

#### 2.4 Troubleshooting

The major reason for any SPICE3 simulation to abort is due to convergence problems. Both the DC and transient solutions are obtained by an iterative process which is terminated when both of the following conditions hold:

1) the non-linear branch currents converge to within a tolerance of 0.1% or 1 picoamps, whichever is larger.

2) The node voltages converge to within a tolerance of 0.1% or 1 microvolts, whichever is larger.

The most common reason for failure to converge is simply due to error in specifying circuit connections, element values or model parameters. One characteristic that has been blamed for many SPICE convergence problem is the "floating nodes". These are circuits which have no conductance from the node to any other part of the circuit. This produces a row and column of zeros in the modified nodal analysis matrix, making it impossible to invert in practice.

Another common error is "time step too small". SPICE3 provides an iteration-count system of timestep control. If convergence is not obtained within a maximum number of iterations, the solution is abandoned, the timestep cut by a factor of eight, and the new smaller step is attempted. If the convergence is obtained in fewer than a minimum number of iterations, the timepoint is accepted and the timestep may be doubled before attempting the next step. This technique relies very heavily on a good choice of the starting timestep by the user. To circumvent this error the .TRAN values are redefined, to change the time step for transient analysis. Also the RELTOL and ABSTOL values are changed to resume simulation.

SPICE also runs into convergence problems if in the circuit a capacitor is connected across a voltage source or a current source feeds an inductor. The simulation in this case aborts with an error message "check node #". One way to solve this problem is to add a small resistor to the circuit elements which causes the convergence problem.

# Chapter 3

# **DIODE BRIDGE RECTIFIERS**

In most power electronic applications, the power input is in the form of a 50 or 60 Hz sinewave ac voltage provided by the electric utility, which is first converted to a dc voltage. A majority of the power electronic applications such as switching dc power supplies, ac-motor drives and so on, use uncontrolled rectifiers. This chapter discusses the six-pulse and twelve-pulse diode bridge rectifier topologies. A model for the  $\Delta$ - $\Delta$ ,  $\Delta$ -Y transformer is presented using d-q axis theory. Simulated and experimental results are presented for comparison. The simulated and experimental performance analysis of the rectifier is done with emphasis on the line current harmonics and the THD.

#### 3.1 Six-Pulse Diode Bridge Rectifier

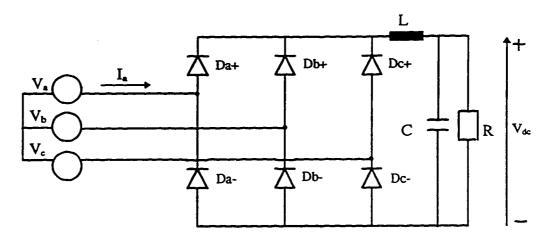

In industrial applications where three-phase ac voltages are available, it is preferable to use three phase rectifier circuits as compared to single-phase rectifiers. Three-phase rectifiers have lower ripple content in the waveforms and a higher power handling capability. A simple circuit for a six-pulse diode bridge rectifier with LC dc-link filter is shown in Fig. 3.1.

The input line current of the three phase rectifier deviates from being perfectly sinusoidal. By Fourier Analysis, the line current can be expressed in terms of the fundamental frequency and other harmonic components. If the line voltage is assumed to be purely sinusoidal, then only the fundamental component of the line current contributes to the average power flow. The line current harmonics are generally dominated by odd harmonics.

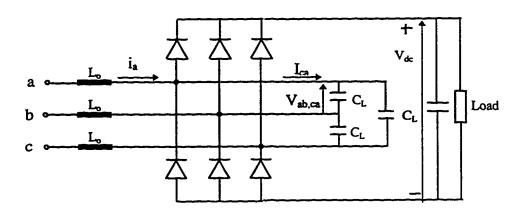

Fig. 3.1 Three-phase diode bridge rectifier circuit

For a three phase diode bridge rectifier with an LC dc-link filter, see Fig. 3.1 the line current harmonics (assuming  $L \rightarrow \infty$ ) are theoretically given as:

$$I_{a} = \frac{2\sqrt{3}}{\pi} I_{o} \left( \sin\theta - \frac{1}{5} \sin 5\theta + \frac{1}{5} \sin 7\theta - \frac{1}{15} \sin 11\theta + \frac{1}{15} \sin 13\theta \dots \right)$$

(3.1)

In a diode bridge rectifier, two devices conduct at any instant. Each diode conducts for 120° per cycle and a new diode begins to conduct after a 60° interval. The output rectified waveform which consists of portions of the line-to-line current ac voltage waveforms, repeat with a 60° duration, making this a six-pulse rectifier.

#### 3.1.1 Simulation of 6-pulse diode bridge rectifier

SPICE3 simulation and modeling is performed for a better understanding of the analysis of the bridge rectifier. Broadly there are two approaches in modeling the behavior of a semiconductor device like a diode. A macro-model, mainly based on an empirical approach, is one that does not take into account the geometry and the physical process of the device. This is to be distinguished from a micro-model that is based on the physical phenomena within the semiconductor model. In the present

work, we use a SPICE model of the diode such that the device's known input/output behavior is presented by an electrical equivalent circuit [25] and can be expressed in terms of its model parameter like breakdown voltage(BV), junction capacitance (CJO) and inverse saturation current (IS). Model parameters for the diode are defined on a separate .MODEL line. The SPICE library has a model for power diode which is aliased as "PD" (power diode) and is used for the present circuit.

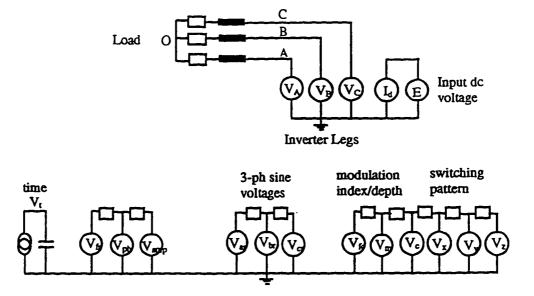

### 3.1.2 C dc-link filter

The SPICE3 model for the 3-phase diode bridge is shown in Fig. 3.2. In this rectifier topology we have a large C (940 $\mu$ F) dc-link filter at the rectifier output. For all practical applications a finite source inductance is always present. The values of the output capacitor and load are exactly the same as used in the experimental setup. The

Fig. 3.2 SPICE3 model for 6-pulse rectifier bridge with C filter

input source inductance in the power electronics laboratory was estimated to be about 0.4 mH. The effect of the line inductance is to slope off the vertical portion on the line current. This attenuates the higher order harmonics in particular. The SPICE3

schematic and its corresponding netlist for the six-pulse diode bridge rectifier is given in Appendix G.1. The salient features of the SPICE model in Fig. 3.2 are:

input sinusoidal voltage, V<sub>a</sub>

$$V_a = V_{amp} * sin(V_{fr} * V_t + V_{ph})$$

The input sinusoidal voltage is modeled with the help of a B-statement which is a voltage function representing the sinusoidal.

#### • time, V<sub>i</sub>:

The time is modeled as the constant current source in parallel with a capacitor.

The capacitor charges and ramps up linearly, thus the voltage node represents time.

# • amplitude, V<sub>amp</sub>:

The amplitude of the sinusoidal wave is modeled as a constant dc voltage source of magnitude 169V ( $\sqrt{2} \times 208 / \sqrt{3}$ ).

## • frequency, V<sub>fr</sub>:

The frequency of the sinusoidal wave is modeled as a constant dc voltage source of magnitude 60V corresponding to 60Hz.

#### phase, V<sub>ph</sub>:

The phase shift between the three phase voltages of the sinusoidal wave is modeled as a constant dc voltage source of magnitude 120V which corresponds to 120°.

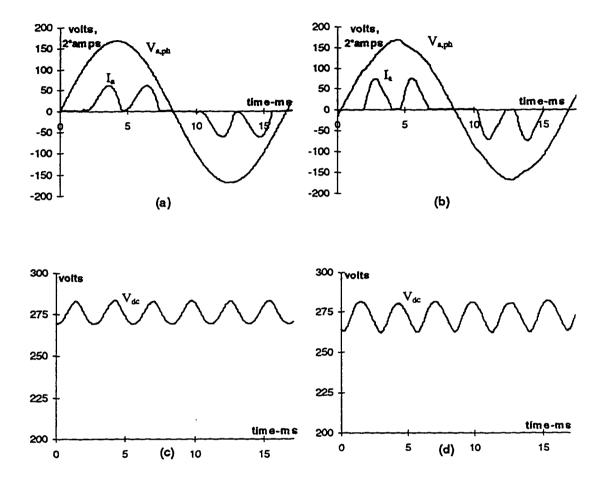

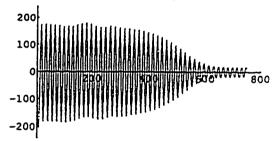

#### 3.1.3 Waveforms and analysis for C filter

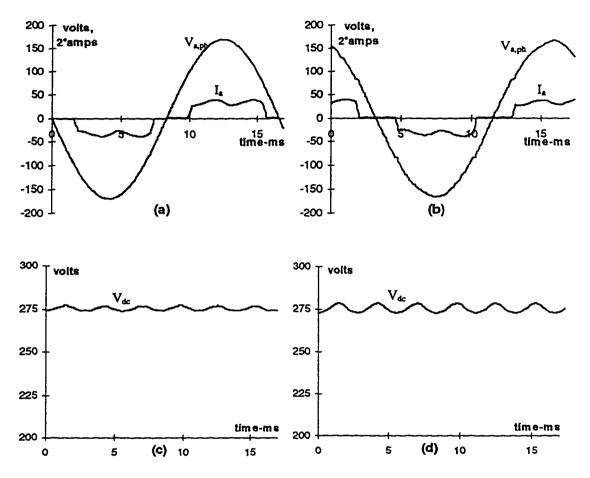

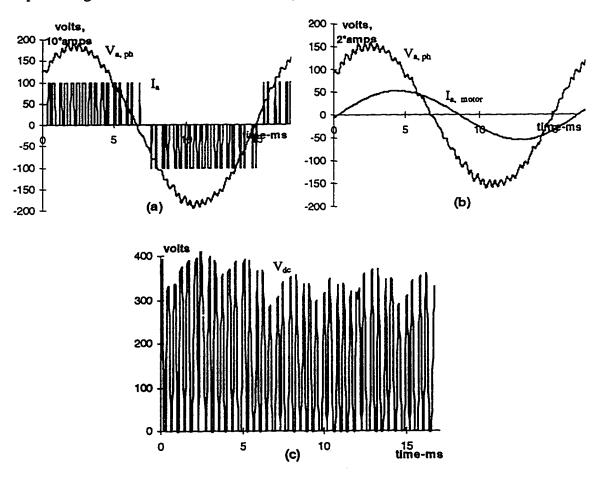

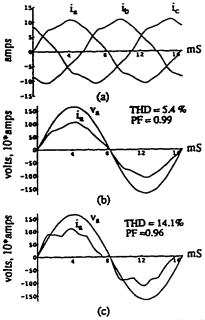

The simulated and experimental waveforms are shown in Fig. 3.3. As seen from Fig. 3.3(a),(b) the output current is always discontinuous. This is more prominent in the experimental waveform of the current. The reason being that the source inductance for the simulation could not be lowered below 0.4mH. With a voltage function feeding an inductor, any attempt to lower the inductance value causes a convergence problem, a problem commonly encountered in SPICE3. A larger value of source inductance in the simulation also causes larger commutation overlap as seen in Fig. 3.3 (a). Two current pulses are drawn from each phase during every half-cycle.

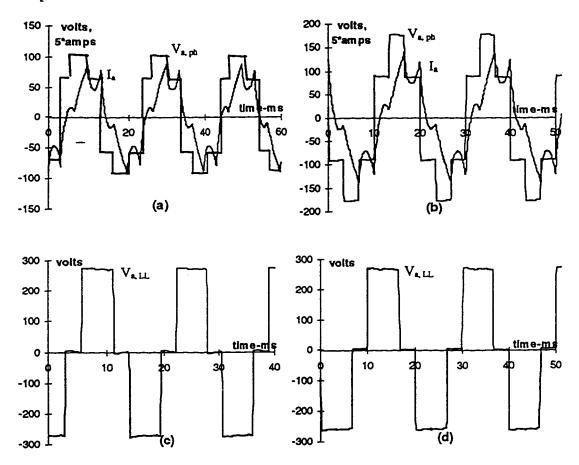

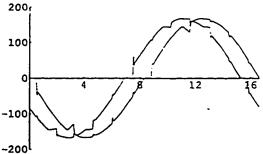

Fig. 3.3 Simulated and experimental waveforms for 6-pulse rectifier with C-filter, (a) simulated phase voltage and line current, (b) experimental phase voltage and line current, (c) simulated 6-pulse output rectified voltage, (d) experimental 6-pulse output rectified voltage.

## 3.1.4 Harmonic analysis for C-filter

Harmonic analysis and the various performance analysis through both experimental data and SPICE3 simulation is given in the Appendix A. Large values of THD are obtained because of dominant 5<sup>th</sup> and 7<sup>th</sup> harmonics. A lower value of THD of 68.3 % is obtained by simulation as compared to the experimental THD of 84.4 % because we used a larger source inductance in the simulation. A larger source inductance also results in a better PF of 0.81 as compared to the experimental PF of 0.77.

#### 3.1.5 LC dc-link filter

Often in three-phase rectifiers, an inductor placed on the dc side between the rectifier and the filter capacitor is used to improve the current waveforms and the ripple in the dc voltage output. It is possible to calculate the minimum value of inductance required to make the output current continuous for a given value of output current and input line-to-line voltage as follows:

$$L_{d,min} = \underbrace{0.013 \, V_{II}}_{\omega L_0} \tag{3.2}$$

Assuming the source inductance to be zero, an increase in the dc-side inductance improves the input power factor and if it is made large enough, such that the output current becomes essentially constant and ripple free, the PF approaches 0.955. Also at light loads the output current tends to be discontinuous. The order and magnitude of the theoretical current harmonics for a 6-pulse converter with LC filter can be determined from

$$\underline{I_h} = 1/h$$

$$I_1$$

where  $h = 6k \pm 1$ ,  $k = 1, 2, 3.....$  (3.3)

#### 3.1.6 Waveforms and analysis for LC-filter

Fig. 3.4 shows the simulated and experimental waveforms of the 6-pulse rectifier with LC dc-link filter. The presence of an inductor in the dc-link causes the current to be continuous as seen from Fig. 3.4(a),(b). The output rectified voltage is substantially lower as compared with the no-inductance case. The L and the C together form a low pass filter and, therefore, the peak-to-peak ripple in the rectified output voltage is less. The overall efficiency remains essentially the same as that with a C-filter; there are additional losses in the inductor, but the conduction losses in the diodes are lower.

Fig. 3.4 Simulated and experimental waveforms for 6-pulse rectifier with LC-filter, (a) simulated phase voltage and line current, (b) experimental phase voltage and line current, (c) simulated 6-pulse output rectified voltage, (d) experimental 6-pulse output rectified voltage.

#### 3.1.7 Harmonic analysis for LC-filter

Harmonic analysis and the various performance analysis through both experimental data and SPICE3 simulation is given in Appendix A. The 5<sup>th</sup> and the 7<sup>th</sup> line current harmonics are drastically reduced on addition of the inductor in the dclink, as compared to the case with only a C-filter. This results in a low THD of 27.6%. The THD obtained by simulation is better than the theoretical THD of 31%, because of a finite source inductance that improves the PF and hence results in a better THD.

The assumption of 1/h per unit harmonics, even when modified to allow for the attenuating effects of the commutation, do not adequately describe the actual magnitude of 6-pulse converter harmonic currents in many cases. To accurately

determine the characteristic converter harmonics, a calculation procedure which takes into account the ripple of the dc current reflected back into the ac line current must be performed [6]. Evaluation of these ripple effects will tend to increase the magnitude of the 5<sup>th</sup> harmonic while decreasing the magnitude of the higher order characteristic harmonics.

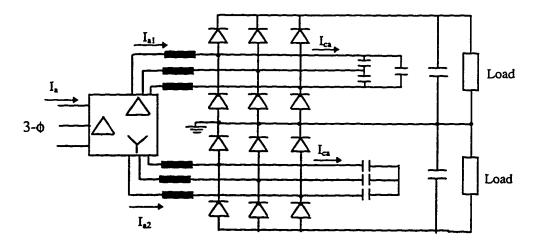

### 3.2 Twelve-Pulse Diode Bridge Rectifier

For higher power applications, when the converter current or voltage is high, diode bridges may be connected in series or parallel. For the present work, the series connection of two diode bridges on the dc side is used. One converter bridge is fed from a  $\Delta$ -Y transformer that introduces a three phase set of secondary voltages shifted by 30° with respect to the primary voltage. The other converter bridge is fed by a secondary voltage, from a  $\Delta$ - $\Delta$  transformer, which has no phase shift. Due to the phase relationships it is seen that some of the current harmonics in one bridge are in antiphase with those of the other. Thus, these phase shifting transformers provide mechanism for harmonic cancellation. In addition, they reduce the dc voltage output

Fig. 3.5 Block Diagram for 12-pulse diode bridge rectifier

ripple. This effectively reduces the size of the filter used in the dc-link. Operation with increasing pulse number is very desirable for high-power converter applications such as HVDC and large dc motor drives [39].

The harmonic cancellation of the input line current in terms of the Fourier components is

$$I_{a1} = \frac{\sqrt{3}}{N\pi} I_o \left(\cos\theta - \frac{1}{5}\cos 5\theta + \frac{1}{7}\cos 7\theta - \frac{1}{12}\cos 11\theta + \frac{1}{12}\cos 13\theta ...\right)$$

(3.4)

$$I_{a2} = \frac{\sqrt{3}}{N\pi} I_o \left( \cos\theta + \frac{1}{5} \cos 5\theta - \frac{1}{5} \cos 7\theta - \frac{1}{11} \cos 11\theta + \frac{1}{13} \cos 13\theta \dots \right)$$

(3.5)

$$I_a = I_{a1} + I_{a2} = \frac{2\sqrt{3}}{N\pi} I_o (\cos\theta - \frac{1}{1}\cos 11\theta + \frac{1}{1}\cos 13\theta ...)$$

(3.6)

In the operation of such multipulse converters, it is assumed that the dc circuit is filtered such that any ripple caused by the dc load does not significantly affect the dc current. This is true for passive loads and for most converters feeding dc power to voltage source inverters. It is less likely to be true for inverter loads of the current source type, where practical filtering may be insufficient to prevent dc load ripple from effecting the total ripple.

#### 3.2.1 d-q Axis Theory model for $\Delta$ - $\Delta/\Delta$ -Y transformer

The input of the 12-pulse rectifier bridge is the  $\Delta$ - $\Delta/\Delta$ -Y transformer, with their secondaries phase shifted by 30°. The series impedance of the autotransformer used in the experimental setup is taken into account in the simulation by using higher inductance values for the  $\Delta$ - $\Delta/\Delta$ -Y transformer.

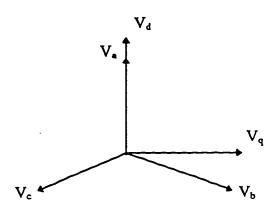

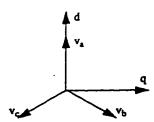

The equivalent per phase circuit of the transformer is considered in terms of the d-q axis theory [40]. In this theory the time varying parameters are eliminated and the variables and parameters are expressed in orthogonal or mutually decoupled direct (d) and quadrature (q) axes, see Fig. 3.6. The supply voltages in terms of d and q voltages are written in matrix form as

$$\begin{bmatrix} Va \\ Vb \\ Vc \end{bmatrix} = \begin{bmatrix} \sin\theta & \cos\theta & 1 \\ \sin(\theta + 120) & \cos(\theta + 120) & 1 \\ \sin(\theta - 120) & \cos(\theta - 120) & 1 \end{bmatrix} \bullet \begin{bmatrix} Vq \\ Vd \\ Vo \end{bmatrix}$$

(3.7)

where  $V_0$  is the zero sequence component which does not exist for a balanced three-phase condition. The angle  $\theta$  is arbitrary between the two sets of axes.

Setting  $\theta = 0$ , the d-axis will coincide with  $V_a$  and ignoring the zero sequence component, the above matrix equation yields the following transformation relations:

$$V_d = (2V_a - V_b - V_c) / 3 (3.8)$$

$$V_{g} = (V_{b} - V_{c}) / \sqrt{3}$$

(3.9)

Fig. 3.6 Phasor diagram for d-q transformation for  $\Delta$ - $\Delta$  transformer

#### 3.2.2 SPICE3 model for $\Delta$ - $\Delta/\Delta$ -Y transformer

The  $\Delta$ - $\Delta$  / $\Delta$ -Y transformer is modeled by considering two separate d-q per phase equivalent circuits having identical parameters. The parameter values for simulation are the same as the one used in the experimental setup. The data for the various tests - Open Circuit Test and Short Circuit Test done on the  $\Delta$ - $\Delta$  / $\Delta$ -Y transformer is given in Appendix B. Each phase is supplied with the  $V_d$  and  $V_q$  voltages by means of voltage functions using B-statements. The SPICE3 schematic with its corresponding netlist is given in Appendix G.2. The current flowing in the respective primaries are reflected back to the supply side. Similarly the secondary

currents are reflected into the load side. The expression for the phase currents in terms of the d and q currents flowing in the  $\Delta$ - $\Delta$  transformer is

$$\mathbf{I_{ai}} = \mathbf{I_d} \tag{3.10}$$

$$I_{bl} = -\frac{1}{2} I_d + \frac{\sqrt{3}}{2} I_q \tag{3.11}$$

$$I_{ci} = -\frac{1}{2} I_d - \frac{\sqrt{3}}{2} I_q \tag{3.12}$$

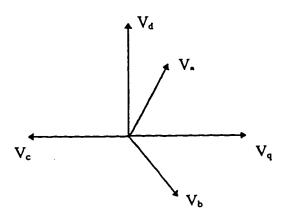

The  $\Delta$ -Y model differs from the  $\Delta$ - $\Delta$  model in that its input supply voltage is 30° phase shifted. The phasor diagram for the  $\Delta$ -Y secondary phase voltages in terms of the d and q voltages is given in Fig. 3.7

Fig. 3.7 Phasor diagram for d-q transformation of the  $\Delta$ -Y transformer

Similarly, the d and q voltages fed to the  $\Delta$ -Y per phase equivalent circuit is given by the transformation

$$V_d = -(2V_c - V_b - V_b)/3 (3.13)$$

$$V_q = (V_a - V_b) / \sqrt{3}$$

(3.14)

and the current relationships are

$$I_{a2} = \frac{\sqrt{3}}{2} V_d + \frac{1}{2} V_q \tag{3.15}$$

$$I_{b2} = -\frac{\sqrt{3}}{2} V_d + \frac{1}{2} V_q$$

$$I_{c2} = -V_q$$

(3.16)

$$I_{c2} = -V_{q}$$

(3.17)

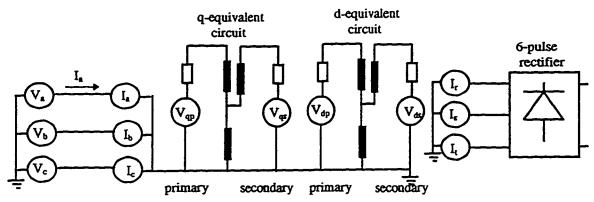

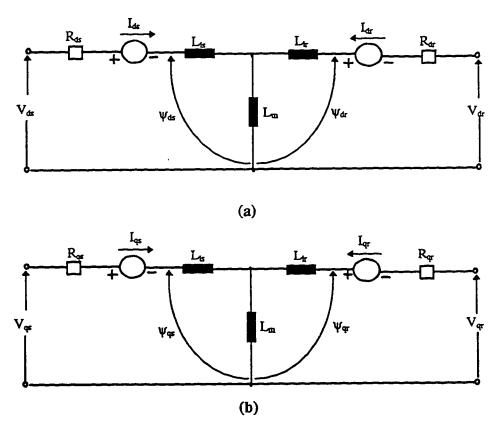

Fig. 3.8 d-q axis theory transformer model

The SPICE model for the  $\Delta$ - $\Delta$  transformer is shown in Fig. 3.8 and is obtained from the various equations derived from the d-q axis theory. Each transformer model consists of separate d and q equivalent circuits with a primary and a secondary. The input to the transformer is the three phase voltages  $V_a$ ,  $V_b$ ,  $V_c$  with phase a represented by a B-statement which is voltage function as explained in section 3.1.2.

Each of the primaries are fed by a B-statement which is a voltage function and is a functional relationship of the input phase voltages. These voltage relations are obtained from Equations (3.8),(3.9).

d-equivalent circuit primary:

$$V_{dp} = (2*V_a-V_b-V_c)/3$$

(3.18)

q-equivalent circuit primary:

$$V_{qp} = (V_b - V_c) / \sqrt{3}$$

(3.19)

The currents flowing in the primaries of each of the equivalent circuit is reflected back to the input side with the help of B-statements that are functions of the current flowing through the B-statements in the two primaries. These current relations are obtained from Equations (3.10), (3.11), (3.12).

Phase a:

$$I_a = I(V_{dp})$$

(3.20)

Phase b:

$$I_b = 0.5*(-I(V_{qp})+1.732*I(V_{qp}))$$

(3.21)

Phase c:

$$I_c = -0.5*(I(V_{dp})+1.732*I(V_{qp}))$$

(3.22)

where  $V_{dp}$  and  $V_{qp}$  are the voltage functions in the primary side of the d and q equivalent circuit respectively.

Similarly, the secondaries of the d and q equivalent circuits are fed by a B function which is a voltage functions of the output voltages. The current in the secondaries are reflected to the output and are functions of the current flowing through the B-statements in the two secondaries. The three output B-statements thus function as the input voltage to the 6-pulse diode bridge rectifier.

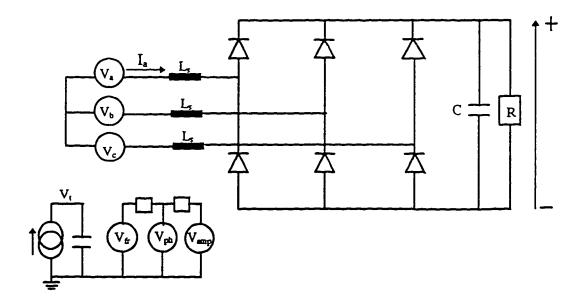

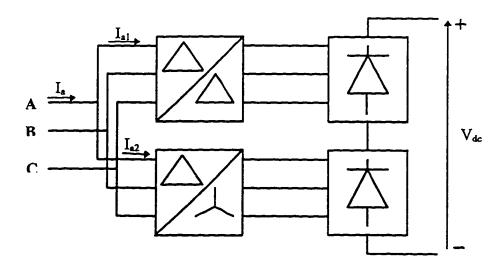

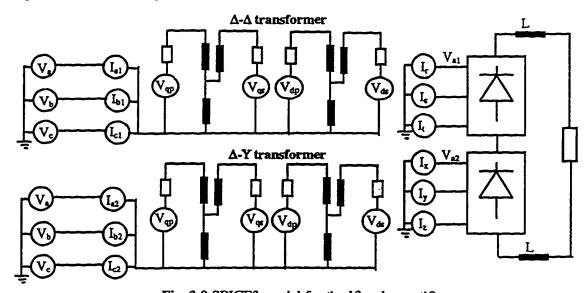

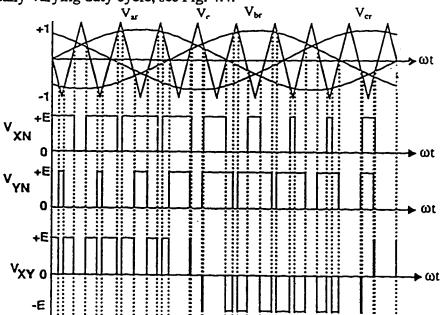

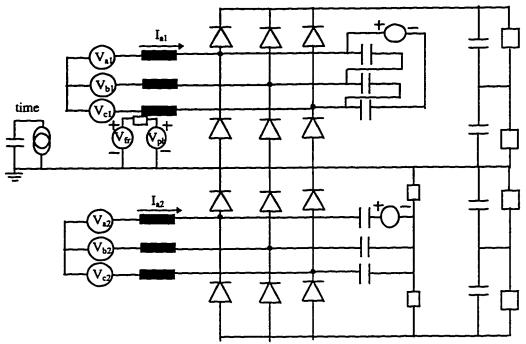

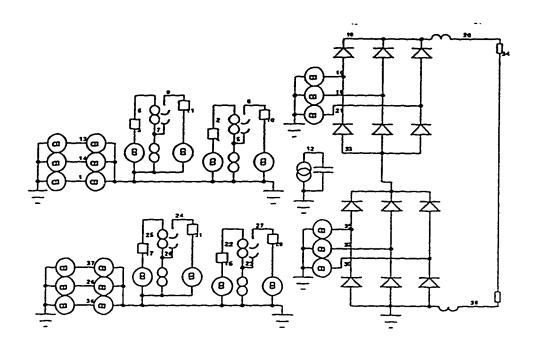

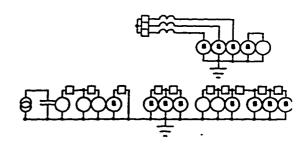

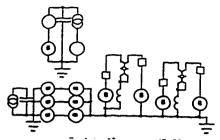

### 3.2.3 SPICE3 model for 12-pulse rectifier

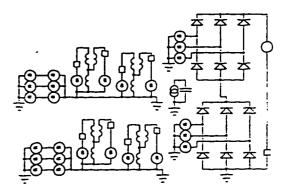

The SPICE3 model of the 12-pulse diode bridge rectifier is shown in Fig. 3.9. Two 6-pulse diode bridges are connected in series to give a 12-pulse operation. The  $\Delta$ - $\Delta$  / $\Delta$ -Y transformer has two primaries and two secondaries. The d-q axis voltages and current for the  $\Delta$ - $\Delta$  transformer are defined by Equations (3.8)-(3.12) and the corresponding relationships for the  $\Delta$ -Y transformer, whose output voltage is 30° phase shifted from the  $\Delta$ - $\Delta$  transformer, are defined by Equations (3.13)-(3.17).

The use of B-statements to decouple the input and the output of the  $\Delta$ - $\Delta$  / $\Delta$ -Y transformer helps to simplify the model by avoiding the non-linear interaction between the input and the output. This decoupling leads to more nodes being connected to the ground thus generating a much sparse nodal admittance matrix during simulation. The Sparse Matrix technique thus used increases the speed of simulation.

Fig. 3.9 SPICE3 model for the 12-pulse rectifier

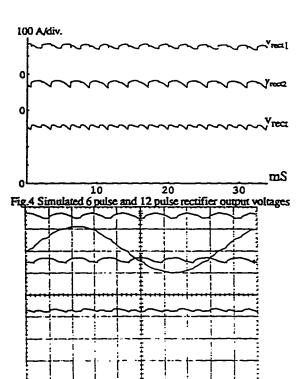

#### 3.2.4 Waveforms and analysis for 12-pulse rectifier

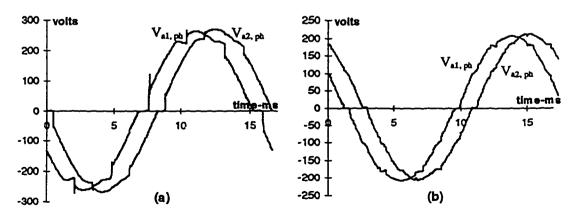

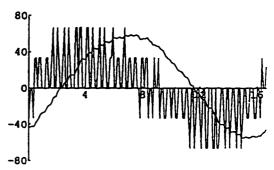

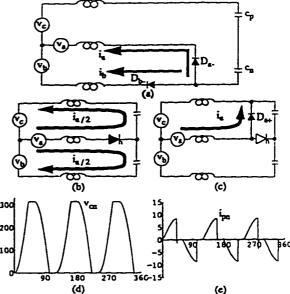

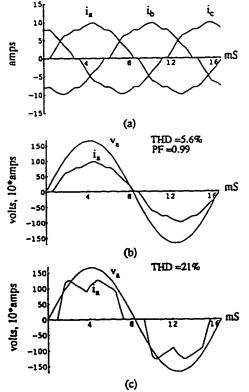

Fig. 3.10 shows the simulated line-to-line output voltage and experimental phase voltage waveforms for the  $\Delta$ - $\Delta$  transformer and  $\Delta$ -Y transformer. Significant commutation overlap is seen in the simulation results due to the large leakage reactance of the transformer. Also, an autotransformer was used in the experimental setup, that further adds to the line inductance. The presence of line inductance does not change the order of characteristic harmonics produced either on the ac side or on the dc side.

Line notching results as shown in Fig. 3.10 due to changeover of current conduction from one device to the other. With diode operation, the current changes naturally from one device to the other, and the notch has one fast rising side. On the other hand with an SCR bridge, the notch will have two fast changing sides, which gives a greater likelihood of high frequency interference. When the converter is operated from the line without phase shift, the line voltage shows one large notch and two smaller notches. On the other hand, if the converter is operated from a phase-shifting transformer, the pattern of notching changes. In the case of the  $\Delta$ -Y transformer with 30° phase shift, there will be two larger notches. In a 12-pulse circuit formed from two 6-pulse circuits, the load current being commutated is reduced to one-half. Notch area is thus reduced by a factor of 2 for a 12-pulse rectifier as compared to the 6-pulse operation [41].

Fig. 3.10 Waveforms for  $\Delta$ - $\Delta$  /  $\Delta$ -Y transformer, (a) simulated line-to-line output voltage, (b) experimental phase voltage.

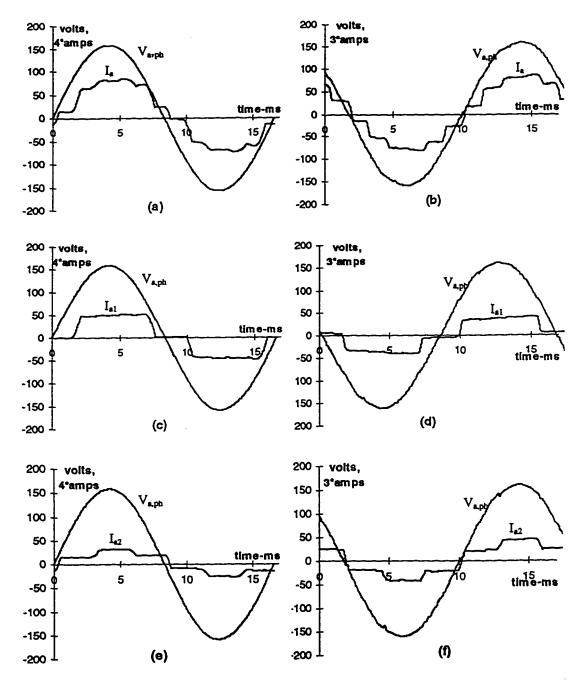

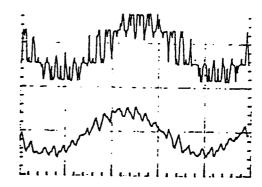

Fig. 3.11 Simulated and experimental line current waveforms for the  $\Delta$ - $\Delta$ /  $\Delta$ -Y transformer, (a) simulated phase voltage ( $V_{\rm uph}$ ) and total line current, (b) experimental phase voltage and total line current, (c) simulated phase voltage and input line current for the  $\Delta$ - $\Delta$  transformer, (d) experimental phase voltage and input line current for the  $\Delta$ - $\Delta$  transformer, (e) simulated phase voltage and input line current for the  $\Delta$ -Y transformer, (f) experimental phase voltage and input line current for the  $\Delta$ -Y transformer.

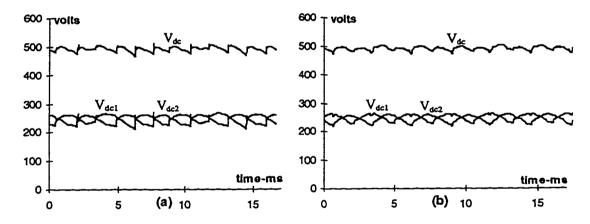

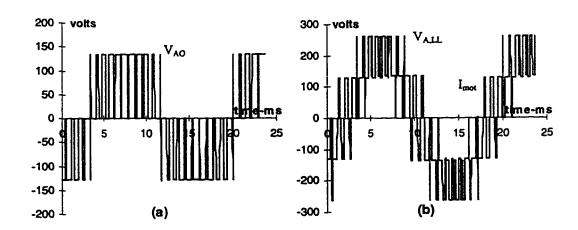

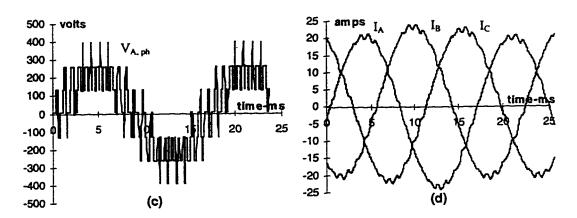

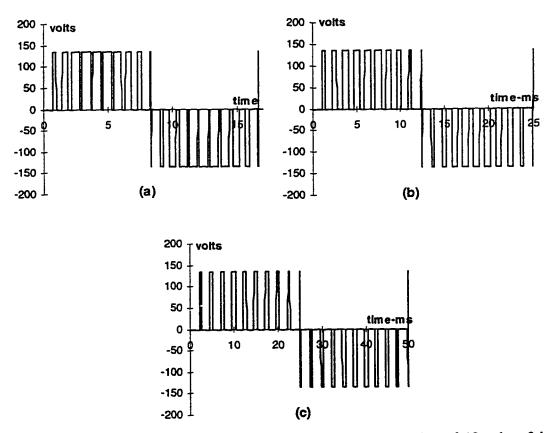

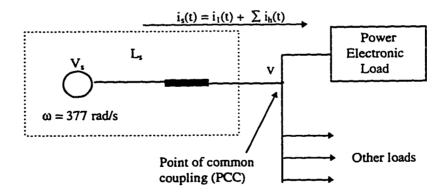

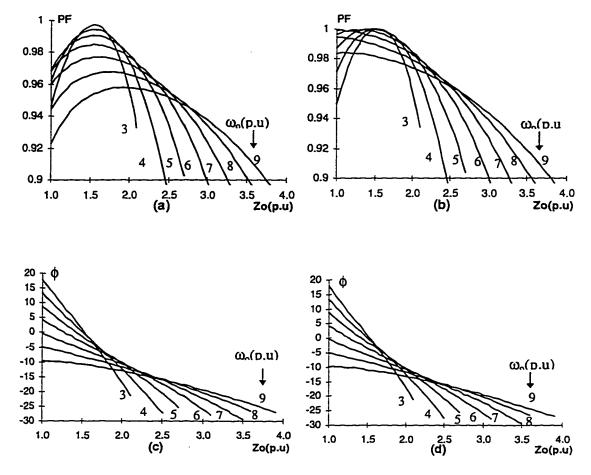

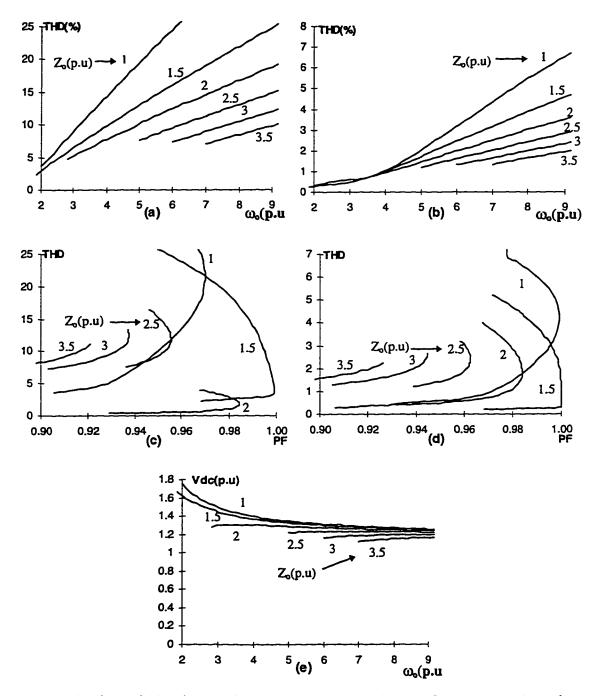

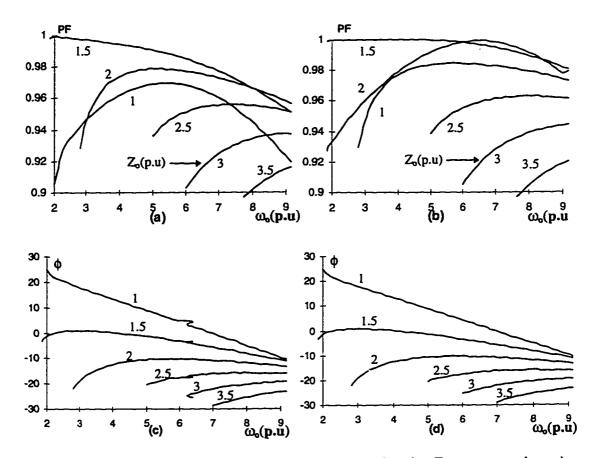

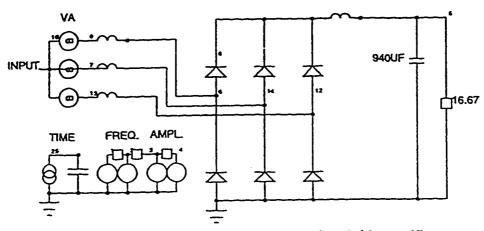

The 12-pulse rectifier model has two six-pulse diode bridge rectifier connected in series. The load is resistive with a 2.5mH inductor in both the positive and the negative dc rail. The value of the load resistance is the same as used in the experimental setup. Typical waveforms of the different line currents are given in Fig. 3.11. The waveforms are rounded instead of being the theoretical stair-type of waveforms because of the inductive source and leakage impedances.