Received 3 September 2014; revised 12 January 2015; accepted 22 March 2015. Date of publication 29 June 2015; date of current version 10 August 2015.

Digital Object Identifier 10.1109/JPETS.2015.2427370

# Real-Time Simulation Technologies for Power Systems Design, Testing, and Analysis

IEEE PES Task Force<sup>1</sup> on Real-Time Simulation of Power and Energy Systems CORRESPONDING AUTHOR: T. STRASSER (thomas.i.strasser@ieee.org)

**ABSTRACT** This task force paper summarizes the state-of-the-art real-time digital simulation concepts and technologies that are used for the analysis, design, and testing of the electric power system and its apparatus. This paper highlights the main building blocks of the real-time simulator, i.e., hardware, software, input-output systems, modeling, and solution techniques, interfacing capabilities to external hardware and various applications. It covers the most commonly used real-time digital simulators in both industry and academia. A comprehensive list of the real-time simulators is provided in a tabular review. The objective of this paper is to summarize salient features of various real-time simulators, so that the reader can benefit from understanding the relevant technologies and their applications, which will be presented in a separate paper.

**INDEX TERMS** Digital real-time simulation (DRTS), digital simulators, hardware-in-the-loop (HIL) simulation, power engineering, power system transient simulation, real-time systems.

### NOMENCLATURE

$T_e$  Execution time.

$t_n$  Time step.

#### **I. INTRODUCTION**

**D** IGITAL real-time simulation (DRTS) of the electric power system is the reproduction of output (voltage/currents) waveforms, with the desired accuracy, that are representative of the behavior of the real power system being modeled. To achieve such a goal, a digital real-time simulator needs to solve the model equations for one time-step within the same time in real-world clock [1], [2]. Therefore, it produces outputs at discrete time intervals, where the system states are computed at certain discrete times using a fixed time-step.

DRTS is a technique for the transient simulation of power systems using digital-computer time-domain solution (e.g., using an electromagnetic transient-type approach) [3]–[6]. Systems are represented by taking advantage of the component models available in the library of the software tool using a graphical interface and simulated on a hardware platform employing parallel computation.

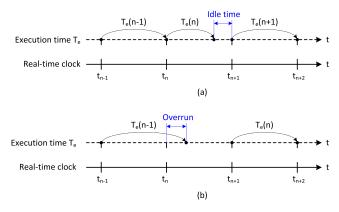

Two situations can arise depending on the time required by the simulation platform to complete the computation of state outputs for each time-step (Fig. 1): 1) if the execution time,  $T_e$ , for the simulation of the system is shorter or equal to the selected time-step, the simulation is considered to be real-time [Fig. 1(a)]; and 2) if  $T_e$  is greater than its time-step size for one or more time-steps, overruns occur and the simulation is considered as nonreal-time or offline. In the latter case, either the time-step can be increased or the system model can be simplified to run it in real time.

The aim of this paper, therefore, is to given an overview of the state-of-the-art in real-time simulation technologies for power systems design, testing, and analysis. The main components and concepts as well as an overview of commonly available solutions are presented in this review paper.

The rest of this paper is organized as follows. Section II introduces different categories of real-time simulators, and in Section III, their evaluation over the last few years is presented. Their computing capabilities are discussed in Section IV, followed by the description of typical

<sup>&</sup>lt;sup>1</sup>Task Force Members: M. O. Faruque, T. Strasser, G. Lauss, V. Jalili-Marandi, P. Forsyth, C. Dufour, V. Dinavahi, A. Monti, P. Kotsampopoulos, J. A. Martinez, K. Strunz, M. Saeedifard, X.Wang, D. Shearer, M. Paolone, R. Brandl, M. Matar, A. Davoudi, and R. Iravani were part of the IEEE PES Task Force on Real-Time Simulation of Power and Energy Systems.

characteristics of the systems in Section V. Finally, the conclusion is drawn in Section VI.

## **II. CATEGORIES OF DIGITAL REAL-TIME SIMULATION**

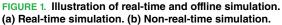

DRTS applied to the domain of power systems can be classified into two categories: 1) fully digital real-time simulation (e.g., model-in-the-loop, software-in-the-loop, or processorin-the-loop), and 2) hardware-in-the-loop (HIL) real-time simulation. A fully digital real-time simulation requires the entire system (including control, protection, and other accessories) to be modeled inside the simulator and does not involve external interfacing or inputs/outputs (I/Os). On the other hand, the HIL simulation refers to the condition where parts of the fully digital real-time simulation have been replaced with actual physical components. The HIL mode of the simulation proceeds with the device-undertest or hardware-under-test (HuT) connected through inputoutput interfaces, e.g., filters, digital-to-analog and analogto-digital converters and signal conditioners. Limited real-time controls of the simulation can be executed with the user-defined control inputs, for example, closing or opening of switches to connect or disconnect the components in the simulated power system.

If the HIL system involves real controller hardware that interacts with the rest of the simulated system, it is called controller hardware-in-the-loop (CHIL). It is also used for rapid controller prototyping. In this method, no real power transfer takes place and the power system is modeled as a virtual system inside the simulator, and the external controller hardware exchanges controller I/Os with the system inside the simulator. In general, a newly designed/developed controller is tested using this method, where the controller takes feedback signals from the simulator and processes them to produce the required output signals, which are then sent back to the system (inside the simulator). Such a setup of a controller prototyping or CHIL arrangement is shown in Fig. 2, where a power electronic converter is modeled inside the simulator and the real controller is connected to it through I/Os.

Any HIL simulation involving power transfer to or from the HuT is known as power hardware-in-the-loop (PHIL) (Fig. 2). In this case, part of the power system is internally

64

simulated and the other part is the real hardware power apparatus connected externally. A power source or sink (connected through the PHIL interface) is needed for this setup, which will either generate or absorb power. Reference signals are generated based on the solution of the virtual system inside the real-time simulator and are sent to the power amplifier that produces voltages or currents to be applied to the HuT. Feedback signals obtained from the voltage/current measurements of the HuT are appropriately scaled and brought back to the simulator to complete the simulation loop.

An example of such simulation could be the real-time testing of machines, converters [7], fault-current limiters, or any other electrical equipment. Testing of protection devices, such as relays, may require voltage or current amplifiers for HIL-based testing; however, no power is exchanged in that case [8], [9]. The use of an amplifier is mainly for the device to sense the actual voltage and/or current signals.

In general, a fully digital simulation is often used for understanding the behavior of a system under certain circumstances resulting from external or internal dynamic influences, whereas an HIL simulation is used to minimize the risk of investment through the use of a prototype once the underlying theory is established with the help of a fully DRTS.

# III. EVOLUTION OF DIGITAL REAL-TIME SIMULATORS

Using parallel processor-based digital technologies and improved numerical analysis techniques with less computational burden, a number of digital real-time simulators have been proposed and tested [10]–[20]. Initial realtime simulators were based on the digital signal processor (DSP) [10]–[12], reduced instruction set computer (RISC) [13]–[16], and complex instruction set computer [17] technologies; however, the use of general-purpose processors as the computation engine has become an attractive option because of their lower cost and faster development cycle [21]. Development of a clustered system, using off-the-shelf digital processors, is based on advanced communication networks, which is becoming a growing trend for the development of the DRTS.

The first commercial real-time digital simulator (RTDS) was demonstrated by RTDS Technologies Inc. in 1991 using DSPs [13]. It was interfaced to the controller of a high voltage direct current converter to assess its performance. A combination of both analog and digital parts was used in that simulator. Since then, this simulator has evolved and become one of the widely used commercial RTDSs. The first small-scale digital real-time simulator for the real-time test of the power system equipment based on a standard multipurpose parallelcomputer system, known as the digital transient network analyzer (DTNA), is presented in [16]. The DTNA could simulate electromagnetic transient phenomena up to 3 kHz, ac/dc interactions, electromechanical transients, and similar longtime phenomena. A wide variety of components, equipment, and controllers, including power electronic-based controllers, can be modeled and simulated using this simulator.

No fully digital real-time simulator was possible in a standard computer before 1996, when Électricité de France introduced their first real-time simulator ARENE [18]. It was capable of simulating the high-frequency phenomenon in a standard, multipurpose parallel computer. Another PC-based real-time simulator, NETOMAC [19], [20] from SIEMENS, was used to simulate large power grids. Almost at the same time, another general-purpose processor-based realtime simulator from OPAL-RT Technologies Inc. [21]-[25] was introduced, which uses the MATLAB/Simulink as the main modeling tool for the simulation. Almost a similar approach of using a standard PC for real-time simulation and control was adopted by dSPACE [26], which uses generalpurpose processors and MATLAB/Simulink as the modeling package, though their older generation simulators used DSPs. HYPERSIM [27]-[29] is another fully digital real-time simulator for the analysis of the electromagnetic and electromechanical transients in large and complex power systems and originally developed by IREQ, the Hydro-Quebec's research institute.

Other than the aforementioned real-time simulators, custom laboratory-scale real-time simulators have been presented in the literature. These real-time simulators use a combination of hardware and software mostly to serve specific requirements. field-programmable gate arrays (FPGAs) [30]-[35] and graphics processing unit (GPU) [43] are two such digital processors that are gaining foundation as a computation hardware for real-time simulation. User-friendly block coding, automatic code generation capability, and interfacing capability with Simulink allows these hardware to be used as an auxiliary platform of large simulators that allow to model and then to simulate a system within a timestep of nanoseconds while the main simulation runs at a larger time-step (in microseconds) [35]. These are other promising avenues for future exploration in the field of realtime simulation of the power system.

## IV. COMPUTING CAPABILITIES OF REAL-TIME SIMULATORS

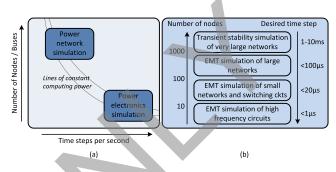

A real-time simulator needs to solve a grid-scale model by roughly 50  $\mu$ s or a smaller time-step (for suitable resolution in 50-/60-Hz power systems) to reproduce transients faithfully. Computing capability may be defined as the product of the number of nodes/buses in the simulated power network and the number of time steps taken per second. For a 50-/60-Hz ac power network, this capability corresponds to a large node/bus count and fairly low speed; however, for power-electronic systems operating with higher switching frequencies, smaller time-steps are required. If controlled digitally, high-frequency switching circuits may operate with a microcontroller having an internal clock speed with periods of 1  $\mu$ s to 10 ns. A simulation of such a system may require more computing capability and the ability to simulate with a very small time-step. Despite the high-speed internal dynamics of the power electronics-based apparatus, the systemlevel interactions may not require a very small time-step. For simulating fast and slow subsystem transients, a multirate cosimulation approach can be adopted.

Fig. 3 shows the relationship between computing nodes and time-step requirements for different systems. The power system simulation may be sufficient at a comparatively larger time-step, and for a constant computing power, it allows a larger system, whereas for power electronics simulation, smaller time-steps are necessary, resulting in a smaller system for the same computation power.

FIGURE 3. Illustration of (a) computing capability requirements for different types of systems and (b) time-step requirement for different types of simulation.

A real-time simulator is often configured to be scalable. The increment of computing power is possible by adding rack-mount units that require data communication between racks. Individual computing units operate in parallel, offering a reasonable scaling property; however, communication adds time delay. Communication bottlenecks are minimized by exploiting the traveling wave properties to decouple the solutions of the network subsystems that are separated by transmission lines of appropriate length that is consistent with the simulation step interval [13]. Power processors or other hardware such as general-purpose central processing units (CPUs) work in parallel by sharing common memories or buses to minimize the communication latencies.

### **V. CHARACTERISTICS OF REAL-TIME SIMULATORS**

A. COMMON FEATURES OF REAL-TIME SIMULATORS

Most DRTS have the following common characteristics:

- 1) multiple processors operate in parallel to form the target platform on which the simulation runs in real time;

- a host computer is used to prepare the model offline and then compile and load it on the target platform. Host computers are also used for monitoring the results of real-time simulation;

- 3) I/O terminals to interface with external hardware;

- a communication network to exchange data between multiple targets when the model is split into multiple subsystems. A separate communication link is required for data exchange between the host and the target.

Hosts, targets, and communication links may sometimes be called otherwise by different vendor-specific names.

# B. LARGE-SCALE AND COMMERCIAL REAL-TIME SIMULATORS

This section describes the characteristics of two widely used large and scalable RTDSs. We refer to them as Type-A and Type-B simulators.

# 1) HARDWARE

For most of the simulation environments, hardware directly influences the computing capability of the simulator. Hardware for different real-time simulators evolved with time, and in this paper, an effort has been made to describe the current state-of the-art hardware.

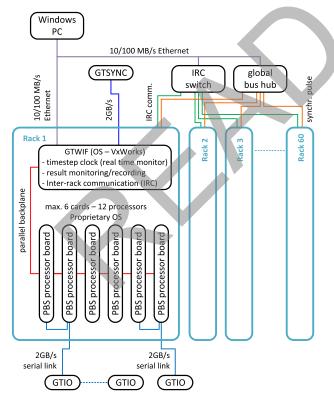

Fig. 4 shows the hardware architecture of a Type-A simulator [13] that employs custom hardware assembled in units called racks. The racks contain several slot-mounted processor cards known as PB5 cards, each containing two PowerPC RISC processors operating in parallel, and serves as the main computational engine. A maximum of six processor cards or 12 processors can be put into one rack and the maximum number of nodes that can be simulated using each card are 72. The processor card also allows two network solutions (each network solution requires one processor) to be included in one rack to represent two subsystems with 72 nodes each. Larger networks with more nodes/subsystems can be represented using additional racks.

FIGURE 4. Hardware architecture of RTDS simulator.

In addition to the main processor cards, each simulator rack of this type contains a workstation interface

card known as a GTWIF card. The GTWIF is an IBM PPC405-based processor card used for the Ethernet communication between the host (i.e., a Windows-based PC) and the target (i.e., the racks). The GTWIF also provides communication links between racks as well as enforces synchronization and real-time operation of the processors. A number of peripheral components are also available for this simulator. The GTSYNC card is used to synchronize the simulation time-step to an external time reference (e.g., a global position system clock, which also synchronizes the devices under test), GTIO cards to facilitate physical connections to external hardware via analogue and digital I/O, the GTNET card to provide communication via high level Ethernet protocols (e.g., IEC 61850, DNP, C37.118, and so on), the global bus hub for real-time synchronization of three racks or more, and so on. This hardware is custom designed, and detailed descriptions are available in [36]. Recently, this simulator introduced the application of FPGAs in conjunction with its main processors to perform the simulation of very highfrequency (20-100 kHz) switching circuits [37].

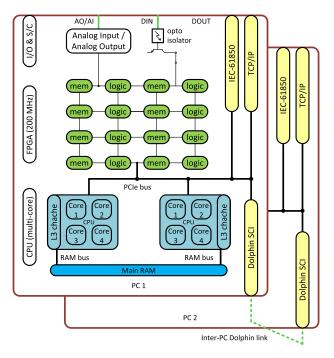

Another commercial off-the-shelf-component-based scalable real-time (Type-B) simulator is developed that uses general-purpose multicore multithread CPUs, such as processors from Intel Xeon or the AMD family of CPUs [38]. Using a multi-CPU motherboard, the simulator can be extended up to many cores per target system, and each core can be used to model a subsystem [38]. Fig. 5 shows how various components of the hardware are connected to form the real-time simulator. In addition to the common PC components, reconfigurable FPGAs are used for conditioning I/O signals and limited modeling environments for high-frequency components using Xilinx toolbox Xilinx System Generator (XSG). The latest trend of this simulator is to customize applicationoriented systems, such as integrating FPGAs, GPUs, or a combination of other hardware components for specific industry application [39]–[41].

### 2) SOFTWARE

Software required for real-time simulators can be divided into two main categories: 1) operating system (OS) software and 2) application software. In general, commercially available real-time simulators run on either Windowsor Linux-based OSs. However, depending on the hardware, specialized OSs may be necessary. For most of the simulators, the OS is supplied by the vendor. For custom-made realtime simulators, hardware-specific OS may be required and normally comes with the hardware.

Application software mainly provides a platform for modeling power system networks and their controls. In general, graphical user interface (GUI)-based modeling environments are provided to drag and drop components to build the entire system. In some cases, a command line language can also be used and scripts are executed to automate the simulation. Application software uses its own built-in modeling tools and solvers to simulate the systems. However,

FIGURE 5. Hardware architecture of eMEGASIM real-time simulator.

the use of a custom model or custom code is possible if the provided model does not meet the user requirement.

Since the simulator described in [36] is built upon custom hardware, the GTWIF OS is based on VxWorks, but the PB5 processor card uses a proprietary bare metal OS for increased efficiency. Its application program software suite runs on a Windows-based host platform and is used to build the model, set up simulations, control, acquire data, and modify system parameters during a simulation. The other simulator [38] uses Linux-based platforms such as RedHawk, RedHat, or QNX as the OS for the targets, and modifies them to support the functionality and the performance required by complex real-time applications. One key aspect of the modified Linux is the complete core shielding, where all the cores except one are dedicated for real-time computation and are shielded from system interrupts. That particular one core performs the job of real-time operating tasks and schedules. For the host OS, it uses Windows, although Linux OS is also an option. This simulator provides a set of proprietary toolboxes to be used for modeling different types of systems.

#### 3) COMMUNICATION AND INTERFACING

The Type-A simulator uses a common communication backplane that links all slot-mounted cards within a rack and facilitates the exchange of information. Direct card-to-card communication is also possible through the multiple fiber optic links located on the processor cards. The processor card fiber optic links are also used to connect I/O cards in parallel and/or in a daisy chain. In a multirack simulator, the backplanes function independently and in parallel, thereby reducing communication bottlenecks. Information that must be shared between racks is passed via interrack communication (IRC) channels on the GTWIF cards (point-to-point communication). For simulators with more than seven racks, an IRC switch is used to provide direct communication between as many as 60 racks (star-point communication). The communication between the simulator racks and the host computer is performed by the GTWIF cards using standard Ethernet.

Due to the fast advancement of digital technologies, including network and communication, Type-B simulators have gone through fast development phases, where various communication techniques and protocols have been used for sharing information between the host and the target nodes. To name a few that are currently used are shared memory for inter CPU communication inside the target, signal wire, InfiniBand, Gigabit Ethernet, Dolphin SCI and PCIe link for target-to-target communication and TCP/IP link for asynchronous communication with the host.

## 4) MODELING TOOLS/LIBRARIES

For Type-A simulators, GUI component model libraries are included as an integral part of the RSCAD suite and allow building of power system models along with the necessary control and protection. Another important feature of the suite is that it allows small time-step  $(1-4 \ \mu s)$  environment subnetworks, which can be freely constructed to represent high-frequency switching dynamics. The small-time-stepbased subnetworks can be interfaced to one another through transmission line models (TLM) or to large-scale power systems models operating with the time-steps on the order of 50  $\mu$ s through TLM or interface transformers. The interface technique is similar to the technique of splitting large models into multiple racks by exploiting the traveling wave delay for transmission lines with a travel time longer than one time-step. The requirements for larger or smaller time-step circuits can also be achieved using FPGA cards, where very high-frequency switching circuits can be modeled with timesteps in the order of hundreds of nanoseconds and can still be interfaced with either small time-step subnetworks or large time-step subsystems. A facility is also provided within RSCAD for the user to create new simulation components. The conversion tool that converts a PSS/E into a RSCAD model is another useful tool for utility application, especially for developing such models of larger power systems.

For Type-B variants, a MATLAB/Simulink environment is employed for the development of power and control system models. Most physical systems and their controllers can be modeled with the built-in MATLAB/Simulink toolboxes; however, the user-defined models written in MATLAB or other high-level languages, such as C/C++ or FORTRAN, can also be included through the MATLAB/Simulink S-function interface. Custom models based on VHDL coding can also be integrated with the Simulink-based models. Large and complex systems models can be divided into several subsystems and distributed over a number of parallel cores. Additional model enhancement tools, such as RT-EVENTS, RTDRIVE, and RT-XSG [38], are good examples of the MATLAB/Simulink environment expansion. In addition, LABView, PYTHON, and other application programming interfaces can also be incorporated for scripting and automating the simulation.

# 5) SOLUTION METHODOLOGY

A Type-A simulator uses Dommel's electro magnetic transients program (EMTP)-type algorithm [4], [8] to discretize all the components of the circuits, including passive elements such as breakers and faults. Active sources are modeled as equivalent sources with several types of impedances, including positive and zero sequences. The network solution performs real-time decomposition of the admittance matrix that allows continually varying conductance elements to be represented in the circuit.

On the other hand, a Type-B simulator also uses a nodal admittance-based solver called ARTEMiS-SSN [42]. In this simulator, models are built upon the Simulink and SimPowerSystems platforms, where default trapezoidal or backward Euler solver/integration algorithms available in MATLAB/Simulink for discrete solution could be used. These solvers, however, are not designed for strictly real-time simulation, because the solution time of each step varies considerably. The ARTEMiS-SSN solvers enforce strictly fixed time-step simulation for these models and are effective for networks under 100 three-phase buses [41]. ARTEMIS-SSN is a nodal admittance solver that uses a fixedstep higher order discretization/solution algorithm and uses the interpolation method, allowing very accurate detection of switching events. It also precomputes the nodal companion matrices, derived from their respective state-space equations, combined with online refactorization of the nodal admittance matrix and thereby provides a faster simulation compared with the SimPowerSystems solvers.

In addition to the EMTP-type solution, both Type-A and Type-B DRTS offer the hybrid solution technique, where part of the network in detail is solved using an EMTP-type simulation while considering its interaction with a much larger network, which is simulated using a transient stability solver. Type-B DRTS also allows the real-time phasor simulation of networks with more than 10 000 busses per core [43]. Irrespective of the simulation type (EMTP or phasor), it is required to address the synchronizing of discrete events that takes place during the time-step of simulation. Although this is a big challenge for DRTS, a number of methods have been published [44]–[47], and such simulators apply suitable methods in respective cases.

### 6) INPUTS AND OUTPUTS

In the Type-A simulator, various I/O cards are typically mounted on DIN rails within the simulator cubicle and connected directly to individual processor cards via optical fibers. The I/O cards provide digital and analog I/O ports for interfacing external hardware to the simulation. Alternatively, the I/O cards can be located remotely and connected using fiber lengths in the range of 75 m. Each processor card has multiple 2-GB/s optical ports to provide a very high bandwidth communication capability to support the I/O. Similarly, the Type-B simulator interfaces real hardware I/O signals of various types (analog, digital, pulsewidth modulation, timers, encoders, and so on) through the FPGA-based multichannel I/O modules. The scalable I/O terminals can detect external events at 10 ns resolution and can capture or generate multiple events within a simulation time-step to incorporate very precise timing into the model. Besides supporting the standard communication protocols such as Gigabit Ethernet, C37.118, IEC 61850, and DNP3, both simulators support many other third-party I/O boards.

# C. OPEN-SOURCE OR NONCOMMERCIAL REAL-TIME SIMULATORS

Outside the proprietary world, there are many real-time simulators built in many laboratories that came out of research projects for serving an in-house purpose. One such lowcost real-time simulator known as virtual test bed (VTB-RT) was developed at the University of South Carolina. While a preliminary approach to real-time extension in VTB was proposed a few years ago [49], a new, more advanced process has been developed in collaboration with RWTH Aachen University in Germany [50]. This first real-time extension is based on exactly the same solver adopted for the desktop version, while the new version is based on a simulation method specifically developed for real-time simulations [51], [52].

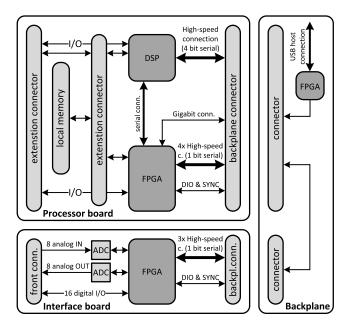

From the hardware perspective, in the current generation of supported processor boards, one DSP is used as a processing node of each processor board. A companion FPGA is used for providing timing, synchronization, and coprocessing as

FIGURE 6. DSP cluster-based architecture of VTB-RT simulator.

| TABLE 1. Summary of salient features | s of RTDSs reported in the literature. |

|--------------------------------------|----------------------------------------|

|--------------------------------------|----------------------------------------|

| Real-Time<br>Simulator                                            | Hardware                                                                                                                                                   | OS and<br>Application<br>Software                                                                                                                                                              | Communication,<br>Protocols, Inter-<br>facing and I/O                                                                                                                                      | Modeling and<br>Solution                                                                                                                                                                     | Application                                                                                                                                                               | Other                                                                                                                                                                                                           |

|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTDS from<br>RTDS Tech-<br>nologies Inc.<br>[13], [14],<br>[36]   | PowerPC RISC<br>processors are<br>implemented in<br>cards (PB5),<br>GTFPGA                                                                                 | Host OS: Windows<br>Target OS:<br>VxWorks<br>Application soft-<br>ware: RSCAD                                                                                                                  | Optical fiber, fast<br>back plane, global<br>bus hub, Gigabit<br>Ethernet, DNP3,<br>IEC61850, TCP/IP<br>C37.118, analog<br>and digital I/O,<br>third party I/O<br>through GTNET            | EMTP -type library<br>of component<br>models, small time-<br>step models for<br>some components,<br>Dommel's algo-<br>rithm based Nodal<br>solver                                            | Real-time simula-<br>tion of power<br>systems, power<br>electronics, control<br>systems, testing of<br>equipment through<br>HIL simulation                                | Allows multi-rate<br>simulation                                                                                                                                                                                 |

| eMEGAsim<br>from OPAL-<br>RT Technol-<br>ogies Inc.<br>[23], [38] | Multi-core CPU,<br>FPGA, commercial-<br>of-the-shelf moth-<br>erboard                                                                                      | Host OS: Windows<br>Target OS: Linux<br>based (QNX,<br>RedHat)<br>Application soft-<br>ware:<br>Matlab/Simulink,<br>RT-Lab suite con-<br>taining tools for<br>EMTP type and<br>Phasor analysis | Shared memory,<br>Gigabit Ethernet,<br>Dolphin network-<br>ing, IEC61850,<br>C37.118, DNP3,<br>FPGA-based analog<br>& digital I/O termi-<br>nals, supports third<br>party I/Os             | Simulink and in-<br>house tool boxes,<br>code (C/C++,<br>Matlab, Fortran)<br>wrapped with S-<br>function, discrete<br>Simulink solvers,<br>vendor specific<br>solvers such as<br>ARTEMIS-SSN | Real-time simula-<br>tion of power<br>electronics, power<br>systems, control and<br>automotive systems,<br>multi-domain<br>simulation, HIL<br>testing and simula-<br>tion | Multi-rate simula-<br>tion, ePHASORsim<br>transient stability<br>extension available,<br>EMT models can be<br>implemented on<br>FPGA cards [48],<br>multi-domain as it<br>supports all Sim-<br>ulink block-sets |

| HYPERSIM<br>[27], [29]                                            | CPUS are used with<br>SGI's NUMAlink<br>processors inter-<br>connect architec-<br>ture, can parallelize<br>up to 2500 cores,<br>FPGAS can be<br>interfaced | Host OS: Windows<br>Target OS: Linux<br>based<br>Application soft-<br>ware: Hypersim<br>software suite                                                                                         | Gigabit Ethernet,<br>IEC 61850, stand-<br>ard PCIe interface<br>with DSP based<br>A/D and D/As                                                                                             | GUI based compo-<br>nent library is<br>available through<br>which system<br>model is built, state-<br>space solution<br>method is used with<br>multiple integration<br>rules                 | Real-time simula-<br>tion of power<br>systems with power<br>electronics, control<br>systems, HIL<br>testing                                                               | Implementable in<br>eMEGAsim plat-<br>form for smaller<br>scale transmission<br>systems, automatic<br>task mapping to<br>available processors                                                                   |

| dSPACE [26]                                                       | CPU                                                                                                                                                        | Host OS: Windows<br>Target OS: QNX<br>ROS                                                                                                                                                      | Gigabit Ethernet,<br>PCIe based com-<br>munication with<br>other hardware and<br>I/O uses proprietary<br>dSPACE protocol,<br>IOCNET                                                        | Simulink, State-<br>flow, AUTOSAR,<br>C coded models                                                                                                                                         | Mainly used for<br>real-time control<br>and rapid prototyp-<br>ing for automotive<br>engineering, aero-<br>space, and industrial<br>control                               |                                                                                                                                                                                                                 |

| VTB [49]-<br>[52]                                                 | DSP cluster or multi-<br>core CPU/FPGA                                                                                                                     | Host OS: Windows<br>Target OS: Linux                                                                                                                                                           |                                                                                                                                                                                            | Modified resistive companion                                                                                                                                                                 | Power system                                                                                                                                                              | Multi-physics<br>possible                                                                                                                                                                                       |

| xPC Target<br>[53]                                                | CPU, FPGA                                                                                                                                                  | Host OS: Windows<br>Target OS: Opti-<br>mized Real-time<br>Kernel                                                                                                                              | Analog and Digital<br>I/O modules are<br>supported through<br>PMC, PCI, PCIe,<br>cPCI, and PC104<br>protocols, serial,<br>TCP/IP, UDP/IP,<br>CAN, J1939,<br>ARINC 429, and<br>MIL-STD-1553 | Simulink and<br>Stateflow for model<br>development,<br>Simulink Coder,<br>HDL coder, C                                                                                                       | Rapid prototyping,<br>real-time testing of<br>applications and<br>HIL simulation.                                                                                         | Multi-physics                                                                                                                                                                                                   |

| rtX from ADI<br>[54]                                              | CPU                                                                                                                                                        | Host OS: Windows<br>Target OS: QNX<br>RTOS<br>Application soft-<br>ware: AdvantageDE                                                                                                           | I/O interfacing<br>through PCI, PXI,<br>PCIe, PMC etc.                                                                                                                                     | GUI based Ad-<br>vantage DE can be<br>interfaced with<br>Simulink, System-<br>Build, C, Fortran,<br>ADEPT, ALTIA                                                                             | Power system<br>simulation for<br>avionics and mari-<br>time industries,<br>aircraft simulation,<br>shipboard simulation                                                  |                                                                                                                                                                                                                 |

| Typhoon<br>RTDs [55],<br>[56]                                     | FPGA                                                                                                                                                       | Host OS: Windows<br>Target OS: FPGA                                                                                                                                                            | FPGA based Ana-<br>log and Digital<br>I/Os, IEEE 1284C,<br>Ethernet RJ45                                                                                                                   | Typhoon schematic<br>editor, SpiceShuttle,<br>Matlab.                                                                                                                                        | Testing of power<br>electronics control-<br>ler                                                                                                                           |                                                                                                                                                                                                                 |

well as communication to the attached interface board. In a minimal system, a small-scale backplane passively connects the processor board to the interface board, which utilizes an

FPGA as a signal conditioning and coprocessing device for the analog and digital inputs and outputs. A pictorial view of such a system is shown in Fig. 6. With this new hardware implementation, the simulation of power electronics in the range of a few microseconds has been already demonstrated [50]. The key component of the new VTB feature is a C code generator. Currently, together with the DSP cluster introduced in this paper, it is possible to generate a real-time code for a PC cluster based on Linux OS.

#### **VI. CONCLUSION**

The main objective of this task force paper is to highlight the current state of the technologies used in the real-time simulation industry for power system applications. It has summarized the most salient features of real-time simulation platforms with applications related to power and energy systems. Although a number of real-time simulators are reported in Table 1, only a few of them are capable of simulating large systems. The remaining are either suitable for small systems or to serve as a real-time controller. Therefore, the characteristics of three main real-time simulators (i.e., RTDS, eMEGAsim, HYPERSIM, and VTB) are discussed in detail, whereas those of the rest of the simulators are listed in the summary table. Most of the real-time simulators are capable of interfacing external hardware to perform HIL tests and experiments.

Although designed for power systems applications, many of these real-time simulators are suitable for performing cosimulation using multirate/multiphysics simulation. With continuous customer support, these simulators can be used to accommodate any special needs of the consumers. In the next step, the task force will work on a similar paper that will summarize the applications of real-time simulators.

#### ACKNOWLEDGMENT

Task Force on Real-Time Simulation Technologies for Power Systems Analysis is with the Working Group on Modeling and Analysis of System Transients Using Digital Programs, General Systems Sub-Committee, T&D Committee, IEEE Power and Energy Society.

M. O. Faruque is with the Center for Advanced Power Systems, Department of Electrical and Computer Engineering, Florida State University, Tallahassee, FL 32310 USA (e-mail: faruque@caps.fsu.edu).

T. Strasser and G. Lauss are with the Electric Energy Systems–Energy Department, AIT Austrian Institute of Technology, Vienna 1220, Austria (e-mail: thomas.strasser@ait.ac.at; georg.lauss@ait.ac.at).

V. Jalili-Marandi and C. Dufour are with OPAL-RT Technologies Inc., Montreal, QC H3K 1G6, Canada, (e-mail: vahidj@opal-rt.com; christian.dufour@opal-rt.com)

P. Forsyth is with RTDS Technologies Inc., Winnipeg, MB R3T 2E1, Canada (e-mail: paf@rtds.com).

V. Dinavahi is with the University of Alberta, Edmonton, AB T6G 2R3, Canada (e-mail: dinavahi@ualberta.ca).

A. Monti is with the E.ON Energy Research Center, Institute for Automation of Complex Power Systems, RWTH Aachen University, Aachen 52062, Germany (e-mail: amonti@eonerc.rwth-aachen.de). P. Kotsampopoulos is with the School of Electrical and Computer Engineering, National Technical University of Athens, Athens 161 21, Greece (e-mail: kotsa@power.ece.ntua.gr).

J. A. Martinez is with the Departament d'Enginyeria Elèctrica, Universitat Politècnica de Catalunya, Barcelona 08034, Spain (e-mail: martinez@ee.upc.edu).

K. Strunz is with the Fakultät Elektrotechnik und Informatik, Technische Universität Berlin, Berlin 10587, Germany (e-mail: kai.strunz@tu-berlin.de).

M. Saeedifard is with the School of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, GA 30332 USA (e-mail: maryam@ece.gatech.edu).

X. Wang is with the Department of Electronics, Carleton University, Ottawa, ON K1S 5B6, Canada (e-mail: xiaoyuw@carleton.ca).

D. Shearer is with ABB Power Systems, Ludvika 771 80, Sweden (e-mail: david.shearer@se,abb.com).

M. Paolone is with the Swiss Federal Institute of Technology of Lausanne, Lausanne 1015, Switzerland (e-mail: mario.paolone@epfl.ch).

R. Brandl is with the Fraunhofer Institute for Wind Energy and Energy System Technology, Kassel 34119, Germany (e-mail: ron.brandl@iwes.fraun-hofer.de).

M. Matar is with the Centre of Applied Power Electronics, University of Toronto, Toronto, ON M5S 2J7, Canada, and also with the Department of Electrical Power and Machines, Ain Shams University, Cairo 11566, Egypt (e-mail: mahmatar@ieee.org).

A. Davoudi is with the Department of Electrical Engineering, University of Texas at Arlington, Arlington, TX 76019, USA (e-mail: davoudi@uta.edu).

R. Iravani is with the Centre of Applied Power Electronics, University of Toronto, Toronto, ON M5S 2J7, Canada (e-mail: iravani@ecf.utoronto.ca).

#### REFERENCES

- P. M. Menghal and A. J. Laxmi, "Real time simulation: Recent progress & challenges," in *Proc. Int. Conf. Power, Signals, Controls Comput. (EPSCICON)*, Thrissur, India, Jan. 2012, pp. 1–6.

- [2] T. Berry, A. R. Daniels, and R. W. Dunn, "Real time simulation of power system transient behaviour," in *Proc. 3rd Int. Conf. Power Syst. Monitor. Control*, London, U.K., Jun. 1991, pp. 122–127.

- [3] H. W. Dommel, "Digital computer solution of electromagnetic transients in single-and multiphase networks," *IEEE Trans. Power App. Syst.*, vol. PAS-88, no. 4, pp. 388–399, Apr. 1969.

- [4] H. W. Dommel, "Nonlinear and time-varying elements in digital simulation of electromagnetic transients," *IEEE Trans. Power App. Syst.*, vol. PAS-90, no. 4, pp. 2561–2567, Nov. 1971.

- [5] C. Dufour, J. Mahseredjian, and J. Bélanger, "A combined state-space nodal method for the simulation of power system transients," *IEEE Trans. Power Del.*, vol. 26, no. 2, pp. 928–935, Apr. 2011.

- [6] J. Mahseredjian, S. Dennetière, L. Dubé, B. Khodabakhchian, and L. Gérin-Lajoie, "On a new approach for the simulation of transients in power systems," *Electr. Power Syst. Res.*, vol. 77, no. 11, pp. 1514–1520, 2007.

- [7] M. Steurer, C. S. Edrington, M. Sloderbeck, W. Ren, and J. Langston, "A megawatt-scale power hardware-in-the-loop simulation setup for motor drives," *IEEE Trans. Ind. Electron.*, vol. 57, no. 4, pp. 1254–1260, Apr. 2010.

- [8] D. Jakominich, R. Krebs, D. Retzmann, and A. Kumar, "Real time digital power system simulator design considerations and relay performance evaluation," *IEEE Trans. Power Del.*, vol. 14, no. 3, pp. 773–781, Jul. 1999.

- [9] M. Kezunovic *et al.*, "Design, implementation and validation of a realtime digital simulator for protection relay testing," *IEEE Trans. Power Del.*, vol. 11, no. 1, pp. 158–164, Jan. 1996.

- [10] X. Wang and R. M. Mathur, "Real-time digital simulator of the electromagnetic transients of transmission lines with frequency dependence," *IEEE Trans. Power Del.*, vol. 4, no. 4, pp. 2249–2255, Oct. 1989.

- [11] A. Rubaai, A. R. Ofoli, and D. Cobbinah, "DSP-based real-time implementation of a hybrid H<sub>∞</sub> adaptive fuzzy tracking controller for servo-motor drives," *IEEE Trans. Ind. Appl.*, vol. 43, no. 2, pp. 476–484, Mar./Apr. 2007.

- [12] P. J. Throckmorton and L. Wozniak, "A generic DSP-based real-time simulator with application to hydrogenerator speed controller development," *IEEE Trans. Energy Convers.*, vol. 9, no. 2, pp. 238–242, Jun. 1994.

- [13] RTDS Technology Inc., Winnipeg, MB, Canada. (2014). Real-Time Simulation. [Online]. Available: http://www.rtds.com

- [14] P. G. McLaren, R. Kuffel, R. Wierckx, J. Giesbrecht, and L. Arendt, "A real time digital simulator for testing relays," *IEEE Trans. Power Del.*, vol. 7, no. 1, pp. 207–213, Jan. 1992.

- [15] M. Foley, Y. Chen, and A. Bose, "A real time power system simulation laboratory environment," *IEEE Trans. Power Syst.*, vol. 5, no. 4, pp. 1400–1406, Nov. 1990.

- [16] O. Devaux, L. Levacher, and O. Huet, "An advanced and powerful real-time digital transient network analyser," *IEEE Trans. Power Del.*, vol. 13, no. 2, pp. 421–426, Apr. 1998.

- [17] H. Taoka, I. Iyoda, H. Noguchi, N. Sato, and T. Nakazawa, "Real-time digital simulator for power system analysis on a hypercube computer," *IEEE Trans. Power Syst.*, vol. 7, no. 1, pp. 1–10, Feb. 1992.

- [18] I. Etxeberria-Otadui, V. Manzo, S. Bacha, and F. Baltes, "Generalized average modelling of FACTS for real time simulation in ARENE," in *Proc. 28th Annu. Conf. IEEE Ind. Electron. Soc. (IECON)*, vol. 2. Seville, Spain, Nov. 2002, pp. 864–869.

- [19] R. Krebs and O. Ruhle, "NETOMAC real-time simulator—A new generation of standard test modules for enhanced relay testing," in *Proc.* 8th IEE Int. Conf. Develop. Power Syst. Protection, vol. 2. Amsterdam, The Netherlands, Apr. 2004, pp. 669–674.

- [20] P. Lehn, J. Rittiger, and B. Kulicke, "Comparison of the ATP version of the EMTP and the NETOMAC program for simulation of HVDC systems," *IEEE Trans. Power Del.*, vol. 10, no. 4, pp. 2048–2053, Oct. 1995.

- [21] L.-F. Pak, M. O. Faruque, X. Nie, and V. Dinavahi, "A versatile clusterbased real-time digital simulator for power engineering research," *IEEE Trans. Power Syst.*, vol. 21, no. 2, pp. 455–465, May 2006.

- [22] S. Abourida, C. Dufour, J. Bélanger, G. Murere, N. Lechevin, and B. Yu, "Real-time PC-based simulator of electric systems and drives," in *Proc. 17th IEEE Conf. Expo. Appl. Power Electron. (APEC)*, vol. 1. Dallas, TX, USA, Mar. 2002, pp. 433–438.

- [23] C. Dufour and J. Bélanger, "A PC-based real-time parallel simulator of electric systems and drives," in *Proc. Int. Conf. Parallel Comput. Elect. Eng. (PARELEC)*, vol. 1. Dresden, Germany, Sep. 2004, pp. 105–113.

- [24] C. Dufour and J. Bélanger, "A real-time simulator for doubly fed induction generator based wind turbine applications," in *Proc. IEEE 35th Annu. Power Electron. Specialists Conf. (PESC)*, vol. 5. Aachen, Germany, Jun. 2004, pp. 3597–3603.

- [25] M. O. Faruque and V. Dinavahi, "An advanced PC-cluster based realtime simulator for power electronics and drives," in *Proc. IEEE Int. Symp. Ind. Electron. (ISIE)*, vol. 3. Montreal, QC, Canada, Jul. 2006, pp. 2579–2584.

- [26] dSPACE GmbH, Paderborn, Germany. (2014). dSPACE Product Manual. [Online]. Available: http://www.dspace.com

- [27] C. Larose et al., "A fully digital real-time power system simulator based on PC-cluster," J. Math. Comput. Simul., vol. 63, nos. 3–5, pp. 151–159, 2003.

- [28] G. Sybille and P. Giroux, "Simulation of FACTS controllers using the MATLAB power system blockset and hypersim real-time simulator," in *Proc. IEEE Power Eng. Soc. Winter Meeting*, vol. 1. New York, NY, USA, Jan. 2002, pp. 488–491.

- [29] F. Guay, J. Cardinal, E. Lemiex, and S. Guerette, "Digital real-time simulator using IEC 61850 communication for testing devices," in *Proc. CIGRE Canada Conf.*, Montreal, QC, Canada, Sep. 2012.

- [30] M. Matar and R. Iravani, "Massively parallel implementation of AC machine models for FPGA-based real-time simulation of electromagnetic transients," *IEEE Trans. Power Del.*, vol. 26, no. 2, pp. 830–840, Apr. 2011.

- [31] R. Razzaghi, M. Paolone, and F. Rachidi, "A general purpose FPGA-based real-time simulator for power systems applications," in *Proc. 4th IEEE Eur. Innov. Smart Grid Technol. Conf. (ISGT)*, Copenhagen, Denmark, Oct. 2013, pp. 1–5.

- [32] R. Razzaghi, C. Foti, M. Paolone, and F. Rachidi, "A novel method for the optimal parameter selection of discrete-time switch model," in *Proc. 10th Int. Conf. Power Syst. Transients (IPST)*, Vancouver, BC, Canada, Jul. 2013.

- [33] Y. Chen and V. Dinavahi, "FPGA-based real-time EMTP," IEEE Trans. Power Del., vol. 24, no. 2, pp. 892–902, Apr. 2009.

- [34] Y. Chen and V. Dinavahi, "Multi-FPGA digital hardware design for detailed large-scale real-time electromagnetic transient simulation of power systems," *IET Generat., Transmiss., Distrib.*, vol. 7, no. 5, pp. 451–463, May 2013.

- [35] G. G. Parma and V. Dinavahi, "Real-time digital hardware simulation of power electronics and drives," *IEEE Trans. Power Del.*, vol. 22, no. 2, pp. 1235–1246, Apr. 2007.

- [36] RTDS Technology Inc., Winnipeg, MB, Canada. (2014). RTDS Website. [Online]. Available: http://www.rtds.com

- [37] R. Meka, M. Sloderbeck, M. O. Faruque, J. Langston, M. Steurer, and L. S. DeBrunner, "FPGA model of a high-frequency power electronic converter in an RTDS power system co-simulation," in *Proc. IEEE Electr. Ship Technol. Symp. (ESTS)*, Arlington, VA, USA, Apr. 2013, pp. 71–75.

- [38] OPAL-RT Technology Inc., Montreal, QC, Canada. (2014). OPAL-RT Website, [Online]. Available: http://opal-rt.com

- [39] Y. Inaba, S. Cense, T. O. Bachir, H. Yamashita, and C. Dufour, "A dual high-speed PMSM motor drive emulator with finite element analysis on FPGA chip with full fault testing capability," in *Proc. 14th Eur. Conf. Power Electron. Appl. (EPE)*, Birmingham, U.K., Aug./Sep. 2011, pp. 1–10.

- [40] C. Dufour, S. Cense, and J. Bélanger, "FPGA-based switched reluctance motor drive and DC-DC converter models for high-bandwidth HIL real-time simulator," in *Proc. 15th Eur. Conf. Power Electron. Appl.* (*EPE*), Lille, France, Sep. 2013, pp. 1–8.

- [41] C. Dufour, V. Jalili-Marandi, J. Bélanger, and L. Snider, "Power system simulation algorithms for parallel computer architectures," in *Proc. IEEE Power Energy Soc. General Meeting*, San Diego, CA, USA, Jul. 2012, pp. 1–6.

- [42] C. Dufour, J. Mahseredjian, J. Bélanger, and J. L. Naredo, "An advanced real-time electro-magnetic simulator for power systems with a simultaneous state-space nodal solver," in *Proc. IEEE/PES Transmiss. Distrib. Conf. Expo., Latin Amer. (T&D-LA)*, São Paulo, Brazil, Nov. 2010, pp. 349–358.

- [43] V. Jalili-Marandi, Z. Zhou, and V. Dinavahi, "Large-scale transient stability simulation of electrical power systems on parallel GPUs," *IEEE Trans. Parallel Distrib. Syst.*, vol. 23, no. 7, pp. 1255–1266, Jul. 2012.

- [44] M. O. Faruque, V. Dinavahi, and W. Xu, "Algorithms for the accounting of multiple switching events in digital simulation of power-electronic systems," *IEEE Trans. Power Del.*, vol. 20, no. 2, pp. 1157–1167, Apr. 2005.

- [45] K. Strunz and E. Carlson, "Nested fast and simultaneous solution for time-domain simulation of integrative power-electric and electronic systems," *IEEE Trans. Power Del.*, vol. 22, no. 1, pp. 277–287, Jan. 2007.

- [46] M. O. Faruque and V. Dinavahi, "Hardware-in-the-loop simulation of power electronic systems using adaptive discretization," *IEEE Trans. Ind. Electron.*, vol. 57, no. 4, pp. 1146–1158, Apr. 2010.

- [47] K. Strunz, "Flexible numerical integration for efficient representation of switching in real time electromagnetic transients simulation," *IEEE Trans. Power Del.*, vol. 19, no. 3, pp. 1276–1283, Jul. 2004.

- [48] C. Dufour, S. Cense, T. Ould-Bachir, L.-A. Grégoire, and J. Bélanger, "General-purpose reconfigurable low-latency electric circuit and motor drive solver on FPGA," in *Proc. 38th Annu. Conf. IEEE Ind. Electron. Soc. (IECON)*, Montreal, QC, Canada, Oct. 2012, pp. 3073–3081.

- [49] B. Lu, X. Wu, H. Figueroa, and A. Monti, "A low-cost real-time hardwarein-the-loop testing approach of power electronics controls," *IEEE Trans. Ind. Electron.*, vol. 54, no. 2, pp. 919–931, Apr. 2007.

- [50] F. Adler, A. Benigni, H. Stagge, A. Monti, and R. W. De Doncker, "A new versatile hardware platform for digital real-time simulation: Verification and evaluation," in *Proc. IEEE 13th Workshop Control Model. Power Electron. (COMPEL)*, Kyoto, Japan, Jun. 2012, pp. 1–8.

- [51] A. Benigni, "Latency exploitation for parallelization of power system simulation," Ph.D. dissertation, E.ON Energy Res. Center, Aachen, Germany, 2013.

- [52] M. Marin, A. Benigni, H. Lakhdar, A. Monti, and P. J. Collins, "Towards the implementation of a parallel real-time simulator for DSP cluster," in *Proc. Summer Simulation Multi-Conf.-Grand Challenges Model. Simulation (GCMS)*, Genoa, Italy, Jul. 2012.

- [53] MathWorks Inc., Natick, MA, USA. (2014). xPC Target. [Online]. Available: http://www.mathworks.com

- [54] Applied Dynamics International Inc., Arbor, MI, USA. (2014). ADI rtX RTS. [Online]. Available: http://www.adi.com

- [55] Tyhoon HIL GmbH, Zürich, Switzerland. (2014). Typhoon HIL RTS. [Online]. Available: http://www.typhoon-hil.com

- [56] D. Majstorovic, I. Celanovic, N. D. Teslic, N. Celanovic, and V. A. Katic, "Ultralow-latency hardware-in-the-loop platform for rapid validation of power electronics designs," *IEEE Trans. Ind. Electron.*, vol. 58, no. 10, pp. 4708–4716, Oct. 2011.

**MD OMAR FARUQUE** (S'03–M'08–SM'14) received the Ph.D. degree from The University of Alberta, Edmonton, AB, Canada, in 2008.

He is with the Center for Advanced Power Systems and the Department of Electrical and Computer Engineering, Florida State University, Tallahassee, FL, USA. His current research interests include real-time simulation, renewable energy integration, all-electric ship power system, and real-time monitoring of smart grid.

Dr. Faruque is the Chair of the IEEE Power and Energy Society Task Force on Real-Time Simulation of Power and Energy Systems.

**THOMAS STRASSER** (M'09–SM'13) received the Ph.D. degree in mechanical engineering with a focus on automation and control theory from the Vienna University of Technology, Vienna, Austria, in 2003.

He is currently a Senior Scientist with the AIT Austrian Institute of Technology, Vienna, where he is involved in smart grids with a focus on power utility automation and real-time systems.

**GEORG LAUSS** (M'10) received the M.S. degree in mechatronics from the Johannes Kepler University of Linz, Linz, Austria, in 2006, and the Degree in scientific thesis from the Eidgenössischen Technischen Hochschule of Zürich, Zürich, Switzerland, and the Université de Paris VI, Paris, France.

He is currently a Researcher with the AIT Austrian Institute of Technology, Vienna, Austria.

**VAHID JALILI-MARANDI** received the Ph.D. degree in electrical engineering with a focus on transient stability simulation for large-scale power systems on PC clusters and GPUs from the University of Alberta, Edmonton, AB, Canada, in 2010.

He is currently with OPAL-RT Technologies Inc., Montreal, QC, Canada, where he is involved in real-time simulation for power systems.

**PAUL FORSYTH** received the B.Sc. degree in electrical engineering with a focus on electrical power systems from the University of Manitoba, Winnipeg, MB, Canada, in 1988.

He was with ABB, Baden, Switzerland, and Haefely-Trench, Basel, Switzerland, in Europe until he joined RTDS Technologies Inc., Winnipeg, in 1995.

**CHRISTIAN DUFOUR** received the Ph.D. degree from Laval University, Quebec, QC, Canada, in 2000.

He has been with OPAL-RT Technologies Inc., Montreal, QC, Canada, since 1999, where he is currently a Lead Researcher in power systems and motor drive simulation software. He was involved in the development of Hydro-Quebec's HYPERSIM real-time simulator, and MathWorks' Sim-PowerSystems blockset.

**VENKATA DINAVAHI** (S'94–M'00–SM'08) received the Ph.D. degree from the University of Toronto, Toronto, ON, Canada, in 2000.

He is currently a Professor with the Department of Electrical and Computer Engineering, University of Alberta, Edmonton, AB, Canada. His current research interests include real-time simulation of power systems, large-scale system simulation, and parallel and distributed computing.

**ANTONELLO MONTI** (M'94–SM'02) received the M.S. and Ph.D. degrees in electrical engineering from the Politecnico di Milano, Milan, Italy, in 1989 and 1994, respectively.

He is currently the Director of the Institute for Automation of Complex Power Systems with the E.ON Energy Research Center, RWTH Aachen University, Aachen, Germany.

**PANOS KOTSAMPOPOULOS** (S'12) received the Diploma degree in electrical and computer engineering from the National Technical University of Athens (NTUA), Athens, Greece, in 2010.

He is currently a Researcher with the Electric Power Division, NTUA, where he is involved in distributed energy resources with a focus on real-time simulation.

**JUAN A. MARTINEZ** (M'83–SM'12) is currently a Professor Titular with the Department d'Enginyeria Elèctrica, Universitat Politècnica de Catalunya, Barcelona, Spain. His current research interests include transmission and distribution, power system analysis, and electromagnetic transients program applications.

**KAI STRUNZ** (A'00–M'02) received the Dr.Ing. (*summa cum laude*) degree from Saarland University, Saarbrücken, Germany, in 2001.

He has been a Professor of Sustainable Electric Networks and Sources of Energy with the Technische Universität Berlin, Berlin, Germany, since 2007.

**MARYAM SAEEDIFARD** (SM'11) received the Ph.D. degree in electrical engineering from the University of Toronto, Toronto, ON, Canada, in 2008. She is currently an Assistant Professor with the School of Electrical and

Computer Engineering, Georgia Institute of Technology, Atlanta, GA, USA.

**XIAOYU WANG** (M'08–SM'13) received the Ph.D. degree from the University of Alberta, Edmonton, AB, Canada, in 2008.

He is currently an Assistant Professor with the Department of Electronics, Carleton University, Ottawa, ON, Canada. His current research interests include integration of distributed energy resources.

**DAVID SHEARER** received the B.S. degree in electrical and electronic engineering from the Faculty of Engineering, University of Auckland, Auckland, New Zealand, in 1984.

He is currently a lead Engineer with ABB Power Systems, Ludvika, Sweden.

**MARIO PAOLONE** (M'07–SM'10) received the Ph.D. degree in electrical engineering with a focus on power systems transients from the University of Bologna, Bologna, Italy, in 2002.

He is currently an Associate Professor with the Swiss Federal Institute of Technology, Lausanne, Switzerland, where he is also the EOS Holding Chair of the Distributed Electrical Systems Laboratory. His current research interests include real-time monitoring, operation, protections, and transients of power systems. **RON BRANDL** received the M.S. degree from the University of Stuttgart, Stuttgart, Germany, in 2010.

He was an Electrical Engineer with the University of Stuttgart. He is currently with Fraunhofer Institute for Wind Energy and Energy System Technology, Kassel, Germany, where he is involved in power system control and dynamics and specializes on the application of HIL systems.

**MAHMOUD MATAR** (S'00–M'10–SM'12) received the B.Sc. and M.Sc. degrees from Ain Shams University, Cairo, Egypt, in 2001 and 2004, respectively, and the Ph.D. degree from the University of Toronto, Toronto, ON, Canada, in 2009, all in electrical engineering.

His current research interests include modeling, real-time and faster-thanreal-time simulation of power systems and power electronics, and power systems dynamics and control. **ALI DAVOUDI** (M'10) received the Ph.D. degree in electrical and computer engineering from the University of Illinois at Urbana-Champaign, Champaign, IL, USA, in 2010.

He is currently an Assistant Professor with the Department of Electrical Engineering, University of Texas at Arlington, Arlington, TX, USA.

**REZA IRAVANI** (M'85–SM'00–F'03) received the B.Sc. degree from Tehran Polytechnic University, Tehran, Iran, in 1976, and the M.Sc. and Ph.D. degrees from the University of Manitoba, Winnipeg, MB, Canada, in 1981 and 1985, respectively, all in electrical engineering.

He is currently a Professor with the Department of Electrical and Computer Engineering, University of Toronto, Toronto, ON, Canada.