National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

#### **NOTICE**

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

La qualité de cette "dicroforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

Bibliothèque nationale du Canada

Canadian Theses Service Service des thèses canadiennes

Ottawa. Canada K1A 0N4

The author has granted an irrevocable nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-55487-8

## The University of Alberta

Development

of a

Digital Correlator

for

Aperture Synthesis

by Pavid R. Karpa

A Thesis

submitted to the Faculty of Graduate Studies and Research

in partial fulfilment of the requirements for the Degree of

Master of Science

Department of Electrical Engineering

Edmonton, Alberta Fall of 1989

## University of Alberta Release Form

Name of Author:

David R. Karpa

Title of Thesis:

Development of a Digital Correlator for

Aperture Synthesis

Degree:

Master of Science

Year this Degree Granted:

1989

Permission is hereby granted to The University of Alberta Library to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly or scientific research purposes only.

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or reproduced without the author's written permission.

c/o D.R.A.O.

Box 248,

Penticton, B.C.

V2A-6K3

September 11, 1989

## University of Alberta

## Faculty of Graduate Studies and Research

The undersigned certify that they have read,

and recommend to the

Faculty of Graduate Studies and Research

for acceptance, a thesis entitled

Development of a Digital Correlator for Aperture Synthesis

ubmitted by

David R. Karpa

in partial fulfilment of the requirements for the degree of Master of Science.

(Supervisor)

(Supervisor)

Date: 04.9,1969

#### Abstract

The Dominion Radio Astrophysical Observatory is expanding and upgrading its synthesis telescope. The existing analog continuum back-end is being replaced by a wider-bandwidth, high-resolution digital correlator.

This thesis describes the development of this digital system. The correlator will support the wider 30 MHz bandwidth, form the cross-polarization products required for polarimetry, and correlate all possible antenna-pairs for 8 dishes. Each of the 1184 correlator channels multiplies two 4-bit numbers at 20 MSPS and can accumulate for several minutes. The 14-level (4-bit) quantization results in a very high correlator efficiency (0.986).

The DSP design uses a parallel-pipelined architecture to maintain high data rates throughout the system (10 billion multiply-accumulate operations per second). The correlation units are modular so the performance of the system scales linearly with size.

The system is designed to require minimal computer control; time-critical and low-level tasks are hidden from the computer. Built-in system test features permit on-line diagnostics for monitoring the performance of the array.

### Acknowledgements

The people at the Dominion Radio Astrophysical Observatory have made a hardened and a many and a non-me; their kindness and encouragement will never be forgotted to the part to be commended for maintaining a challenging and friendly research environment.

The advice from my supervisors, Tom Landecker and Peter Dewdney at the NRC, as well as David Routledge and Fred Vaneldik at the U of A, kept me off most of the dead-end streets. I am just beginning to realise the importance of the administrative skills they demonstrated throughout the project.

The coffee room was where the most important design decisions were discussed: Gary Hovey's engineering expertise was appreciated at every stage of the design; Chris Purton's passion for the science is infectious — a powerful motivator; Everet Sheehan has an amazing tolerance for fickle engineers.

Thank you Elizabeth Landecker for officiating at the arrival ceremonies for Jared and Alanna.

I am grateful for the almost endless financial support of the Herzberg Institute of Astrophysics, The Alberta Heritage Foundation and the Low-Noise Amplifier Group at the University of Alberta. Without them, this project would not have been.

Most of all, I owe a lifelong debt of gratitude to my friend and wife, Janiese, for her steadfast love and support.

# **Contents**

| 1 | In t | he beg | ginning                                                | 8  |

|---|------|--------|--------------------------------------------------------|----|

|   | 1.1  | From   | Babylon to British Columbia                            | 8  |

|   | 1.2  | A Rev  | riew of Interferometry                                 | 10 |

|   |      | 1.2.1  | The Monochromatic Interferometer                       | 10 |

|   |      | 1.2.2  | The Bandwidth Pattern                                  | 14 |

|   |      | 1.2.3  | The non-isotropic interferometer: tracking the source. | 15 |

|   | 1.3  | The D  | RAO Synthesis Telescope                                | 23 |

|   | 1.4  | The N  | ew 1420 MHz Continuum Correlator                       | 26 |

|   |      | 1.4.1  | The Expanding Array                                    | 27 |

|   |      | 1.4.2  | Improving the Performance Parameters                   | 28 |

|   |      | 1.4.3  | The Design Baseline                                    | 33 |

|   |      | 1.4.4  | Project Progress Overview                              | 34 |

| 2 | The  | Corre  | elator                                                 | 36 |

|   | 2.1  | The C  | hannel Design                                          | 38 |

|   |      | 2.1.1  | The Channel Multiplier                                 | 40 |

|   |      |        |                                                        |    |

| CONTENTS | 2 |

|----------|---|

|----------|---|

|   |     | 2.1.2    | The Channel Accumulator                    | 41 |

|---|-----|----------|--------------------------------------------|----|

|   |     | 2.1.3    | Channel Control                            | 42 |

|   |     | 2.1.4    | Correlator Channel Summary                 | 45 |

|   | 2.2 | The C    | orrelator Card                             | 47 |

|   |     | 2.2.1    | The Polarized Interferometer               | 47 |

|   |     | 2.2.2    | The Physical Design of the Correlator Card | 50 |

|   |     | 2.2.3    | Correlator Card Summary                    | 55 |

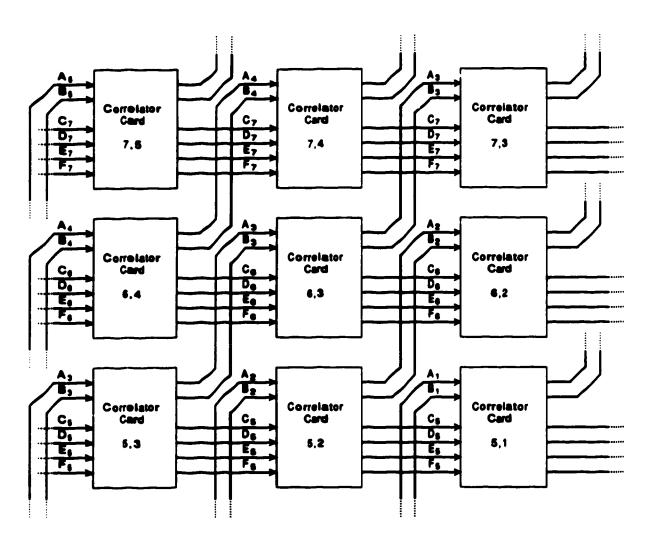

|   | 2.3 | Correl   | ation System Topology                      | 55 |

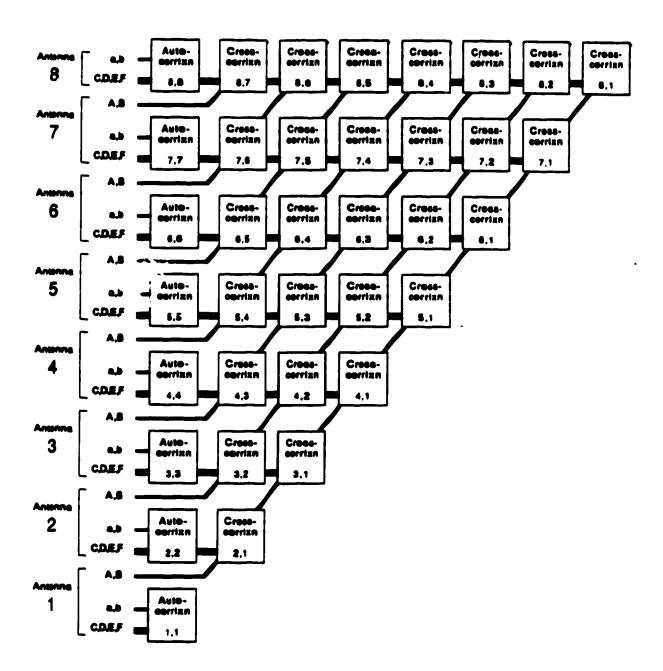

|   |     | 2.3.1    | The Correlation Matrix                     | 55 |

|   |     | 2.3.2    | Autocorrelation                            | 57 |

|   | 2.4 | Correla  | ation System Summary                       | 67 |

| 3 | Cor | ntrollin | g the Correlator System                    | 70 |

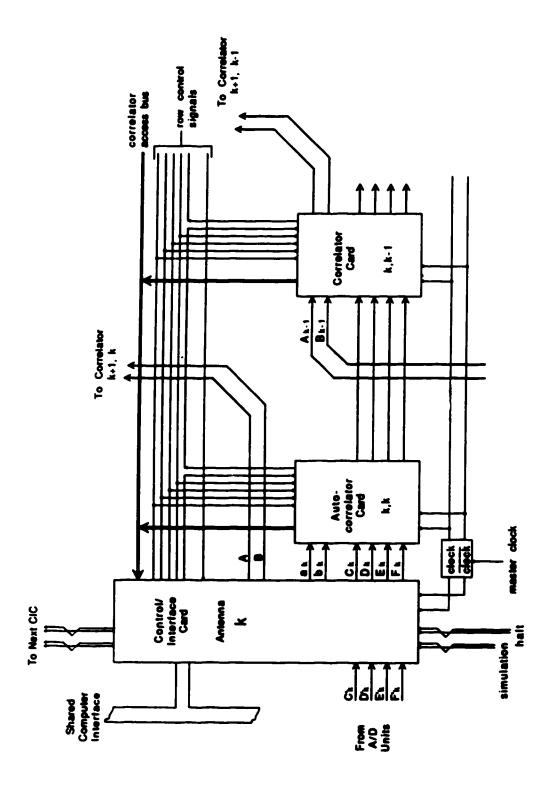

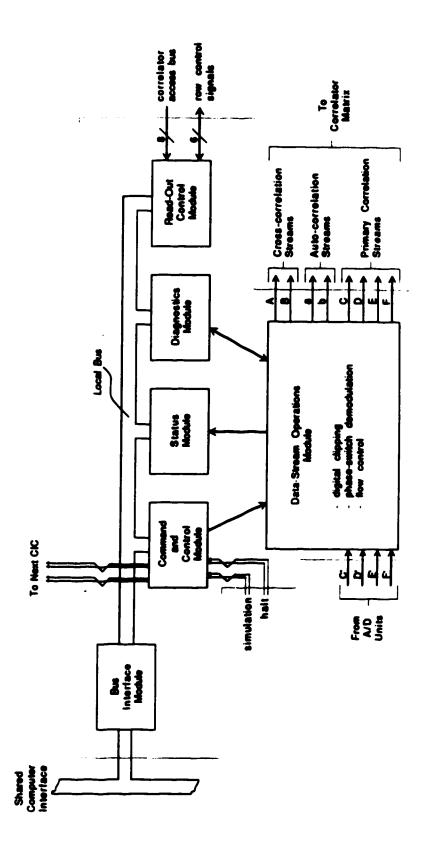

|   | 3.1 | Develo   | ping the Control/Interface Card            | 71 |

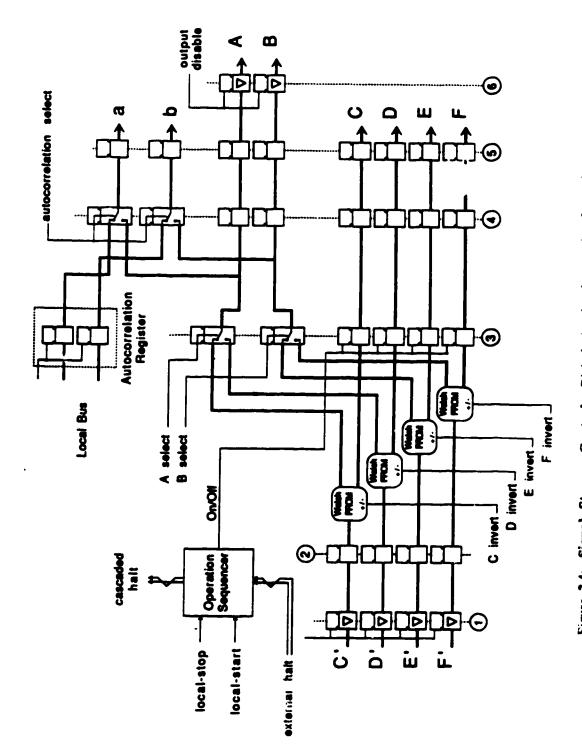

|   | 3.2 | Signal   | Stream Control                             | 77 |

|   | 3.3 | Result   | Read-Out Control                           | 81 |

|   | 3.4 | Hardwa   | are Testing and Diagnostic Features        | 85 |

|   |     | 3.4.1    | Diagnostic Data RAM                        | 85 |

|   |     | 3.4.2    | Correlation Interval Timer                 | 90 |

|   |     | 3.4.3    | Bench Top Testing                          | 93 |

|   | 3.5 | Compu    | ter Control of the DSP System              | 96 |

|   |     | 3.5.1    | The Computer Access Bus                    | 96 |

| CONTENTS | 3 |

|----------|---|

|          |   |

|   |      | 3.5.2   | The CIC's Internal Address Map 99      |

|---|------|---------|----------------------------------------|

|   |      | 3.5.3   | The Control Registers                  |

|   |      | 3.5.4   | The Status Registers                   |

|   |      | 3.5.5   | Packaging the DSP System               |

|   | 3.6  | Summ    | nary of the Correlation Control Design |

| 4 | Sign | nal Pro | ocessing and Data Acquisition 114      |

|   | 4.1  | Analo   | g Signal Processing                    |

|   |      | 4.1.1   | Continuum IF Signal Processing         |

|   | 4.2  | Analo   | g-to-Digital Conversion                |

|   |      | 4.2.1   | Thermal Considerations                 |

|   |      | 4.2.2   | Performance Testing                    |

|   | 4.3  | A/D I   | Development Summary                    |

| 5 | Pro  | ject S  | ummary 124                             |

|   | 5.1  | The D   | Development Stages                     |

|   |      | 5.1.1   | Version 1: the Lash-Ups                |

|   |      | 5.1.2   | Version 2: the Bench Models            |

|   |      | 5.1.3   | Version 3: the Production Models 126   |

|   | 5.2  | The P   | Present Status 197                     |

# List of Figures

| 1.1  | An Interferometer Pair                     | 11 |

|------|--------------------------------------------|----|

| 1.2  | The Isotropic Interferometer Pair          | 11 |

| 1.3  | The Quadrature Channel Interferometer Pair | 13 |

| 1.4  | A Rectangular Frequency Response           | 14 |

| 1.5  | Pointing the Delay-Beam                    | 17 |

| 1.6  | Phase Path Equalization                    | 18 |

| 1.7  | Phase Switching for 8 Antennas             | 22 |

| 1.8  | The DRAO Synthesis Telescope               | 24 |

| 1.9  | Observed Frequencies at 1.42 GHz           | 25 |

| 1.10 | Correlation Frequency Options              | 29 |

| 1.11 | Worst-Case Delay Beams                     | 30 |

| 1.12 | Correlator Efficiency                      | 32 |

| 2.1  | Digital Correlation                        | 37 |

| 2.2  | A Correlator Channel                       | 39 |

| 2.3  | Channel Control Signals                    | 13 |

| LIST OF FIGURES | 5 |

|-----------------|---|

|-----------------|---|

| 2.4  | The Complex-Value Correlator                     | 48 |

|------|--------------------------------------------------|----|

| 2.5  | The Digital Correlator Card                      | 51 |

| 2.6  | Correlator Input Design                          | 52 |

| 2.7  | Lata-Pessing Design                              | 54 |

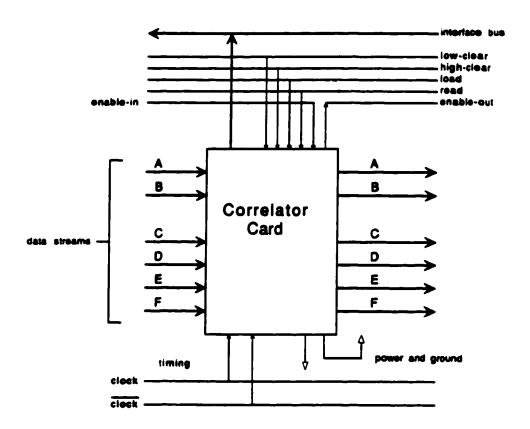

| 2.8  | Correlator Card I/O Block Diagram                | 56 |

| 2.9  | Correlator Interconnections                      | 58 |

| 2.10 | Autocorrelation Points in the Matrix             | 59 |

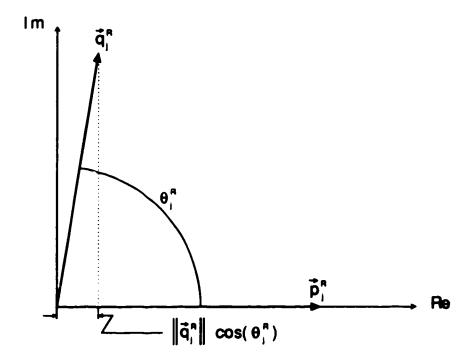

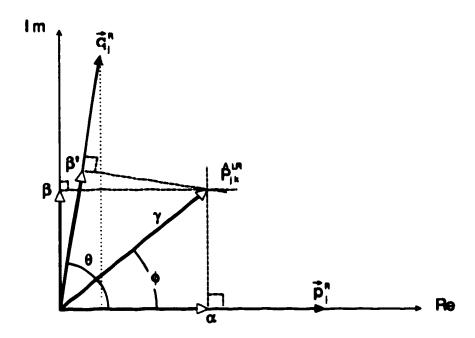

| 2.11 | Phasor Signal Representation                     | 64 |

| 2.12 | Correlation as Function-Space Projection         | 65 |

| 3.1  | Location of the Control/Interface Card           | 72 |

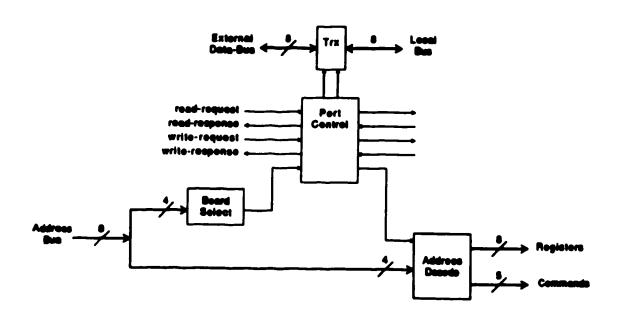

| 3.2  | Internal Structure of the Control/Interface Card | 73 |

| 3.3  | The Control/Interface Card                       | 76 |

| 3.4  | Signal Stream Control                            | 79 |

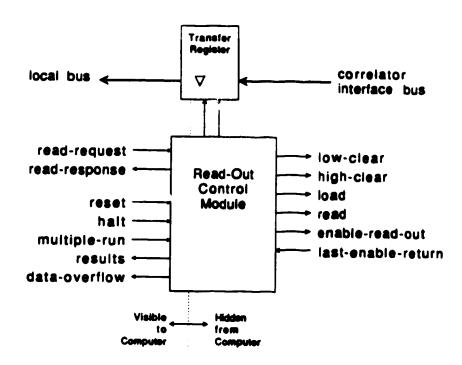

| 3.5  | Read-Out Control                                 | 81 |

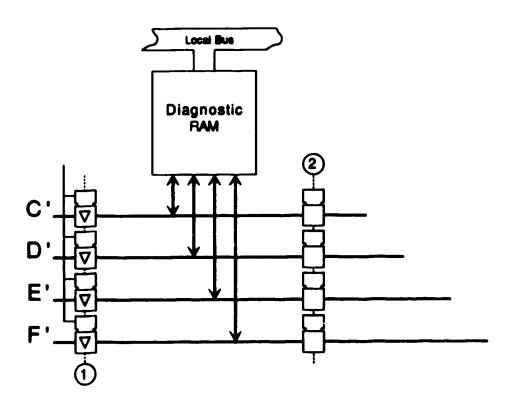

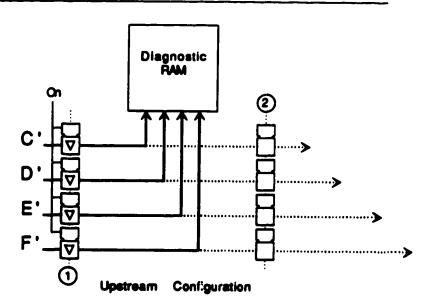

| 3.6  | Diagnostic Data-Stream RAM                       | 86 |

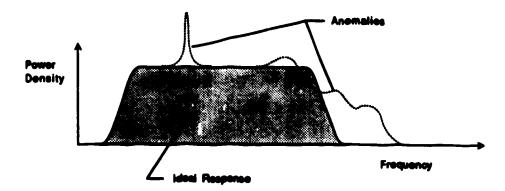

| 3.7  | Signal Path Anomolies                            | 89 |

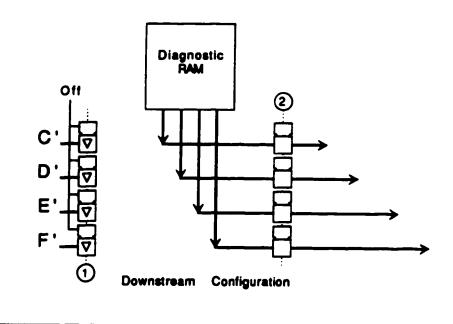

| 3.8  | Diagnostic Configurations                        | 91 |

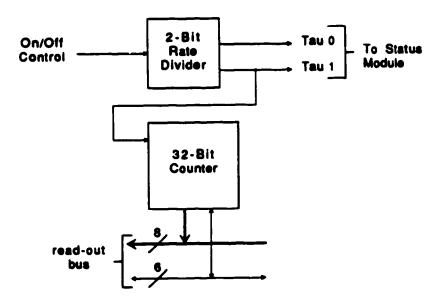

| 3.9  | Correlation Interval Timer                       | 92 |

| 3.10 | Development Features                             | 94 |

| 3.11 | Bench-Test Configuration                         | 95 |

| 3 12 | The Computer Access Bus                          | 97 |

| LIST OF FIGURES                          | 6 |

|------------------------------------------|---|

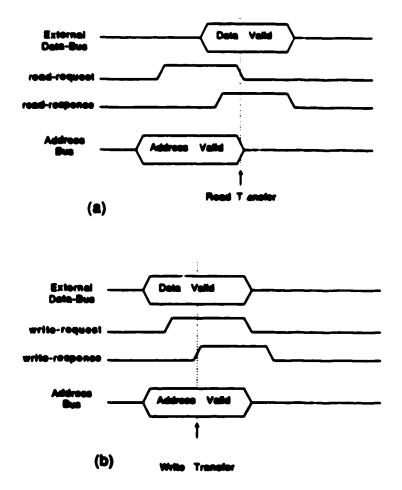

| 3.13 Bus Transaction Protocol            | 3 |

| 3.14 The Prototype System Chassis        | 3 |

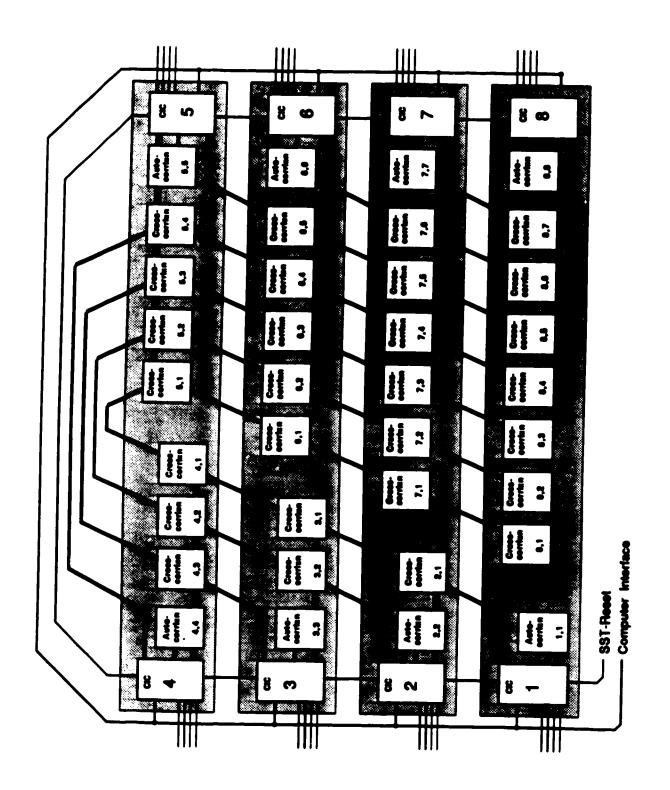

| 3.15 The Packaged Correlation Matrix 109 | • |

| 3.16 The Mother Board                    | ) |

| 3.17 The Baseline Configuration          | l |

| 4.1 The Continuum IF Signal Chain        | 3 |

| 4.2 The A/D Circuit Groups               | 3 |

| 4.3 The A/D Version-3 Prototypes         | ) |

| 4.4 The Crosstalk Test Configuration     | Į |

# List of Tables

| 2.1 | Correlation Matrix Signal Inventory |

|-----|-------------------------------------|

| 3.1 | CIC Command Map                     |

| 3.2 | CIC Register Map                    |

| 3.3 | Control 1 Flags                     |

| 3.4 | Control 2 Flags                     |

| 3.5 | Status 1 Flags                      |

| 3.6 | Status 2 Flags                      |

# Chapter 1

# In the beginning...

# 1.1 From Babylon to British Columbia

Astronomy is often cited as being one of Man's oldest scientific endeavors. The earliest records are those of Babylonians who meticulously charted the movements of the heavenly bodies. While one might question whether the ancients were sorcerers or scientists, their efforts have formed the rich heritage of the science. The quest to see and understand the heavens is one that is certainly thousands of years old. Through the years, this quest has been aided by technological advances — indeed, astronomy has often been the motivation for such advances. Recent history has been characterized by a rapid growth in technology and the sciences so that today scientists focus on specific aspects of astronomy such as astrometry, astrophysics and interstellar chemistry. Naturally, the partnership between astronomy and technology continues to be a fruitful one as new techniques allow us to see and understand the old universe in new ways.

One such technique is radio astronomy. Processes and objects unobserved prior to 1932, when Karl Jansky [Jan33] detected radio emmisions from the galactic plane, now form a vital part of our view of the universe. By 1950, radio astronomy was steadily gaining momentum as more and more scientists realised its significance. At first, better meant bigger; the trend was towards

building larger and larger antennas but by 1964 this was giving way to a technique called aperture synthesis.

Aperture synthesis uses a group of small antennas to mimic the performance of an impossibly large antenna. By operating antennas in concert, we are now able to observe features that would be unseen with a single antenna unless it were miles in extent. The synthesis technique allows astronomers to view extraterrestrial radio phenomena with resolution comparable to (and in some cases surpassing) the performance of optical instruments.

Today, our appetite for understanding the universe is as healthy as it ever was. Often communities of specialists, both scientific and technical, combine their skills and intelligence for greater effectiveness. The Dominion Radio Astrophysical Observatory (DRAO) in British Columbia is evidence of this combined effort. Operating under the National Research Council's Herzberg Institute of Astrophysics, its mandate is to provide the scientific community with high-calibre facilities for radio astronomy. Besides operating and maintaining several radio telescopes, the scientists and engineers at the DRAO are actively involved in developing the future tools for radio astronomy. One aspect of this lies in applying new technology to the design of new instruments and the refurbishment of existing ones. The observatory interacts with the scientific community to the extent that it often enlists the cooperation of universities when challenging problems arise.

This thesis describes the design of a signal processing system for the DRAO aperture synthesis telescope. The system design involved selecting a strategy based on current technology as well proving its feasibility by building and testing representative system components. The system described herein will improve on an existing signal processor which is unable to meet the growing demands of the instrument.

The following chapters will address how the system demands were met and why certain techniques were chosen. To provide a foundation for such discussions, the remainder of this chapter will focus on three areas: first, a review of the basic principles of aperture synthesis relevant to this project and to the synthesis telescope at the DRAO<sup>1</sup>; second, a brief description of

<sup>&</sup>lt;sup>1</sup>Readers wanting a thorough treatment of the theory and practice of interferome-

DRAO's synthesis telescope with emphasis on the aspects relating to this project; third, an introduction to the performance requirements of the new signal processing system.

# 1.2 A Review of Interferometry

This section will review some basic properties of interferometry, including instrumental considerations such as system bandwidth and tracking, and will close with a description of how the interferometer is used for polarimetry and aperture synthesis.

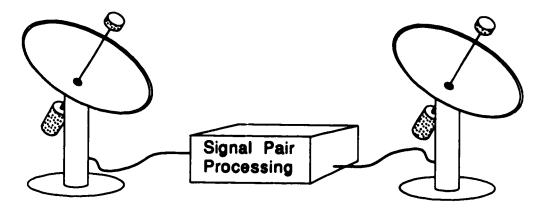

Interferometry is a technique where the signals from two antennas are used to generate a multiple fan-beam response—an interference pattern. Typically, the signals are multiplied by each other and integrated for long periods of time. Since each signal has units of volts, their product can be interpreted as power. The response of the interferometer pair will be referred to as the *cross-power*, generally a complex number. Figure 1.1 shows an interferometer pair.

#### 1.2.1 The Monochromatic Interferometer

The interferometer behavior is readily understood by considering the scenario depicted in Figure 1.2. Suppose, for now, antennas 1 and 2 are identical and isotropic.

Consider the effect of a monochromatic radio source of wavelength  $\lambda$  located at infinity in the direction  $\hat{k}$  (a unit vector). Since both antennas are equally sensitive in all directions, the response pattern is azimuthally symmetric about the axis defined by the baseline vector  $\vec{B}_{\lambda}$ . The subscript  $\lambda$  will indicate that  $\vec{B}_{\lambda}$  is measured in units of the source's wavelength.

First consider the case where the source lies on the meridian plane (the

try and synthesis should look to "Interferometry and Synthesis in Radio Astronomy" by Thompson, Moran and Swenson [TMS86]

Figure 1.1: An Interferometer Pair: The product of two antenna signals is the cross-power. The pair's response is an interference pattern caused by the relative phase delay of signals arriving at the two antennas. The cross-power result can be negative or positive.

Figure 1.2: The Isotropic Interferometer Pair: The isotropic antennas respond uniformly to signals from any direction. The hypothetical transmitter is located at infinity in the direction  $\hat{k}$ .

meridian plane is the perpendicular bisector of the baseline vector  $\vec{B_{\lambda}}$ ). In this case signals  $S_1$  and  $S_2$  are identical; the cross-power is equal to the power that would be measured at either antenna independently.

#### Meridian Case:

cross-power

$$S_1 = S_2$$

$P_{2,1}|_{meridian} = S_1 S_2^{\dagger}$

$= (S_1)^2 = (S_2)^2$

$= P_-$

† denotes conjugation

Now consider the effect of moving the source to a point off the meridian plane in the direction  $\hat{k}$ . Signal  $S_2$  is now shifted in phase with respect to signal  $S_1$ . The phase shift is produced by the path difference of  $\vec{B}_{\lambda} \cdot \hat{k}$  wavelengths.

$$S_2 = S_1 e^{j2\pi \vec{B}_\lambda \cdot \hat{k}} \tag{1.1}$$

$$P_{2,1} = \operatorname{Re}(P_{m}e^{-j2\pi \hat{\mathcal{B}}_{\lambda} \cdot \hat{k}}) \tag{1.2}$$

If we define the angle  $\theta$  as the departure angle from the meridian plane the expression for the interferometer response becomes:

$$P_{2,1} = P_m \cos(2\pi B_\lambda \sin \theta) \tag{1.3}$$

The expression is simplified by defining a new parameter  $\zeta = \sin \theta$ .

$$P_{2,1} = P_m \cos(2\pi B_\lambda \zeta) \tag{1.4}$$

As shown by equation 1.4 the monochromatic interferometer response pattern is a sinusoidal function of the variable  $\zeta$  which has values between -1 and +1. The antenna separation,  $B_{\lambda}$ , determines the spacing between the peaks  $(+P_m)$  and troughs  $(-P_m)$  of the interferometer response pattern.

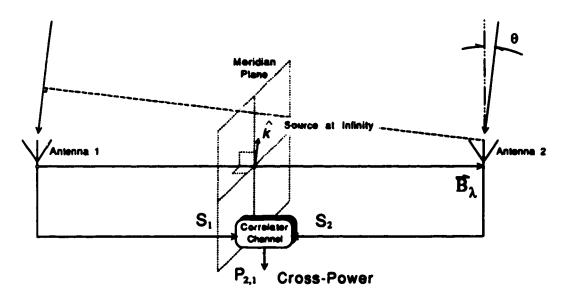

It is worthwhile to note here that if a phase lag of  $\frac{\pi}{2}$  was added to  $S_2$  in equation 1.1 the response would be a sine function instead of the cosine in equation 1.4. The phase shifted version will be referred to as the quadrature signal (denoted by a prime ').

$$S_2' = S_2 e^{-j\frac{\pi}{2}} \tag{1.5}$$

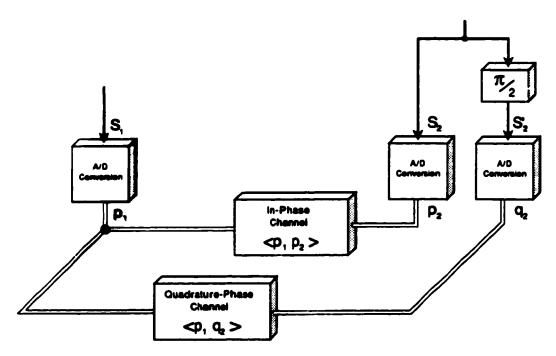

Figure 1.3: The Quadrature Channel Interferometer Pair: The response pattern of the quadrature correlator channel is a sine function of the variable  $\zeta$ . Its peaks coincide with the nulls of the in-phase channel's pattern and vice versa. The measurements made with the two channels are independent, further, they are orthogonal. The power radiated from any point in the sky will be detected by one of these two channels.

This produces the quadrature-channel interferometer response:

$$P'_{2,1} = \operatorname{Re}\left(P_{m}e^{-j2\pi\vec{B}_{\lambda}\cdot\hat{k}+j\frac{\pi}{2}}\right) \tag{1.6}$$

$$P'_{2,1} = P_m \sin(2\pi B_\lambda \zeta) \tag{1.7}$$

Figure 1.3 shows a functional representation of the interferometer with the quadrature channel added. Because the peaks and troughs of the inphase response  $P_{2,1}$  coincide with the nulls of the quadrature response,  $P'_{2,1}$ , (and vice versa), they are independent response patterns.

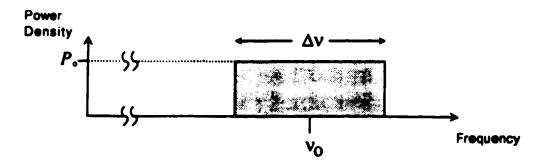

Figure 1.4: A Rectangular Frequency Response: The system frequency response pattern has a bandwidth of  $\Delta\nu$  at center frequency  $\nu_o$ . The abscissa represents spectral power density ...  $P_m = P_o \Delta \nu$ .

#### 1.2.2 The Bandwidth Pattern

We will now examine the effect of the interferometer bandwidth. The simple monochromatic model discussed above can be expanded to include a range of frequencies. If we cast equations 1.4 and 1.7 in exponential form, the response can be represented as a complex value.

$$\hat{P}_{2,1} = P_{2,1} + jP'_{2,1} = P_m e^{j2\pi B_{\lambda}\zeta}$$

(1.8)

A useful result is obtained by examining the interferometer response to a rectangular spectral power distribution such as the one shown in Figure 1.4. Suppose that the power of the imaginary source at infinity is spread uniformly over the bandwidth. To derive the interferometer response in the broadband case we should rewrite equation 1.8 in terms of frequency  $\nu$ .

$$d\hat{P}_{2,1} = P_o e^{j2\pi \frac{R}{c}\nu\zeta} d\nu \tag{1.9}$$

The broad-band interferometer response pattern is the integral sum of the responses of the elemental interferometers  $d\hat{P}$  each with power  $P_0d\nu$ .

$$\hat{P}(\Delta\nu) = P_o \int_{\nu_o - \frac{\Delta\nu}{2}}^{\nu_o + \frac{\Delta\nu}{2}} e^{j2\pi \frac{B}{c}\nu\zeta} d\nu \tag{1.10}$$

After integration:

$$\hat{P}(\Delta\nu) = \underbrace{(P_o\Delta\nu)}_{1} \underbrace{e^{j2\pi\frac{B}{c}\nu_o\zeta}}_{2} \underbrace{\left(\frac{\sin\left(\pi\Delta\nu\frac{B}{c}\zeta\right)}{\pi\Delta\nu\frac{B}{c}\zeta}\right)}_{2}$$

(1.11)

The resulting expression has three terms: term 1 is the total incident power from the source; term 2 is the monochromatic interferometer response at frequency  $\nu_o$ ; term 3 is referred to as the bandwidth pattern (also as the delay beam). The bandwidth pattern attenuates the two-dimensional sinusoidal response (term 2) of the monochromatic interferometer as  $\zeta$  departs from the meridian plane ( $\zeta = 0$ ). Its effect is most noticeable when the bandwidth and baselines are both large.

# 1.2.3 The non-isotropic interferometer: tracking the source

By replacing the fictitious isotropic antennas with realistic antennas, further characteristics of interferometers can be developed. Actual antennas have non-uniform directional properties. The directional sensitivity of an antenna is called its primary pattern and the direction of greatest sensitivity is referred to as its main beam. During typical observation sessions, the antennas track the region of interest keeping the main beams centered on a point on the celestial sphere; this will be the image center. The response pattern for the non-isotropic interferometer is obtained simply by adding a fourth term (expressing the directional properties of the antennas) to equation 1.11.

$$\hat{\mathbf{P}} = (P_o \Delta \nu) e^{j2\pi \frac{R}{c} \nu_o \zeta} \left( \frac{\sin \left( \pi \Delta \nu \frac{B}{c} \zeta \right)}{\pi \Delta \nu \frac{B}{c} \zeta} \right) \cdot \underbrace{G(\zeta, \eta)}_{4}$$

(1.12)

In equation 1.12,  $\eta$  is a parameter, like  $\zeta$ , that results from projecting the curvilinear coordinates  $\theta$  and  $\phi$  onto a flattened image plane (see Thompson et al. [TMS86, page 79]);  $\phi$  is the departure angle between  $\hat{k}$  and the plane containing the baseline and the image center (the baseline plane). The image

plane is tangent to the celestial sphere at the *point* mentioned above (the image, baseline and meridian planes all intersect orthogonally at the image center *point*).

#### Pointing the Delay Beam

The antenna beam characteristics are defined by  $G(\zeta, \eta)$ . As the region of interest moves across the sky from east to west, the antenna beams are made to track this motion; motorized antenna mounts keep each antenna directed at the field center. Like the physical antenna beams, the bandwidth pattern (delay beam) also has directional properties. A re-examination of the function arguments in equation 1.12 is useful at this point:

$$\frac{B}{c}\zeta = \frac{B}{c}\sin\theta = \tau_{\theta} \tag{1.13}$$

Term 3 of equation 1.12 is simplified by substituting equation 1.13, the geometric delay:

$$\frac{\sin\left(\pi\Delta\nu\frac{B}{c}\zeta\right)}{\pi\Delta\nu\frac{B}{c}\zeta} = \frac{\sin\left(\pi\Delta\nu\tau_{g}\right)}{\pi\Delta\nu\tau_{g}} \tag{1.14}$$

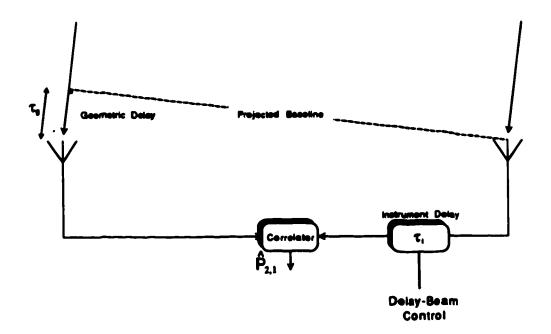

$\tau_g$  is the geometric delay between signals arriving at the two antennas. (The bandwidth pattern has a maximum when the relative delay is zero:  $\tau_g = 0$ ). For this reason, the bandwidth pattern is often called the delay beam. To attain practical sensitivity, the delay beam must also track the region of interest. This can be done by artificially delaying the signal from one antenna before the cross-power measurement is made. Figure 1.5 shows the interferometer with a delay compensation system for tracking with the delay-beam. As the earth rotates, the antenna beams track the source (the antennas are in constant motion); the delay-beam is also made to track the source by continually adjusting the instrumental delay  $\tau_i$  to cancel the geometric delay  $\tau_g$ . The interferometer response can be written in terms of these delay values:

$$\hat{\mathbf{P}} = (P_o \Delta \nu) \underbrace{e^{j2\pi\nu_o(\tau_g - \tau_i)}}_{1} \underbrace{\operatorname{sinc}\left(\Delta\nu\left(\tau_g - \tau_i\right)\right)}^{2} \cdot G \tag{1.15}$$

Figure 1.5: Pointing the Delay-Beam: The delay-beam must track the field center. The compensating delay,  $\tau_i$ , is constantly adjusted to cancel the geometric delay,  $\tau_g$ , thus keeping the delay-beam aligned with the primary beams. This compensation projects the antenna baseline onto a plane facing the source.

Figure 1.6: Phase Path Equalisation: Phase path compensation is applied at the RF-to-IF mix stage at antenna 2. The local oscillator phase difference,  $\phi_1 - \phi_2$ , is constantly adjusted to cancel the relative phase delay between  $S_1$  and  $S_2$ .

Recall that  $\tau_g = \tau_i$  is only true for the center of the delay-beam and that term 2 attenuates the response for sources where  $\tau_g \neq \tau_i$  (off the meridian plane). Term 1, the isotropic interferometer response, represents the phase difference between the signals from sources in the field of view.

#### Pointing the Interference Pattern

It is desirable to keep the interference pattern (term 1 of equation 1.15) fixed with respect to the image center to allow long integrations of the cross-power. This is accomplished by equalizing the phase paths from the source to the correlator for each antenna. Achieving this for the tracking interferometer is more difficult than equation 1.15 would imply.

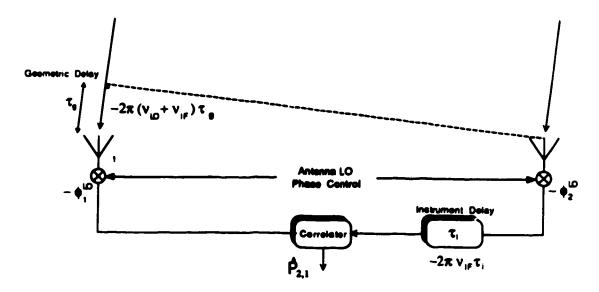

A further step must be taken towards defining the characteristics of an actual interferometer. Because of cable losses and dispersion, the compensating instrumental delay shown in Figure 1.5 is impractical at the high radio

frequencies. Signal delay is often done after the radio frequency (RF) band has been mixed down to a more manageable intermediate frequency (IF). Because the phase path at RF  $(2\pi\nu_{RF}\tau_g)$  is different from that at IF  $(2\pi\nu_{IF}\tau_i)$ , some phase path compensation is needed. It is possible, by controlling the phase of the local oscillators, to apply the correction during RF-to-IF mixing. The phase path that each signal experiences is shown in Figure 1.6. To track the source with the interference pattern as it moves across the sky the following condition must be maintained: the phase-lags,  $\Delta\Phi$ , in both signal path must be equal.

$$\Delta \Phi_1 = \Delta \Phi_2 \tag{1.16}$$

Signal 1 phase is a result of the geometric delay at RF, while Signal 2 phase is a result of the instrument's compensating delay at IF (both signal phases are also dependent on their local oscillator phases,  $\phi^{LO}$ ):

$$-2\pi\nu_{RF}\tau_{s} - \phi_{1}^{LO} = -2\pi\nu_{IF}\tau_{i} - \phi_{2}^{LO}$$

(1.17)

Since  $\nu_{RF} = \nu_{IF} + \nu_{LO}$ :

$$-2\pi(\nu_{IF} + \nu_{LO})\tau_g = -2\pi\nu_{IF}\tau_i + (\phi_1^{LO} - \phi_2^{LO})$$

(1.18)

The relative phase between the two local oscillator signals must be adjusted to be:

$$\phi_1^{LO} - \phi_2^{LO} = \underbrace{2\pi\nu_{LO}\tau_g}_{i} + \underbrace{2\pi\nu_{IF}(\tau_g - \tau_i)}_{2}$$

(1.19)

Equation 1.19 shows the corrective phase required: term 1 is a result of performing the delay compensation at a frequency other than the original RF frequency; term 2 is zero when  $\tau_g = \tau_i$  (this requires the delay system to be very precise). For delay systems where the instrumental delay,  $\tau_i$ , is not continuously variable<sup>2</sup>, the relative phase,  $\phi_1^{LO} - \phi_2^{LO}$ , can be used to substitute phase for delay; such a correction is exact for only one frequency, usually chosen to be the center frequency of the correlation bandwidth,  $\nu_{iF}^{c}$ .

$$\phi_1^{LO} - \phi_2^{LO} = 2\pi \nu_{LO} \tau_g + 2\pi \nu_{IF}^c (\tau_g - \tau_i) \tag{1.20}$$

<sup>&</sup>lt;sup>2</sup>The compensating delay at the DRAO is a selection of cables of various lengths, each of which can be electronically inserted or removed from the signal path. The computer selects the cable combination which most nearly matches  $\tau_g$ . Residual phase correction is done for the center of the IF band ( $\nu_{IF}^c = 30.0 \mathrm{MHz}$ ).

#### Mapping the Sky

This short discussion will review the interferometer characteristics discussed above in terms of their impact on the imaging process.

Many interferometer measurements are made before there is enough information to make a map of the sky brightness. The mapped region is defined by the primary beam width of the antennas (assumed identical). Within the main beam, the response (for an interferometer pair) is modulated by the striped phase-interference pattern. This striped response pattern allows the complex interferometer to measure a spatial Fourier component of the two-dimensional image brightness. The result, obtained by integrating the cross-power, corresponds directly with the amplitude and phase of the image's Fourier component. The orientation and spacing of the striped response is dependent on the direction and magnitude respectively of the antenna baseline vector with respect to the image coordinates. Two mechanisms are used to alter the antenna baseline vectors: antennas are physically placed to produce the desired baselines (the DRAO has two movable antennas), and the motion of the Earth changes the orientation and projected magnitude of the antenna baseline with respect to the image. When enough spatial frequencies have been measured (at the DRAO this takes about 35 days of observing), the image can be reconstructed using a two-dimensional Fourier transformation.

During any given interferometer measurement (lasting several seconds), the striped interference pattern must be held stationary with respect to the image coordinates. This requires continuous precise control of the phase and delay at each antenna.

#### **Polarimetry**

Except for spectral-line emissions, the signals received from space are broadband noise. In some cases the signals are partially linearly polarized. To measure (i.e. make a map of) the polarized components of the sky brightness requires dual-polarization antennas and a more elaborate correlator system. The polarization parameters that are typically mapped are the Stoke's

#### parameters:

I is the total incident power.

U and Q are linearly polarized components of power.

V represents the circularly polarized component.

Some astronomical objects exhibit small degrees of linear polarization. The best measurements of linear polarization are made with circularly polarized receivers (feeds); the antennas at the DRAO receive left and right hand circularly polarized radio waves.

To accomplish the polarization measurement (polarimetry), the interferometer pairs must each form the cross-polarization correlation products (left-right and right-left) in addition to the regular correlation products (right-right and left-left).

#### Phase Switching

Signals received from space are typically 50 decibels weaker than the noise generated in the front-end antenna electronics; this is the signal level received from the weakest source detectable by the telescope. The correlation process is a very sensitive measurement technique used to detect minute amounts of signal similarity. In the perfect system, the only similarity between two antenna signals would be due to the weak extraterrestrial radiation. In practise, similarity also results from d.c. signal bias, crosstalk between lines or from system sources of EMI (switching power supplies or high-speed logic). A technique for reducing the impact of these system imperfections on the correlation results is called *phase-switching*. Alternate correlation integrations are made with one antenna signal inverted. The inversion is usually done at the antenna focus box by shifting the LO phase by 180°. This inverts the interferometer response; ideally, the effect of the system imperfections will be the same (non-inverted) for successive integrations. Because the sense of the corruption has changed with respect to the desired measurement, the

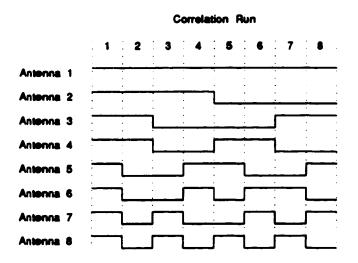

Figure 1.7: Phase Switching for 8 Antennas: The antennas are phase-switched on successive correlation-runs according to the Walsh fuctions.

unwanted component can be eliminated. The technique is effective to the extent that the sources of corruption are stable (stationary).

Phase-switching is currently used at the DRAO<sup>3</sup> where the two fixed dishes are 'correlated' with the two movable ones (track mounted). On alternate correlation-runs (integrations), the track-mounted antennas are phase-switched (relative to the fixed ones).

The phase-switching becomes more complex in an array forming all possible antenna-pair combinations. Walsh functions are bimodal (+ or -) orthogonal patterns which provide an efficient algorithm for phase-switching any number of antennas. Figure 1.7 shows the switching pattern for 8 antennas.

The phase-switch process involves modulating (inverting) the signal as soon as possible in the signal path (at the focus) and then demodulating at a point where the signal is no longer susceptible to contamination. With an

<sup>3&</sup>quot;...to cover a multitude of sins." — T.L. Landecker

analog correlator system, this point is after correlation (in software); with a digital system, the quantized signals can be demodulated (by hardware) prior to correlation. The latter approach is straightforward and it allows multiple integrations to accumulate in the channel hardware (since the sign of the measurement has already been corrected). This would allow much higher (more effective) phase-switch rates to be attained because channel read-out is not required between runs.

## 1.3 The DRAO Synthesis Telescope

At the Dominion Radio Astrophysical Observatory (DRAO), the main instrument is an earth-rotation synthesis telescope composed of four 9 meter dish antennas on a 600 meter east-west baseline. Two of the antennas are track mounted (movable) allowing any antenna spacing to be formed (see Figure 1.8).

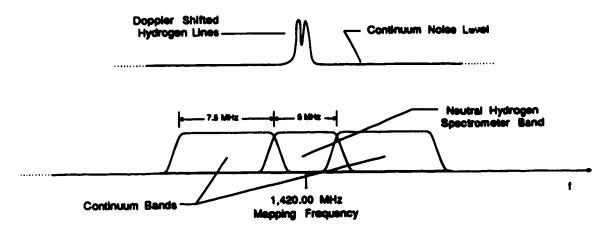

The telescope provides simultaneous mapping of two regions of the radio spectrum: the image (field of view) is 2° across at 1.42 GHz and 7° at 408 MHz. The 1.42 GHz region is mapped by two systems: the first, the spectrometer system, produces 128 maps of the HI (neutral hydrogen) spectral line intensity (each map corresponds to a Doppler frequency shift produced by the different relative velocities of the radiating hydrogen); the second system maps the broad-band (continuum) radiation in two 7.5 MHz bandwidths which straddle the spectral line bandwidth.

The 408 MHz system (4 MHz bandwidth) is a continuum mapping system (see Veidt, et al. [Vei84] and Lo, et al. [Lo84] for details about this system). Both fields of view are quite wide by astronomical standards. This unique property of the DRAO telescope makes it well suited to the study of dispersed structures in the interstellar medium. To help the telescope meet the future requirements of the scientific community, the observatory is taking significant steps to improve the instrument's performance.

The most recent step was the addition of dual polarization processing (previously only left-hand circularly polarized signals were detected); this increases the sensitivity of the telescope by a factor of  $\sqrt{2}$ .

Figure 1.8: The DRAO Synthesis Telescope: Two of the four dishes can be located anywhere on the 300 meter track. A fifth dish (unpainted) is shown under construction.

Figure 1.9: Observed Frequencies at 1.42 GHs: The 5 MHs band produces 128 maps corresponding to Doppler shifts of the neutral hydrogen spectral line. The continuum bands measure the nen-spectral radio brightness. The two 7.5 MHs bands represent the old analog continuum system's frequency response.

A further step will be to use the dual polarization system to perform polarization measurement or polarimetry. This requires more 'back-end' processing; in addition to the visibilities measured by correlating right-right and left-left (present system), the cross-polarization products, right-left and left-right, must be formed for each interferometer pair (8 correlator channels per interferometer pair — 2 channels per complex correlator).

To increase the sensitivity of the telescope's continuum system, the map bandwidth is being increased from the present 15.0 MHz to 30.0 MHz. While this requires some improvement of the telescope's 'front end' (better filters) the 'back-end' processing (correlators) is where most of the improvements are needed. Doubling the system bandwidth will improve the sensitivity of the continuum system by  $\sqrt{2}$ .

The most visible improvement to the telescope will be three (possibly four) additional antennas. These will be added one at a time, the last scheduled to become active in 1992. This will reduce the observing time from 35 to 12 days. A further advantage of more antennas results from of a technique for self-calibrating the telescope. The technique, known as closure-phase, be-

comes more effective as the number of antennas in the array increases (see Thompson et al. [TMS86, page 356]).

The closure-parameters, derived from the observations, provide a set of constraints which will guide the subsequent image generation and enhancement. This technique is effective in reducing system phase errors. At the DRAO, the dynamic range of instrument is presently limited by phase errors in the observations. More antennas, together with self calibration techniques such as 'closure-phase', will allow better images (with wider dynamic range) to be produced in less time.

In order for closure-phase to be effective, the telescope must meet an important criterion: phase errors in the observations must reside solely in the antennas (not 'downstream' in the signal distribution and processing systems). This means that the signal distribution paths and correlator channels should be very closely matched. With an an analog system, such performance is not maintainable for even a modest system with 16 correlator channels. Component aging and temperature drift are factors which perpetually change the conditions in the analog system. This is the most desirable aspect of a digital correlation system: after the signals have been digitized (antenna-based) all the processing, whether signal distribution or correlation, is identical and error-free. There are no correlator-based errors in a digital system.

# 1.4 The New 1420 MHz Continuum Correlator

What are the system-level considerations behind the decision to replace the old continuum correlator system? This project is a direct result of the decision to 'replace' rather than 'reproduce' the existing strategy ... yet another analog system is superseded by its digital counterpart. The items discussed here will reflect the previous section's introduction to the DRAO synthesis telescope and its performance objectives.

### 1.4.1 The Expanding Array

The main reason for re-evaluating the continuum correlator design is the demand for many more correlators than presently exist. The addition of 4 antennas (and forming all possible antenna-pairs) will increase the number of interferometers from 4 to 21. Adding correlator channels for the cross-polarization products required by polarimetry effectively doubles the requirement to 42. Virtually the entire correlator system would be new, even if the old strategy were copied.

A related reason to evaluate the old system comes as a result of the rapid advances being made in electronics technology. The cost constraints associated with various designs (both digital and analog) have changed dramatically since 1975 when the analog system was designed. The digital trend is driven by the still-increasing performance-to-cost ratio of digital devices; a digital system is much cheaper now than it was then.

Analog components have also seen remarkable improvements, implying that a similar strategy to the existing one could provide better performance for an equivalent cost. The system described herein (the new continuum correlator) uses a substantial number of analog components in the IF processing prior to digitization (see Chapter 4). At the time of design (1986) the system strategy represented a balance between analog and digital complexity for the larger array. For example, quadrature channel signals are more easily generated in the IF analog hardware than in digital circuitry (Hilbert transform filters).

The DRAO needs a significantly larger continuum correlator. The new system must be easily manufactured, expandable, and reliable. As well as present system's requirements, the new correlator should provide the interview to permit—even encourage—further improvements to the interview t's performance.

#### 1.4.2 Improving the Performance Parameters

The smallest signal detectable by an interferometer pair is proportional to (see Thompson et al [TMS86, page 160]):

$$\Delta s \propto \frac{kT}{\eta_c A_{rs} \sqrt{\Delta \nu \tau}} \tag{1.21}$$

k is the Boltzmann constant

T is the system noise temperature

$\eta_c$  is the correlator efficiency

A. is the effective antenna area

$\Delta \nu$  is the correlated bandwidth

$\tau$  is the correlation time

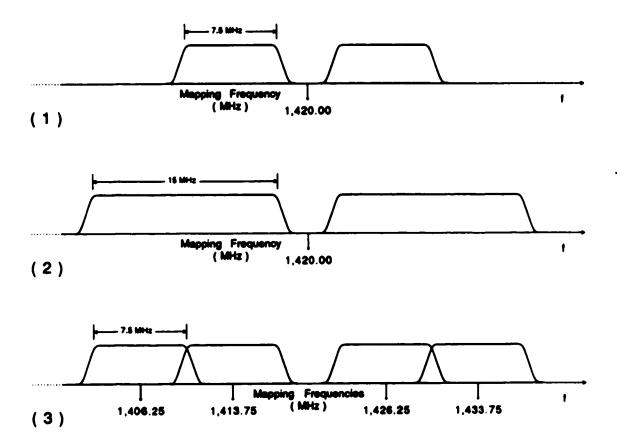

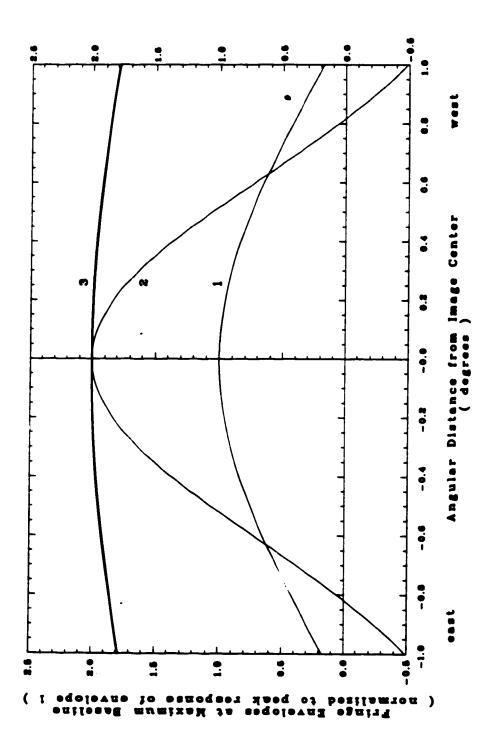

The sensitivity of the continuum system can be improved by widening each of the 7.5 MHz bands to 15.0 MHz. The disadvantage of the wider correlation bandwidth is the narrow delay beam this produces. For the larger antenna spacings, the sources at the edges of the field are severely attenuated (the improved sensitivity applies only to sources at the field center). This results in a 'smearing' of sources at the edge of the image. The way around this dilemma is to break the bandwidth into smaller sub-bands, each with its own correlation system. Because the normalized antenna baseline,  $B_{\lambda_i}$ , is different for each sub-band ( $\lambda_i$  is the center wavelength of each band), sub-maps must be scaled to compensate. The scaled sub-maps can be combined to obtain a map whose sensitivity has been increased over the entire field of view. Figures 1.11 and 1.10 show three correlation bandshapes and their effect on the delay beam.

The bandwidth processing approach chosen for the new correlator is shown in Figure 1.10 (c). The two 15.0 MHz bandwidths are each filtered into two 7.5 MHz sub-bands. Each of the four sub-bands is digitized and correlated independently.

Another good reason for correlating bands 7.5 MHz wide was the state of technology in 1985. Reasonably priced (less than \$100) analog-to-digital

Figure 1.10: Correlation Frequency Options: The frequencies processed by the correlator determine the performance of the telescope: 1 shows the present strategy; 2 is similar but with double the bandwidth; 3 shows the wider bandwidth correlated in four sub-bands.

Figure 1.11: Worst-Case Delay Beams: The worst case occurs at the maximum baseline (600 meters). The three cases correspond to the correlation bandwidths shown in Figure 1.10.

converters capable of the 7.5 MHz bandwidths were being introduced. The required sample and processing speeds (nominally 20 MSPS) were just slow enough to provide a broad selection of standard digital signal processing components.

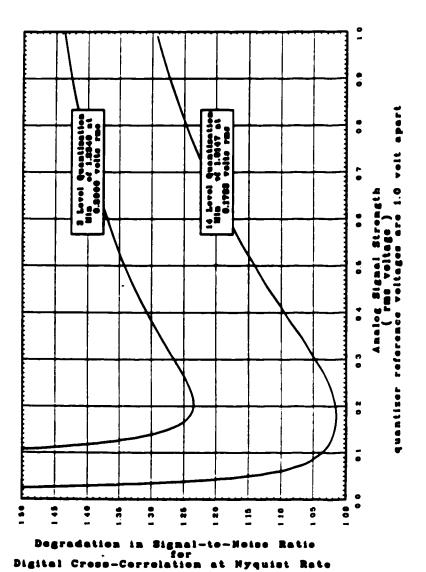

The other parameter in equation 1.21 which lies within the scope of this project is the correlator efficiency,  $\eta_c$  (maximum 1). For a digital correlator system, the value of  $\eta_c$  reflects the signal-to-noise penalty incurred by digitizing the antenna signals. For example, a polarity coincidence correlator (1 bit sampling) has an efficiency of  $\frac{2}{\pi}$  (shown by Weinreb [Wei63]). Using techniques presented by Klingler and Bowers [KB74] the correlator efficiency for various quantization schemes can be compared <sup>4</sup>; two degradation curves are shown in Figure 1.12.

An ideal analog correlator has an efficiency of 1. The more resolution (bits) an A/D converter has, the more its efficiency resembles that of the ideal analog unit. To maximize efficiency, a 4-bit sampling scheme was chosen for this system. For reasons described later, the signal quantization employs 14 levels (out of 16 possible) to attain a correlator efficiency of  $\eta_c = 0.985$ . Figure 1.12 shows a comparison of the performance attainable with 2 types of quantization schemes: 2-bit (3 levels) and 4-bit (14 levels) quantization. The penalty paid for more bits is in the complexity of the digital hardware. No substantial improvement in performance is possible beyond 4-bit quantization.

In summary, the four bit/four band system was selected as a baseline for the design because of the following reasons:

- Very high correlation efficiency virtually indistinguishable from an ideal analog correlator.

- Mature device technology resulting in a broad selection of economical (and available) components for the design.

<sup>&</sup>lt;sup>4</sup>The correlation efficiency,  $\eta_e$ , is the reciprocal of the degradation factor 'D' described by Klingler and Bowers.

Figure 1.12: Correlator Efficiency:  $\eta_c$ , is the reciprocal of the degradation. The abscissa is the input signal standard deviation,  $\sigma$ : in terms of the A/D output weighting range [-13,+13], an analog input of 0.5 volts corresponds to +16. Optimum correlator performance is attained when the standard deviation of the digital samples is near 5.7.

### 1.4.3 The Design Baseline

This section will present the system design agreed upon at the outset of the project.

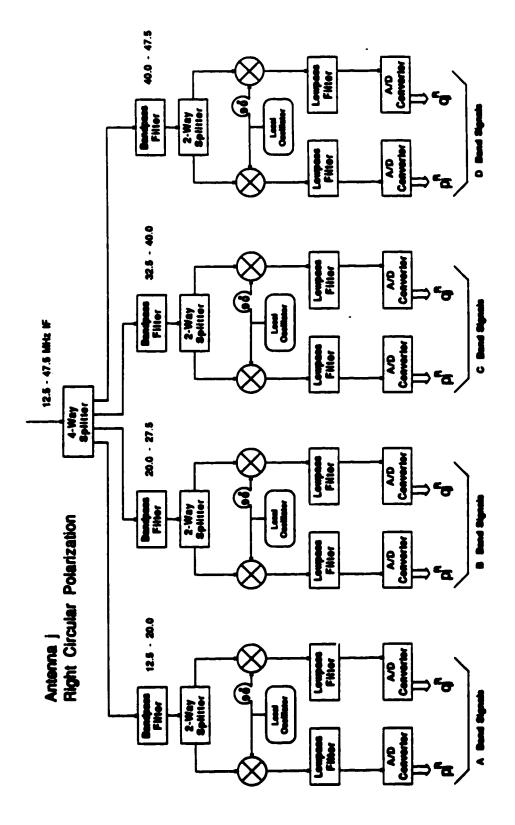

As discussed above, the continuum frequencies would be separated into four sub-bands, each 7.5 MHz wide (see Figure 4.1). This separation applies to both polarizations (left and right) of all eight antennas. Hence each antenna will produce eight independent sub-bands (4 right and 4 left). The bandwidth separations would be done at IF frequencies (12.5 - 47.5 MHz) using bandpass filters; for example a 12.5-20.0 MHz filter isolates the lowest band. Each 7.5 MHz band is then mixed down to baseband (actually, 0.5 - 8.0 MHz) prior to A/D sampling. The quadrature signal ( $\frac{\pi}{2}$  phase shifted) is formed during this last mixing stage by splitting each band signal and using LO signals  $\frac{\pi}{2}$  apart. This results in 16 separate signals for each antenna's continuum. Sixteen A/D converters per antenna (128 total) are required to sample the signals.

Further system design takes advantage of the symmetry of the design. The processing requirements for each of the four bandwidths are identical.

Designing and testing a correlator system for one band will accomplish the design requirement for the entire system. The correlator system for each band must meet the following requirements:

- All possible interferometer pairs must be formed within the band. This facilitates self-calibration.

- 8 antennas form 28 pairs.

- An interferometer pair must measure all polarization visibilities (LL, RR, LR and RL) so that the telescope can measure polarization.

- 4 visibilities require 8 correlator channels per pair.

- Correlator channels must multiply and accumulate 4-bit x 4-bit values at a nominal rate of 20 MSPS for intervals as long as 90 seconds. Channel results must be easily accessible to the computer controlling the system.

- For proper phase-switch demodulation, the system must start and stop operations in synchronism with the other observing systems (HI) sharing the antennas.

- The total 4-band system will have at least 896 correlator channels (auto correlation channels included, 1,152) providing a processing rate of 1.8 billion correlation operations per second.

The initial scope of this project included:

- 1. Development of the analog IF signal chain.

- 2. Development of an A/D converter unit.

- 3. Development of the digital correlator system.

- 4. Development of the software required to control the system and integrate it with the existing DRAO computer.

## 1.4.4 Project Progress Overview

The volume of work in the project baseline dictated a reduction in scope: since the DRAO had expertise in areas 1 and 4, the project proceeded on fronts 2 and 3.

The IF processing system, area 1, was constructed and tested at the unit-level by DRAO staff and is now ready for system-level testing.

Area 2, the A/D converter design, proceeded as far as preliminary testing of Version 3 prototypes. Further development and testing is being done at the DRAO. Chapter 4 describes the development and testing done on the A/D converter unit. The system is in the latter stages of hardware construction and has passed the required unit level tests.

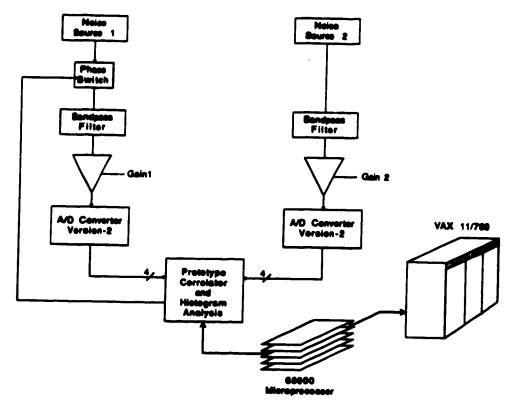

Area 3, the development of the digital system, proceeded to the successful testing of a subsystem composed of a microprocessor controller and the three fundamental system components: the control/interface card (CIC); the

mother board and chassis; and correlator cards. Using these units, a complete continuum correlator system can be built.

Software development, area 4, will probably proceed in parallel with the development of the A/D converters. Considerable work was done in this area facilitate the development tests in area 2 and 3 (the 68000 microprocessor concolled all of the test configurations). A microprocessor-to-CIC interface (hardware and software) was designed for use during the testing in area 3; this design will probably meet the needs of the full system.

System integration testing will probably be nearing completion in 1991.

<sup>&</sup>lt;sup>5</sup>Gary Hovey provided much valuable advice and assistance during these activities.

# Chapter 2

## The Correlator

This chapter presents the development of the digital correlator<sup>1</sup> beginning with the channel requirements, followed by the particular design choices made. The focus will move from microscopic to macroscopic concluding with the correlation system topology.

The correlator is the 'heart' of an interferometer; it performs the multiplication of signals to obtain the cross-power discussed in Chapter 1. In practice, the cross-power has a very large standard deviation relative to the mean. To achieve a meaningful measurement, the cross power must be averaged over several seconds. The accumulation implied by the average is done, at least in part, by the correlator.

In fact, signals from each antenna are dominated by terrestrial noise. Usually the correlated signal components (power) are several orders of magnitude smaller than signal components produced by amplifier noise and antenna spill-over (sources outside the main beam). The system noises produced by different antennas arise from independent, random processes and so contribute, on average, nothing to the integral of the cross-power. Manmade noise entering through the antenna side-lobes, on the other hand, can

<sup>&</sup>lt;sup>1</sup>The term correlator will be used loosely to refer to a correlator system or to a single channel. One can infer which of the meanings (or both, as in this case) is meant from the context.

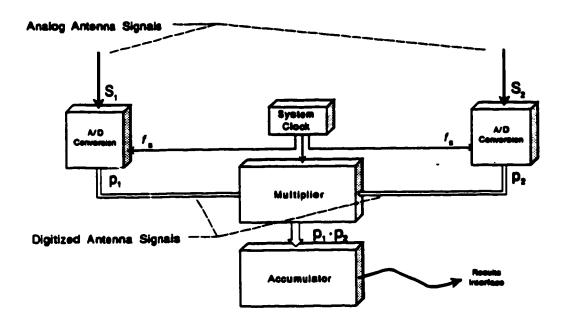

Figure 2.1: Digital Coerelation: Antenna signals are digitized, multiplied and accumulated at the rate  $f_s$ .

produce a non-zero component in the cross-power.

Often the unwanted signal sources (usually man-made) are fixed with respect to the antennas, behaving like a source at the pole of the celestial sphere.

## 2.1 The Channel Design

Channel Requirements. Some of the features of a digital correlator are shown in Figure 2.1. Prior to correlation, the antenna signals  $S_1$  and  $S_2$  are sampled (converted to sequences of binary numbers); each sample represents the antenna signal amplitude at an instant in time. For each processing cycle, the digital correlator multiplies two values to attain the instantaneous crosspower. After many cross-power values have been saved in an accumulating buffer, the buffer contents (cross-energy) must be transferred to the computer. Some amount of channel control is required: first, the ability to start and stop correlation; second, the ability to reset the channel (old results must be flushed out). In this system, each correlator channel must measure the cross-power in a 7.5 MHz bandwidth. To make full use of the signal's power requires the sample rate to be at least 15 MSPS. Adding a 30% design margin results in a 20 MSPS processing rate; oversampling compensates somewhat for quantization noise and for short-lived events. This speed requirement is well suited to the capabilities of standard digital hardware. This is also true for data acquisition components; inexpensive A/D converters allowed a 4-bit sampling scheme to be used on all signals.

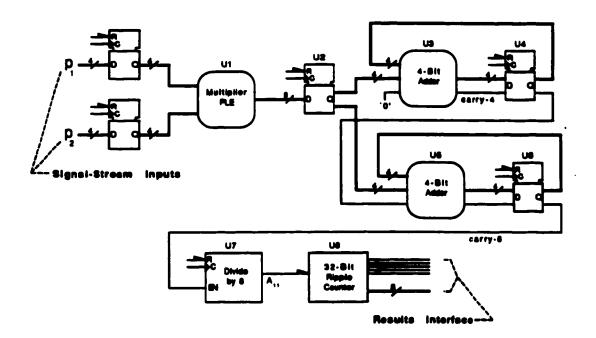

Correlator operations are synchronized to the processing clock. This is done using edge triggered D-type flip-flops (DFF's) and counters. Partitioning an algorithm into sequential tasks is called *pipelining*. Channel operations are pipelined to attain a higher processing rate. The four pipeline segments in a channel are:

- 1. The multiplier: U1 and U2

- 2. The least significant nibble (4 bits) accumulation: U3 and U4

Figure 2.2: A Correlator Channel: Asynchronous channel components are interspersed amongst the synchronous D registers. In general, limiting the complexity of an asynchronous section reduces its propagation delay. The channel has four such sections to allow a faster processing rate.

- 3. The most significant nibble accumulation: U5 and U6

- 4. The carry-out counter: U7 and U8

The operation of each pipeline segment is discussed in turn.

## 2.1.1 The Channel Multiplier

Recent advances in memory technology have made it feasible to use memory devices in high speed logic systems. This channel design uses a 256 x 8-bit PROM as the multiplier. The two 4-bit signals compose an 8-bit address value; stored at the location specified by the address is the cross-power result. Memory devices embedded in logic circuits are referred to as programmable logic elements (PLE's). Compared to the cheapest design alternative (the use of MSI multiplier chips such as the Cray multiplier chips 557/558) the PLE is faster, (25 ns vs. 60 ns) cheaper (\$11 vs. \$50) and more efficient (1 device vs. 7 devices). A further advantage, which will be discussed at some length, is that the PLE can be tailored to fit the application better than the generic logic devices.

## The Multiplication and Offset Algorithm

The algorithm stored in the PLE has channel control features as well as computation features: first we will concentrate on the computation algorithm.

Each of the two data streams entering the correlator channel is 4-bits wide allowing 16 unique values to appear at each of the multiplier inputs. Only 14 of the 16 are used for data values. The other two are reserved for control features (discussed a little later). The multiplier interprets the 14 data values as odd numbers from -13 to +13. The corresponding range of possible products is from -169 to +169. If the multiplier produced a result with a signed number format (eg. 2's complement), the subsequent channel logic would have to add or subtract values from the accumulation buffer. Introducing a numerical offset to the multiplier result simplifies the accumulating buffer (only additive operations are required). Consider first

the smallest possible offset which will ensure positive values. Biasing the multiplier output by 169 means the range of products is from 0 to 338. To uniquely represent all the numbers in this range requires 9-bits. Since the product of two odd numbers is also odd we see that using an odd valued offset will always produce an even valued result; the least significant bit is always a '0'. It is not necessary to carry this bit (referred to hereafter as the phantom bit) through any computations. The actual offset used is 333 giving a result range from 164 to 502. The multiplier PLE output represents the upper 8 bits of an unsigned binary value within the result range. The 8-bit result,  $P_{1,2}$ , is passed from the multiplier PLE to the channel accumulator at the rising clock edge. The PLE algorithm is:

$$P = \frac{(n_1 n_2 + 333)}{2} \tag{2.1}$$

where

$$n_1, n_2 \in [-13, -11, -9... + 7, +9, +11, +13]$$

(2.2)

#### 2.1.2 The Channel Accumulator

The input to the channel accumulator is the byte-wide data path flowing from the multiplier PLE. Consider first the least significant 4 bits (nibble) in the path. These are seen by the A-side inputs of a 4-bit adder (U3); the adder's B-side sees the result from the previous cycle's addition. As this 4-bit accumulator overflows it produces 'carry-outs' which are fed to the 'carry-in' input of the adder for the most significant nibble. Notice in Figure 2.2 that the carry-out signals from both adders pass through a DFF; they are seen by the following pipeline segment during the next process cycle. This permits a shorter process cycle since the carry propagation time does not have to incur two adder delays. The rest of the accumulation is done simply by counting the overflow carries from the most significant adder (U5). The first three bits of carry counting are done in U7, a gated synchronous counter. The presence of a carry allows (gates) the counter to increment at the clock rising edge. This device is simply a rate divider to slow down the carry count rate for the last device in the channel. The last device, U8, is a 32-bit ripple counter whose value will eventually be read by the computer.

Each time the third counting bit of U7 makes a high-to-low transition, the ripple counter in U8 increments. Only the final 32 bits of the channel accumulator (the contents of U8) can be read by computer, so the rate dividing counter was kept as small (3 bits) as possible. The ripple-count device 'U8' was selected mainly for its ease of interface.

The channel's accumulation capacity can now be examined. The parallel input portion of the accumulator (adders, etc.) is 9 bits wide (including the phantom bit); the serial accumulation is comprised of a 3-bit rate divider together with the 32-bit ripple counter. In total, the accumulator has a capacity of 44 bits or  $2^{44}$ . Assuming a continuous maximum result from the multiplier (say 512 or  $2^9$ ), the channel can record up to  $2^{(44-9)} = 2^{35}$  (more than a billion) process cycles without overflowing. At a processing rate of 20 MSPS, this allows 30 minutes of processing which is more than adequate.

#### 2.1.3 Channel Control

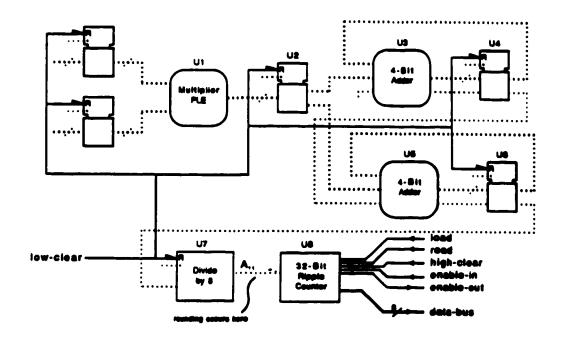

Figure 2.3 shows the control network associated with each channel. This section will describe channel control associated with typical operations including:

- starting and stopping correlation

- reading results

- preparing the channel for the next correlation interval

Starting and Stopping Correlation Recall from the discussion of the channel multiplier PLE, that of the 16 possible 4-bit input values, two were not used for data. One of these values, referred to as 'STOP' (1111), is used to stop the processing in the channel. The PLE is programmed to produce zero if 'STOP' appears at either 4-bit input. The zero value is very different from the range of values (164—502) that occur during normal operations. The appearance of a zero at the 4-bit adders stops further accumulation. One processing cycle after the appearance of the zero at the output of U2,

Figure 2.3: Channel Control Signals:

the final 'carry-out' (if any) appears at U7. The next process cycle sends the final count pulse (if any) to U8, the ripple-chip. From 'STOP' arriving at U1 to the last count pulse at U8 takes 3 clock cycles. It is important to recognize that the channel is still operating (process clocks are still running and all the channel devices are still active), it is merely processing zeroes. Hence, channel operation starts and stops depending on the values arriving at the channel multiplier. There are some practical advantages to multiplexing control conditions onto the data distribution network feeding the channel. Because these advantages are system-level considerations, they are best treated later in the chapter.

Reading Results: At the end of a correlation run the processing stops as described above. The contents of the ripple counter need to be read by a computer. Within this device is a 4-byte storage register for saving the 32 bit result. Saving is done by activating the 'load' signal on the device. The result bytes are now ready to be placed on the data bus. Internal and external tristate drivers are activated by two signals: first an active 'enable-in' condition must be seen; second an active 'read' condition places the value of the first (least significant) byte on the data bus. Successive bytes are displayed as the 'read' line toggles. When 'read' goes inactive for the fourth time, the 'enable-out' signal turns on and further activity on the 'read' line will have no effect. This iterface strategy allows an unlimited number of counter devices to share the same bus and control lines simply by daisy-chaining the 'enable' lines from one device to the next.

Clearing the Channel Prior to the start of a new correlation run, the channel results from the previous run must be removed. This is done by exercising the two reset lines 'low-reset' and 'high-reset'. The 'low reset' line clears the 9-bit parallel accumulator as well as the 3-bit rate divider. The 'high-reset' line clears the 32-bit ripple counter. (Notice that the read-out register contents are not affected; the channel can begin another correlation run before the results have been read.) The reason for a separate 'low-reset' line is for rounding the accumulated result. Recall that the lower 12 bits  $(A_0-A_{11})$  of the accumulator are not readable. If they are more than half full,  $A_{11}$  is a '1'; in this case we would like to add a count to the upper 32-bit

result so the visible value represents the rounded channel result (as opposed to the truncated result). By sending the 'low-clear' signal, these bits are set to '0's which generates the count event when needed (high-to-low transition on signal  $A_{11}$ ). Results returned to the computer are free of bias produced by truncation errors.

### 2.1.4 Correlator Channel Summary

The correlator channel is capable of operating at a 20 MHz processing clock rate. For each clock cycle the channel will correlate two 4-bit inputs. The channel employs a PLE (look-up table) multiplier and forms all the possible data products. Channel operation (On/Off) is controlled through the data inputs using reserved codes. The accumulator has 44 bits of capacity, with the upper 32 accessible as the correlation result. The 32-bit result can be rounded prior to readout. Because each channel has embedded storage registers, the channel can be cleared and begin the next correlation run before results have been read. This avoids reduction of the observing time by the need for the computer to gather results.

#### Channel Performance

At this point it is appropriate to give some attention to the characteristics of the channel output. From the statistical nature of the two input signals, we can determine the precision of the channel output. The correlator operates optimally when the standard deviation,  $\sigma$ , of the input signal is 5.71 (on the -13 to +13 scale) <sup>2</sup>. The standard deviation of the product of two such signals increases by  $\sqrt{2}$  to +8.07. Averaging products over N independent samples reduces the standard deviation by  $\sqrt{N}$ . In a typical correlation run (5.6 seconds) roughly 90 million (5.6 × 15 × 10<sup>6</sup>) independent<sup>3</sup> samples will

<sup>&</sup>lt;sup>2</sup>This value of  $\sigma$ , discussed further in Chapter 4, makes optimum use of the 14 quantiser levels.

<sup>&</sup>lt;sup>3</sup>For purposes of these calculations, the Nyquist rate, 15 MSPS, is used.

have been taken. The expected channel output is:

$$\langle C \rangle = \frac{(O_A + \langle p_{1,2} \rangle) \times \tau \times f_S}{d_L} \tag{2.3}$$

(C) is the expected channel output value.

$O_A$  is the accumulator offset (333).

$\langle p_{1,2} \rangle$  is the expected signal product (+8.07 if  $\rho = +1$  or -8.07 if  $\rho = -1$ ).

$d_L$  is a divider which accounts for the 12 invisible channel bits.

$\tau$  is correlation-run duration (5.6 seconds).

$f_S$  is sampling rate for each antenna signal (15 MSPS).

The extremes at the correlator output are determined by the perfect correlation  $(\rho = +1)$  and anti-correlation  $(\rho = -1)$  cases:

$$\langle C \rangle_{min} = 6.67 \times 10^6 \tag{2.4}$$

$$\langle C \rangle_{mas} = 7.00 \times 10^6 \tag{2.5}$$

The standard deviation at the channel output is related to these values:

$$\sigma_C = \frac{\langle p_{1,2} \rangle \sqrt{\tau \times f_S}}{d_L} = 18.06 \tag{2.6}$$

In general, the uncertainty in the result will be confined to a magnitude within the lower 5 bits of the channel output. The correlation output range will be confined to 19 bits, 14 of which are potentially significant depending on the correlation coefficient  $\rho$ . Based on equations 2.3 and 2.6 the detection threshhold is  $\rho = 0.011\%$  in 5.6 seconds with the result resolution exceeding that by 4 bits. The digital result is well represented with the 32 output bits.

Contrast the digital correlation results above with the old continuum correlators where a channel's analog output is sampled with a 10-bit A/D converter. Channel sensitivity is limited by the output resolution; some

improvement is had by increasing the channel gain. This is based on the reasonable assumption that the signal correlation will generally be small  $(\rho < 5\%)$ . Nevertheless, correlator effects are seen when an image field has a large dynamic range. The coarse 10-bit result range adds quantization noise to the observations.

The new digital correlator processing strategy will improve both the sensitivity and the dynamic range of the instrument.

### 2.2 The Correlator Card

With the correlator channel design established, 'larger' aspects of the system can now be addressed. Channels must be packaged (a counting, cooling) and serviced (electrical connections) and efficient groups. The number of channels required to form an interferometer pair (8) provides a natural design partition for the system; the eight channels, grouped on a printed circuit board, share timing, interface and signal distribution circuitry. This grouping simplifies the traffic between correlation blocks in the system. Interconnecting these boards (correlator cards) forms the processing network required by the antenna array.

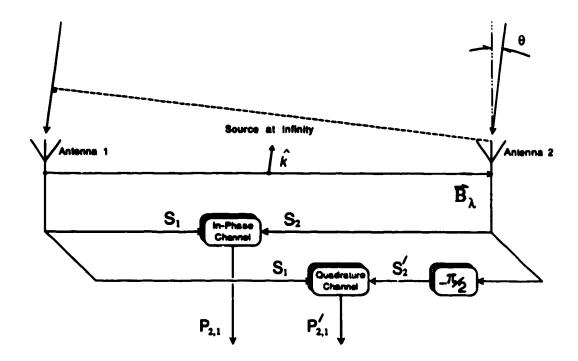

#### 2.2.1 The Polarized Interferometer

Figure 2.4 shows the in-phase and quadrature channel correlations associated with the complex interferometer. To discuss details of the correlator board operation, the following notation is needed:

```

p is an in-phase (unaltered) signal.

q is a quadrature-phase signal (\frac{\pi}{2} phase-shift).

<...> Poisson brackets denote time average (expectation value).

j,k subscripts denote antenna number.

```

Figure 2.4: The Complex-Value Correlator: The channels measure the cross-power vector (a complex number) between antenna signals.

R,L superscripts denote right-hand and left-hand circular polarization.

In this notation, the complex correlator output has the form:

$$\hat{P}_{j,k}^{RL} = \underbrace{\left\langle p_j^R p_k^L \right\rangle}_{1} + \underbrace{j \left\langle p_j^R q_k^L \right\rangle}_{2} \tag{2.7}$$

Figure 2.4 shows this notation. Each expectation value is derived from a correlator channel output, hence, Poisson brackets are synonymous with correlation. The measurement of  $\hat{P}_{j,k}$  requires two correlator channels: term 1 is the in-phase channel; term 2 is the quadrature channel.

The measurement of the polarization parameters of the sky brightness requires the following cross-polarization quantities to be measured:

$$\hat{P}_{j,k}^{R,R} = \left\langle p_j^R p_k^R \right\rangle + j \left\langle p_j^R q_k^R \right\rangle$$

$$\hat{P}_{j,k}^{R,L} = \left\langle p_{j}^{R} p_{k}^{L} \right\rangle + j \left\langle p_{j}^{R} q_{k}^{L} \right\rangle

\hat{P}_{j,k}^{L,R} = \left\langle p_{j}^{L} p_{k}^{R} \right\rangle + j \left\langle p_{j}^{L} q_{k}^{R} \right\rangle

\hat{P}_{j,k}^{L,L} = \left\langle p_{j}^{L} p_{k}^{L} \right\rangle + j \left\langle p_{j}^{L} q_{k}^{L} \right\rangle$$

(2.8)

For unpolarized or linearly polarized radiation,  $\hat{P}_{j,k}^{R,R}$  and  $\hat{P}_{j,k}^{L,L}$  are independent measurements of the same quantity; a  $\sqrt{2}$  improvement in sensitivity results. Notice that for the eight correlations, six signal streams are required:

From Antenna k:  $p_k^R$ ,  $p_k^L$ ,  $q_k^R$ ,  $q_k^L$

From Antenna j:  $p_j^R$ ,  $p_j^L$

The four correlation vectors can be used to derive the four Stokes parameters I, Q, U and V: I represents the total incident power, Q and U the power in the linearly polarized component and V the power in the circularly polarized component of radiation.

The relationships between correlations and Stokes parameters (see Thompson et al. [TMS86, page 105]) are, in their simplest form:

$$I = \frac{1}{2} \left( \hat{P}_{j,k}^{R,R} + P_{j,k}^{L,L} \right)$$

$$Q = -j \frac{1}{2} \left( \hat{P}_{j,k}^{R,L} + P_{j,k}^{L,R} \right)$$

$$U = \frac{1}{2} \left( \hat{P}_{j,k}^{R,L} - P_{j,k}^{L,R} \right)$$

$$V = \frac{1}{2} \left( \hat{P}_{j,k}^{R,R} - P_{j,k}^{L,L} \right)$$

(2.9)

Stokes parameters (having dimensions of flux density) propagate through space in the same manner as the electromagnetic field, therefore the response pattern of the interferometer applies to these quantities as well. In other words, providing the eight correlator channels shown above will allow mapping (images) of each Stokes parameter.

## 2.2.2 The Physical Design of the Correlator Card

The eight digital correlator channels are packaged together on the circuit board shown in Figure 2.5. The six 4-bit data streams are labelled 'A' through 'F'. The eight channels form the following correlation products:

Channel 1  $\longrightarrow$   $\langle AC \rangle$   $\longrightarrow$  [1] Channel 2  $\longrightarrow$   $\langle AD \rangle$   $\longrightarrow$  [2] Channel 3  $\longrightarrow$   $\langle AE \rangle$   $\longrightarrow$  [3] Channel 4  $\longrightarrow$   $\langle AF \rangle$   $\longrightarrow$  [4] Channel 5  $\longrightarrow$   $\langle BC \rangle$   $\longrightarrow$  [5] Channel 6  $\longrightarrow$   $\langle BD \rangle$   $\longrightarrow$  [6] Channel 7  $\longrightarrow$   $\langle BE \rangle$   $\longrightarrow$  [7] Channel 8  $\longrightarrow$   $\langle BF \rangle$   $\longrightarrow$  [8]

If streams A and B are used for  $p_j^R$  and  $p_j^R$  while streams C, D, E and F are used for  $p_k^R$ ,  $q_k^R$ ,  $p_k^L$  and  $q_k^L$  respective in the complex interferometer response vectors from Equation 2.8 (using the loose notation shown above) become:

$$\hat{P}_{j,k}^{R,R} = \{1 : j[2]

\hat{P}_{j,k}^{R,L} = [3] + j[4]

\hat{P}_{j,k}^{L,R} = [5] + j[6]

\hat{P}_{j,k}^{L,L} = [7] + j[8]$$

(2.10)

The correlator card provides the necessary input, output and control signals for each channel.

Power Distribution: The obvious, though often badly treated, connections on a circuit board are those for power and ground. The digital correlator card design minimizes power system noise and ground-loop problems by using a 4-layer circuit board (one layer is dedicated to power, another to ground), as well as filter capacitors at each device.

Clock Distribution: The signal which is most important to the correct operation of a fast digital system is the system clock. Care was taken to

Figure 2.5: The Digital Correlator Card: provides all the signal correlations needed by an interferometer for polarization measurement. The 4-layer circuit boards operate at 20 MHz clock rates.

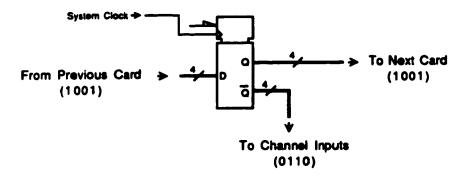

Figure 2.6: Correlator Input Design: At the rising edge of the clock, the value at the input of the D flip-flop is latched and transferred to the inverting (seen by the local correlator channels) and non-inverting (sent to the next correlator card) outputs.

ensure that proper clock distribution was achieved:

- Whenever possible, signal traces stay on one layer.

- Branches on high-speed signal traces were not allowed.

- Signal fan-out never exceeds 8.

- Clocks are driven from a single distribution device to minimize timing skew.

Similar precautions are taken for the other signals on the correlator card, with the exception of the reset control signals which are relatively slow (the signal branching rule was relaxed).

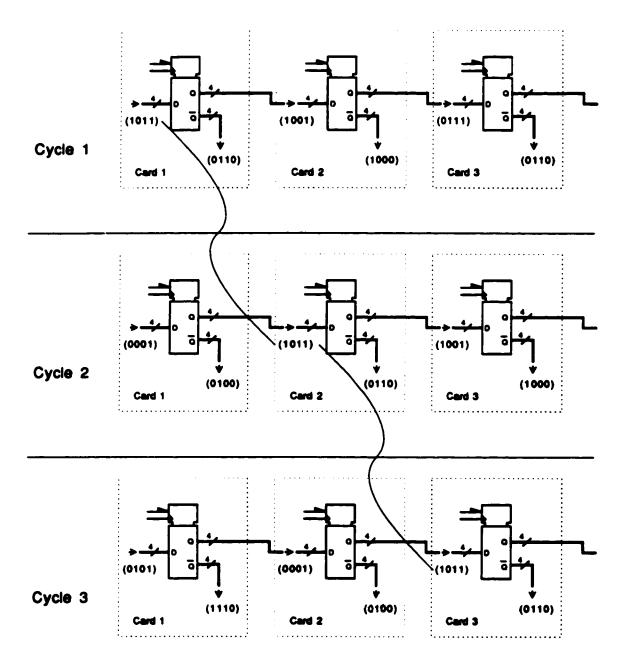

Antenna Signal Distribution: Distributing the digital signal data to the hundreds of channels is an important prerequisite for correlation. An effective strategy is to pass data values in bucket-brigade fashion from one correlator card to the next. To clock values from card to card, each data-stream requires 4 inputs and 4 outputs. Each stream input is connected to a dual-output D-type flip-flop as shown in Figure 2.6. These devices, which synchronize