National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

# NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

# **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylogra phiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# University of Alberta

# A RISC DESIGN INCLUDING INCREASED I/O BANDWIDTH AND BACKGROUND REGISTER SAVES

by

# Norman Jantz

# A thesis

submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Master of Science

Department of Electrical Engineering

Edmonton, Alberta Spring, 1990

National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le die d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

ISBN 0-315-60182-5

#### THE UNIVERSITY OF ALBERTA

#### RELEASE FORM

NAME OF AUTHOR: Norman Jantz

TITLE OF THESIS: A RISC Design Including Increased I/O Bandwidth

and Background Register Saves

DEGREE FOR WHICH THIS THESIS WAS PRESENTED: Master of Science

YEAR THIS DEGREE GRANTED: 1990

Permission is hereby granted to The University of Alberta Library to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly or scientific research purposes only.

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.

> (Signed) Moman Jant Permanent Address: 11523 - 76 Avenue Edmonton, Alberta

Canada

Dated: December 15, 1989

# THE UNIVERSITY OF ALBERTA

# FACULTY OF GRADUATE STUDIES AND RESEARCH

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies and Research, for acceptance, a thesis entitled A RISC Design Including Increased I/O Bandwidth and Background Register Saves submitted by Norman Jantz in partial fulfillment of the requirements for the degree of Master of Science.

Supervisor: Dr. Emil Girczyc

Keill a Strongence

Dr. Keith Stromsmoe, Dept. of E.E.

Dr. Ahmed Kamal, Dept. of C.S.

Dans Dec 15, 1989

#### Abstract

This thesis presents a novel 32 bit RISC architecture which achieves greater I/O bandwidth and executes fewer nonprocessing states than conventional RISC designs. Greater I/O bandwidth is achieved by encoding 2 instructions per 32 bit word, moving the program counter offchip, and by utilizing unidirectional busses. Fewer non-processing states are achieved by "background" register saves and restores and with pipelined memory accesses and instruction execution. The architectural design of the processor combines these novel features with good features of previous RISC designs to meet philosophical goals such as efficient use of I/O bandwidth and locality of information processing. The implications of the unconventional division between processor and external memory controller on the system level architecture are then discussed. Next, circuit designs and floorplans of the implemented IC are shown to verify that this architecture could be fabricated in a conservative CMOS technology. Finally, a summary of emulation and testing results is presented.

# Acknowledgements

I would like to thank my supervisor, Dr. Emil Girczyc, for his guidance and support throughout this research project. As well, I would like to thank Dr. Jack Mowchenko and other faculty members within Computer Engineering who showed patience and understanding as well as admirable professional qualities. In the design of ARC, several fellow students contributed in the initial stages including Duncan Glendenning, Tai Ly, Trevor May, and Mike Smith. In this research endeavor, many people contributed helpful suggestions to problems which had to be overcome. In this respect, I would like to thank Mak Paranjape, Stuart Olsen, Harold Peacock, Steve Sutphen, Rene Leiva, Trevor May, Trevor Monson, Doug Konrad, Ash Parameswaren, Joe DeAlmeida, and Scott Stephens. Most importantly, however, I would like to thank my parents and sisters, who were not only encouraging and supportive throughout this project, but also showed a great deal of understanding during my university education.

# **Table of Contents**

| 1. Introduction                                       | 1  |

|-------------------------------------------------------|----|

| 2. Previous Research                                  | 4  |

| 2.1 Instruction Set                                   | ě  |

| 2.2 Load and Store Architecture                       | 7  |

| 2.3 Registers                                         | 8  |

| 2.3.1 Special Purpose Registers                       | 8  |

| 2.3.2 General Purpose Registers                       | 8  |

| 2.4 Pipelining                                        | 9  |

| 2.5 Caching                                           | 12 |

| 2.5.1 Caching Techniques                              | 12 |

| 2.5.2 Overview of Instruction and Data Caching        | 13 |

| 2.6 Architectural Features of Stanford's MIPS         | 14 |

| 2.7 Architectural Features of the Ingrkeley RISC II   | 15 |

| 2.8 Summary of Previous Research                      | 18 |

| 3. Novel Concepts That Increase Speed and Efficiency  | 20 |

| 3.1 Two Instructions per 32-bit Word                  | 21 |

| 3.2 Unidirectional I/O                                | 22 |

| 3.3 Background Register Saves and Restores            | 23 |

| 3.4 Pipelined Memory Access and Instruction Execution | 24 |

| 3.5 External Program Counter                          | 26 |

| 3.6 Intelligent Memory                                | 27 |

| 3.7 Philosophy Behind ARC and MCU Design              | 28 |

| 4. Architecture                                       | 31 |

| 4.1 ARC Processor Architecture                        | 31 |

| 4.1.1 Datapath                                        | 31 |

| 4.1.1.1 The ALU                                       | 32 |

| 4.1.1.2 The Register File                             | 32 |

| 4.1.2 The I/O and Control Unit                        | 33 |

| 4.1.3 Instruction Set                                 | 34 |

| 4.1.3.1 ALU Instructions                              | 34 |

| 4.1.3.2 Transport Instructions                        | 36 |

| 4.1.3.3 Control Instructions                          | 45 |

| 4.1.4 Pipeline and Resource Scheduling                | 73 |

| · · · · · · · · · · · · · · · · · · ·                 |    |

| 4.2 ARC System Architecture                           | 56  |

|-------------------------------------------------------|-----|

| 4.2.1 Interface of ARC to Memory Control Unit         | 57  |

| 4.2.1.1 PC and Special Registers of the MCU           | 58  |

| 4.2.1.2 The Register Stack of the MCU                 | 59  |

| 4.2.1.3 MCU I/O Control                               | 59  |

| 4.2.1.4 MCU Caching                                   | 60  |

| 4.2.1.4 Optional MCU Functions to Enhance Performance |     |

| 5. ARC Circuit/Hardware Design Description            | 66  |

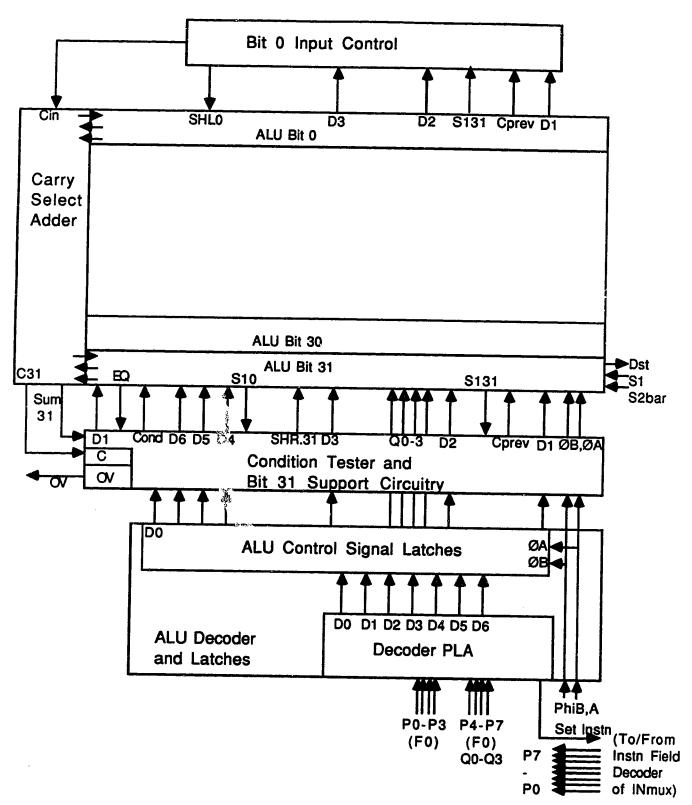

| 5.1 The Arithmetic and Logic Unit                     | 66  |

| 5.1.1 ALU Adder                                       | 68  |

| 5.1.2 ALU Decoder                                     | 68  |

| 5.1.3 ALU Bitslice Circuitry                          | 68  |

| 5.1.3.1 ALU Bitslice Schematics                       | 71  |

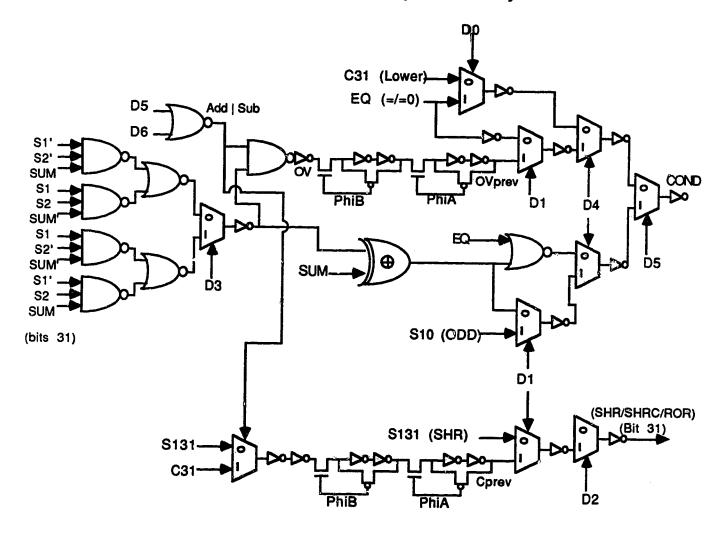

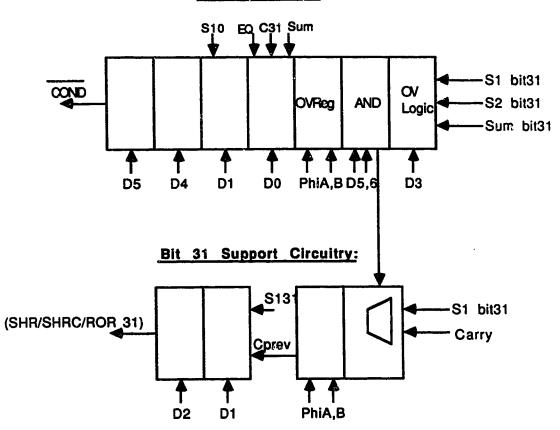

| 5.1.4 Condition Tester                                | 74  |

| 5.1.4 Condition Tester                                | 74  |

| 5.1.5 Other Non-Bitslice ALU Circuitry                | 77  |

| 5.2 Register File                                     | 78  |

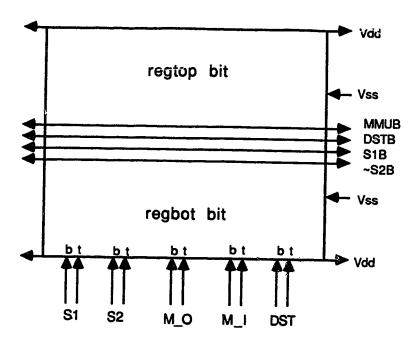

| 5.2.1 Register Array                                  | 82  |

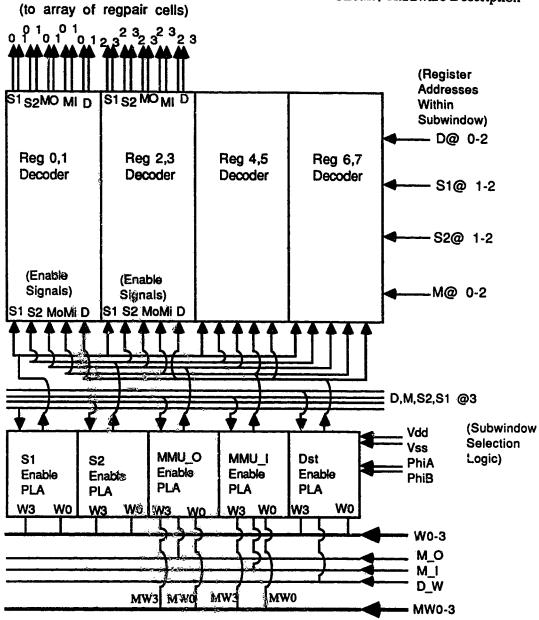

| 5.2.2 Subwindow Decoder                               | 84  |

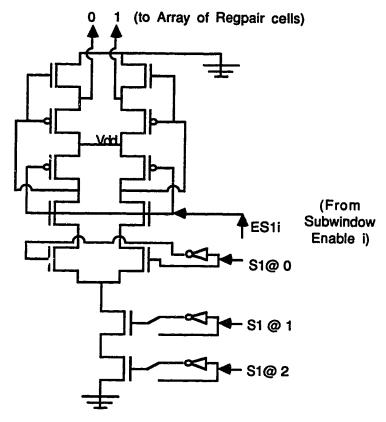

| 5.2.3 Subwindow Enables                               | 86  |

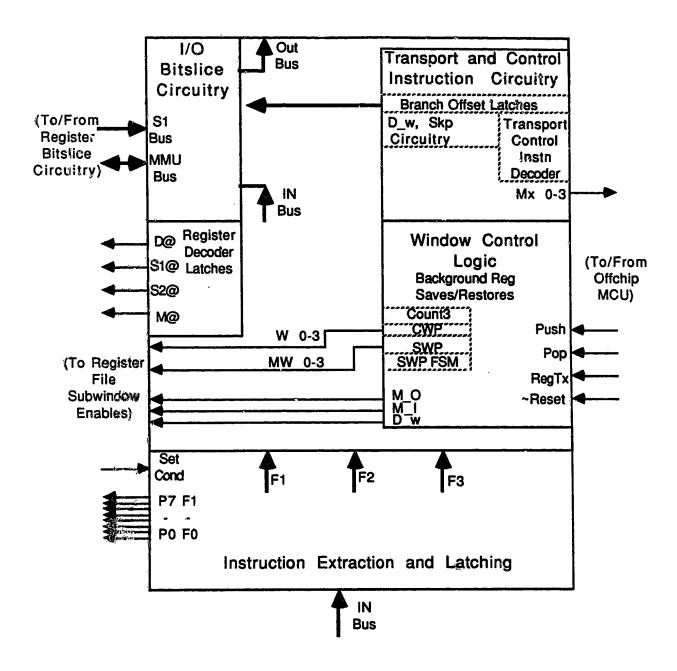

| 5.3 The I/O and Control Unit (IOCU)                   | 88  |

| 5.3.1 I/O Bitslice Circuitry                          | 90  |

| 5.3.2 Instruction Extraction and latching Circuitry   | 92  |

| 5.3.3 Transport and Control Instruction Circuitry     | 94  |

| 5.3.4 Window Control Logic                            | 97  |

| 6. Analysis of Concepts                               | 107 |

| 6.1 Emulation of Architecture                         | 107 |

| 6.2 Analysis of Architectural Features                | 107 |

| 6.2.1 Bandwidth Utilization/Availability              | 109 |

| (00 D 1 : 14 D 1 )                                    | 111 |

| 6.2.3 Bandwidth Available for Background Register     | 111 |

|                                                       | 112 |

| 20 43 Y                                               | 115 |

| / A / M                                               | 115 |

| (4)                                                   | 116 |

| / A / TT 111 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1            | 117 |

| /A/m + - +                                            | 117 |

|                                                       | 119 |

|                                                       | 119 |

|                                                       | 119 |

|                                                       | 120 |

| <b>** * * * * * * * * * * * * * * * * * *</b>         | 120 |

|                                                       | 121 |

| 7.1.5 Background Register Saves/Restores             | 121 |

|------------------------------------------------------|-----|

| 7.2 Further Work                                     |     |

| 7.2.1 Enhancements to Instruction Set                | 121 |

| 7.2.2 Improvements to Architecture/System            |     |

| 7.2.3 Improvements to Hardware                       |     |

| References                                           |     |

| Appendix A: ARC Emulator Listings                    |     |

| Appendix B: ARC Implementation of Example Algorithms |     |

# List of Figures

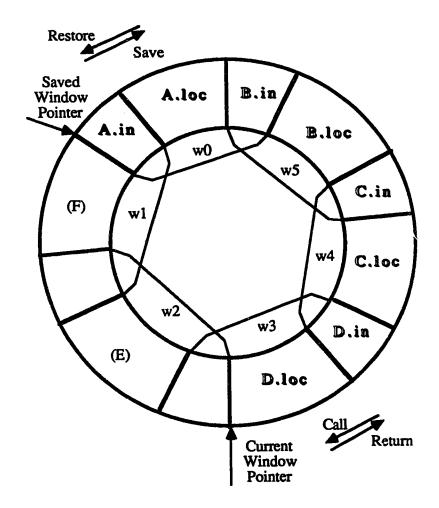

| Figure 2.1: Circular Buffer Organization of Overlapped Windows | Page 10 |

|----------------------------------------------------------------|---------|

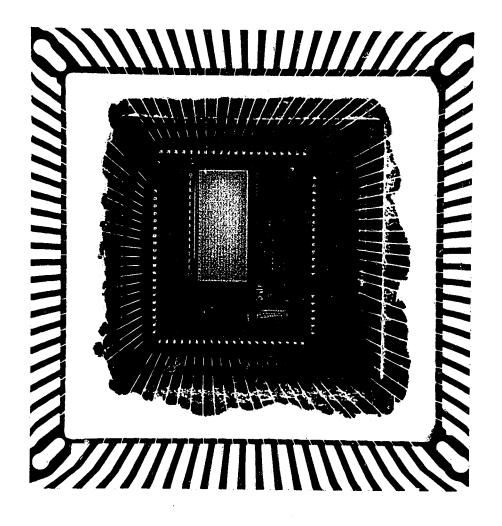

| Figure 4.1: Photograph of Bonded ARC Die                       | Page 32 |

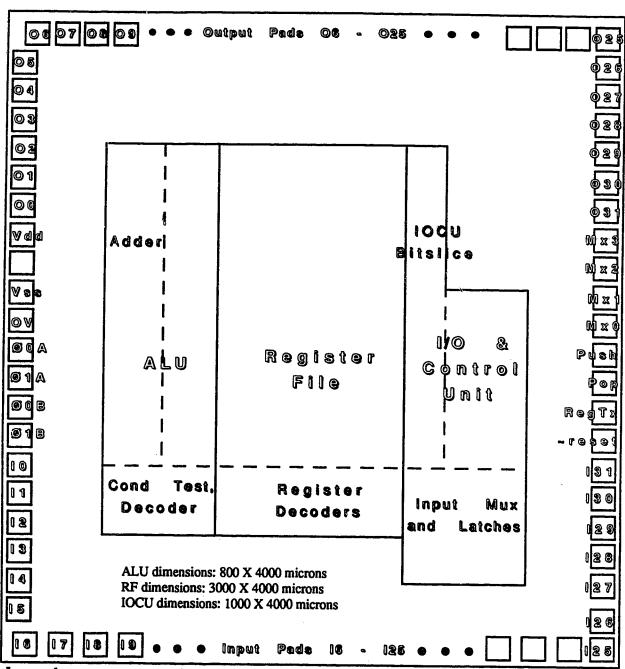

| Figure 4.2: ARC Block Diagram                                  | Page 33 |

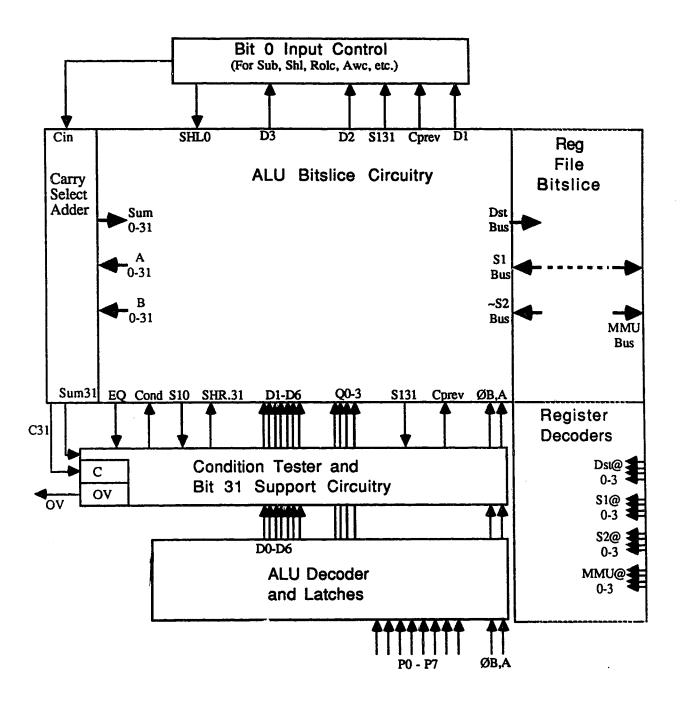

| Figure 4.3: ALU Block Diagram                                  |         |

| Figure 4.4: Register Stack Structure                           |         |

| Figure 4.5: I/O and Control Unit Block Diagram                 | Page 39 |

| Figure 4.6: Instruction Formats                                | Page 43 |

| Figure 4.7: Pipeline and Resource Scheduling                   | Page 49 |

| Figure 4.8: Timing of Load Instruction                         | Page 51 |

| Figure 4.9: Timing of Store Instruction                        | Page 53 |

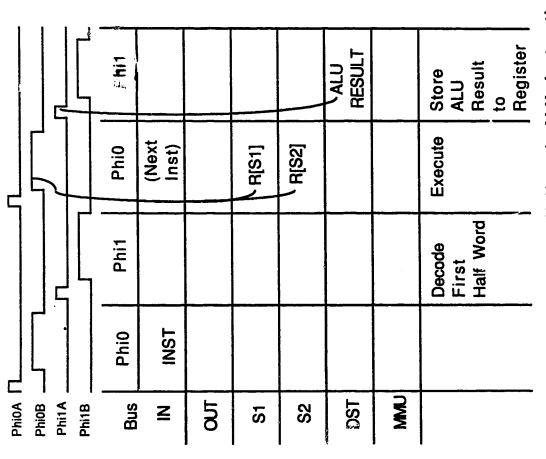

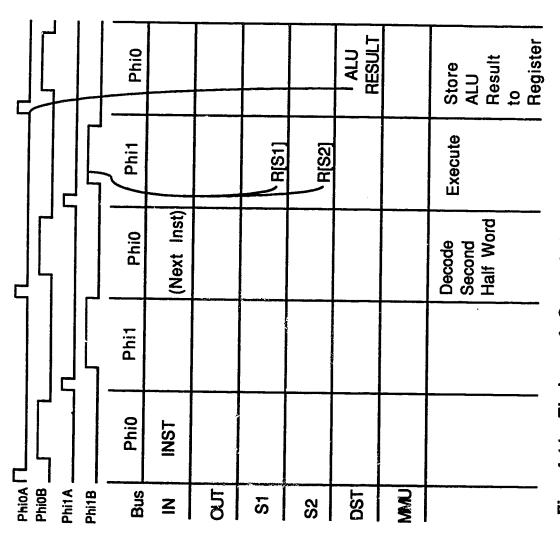

| Figure 4.10: Timing of First-Halfword ALU Instruction          | Page 54 |

| Figure 4.11: Timing of Second-Halfword ALU Instruction         | Page 55 |

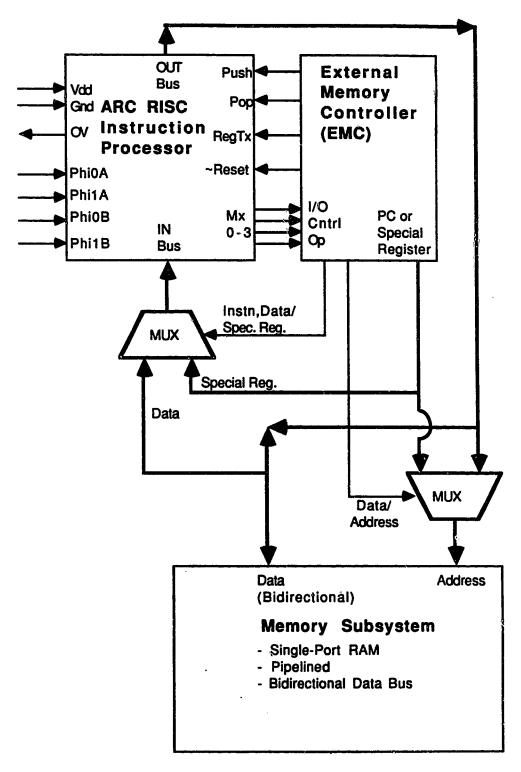

| Figure 4.12: ARC Interface to Single-Port RAM                  | Page 58 |

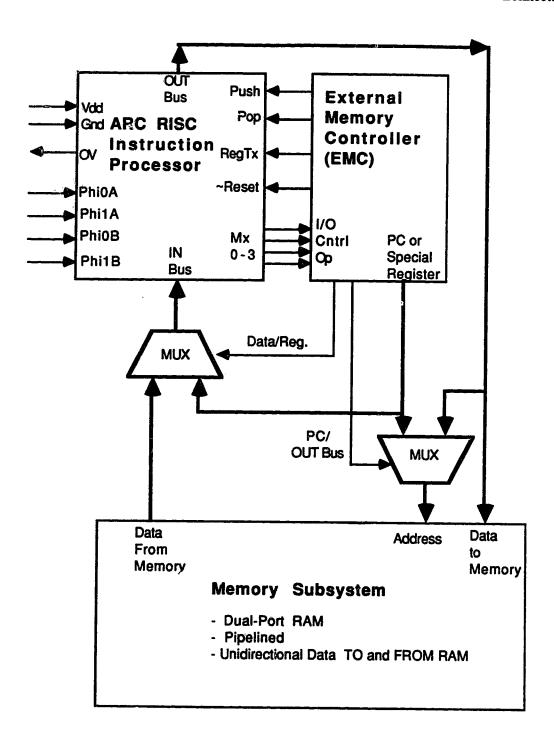

| Figure 4.13: ARC Interface to Dual-Port RAM                    |         |

| Figure 4.14: ARC System Diagram                                | Page 60 |

| Figure 5.1.1: ALU Floorplan                                    |         |

| Figure 5.1.2: ALU Decoder PLA Equations                        |         |

| Figure 5.1.3: ALU Bitslice Floorplan                           |         |

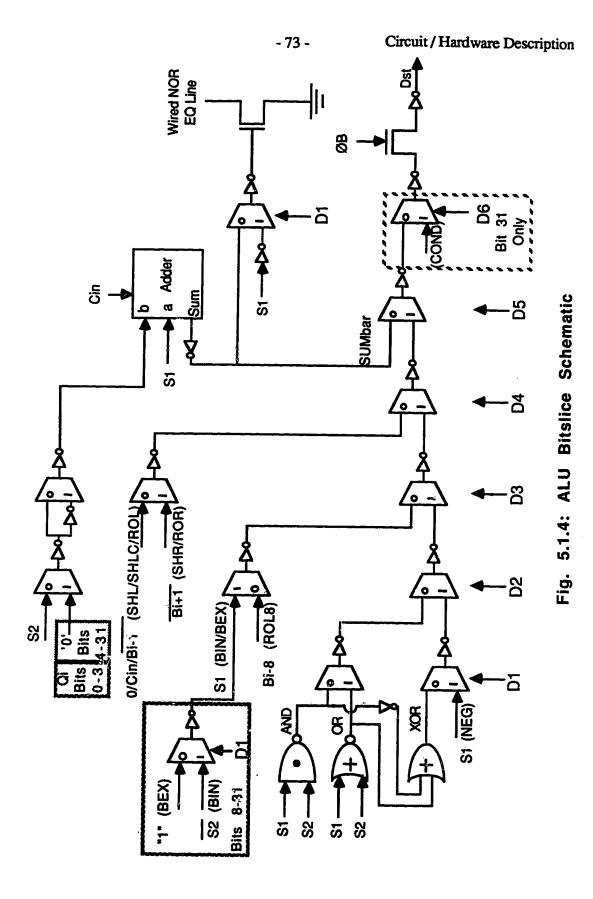

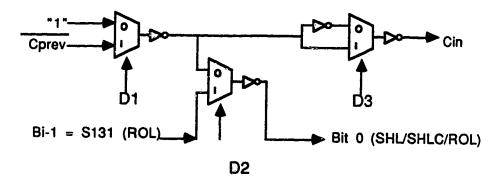

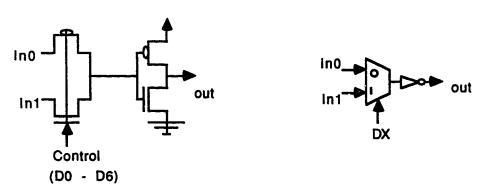

| Figure 5.1.4: ALU Bitslice Schematics                          |         |

| Figure 5.1.5: Non-Bitslice ALU Support Schematics              |         |

| Figure 5.1.6: ALU Transistor Schematics                              | Page  | <del>.</del> 76 |

|----------------------------------------------------------------------|-------|-----------------|

| Figure 5.1.7: Condition Tester Floorplan                             | _     |                 |

| Figure 5.2.1: Register File Floorplan                                | Page  | 80              |

| Figure 5.2.2: Register-Pair Cell Floorplan                           | Page  | 83              |

| Figure 5.2.3: Register Bit Schematic                                 | Page  | 83              |

| Figure 5.2.4: Subwindow Decoder Floorplan                            | Page  | 85              |

| Figure 5.2.5: Example Decoder Schematic                              | Page  | 86              |

| Figure 5.2.6: PLA Equations for Enable Circuitry                     | .Page | 86              |

| Figure 5.3.1: I/O and Control Unit Floorplan                         | .Page | 89              |

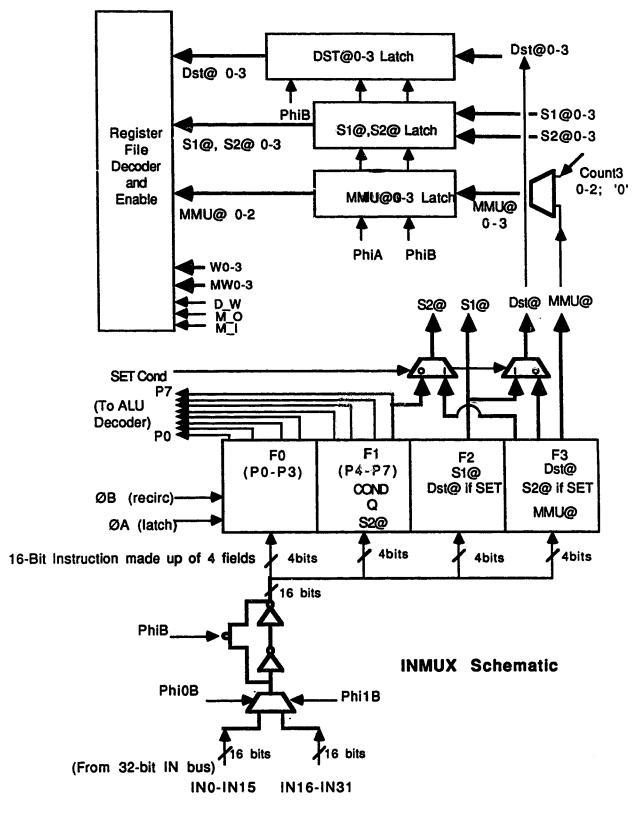

| Figure 5.3.2: Instruction Field Extraction/Multiplexing and Latching | .Page | 93              |

| Figure 5.3.3: I/O Control Opcodes and Decoder PLA Equations          | .Page | 95              |

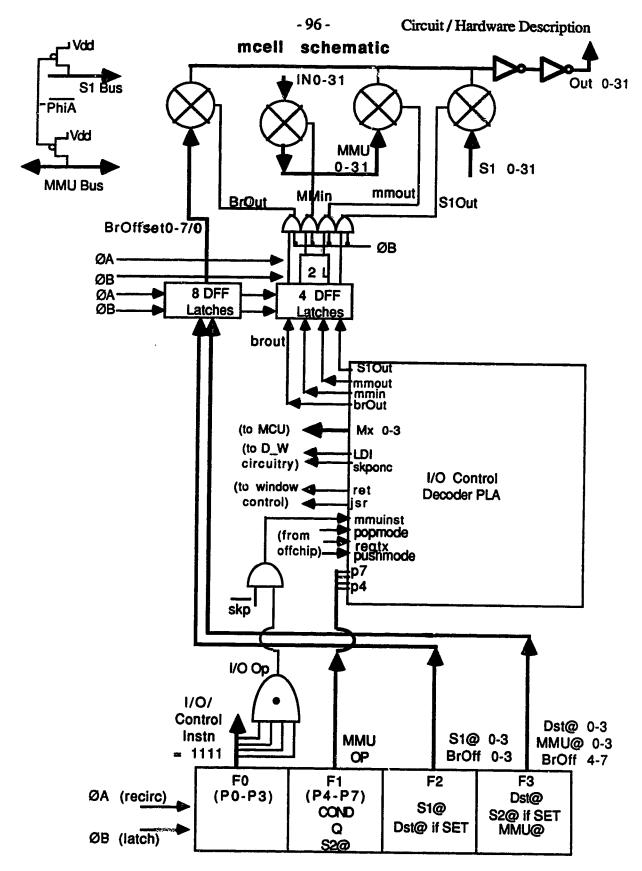

| Figure 5.3.4: I/O Control Operations Decoding and Latching           | .Page | 96              |

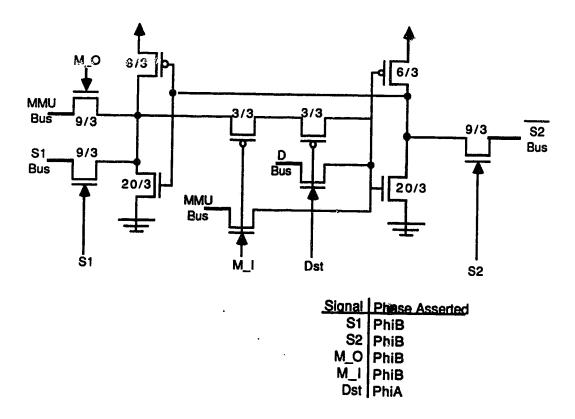

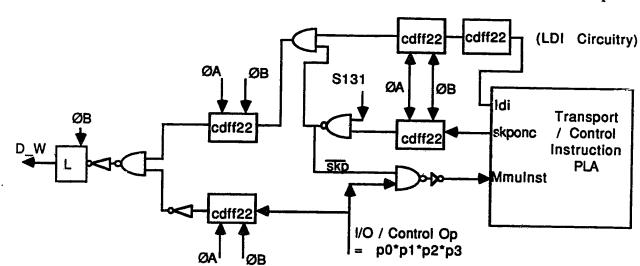

| Figure 5.3.5: Control Operations D_w Circuitry                       | .Page | 98              |

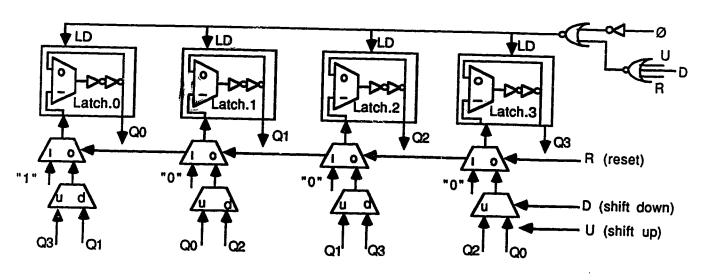

| Figure 5.3.6: 4-Bit Shift Register (SR4) Schematic                   | .Page | 100             |

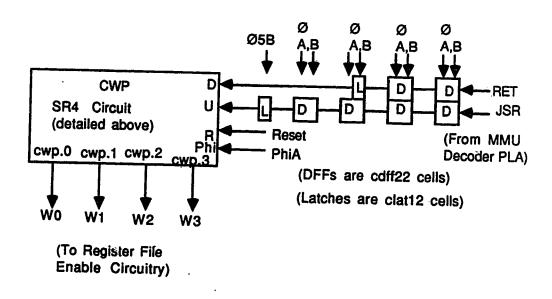

| Figure 5.3.7: Current Window Pointer (CWP) Schematic                 | .Page | 100             |

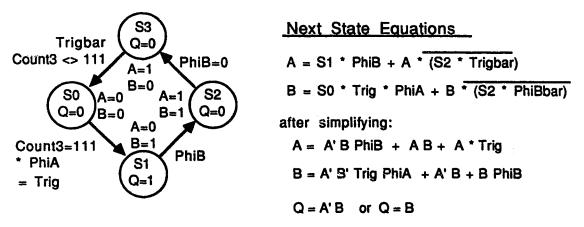

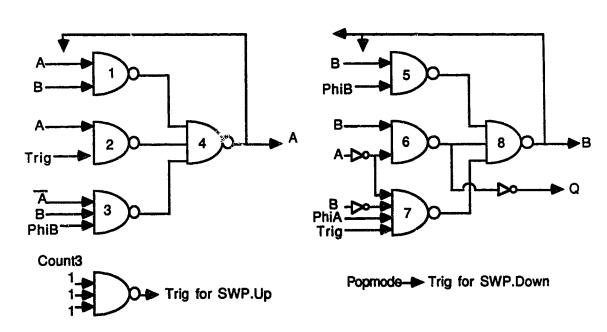

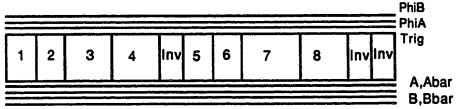

| Figure 5.3.8: SWP Circuitry Design, Schematics, and Floorplan        | .Page | 103             |

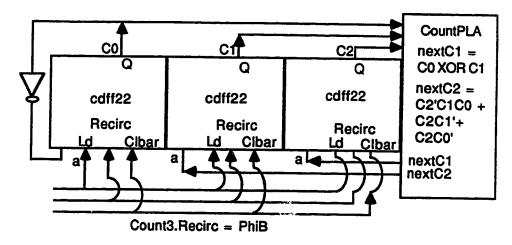

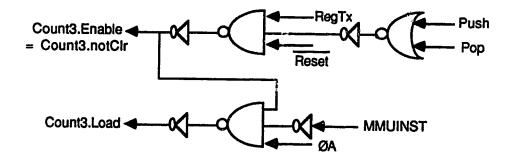

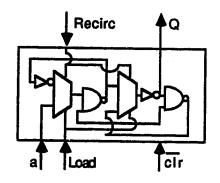

| Figure 5.3.9: 3-Bit Counter Schematics                               | Page  | 104             |

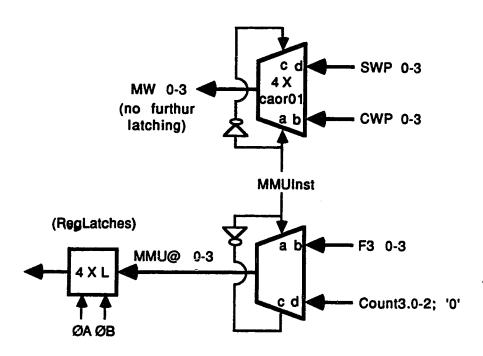

| Figure 5.3.10: MMU Bus Window and Address Multiplexing               | Page  | 106             |

# List of Tables

| Table 4.1: ARC Instruction Opcodes                   | Page 42  |

|------------------------------------------------------|----------|

| Table 4.2: Instruction/Operation Restrictions        | Page 57  |

| Table 6.1: Dynamic Benchmarks for Various Algorithms | Page 108 |

| Table 6.2: Static Instruction Statistics             | Page 110 |

| Table 6.3: Dynamic Instruction Statistics            | Page 110 |

| Table 6.4: Dynamic Push and Pop Opportunities        | Page 110 |

#### 1. INTRODUCTION

This thesis presents a Reduced Instruction Set Computer (RISC) architecture which combines *standard* RISC elements and ideas from previous research with a number of novel ideas. The result is a novel 32 bit RISC architecture with a number of advantages over conventional RISC architectures.

The RISC concept was first presented by Patterson and Ditzel in 1980 [Patt80]. The concept of RISC was presented because of evidence showing the non-optimal utilization of silicon resources of conventional CISC processors due to the increased complexity of their instruction sets. [Kate 83] The Reduced Instruction Set concept initially implies a simplification and reduction in size of the instruction set. This results in a higher frequency of operation because instructions which are rarely used and would slow down the other instructions are not included in the RISC instruction set. Typically, this increase in operating frequency more than offsets the cost of emulating the omitted instructions resulting in greater system performance. Additionally, the RISC concept has come to imply efficient use of silicon resources and an addition of complexity only when it will lead to better system performance.

The Alberta Risc Chip (ARC) incorporates ideas from several RISC architectures which have been developed over the past several years. From this research several architectural features have emerged as *standard* RISC elements. These standard elements provide guidelines in terms of instruction set design, register architecture, compiler design, and pipelining.

In addition to the standard RISC elements, characteristics from Stanford's MIPS [Henn82,83] and the Berkeley RISC [Kate83] [Patt82] were incorporated into the ARC architecture. In particular, these characteristics include the following:

a) circular, overlapping register windows. [Kate83] [Patt82]

- 2 - Introduction

- b) non-interlocked pipeline, optimizing compiler [Henn82,83]

- c) delayed branches [Henn82] [Kate83]

- d) lack of condition code [Henn82]

These features have been combined with a number of novel architectural ideas resulting from a VLSI architecture course offered during the fall of 1986, including:

- a) 2 instructions per 32-bit word

- b) unidirectional I/O busses

- c) external PC; intelligent memory or Memory Control Unit(MCU)

- d) "background" register saves and restores to memory or MCU.

- e) pipelined access to memory

These features are combined in the ARC design to realize:

- a) high I/O bandwidth available

- b) reduced delays from bus turnaround and skew by utilizing unidirectional I/O busses

- c) fewer nonprocessing states

- d) versatile interface to memory and other subsystems.

- e) implementable in very conservative technologies (3 micron CMOS) and scalable to more aggressive technologies.

- f) low pin count

These are discussed in more detail in Chapter 3.

#### 1.1. Conception of the Alberta Risc Chip (ARC)

This endeavor to design, implement, and test a RISC chip began as a VLSI architecture course taught by Dr. Emil Girczyc September through December, 1986. Five

students enrolled in the course including Duncan Glendenning, Norman Jantz, Tai An Ly, Trevor May, and Mike Smith. All of those involved participated in design discussions. The objective of the course was to study current RISC architectures, design and implement a RISC processor incorporating some original ideas and improvements. Limitations included the available process technology(3 micron CMOS), IC design software, and human resources(5 Students, 4 months). Through the course of the term, the novel architectural concepts of ARC (presented on the previous page) evolved.

During the course, preliminary versions of an ALU(by Tai Ly) and a register file(by Norman Jantz) were implemented in 3 micron CMOS. Trevor May and Mike Smith did some work on an instruction unit, and Duncan Glendenning did a partial design of an on-chip memory management unit. Due to time limitations, the instruction and memory management units were not implemented.

# 1.2. Thesis Objectives

The objectives in preparing for this thesis have been:

- a) to correct, improve, and complete the design outlined during the course.

- b) to demonstrate that the architecture could be implemented in an available technology, (i.e.: 3 micron CMOS).

- c) to verify the advantages of the architectural concepts

Architectural improvements to the class design include refining the instruction set, pipeline, intermodule communications, as well as resource and bus scheduling. In all cases the major architectural concepts remain the same while the implementation is defined or improved (see Chapter 4 and 5). The architecture was verified by an emulator program as described in Chapter 6.

Some ALU and register file hardware was designed during the course but architectural improvements and rigid area requirements led to a complete reimplementation

- 4 - Introduction

of this circuitry. The instruction unit (IU) and on-chip memory management unit (MMU) were merged into the I/O Control Unit (IOCU) which was designed from scratch. The first full implementation of ARC was submitted for fabrication in Northern Telecom's 3 micron CMOS process during January, 1989. Due to implementation errors as described in Section 6.3, the design was only partially functional. Chapter 7 summarizes the evaluation of the novel architectural features and suggests future research.

#### 2. PREVIOUS RESEARCH

In the past several years, there has been increasing interest in the RISC architecture philosophy. Many microprocessor manufacturers have subscribed to the RISC architecture philosophy and extensive research and development has been undertaken by both corporations and universities. From this research, several architectural features have become widely accepted as standard RISC elements [Stall88]. These standard RISC elements have been incorporated into ARC and are presented as follows:

- A limited and simple instruction set.

- A large number of registers.

- Load and store access to memory.

- All instruction operands in registers.

- A strategy of maximizing the use of registers and minimizing references to memory.

- The use of an optimizing compiler

- An emphasis on optimizing the pipelined execution of instructions to approach a throughput of 1 instruction per cycle.

A Summary of recent work in these areas will be presented below.

The two architectures most influential in the development of ARC, Stanford's MIPS [Henn82,83] and Berkeley's RISC [Kate83], will also be presented. The MIPS architecture was influential in terms of pipelining, instruction set, and philosophical issues. The Berkeley architecture was influential in terms of it's register file structure.

#### 2.1. Instruction Set

In general, the size of the instruction set can be viewed as a tradeoff between hardware and software/compiler complexity. Increasing the size of the instruction set, for example, would increase the amount of ALU and instruction decoder logic, require

more silicon area, and slow down the execution speed. Besides slowing down other instructions, a complex instruction or addressing mode is sometimes slower than a customized sequence of simpler instructions [Patt80], [Stal88]. The Reduced Instruction Set concept argues against large or complicated instruction sets for precisely the above reasons. On the software side, an increase in complexity is realized because the compiler has to deal with the following issues:

- emulation of complex instructions or addressing modes

- increased code size

- pipeline restrictions and operand dependencies

- code optimization and reordering

- reordering instructions after branches

- register allocation

For the compiler, it is a simple matter to emulate a complex instruction or addressing mode with a few simpler instructions. Because of this, the size of a RISC executable file is usually larger than a CISC executable. This results in a greater instruction bandwidth requirement.

Pipeline conflicts are a result of the way instructions utilize hardware resources. Having the compiler generate code that is free of pipeline conflicts simplifies the hardware because hardware resource allocation/interlocking is not required. To insure proper pipeline operation, the compiler must reorder instructions to insure a valid instruction sequence free of pipeline conflicts and satisfying all operand dependencies. The compiler must insure that an operand must be loaded into a register before being processed. This is achieved by ordering code such that a sufficient number of cycles separate the LoaD instruction of an operand and the first instruction processing this data. Most RISC compilers also optimize and reorder the code produced by packing independent instructions together, replacing NOPs, etc. Additional relationships

between the pipeline and the compiler will be presented later in the pipelining discussion.

A register allocation algorithm is required by all RISC compilers. This algorithm ensures that the least number of LoaD instructions are used to load register operands into registers which reduces I/O bandwidth and increases performance.

# 2.2. Load and Store Architecture

In general, the number of addressing modes can be viewed as a tradeoff between hardware and software complexity. Several addressing modes, as in CISC architectures, would greatly increase the amount of instruction decoder and pipeline scheduling logic, require more silicon area, and slow down the execution speed. According to the RISC concept, only essential addressing modes should be used and addressing modes which are seldom used and which slow down the processor should not be included. Therefore, most RISC machines follow the load-and-store architecture.

Load-and-store machines have 2 types of instructions: a) instructions which transfer data between memory and registers, and b) instructions which process data in registers (ALU instructions). Therefore, this type of architecture usually only has 2 simple addressing modes for ALU instructions (Register-Register and Register-Immediate). The advantages of a load-and-store architecture include hardware simplicity and increased performance. The hardware simplicity results from the simplified execution and decoding of few addressing modes. In terms of added software complexity, compilers do not have a difficult time generating code for load-and-store architectures because they simply first get the operands, then use them. Performance is increased by keeping operands in registers so that processing does not stop for operands to be loaded from memory [Henn 82] [Kate 83].

## 2.3. Registers

Registers may be divided into special purpose and general purpose registers. Special purpose registers usually include control and status registers such as the program counter and the condition codes. General purpose registers are always user-visible and usually contain data and addresses. RISC processors differ greatly in the number and types of registers as described in the following subsections.

# 2.3.1. Special Purpose Registers

Each CPU architecture uses a different set of special purpose registers. While the MIPS machine [Henn82] has done away with a special condition code (CC) flag register, the current trend still seems to be towards including special purpose control and status registers [Stal88]. Most machines have a Program Status Word (PSW) which usually contains the Program Counter (PC), Flags (e.g.: Overflow, Carry, Negative, CC, interrupt), security codes, etc. Machines with PSWs can recover from interrupts by restoring the PSW and other special and general purpose registers.

#### 2.3.2. General Purpose Registers

Increasing the size of the general purpose register file will increase performance because more temporal and spatial locality of an executing program is captured. As the size of the register file is increased, it becomes necessary for a subset of the registers to be "active" at a time because:

- It becomes difficult to set the optimum unstructured register utilization for a program with many procedures at compile time.

- Restrictions on number of bits available in an instruction for two(or more) register addresses.

Overhead of context switches and procedure calls which must save all registers used as well as those storing global variables.

The register window concept was pioneered by the Berkeley RISC group who imposed a circular buffer structure on their register file [Patt82] [Kate83]. This circular buffer structure facilitates procedure calls and returns and parameter passing between procedures via overlapping register windows. Research done by members of the Berkeley RISC team indicates that about 94% of procedure activations are passed fewer than 5 arguments and use fewer than 12 words of arguments and local scalars. Therefore, an overlap of 4-8 registers and approximately 8-12 local registers per activation will usually be enough for a typical procedure activation. Fig. 2.1 (extracted from [Kate83] of the Berkeley RISC group) shows the "Circular Buffer Organization of Overlapped Windows". A register file based on the Berkeley RISC is incorporated into the ARC.

# 2.4. Pipelining

Most RISC machines utilize pipelining to increase instruction throughput and achieve a high frequency of operation [Stall 88]. Pipelining can be used to speed up the execution of instructions by decomposing instructions into several stages, each of which utilizes a different set of the processor's resources. This results in a greater operating frequency because the critical path of every stage is less than the critical path of the entire instruction. Throughput is maintained if instructions are sufficiently independent with respect to pipeline conflicts and operand dependencies.

In RISC machines, a common instruction processing pipeline consists of the following stages:

Calculate next instruction address: Put the program counter onto the address bus.

Resources required: PC, address bus

# Legend:

w0-w5 denote the 6 overlapping windows, each divided into 3 segments. For example, w0 has 10 local registers (A.loc), 6 registers used to transfer input parameters from the calling function (A.in), and 6 registers which are used to transfer parameters to the called function (B.in).

# **Function Calls**

The above diagram portrays register window usage if function A called function B, function B called function C, and function C called function D. Function D is currently executing.

Fig. 2.1: Circular Buffer Organization of Overlapped Windows

- b) Fetch instruction: Read the next expected instruction into a buffer.

Resources required: input data bus, instruction buffer 1.

- c) Decode: determine the opcode and register operands.

Resources required: decoder, instruction buffer 2.

- d) Execute: Perform instruction operation with register operands.

Resources required: ALU, operand busses from registers.

- e) Store Result: Store result in register file.

Resources required: bus to register file.

Depending upon the specific processor, the above example pipe stages may be combined to make the pipeline shorter, or further decomposed to lengthen the pipe and increase the clock frequency. Ideally, all pipe stages should have equal delay to maximize efficiency.

The above pipeline will operate smoothly as long as there are no conditional branches and all operands are in registers. Conditional branches are handled in the MIPS and RISC I machines [Henn82] [Kate85] by a "delayed branch" technique. In this technique, the instruction following a conditional branch is always executed to allow time for the conditional branch and next address calculation to clear the pipe.

Practical limits are placed on the number of pipeline stages by the *delayed* branch, and operand dependencies. It is the responsibility of the compiler to reorder the instructions to insure that:

- a) operands are prefetched into registers (LoaD Instruction),

- b) after each conditional branch there exists an instruction (or NOP), which does not depend on the branch, to keep the pipeline full.

- c) operand (register) dependencies are taken into account.

If an operand of an instruction is the result of a previous instruction, idle cycles (NOPs) may be inserted to delay the start of that instruction until the previous one has

completed. In general, the higher the number of pipe stages, the more difficult it is for the compiler to create NOP-free code.

# 2.5. Caching

An I/O bottleneck problem exists in current RISC processors because, according to the standard elements, they ought to execute one instruction per cycle. This means an instruction fetch every cycle which would use all address and data bus bandwidth. Most modern RISC architectures combat this problem by embracing hardware cache support and/or on-chip caches to attain better performance [Furl89]. The caching techniques vary between processors. Intel favors a unified instruction and data cache while Motorola favors separated instruction and data caches (as per the Harvard Architecture) in current and future RISC and CISC processors. Most other RISC chips incorporate an on-chip instruction cache and off-chip data cache to combat the I/O bottleneck problem. The Commercial version of MIPS (MIPS-X) [Horo87] uses both a 2-kbyte on-chip instruction cache and an external interface for high-speed cache access to provide the required memory bandwidth for the processor.

Caching has become necessary to achieve high performance in microprocessor systems. This is particularly so with RISC processors because slower memory cannot supply data at the high clock frequency without wait states given the high I/O bandwidth requirements resulting from an instruction throughput of 1 instruction per cycle. Typical RISC clock speeds have not only increased past the capability of DRAM main memory, but even faster, much more expensive SRAM cannot keep up with RISC processors running above 25 MHz and beyond [Furl89]. Even techniques such as page-mode interleaving for the main memory - where two (or more) banks of RAM may be accessed alternately to reduce the apparent access time - is not good enough because it will cause wait states more frequently than will a cache.

# 2.5.1. Caching Techniques

Issues in selecting a caching technique include cache placement in the system as well as whether instruction and data caches should be separate or unified.

Placing the cache on-chip or before the address translation of the MMU creates what is called a virtual cache [Furl89]. Because most processors use virtual address locations, a cache that can access data directly from the virtual address without looking up the physical equivalent, will be more effective.

The issue of whether to use a Harvard architecture (divided instruction and data caches) or to use a unified cache is a tradeoff between bandwidth requirements and resource limitations. The Harvard architecture provides an increase in memory bandwidth. The increased memory bandwidth results from an address and data bus to the instruction cache and another address and data bus to the data cache. Therefore, a Harvard architecture machine may have double the bandwidth and also double the number of bus lines and bus pins. A unified cache can encounter more bus contention between data and instruction than a divided cache but a lower pin-count will result.

The ARC may be interfaced to unified or separate instruction and data caches which use virtual addresses.

# 2.5.2. Overview of Instruction and Data Caches

Instruction caches are normally implemented on-chip because with 1 instruction fetched from cache instead of memory per cycle, the bandwidth saving is high and because the behavior of instructions is well understood as described by [Kate83].:

Instruction fetches are read-only accesses. They are sequential in small blocks (between if or call or loop statements). Locality arises from the repeated accesses to instructions inside loops. Since programs spend most of their time in small inner loops, this locality is high

The above behavior allows for a simple instruction cache design.

Data caches are generally larger and more complex than instruction caches and therefore usually implemented as part of an off-chip MMU due to silicon area restrictions. Data memory references are not as predictable as instruction referencing. Locality arises from repeated accesses to the same scalar variables or to sequential access to non-scalar variables such as arrays and structures. For a detailed discussion of microprocessor cache architectures, the reader is referred to [Furl89] [Kate83] [Kado87] [Horo87] and [Hunt87].

#### 2.6. Architectural Features of Stanford's MIPS [Henn82,83]

The Stanford MIPS project [Henn82,83] concentrated on obtaining maximum performance by making simultaneous tradeoffs across three areas: hardware, software support, and systems support. After considering possible design tradeoffs, the MIPS designers opted for less hardware and more complex software. Key features of MIPS in which this is apparent include: load/store architectures, packing constants into instructions, omission of condition codes, word-addressed machines, and imposing pipeline interlocks in software (optimizing compiler).

Load/store architectures require that operands be loaded into registers, from which they are processed. Load/store architectures can yield performance increases if frequently-used operands are kept in registers. The MIPS designers therefore used a large number of registers and an efficient register allocation algorithm as part of the compiler.

To further reduce the number of loads from memory to registers, the MIPS designers also incorporated 4-bit and 8-bit constant fields into some instructions. By studying a collection of programs, they determined that a 4-bit constant would cover 70 % of the cases in which a constant was necessary. An 8-bit constant(allowing a character constant) would cover 95 % of the cases.

The MIPS designers argued against the use of condition codes because they are difficult to implement, difficult for compiler writers, and inefficient for conditional control flow breaks. Condition codes are difficult to implement because they are irregular structures, some instructions set the condition code and others do not. This causes additional logic for condition code control and problems with branches in a heavily pipelined machine (pipe may have to clear or be flushed before a branch). Condition codes are difficult for compiler writers, especially in nonorthogonal architectures, because condition codes are side effects of instruction execution. In terms of efficiency, the MIPS designers compared the use of condition codes in conditional control flow with their scheme of conditionally setting the contents of a general purpose register to 0 or 1, and found the MIPS scheme faster. One notable exception to this scheme was the overflow flag which generates a processor interrupt in the MIPS.

Word-based addressing is advocated by the MIPS designers because it has a lower overhead associated with each fetch or store, and word references occur much more frequently than byte references. To make a word-based approach feasible, special support for accessing bytes was provided in the MIPS instruction set.

Finally, and perhaps most significantly, the MIPS designers advocate shifting the burden of cost from the hardware to the compiler. The MIPS design depends upon a more complex compiler capable of imposing pipeline interlocks and delayed branches by reordering instructions and insertion of NOPs. This resulted in much simpler and much faster hardware. This shifting of the complexity from hardware to software has several major advantages as described by [Henn82].:

The complexity is paid for only once during compilation. When a user runs his program on a complex architecture, he pays the cost of the architectural overhead each time he runs his program. It allows the concentration of energies on the software, rather than constructing a complex hardware engine, which is hard to design, debug, and effectively utilize.

#### 2.7. Architectural Features of the Berkeley RISC II

The designers of the Berkeley RISC [Patt82] [Kate 83] analyzed the behavior of high level language (HLL) programs, patterns of procedure calls and returns, as well as the optimization of register usage. In addition, they studied the trade-offs between size, complexity, and speed to obtain the most effective use of the scarce hardware (silicon) resource in the execution of HLL programs.

The Berkeley RISC project began in the spring of 1980. The RISC I processor was implemented in the fall of 1980. Additions to the instruction set and changes to the on-chip organization/communication resulted in the RISC II by spring 1983.

The RISC II has 39 instructions. These instructions are subdivided into 4 categories:

- 12 ALU instructions

- 16 Memory Access (Load/Store) instructions

- 7 Branch and Call instructions

- 4 Miscellaneous Instructions

All instructions are 32 bits in size. Most instructions contain 3 operands with 2 sources and a destination register specified in the instruction. There are also some two- and single-operand (address) instructions. For memory access instructions, there are two addressing modes: a) indexed (contents of register + immediate offset), and b) PC relative (PC + immediate offset).

The RISC II has 138 32-bit working registers available to the user. Each procedure can access 32 of these registers. The first 10 registers, R0, R1, ..., R9, are global registers and are always accessible. The other registers are called window registers. 22 of these registers, R10, R11, ..., R31, are accessible within a procedure. Ten of the registers, R16 to R25, within each register window are local registers. Registers.

ters R10 to R15 are used to hold parameters passed by the current procedure to a called procedure. Registers R26 to R31 hold parameters passed to the current procedure from the procedure which called it.

There are 8 windows in the RISC II register file. The current window is indicated by the 3-bit Current Window Pointer (CWP) of the Program Status Word (PSW). When a procedure call occurs, the CWP is decremented (mod 8). When a procedure return occurs, the CWP is incremented (mod 8). To support the register organization described above, the register windows are organized in a circularly overlapping fashion so that all register windows have 6 registers in common with each of the adjacent register windows. The registers which overlap are used for parameter passing between procedures. The circularly overlapping structure of the RISC multi-window register file is shown in Fig. 2.1.

The most recently used window of the register file which has been saved to memory is indicated by the 3-bit Saved Window Pointer (SWP) of the PSW. When a procedure call occurs so that CWP would become equal to SWP, a register file overflow occurs. Similarly, when a procedure return occurs so that the CWP would become equal to the SWP, a register file underflow occurs. These underflow and overflow traps essentially occur when there is no more space in the register file. When a register overflow occurs, a register window is saved to memory and when a register underflow occurs, a register window is restored from memory. Tamir and Sequin [TaSe83] have investigated this aspect of the RISC architecture and concluded that the best strategy is to save only one window per overflow trap. In the ARC processor, improvements on the above scheme for saving and restoring registers have been made. In the ARC, register windows are saved and restored in the background without halting or a context switch to an interrupt service routine. The background register save/restore concept will be explained further in chapter 3.

The RISC II instruction pipeline has three stages: a) Fetch, b) Compute, and c)

Write. As well, a delayed branch feature has been incorporated into the RISC II. This means that the jump or branch takes effect only after the instruction following the branch has been executed. Another restriction of the RISC II pipeline was that the pipeline was suspended during data memory accesses. This suspension occurred because the address and data busses are used for the data load or store thereby disallowing instruction fetches to occur (which also require the address and data busses). As well, the RISC II register file allows only one register-write per cycle. This means that a dummy pipeline stage must be inserted into all instructions at the place where loads perform their memory access. An on-chip instruction cache would combat the problem of pipeline suspension during data access as long as a cache miss does not occur. Pipelined memory access (more than 1 memory access in progress at a time) combined with dual-ported memory would also alleviate the problem.

# 2.8. Summary of Previous Research

The ARC architecture incorporates many standard RISC characteristics:

- A limited and simple instruction set.

- A large number of registers.

- Load and store access to memory.

- All instruction operands in registers.

- A strategy of maximizing the use of registers and minimizing references to memory.

- The use of an optimizing compiler

- An emphasis on optimizing the pipelined execution of instructions to obtain a throughput of 1 instruction per cycle.

In addition to the standard RISC elements, characteristics from Stanford's MIPS [Henn82,83] and the Berkeley RISC [Kate83] [Patt82] were incorporated into the ARC

architecture.

In particular, these characteristics include the following:

- a) circular, overlapping register windows. [Kate83] [Patt82]

- b) non-interlocked pipeline, optimizing compiler [Henn82,83]

- c) delayed branches [Henn82] [Kate83]

- d) lack of condition code [Henn82]

Most RISC processors require caching techniques to obtain sufficient I/O bandwidth and an instruction throughput of 1 instruction per cycle. This is evident in the commercial versions of the RISC II [Kate85], and the MIPS-X [Horo87], both of which require an on-chip instruction cache and off-chip data cache. The more aggressive Motorola 88000 RISC chip utilizes a Harvard architecture cache structure to facilitate high I/O bandwidth. ARC employs I/O bandwidth reduction to eliminate the need for an on-chip cache (as long as the memory is fast enough). If memory is not fast enough, ARC will require a cache structure. Separate instruction and data caches could be used to afford some advantages of the Harvard architecture with fewer bus lines and pins. If the process technology permits, the cache(s) together with other memory management functions can be moved on-chip. The novel concepts of the ARC which increase performance are presented in the next chapter.

#### 3. NOVEL CONCEPTS THAT INCREASE SPEED AND EFFICIENCY

A number of novel concepts have been introduced with ARC which afford improvements over previous RISC designs. These concepts include:

- a) 2 instructions per 32-bit word

- b) unidirectional input and output busses

- c) background register saves

- d) pipelined memory access

- e) external program counter and associated logic

- f) memory control unit (MCU) or intelligent memory

The improvements are realized in terms of greater I/O bandwidth available, fewer nonprocessing states, and the ability to access slow memory. Greater I/O bandwidth is available because concepts a), c), e) and f) cause a reduction in the total bandwidth required for instruction fetches and subroutine calls, while concepts b), c), e), and f) are used to balance the bandwidth between the I/O resources available. The ARC has fewer nonprocessing states because of the MCU and background register saves. The ARC may also be interfaced with slow memory by pipelining memory access.

The increase in available input bandwidth results largely from packing two instructions per word, and from the unidirectional IN bus. The increase in available output bandwidth results largely from the external PC (instruction addresses do not originate from ARC) and from the unidirectional OUT bus. Conventional and RISC processors normally increase their available bandwidth by having on-chip instruction and/or data caches. This works well for traditional programming languages which display good locality properties. In comparison, techniques to be detailed in this chapter for increasing ARC's available bandwidth do not rely upon program locality and thus should provide better support for languages such as LISP and Smalltalk. Nonetheless, the ARC techniques can also operate in conjunction with a cache struc-

ture to gain the normal benefits of caches.

Background register saves and restores are made possible by the large amount of available bandwidth. This feature allows procedure calls and returns to occur with a minimum of LoaD and STore overhead associated with restoring/saving register windows.

The division/interface between ARC and the MCU (or intelligent memory) is also a key concept which results in a desirable division/interface between processor and memory. This interface between ARC and the memory system forms the basis of a set of philosophical objectives detailed at the end of this chapter.

# 3.1. Two Instructions per 32-bit Word

The available input bandwidth is significantly increased by encoding most ARC instructions into 16 bits. Thus two instructions are loaded in most 32-bit instruction fetches. As the ARC executes 1 instruction per cycle, the unidirectional IN bus is available for data transfers every second cycle. This reduces the I/O bottleneck, leaving bandwidth on the IN bus available for incoming data or register restores. In addition, halfword instructions are easier to decode and should result in less memory and cache space required for executable code than would fullword instructions. The reduction in cache space required is an important feature because cache memory is always at a premium if it is to be implemented on the same IC as the ARC or the MCU.

To gain the above advantages, several tradeoffs were made. Because the instructions are restricted to 16 bits in length, the instruction set is limited and slightly less orthogonal than it might be otherwise. As well, the register operand fields are only 4 bits wide so that a maximum of 16 registers can be addressed. Therefore the register windows contain 16 registers and only 1 16-register window is available to each procedure. These disadvantages are not serious because the instruction set is adequate and follows the RISC philosophy and the register window size is only 6 smaller than

that of the Berkeley RISC II but missing 10 global registers. The advantages of greatly reducing the I/O bottleneck and of reducing memory and cache requirements should outweigh these disadvantages.

#### 3.2. Unidirectional I/O

Conventional microprocessors have a unidirectional address bus and a bidirectional data bus. In conventional microprocessors, the address bus is used for both instruction addresses and data addresses, while the data bus is used for instructions, incoming data and outgoing data.

Higher performance microprocessors with high I/O requirements such as the Motorola 68030 and 88000 follow the Harvard architecture scheme. This is a four bus architecture having an instruction address bus, a data address bus, an instruction input bus and a bidirectional data bus. The Harvard architecture eliminates conflicts between instructions and data at the expense of additional pins and busses.

In the ARC, outgoing data addresses and data utilize the OUT bus while instruction pairs and incoming data utilize the IN bus. This I/O structure provides equal input and output bandwidth resources to support the almost equal input and output bandwidth demand which results when instruction addresses do not originate from the cpu. The ARC processor has certain similarities with Harvard architecture processors, using time division multiplexing (TDM) to eliminate the high pin count. The ARC architecture may be considered as a TDM Harvard architecture with respect to the IN bus because the IN bus is reserved for instructions and data on even and odd clock phases respectively. The ARC can also be interfaced to separate instruction and data caches as is done in the Harvard architecture. ARC does not require as much I/O bandwidth as is available with the Harvard architecture because of the features which reduce the necessary I/O bandwidth requirements. Conflicts between instructions and data are resolved by pipelining as explained in sections 3.4 and 3.5.

ARC has higher input bandwidth available than a conventional RISC. This is because ARC's IN bus supports incoming instruction pairs and incoming data. In comparison, the conventional data bus must support outgoing data in addition to incoming full-word instructions and incoming data. ARC also has a higher output bandwidth available for data transfer. This is because ARC does not need to send out an instruction address on each cycle as is necessary with conventional processors.

Further, the traditional bus structure of most RISCs incorporates a bidirectional bus. The associated bus *turn-around* delay and clock skew may reduce the maximum operating frequency. Utilizing uniclirectional busses in ARC eliminates bus turnaround delays and makes complicated bidirectional drivers/receivers between the processor and memory unnecessary. <sup>1</sup>

As well, unidirectional busses may make it easier to design a pipelined memory subsystem, impossible in a conventional system with a bidirectional data bus. The ARC's unidirectional bus system eliminates bus conflicts between data to be stored and data to be loaded.

# 3.3. Background Register Saves and Restores.

To reduce the number of nonprocessing states, the ARC design supports back-ground register saves and restores. The ARC includes a register file made up of circular overlapping register windows, similar to those developed in the Berkeley RISC [Patt82]. During procedure calls, a new register window becomes the "active" window. The "active" window holds the only registers that can be accessed by ARC instructions. To reduce the number of wait states (LoaD or STore instructions) associated with restoring or saving the window context to a register stack, the ARC incorporates additional logic which saves and restores register context windows in parallel

<sup>&</sup>lt;sup>1</sup> Tristate drivers would still be required to support DMA.

with ALU operations. Whenever the IN bus is not being used, this logic checks register context windows and will restore the context of ancestors of the currently active window in anticipation of subroutine returns. Similarly, when the OUT bus is not being used, this logic will attempt to store the context of a higher register window to the register context stack in anticipation of a subroutine call. This feature is used to make it seem like there is an infinite number of windows in the register file. If a number of calls or returns occur quickly in succession, it is possible that the background saving and restoring will fall behind. The MCU will detect this condition and the processor will be fed NOPs so that the registers will be saved/restored at the rate of one per cycle. <sup>2</sup>

ALU instructions do not utilize the IN, OUT, or MMU busses. Therefore, while the processor is executing ALU instructions, the OUT and MMU busses are free and the IN bus is free every odd phase (instruction fetch on even phases). This available I/O bandwidth is exploited to save and or restore registers without interfering with the normal instruction execution throughput. Because this process occurs while ALU instructions execute, it is referred to as a background save or restore of registers.

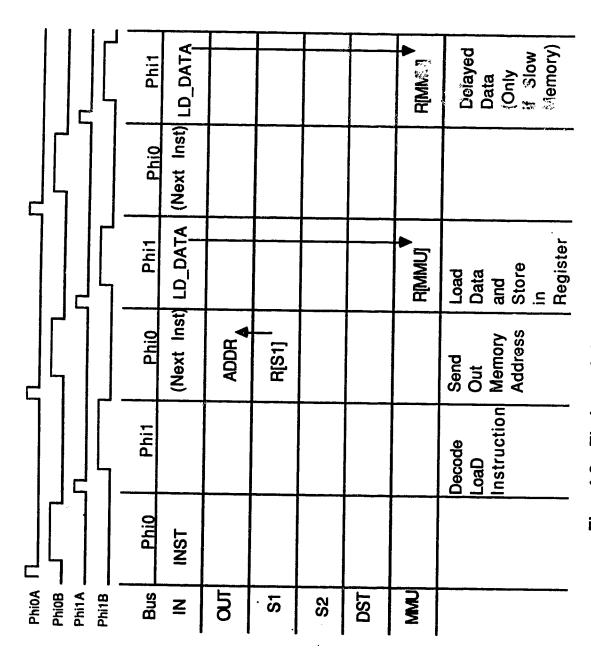

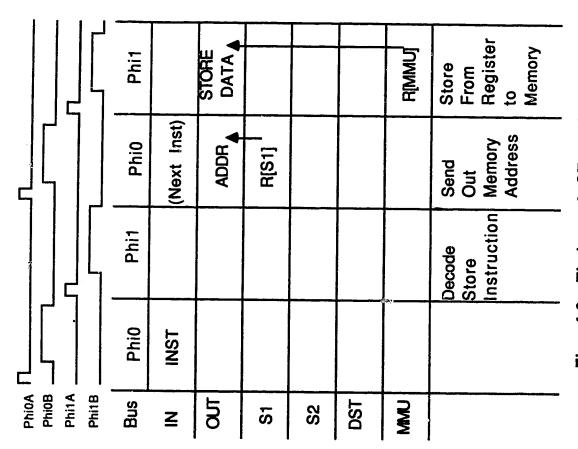

# 3.4. Pipelined Memory Access and Instruction Execution

Pipelined memory access allows more than one memory access to occur at the same time in a pipelined fashion. Pipelined memory access reduces the number of overhead states and allows a higher operating frequency. In a traditional RISC approach, the MMU must decide if data is resident (in cache or memory) and return the data within a specified time to the cpu (typically 1 cycle). When the data is not resident, the processor is halted until the data is fetched. Further, the time required to determine if the data is resident affects the maximum operating frequency of the sys-

<sup>&</sup>lt;sup>2</sup> This achieves the same effect as would a burst mode Load/Store of the register window.

tem. The ARC incorporates a pipelined memory access scheme. For LoaD instructions, addresses are sent out in one cycle and the data is expected to be returned N cycles later. This allows the external MCU to take several cycles to locate the requested data and return it to the cpu.

Further, N can be dynamically adjusted <sup>3</sup> to support complex memory decoding. For example, when running LISP or object-oriented programs, the pipeline length can be increased to allow time for the MMU to accomplish translation of symbolic program addresses to physical addresses without inserting wait states. The Pipeline is extended to the Memory Control Unit because transport and control instructions are pipelined. In the first version of ARC, Load and Store instructions send out the memory address and expect the data to be transferred to or from ARC, on the next phase. In the case of JMP or JSR, the new instructions are not fed to ARC until 2 phases after the memory address is sent out.

Caching and memory interleaving can be used to allow ARC to work at a significantly higher speed than the main memory. Caching is favored by most high performance processors because very high hit ratios can be achieved with a moderately sized cache and the hit ratio can be increased by increasing the size of the cache. Page mode memory interleaving (Least significant address bits select bank) can also be used when sequential memory locations are accessed. This allows different banks of memory to be accessed alternately to increase the memory transfer throughput in a pipelined fashion. Page mode interleaving has not proven to be as successful as caching because often the same memory bank is accessed twice in succession.

The pipelined memory access described above is beneficial because it allows the processor to interface with slower RAM. The number of pipe stages could conceivably be changed depending upon the memory subsystem (slower memory or to take

<sup>&</sup>lt;sup>3</sup> The maximum size of N would, however have to be known at compile time and it is likely that less efficient code will result as the ceiling of N increases.

into account cache misses).

### 3.5. External Program Counter

Locating the program counter (PC) off-chip significantly increases the output bandwidth available for data transfers. In the ARC, the instruction address does not originate from the cpu, but rather, from a memory control unit (MCU) (except in the case of a branch). Because most instruction addresses are externally generated and stored, the instruction address requires little of ARC's OUT bus bandwidth. By monitoring the instruction stream for branch instructions and receiving the result of branch conditions from the ARC cpu, the MCU could also generate branch destinations.

Other advantages of an off-chip PC include an increase in parallelism, a simpler on-chip pipeline, and locality of instruction address generation. Associated with the external PC is some logic to allow instruction address sequencing, addition, etc. By having the PC and associated logic off-chip, on-chip resources such as the ALU are not used to update the PC. The instruction pipeline of ARC is simplified because next instruction calculation does not have to fit into the pipeline resource scheduling. By associating the PC more closely with memory, there exists a greater locality of instruction address generation. Thus, instruction addresses are not propagated to the processor and calculated there. Rather processor addresses are calculated locally within the *intel-ligent* memory subsystem (or MCU) and only the instructions are fed to the processor.

It is possible to locate the PC off-chip as part of the MCU because ARC has simple addressing modes and control instructions. (See chapter 4 for details of the ARC instruction set.)

During sequential instruction flow, the external PC simply increments. Otherwise, the external PC unit needs to be notified when JUMP, Jump to SubRoutine, RETurn, and relative BRanch control instructions occur. When a JUMP instruction occurs, the contents of a register are placed on the OUT bus to become the new PC. When a JSR

instruction occurs, the PC is saved to the PC stack, and the contents of a register are placed on the OUT bus to become the new PC. When a RETurn instruction occurs, the last value on the PC stack becomes the new PC. When a relative BRanch instruction occurs, the 8 least significant bits on the OUT bus are added (2's complement) to the current PC.

ARC has 2 addressing modes: a) register direct and b) immediate. Therefore all data memory addresses originate from the general purpose registers. PC relative and other addressing modes are synthesized by loading the PC (or other special purpose register) into a general purpose register, performing an arithmetic operation on the register (such as ADD constant), and then using the resulting address in a LoaD or STore.

# 3.6. Intelligent Memory

The Memory Control Unit (MCU) may be considered as a single chip unit or as several chips distributed within the *intelligent* memory subsystem. The MCU works in conjunction with ARC to enable bandwidth reduction, bandwidth balancing, background register saves, and pipelined memory access.

Bandwidth reduction from ARC is made possible, in part, because the PC and other special registers are part of the MCU. By associating the PC more closely with memory, instruction addresses are calculated within the *intelligent* memory subsystem. This leads to saved bandwidth because the PC is only sent out on branch instructions. An external PC also results in an increase in parallelism and locality of instruction address generation.

Associating most other special registers with the MCU leads to further bandwidth reduction and locality of interrupt handling and context switching. When an interrupt occurs, it is unnecessary for ARC to transfer all special registers to the MCU, thereby saving bandwidth. Interrupts and context switches are primarily the responsibility of

the MCU. (ARC treats interrupt service routines as just another subroutine call.) Having the MCU handle interrupts makes sense because most interrupts result from memory and I/O devices and can thus be handled more locally. Having the MCU handle context switches also makes sense because a context switch involves memory real-location and sometimes disk swapping as a new process becomes active.

Bandwidth balancing is made possible by the interface between ARC and the MCU. When the PC is part of the MCU, nearly equal IN and OUT bus bandwidth requirements exist to and from ARC. The OUT bus of ARC supports outgoing data, data addresses, and register saves. The IN bus of ARC supports instruction pairs, incoming data, and register restores. Bandwidth must also be balanced between phases of Phil and Phi2 as hinted in section 3.2 in the paragraph on time-division-multiplexing (TDM) of the IN and OUT busses. Bandwidth balancing is explained more fully in terms of resource scheduling in section 4.1.4 and pictorially in Fig. 4.8.

Background register saves are also made possible by the MCU. The MCU manages the register stack. The algorithm to have registers saved to (or restored from) the register stack is a responsibility of the MCU. Storage space for the registers is also a responsibility of the MCU. When the MCU determines that it is time to either save or restore a register subwindow, it notifies ARC. Then during each subsequent ALU instruction, a register from the subwindow to be saved/restored will be pushed onto/poped from the register stack.

Pipelined memory access is another useful feature of the interface between ARC and the MCU. The MCU may control slow memory, utilize virtual address translation, utilize caching, or queue addresses to interleaved memory. In these cases, the number of cycles between the assertion of a data address from ARC and the response from memory can be customized for each different type of memory subsystem.

# 3.7. Philosophy Behind ARC and MCU Design

In addition to the concepts presented in this chapter to improve speed and efficiency, a number of other high level objectives are set for the design of ARC and its companion MCU.

The ARC and MCU are partitioned such that generic processing functions are incorporated into ARC while memory control functions are incorporated into the MCU. The implementation of the processing and memory control functions on separate chips have a number of advantages:

- a) It allows the processor to be generic and attached to different, specialized memory controllers. Memory controllers tend to be dependent upon the system architecture, memory subsystem hardware, the operating system, etc. In contrast, processors should be as generic as possible so that they can be incorporated into a wide variety of systems and the executable code will be the same on all systems.

- b) Fewer compromises are necessary with this partition than if memory and processor functions are incorporated together on the same chip (e.g. number of registers/bits vs. size of cache, more transistors vs. lower yield).

- c) A sibling relationship between cpu(s) and memory subsystem(s) results in increased parallelism and locality of information processing. Conventional processors exhibit a master-slave relationship between the cpu and the memory subsystem. The MCU thus operates in parallel with ARC by performing memory control functions and feeding instructions and routing data to and from ARC. Functions such as caching, interrupt handling, context switches, and virtual memory translation are functions of the MCU because these functions are associated more closely with memory control than data processing. By giving the MCU these responsibilities, some of the processing and bandwidth load are taken from the processor.

- d) More efficient use of I/O bandwidth as well as locality of information processing and an increase in parallelism results from incorporating special registers such as the PC into the MCU. Because instructions originate from memory and the generation of instruction addresses requires little CPU intervention, the PC and associated sequencing logic is implemented in the MCU. Other special registers such as the Register Stack Pointer are associated with the MCU because they address memory locations used by memory control functions. Because these special registers do not have to be saved and restored to ARC at the advent of an interrupt, interrupt handling because the responsibility of the MCU. This leads to locality of interrupt handling because many interrupts originate from the memory subsystem(s) (e.g.: page faults, segmentation faults); It also leads to increased parallelism because the MCU takes responsibility for feeding ARC the call to the correct interrupt service routine.

- e) The ARC design is versatile and expandable. On-chip enhancements could include more registers, different register window overlaps, more sophisticated I/O Control Unit (IOCU) functions, different ALU operations, and possibly expansion to 64 bits. The Memory Control Unit would be closely bound to the system and memory architecture. The MCU could be a single chip or distributed control in the memory subsystem(s). Enhancements to the MCU could include larger caches, virtual memory, tags and security features. In effect, both ARC and the MCU can be "scaled" according to the available technology.

The architectural relationships between ARC and the MCU will be discussed in more detail in the next chapter.

### 4. ARCHITECTURE

This chapter presents a description of the architecture of the ARC processor at the block diagram or functional level. Architectural details of the ARC processor include datapath functions, I/O Control Unit (IOCU) functions, the instruction set, and the instruction pipeline. The implications of the ARC architecture on the system level design are then discussed. ARC system architectural details include the interface of ARC to different types of memory subsystems. These discussions will highlight the implementation details of the novel architectural concepts and philosophical issues presented in Chapter 3.

# 4.1. ARC Processor Architecture

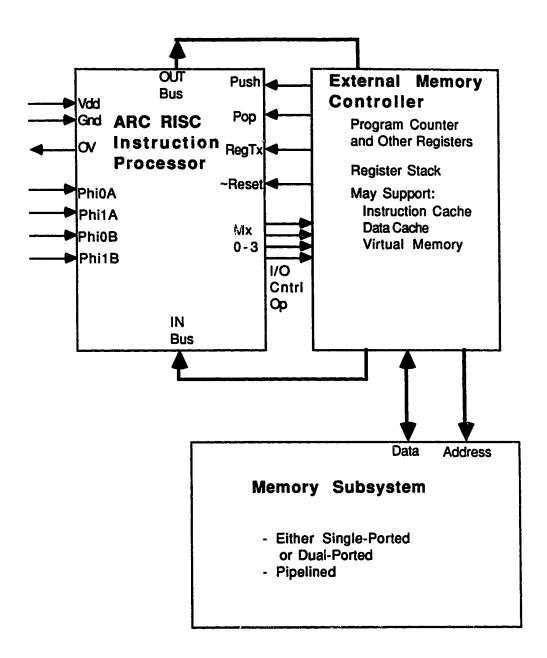

A picture of ARC is shown in Fig. 4.1. The 2 major functional blocks of ARC are the Datapath and the IOCU. The Datapath is composed of the ALU and Register File while the IOCU handles background operations and pipelining as well as I/O operations. The relative positions of the functional blocks and I/O signals are detailed in Fig. 4.2. Note the nonstandard unidirectional IN and OUT busses, interface to the external MCU, and 4 nonoverlapping clock phases. <sup>1</sup>

#### 4.1.1. Datapath

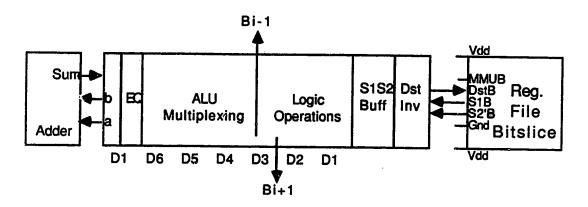

A Block diagram of the Datapath is shown in Fig. 4.3 The Datapath is composed of the ALU and the Register File. The ALU communicates with the register file via 2 read ports and 1 write port. The Register File communicates with the outside world via the IOCU.

<sup>&</sup>lt;sup>1</sup> Clock phases are divided into even and odd, as well as A and B clock phases. Even clocks include Phi0A and Phi0B. Odd clocks include Phi1A and Phi1B. During A phases, busses are precharged, the ALU writes to the register file, and latching occurs. During B phases, all decoding, execution, memory access, etc. occurs.

- 32 - Architecture

Fig. 4.1: Photograph of ARC Die

Legend:

I0-I31: IN Bus/Input Pads

O0-O31: OUT Bus/Output Pads

OV: Overflow Flag (from ARC to M

OV: Overflow Flag (from ARC to MCU)

Mx0-Mx31: MCU Opcode ("ARC TO MCU)

Push,Pop,RegTx,~reset: Background Register

Save/Restore Control Signals (MCU to ARC)

Ø0A: Clock used for even-phase precharge and latching

Ø0B: Clock input used for even-phase execution

Ø1A: Clock used for odd-phase precharge and latching Ø1B: Clock used to synchronize odd-phase execution

Fig. 4.2: ARC Die Floorplan

Fig. 4.3: ALU Block Diagram

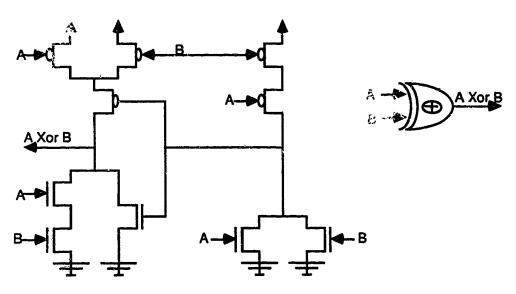

### 4.1.1.1. The ALU

The ALU is shown as the left half of the Datapath Block Diagram of Fig. 4.3. The ALU is responsible for operations on register and instruction operands. The result of each ALU operation is stored in the register file. A carry-select adder, condition testing logic, and an ALU instruction decoder are incorporated into the ALU. The interface and relative placement of these blocks of the ALU are illustrated in Fig. 4.3. The architectural design of the ALU is fairly conventional. The instructions supported by the ALU are presented in Section 4.1.3.1 and the logic design of the ALU is presented in Chapter 5.

### 4.1.1.2. The Register File

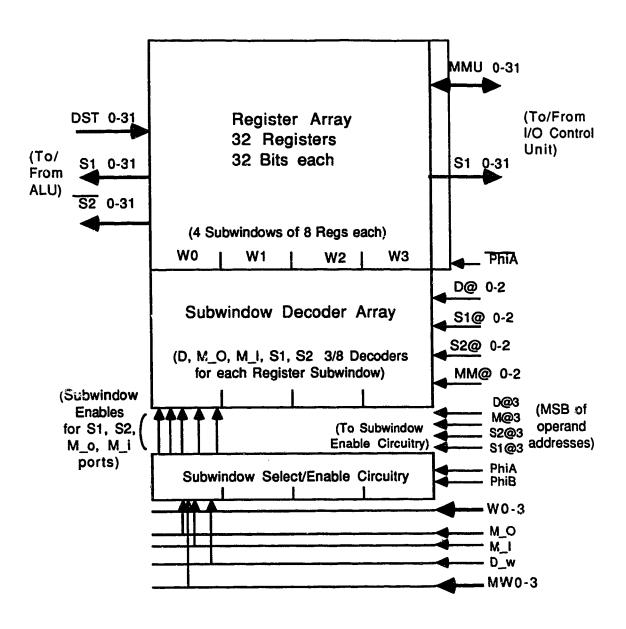

The register file is responsible for storing the working set of data to be operated upon by the ARC processor. In any LoaD-and-STore architecture, the design of the register file greatly influences the throughput of the processor. Previous RISC processors have incorporated register files as large as possible given the physical constraints of the implementation technology. With a large register file, more of the working set of data can be held on-chip, causing fewer LoaD and STore accesses to memory. In a conventional RISC, memory accesses are costly in terms of bandwidth, data latency, and pipeline conflicts (e.g.: interference of LoaD and STore with Instruction Fetch in Berkeley's RISC).

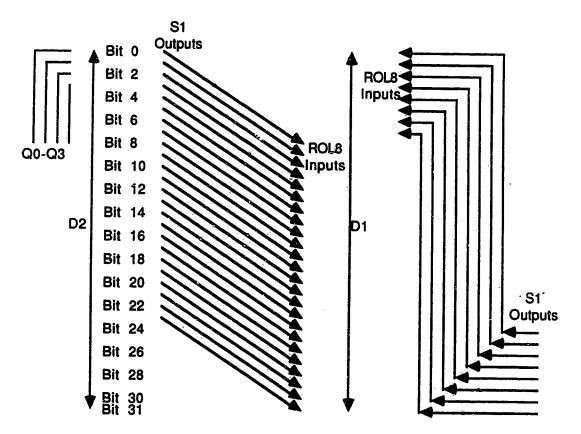

The register file is shown as the right half of the Datapath Block Diagram of Fig. 4.3. The main difference with regard to previous register file designs is that four busses are served by the ARC Register File: S1, ~S2, Dst, and MMU. The S1 bus carries the contents of a register to the ALU and the IOCU. The ~S2 bus carries the contents of a register to the ALU. The Dst Bus carries the result of ALU operations back to a register. The MMU bus is bidirectional and is used for data transfer between a register and the IN and OUT busses via the IOCU. The register addresses for each of the 4 busses are input to the subwindow decoders and are labeled Dst@,

- 36 - Architecture

\$1@, \$2@, and MMU@ in Fig. 4.3.

This high connectivity to the register file allows more independence of operation between the ALU and the IOCU thereby simplifying background register saves/restores, simple pipeline scheduling, and high instruction throughput. Background register saves/restores or memory access instructions can occur in ARC while an ALU operation is in the pipe because sufficient busses exist to access the register file concurrently.<sup>2</sup>

The Register File is organized as a set of overlapped register windows. The advantages of a circular buffer organization of Overlapped windows was shown by the Berkeley RISC group [Patt82] and was mentioned in Chapter 2. Essentially, register windows allow the exploitation of temporal and spatial locality of address and data references within a procedure and across procedure calls. Because the register windows are overlapping, some registers accessed by the calling subroutine are also accessible by the called subroutine. This enables efficient parameter passing.

The version of the ARC implemented had 32 registers in total, divided into 4 subwindows of 8 registers each. 2 subwindows are accessible at any one time, 1 of the subwindows would previously have been accessible to the calling procedure resulting in an overlap of 8 registers between procedure calls. (A more detailed physical description of the ARC register file circuitry is given in Section 5.2)

This circular buffer organization of overlapped register windows leads to a register stack structure as depicted in Fig. 4.4. The register stack is essentially the register window of old procedure activations stored in memory because of limited space within the register file.

<sup>&</sup>lt;sup>2</sup> In a processor architecture with one less bus to the register file, background register saves could still occur by using the idle bus during 2 operand ALU instructions and branches. However, this would reduce the opportunity to perform background saves and restores resulting in more waits required to keep pace with subroutine calls and routines.

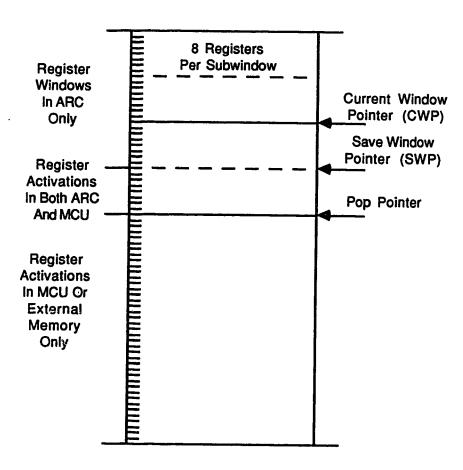

Fig. 4.4: Register Stack

The register stack is controlled by the MCU and the background register save/restore finite state machine. The MCU keeps track of procedure calls and returns and interrupts and notifies ARC if a register subwindow push or pop is to occur. The current register window is referenced by the Current Window Pointer (CWP). A background register save pushes the register subwindow referenced by the Save Window Pointer (SWP) A background register restore pops the register subwindow preceding the pop pointer. As shown in Fig. 4.4, only the current and most recent procedure register sets are held in the ARC register file. The register sets of distant ancestors of the current procedure are stored only in memory controlled by the MCU except when the register stack is nested less than two levels deep in which case all procedure activations are in registers (e.g.: at boot)

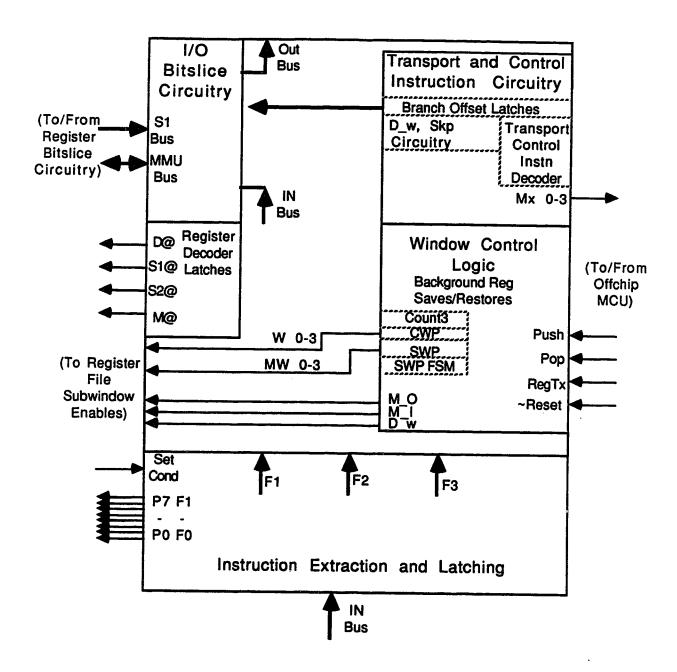

#### 4.1.2. The I/O and Control Unit (IOCU)

A block diagram of the IOCU is shown in Fig. 4.5. The IOCU interfaces the register file to the IN and OUT busses and the MCU. The IOCU may be considered as being composed of four functional blocks:

- 1) I/O Bitslice Circuitry (upper left of Fig. 4.5)

- 2) Instruction Extraction and Latching Circuitry (bottom of Fig. 4.5)

- 3) Transport and Control Instruction Circuitry (upper right of Fig. 4.5)

- 4) Window Control Logic (mid right of Fig. 4.5)

An overview of each of the four functional blocks follows. For more detailed information about the IOCU circuitry consult Section 5.3.

The I/O Bitslice Circuitry is responsible for routing of data between the IN bus, the OUT bus, and the S1 and MMU busses of the register file. This circuitry facilitates a high bandwidth interface between the Register file and the unidirectional IN and OUT busses, providing support for the routing of data, necessary for transport and con-

Fig. 4.5: I/O and Control Unit Block Diagram

trol instructions as well as background register saves and restores.