#### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

#### University of Alberta

# On-Line Current Monitoring of Low-Voltage VLSI Circuits

by

Ivan Pecuh

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of **Master of Science**.

Department of Electrical and Computer Engineering

Edmonton, Alberta Spring 2000

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-60163-3

University of Alberta

**Library Release Form**

Name of Author: Ivan Pecuh

Title of Thesis: On-Line Current Monitoring of Low-Voltage VLSI Circuits

Degree: Master of Science

Year this Degree granted: 2000

Permission is hereby granted to the University of Alberta to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly of scientific research purposes only.

The author reserves all other publication and other rights in association with the copyright in the thesis, and except as herein before provided, neither the thesis nor any substantial portion thereof may be printed or otherwise reproduced in any material form whatever without the author's prior written permission.

# 5, 1130 Cecile Drive

Port Moody, V3H 1M7

British Columbia, Canada

Date: Nov. 26, 1999

#### **University of Alberta**

#### Faculty of Graduate Studies and Research

The undersigned certify that they have read, and recommended to the Faculty of Graduate Studies and Research for acceptance, a thesis entitled **On-Line Current Monitoring of**'Low-Voltage VLSI Circuits submitted by Ivan Pecuh in partial fulfillment of the requirements for the degree of Master of Science.

Dr. Martin Margala

Dr. Nelson G. Durdle

Dr. Jim Hoover

Date: havember 26, 1999

# **Abstract**

This thesis presents the designs for two on-line current monitors for testing of VLSI circuits. Both monitors are designed to operate in a low-voltage environment with 1.5 Volts power-supply. The first design (Monitor 1) is an improvement of the Stopjavová/Manhaeve design, and the second one (Monitor 2) is a new proposed monitor scheme with two current-sensing elements. These designs can be used in quiescent current-monitoring—Iddq, and transient-current monitoring—Iddt. The second design can also be used in tesing of mixed-signal VLSI circuits. The simulation test results of the two monitors demonstrate an ability to detect a short and an open fault in a circuit-undertest.

# Acknowledgements

I would like to thank my supervisor, Dr. Martin Margala and Dr. Igor M. Filanovsky for their guidance throughout this research project. Most importantly, I would to thank my parents, my wife Julija, and my kids, Roman, Anna-Maria and Ivan for their support and understanding during the course of my studies.

This project was supported by: NSERC (National Science and Engineering Council of Canada), CMC (Canadian Microelectronics Corporation) and J. Gordin Caplan—Graduate Student Award.

# Contents

| CHAPTER 1                                      | 1          |

|------------------------------------------------|------------|

| INTRODUCTION                                   | 1          |

| 1.1 Testing in IC Manufacturing                | 2          |

| 1.2 ASPECTS OF IC TESTING                      | 3          |

| 1.3 IC TESTING METHODOLOGIES                   | 5          |

| 1.4 THESIS SUMMARY                             | 11         |

| CHAPTER 2                                      | 13         |

| BACKGROUND AND LITERATURE REVIEW               | 13         |

| 2.1 CURRENT BEHAVIOR OF CMOS CIRCUITS          | 13         |

| 2.1.1 Quiescent Current - Iddq                 | 14         |

| Junction Leakage Current                       | 14         |

| Subthreshold Current                           | 16         |

| 2.1.2 Transient Current - Iddt                 | 17         |

| 2.2 FAULT MODELING                             | 18         |

| 2.2.1 Shorts                                   | 19         |

| 2.2.2 Bridging Faults                          | 20         |

| 2.2.3 OPEN FAULTS                              | 21         |

| 2.3 CURRENT MONITORING                         | 22         |

| 2.3.1 Current Monitoring Methodologies         | 24         |

| Monitoring of Digital Circuits                 | 24         |

| Monitoring of Mixed-signal Circuits            | 26         |

| Time-Domain Analysis                           | 26         |

| 2.4 LIMITATIONS OF CURRENT MONITORING          | 27         |

| 2.4.1 Limitations in Detection of Shorts       | 28         |

| 2.4.2 Limitations in Detection of Open Defects | 29         |

| 2.5 ASPECTS OF TECHNOLOGY SCALING              | 30         |

| 2.5.1. Constant Field Scaling                  | <i>3</i> 2 |

| 2.5.2 Reducing supply voltage Vdd only                    | 32 |

|-----------------------------------------------------------|----|

| 2.6 Current Monitors                                      | 36 |

| 2.6.1 Off-Chip and On-Chip Current Monitors               | 36 |

| 2.6.2 Design of a Built-In Current Monitors               | 37 |

| 2.6.3 Previous Designs of Current Monitors                | 38 |

| Flip-flop based design proposed by Maly et.al.            | 38 |

| Monitor Design proposed by Miura                          | 39 |

| Monitor Design proposed by Tang                           | 39 |

| Monitor Design proposed by Kim et.al                      | 40 |

| Conveyor Based Monitor proposed by Stopjaková et.al       | 41 |

| Monitor Design proposed by Antonioly et.al                | 43 |

| Monitor Design proposed by Maidon et.al                   | 44 |

| Current Mirror Based Monitor Proposed by Stopjaková et.al | 45 |

| CHAPTER 3                                                 | 47 |

|                                                           |    |

| CURRENT MONITOR 1 DESIGN                                  | 47 |

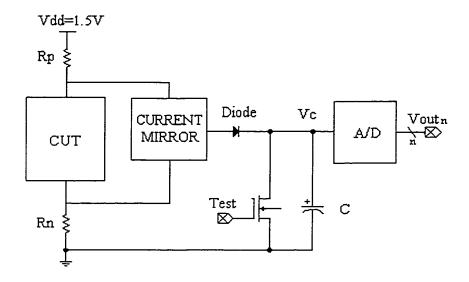

| 3.1 Monitor 1 Design Scheme                               | 48 |

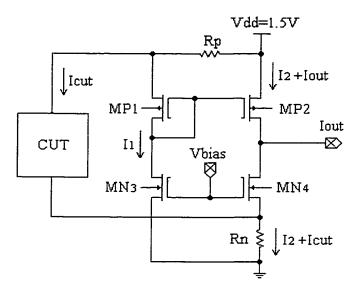

| 3.2 CURRENT MIRROR DESIGN                                 | 51 |

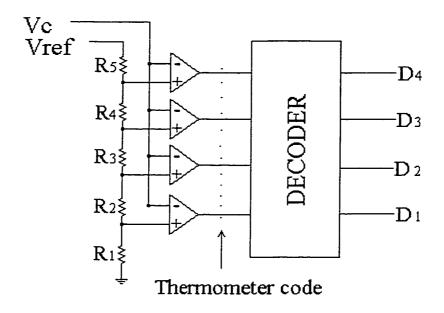

| 3.3 A/D CONVERTER                                         | 53 |

| 3.4 COMPARATOR DESIGN                                     | 54 |

| 3.5 CUT – CIRCUIT-UNDER-TEST                              | 56 |

| 3.6 SIMULATION RESULTS                                    | 57 |

| 3.8 SIGNAL PROCESSING                                     | 60 |

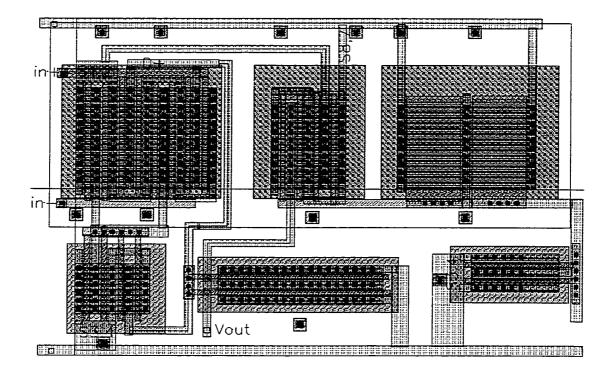

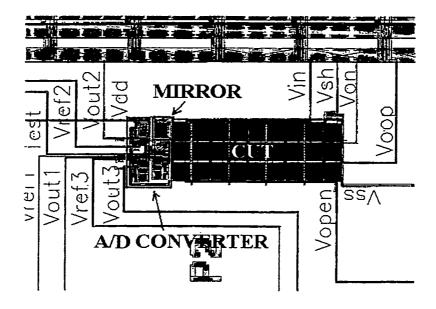

| 3.9 CIRCUIT IMPLEMENTATION OF MONITOR 1                   | 60 |

| 3.10 ADVANTAGES AND DISADVANTAGES                         | 62 |

| 3.11 TEST RESULTS                                         | 62 |

| CHAPTER 4                                                 | 66 |

| CURRENT MONITOR 2 DESIGN                                  | 66 |

| 4.1 Monitor 2 Design Scheme                               | 66 |

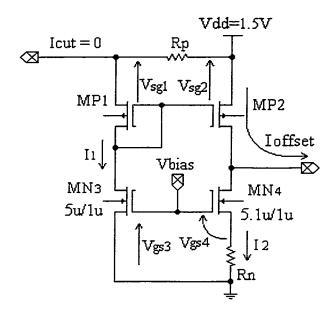

| 4.2 Current Mirror Design                                 | 68 |

| 4.3 SIMULATION RESULTS                                    | 71 |

| 4.3.1 Testing of Digital Circuits                         | 73 |

| 4.3.2 Testing of Mixed-Signal Circuits                    | 75 |

| 4.4 CIRCUIT IMPLEMENTATION                                |    |

| 4.5 SIGNAL PROCESSING                                     | 79 |

| 4.6 TEST RESULTS                                          | 79 |

| CHAPTER 5                                   | . 80 |

|---------------------------------------------|------|

| CRITICAL ANALYSIS AND                       |      |

| FUTURE DEVELOPMENTS                         | . 80 |

| 5.1 Inductive Element in Current Monitoring | . 81 |

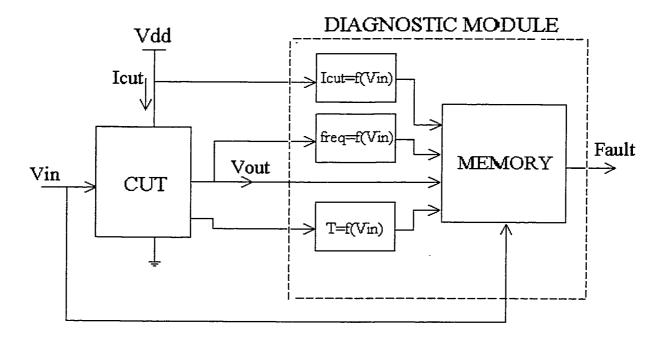

| 5.2 DIAGNOSTIC MODULE                       | . 84 |

| CHAPTER 6                                   | . 86 |

| CONCLUSION                                  | . 86 |

| BIBLIOGRAPHY                                | . 86 |

# List of Tables

| Table 1.1: Bandwidth gap prediction (Source: 1998 SIA Roadmap)                      | 5  |

|-------------------------------------------------------------------------------------|----|

|                                                                                     |    |

| Table 2.1: Overall defect coverage data                                             | 30 |

| Table 2.2: Trends in CMOS technology at 100°C (SIA roadmap values)                  | 33 |

| Table 2.3: Trends in CMOS technology with scaling $V_t$ proportional to Vdd at 25°C | 34 |

| Table 2.4: Variation of relative distances (Mg-Md) on ratio V <sub>t</sub> /Vdd     | 35 |

| Table 2.5: Relative distance between the means Md and Mg.                           | 35 |

| Table 2.6: Iddq test accuracy results                                               | 43 |

|                                                                                     |    |

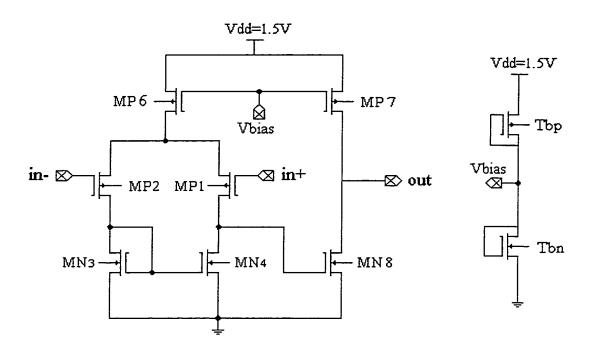

| Table 3.1: Current mirror device sizes                                              | 52 |

| Table 3.2: Comparator device sizes                                                  | 55 |

# List of Figures

| Figure 1.1: Major steps in IC manufacturing process                   | 2  |

|-----------------------------------------------------------------------|----|

| Figure 1.2: Testing complexity index                                  | 4  |

| Figure 1.3: General testing environment                               | 6  |

| Figure 1.4: Embedded test                                             | 7  |

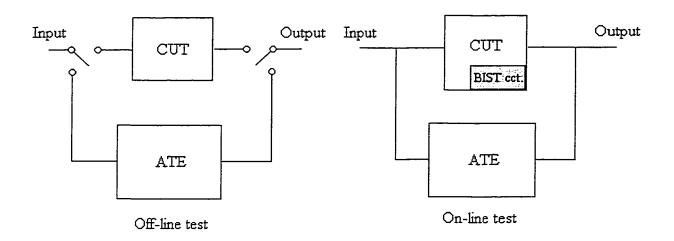

| Figure 1.5: Off-line test and on-line test                            | 8  |

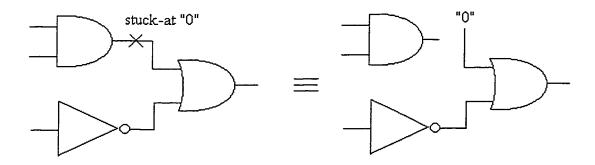

| Figure 1.6: Stuck-at fault model                                      | 9  |

|                                                                       | _  |

| Figure 2.1: Voltage supply current (Idd)                              |    |

| Figure 2.2: Junction leakage current and subthreshold current         | 15 |

| Figure 2.3: Parasitic PN-junctions in a MOS device with a p-substrate | 15 |

| Figure 2.4: Structure of gate-oxide short in a MOS-transistor         | 19 |

| Figure 2.5: GOS model for NMOS transistor                             | 20 |

| Figure 2.6: GOS model for PMOS transistor                             | 20 |

| Figure 2.7: Bridging fault model                                      | 21 |

| Figure 2.8: The Floating gate fault model                             | 22 |

| Figure 2.9: General distribution of the Iddq values in CMOS network   | 23 |

| Figure 2. 10: Current monitoring scheme for CMOS digital circuits     | 25 |

| Figure 2.11: Time-domain analysis for mixed-signal circuits           | 27 |

| Figure 2. 12: Limitations of s-a-f test                               | 28 |

| Figure 2.14: Source/drain open                                        | 29 |

| Figure 2.15: Device before and after scaling                          | 30 |

| Figure 2.16: Monitor proposed by Maly et.al.                          | 38 |

| Figure 2.17: Monitor Design by Miura                                  | 39 |

| Figure 2.18: Monitor proposed by Tang                                 | 40 |

| Figure 2.19: Monitor proposed by Kim and Hong                         | 41 |

| Figure 2.20: Monitor proposed by Stopiaková et al                     | 42 |

| Figure 2.21: Monitor proposed by Antonioli and Kinoshita   | 44 |

|------------------------------------------------------------|----|

| Figure 2.22: Monitor proposed by Maidon et.al.             | 45 |

| Figure 2.23: Monitor proposed by Stopjaková et.al.         | 46 |

|                                                            |    |

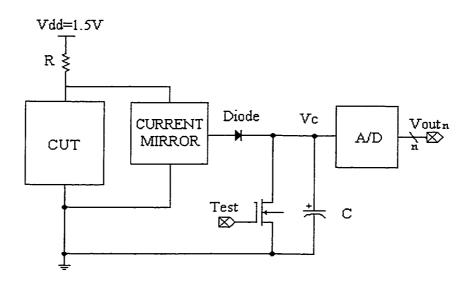

| Figure 3.1: Proposed Monitor 1 Scheme                      | 48 |

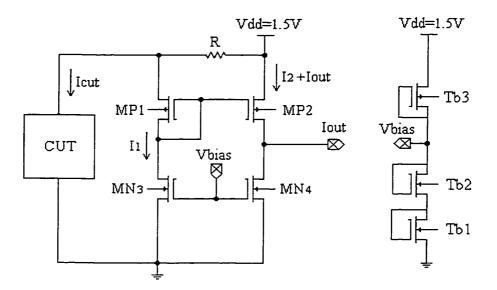

| Figure 3.2: Current mirror.                                | 49 |

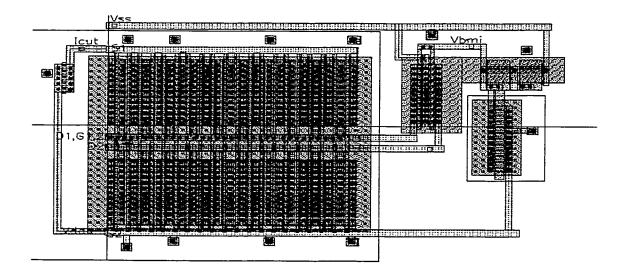

| Figure 3.3: Current mirror layout                          | 52 |

| Figure 3.4: Flash A/D converter                            | 53 |

| Figure 3.5: Example of A/D converter voltage references    | 54 |

| Figure 3.6: Comparator schematics                          | 55 |

| Figure 3.7: Comparator layout                              | 56 |

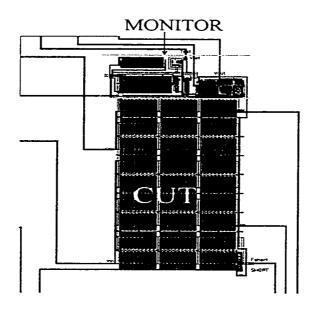

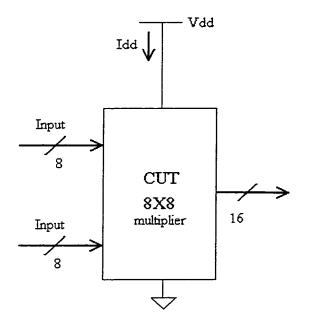

| Figure 3.8: Circuit under test (CUT)                       | 57 |

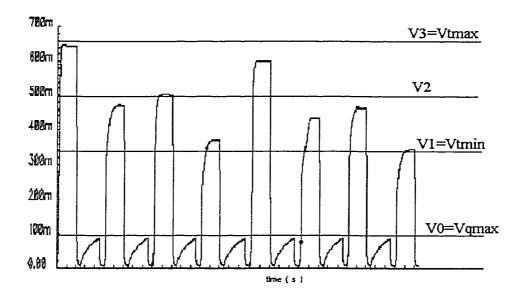

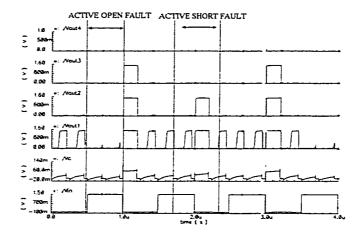

| Figure 3.9: Monitor transient response (1 MHz)             | 58 |

| Figure 3.10: Monitor transient response (100 MHz)          | 58 |

| Figure 3.11: 0.5 µm Monitor transient response (1 MHz)     | 59 |

| Figure 3.12: Layout of the Monitor with CUT - 0.35 $\mu m$ | 61 |

| Figure 3.13: Layout of the Monitor with CUT - 0.5 μm       | 61 |

| Figure 3.14: Test environment                              | 63 |

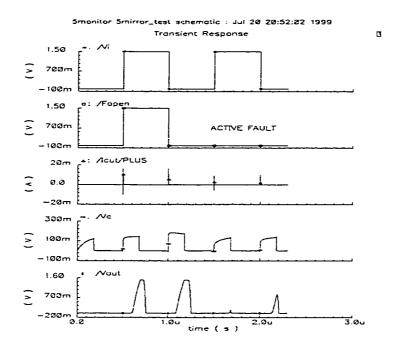

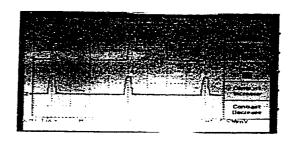

| Figure 3.15: f=100 kHz / Vdd=1.5 V                         | 64 |

| Figure 3.16: f=1 MHz / Vdd=1.5 V                           | 64 |

| Figure 3.17: 100 kHz / 2 V                                 | 65 |

| Figure 3.18: 1 MHz / 2 V                                   | 65 |

|                                                            |    |

| Figure 4.1: Proposed Monitor 2 scheme                      | 67 |

| Figure 4.2: Current mirror schematics                      | 69 |

| Figure 4.3: Offset current                                 | 71 |

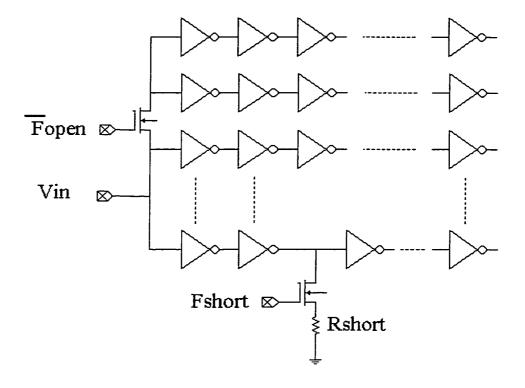

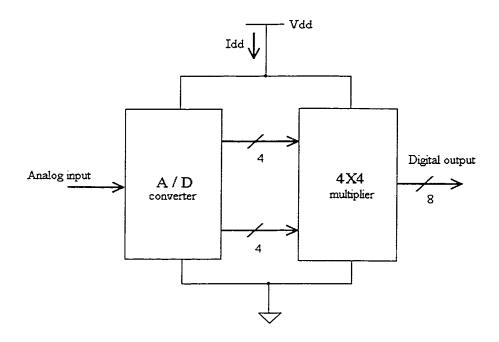

| Figure 4.4: Digital circuit under test                     | 72 |

| Figure 4.5: Mixed-signal circuit under test                | 72 |

| Figure 4.6: 4-bit multiplier for unsigned numbers          | 73 |

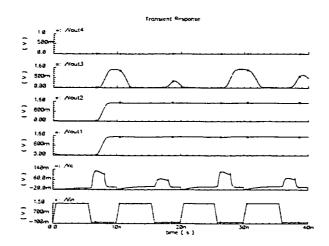

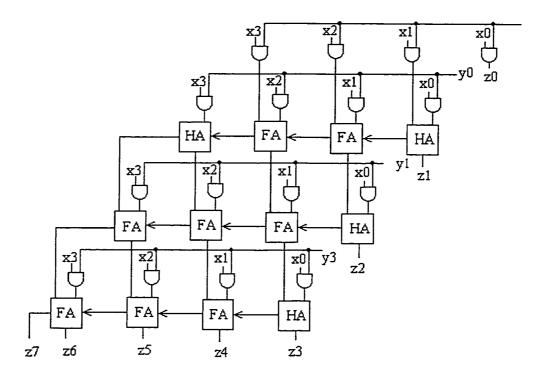

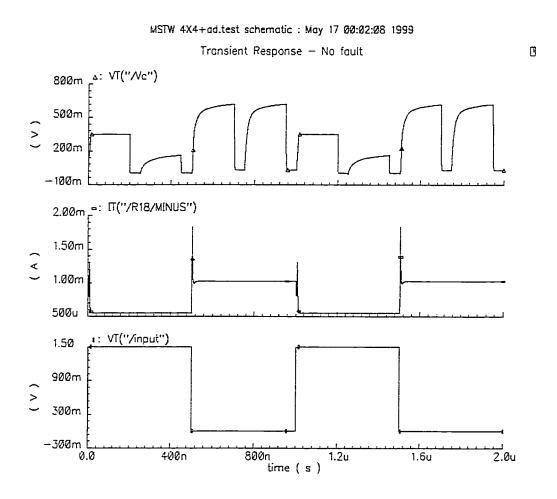

| Figure 4.7: No fault response (top-Vc, bottom-Idd)         | 74 |

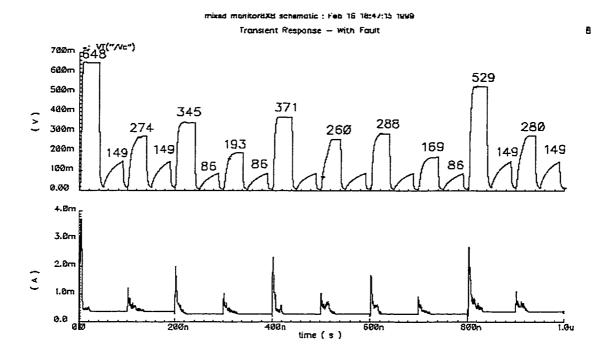

| Figure 4.8: Fault response (top-Vc, bottom-Idd)            | 75 |

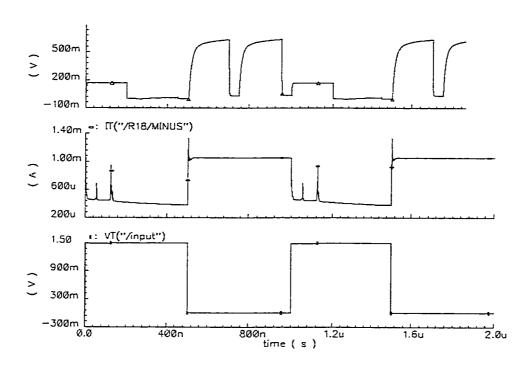

| Figure 4.9: No-fault response (bottom-top: Vin, Idd, Vc) | 76 |

|----------------------------------------------------------|----|

| Figure 4.10: Short-fault response                        | 77 |

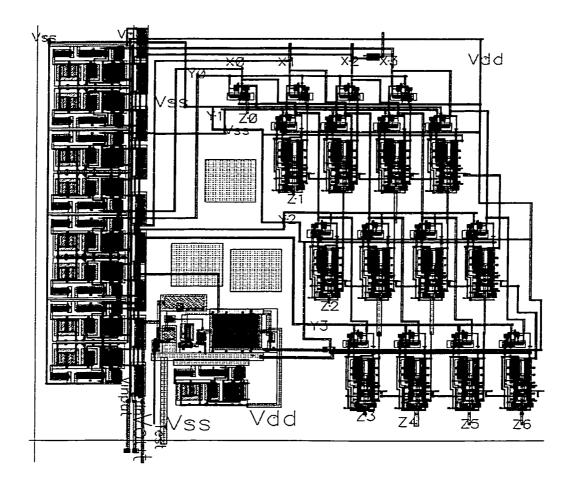

| Figure 4.11: Layout of Monitor 2 with the CUT            | 78 |

|                                                          |    |

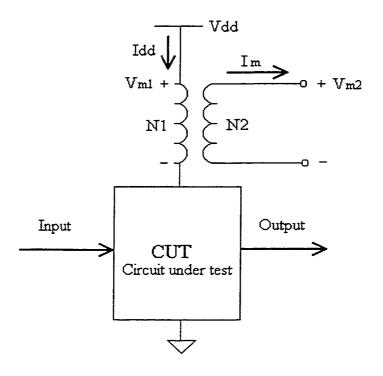

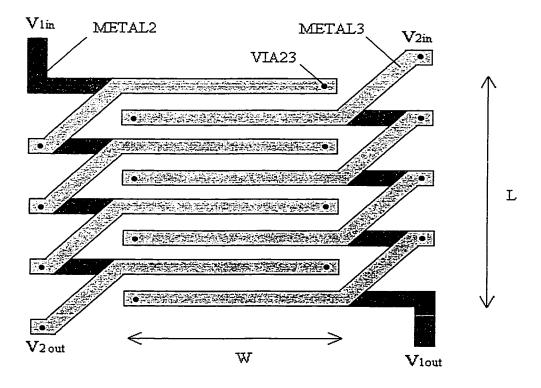

| Figure 5.1: Inductive element as a current sensor        | 82 |

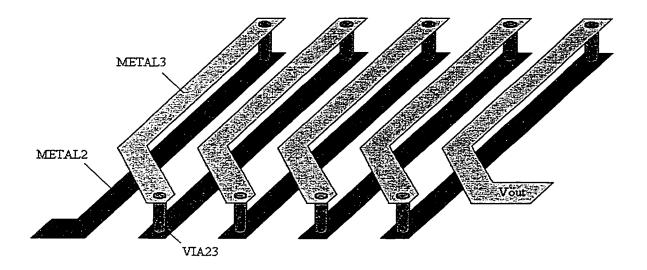

| Figure 5.2: The new inductor layout design               |    |

| Figure 5.3: Transformer layout design                    | 83 |

| Figure 5.4: Diagnostic module scheme                     | 84 |

|                                                          |    |

# Chapter 1

## Introduction

The testing of integrated circuit (IC) designs is gaining in importance every day. This is understandable since better testing implies higher quality. Low quality products can ultimately have a negative impact on society through the cost of their development, maintenance and repair. With the continuing advances in the manufacturing of IC technology, testing constitutes a large portion of the total cost. Decreasing silicon costs, together with the increased complexity of integrated circuits present two of the most important elements of this trend [1]. It is expected that chips with 100-milion transistors will emerge in the near future [2]. Market-driven developments in the area of wireless communications lead to the emergence of complex mixed-signal (analog-digital) circuits and indicate a trend toward the integration of the radio frequency (RF) and baseband mixed-signal technologies. In addition, submicron design techniques and low-power designs demand an improvement in fault coverage and the necessity for development of new testing techniques.

#### 1.1 Testing in IC Manufacturing

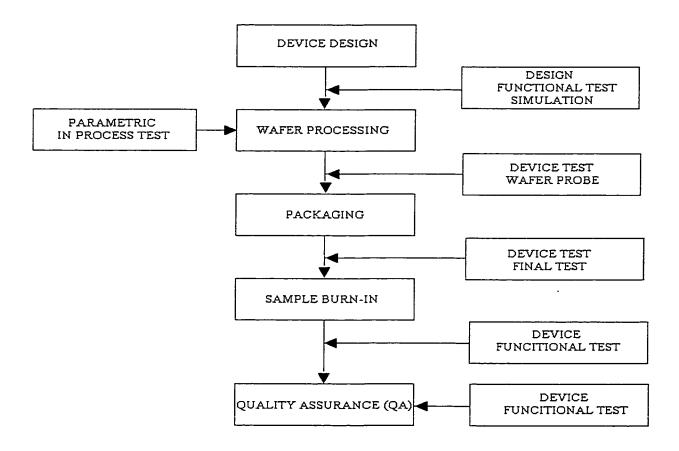

Testing has two important functions in the process of IC manufacturing. One is the go/no-go testing used during the manufacturing process and the other is defect analysis done during diagnosis. Go/no-go testing is done repeatedly in several steps [3]. Wafers, dice, and chips are probed and tested to screen devices that fail performance specifications under specified conditions. Figure 1.1 describes the major steps in the IC manufacturing process, together with the points where IC testing is performed. A bad device is considered to be any IC that fails to meet one or more specifications at any point in the process. Each of the steps has different issues and requirements.

Figure 1.1: Major steps in IC manufacturing process

Initially, when a design is developed using computer-aided-design (CAD) tools, a designer verifies desired functionality through simulations. During the processing of wafers, parametric tests are performed to evaluate process control. At the end of the wafer processing, functional tests are used to eliminate faulty devices. This is commonly referred to as the "test suite." It identifies any catastrophic process control errors. At this point, wafer probing can be done either by using a complete set of tests needed for a particular design or only a subset of tests. Bad devices are marked, and the wafer is ready for scribing. Good dies are selected for packaging. After a packaging, a final test is performed to ensure proper handling, bond wiring and packaging. The performance of the device is checked over the specific temperature range it will function in. In the next step, a sample burn-in test is performed only on a selected set of IC's. This is done using a higher temperature for an extended period of time. The initial part of the so-called "bathtub curve" describes the failure behavior of devices in the early period of operation. Before the delivery of the product to the customer, the Quality Assurance (QA) test has to be performed. The need for standardization of the QA test was driven by globalization in the microelectronics industry, resulted in two popular ISO9000 and ISO9001 standards.

The main purpose of apparently redundant tests is to increase the probability of detection of bad devices in the early stages of the manufacturing process. The "factor of ten" rule is used in describing the costs resulting from the production of bad devices. Every additional step that a bad device reaches without detection multiplies the original cost of production by a factor ten. If a faulty device reaches the market, it leads to a damaged reputation and ultimately to a loss of market share.

#### 1.2 Aspects of IC Testing

Increasing complexity increases the probability of bad devices, reducing the yield. Yield is defined as the ratio of good devices over the total number of devices fabricated. Increased complexity also introduces new challenges to the testing of IC's. The International Technology Roadmap of Semiconductors (ITRS), produced by the

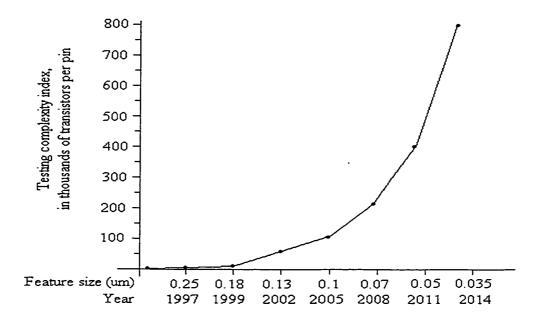

Semiconductor Industry Association (SIA) [4], predicts a rapid increase in the number of transistors per pin (Figure 1.2). The testing complexity index, as shown in this graph, predicts rapid decrease in the accessibility of transistors from the chip pins. This presents one of the biggest problems in IC testing.

Figure 1.2: Testing complexity index

Another major problem in IC testing is the gap between internal performance and output capabilities of the input/output (I/O) link. The difference between the internal clock speed and external capabilities of the IC chip constantly increases and creates the problem of interaction between the two media, rendering at-speed testing of IC performance almost impossible. The I/O bandwidth lags far behind the speed at which the information can be generated and moved inside or outside the chip. This gap, as analyzed in SIA Roadmap for the next 14 years is shown in Table 1.1. External bandwidth, defined as number of I/O's times I/O switching speed, does not follow the internal bandwidth at the same rate. Internal bandwidth is basically the speed at which the chip can generate and process information, and it is defined as the number of transistors per IC times internal switching frequency.

Table 1.1: Bandwidth gap prediction (Source: 1998 SIA Roadmap)

| BANDWIDTH: |      |       |       |       |        |         |         |

|------------|------|-------|-------|-------|--------|---------|---------|

| Internal   | 1    | 3.165 | 19.52 | 85.26 | 375.35 | 1621.62 | 7132.76 |

| External   | 1    | 1.97  | 3.59  | 6.14  | 10.5   | 17.24   | 28.89   |

|            | 1997 | 1999  | 2002  | 2005  | 2008   | 2011    | 2014    |

#### 1.3 IC Testing Methodologies

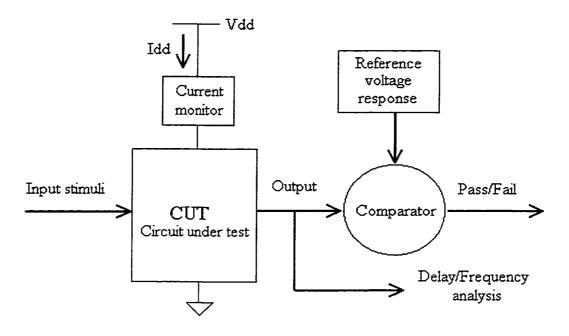

Generally, IC testing methodologies can be classified into two categories: voltage testing and parametric testing. The first analyzes logic levels of the circuit-uder-test (CUT) outputs. The CUT is a generic term used in the literature to refer to the integrated circuit design or component being tested. After the input stimuli have been applied to the CUT, circuit response is compared with the logic values produced by the reference circuit for the same input stimuli. The second one is concerned with the values of CUT parameters such as power supply current, propagation delay, frequency response, temperature etc. Parameters are monitored and compared to the expected values under certain circuit operation conditions. Both methods are shown in the Figure 1.3.

IC testing can be either external or internal (embedded). In the early days of IC design, the testing of IC's started as bench-top testing. An external source of input stimuli would be applied to the circuit under test (CUT), and circuit response would be collected and analyzed at the output. This was sufficient, considering the small number of devices per chip and the low speed at which the chips operated. As IC complexity and speed increased, it was more difficult to fully test IC's on the bench. This led to the development of automatic test equipment (ATE). ATE resulted in the integration of a collection of interconnected and synchronized bench-top instruments into a test station.

Figure 1.3: General testing environment

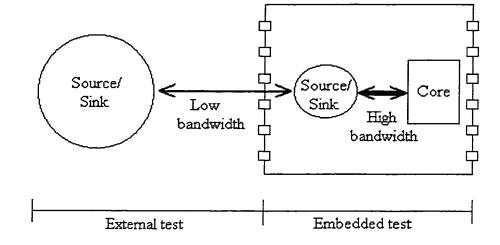

The main drawback of ATE equipment is its high cost. With the next generation of IC technology, the testing of even more complex circuits operating at high speed can not rely only on external testing. The idea of internal or embedded type testing was thus introduced. Scan path and built-in-self-test (BIST) designs are the most widely used embedded methodologies. Testing hardware added to the chip performs the function of analyzing and monitoring the operation of the chip. In scan design methodology, specially designed memory elements are used so thet.al.l or some subset of these memory elements can be fully controlled and observed via some special access mechanism usually consisting of one or more shift-register scan-chains. A scheme of the embedded testing is depicted in Figure 1.4. A low-bandwidth signal is generated by the external source and transported to the internal source/sink at the speed at which the signal can be handled bye the I/O's. This high bandwidth signal is processed internally, and the final processing result is handed out to the external source/sink for evaluation. The idea of embedded test hardware was defined as "design for testability". Economic factors favor for embedded testing. The application of embedded testing circuitry reduces the need for expensive ATE.

Figure 1.4: Embedded test

Today, the increasing gap between external and internal bandwidth is the main limiting factor in at-speed testing in the application of external testing equipment. The at-speed testing is performed at the rated operational speed of the circuit. As a result of this tendency, it will not be possible to test chips with external testing equipment in the near future. It is predicted that the balance of external and internal testing functions will shift to the solely internal ones. Embedded testing will most likely rise to the higher level of the IC testing, where diagnostics, measurement, debugging and repair will be possible with the next generation of IC designs.

Two basic testing methods are off-line and on-line testing. Off-line testing is more traditional and is performed when the normal operation of the circuits under test is interrupted. See Figure 1.5. The circuit enters test mode and is either switched to ATE equipment or tested by the BIST structure. The main drawback is the memory limitation of ATE. Even with medium complex circuits, large amounts of response information have to be stored in order to evaluate circuit performance. Another problem is the long connection lines between the CUT and ATE. These lines can introduce parasitic effects and limit the reliability of the testing. On-line testing is performed during the normal operation of a circuit and in a few different modes (Figure 1.5). There is the possibility of concurrent checking, testing in intervals, or testing during the idle operation of the circuit.

When the CUT is in the idle state the user has a higher priority, and testing can be interrupted at any time. A larger part of the testing procedure is performed by the BIST circuitry, so that ATE equipment can be significantly simpler. The area overhead required for the BIST structure is expected to be less than 15% of the CUT.

Figure 1.5: Off-line test and on-line test

A number of testing techniques are available today for the testing of very large scale integration (VLSI) circuits. Generally, these techniques can be classified into five different methods:

- Functional testing: the CUT is tested in normal operation mode at its rated speed

- Structural fault testing: the CUT is tested for permanent faults such as stuck-at-fault, bridging faults, shorts, etc., The circuit can be operated at a lower speed

- Inductive fault analysis: a simulation is used in the analysis of the defect generation mechanisms for possible permanent faults. In this case as well, the CUT does not have to be operated at the rated speed.

- Delay testing: the CUT is tested at its rated speed and observed for any delays in signal propagation.

- Current monitoring: the voltage supply current, drawn by the CUT, is analyzed while different input conditions are applied to the circuit. This can be done either when the circuit is in the static (quiescent) or dynamic (transient) state.

Functional testing is the oldest approach. A sequence of input vectors is generated and fed into the CUT. The advantage of this approach is in the fact that these tests can verify the correct operation of the CUT and that test vectors are already available from test cases used by the design engineer. Even though these tests discover a large percentage of faults, the fault coverage has recently come under question. The major drawback is that even the testing of relatively small digital circuits, such as a 32-bit adder, requires a pattern of 2<sup>65</sup> input vectors, rendering this approach inapplicable even with the fastest ATE tools.

Structural testing is based on "stuck-at" fault models that are artificial presentation of failures in digital circuits. The stuck-at fault model is the most widely used in IC testing. This fault model is based on the assumption that one of the connection lines between the digital gates is permanently stuck at some logic value, "0" or "1". Stuck-at fault can be single or multiple, if it happens in various parts of the circuit. A single stuck-at fault model is shown in Figure 1.6.

Figure 1.6: Stuck-at fault model

Experience shows that this type of fault modeling can detect a high percentage of faulty IC's. The biggest advantage of this type of fault modeling is that the response of the digital circuit can be mathematically analyzed, using Boolean algebra. The CUT response is analyzed after the previously defined set of test vectors had been applied to the CUT input. There are a number of techniques to define test vectors (test pattern generation - TPG), some of which are based on Boolean algebra, some on search-

algorithms, and on a combination of the two previous techniques. An inability to use the stuck-at type model with certain types of CMOS failures has resulted in alternative fault models such as stuck-open, stuck-on and bridging fault models.

Furthermore, limitations of permanent fault models in digital circuits inspired development of alternative approach as to fault modeling, namely *inductive fault analysis* (IFA). By means of simulation, faults resulting from particular modes of failure, such as particle contamination, are inserted into the circuit. These faults can be in the form of metal blobs causing shorts between two interconnection lines or some other deviations on particular layers of the IC. The main advantage of IFA is that modeled faults are more realistic as compared to the traditional stuck-at fault models. The main drawback is that the technique is time and cost extensive, since it requires sophisticated testing equipment.

Delay testing is based on the assumption that these delay-type of faults do not affect circuit performance, but circuit functionality. This means that a circuit will operate correctly at a low speed but will fail at the rated speed. Two types of delay models are the gate delay model and the path delay model. The former assumes a delay at a certain gate; the latter one assumes a delay accumulated along the path of signal propagation. The disadvantage of delay testing is that it is very sensitive to additional delays in other parts of the circuits that are not the target of the testing.

In current monitoring, the voltage supply current drawn by the circuit under test is monitored and compared to the reference current value. It is assumed that a faulty circuit produces an abnormal or at least a significantly different amount of current compared to the current produced by fault-free circuits. There are two types of current monitoring: quiescent current monitoring--Iddq, performed after the input has been applied and the CUT has reached its stable (quiescent) state and transient current monitoring--Iddt, the monitoring of the dynamic current at the time of input application. Monitoring can be done externally using ATE or internally using built-in-current-sensor (BICS). Traditional voltage-based testing techniques, such as stuck-at-fault, have limitations in detecting faults that do not affect output voltage levels such as shorts and bridging faults. Also, certain faults cannot be described by the stuck-at-fault model and show the necessity for more realistic fault modeling. In both cases, current monitoring has proved to be very effective in the detection of these faults and it is widely used in the industry, mostly as

Iddq testing. The major drawback of this type of testing is the degradation of CUT performance as a result of the insertion of a current sensing element into the current path between the CUT and the ground between the CUT and the voltage supply. The largest obstacle for Iddq is its low testing speed. Since a quiescent current can be observed only after the transient part has settled down, a high testing speed cannot be achieved. A few recent papers argue about the limits that Idqq testing has reached. The increased complexity of VLSI circuits with a high density of devices on the same chip has resulted in high levels of static current and the problem of setting the quiescent current reference value. In any case, Iddq testing currently provides valuable tool in the detection of shorts and bridging faults, and Iddt continues to be an attractive research subject.

#### 1.4 Thesis Summary

Limitations in traditional stuck-at fault testing methodologies show necessity for more efficient testing approaches. As well, faults that cannot be modeled by existing fault models require the development of a new testing methodologies. A current monitoring technique demonstrated the potentials in overcoming these obstacles in VLSI testing. Additionally, built-in current monitors provide the possibility for on-line testing, performed during the normal at-speed operation of the CUT. These were the main reasons for the selection of current monitors, as a subject of the research presented in the thesis.

The thesis presents two designs of built-in current monitors for on-line testing VLSI circuits. Both monitors are designed in low-voltage environment. The first design is the improved version of the Stopjaková/Manhaeve design, described in Section 2.6.3. The second monitor is the new design based on the unbalanced current mirror design. This design introduces additional sensing element which improves sensibility of the current monitor.

Current monitoring is the subject of this thesis and it is described in greater detail in the following Chapter 1. Chapter 2 provides background information and literature review. Definitions of the quiescent and the transient current monitoring are presented.

Various designs of current monitors are discussed along with examples of each of the analyzed approaches. Previous work is discussed with comments on every given example.

Chapter 3 proposes an improved design of current monitor based on earlier designs. The monitor is designed for the testing of Low-Voltage environment (1.5 V) circuits. The design is then implemented in 0.35  $\mu$ m and 0.5  $\mu$ m technology and. It is intended for monitoring both quiescent and transient current elements. The design is suited for the testing of digital circuits. Simulation results are discussed and analyzed. Finally, measurement results of chips implemented in 0.35  $\mu$ m and 0.5 $\mu$ m are provided.

Chapter 4 presents a new current monitor for combined Iddq and Iddt testing. This is also a low-voltage design that can be applied to mixed signal (analog/digital) circuits. Its design is simulated and manufactured in 0.35 µm and 0.5 µm technology. Simulation and measurement results are discussed.

Chapter 5 gives an overview of future developments in the field of current monitoring. A new idea for introducing an inductive element as a sensing device is elaborated. A new design of the solenoidal inductor is proposed.

Chapter 6 draws conclusions about the work described in the thesis and summarizes the presented material.

# Chapter 2

# Background and Literature Review

This chapter presents background and literature review on current monitoring. Current behavior of CMOS circuits is presented in the Section 2.1. Section 2.2 contains a description of the fault models used in testing by voltage supply current. Section 2.3 defines the basics of current monitoring, including Iddq and Iddt monitoring techniques. Limitations of current monitoring are explained in Section 2.4. In Section 2.5, various aspects of technology scaling are described. Design of current monitors, presented in a literature review, is given in Section 2.6.

#### 2.1 Current Behavior of CMOS Circuits

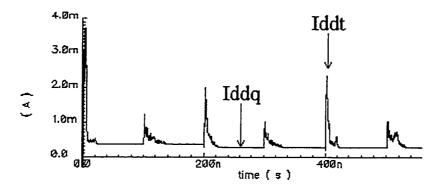

Two elements of the voltage supply current Iddq – quiescent current and Iddt – transient current can be seen in Figure 2.1. During the switching phase of the CMOS circuit, a dynamic (transient) current is drawn by the circuit. After the settling period, when the CUT has reached its stable state, current drawn by the CUT becomes very small, and it is referred to as leakage or quiescent current.

Figure 2.1: Voltage supply current (Idd)

## 2.1.1 Quiescent Current - Iddq

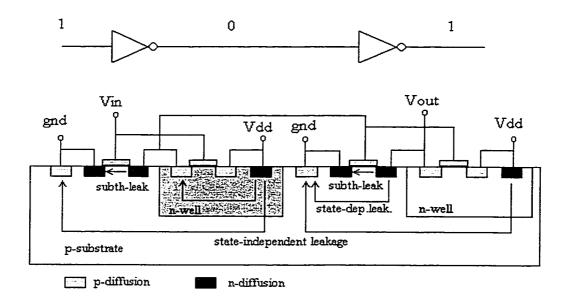

Quiescent or Iddq current is made of two major components: the junction leakage current and subthreshold leakage current [5]. Both components can be seen in Figure 2.2.

#### Junction Leakage Current

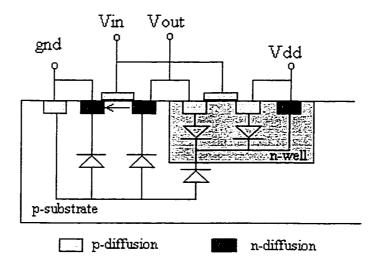

Reversed biased PN-junction leakage currents result from various mechanisms such as diffusion and thermal generation in the depletion region of the PN-junctions [6,7]. The leakage currents of reverse-biased sources and drain junctions are state-dependent, while the leakage current of reverse-biased well-substrate junctions is state-independent (Figure 2.2). A simple model that describes formation of parasitic PN-junctions for a CMOS inverter will help understand the mechanism of leakage involved in the device (Figure 2.3). The source-drain diffusions and the n-well diffusion form parasitic diodes. As well, one diode is formed between the substrate and the n-well.

Figure 2.2: Junction leakage current and subthreshold current

Figure 2.3: Parasitic PN-junctions in a MOS device with a p-substrate

Junction leakage currents can be estimated by the formula:

$$I_{leak} = Js \sum [Ai] \tag{2.1}$$

where Js is the reverse saturation current density of the PN junction defined by the process, N is total number of reverse-biased PN junctions and Ai and the total area of the i-th junction. The total area A can be estimated as:

$$A = W \cdot L \cdot \pi \cdot X_j \cdot (W + L) + \frac{\pi}{6} X_j^2$$

(2.2)

where W and L are the width and the length of the device and Xj is the junction depth. For simplicity, Figure 2.3 describes junction areas as rectangular, but in reality, there is always some roundness in diffusion areas. To include this curvature-effect, the  $\pi$  multiplier was introduced in Formulas (2.2) and (2.3). For a well-substrate PN junction, the effective area A is estimated by equation (2.3):

$$A = W \cdot L \cdot 1.6X_{j} \cdot (W + L) + 0.8\pi \cdot (W + L) + \frac{\pi}{6} (0.8X_{j})^{2}$$

(2.3)

#### Subthreshold Current

Subthreshold current is generated when the gate voltage is lower than the threshold voltage Vt and there is some voltage between the source and drain of the MOS transistor [8]. It is generated by the minority carriers and diffusion. The carriers move in a similar way as they would move in the base of a bipolar transistor. This component is state independent. Subthreshold current depends exponentially on Vgs and Vds through the carrier concentration. The subthreshold current in an NMOS transistor can be estimated by the following equation:

$$Ids = \mu_N Cox \frac{W}{L} V_t^2 \exp \left[ \frac{Vgs - V_{THN}}{nV_t} \right] \times \left( 1 - \exp \left[ -\frac{Vds}{V_t} \right] \right), \tag{2.4}$$

where  $\mu_n$  is the electron mobility, Cox is the gate capacitance by the area, W and L are length and width of the device, Vth is threshold voltage and  $V_T$  is the thermal voltage.

Other leakage currents may appear in CMOS technology, but these currents are undesirable and here are assumed to make up a small portion of the total leakage current:

- Gate-induced drain leakage currents: it occurs with the low gate and high drain bias due to band-to-band tunneling of electrons across the pn-junction in the gate-to-drain overlap region where a high negative electric field exists in the oxide [9]. These currents flow from drain to substrate.

- Bulk punch-through current: It flows from the drain to the source due to a lateral bipolar transistor formed by the source (emitter), the bulk (base) and the drain (collector). This component is controlled by raising the impurity concentration in the bulk channel region.

- Tunneling currents: These are generated across the oxide between the gate and drain. For feature sizes above  $0.1 \mu m$ , they are assumed to be negligible [10].

#### 2.1.2 Transient Current - Iddt

The peak of Iddt can be estimated by taking into account the number of switching nodes at the time of evaluation [11]. Drive strength and capacitance of switching nodes determine this peak value of the supply current. Quantification of these elements is possible through the electrical models and the parameters characteristic of the technology in use. The estimated transient current is:

$$I_{TRmean} = \frac{1}{T_{TR}} \left( Vdd \cdot \sum_{H}^{L} C_i + \sum_{i} I_{SCj} + \sum_{i} n_k \cdot I_{FTk} \right)$$

(2.5)

where  $T_{TR}$  is switching period, Vdd—power supply, Ci—node capacitance,  $n_i$ —circuit node. The main contributor to  $I_{TR}$  is capacitance charging currents, the first term. The

second term in equation (2.5) is the short circuit current at the switching nodes. The last term is the stochastic current representing the contribution of false transitions that may depend on circuit design, input pattern and signal timing.

If N--the number of switching transistors is very large, like in case of VLSI circuits, then the transient peaks value can be very high. This high value of the current peaks presents the main problem in the design of current monitors. To be effective, current monitors must have, on one hand, a very large dynamic range for these high transients, and on the other hand, they have to be very sensitive and have high resolution in order to detect low values of leakage currents. Consequently, dynamic current monitoring has not yet found practical implementation in industry. Two exactly opposite requirements, a small impact on the circuit under test and high sensitivity for the wide range of voltage supply currents, render design of dynamic current monitors extremely challenging.

## 2.2 Fault Modeling

In the presence of a fault, current response of the CUT depends on the type of the fault involved. Short and bridging faults result in increased levels of static and dynamic current being drawn by the CUT, whereas open faults lead to decreased activity of the CUT, reducing the Iddq and the Iddt values. Fully understanding the mechanism of faults and the behavior of voltage supply current in the presence of fault requires a proper understanding of fault models. Most physical defects can be classified as "shorts" and "opens". The fault models involved in MOS are electrical models of defects such as gate-oxide shorts, bridging faults, floating gates and open faults. These models are used in simulation analysis in order to obtain results of the specific failures and their impact on circuit performance.

#### **2.2.1** Shorts

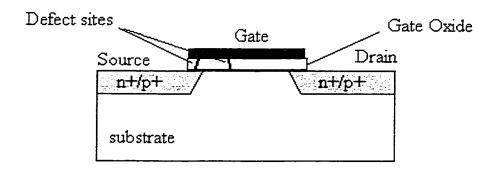

These faults result from unintended connections between metal, polysilicon or conducting paths through insulation layers. The s-a-f test is not always able to detect these faults. However, most shorts will produce an abnormal current that can be easily detected. Shorts of particular interest in the testing of CMOS circuits are gate-oxide shorts (GOS) [ 12 ], electrical connection through the thin oxide between the gate and the silicon surface of a MOS transistor (Figure 2.4).

Figure 2.4: Structure of gate-oxide short in a MOS-transistor

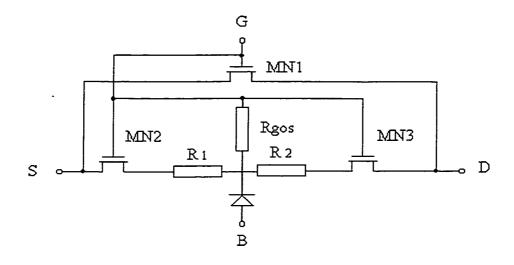

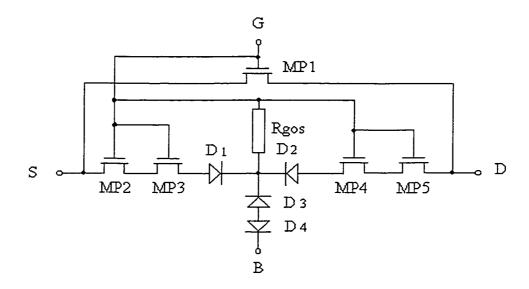

GOS result from the manufacturing process or material defects. All shorts located in the gate-source region and gate-drain region can be classified as one type of shorts. The second type of shorts is located in the channel region, far away from the gate-source and gate-drain area. The structure and models of NMOS and PMOS models of gate-oxide shorts are illustrated by Figure 2.5 and Figure 2.6. These shorts are very hard to detect, and testing of VLSI circuits presents special problems [13]. Gate-oxide shorts cause the Idd current to increase, and in most cases, logic voltage levels and propagation delay times to degrade. However, the functionality of the circuit may not be affected by the GOS.

Figure 2.5: GOS model for NMOS transistor

Figure 2.6: GOS model for PMOS transistor

#### 2.2.2 Bridging Faults

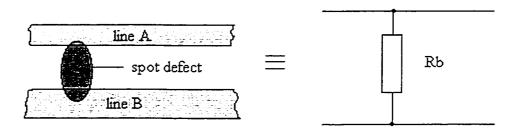

Bridging faults occurs when two or more conducting lines are interconnected or when the insulating material is missing. These faults may originate during the fabrication of in field-operation. These defects are classified as horizontal bridging interconnections inside the same layer or as vertical bridging interconnections between different layers. Figure 2.7 shows the fault model of the bridging defect. A bridging fault in a MOS transistor can result in bridging between any two of transistor's four terminals. Since it does not behave as a permanent stuck node to a logic value, the bridging fault typically cannot be modeled as a stuck-at-fault model. A bridging fault can be represented by the resistor connecting two interconnection lines or layers (Figure 2.7).

Figure 2.7: Bridging fault model

These faults can be divided into high-resistance and low-resistance faults. Statistically, most low-resistance bridges occur between two conducting layers and have a value below  $500 \Omega$  [14]. In this case, they cannot be ignored like high-resistance bridges. Bridging faults usually lead to propagation delay times. Hard bridges cause degradation of voltage levels, stuck-open and stuck-on faults.

#### 2.2.3 Open Faults

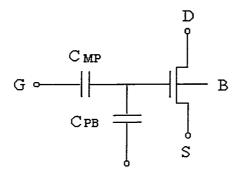

Open faults appear when the conducting path is broken. A conducting path in one of several layers can be broken horizontally or vertically. A break on the gate connection results in a floating gate. Another important fault is source/drain open. The floating gate fault model is presented in Figure 2.8. C<sub>PM</sub> represents capacitance poly-metal and C<sub>PB</sub> represents poly-base capacitance.

Figure 2.8: The Floating gate fault model

# 2.3 Current Monitoring

More than a decade ago, supply current monitoring was introduced as a very promising method in the testing of CMOS circuits. This method is based on the fact that defective circuits produce an abnormal or at least significantly different amount of current compared to the current produced by fault-free circuits. This excess current can be sensed and fault detected.

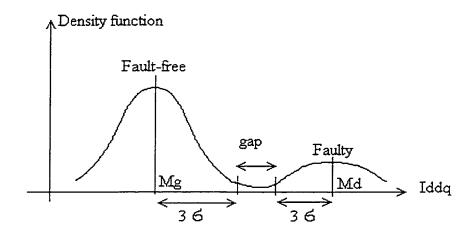

The power supply current (Idd) can be defined by its two elements: Iddq-quiescent current and Iddt--transient or dynamic current. Iddq is basically a leakage current drawn by the CMOS circuit when it is in its stable (quiescent) state. Iddq testing relies on the fact that defect-free CMOS devices have a very low leakage current when the circuit is in the quiescent state. For Iddq testing to be successful, it is important that defective current be significantly higher than the fault free current value. A general distribution of Iddq values in a CMOS network is presented in Figure 2.9, where Mg and Md represent the mean values for non-faulty and faulty Iddq values, respectively. The decision between faulty and non-faulty Iddq response can be made by setting the reference value between the two distributions.

In order to detect the fault by Iddq testing, the faulty-current path between a power-supply and a ground has to be acitvated. Therefore, a set of CUT's test vectors that will satisfy this condition has to be defined. Iddt is a supply current produced by the circuit under test (CUT) during the transition period after an input has been applied to the CUT. Every input vector produces different dynamic-current response of the CUT. If

there is an active fault, circuit's current response will differ from the normal current response. This information about the CUT is used in the Iddt testing.

Figure 2.9: General distribution of the Iddq values in CMOS network

Numerous current monitoring techniques as well as numerous designs of current monitors have been proposed. Most of these are Iddq-based techniques. Iddt testing has not yet found practical implementation in industry because of the difficulty of extracting of useful information from fast-changing current response. Current pulses can range from several µA's to a few hundred of mA's. Even though only Iddq techniques have been used in practice, it has been proven that some faults, such as opens, do not affect quiescent current and cannot be detected through this testing. On the other hand, these types of faults affect transient response of the circuit and can be detected by Iddt testing. Consequently, Iddt can be used as a powerful complementary technique.

Some researches argue that Iddq testing has reached its limits as a result of device scaling [15]. This is supported by predictions of the Semiconductor Industry Association's (SIA) road map for the next fifteen years of development of submicron technologies (The National Technology road map for the Semiconductor Industry Association 1994). On one hand, SIA objectives encourage further work in Iddq testing because Iddq testing is very efficient in detecting faults resulting from decreasing device sizes and from increasing circuit complexities [16]. On the other hand, the SIA road map

questions the efficiency of Iddq testing because of a radical increase of leakage current in high-density integrated circuits.

One of the parameters that has been affected by scaling is leakage current. A critical requirement of Iddq testing is accurate measurement of a very small current. Typically, the Iddq threshold for the decision pass/fail making is set to 1  $\mu$ A to 10  $\mu$ A. In order to make a correct decision, the Iddq of a fault-free CUT has to be at least one order of magnitude lower than the Iddq threshold. With millions of devices on a single chip, leakage current becomes significant. As a result of increased current leakage, the values of fault-free and faulty Iddq current start to overlap, and it is impossible to set an adequate threshold value. Partitioning of the CUT into smaller parts which lowers leakage current to some acceptable level, is one way of overcoming this problem [17].

#### 2.3.1 Current Monitoring Methodologies

Several different methodologies have been developed to test VLSI CMOS circuits. Classification can be done by the type of the circuits being tested or by the specific approach used in the monitoring technique. Also, as mentioned in the previous chapter, current monitoring can be done externally or internally by built-in current sensor, as well as off-line when the circuit is not in the normal mode operation and on-line when the operation of the circuit is not interrupted.

Depending on the type of circuit being tested, different methods for digital and analog/mixed-signal circuits exist. Depending on the approach, CUT current response can be analyzed using reference voltage analysis, signature analysis, waveform analysis, etc.

#### Monitoring of Digital Circuits

The traditional technique for testing digital CMOS circuits is voltage testing by using stuck-at-fault modeling. As was mentioned in the previous section, a number of failures cannot be modeled by the stuck-at fault model. Moreover, certain types of CMOS faults, such as gate-oxide shorts, certain bridging faults, certain open faults, stuck-on faults, punch-through faults, operation-induced faults and soft pn-junction faults, may not

manifest themselves as logic faults. Parametric faults such as incorrect threshold voltages, excessive parasitics, etc., are also difficult to detect by the traditional voltage techniques but often affect signal time propagation delays as well as power consumption of the circuit. Iddq monitoring techniques have shown to be very effective in detection of these types of faults. Iddq tests implemented prior to the burn-out test can significantly decrease fall-out.

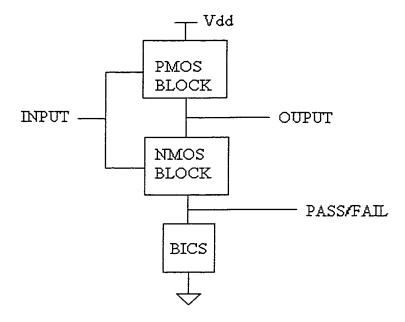

In functional testing, the site of the fault has to be excited and the effect of the fault has to be propagated to the output. In current monitoring, testing the propagation of the fault is automatic. The current response is picked up by the current monitor and compared to the reference value. The scheme for current monitoring is shown in Figure 2. 10.

Figure 2. 10: Current monitoring scheme for CMOS digital circuits

#### Monitoring of Mixed-signal Circuits

In recent years, the success of current monitoring in testing VLSI digital circuits has inspired researchers to try to implement current monitoring technique in testing of mixed-signal integrated circuits (MSIC). As well, the implementation of digital and analog devices on a single chip has supported the great need for the development of reliable testing techniques for this type of circuit. Nevertheless, testing of mixed-signal circuits presents far more complex problem than testing of digital circuits. Analog circuits are characterized by many parameters including gain, frequency, phase shift, etc.; therefore proper operation of a CUT, including monitoring of all parameters, is not an easy task.

Many techniques have been proposed for testing MSIC circuits. Many of them use the division of a circuit on a digital and an analog part, where tests are applied to each part separately. The problem with this approach is that analog parts contain circuits such as A/D converters and switched-capacitor circuits that exhibit characteristics of both analog and digital circuits. Several papers discussing the implementation of current monitoring techniques apply only transient current analysis [2,3] or integration of current signal. [1]. The first technique does not consider the quiescent response of the CUT and the second one can result in a high level of aliasing, that is, in a number of identical responses as a result of current averaging.

#### Time-Domain Analysis

A procedure for testing of mixed-signal integrated circuits (MSIC's), called "time-domain testing," was used in the work for this thesis [2]. The basic idea is explained in Figure 2.11.

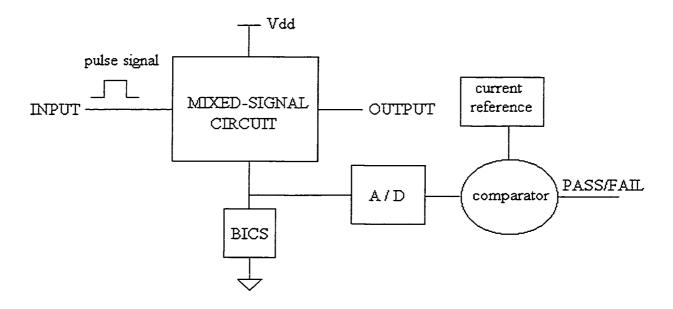

Figure 2. 11: Time-domain analysis for mixed-signal circuits

This procedure is based on the excitation of CUT with a series of pulses at the same time that the current response is monitored and evaluated. This response is digitized and compared to a predetermined fault-free value. This predetermined value represents signature of the CUT. Of course, this value depends on the input value, so changing the input stimulus produces different signatures for static states—state-high and state-low and transient states—low-to-high and high-to-low.

# 2.4 Limitations of Current Monitoring

Testing of integrated circuits by current monitoring has some limitations. These are due to the fact that in order to detect a fault in an IC, a fault has to be activated by activating the current path through the fault. In certain circuit configurations, when this current path cannot be activated, the fault cannot be detected. Also, with constant scaling of device sizes with new technologies together with increased density of integrated circuits, leakage currents have increased to the level where it is not possible to set a reference value between the normal and the faulty current value.

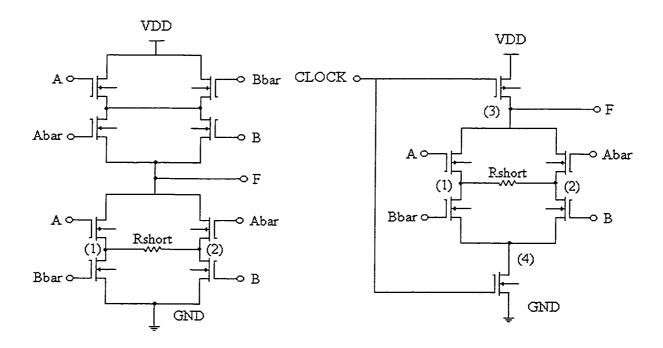

#### 2.4.1 Limitations in Detection of Shorts

Shorts are faults resulting from unintended connections between metal, polysilicon or conducting paths through the insulation layer. The s-a-f test is not always able to detect these faults. However, most shorts will produce an abnormal current, which can be easily detected. An excessive amount of current will be produced if an input pattern can connect the VDD node to the GND node. If we consider a short between nodes (1) and (2) in Figure 2.12 and apply a logic "high" to A and B, VDD and GND will be shorted, and excessive Iddq will be registered, and a fault will be detected. Figure 2.13 shows limitations of the Iddq method [1]. If we consider a short between nodes (1) and (2), both nodes will be charged to VDD or discharged to GND when the clock is "high." In this case both nodes are at the same potential, so it will not result in a significant Iddq current, and the fault will not be detected.

Figure 2. 12: Limitations of s-a-f test

Figure 2. 13: Limitations of  $I_{DDQ}$  test

# 2.4.2 Limitations in Detection of Open Defects

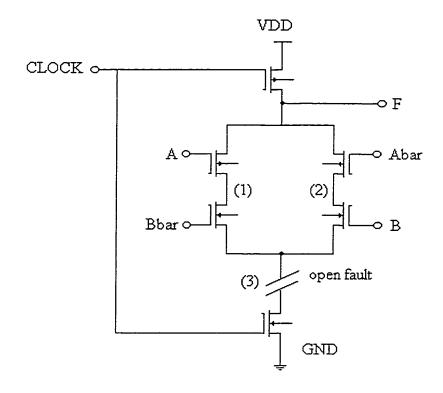

Open defects happen when a conducting path in one of several layers can be broken horizontally or vertically. The two most important open defects are floating gate and source/drain open.

The Iddq test may not always detect an open defect. Figure 2.14 shows a source/drain open defect (node 3). If transistors T1 and T3 or T2 and T4 are on, and the clock input signal goes from "high" to "low" or "low" to "high", a temporary path from PWR to GND induces a high Iddqt peak. However, this path will be removed because of the source/drain open, and the Iddq will not detect the fault.

Figure 2.14: Source/drain open

These examples as many other experiments demonstrate that the s-a-f test and the Iddq test cannot always detect these faults, whereas the Iddt test is able to do so. The comparison of these three techniques' statistical data for the overall defect coverage is shown in Table 2.1. Two hardware experiments are conducted by Shyang et.al. [17]. Both experiments include IC designs with built-in defects and physical measurements of both, power supply current response and output voltage response. Four types of faults were observed: open drain/source, single floating gate, double floating date and short in the pre-charge chip. Experimental results of the fault coverage are very encouraging and show high fault coverage in case of Iddq and Iddt test methods.

Table 2.1: Overall defect coverage data

|                      | DEFECT COVERAGE (%) |      |      |           |               |

|----------------------|---------------------|------|------|-----------|---------------|

|                      | Total gates tested  | Iddq | Iddt | Iddq+Iddt | Logic<br>test |

| Open drain/source    | 128                 | 28.1 | 96.9 | 100       | 72.7          |

| Single floating gate | 56                  | 92.9 | 100  | 100       | 64.3          |

| Double floating gate | 44                  | 90.9 | 100  | 100       | 90.6          |

| Short in pre-charge  | 8                   | 0.0  | 100  | 100       | 100           |

# 2.5 Aspects of Technology Scaling

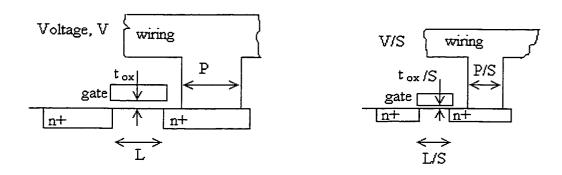

The basic idea of scaling, shown in Figure 2.15, is to reduce the dimensions of the MOS transistors and the wires connecting them. The scaling of devices affects numerous device parameters, one being the subthreshold currents or leakage current [18]. Plotting the distribution of the Iddq values for a collection of chips from the same CMOS network should reveal a bimodal distribution, similar to the one shown in Figure 2.9. The first normal segment of the distribution depicts the Iddq values in the non-defective

device, with a mean value denoted by Mg. The defective parts drawing excessive current due to the presence of a defect have their own distribution with higher values for the quiescent current, with the mean value Md. If the two distributions are far apart, a quiescent current limit can be selected that differentiates the non-defective product from the defective one. As long this separation gives an discriminatory difference, testing can be sufficiently reliable.

Figure 2.15: Device before and after scaling

Iddq is basically the leakage current in a CMOS when it is in a stable state. This leakage occurs when the transistor is in a cut-off region where the drain-source current can be approximated with formula (2.4) which is repeated here for the convenience:

$$Ids = \mu_n Cox \frac{W}{L} V_T^2 \exp\left[\frac{Vgs - V_m}{nV_T}\right] \times \left(1 - \exp\left[-\frac{Vds}{V_T}\right]\right)$$

(2.6)

[ $\mu_N$ - surface mobility of carriers, Cox-gate oxide capacitance, Vtn-threshold voltage, V<sub>T</sub>-thermal voltage, W- gate width, L-gate length].

In the low-voltage/low-power design, reducing the channel length also reduces the peak of the surface potential and increases the current [4]. If Vdd is reduced, the peak is further reduced. Therefore, the short channel effect contributed to the penetration of the junction electric fields into the channel region, causing a lowering of the barrier and  $V_{th}$  reduction

leading to further increasing of the leakage current. The low-voltage/low-power circuits can be mainly designed by two techniques: constant field scaling and reducing the Vdd.

#### 2.5.1. Constant Field Scaling

The scaled design is obtained by applying a dimensionless factor S to all dimensions including those vertical to the surface, device voltage and the concentration densities. As a result,  $V_{th}$  is reduced by factor  $\alpha$  and the gate-oxide capacitance given in the equation (2.7) also decreases by the same factor.

$$C_{ox} = \frac{\varepsilon WL}{t_{ox}} \tag{2.7}$$

Therefore, Ids is reduced. If we define  $I_f$  as the faulty current drawn by the CUT, the  $I_f$  will also decrease by the factor S:  $I_f$  '= $I_f$ /S. Since the fault-free current is increased, and the faulty current is decreased, the ratio between these two currents is therefore reduced. As a result, distinguishing faulty from the fault-free current value is diffucult.

## 2.5.2 Reducing supply voltage Vdd only

By decreasing the supply voltage Vdd, drain-source voltage is reduced. According to formula (2.8) V<sub>th</sub> will increase:

$$V_{t} (Vds) = V_{t}^{*} - \sigma Vds$$

(2.8)

[ $V_t^*$  - threshold voltage at low Vds < 0.1 V,  $\sigma$  - drain induced barrier lowering parameter]

Therefore, the leakage current will also decrease. As a result, the faulty and the fault-free values decrease, the ratio is preserved, and in this case, the Iddq test methods can still be used in this kind of low power circuits.

The impact of changing design and operating parameters on the effectiveness of Iddq testing can be analyzed by calculating the distance between the two means Mg and Md of the distribution, according to equation (2.9)

$$\frac{Md - Mg}{Mg} \tag{2.9}$$

Technological trends used on analysis are shown in Tables 2.2 and 2.3 [15]. The Ioff is the subthreshold current estimated over limited interval of device parameters and at zero gate voltage.

Table 2.2: Trends in CMOS technology at 100°C (SIA roadmap values)

| Year | Gates (x10 <sup>6</sup> ) | Vdd(V)  | Leff (um) | Max I <sub>dd</sub> off (nA/μA) |

|------|---------------------------|---------|-----------|---------------------------------|

| 1995 | 5                         | 3.3-2.5 | 0.25-0.45 | 5-10                            |

| 1998 | 14                        | 2.5-1.8 | 0.21-0.25 | 10-20                           |

| 2001 | 26                        | 1.8-1.5 | 0.1-0.15  | 20                              |

| 2004 | 50                        | 1.5-1.2 | 0.1-0.15  | 30                              |

| 2007 | 210                       | < 1.2   | < 0.1     | 30                              |

The fifth column of the Table 2.2 shows estimates for the Max  $Idd_{off}$  at  $100^{\circ}C$  as given in the SIA Roadmap [1]. The fifth column in Table 2.3 is the more accurate estimate, according to the [1], assuming that  $V_t$  is scaled down directly with the Vdd.

Table 2.3: Trends in CMOS technology with scaling V<sub>t</sub> proportional to Vdd at 25°C.

| Year | Gates (x10 <sup>6</sup> ) | Vdd(V) | Leff (um) | Average Idd <sub>off</sub> (nA/μA) |

|------|---------------------------|--------|-----------|------------------------------------|

| 1995 | 5                         | 3.3    | 0.45      | 0.004                              |

| 1998 | 14                        | 2.5    | 0.25      | 0.12                               |

| 2001 | 26                        | 1.8    | 0.15      | 2.5                                |

| 2004 | 50                        | 1.5    | 0.10      | 14.2                               |

| 2007 | 210                       | 1.2    | 0.07      | 82                                 |

The calculation of Mg and Md are based on several assumptions. If the calculation is based on Max Idd<sub>off</sub>, then it is assumed that only 10% of all the gates in the network would have Idd<sub>off</sub> values near the maximum of the distribution. The cumulative Iddq current of this 10% of the gates dominates the Iddq value of the good network. If the calculation is based on Average Idd<sub>off</sub>, all gates in the network contribute towards Mg. Here, it is assumed that only one leaky transistor per gate is present even though there are other possibilities. A defect can cause a gate to have a path from Vdd to GND through one PFET and two NFETs. Assume also that resistance PFETon = 15 k and NFETon = 6 k. Calculations are done by the equations (2.10), (2.11) and (2.12). First, Ioff values from Table 2.2 and Table 2.3 are multiplied by W to obtain Ioff values for a single device.

$$W = 20 Leff (2.10)$$

$$Mg = Gates \ X (10/100) / Max \ I_{dd}off$$

(2.11)

$$Md - Mg = Vdd / (2R_{NFET} + 2R_{PFET})$$

(2.12)

Table 2.4 presents the results of the calculation, revealing the sensitivity of  $Idd_{off}$  current to the variations of  $V_t$ . Table 2.4 demonstrates that ratios of 1/6 or above are required for Iddq testing to be useful. Unfortunately, an increase from 1/10 to 1/6 in Vt/V0 Vdd will result in about a 20% penalty in speed performance. In today's marketplace, manufacturers are unlikely to be willing to tolerate such an overhead for the benefits derived from Iddq testing. The suggested solution to this problem is the partitioning of the original design. Partitioning created lower Idd current in each portion. This increases the  $I_{DDQ}$  observability and improves reliability of the Iddq testing.

Table 2.4: Variation of relative distances (Mg-Md) on ratio V<sub>t</sub>/Vdd

| V <sub>t</sub> / Vdd | Ave Idd <sub>off</sub> (estim.) | (Md-Mg)/ Mg |

|----------------------|---------------------------------|-------------|

| 1/6                  | 9.9 x 10-4                      | 2670%       |

| 1/8                  | 0.02                            | 133%        |

| 1/10                 | 0.12                            | 22%         |

| 1/20                 | 4.38                            | 0.6%        |

A similar calculation to that used in an earlier section can be used to determine relative distance between means Md and Mg for the next ten years, using Table 2.3 and Table 2.4. The results are given in Table 2.5.

Table 2.5: Relative distance between the means Md and Mg.

| Year | Roadmap (Md-Mg)/Mg | Estimated (Md-Mg)/Mg |

|------|--------------------|----------------------|

| 1995 | 19.6%              | 1358%                |

| 1998 | 3.15%              | 22.1%                |

| 2001 | 1.28%              | 0.68%                |

| 2004 | 0.37%              | 0.08%                |

| 2007 | 0.07%              | 0.00%                |

Table 2.5 indicates that Iddq testing will cease to be possible for high performance designs as a device's geometry and power supply voltages are scaled down. In that case, new techniques to control the quiescent current must be developed.

#### 2.6 Current Monitors

#### 2.6.1 Off-Chip and On-Chip Current Monitors

Current-measurement devices can be designed as Off-chip monitors (OCM) and On-chip monitors (Built-In-Current-Sensors-BICS). Both can be classified according to a method using current monitoring. The direct method compares the monitored value to some reference value, and the indirect method uses the conversion of current value to a different quantity such as the voltage drop or the time required for the capacitor discharge [19]. According to the type of sensing element, monitors can be classified as capacitor sensors, resistor sensors or transistor sensors. Nonlinear devices (transistor, diode) can have a better dynamic range compared to linear elements (resistors).

Since OCM is usually implemented by external Automatic Test Equipment (ATE), using BICS has some advantages over the ATE. BICS significantly reduces the test equipment cost. Because of the high capacitance of I / O pads, the testing rate can be significantly reduced. BICS has improved detectability and observability of the circuit-under-test and higher resolution and higher testing resolution. Recently much work has been done in order to improve BICS sensitivity and reduction of the degradation of CUT performance, as these are two crucial elements of the design of a good current sensor.

#### 2.6.2 Design of a Built-In Current Monitors

Built-in current monitors should have the following characteristics [14]:

- High functional speed

- High current resolution

- Small voltage drop due to the testing circuit

- Simple testing circuit

- Small chip area of the testing circuit

- Small performance degradation of the CUT due to the testing circuit

The design of a current monitor is a trade-off between circuit speed, size, sensitivity, and accuracy. The higher resistance of the sensing element leads to an increased sensitivity but also to a lower speed and a higher voltage supply degradation, which is very important for low-voltage designs. A number of current monitors have been built, and a short analysis of some of them follows.

Most of the current monitors presented in the literature use a resistor or a MOS transistor biased in a triode region as a sensing element [20, 21]. The sensing element is inserted into the supply current path, and the voltage drop across the element or the current is sensed and evaluated. When a MOS transistor is used as a sensing element, nonlinear resistive elements are inserted into the Idd path, resulting in a degradation of the performance of the CUT, i.e., additional delay and voltage supply degradation. If a minimum supply voltage degradation and a high testing speed are to be achieved, the size of the transistor needs to be dramatically increased in order to decrease the resistance. On the other hand, a larger parasitic capacitance is achieved with the increased transistor size. Because of this RC parasitic effect, resistor as a sensing element is a better choice for high-speed applications [22].

#### 2.6.3 Previous Designs of Current Monitors

#### Flip-flop based design proposed by Maly et.al.

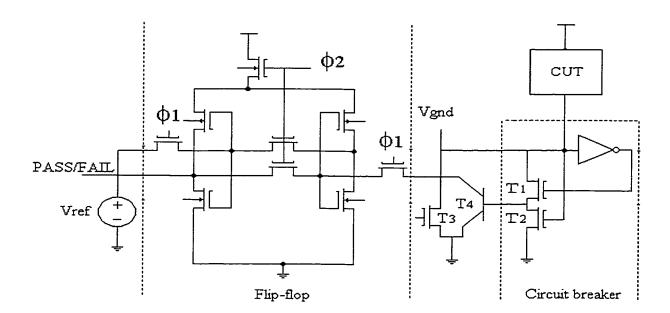

This current monitor consists of a flip-flop and a transistor-based nonlinear resistance circuit breaker [23] (Figure 2.16). It is connected between the CUT and ground. In a defect-free state, the virtual ground Vgnd point is at "0" where T1 is turned "on" and T2 is "off", In the presence of a fault, the defective current is drawn by the CUT, and the increased Vgnd voltage turns T1 "off" and T2 "on". This voltage level is compared to the Vref value by the flip-flop. The result is the PASS/FAIL signal at the monitor output. In case of a high current resulting from the shorts between the "power supply" point and "ground" point, the circuit breaker turns off the T4 and disconnects the CUT from the power supply. Transistor T3 ensures the correct operation of the circuit breaker by restoring the voltage at Vgnd.

Figure 2.16: Monitor proposed by Maly et.al.

A great deficiency of this design is the position of the monitor between the CUT and ground point. This position introduces a virtual ground point affecting the circuit's

performance. Another drawback is the requirement of a two-phase clock. Finally, the lateral NPN BJT used in the design makes this circuit difficult to implement.

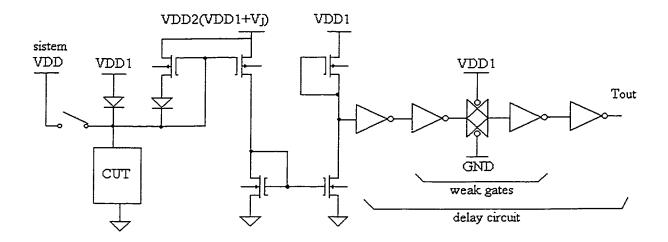

#### Monitor Design proposed by Miura

This is an example of a direct monitor [24]. The two voltage sources supply CUT through two diodes. The monitor design is shown in the Figure 2.17. The current is mirrored to the delay circuit preventing false error signal due to a dynamic current during switching. The main drawback of the circuit is the requirement of two power supplies, which make the monitor impractical for the most of the applications.

Figure 2.17: Monitor Design by Miura

#### Monitor Design proposed by Tang

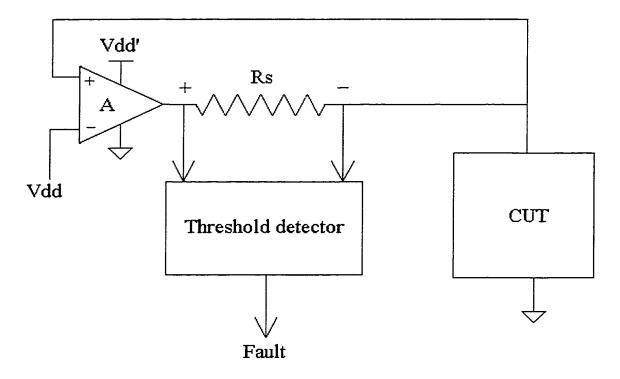

The current sensor is made of a two-stage operational amplifier (OPAMP), a threshold voltage detector and a resistor [25]. The monitor is shown in Figure 2.18. The CUT current passes the resistor Rs and produces the voltage drop on Rs. This voltage drop is sensed by the Threshold detector. A signal "Fault" is produced each time the current goes over the predefined threshold value.

The main disadvantage is the additional power supply Vdd' required for the operation of an operational amplifier. The Vdd' should be higher than the CUT power supply. As well, the characteristics of the OPAMP are difficult to implement accurately.

Figure 2.18: Monitor proposed by Tang

#### Monitor Design proposed by Kim et.al.

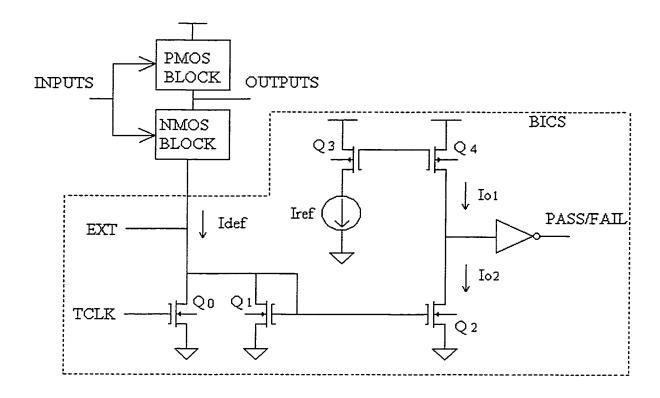

The essential element of this monitor is the current mirror [14]. See Figure 2.19. The current of the circuit-under-test is mirrored and compared to the reference current. If the CUT current is larger, then the reference current PASS / FAIL signal is set to "1", indicating the presence of a fault. The function of Q<sub>0</sub> is to connect or disconnect the monitor. Transistor Q<sub>0</sub> is controlled by the TCLK signal and turned off as soon as CUT reaches the quiescent state. As a result, the dynamic current produced by the CUT has no effect on the monitor since it is sinked through the Q<sub>0</sub> during the switching period.

The monitor is inserted in series between the circuit-under-test and the ground and suffers from the same deficiency as the Maly design. In order to be able to sink large transient currents, the transistors have to be large, introducing a large capacitance and an extra

delay. This factor may also cause a ground-bounce problem and seriously affect the functionality of the CUT. Signal EXT is applied to solve the problems of parasitic capacitance and ground bouncing providing the ground point in normal operation and floating during the test mode.

Figure 2.19: Monitor proposed by Kim and Hong

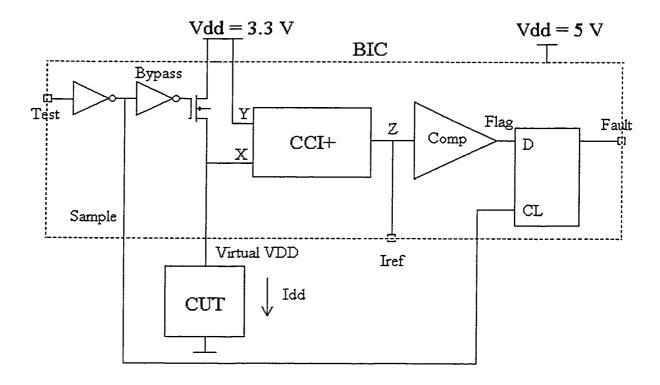

#### Conveyor Based Monitor proposed by Stopjaková et.al.

An interesting example of Iddq testing design is shown in the Figure 2.20 [26]. A CCI+ current conveyor is used as a monitor. The results obtained are shown in Table 1. Investigate range of currents was from 50 nA to 10  $\mu$ A with the testing frequency of 100 kHz and  $C_{LOAD} = 50$  pF. CCI+ current conveyor has two main functions in the design. One is to convey the  $I_{DD}$  current to the output terminal and the other is to keep the voltage level at the both input terminals. During the switching the circuit produces high transition currents and the Bypass circuit is added to protect the monitor. At the output  $I_{DD}$  current

is compared to the reference value  $I_{ref}$  at the current comparator and the signal Flag is produced as a result of the comparison. Since this is done continuously, this signal is then sampled at the end of the measurement period.

Figure 2.20: Monitor proposed by Stopjaková et.al.

As we can see, accuracy depends on the value of the current and the best results are obtained for the currents in the range 1  $\mu$ A to 100  $\mu$ A. Unfortunately the paper from this research did not provide any data on fault coverage.

Table 2. 6: Iddq test accuracy results

| Iddq current | Measured Iddq | Accuracy |

|--------------|---------------|----------|

| 50 nA        | 43 nA         | 14 %     |

| 100 nA       | 92 μΑ         | 8 %      |

| 1 μΑ         | 0.98 μΑ       | 2 %      |

| 10 μΑ        | 9.99 μΑ       | 0.1 %    |

| 100 μΑ       | 100.3 μΑ      | 0.3 %    |

| 600 μΑ       | 550 μΑ        | 8.3 %    |

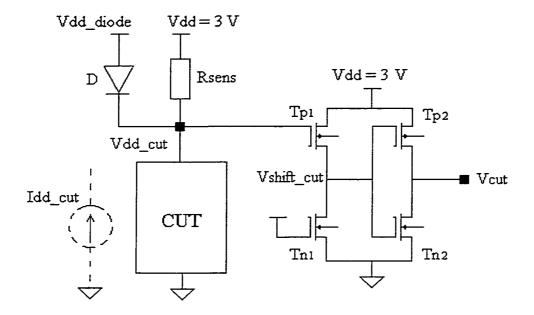

#### Monitor Design proposed by Antonioly et.al.

The main idea for this monitor was to amplify voltage drop initially caused by the current flowing through the current-to-voltage translator inserted between the CUT and the power supply [27]. The schematics of the monitor can be seen in Figure 2.21. Diode D limits the voltage drop produced from large transient currents. Tp1 and Tn1 use as a voltage shifter the sensed voltage to a Vshift\_cut. This voltage is further amplified by the inverter. The use of a depletion type P-MOS transistor in a level shifter allows for good sensitivity of voltage levels nearly equal to Vdd, so that only one power supply is sufficient. Large Rsens produces a large supply voltage deviation and, for large transient currents, affects Iddq settling time. The biggest drawback is that extra process steps are required to manufacture depletion type transistor Tp1.

Figure 2.21: Monitor proposed by Antonioli and Kinoshita

## Monitor Design proposed by Maidon et.al.