# Design of an Integrated mm-wave Area and Energy-Efficient Analog (RF) Beamformer

by

Ehsan Khodarahmi

A thesis submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Integrated Circuits and Systems

Department of Electrical and Computer Engineering

University of Alberta

© Ehsan Khodarahmi, 2024

### Abstract

The rising demand for high-data-rate services has led to increased congestion in traditional low-GHz RF wireless communication channels. To alleviate this bandwidth shortage, higher-frequency bands like millimeter-wave and sub-THz frequencies are used. However, these higher-frequency signals suffer from greater path losses, limiting their communication range. Directional and phased array antennas have emerged as solutions to this challenge, enabling the focused transmission or reception of signals in specific directions to extend the communication range. Phased array systems, utilizing techniques known as beamforming, adjust phase shifts between antenna elements to create directional beams. Their advantages include faster response times, greater flexibility, and smaller form factors compared to mechanical alternatives, making them popular in various modern wireless applications. Moreover, there is a growing demand for energy-efficient and compact phased array systems to make them more suitable for use in applications in which battery life and device sizes are the main concerns, ranging from handheld 5G/6G devices to UAV and satellite communication equipment. This study proposes innovative circuit solutions to meet this demand, addressing RF analog beamforming and exploring methods to improve power efficiency and reduce chip size.

In loving memory of my father

To my mother, Azam, whose unwavering encouragement has ignited my passion for learning

To my two sons, Soroush and Sepehr, whose understanding and patience during this pursuit of knowledge meant spending less time together, yet their presence has been my source of strength.

And to my beloved wife, Mona, whose love, sacrifice, and resilience have carried us through the challenges of this PhD program and beyond. Your unwavering support has been the cornerstone of my success.

### Acknowledgements

I extend my deepest gratitude to my supervisor, Dr. Kambiz Moez, whose unwavering guidance, invaluable insights, and constant encouragement have been instrumental in shaping this thesis and my academic journey. Your mentorship has been a beacon of light, guiding me through challenges and milestones alike.

I am equally thankful to my co-supervisor, Dr. Igor M. Filanovsky, for his invaluable contributions, support, and constructive feedback throughout this research endeavor. Your expertise and encouragement have greatly enriched the quality of this work.

To my family, I owe a debt of gratitude for their unwavering patience, understanding, and unwavering support during the ups and downs of thesis writing. Your love and encouragement have been my rock, sustaining me through the long hours and challenges of this journey.

Special thanks are due to Mrs. Mona Mostafavi, for her invaluable assistance in writing this thesis and providing essential figures. Your support and expertise have been indispensable in bringing this work to fruition.

I would also like to express my appreciation to my labmates, Mohammad, Marzban, Martin, Nan, Anil, Motaz, and Jun for their stimulating discussions, camaraderie, and words of encouragement. Your insights and friendship have enriched my academic experience immeasurably.

Completing my PhD degree at the University of Alberta necessitated relocating to a new country, a journey that would have been impossible without the invaluable support of numerous kind-hearted individuals both here in Canada and in my home country, Iran. I extend my deepest gratitude to my father and mother-in-law, Ahmad and Zari, for their consistent support during this transition. Additionally, I am profoundly grateful to my mother Azam and my siblings, Pejman, Peiman, and Mahsa, for their steadfast encouragement. Special thanks are also due to my dear friend Salman, whose assistance was instrumental during my arrival in the enchanting city of Edmonton. I also express my heartfelt appreciation to the warm and hospitable residents of Edmonton for their generous welcome.

Lastly, I extend my heartfelt thanks to all those who have contributed, directly or indirectly, to this thesis. Your support and encouragement have been deeply appreciated and have made this accomplishment possible.

# **Table of Contents**

| 1        | Intr | roduction                                                          | 1  |  |  |

|----------|------|--------------------------------------------------------------------|----|--|--|

|          | 1.1  | Motivation                                                         | 1  |  |  |

|          | 1.2  | Beamforming Fundamentals                                           | 4  |  |  |

|          | 1.3  | Beamforming Techniques                                             | 8  |  |  |

|          |      | 1.3.1 Digital Beamforming                                          | 8  |  |  |

|          |      | 1.3.2 Analog Beamforming                                           | 9  |  |  |

|          |      | 1.3.3 Hybrid Analog/Digital Beamforming                            | 11 |  |  |

|          |      | 1.3.4 Comparison of Beamforming Methods                            | 13 |  |  |

|          | 1.4  | Objectives                                                         | 14 |  |  |

| <b>2</b> | An   | alog (RF) Beamformers Literature Review                            | 15 |  |  |

|          | 2.1  | Introduction                                                       | 15 |  |  |

|          | 2.2  | Recent Advances in Implementing RF Phase Shifters                  | 16 |  |  |

|          |      | 2.2.1 Vector Modulator Based (VMB) Phase Shifters                  | 16 |  |  |

|          |      | 2.2.2 Passive Phase Shifters                                       | 24 |  |  |

|          | 2.3  | Recent Advances in Analog (RF) Beamformers                         | 35 |  |  |

|          |      | 2.3.1 Requiring a large scale phased array                         | 35 |  |  |

|          |      | 2.3.2 Novel Architectures for Multiple Beam Phased Arrays          | 37 |  |  |

| 3        | Are  | ea-Efficient Tapered Tunable Transmission Line Phase Shifters      | 39 |  |  |

|          | 3.1  | Proposed Tapered TTL Phase Shifter                                 | 40 |  |  |

|          | 3.2  | 2 Analysis of Tapered Tunable Transmission Line (TTTL) Based Phase |    |  |  |

|          |      | Shifter                                                            | 43 |  |  |

|          |      | 3.2.1 Calculation of Optimum Scaling Factor                        | 44 |  |  |

|          |      | 3.2.2 Calculation of Loss                                          | 49 |  |  |

|          | 3.3  | Design Procedure                                                   | 50 |  |  |

|          |      | 3.3.1 Design of a Non-Tapered Conventional TTL Phase Shifter       | 50 |  |  |

|          |      | 3.3.2 Design of a Tapered TTL Phase Shifter                        | 57 |  |  |

|          | 3.4  | Ku/K/Ka Band Tapered TTL Phase Shifter                             | 61 |  |  |

|          |       | 3.4.1   | Design of a Ku/K/Ka Band Tapered TTL Phase Shifter $\ . \ .$ | 61  |

|----------|-------|---------|--------------------------------------------------------------|-----|

|          |       | 3.4.2   | Tape-out and Fabrication                                     | 63  |

|          |       | 3.4.3   | Measurements                                                 | 65  |

|          | 3.5   | Discus  | ssion and Conclusion                                         | 70  |

| 4        | Are   | a-Effic | cient Analog Beamformers with Pseudo-Distributed Am          | -   |

|          | plifi | ier Are | chitecture                                                   | 71  |

|          | 4.1   | Propo   | sed Pseudo Distributed Amplifier Beamformer                  | 71  |

|          |       | 4.1.1   | Design Concept                                               | 72  |

|          | 4.2   | Lump    | ed Element Design of On-Chip Transmission Lines with Tunable |     |

|          |       | Electr  | ical Length                                                  | 75  |

|          |       | 4.2.1   | Analysis of an ATL Cell                                      | 75  |

|          | 4.3   | Design  | n of a 4-Element $K$ Band Analog Beamformer with a Pseudo-DA |     |

|          |       | Archit  | tecture                                                      | 80  |

|          |       | 4.3.1   | Design of Tunable Output Transmission Line                   | 80  |

|          |       | 4.3.2   | Design of Transconductance Gain Cells and Input Matching     |     |

|          |       |         | Circuit                                                      | 81  |

|          |       | 4.3.3   | Beamforming Simulation Results                               | 86  |

|          |       | 4.3.4   | Sensitivity to Process, Voltage, and Temperature (PVT) vari- |     |

|          |       |         | ations                                                       | 91  |

|          |       | 4.3.5   | Verifying Beamformer Stability                               | 93  |

|          |       | 4.3.6   | Verifying Beamformer Linearity                               | 93  |

|          | 4.4   | K-bar   | nd Analog Beamformer Fabrication and Measurement Results .   | 94  |

|          |       | 4.4.1   | Tape-out and Fabrication                                     | 94  |

|          |       | 4.4.2   | Measurements                                                 | 95  |

|          |       | 4.4.3   | Comparison to Other Work                                     | 99  |

|          |       | 4.4.4   | Discussion and Future Work                                   | 102 |

| <b>5</b> | Cor   | nclusio | ns and Future Work                                           | 104 |

|          | 5.1   | Summ    | nary of Contributions                                        | 104 |

|          | 5.2   | Futur   | e Work                                                       | 105 |

| Bi       | bliog | graphy  |                                                              | 107 |

# List of Tables

| 1.1 | Comparing Beamforming Methods                                             | 13  |

|-----|---------------------------------------------------------------------------|-----|

| 2.1 | Comparing Phase Shifting Methods                                          | 34  |

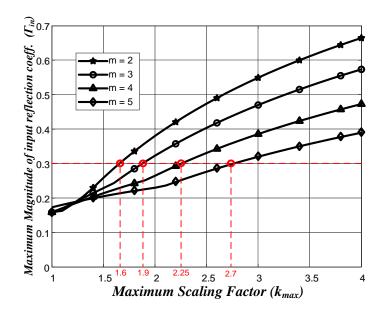

| 3.1 | Area estimation for $m$ and $k_{max}$ pairs extracted from Fig. 3.10      | 60  |

| 3.2 | Design table for matched cells in conventional Tunable Transmission       |     |

|     | Line (TTL) phase shifter in 65 nm cmos Technology                         | 62  |

| 3.3 | Attenuation factor for cells with different Characteristic Impedance in   |     |

|     | 65 nm cmos Technology                                                     | 62  |

| 3.4 | Extracted pairs of $m$ and $k_{max}$ in 65nm CMOS Technology for Return   |     |

|     | loss better than 10 dB and estimated FOM                                  | 63  |

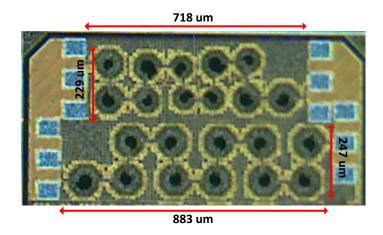

| 3.5 | Physical dimensions of the cell inductors and varactors in the fabricated |     |

|     | Tapered Tunable Transmission Line (Tapered TTL) phase shifter             | 64  |

| 3.6 | Input referred third intersection point (IIP3)                            | 69  |

| 3.7 | Comparison table with related research works                              | 70  |

| 4.1 | Beamformer's pattern statistics $(V_{ctrl} = 1.7V)$                       | 92  |

| 4.2 | Comparison table with related research works                              | 102 |

# List of Figures

| 1.1                                               | Phase array concept                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2                                                          |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| 1.2                                               | SNR improvement in a phased array system                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3                                                          |

| 1.3                                               | (a) Single transmitter and receiver. (b) Generalized N transmitter to                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                            |

|                                                   | one receiver (c) Linear phased array with N elements.                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4                                                          |

| 1.4                                               | Array Factor for a Linear Array when $D = \frac{\lambda}{2}$ and (a) $N = 2$ (b) $N = 4$                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                            |

|                                                   | (c) $N = 16$ (d) $N = 64$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6                                                          |

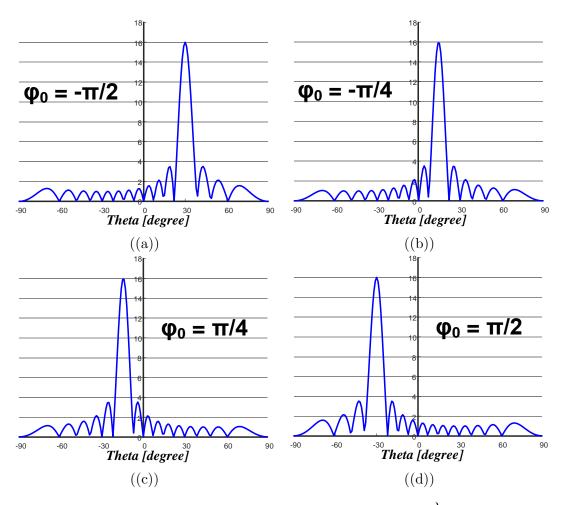

| 1.5                                               | Array Factor for a Phased Array when $N = 16$ , $D = \frac{\lambda}{2}$ , and (a)                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                            |

|                                                   | $\Phi_0 = -\frac{\pi}{2}$ (b) $\Phi_0 = -\frac{\pi}{4}$ (c) $\Phi_0 = \frac{\pi}{4}$ (d) $\Phi_0 = \frac{\pi}{2}$                                                                                                                                                                                                                                                                                                                                                                                               | 7                                                          |

| 1.6                                               | Block diagram of a Digital Beamformer (Receiving mode). $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9                                                          |

| 1.7                                               | Block diagram of an Analog (RF) Beamformer (Receiving mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10                                                         |

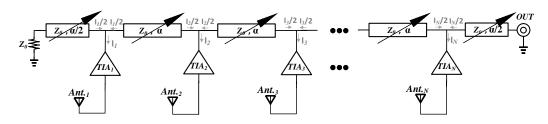

| 1.8                                               | (a) Analog beamformer with series-fed combining network, (b) Classi-                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                            |

|                                                   | cal Distributed Amplifier (DA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10                                                         |

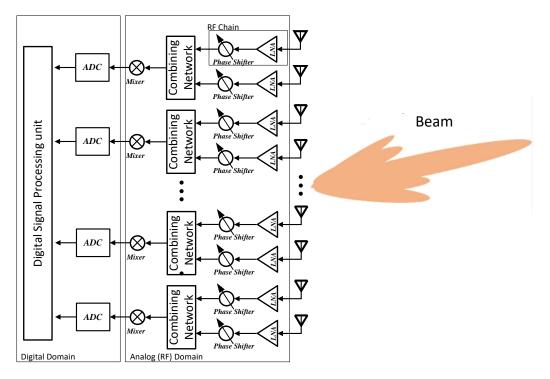

| 1.9                                               | Block diagram of an Analog (RF) Beamformer (Receiving mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12                                                         |

| 1.10                                              | Block diagram of a Hybrid Beamformer (Receiving mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12                                                         |

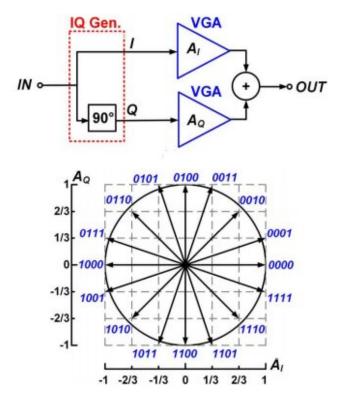

| 2.1                                               | The Block diagram of a typical Vector Modulator Based (VMB) phase                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                            |

|                                                   | shifter [16]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                            |

|                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17                                                         |

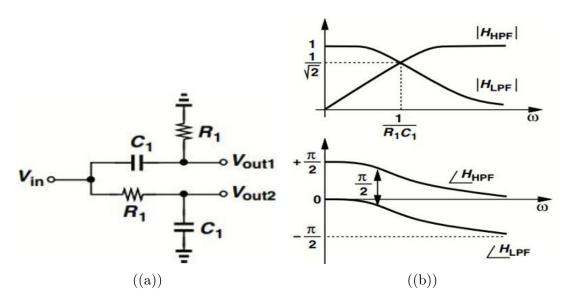

| 2.2                                               | (a) schematic and (b) phase and amplitude relation between two out-                                                                                                                                                                                                                                                                                                                                                                                                                                             | 17                                                         |

| 2.2                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17<br>18                                                   |

| <ul><li>2.2</li><li>2.3</li></ul>                 | (a) schematic and (b) phase and amplitude relation between two out-                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                            |

|                                                   | (a) schematic and (b) phase and amplitude relation between two outputs of an RC-CR network [17]                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                            |

|                                                   | <ul> <li>(a) schematic and (b) phase and amplitude relation between two outputs of an RC-CR network [17]</li> <li>(a) Schematic and (b) amplitude balance and (c) phase balance of a</li> </ul>                                                                                                                                                                                                                                                                                                                 | 18                                                         |

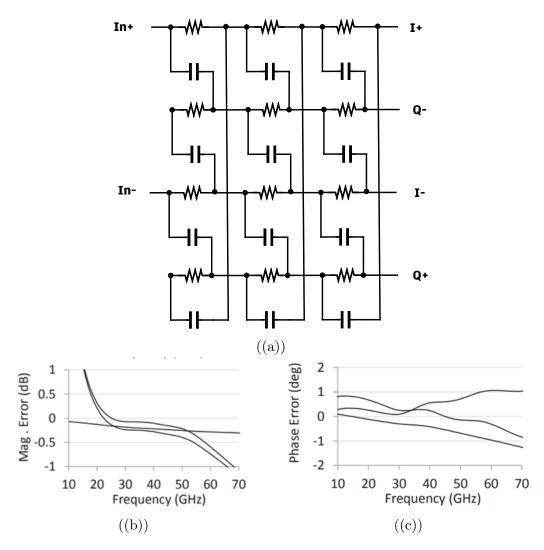

| 2.3                                               | <ul> <li>(a) schematic and (b) phase and amplitude relation between two outputs of an RC-CR network [17]</li> <li>(a) Schematic and (b) amplitude balance and (c) phase balance of a millimeter-wave PPF [18]</li> </ul>                                                                                                                                                                                                                                                                                        | 18                                                         |

| 2.3                                               | <ul> <li>(a) schematic and (b) phase and amplitude relation between two outputs of an RC-CR network [17]</li> <li>(a) Schematic and (b) amplitude balance and (c) phase balance of a millimeter-wave PPF [18]</li> <li>Generation of resonance-based second-order all-pass quadrature net-</li> </ul>                                                                                                                                                                                                           | 18<br>19                                                   |

| 2.3<br>2.4                                        | <ul> <li>(a) schematic and (b) phase and amplitude relation between two outputs of an RC-CR network [17]</li> <li>(a) Schematic and (b) amplitude balance and (c) phase balance of a millimeter-wave PPF [18]</li> <li>Generation of resonance-based second-order all-pass quadrature network (Single-ended configuration) [23]</li> </ul>                                                                                                                                                                      | 18<br>19                                                   |

| 2.3<br>2.4                                        | <ul> <li>(a) schematic and (b) phase and amplitude relation between two outputs of an RC-CR network [17]</li> <li>(a) Schematic and (b) amplitude balance and (c) phase balance of a millimeter-wave PPF [18]</li> <li>(b) Generation of resonance-based second-order all-pass quadrature network (Single-ended configuration) [23]</li> <li>(c) Effect of load capacitance on quadrature accuracy in a single-ended</li> </ul>                                                                                 | 18<br>19<br>21                                             |

| <ol> <li>2.3</li> <li>2.4</li> <li>2.5</li> </ol> | <ul> <li>(a) schematic and (b) phase and amplitude relation between two outputs of an RC-CR network [17]</li> <li>(a) Schematic and (b) amplitude balance and (c) phase balance of a millimeter-wave PPF [18]</li> <li>Generation of resonance-based second-order all-pass quadrature network (Single-ended configuration) [23]</li> <li>Effect of load capacitance on quadrature accuracy in a single-ended QAF [20]</li> </ul>                                                                                | 18<br>19<br>21                                             |

| <ol> <li>2.3</li> <li>2.4</li> <li>2.5</li> </ol> | <ul> <li>(a) schematic and (b) phase and amplitude relation between two outputs of an RC-CR network [17]</li> <li>(a) Schematic and (b) amplitude balance and (c) phase balance of a millimeter-wave PPF [18]</li> <li>Generation of resonance-based second-order all-pass quadrature network (Single-ended configuration) [23]</li> <li>Effect of load capacitance on quadrature accuracy in a single-ended QAF [20]</li> <li>(a) Differential formation of QAF, (b) Elimination of redundancy, and</li> </ul> | <ol> <li>18</li> <li>19</li> <li>21</li> <li>21</li> </ol> |

| 2.8  | An Analog differential adder/VGA implemented in CMOS [25]                                                                           | 25 |

|------|-------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.9  | Switched delay line phase shifter concept                                                                                           | 26 |

| 2.10 | Example of ATL cell including/excluding mechanism in an Switched                                                                    |    |

|      | Type Phase Shifter (STPS) $[28]$                                                                                                    | 27 |

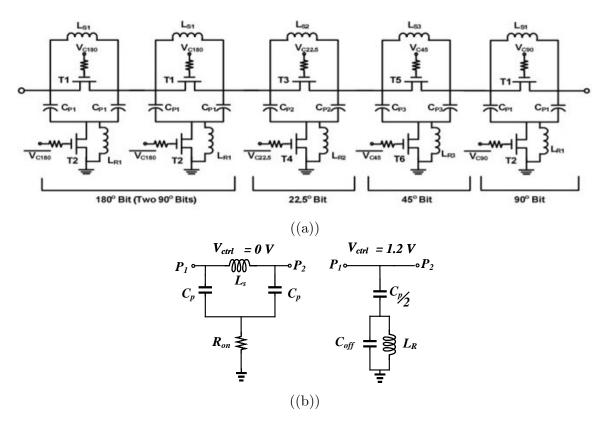

| 2.11 | (a) A 4-bit switched delay line 67 to 78 GHz phase shifter and (b) the                                                              |    |

|      | ATL cell including/excluding mechanism [30]                                                                                         | 28 |

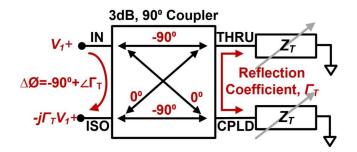

| 2.12 | Block diagram of a typical reflection-type phase shifter $[33]$                                                                     | 30 |

| 2.13 | Reflective Type Phase Shifter with Loss compensation $[31]$                                                                         | 31 |

| 2.14 | Operation of a switched transmission line phase shifter $[35]$                                                                      | 32 |

| 2.15 | Cancellation of non-delayed signal: (a) Active approach. (b) Passive                                                                |    |

|      | approach employing a Hybrid coupler. [35]                                                                                           | 32 |

| 2.16 | (a) The circuit model and (b) On-chip realization of C-Band Tunable                                                                 |    |

|      | Transmission Line (TTL) phase shifter. Chip size is $1.4mm \times 0.6mm$                                                            |    |

|      | $[36] \qquad \dots \qquad $ | 34 |

| 2.17 | Normalized array factor of a uniform phased array system with (a) 16                                                                |    |

|      | and (b) 1024 elements [37] $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                    | 36 |

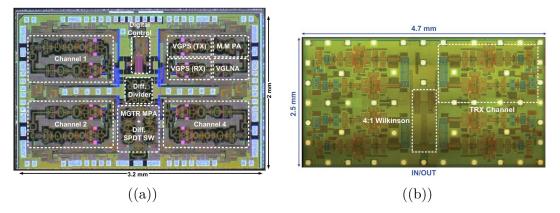

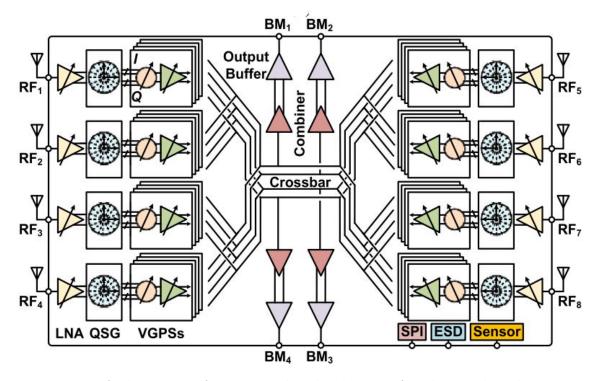

| 2.18 | (a) 28-GHz four-channel beamforming front-end IC [38] and (b) 28-                                                                   |    |

|      | GHz 2x2 TRX array [39] $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                 | 36 |

| 2.19 | Architecture of a Ka-Band eight-element, four-beam phased-array re-                                                                 |    |

|      | ceiver front end $[42]$                                                                                                             | 37 |

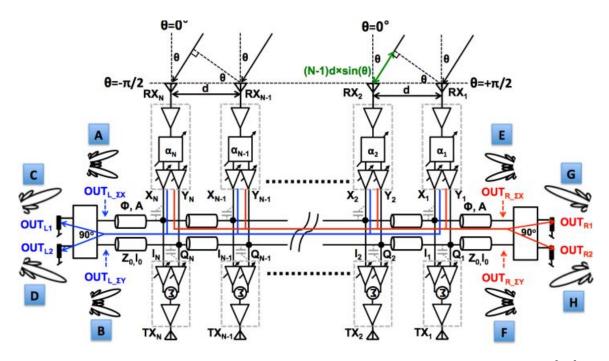

| 2.20 | Block diagrams of a 28-GHz series-fed distributed beamformer $[43]$ .                                                               | 38 |

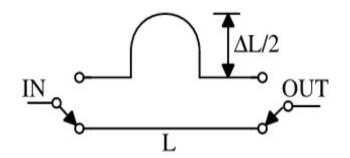

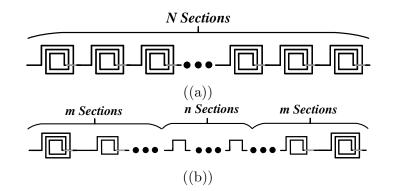

| 3.1  | The appearance of the inductors in the layout of (a) an $N$ -cell conven-                                                           |    |

|      | tional and (b) an N-cell proposed Tapered TTL phase shifter                                                                         | 40 |

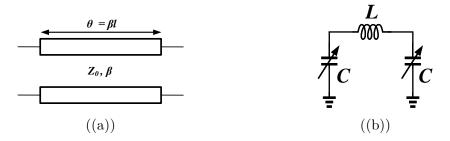

| 3.2  | (a) Transmission line with electrical length $\theta$ and (b) lumped-element                                                        |    |

|      | realization of transmission line                                                                                                    | 40 |

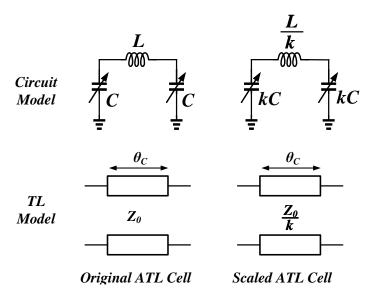

| 3.3  | Original and scaled $\pi$ -Artificial Transmission Lines (ATLs) and their                                                           |    |

|      | equivalent TL models.                                                                                                               | 42 |

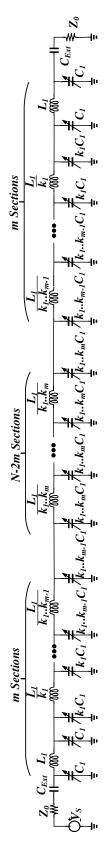

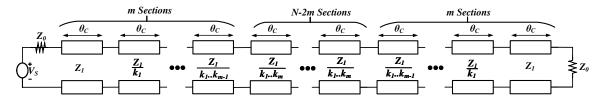

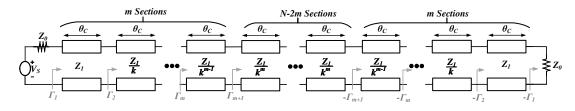

| 3.4  | Circuit model of an N cascaded $\pi$ -ATL cells having $2m$ tapered cells                                                           |    |

|      | with arbitrary scaling factors distribution                                                                                         | 46 |

| 3.5  | Transmission line model of an N cascaded $\pi$ -ATL cells having $2m$                                                               |    |

|      | tapered cells with arbitrary scaling factors distribution                                                                           | 47 |

| 3.6  | $N$ cascaded $\pi\text{-ATL}$ cells having $2m$ tapered cells with optimum scaling                                                  |    |

|      | factors distribution (partial reflection coefficients are shown) $\ldots$                                                           | 47 |

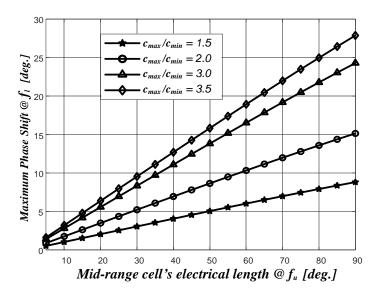

| 3.7  | The maximum phase shift at the lowest frequency $(\Delta \theta_{max@f_l})$ vs. $\theta_{0f_u}$                                     |    |

|      | in a conventional ATL cell for different values of $C_{max}/C_{min}$                                                                | 53 |

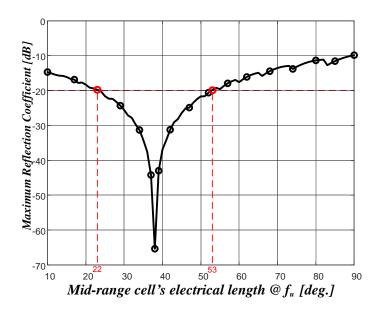

| 3.8  | The maximum reflection coefficient $(S_{11max})$ of an 180 degree phase                                                        |    |

|------|--------------------------------------------------------------------------------------------------------------------------------|----|

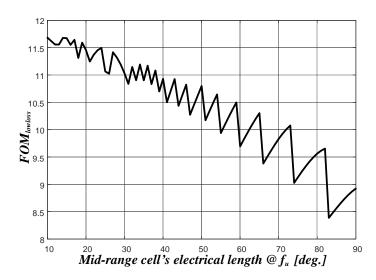

|      | shifter as function of $\theta_{0f_u}$ in a conventional low-loss TTL phase shifter.                                           | 55 |

| 3.9  | $FOM_{lowloss}$ of an 180 degree phase shifter as a function of $\theta_{0f_u}$ in a                                           |    |

|      | conventional lossless TTL phase shifter                                                                                        | 56 |

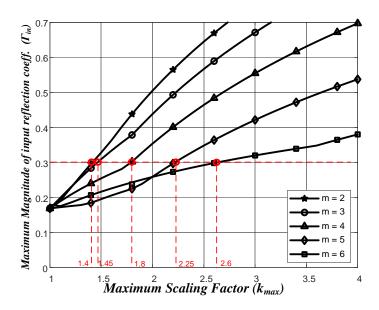

| 3.10 | Magnitude of input reflection coefficient (maximum magnitude of the                                                            |    |

|      | input reflection coefficient $( \Gamma_{in_{max}} ))$ versus $k_{max}$ for $m = 2, 3, 4, 5$ and                                |    |

|      | 6 where $\theta_{0f_u} = 53^o$ and $N = 13$ .                                                                                  | 59 |

| 3.11 | Magnitude of input reflection coefficient at $\theta_0 f_u$ versus $k_{max}$ for $m =$                                         |    |

|      | 2, 3, 4 and 5 for the 180 degree, Ku/K/Ka band, 11-cell Tapered TTL                                                            |    |

|      | phase shifter.                                                                                                                 | 63 |

| 3.12 | Implemented 11-cell Tapered TTL (Upper) and TTL (Lower) Phase                                                                  |    |

|      | Shifters in 65nm CMOS technology.                                                                                              | 65 |

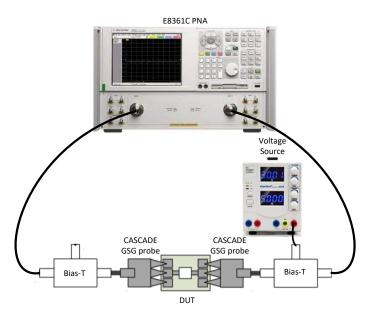

| 3.13 | Measurement setup.                                                                                                             | 66 |

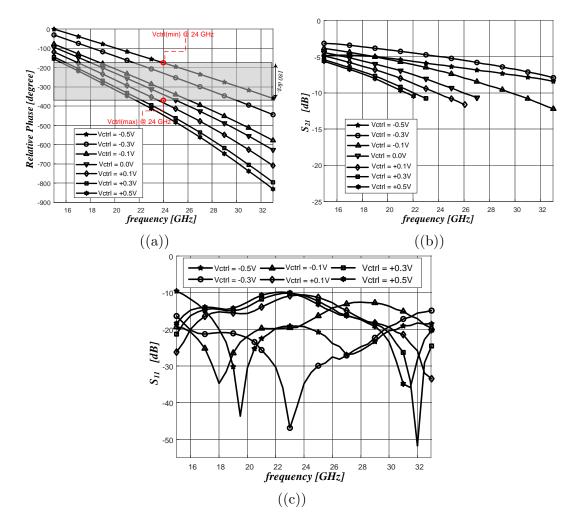

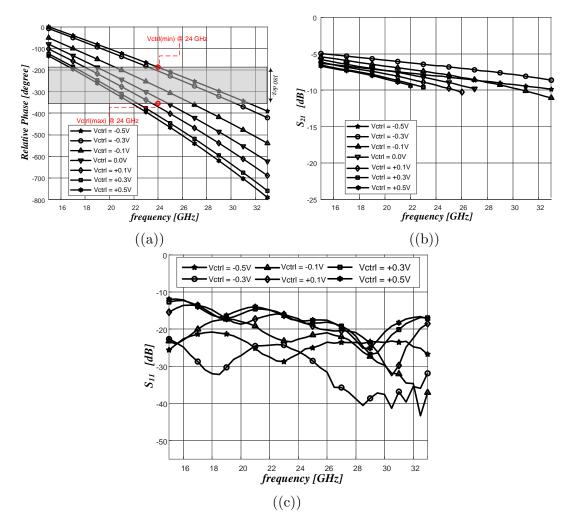

| 3.14 | Measured (a) Relative Phase, (b) $S_{21}$ and (c) $S_{11}$ of the 11-cell Tapered                                              |    |

|      | TTL phase shifter versus frequency for different control voltages                                                              | 67 |

| 3.15 | Measured (a) Relative Phase, (b) $S_{21}$ and (c) $S_{11}$ of the 11-cell TTL                                                  |    |

|      | phase shifter versus frequency for different control voltages                                                                  | 68 |

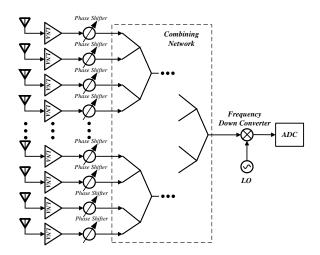

| 4.1  | A receiver with an analog RF beamformer                                                                                        | 72 |

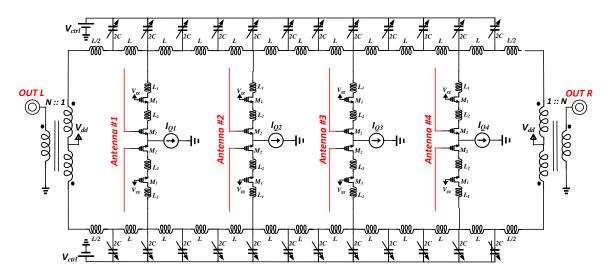

| 4.2  | A N-element linear antenna array                                                                                               | 72 |

| 4.3  | (a) Conventional distributed amplifier, and (b) proposed RF analog                                                             |    |

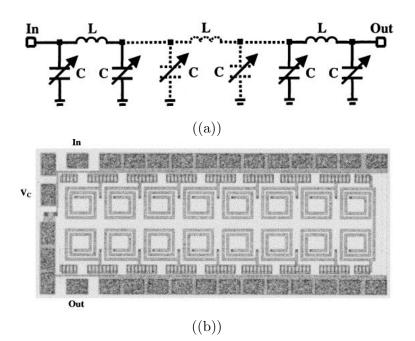

|      | beamformer architecture                                                                                                        | 74 |

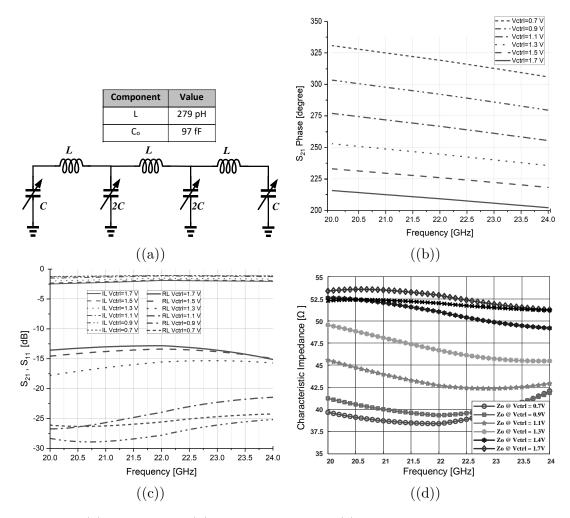

| 4.4  | (a) Schematic, (b) electrical length, (c) Insertion and Return loss, and                                                       |    |

|      | (d) characteristic impedance of simulated Tunable Artificial Transmis-                                                         |    |

|      | sion Line (Tunable-ATL).                                                                                                       | 82 |

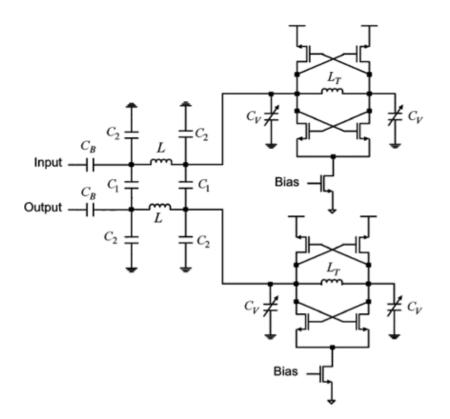

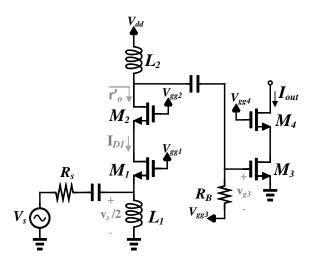

| 4.5  | The designed transconductance gain cell for the proposed $K$ band                                                              |    |

|      | beamformer                                                                                                                     | 83 |

| 4.6  | (a) The implemented transconductance gain cell of the $K$ -band beam-                                                          |    |

|      | former and (b) its simulated gain and return loss                                                                              | 85 |

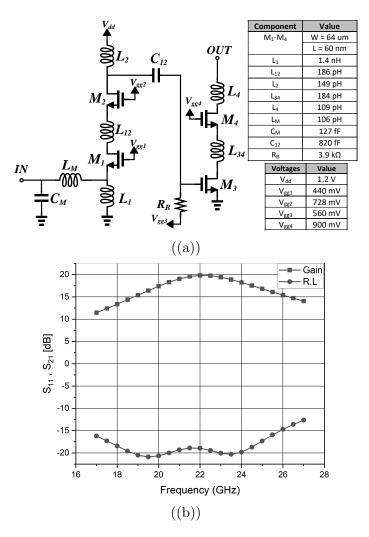

| 4.7  | Relative phase responses of gain cells at (a) $V_{ctrl} = 1.7$ V and (b) $V_{ctrl}$                                            |    |

|      | $= 0.7 \text{ V} \dots $ | 86 |

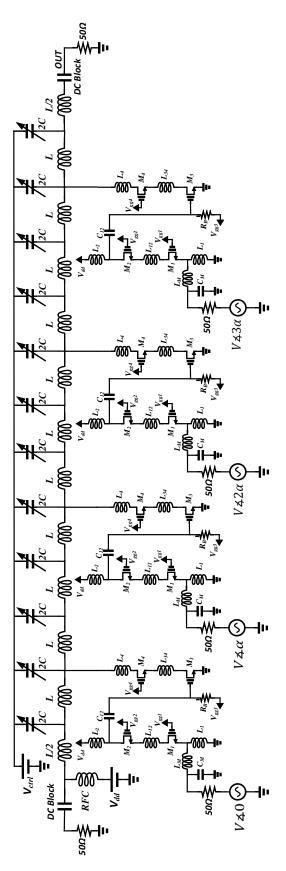

| 4.8  | Simulation setup for the designed $K$ -band beamformer $\ldots \ldots \ldots$                                                  | 88 |

| 4.9  | Simulation results of the array pattern for (a) 21 GHz, (b) 22 GHz,                                                            |    |

|      | and (c) 23 GHz                                                                                                                 | 89 |

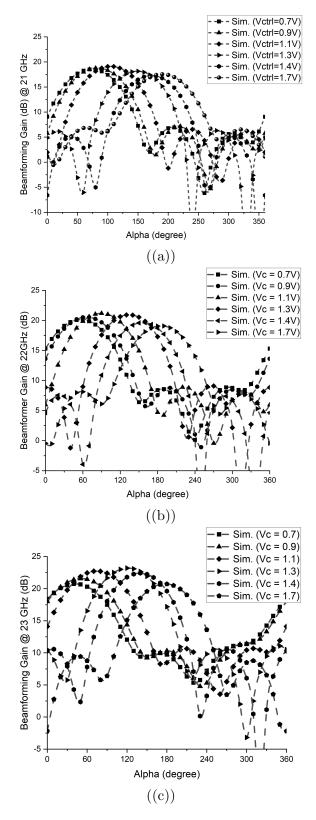

| 4.10 | Simulation results of the array pattern when the mutual coupling be-                                                           |    |

|      | tween ATL cells is taken to account for (a) 21 GHz, (b) 22 GHz, and                                                            |    |

|      | (c) 23 GHz                                                                                                                     | 90 |

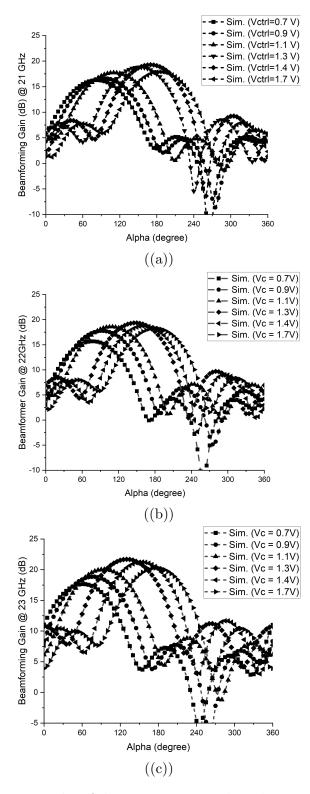

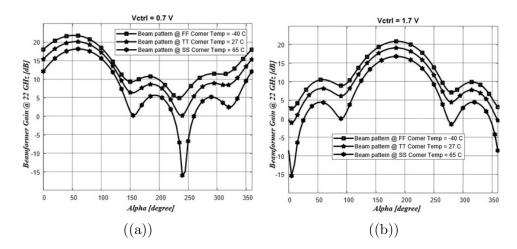

| 4.11 | Variation of beamformer's gain for nominal and the process corners                                    |     |

|------|-------------------------------------------------------------------------------------------------------|-----|

|      | when (a) $V_{ctrl} = 0.7V$ and (b) $V_{ctrl} = 1.7V$                                                  | 91  |

| 4.12 | Monte Carlo simulation results when $Vctrl = 1.7 V$ at 22 GHz for (a)                                 |     |

|      | pattern's peak ( $\phi = 180$ ) and (b) first sidelobe ( $\phi = 60$ )                                | 92  |

| 4.13 | Mu and Mu-Prime vs. frequency when $Vctrl = 1.2V$ for the (a) First,                                  |     |

|      | (b) Second, (b) Third, and (c) Fourth Amplifier.                                                      | 94  |

| 4.14 | Implemented 4-element K-band analog beamformer in 65-nm CMOS                                          |     |

|      | technology. $\ldots$ | 95  |

| 4.15 | (a) Block diagram of characterization setup for measuring beamformer's                                |     |

|      | S-parameters and (b) Printed Circuit Board (PCB) of tested beam-                                      |     |

|      | former                                                                                                | 97  |

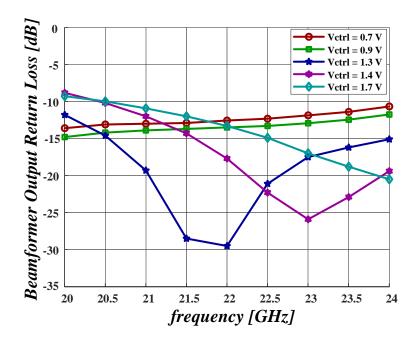

| 4.16 | Measured output return loss $( S_{55} )$ of beamformer at different biasing                           |     |

|      | ${\rm conditions.}  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $         | 98  |

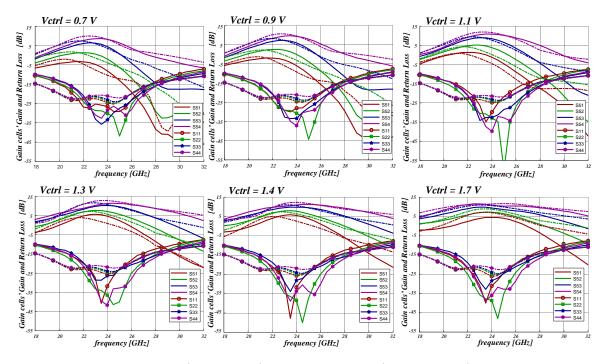

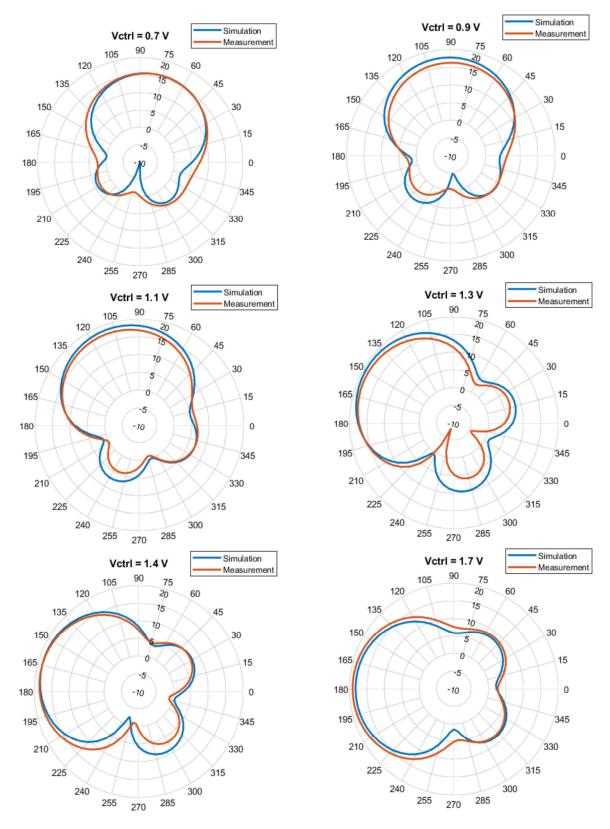

| 4.17 | Measured (solid lines) and simulated (dotted lines) S parameters of                                   |     |

|      | fabricated beamformer.                                                                                | 99  |

| 4.18 | Simulated beamforming pattern based on measured and simulated S                                       |     |

|      | parameters of fabricated beamformer at 22 GHz                                                         | 100 |

| 5.1  | Proposed four-element phased array system                                                             | 106 |

|      |                                                                                                       |     |

### Abbreviations

- $\Delta \theta_{max@f_l}$  maximum achievable phase shift at the lowest frequency.

- $\Gamma_{in}$  Input Reflection Coefficient.

- $k_i$  Scaling Coefficient.

- $k_{max}$  Maximum Scaling Coefficient.

- $|\Gamma_{in,max}|$  maximum absolute value of the Input Reflection Coefficient.

- $|\Gamma_{in_{max}}|$  maximum magnitude of the input reflection coefficient.

- ADC Analog-to-Digital Converter.

- ATL Artificial Transmission Line.

- CG Common Gate.

- **CMOS** Complementary Metal–Oxide–Semiconductor.

- **DA** Distributed Amplifier.

- **DAC** Digital-to-Analog Converter.

- **DSP** Digital Signal Processor.

- **EIRP** Equivalent Isotropic Radiated Power.

- FOM Figure of Merit.

- **GSG** Ground-Signal-Ground.

- **IDC** Insulation Displacement Connector.

- **IL** Insertion Loss.

LNA Low-Noise Amplifier.

- LO Local Oscillator.

- LWA leaky wave antenna.

PCB Printed Circuit Board.

**Pseudo-DA** Pseudo-Distributed Amplifier.

**PVT** Process, Voltage, and Temperature.

RFC Radio Frequency Choke.

**RL** Return Loss.

**RTPS** Reflection Type Phase Shifter.

**SNR** Signal-to-Noise Ratio.

**SOLT** Short/Open/Load/Through.

**STPS** Switched Type Phase Shifter.

Tapered TTL Tapered Tunable Transmission Line.

**TTL** Tunable Transmission Line.

**TTLPS** Tunable Transmission Line Phase Shifter.

Tunable-ATL Tunable Artificial Transmission Line.

VGA Variable Gain Amplifier.

VMB Vector Modulator Based.

# Chapter 1 Introduction

#### 1.1 Motivation

Since the demand for higher data rate services continues to increase, the available bandwidth in traditional low-GHz RF wireless communications becomes increasingly congested. Developing new wireless technologies that use higher frequency bands, such as millimeter-wave and sub-THz frequencies, is considered as one of the most promising solutions to address the bandwidth shortage [1-3]. However, millimetrewave signals experience increased free space and atmospheric losses when compared to lower-frequency signals. Moreover, the propagation of high-frequency radio waves is often hindered by higher absorption rates when encountering obstacles such as buildings, trees, and raindrops. Consequently, these factors collectively contribute to a reduction in the overall range of communication [4]. To overcome these challenges, directional and phased array antennas are typically used to focus a transmitted or received signal in a particular direction or towards a specific receiver to improve the Signal-to-Noise Ratio (SNR) and increase the system transmission range [5]. Utilizing either of these methods increases the capability for directional wireless communication, as opposed to the traditional omnidirectional communication that is common in the lower RF frequency range. While the omnidirectional approach offers alignmentfree communication, directional communication presents numerous advantages. It is more energy-efficient due to targeted delivery, facilitates multiple simultaneous communications at the same frequency, reduces susceptibility to multipath fading, and avoids interference with other communication channels [6].

Phased array systems are essentially arrays of multiple antenna elements. They

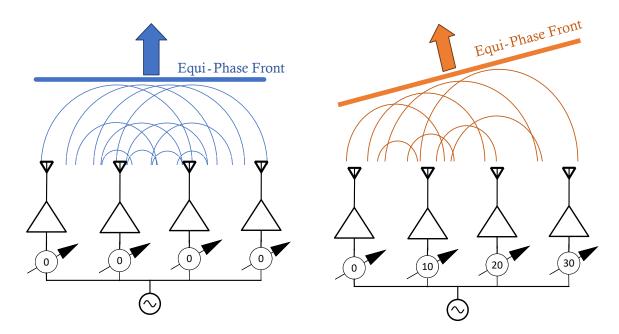

Figure 1.1: Phase array concept.

use a variety of techniques to control the amplitudes and phase shifts between the element signals in the array to create a constructive interference pattern that results in a directional beam. Moreover, these techniques, which are generally called beamforming, provide the ability to steer the beam in a specific direction without physically moving the antenna by independently adjusting the phase and amplitude of each array element's signal [7]. Fig. 1.1 provides an intuitive representation, demonstrating how the manipulation of the phase for each antenna element within an array enables the dynamic adjustment of the equi-phase front of the radiated signal. This visual insight underscores the capability of phased arrays to alter the direction of signal radiation by controlling individual antenna phases. It is worth noting that phased arrays find utility in both transmitters and receivers, showcasing their versatility in diverse applications across communication systems.

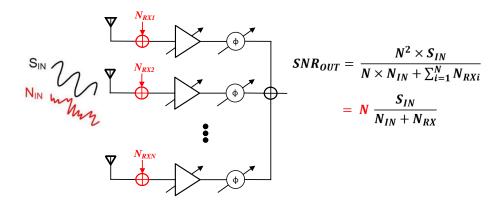

In a phased array receiver, in addition to the mentioned benefits, for fixed antenna sizes, the SNR consistently improves within an array due to the presence of uncorrelated noise in parallel independent receivers. It is crucial to note that the advantage of noise reduction is contingent upon the independence of the noise sources. Therefore, the extent of the SNR improvement is influenced by the specific architecture of the phased array (beamforming). As illustrated in Fig. 1.2, the array manipulates

Figure 1.2: SNR improvement in a phased array system.

the phase of input signals to achieve constructive addition at the output port. Importantly, since the input noise in each branch of the array  $(N_{RX_i})$  is statistically independent of others, constructive addition does not apply to these noise sources. Consequently, the SNR undergoes improvement by a factor of n, where n represents the number of elements in the array.

Due to the faster response time, greater flexibility, and smaller size of the phased array antennas in comparison to mechanical directional counterparts [8], they have become increasingly popular in a wide range of growing wireless applications. For example, phased array systems are widely used in 5G/6G, satellite communication wireless transceivers, automotive radars, and medical imaging systems [9]. Specifically, as there is a widespread demand for using high-rate millimeter wireless communication in consumer electronic devices, such as smartphones and tablets, it is desirable to further reduce the power consumption and size of the beamformers to arrive at an energy-efficient, low-cost phased array solution.

This study is focused on proposing new circuit ideas to reduce the area and power consumption of integrated beamformers. In this chapter, a brief description of beamforming and the possible realization of the beamformers in analog, digital, and hybrid domains is provided. The details of the RF analog beamforming, a widely used method for on-chip realization, are further elaborated and its advantages and disadvantages are discussed. The possible solutions and previous work on improving the power consumption and reducing the chip area of the RF analog beamformer are also investigated.

#### **1.2 Beamforming Fundamentals**

Beamforming, or Spatial Filtering, is a technique that focuses or directs a transmitted or received signal in a specific direction [7]. This technique is essential in many wireless communication and radar systems. In modern 5G/6G wireless communication systems, increasing demand for higher data rates requires the utilization of frequency bands in the millimeter wave region and above. Due to the high path and penetration losses at millimeter wavelengths, beamforming is needed to overcome path losses and establish robust communication links by concentrating the radiation energy in the desired direction [10]. In radar systems, beamforming is needed to track high-speed targets with high angular resolution [11]. Phased array antenna systems are often used for directional transmission and reception of directional EM beams by progressively setting the phase of signals for elements of the antenna array.

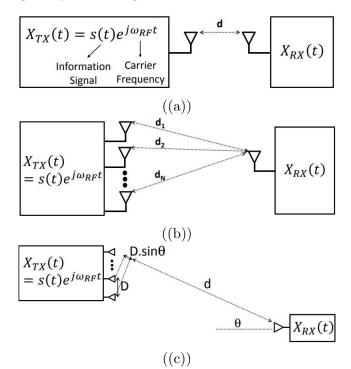

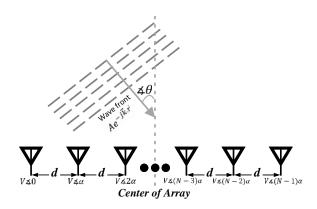

Figure 1.3: (a) Single transmitter and receiver. (b) Generalized N transmitter to one receiver (c) Linear phased array with N elements.

In the context of a wireless transmitter system, the modulated signal at the output (as illustrated in Fig. 1.3(a)) is generally represented as

$$X_{TX}(t) = S(t)e^{j\omega_{RF}t},$$

(1.1)

where S(t) denotes the information signal and  $e^{j\omega_{RF}t}$  represents the carrier frequency. Upon transmission through an omnidirectional antenna, the received signal at a receiver positioned at a distance d is given by

$$X_{RX}(t) = \frac{k}{d^2} X_{TX}(t - \frac{d}{c})$$

$$= \frac{k}{d^2} S(t - \frac{d}{c}) e^{j\omega_{RF}(t - \frac{d}{c})}$$

$$= \frac{k}{d^2} e^{-j2\pi} \frac{d}{\lambda} S(t - \frac{d}{c}) e^{j\omega_{RF}t},$$

(1.2)

where k is a constant, c is the wave propagation velocity, and  $\lambda$  denotes the wavelength defined as

$$\lambda = \frac{c}{\omega_{RF}}.\tag{1.3}$$

When considering N transmitters emitting the same modulated signal  $X_{TX}$ , the received signal can be calculated using

$$X_{RX}(t) = \sum_{i=1}^{N} \frac{k}{d_i^2} e^{-j2\pi} \frac{d_i}{\lambda} S(t - \frac{d_i}{c}) e^{j\omega_{RF}t}.$$

(1.4)

Assuming negligible variations in  $d_i$  in the  $d_i/c$  term, and with the receiver located far from the transmitter, this expression can be approximated as

$$X_{RX}(t) \approx \frac{k}{d^2} \sum_{i=1}^{N} e^{-j2\pi} \frac{d_i}{\lambda} S(t - \frac{d}{c}) e^{j\omega_{RF}t}.$$

(1.5)

In a linear array system, as depicted in Fig. 1.3(c), the antenna elements are equally spaced at a distance D between each consecutive elements. In this case,  $d_i$  can be replaced by  $d_i = d + (i - 1)Dsin(\theta)$ . As a result, (1.5) is changed to

$$X_{RX}(t) \approx \frac{k}{d^2} e^{-j2\pi} \frac{d}{\lambda} \sum_{i=1}^{N} e^{-j2\pi(i-1)} \frac{D}{\lambda} sin(\theta)} S(t-\frac{d}{c}) e^{j\omega_{RF}t}.$$

(1.6)

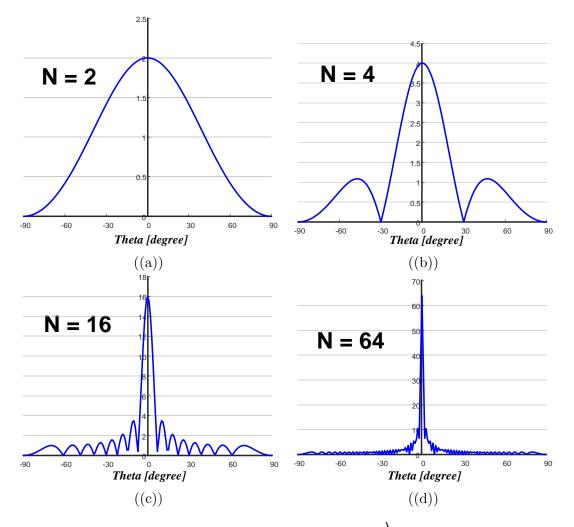

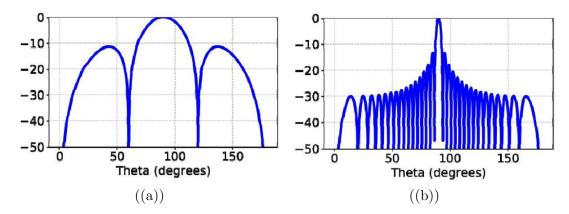

The part highlighted in red is known as the Array Factor. This factor plays a significant role in influencing the pattern and directs the pattern toward the desired point. Increasing the number of antenna elements results in a more pronounced effect on the pattern, notably achieving a narrower beamwidth. Fig. 1.4(a) to Fig. 1.4(d) visually illustrate the array factor for a linear array configuration with antenna elements spaced at  $\lambda/2$ , showcasing the impact of varying the number of elements (2, 4, 16, and 64) on the array factor.

Figure 1.4: Array Factor for a Linear Array when  $D = \frac{\lambda}{2}$  and (a) N = 2 (b) N = 4 (c) N = 16 (d) N = 64

As previously noted, the primary distinction between a phased array system and an antenna array lies in the independent manipulation of phase and amplitude in each channel within the former (refer to Fig. 1.1). The ability to control the phase of signals in individual antenna elements facilitates beam steering. Given that the phase shifter in the *i*-th element introduces an additional phase shift of  $\phi_i = (i - 1)\phi_0$ , the array factor in (1.6) can be reformulated as

$$AF = \sum_{i=1}^{N} e^{-j2\pi(i-1)(\frac{D}{\lambda}\sin(\theta) + \frac{\phi_0}{2\pi})}.$$

(1.7)

By varying the value of  $\phi_0$ , it becomes possible to alter the direction in which the phased array is oriented. Figs. 1.5(a) to 1.5(d), visually represent the changes in the main beam direction of a phased array consisting of 16 antenna elements, where the spacing between the antennas is  $\lambda/2$ . These figures provide a depiction of how adjusting the parameter  $\phi_0$  influences the directional characteristics of the main beam in the phased array configuration.

Figure 1.5: Array Factor for a Phased Array when N = 16,  $D = \frac{\lambda}{2}$ , and (a)  $\Phi_0 = -\frac{\pi}{2}$ (b)  $\Phi_0 = -\frac{\pi}{4}$  (c)  $\Phi_0 = \frac{\pi}{4}$  (d)  $\Phi_0 = \frac{\pi}{2}$ .

#### **1.3 Beamforming Techniques**

Beamforming can be performed in any of the digital, analog, or hybrid digital-analog domains. The choice of domain depends on the specific requirements and constraints of the application. Digital beamforming is favored in situations demanding precise control, adaptability, and the ability to implement sophisticated algorithms [12]. Analog beamforming, on the other hand, is preferred in scenarios where simplicity, low power consumption, and real-time processing are essential. Hybrid digital-analog beamforming offers a middle ground, allowing for a tailored approach to meet the specific needs of diverse applications, making beamforming a versatile and powerful technology across a spectrum of domains. The block diagrams and a brief description of each method will be further discussed in this section.

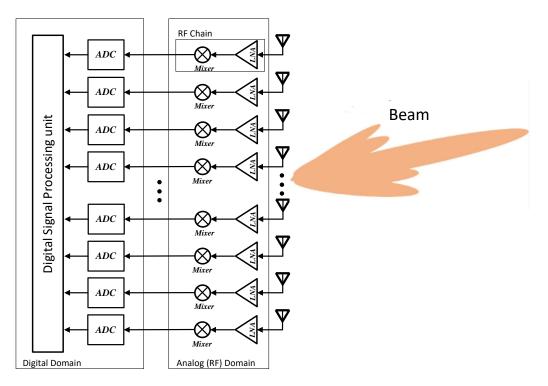

#### 1.3.1 Digital Beamforming

In a digital beamformer, as shown in Fig. 1.6, the received signals from each antenna are digitized and processed digitally. Therefore, the required number of high-speed Analog-to-Digital Converters (ADCs) and RF chains, including Frequency Converter (Mixer) and Low-Noise Amplifier (LNA), is equal to the number of array's elements demanding high power consumption to perform beamforming. Requiring a synchronized Local Oscillator (LO) distribution for frequency conversion in each branch adds to their implementation complexity.

The digital beamformer employs digital signal processing (DSP) to manipulate the signals in the digital domain. This enables real-time adjustments and precise control over the beam, allowing for enhanced performance in various applications. Consequently, this type of beamformer offers higher angular resolution, lower side lobe magnitudes, increased radiated power, and a simpler calibration process [9]. As in digital beamformers, each antenna element requires a dedicated high-speed mixedsignal data converter and a high-performance RF frequency converter, the high power consumption and the cost associated with the implementation of such a complex system prevent purely digital front ends from being utilized in many applications with power/cost restrictions. As another limitation of this technique, it should be noted that using digital signal processing in digital beamformers introduces some

Figure 1.6: Block diagram of a Digital Beamformer (Receiving mode).

delay, which can be a critical factor in applications where real-time responsiveness is crucial.

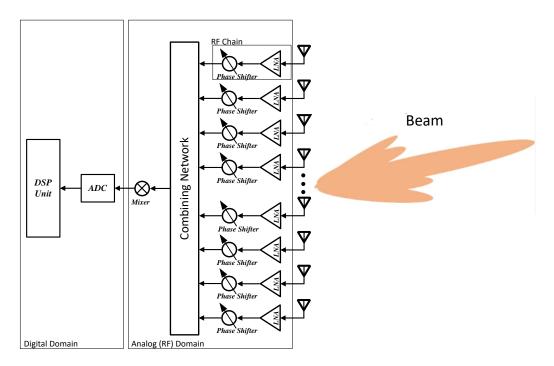

#### 1.3.2 Analog Beamforming

The analog beamformers perform the task using analog building blocks, such as phase shifters and variable gain amplifiers, by combining the phase-shifted transmitted/received signals in the analog domain (see Fig. 1.7). Since ADC/Digital-to-Analog Converters (DACs) or Digital Signal Processors (DSPs) are not required in the beamforming process, analog beamformers consume significantly less power and can be constructed at lower cost in a smaller form factor in comparison to their digital counterparts [5].

Moreover, as only one frequency mixer is required in an analog beamformer, eliminating the LO distribution circuitry further simplifies the scheme. Generally, analog beamforming systems are often simpler in design and implementation compared to digital systems, making them more straightforward to configure and maintain. In addition, they operate in real-time without the latency introduced by digital signal

Figure 1.7: Block diagram of an Analog (RF) Beamformer (Receiving mode).

processing, making it suitable for applications where immediate response is critical. However, this type of beamformer lacks the adaptability of digital systems. Furthermore, as adjustments to the beam characteristics are performed in the analog domain, this method has less accuracy and provides lower angle resolution.

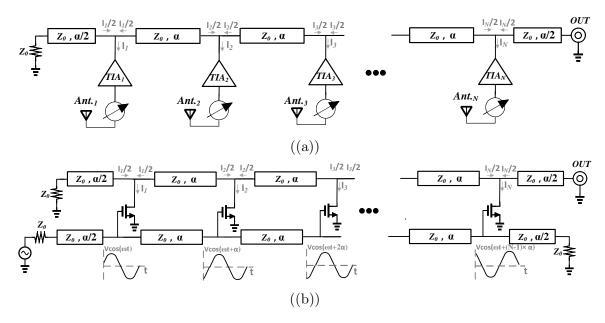

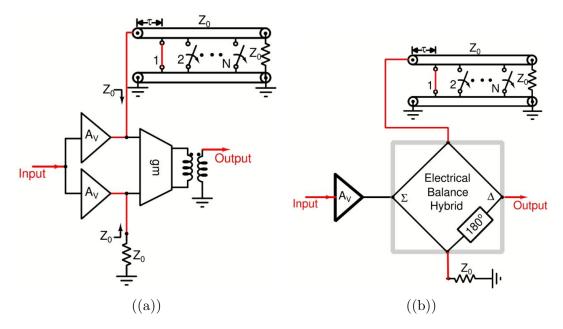

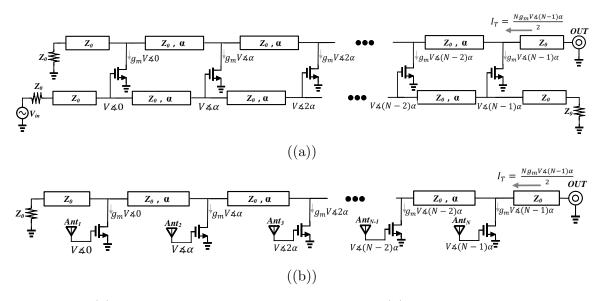

Figure 1.8: (a) Analog beamformer with series-fed combining network, (b) Classical Distributed Amplifier (DA)

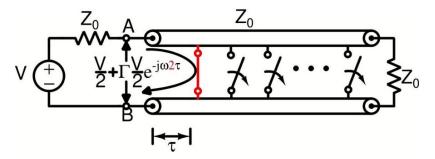

The methodology illustrated in Fig. 1.7 is commonly referred to as a parallel-fed combining network. However, an alternative approach, known as series-fed combining, is depicted in Fig. 1.8(a). In this configuration, if the phase difference between the output currents of consecutive Trans Impedance Amplifiers (TIAs) matches the electrical length of the transmission lines connecting them, then half of each branch's current is constructively summed at the output port. Nevertheless, the other halves are wasted in the terminated port.

The series-fed combining network in an analog beamformer functions similarly to a conventional Distributed Amplifier (DA), as shown in Fig. 1.8(b). In a DA, the input and output transmission lines are designed to absorb the input and output parasitic capacitance of TIAs, enabling a wide operational bandwidth [13]. Consequently, in a DA, the sacrifice of half of the currents in the terminated port is accepted as the cost for achieving ultra-wideband performance.

However, in a phased array with a series-fed combiner, the absence of an input transmission line can lead to a significant restriction in the operational bandwidth due to the parasitic input capacitance of the TIAs. This limitation underscores the importance of considering the specific design context and trade-offs when choosing between the parallel-fed and series-fed combining networks for optimal performance in specific practical applications.

Despite its apparent inefficiency, the series-fed beamforming method has distinct advantages that render it a viable consideration in certain scenarios. First, it has been demonstrated that series-fed beamformers can generate multiple simultaneous beams. This capability is noteworthy as it enhances the area efficiency of the beamformer [14] Second, in cases where the electrical length of the transmission lines within the series combining network is tunable, as depicted in Fig. 1.9, it becomes possible to eliminate the need for a phase shifter in each branch. This specific implementation contributes to making the beamformer more area-efficient, a topic that will be explored in greater detail in Chapter 4.

#### 1.3.3 Hybrid Analog/Digital Beamforming

Hybrid Analog/Digital beamforming is a cutting-edge signal processing approach that amalgamates the advantages of both analog and digital beamforming techniques. This

Figure 1.9: Block diagram of an Analog (RF) Beamformer (Receiving mode).

Figure 1.10: Block diagram of a Hybrid Beamformer (Receiving mode).

technique has gained prominence in modern communication and radar systems for its ability to strike a balance between the efficiency of analog beamforming and the adaptability of digital beamforming [9]. Hybrid beamformers perform beamforming for a subset of phased array elements in the analog domain while processing the transmitted/received signals of each subset in the digital domain (See Fig. 1.10). In fact, each subset in a hybrid beamformer acts as an analog (RF) beamformer but with a smaller number of antenna elements. This means that for the digital beamformer part, a simpler LO distribution network is required and the number of required ADCs (DACs in transmitting mode) is significantly reduced. Consequently, by reducing the number of required power-hungry elements, hybrid beamforming provides a compromise solution between analog and digital beamforming [15]. Hybrid

| Parameters           | RF beamforming            | Hybrid beamforming                                  | Digital beamforming                                |

|----------------------|---------------------------|-----------------------------------------------------|----------------------------------------------------|

| Main Required Blocks | Attenuator/Phase Shifter* | ADC/DAC**+ Attenuator/Phase Shifter** + Simple LODN | ADC/DAC $^{\ast}$ + Complex LODN $^{\ast\ast\ast}$ |

| Flexibility          | Low                       | Moderate/High                                       | High                                               |

| Complexity           | Low                       | Moderate                                            | High                                               |

| Power Consumption    | Low                       | Moderate                                            | High                                               |

| Cost                 | Low                       | Moderate/Low                                        | High                                               |

| Table 1.1:  | Comparing  | Beamforming | Methods     |

|-------------|------------|-------------|-------------|

| 100010 1011 | 0 omponing | Document    | 11100110000 |

\* per antenna element

\*\* fewer than the number of the antenna elements

\*\*\* Local Oscillator Distribution Network (LODN)

beamformers possess several advantages over the other methods. First, the digital processing component allows for fine adjustments, leading to enhanced signal quality, reduced interference, and improved overall system performance. In addition, they exhibit lower latency compared to fully digital systems, making them suitable for applications where real-time responsiveness is essential. Finally, the hybrid nature of the architecture provides flexibility in design, allowing for customization based on specific application requirements and constraints.

#### **1.3.4** Comparison of Beamforming Methods

Table 1.1 presents a comparative analysis of three beamforming methods. The contents of the table suggest that the selection of the appropriate method is highly contingent upon the specific requirements of the desired application. In cellular network applications, at the base station side, usually high-performance equipment is required, and simultaneously high power consumption and large-size devices can be tolerated. Therefore, wherever phased array systems are required, digital beamformers would likely be the proper choice. On the other side, in the end-user equipment of the cellular networks, which are usually implemented on-chip, reducing the power consumption and the size of the handheld devices are crucial. Consequently, in such applications, the phased array system must use analog or hybrid beamformers to trade off some performance to get more area and energy-efficient design. Given these considerations and acknowledging the crucial significance of analog beamformers in the modern millimeter-wave transceivers, the subsequent chapter is devoted to a comprehensive examination of the architectures, building blocks, and challenges inherent in this category of beamforming technique.

#### 1.4 Objectives

The main objective of this study is to develop energy-efficient and compact beamformers to design phased array systems that can be implemented in handheld devices or used in applications with strict limitations on size and power consumption. To address this goal, two main subjects are investigated in this research. Since phase shifters are the key component of analog (RF) beamformers, the design of an area-efficient phase shifter is determined as the first objective of this study. It is well-known that TTL phase shifters have useful capabilities such as having a wide operational frequency band, consuming no power, and providing continuous phase shift. However, at the same time, they are not very popular in on-chip design because of their large size and their excess insertion loss. Accordingly, proposing an area-efficient TTL phase shifters, to make them more appropriate for on-chip realization, is an interesting research subject. Therefore, chapter 3 of this study is dedicated to the design of a new Tapered TTL phase shifter which reduces the consuming chip area and improves the insertion loss performance. To verify the efficacy of the proposed phase shifter design, a wideband (Ku/K/Ka band) Tapered TTL phase shifter is designed, fabricated, and tested with its measurement results presented in this chapter.

The other objective of this research is to propose a new distributed beamformer that combines all functions of an analog (RF) beamformer in a single circuit thereby reducing the overall power consumption, occupied chip area, and fabrication costs. In Chapter 4, the design process for optimizing the beamformer gain, noise performance, and beam steering capability of the proposed design is presented and supported by mathematical analysis. Moreover, to demonstrate the effectiveness of the proposed beamforming approach, the fabrication process and measurement results of a fourelement K-band beamformer of this type are discussed in this chapter

### Chapter 2

# Analog (RF) Beamformers Literature Review

#### 2.1 Introduction

Analog (RF) beamforming is the simplest beamforming architecture. This approach forms the foundation of beamforming techniques, leveraging RF phase shifters to dynamically control the direction and characteristics of transmitted or received electromagnetic signals. As shown in Fig. 1.7, this type of beamformer relies on a single ADC (or DAC in transmitting mode). This gives this architecture low complexity and low power consumption, which makes it particularly suitable for scenarios where resource efficiency is critical.

The key to the success of this architecture lies in the precision and resolution of RF phase shifters. These components play a pivotal role in dynamically adjusting the phase of the signals, allowing for the steering of beams in specific directions. As the resolution of phase shifters increases, so does the beamforming performance, enabling finer control and optimization of the transmitted or received beams.

It should be noted using only analog (RF) or hybrid beamformers may not adequately address the increasing demand for newer wireless equipment with longer battery life and smaller form factors. Consequently, extensive research and development efforts are currently being undertaken to further reduce the cost and power consumption of these beamformers while maintaining acceptable performance [15]. Many studies have been conducted to find new approaches to design and implement more energy-efficient and less area-consuming phase shifters as the key building blocks of analog (RF) beamformers. Nonetheless, several other researchers focused on proposing innovative and more integrated designs and schemes for the entire beamformer rather than using the conventional architecture shown in Fig. 1.7. In this chapter, a comprehensive review of both kinds of studies is performed.

### 2.2 Recent Advances in Implementing RF Phase Shifters

In analog or hybrid beamformers, the phase shifters are often required to produce the desired phase shift range and resolution with low return and insertion losses while being implemented at the lowest possible cost and with the minimum possible power consumption as the number of required phase shifters scales linearly with the number of antenna elements in a phased-array antenna system. The phase shifters can be constructed using several different techniques including vector modulation circuits, switched delay lines, tunable reflective loads, and loaded transmission lines, where the phase shifts are created using passive or active circuit components or both.

#### 2.2.1 Vector Modulator Based (VMB) Phase Shifters

The vector modulation method creates a phase-shifted signal by summing two orthogonal current vectors (I and Q) with different weights. The typical block diagram of a VMB phase shifter is shown in Fig. 2.1. As can be seen, a VMB phase shifter consists of three main parts: a 90-degree hybrid coupler, a Variable Gain Amplifier (VGA) in the I and Q branches, and an Analog Adder. Given that VGAs, integral components of the VMB phase shifter, must consume DC power, they are classified as active phase shifters. Diverging from passive phase shifters, active phase shifters introduce gain rather than loss. This unique characteristic eliminates the need for additional amplifiers in transceivers utilizing passive phase shifters to compensate for signal losses. Consequently, the elimination of this amplification requirement enhances the overall power efficiency of transceivers equipped with active phase shifters. Despite their advantages, active phase shifters come with trade-offs. Their gain-oriented nature implies a lower noise figure compared to passive alternatives. However, it is essential to note that they simultaneously exhibit increased nonlinearity. As a result, active

Figure 2.1: The Block diagram of a typical VMB phase shifter [16]

phase shifters find greater utility in applications that prioritize sensitivity to noise, such as receivers, as opposed to those necessitating a higher degree of linearity, such as transmitters. In order to enhance the performance of this type of phase shifters, various studies have been conducted to explore avenues for improvement in each constituent building block of VMB phase shifters. The forthcoming sections will delve into the detailed elaboration of select studies addressing these enhancements.

#### Quadrature (90-degree) Hybrid Coupler

For accurate phase shifting, it is essential that the signals in the I and Q branches have an exact 90 degree phase shift and equal amplitudes. Utilizing an RC-CR circuit is the most well-known method to provide suitable I and Q signals. This method is based on the phase lead and phase lag, which are applied by CR and RC network as demonstrated in Fig. 2.2.

As observed, the quadrature hybrid under consideration produces a satisfactory phase difference across its operational bandwidth. However, a noteworthy deficiency is discerned in its amplitude difference, particularly when deviating slightly from

Figure 2.2: (a) schematic and (b) phase and amplitude relation between two outputs of an RC-CR network [17]

the center frequency. As previously elucidated, the VMB phase shifter relies on the weighted amplification of the In-phase (I) and Quadrature-phase (Q) signals. Consequently, the utilization of this specific quadrature hybrid is notably limited within the realm of VMB phase shifters, primarily due to its constrained amplitude balance performance.

For the purpose of arriving at a wideband 90-degree hybrid coupler with a good amplitude balance, a wide variety of techniques based on Poly Phase Filters (PPF) [18, 19] or Quadrature All-pass Filter (QAF) [16, 20] is reported.

The Poly Phase Filter is a modified version of the classical RC-CR network, inheriting key traits from its predecessor. It demonstrates good phase balance, a legacy from the RC-CR network, and achieves effective amplitude balance, especially when employing more sections [21]. The configuration of a wideband, millimeter-wave Poly Phase Filter (PPF) is depicted in Fig. 2.3(a), resembling 3 stages of RC networks interconnected in cascade. Each stage comprises four identical resistors and four identical capacitors, with variations in their values from one stage to the next. In Fig. 2.3(a), In+ and In- represent the differential inputs, I+ and I- are the differential outputs of the I path, and Q+ and Q- are the differential outputs of the Q path. PPFs operate on the principle of the 'stagger tuning' technique, employing two or more cascaded stages of RC-CR networks to smooth the amplitude of the

Figure 2.3: (a) Schematic and (b) amplitude balance and (c) phase balance of a millimeter-wave PPF [18]

generated quadrature signal and extend the bandwidth [21]. As an example, the millimeter-wave PPF, introduced in [18], shows great phase and amplitude balance over its operational bandwidth. The measurement results show less than  $\pm 0.5$  dB magnitude ripple and less than  $\pm 1$  degree phase error over more than 30 GHz bandwidth, as shown in Fig. 2.3(b) and Fig. 2.3(c), respectively. The reported insertion loss for this configuration is around 19 dB.

PPFs, when employed as quadrature generators, presents numerous advantages over conventional RC-CR techniques [22]:

Simplicity in Implementation: PPFs achieve simplicity by utilizing only resistors and capacitors in their design.

Mitigation of CMOS Process Variation Challenges: The stagger-tuning technique is employed by PPFs to address CMOS process variation challenges without requiring additional complex tuning circuitry.

Well-Suited for Wideband Quadrature Signal Generation: PPFs exhibit suitability for the generation of quadrature signals in a wide bandwidth.

These characteristics render PPFs highly suitable for CMOS implementation, especially as RF quadrature generators, where they are specifically referred to as RF CMOS PPFs. However, despite their appropriateness for RF quadrature signal generation in a CMOS process, RF CMOS PPFs manifest certain drawbacks:

Insertion Loss of 3 dB per Stage: Passive filters in RF CMOS PPFs result in an insertion loss of 3 dB per stage. Moreover, unlike matched configurations, PPFs usually don't adhere to impedance matching [18]. However, they often incur excessive loss, which can impact overall performance.

**Need for Buffers (Amplifiers):** Buffers, or amplifiers, are often required to compensate for signal attenuation.

**Power-Hungry Buffers for High Accuracy:** Achieving high accuracy in quadrature signal generation necessitates multiple cascaded stages, leading to power-hungry buffers.

**Thermal Noise Impact:** When used in the signal path, the thermal noise of resistors adversely affects the noise figure (NF) of the receiver.

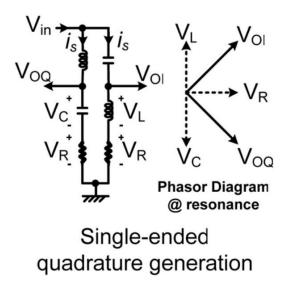

In a Quadrature All-Pass Filter (QAF) the quadrature generation is based on the orthogonal phase splitting between  $V_{OQ}$  and  $V_{OI}$  in the series R-L-C resonators, as shown in Fig. 2.4. The Transfer function of this network can be written as

$$\begin{bmatrix} V_{OI} \\ V_{OQ} \end{bmatrix} = V_{in} \times \begin{bmatrix} s(s + \frac{\omega_0}{Q}) \\ \overline{s^2 + \frac{\omega_0}{Q}s + \omega_0^2} \\ \frac{\omega_0}{Q}(s + Q\omega_0) \\ \overline{s^2 + \frac{\omega_0}{Q}s + \omega_0^2} \end{bmatrix}, \qquad (2.1)$$

where  $\omega_0 = 1/\sqrt{LC}$  and  $Q = \sqrt{L/C}/R$ . Considering the above-mentioned transfer function, a consistent 90-degree phase shift between the I and Q paths for all values of  $\omega$  can be ensured. Moreover, it shows that, while having Q = 1, a 3-dB voltage

Figure 2.4: Generation of resonance-based second-order all-pass quadrature network (Single-ended configuration) [23]

gain can be achieved at the center frequency, selecting Q in the  $0.8 \le Q \le 1$  results in a 2 to 3 dB voltage gain over a wideband frequency range as 3:1 [20].

Figure 2.5: Effect of load capacitance on quadrature accuracy in a single-ended QAF [20]

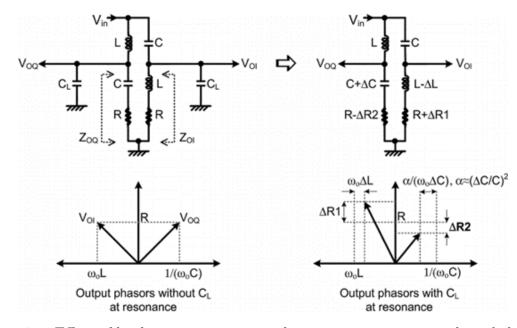

Even with the numerous advantages of the single-ended configuration of the QAF network, it has limited usage in practical applications due to its sensitivity to the load capacitance [23]. The concept of the problem is illustrated in Fig. 2.5. As can be

seen, the load capacitances affect  $Z_{OI}$   $(R + j\omega L)$  and  $Z_{OQ}$   $(R + 1/j\omega C)$  in a different manner. Intuitively, one can conclude that the load capacitance  $(C_L)$  reduces the effective L and decreases the loaded Quality factor (increasing R to  $R + \Delta R_1$ ) in  $Z_{OI}$ , while for  $Z_{OQ}$  it increases the effective C and the loaded Quality factor (decreasing R to  $R - \Delta R_2$ ), which results in I and Q imbalance.

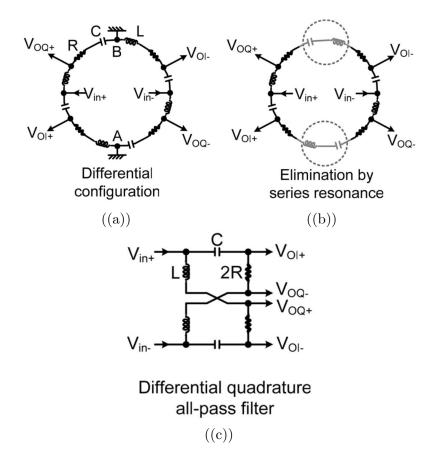

If the QAF network, shown in Fig. 2.4 is modified to the differential configuration, which is shown in Fig. 2.6(a), the real ground can be eliminated because the differential architecture provides a virtual ground at those points. By eliminating the real ground, the series L-C resonator can be substituted by a wire, as shown in Fig. 2.6(b), and the architecture, shown in Fig. 2.6(c), can be used as a differential QAF. The differential configuration in the all-pass mode can mitigate these errors. This is attributed to the fact that any output node impedance in Fig. 2.6(c) is constructed from both low-pass and high-pass networks, offering counterbalances to the impact of  $C_L$

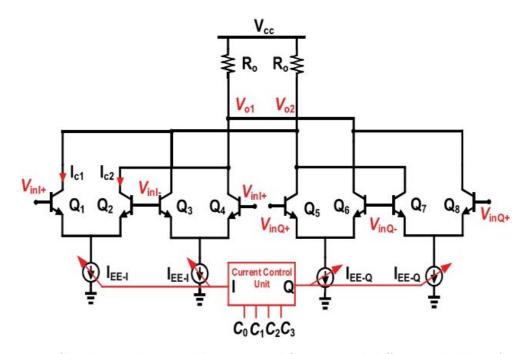

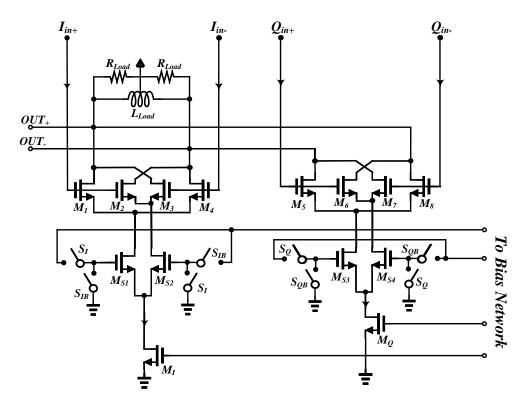

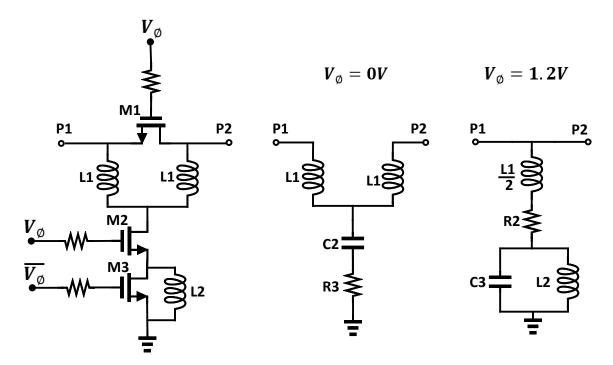

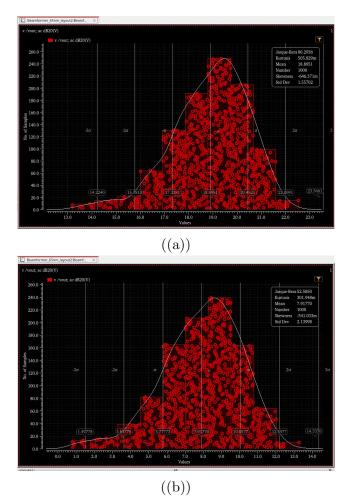

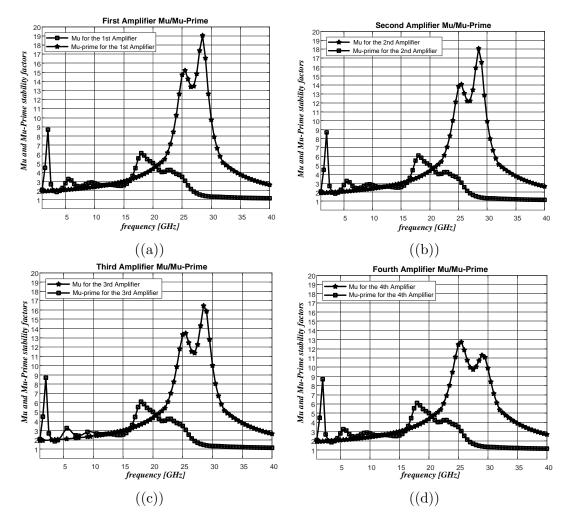

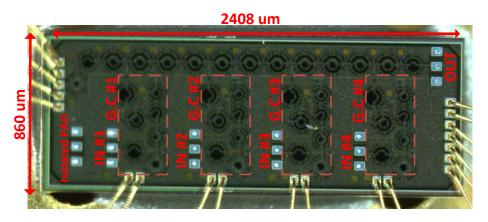

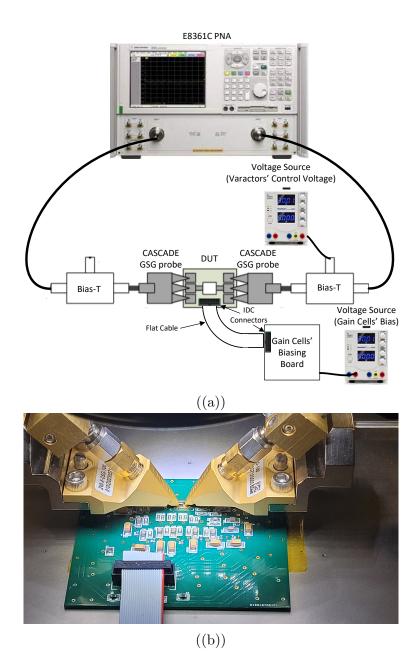

#### Variable-Gain Amplifiers (VGAs) and Analog Differential Adder