#### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

#### University of Alberta

| DESIGN | AND | IMPLEMENTATION | OF  | DIGIT-SERIAL | ONLINE | MULTIPLY- | ACCUMUI | JATE |

|--------|-----|----------------|-----|--------------|--------|-----------|---------|------|

|        |     | Aπ             | TTH | METIC OPERAT | TIONS  |           |         |      |

by

William Natter

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Master of Science.

Department of Department of Electrical and Computer Engineering

Edmonton, Alberta spring 2001

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre rélérence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-60479-9

#### University of Alberta

#### Library Release Form

Name of Author: William Natter

Title of Thesis: Design and Implementation of Digit-Serial Online Multiply-Accumulate

**Arithmetic Operations**

Degree: Master of Science

Year this Degree Granted: 2001

Permission is hereby granted to the University of Alberta Library to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly or scientific research purposes only.

The author reserves all other publication and other rights in association with the copyright in the thesis, and except as hereinbefore provided, neither the thesis nor any substantial portion thereof may be printed or otherwise reproduced in any material form whatever without the author's prior written permission.

**CEB 238**

University of Alberta

Edmonton, AB

Canada, T6G 2G7

Date: January 23, 2001

#### University of Alberta

#### Faculty of Graduate Studies and Research

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies and Research for acceptance, a thesis entitled Design and Implementation of Digit-Serial Online Multiply-Accumulate Arithmetic Operations submitted by William Natter in partial fulfillment of the requirements for the degree of Master of Science

Dr. T. Chen/(Committee chair)

Dr. B. Nowrouzian (Supervisor)

Dr. W. Pedrycz

Dr. L. Stewart

Date: January 26,2001

To my wife, and both our families.

### Abstract

This thesis is concerned with the combination of the online and digit-serial arithmetic techniques for the design, development, and hardware implementation of algorithms for multiplication and multiply-accumulate arithmetic operations. The online technique processes digital signals as generated and consumed by current practical analog-to-digital and digitalto-analog converters. The digit-serial technique permits a trade-off between speed and area in a corresponding hardware implementation, and is extended to dynamically changing wordlengths (with small hardware overhead). Multiplication and multiply-accumulate operations are performed as successive additions of partial operation updates, justifying the use of (redundant) ordinary signed-digit number systems where the addition architecture delays can be made independent of the wordlengths of the inputs. Emphasis is placed on the signed-binary number system, as it is closest to the current practical number systems (signed-magnitude and two's complement). Relationships between number systems are established to subsequently exploit their addition scheme similarities and allow the determination of the corresponding fastest and smallest hardware implementations for the signed-binary and binary carry-save number systems. A generic online algorithm for multiply-accumulate operation is developed so as to allow its modification into an algorithm for inner product by the mere change of the computation of a single variable (a partial operation update), the other variables being operation-independent. Consequently, considerable design time savings are achieved by sharing the same core element for numerous different arithmetic operations. The feasibility of a re-pipelined online digit-serial signed-binary multiplication algorithm is established by employing the IEEE 754 SB RNE rounding technique, and compares it to an existing re-pipelined least-significant-digit- (LSD-) first digit-serial two's complement multiplication algorithm employing the same rounding technique. A simulation of the corresponding FPGA hardware implementation confirms the correct functionality of the algorithm. Parameterized gate-level area and delay estimates of corresponding ASIC hardware implementations are given. Moreover, an online bit-parallel signed-binary algorithm for multiply-accumulate operation employing a novel signed-binary

to minimally redundant base-4 recoding technique, the IEEE 754 SB RNE rounding technique, and a novel overflow detection and correction technique is developed. The resulting algorithm is subsequently compared to an existing LSD-first bit-parallel signed-binary algorithm for multiply-accumulate operation employing an existing signed-binary to minimally redundant base-4 recoding technique and the IEEE 754 SB RNE rounding technique. A simulation of FPGA hardware implementation again confirms the correct functionality of the algorithm.

## Acknowledgements

First, let me thank my wife, our families, and our close friends for supporting me during the journey coming to an end with this thesis, in particular for proof-reading part of it.

Neil definitely deserves my humble gratitude for accepting to proof-read the thesis when he had so much to do.

The writing of this thesis would not have been possible without NSERC and Micronet grants, obtained through the hard work of numerous students in the research group. In particular, Vishwas Rao has initiated the work on which this thesis is based.

Last, but far from being least, I would like to acknowledge the help, support, and guidance of my supervisor, Dr Nowrouzian.

# Contents

| 1 | Intr | oduction                                                           | 1                    |

|---|------|--------------------------------------------------------------------|----------------------|

|   | 1.1  | Digital Signal Processing                                          | 1                    |

|   | 1.2  | Arithmetic for Digital Signal Processing                           | 3                    |

|   | 1.3  | Data Processing Techniques                                         | 5                    |

|   |      | 1.3.1 The Digit-Serial Arithmetic Technique                        | 6                    |

|   |      | 1.3.2 Online Arithmetic Technique                                  | 7                    |

|   | 1.4  | Open Problems                                                      | 8                    |

|   |      | 1.4.1 Online Processing                                            | 8                    |

|   |      | 1.4.2 Constant-Delay Addition                                      | 9                    |

|   |      | 1.4.3 Digit-Serial Online Operations                               | 9                    |

|   | 1.5  | Overview of the Thesis                                             | 10                   |

| 2 | The  | eoretical Background for High-Speed Digit-Serial Online Arithmetic |                      |

|   | One  |                                                                    |                      |

|   | OP.  | erations                                                           | 12                   |

|   | 2.1  | erations Introduction                                              | 12<br>12             |

|   | •    |                                                                    |                      |

|   | 2.1  | Introduction                                                       | 12                   |

|   | 2.1  | Introduction                                                       | 12<br>13             |

|   | 2.1  | Introduction                                                       | 12<br>13<br>13       |

|   | 2.1  | Introduction                                                       | 12<br>13<br>13       |

|   | 2.1  | Introduction                                                       | 12<br>13<br>13<br>13 |

|   | 2.1  | Introduction                                                       | 12<br>13<br>13<br>13 |

|   | 2.4 | High-S | Speed Signed-Binary Addition                                            | 34    |

|---|-----|--------|-------------------------------------------------------------------------|-------|

|   |     | 2.4.1  | Redundant Binary Addition Schemes                                       | 35    |

|   |     | 2.4.2  | Characterization and Equivalence of Redundant Binary Addition Schem     | es 38 |

|   |     | 2.4.3  | Bit-Serial and Digit-Serial Signed-Binary Limited-Carry Addition Ar-    |       |

|   |     |        | chitectures                                                             | 43    |

|   | 2.5 | Chapt  | er Summary                                                              | 47    |

| 3 | The | oretic | al Background for Online Signed-Digit Multiplication and Multi          | ply-  |

|   | Acc | umula  | te Operations                                                           | 48    |

|   | 3.1 | Introd | luction                                                                 | 48    |

|   | 3.2 | Propo  | sed Algorithm for Signed-Digit Online MAC Operation                     | 49    |

|   |     | 3.2.1  | Nomenclature                                                            | 49    |

|   |     | 3.2.2  | Signed-Digit Online MAC Algorithm                                       | 51    |

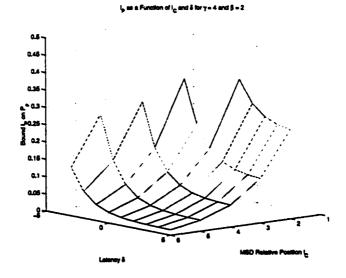

|   |     | 3.2.3  | Determination of the Parameters of the Algorithm                        | 54    |

|   | 3.3 | Algori | thms and Building Blocks for High-Speed Signed-Binary Multiplication    |       |

|   |     | Archi  | tectures                                                                | 59    |

|   |     | 3.3.1  | Single-Digit Multiplier and Digit Clearing Unit                         | 59    |

|   |     | 3.3.2  | Signed-Binary to Minimally Redundant Base-4 Recoding Technique          | 61    |

|   | 3.4 | Round  | ding and Overflow Handling in Online Arithmetic Operations              | 70    |

|   |     | 3.4.1  | Rounding of Signed-Binary Words                                         | 70    |

|   |     | 3.4.2  | Overflow Handling in Online Arithmetic Operations                       | 79    |

|   | 3.5 | Chap   | ter Summary                                                             | 88    |

| 4 | Arc | hitect | ure for Online Signed-Digit Digit-Serial Multiplication                 | 90    |

|   | 4.1 | Intro  | luction                                                                 | 90    |

|   | 4.2 | Algor  | ithm for Bit-Serial Signed-Binary Online Multiplication                 | 91    |

|   | 4.3 | Exten  | sion to a Digit-Serial Signed-Binary Online Multiply-and-Round Algo-    |       |

|   |     | rithm  |                                                                         | 95    |

|   | 4.4 | Archi  | tecture for Digit-Serial Signed-Binary Online Multiplication and Round- |       |

|   |     | ing .  |                                                                         | 99    |

|   |     | A A 1  | Multiplicand Selection Unit                                             | 101   |

|   |       | 4.4.2   | Online Multiplication Units                                      | 101 |

|---|-------|---------|------------------------------------------------------------------|-----|

|   |       | 4.4.3   | Online Rounding Units                                            | 103 |

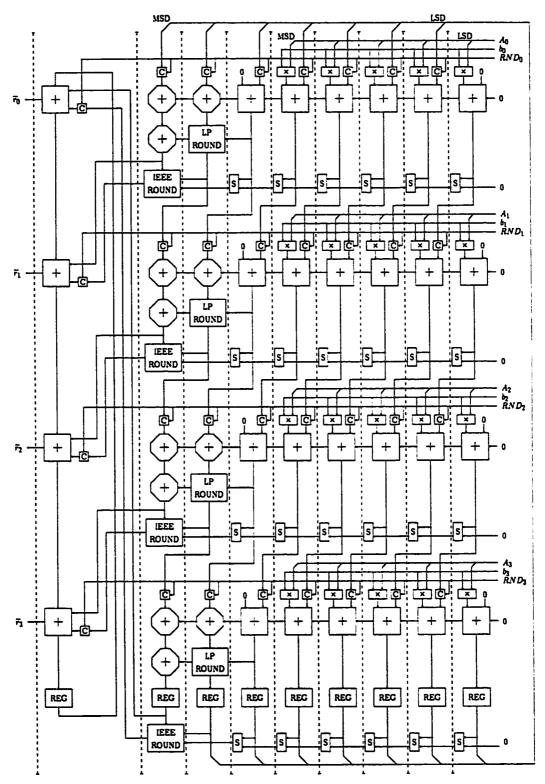

|   | 4.5   | Comp    | uter Simulation Results and Performance Comparison               | 104 |

|   |       | 4.5.1   | Simulation Results                                               | 104 |

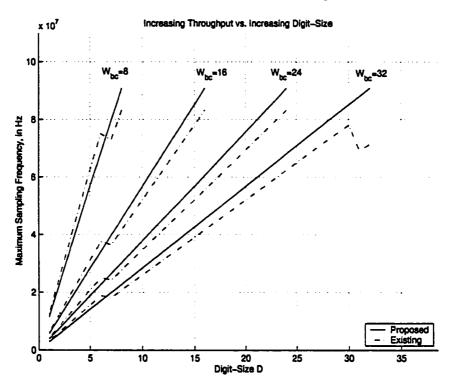

|   |       | 4.5.2   | Throughput Parameterization and Improvement Via Re-Pipelining .  | 106 |

|   |       | 4.5.3   | Area Parameterization                                            | 109 |

|   |       | 4.5.4   | Performance Comparisons                                          | 110 |

|   | 4.6   | Concl   | usion                                                            | 112 |

| 5 | Arc   | hitect  | ure for Online Signed-Binary Bit-Parallel Multiply-Accumulat     | :e  |

|   |       | eration |                                                                  | 114 |

|   | 5.1   |         | -<br>luction                                                     | -   |

|   | 5.2   |         | arallel Signed-Binary MAC Algorithm Employing SB to MRB4 Recodin |     |

|   | 5.3   |         | tecture for MAC Operation Employing Signed-Binary Multiplier Re- | .6  |

|   | 0.0   |         | g                                                                | 122 |

|   |       |         | ~                                                                | 122 |

|   |       | 5.3.1   | Signed-Binary to Minimally Redundant Base-4 Recoders             |     |

|   |       | 5.3.2   | Online Multiplication Units                                      |     |

|   |       | 5.3.3   | Rounding and Overflow Correction Unit                            | 124 |

|   | 5.4   | Comp    | outer Simulation Results and Performance Comparison              | 124 |

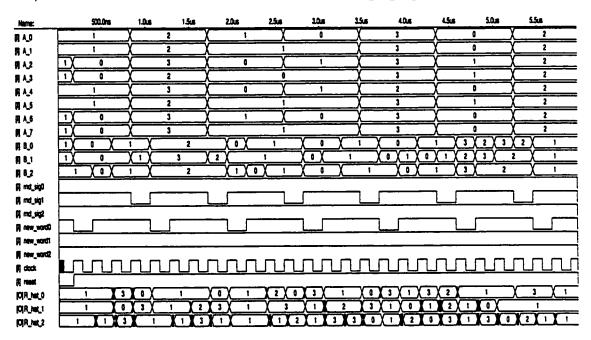

|   |       | 5.4.1   | Simulation Results                                               | 125 |

|   |       | 5.4.2   | Throughput Parameterization                                      | 127 |

|   |       | 5.4.3   | Area Parameterization                                            | 127 |

|   |       | 5.4.4   | Comparison                                                       | 128 |

|   | 5.5   | Concl   | lusion                                                           | 130 |

| 6 | Co    | nclusio | on .                                                             | 131 |

|   | 6.1   | Revie   | ew of Material Presented                                         | 131 |

|   | 6.2   | Propo   | osed Areas of Future Work                                        | 132 |

|   | 6.3   | _       | luding Remarks                                                   |     |

|   |       |         |                                                                  |     |

| В | iblio | graphy  | <b>y</b>                                                         | 135 |

| A | Syst | tematic Enumeration of Redundant Binary Addition Schemes                                                                                                         | 139 |

|---|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | A.1  | Determination of Set Cardinalities                                                                                                                               | 139 |

|   | A.2  | Systematic Determination of the Sets $S_{c_1}$ , $S_{\alpha}$ , $S_{c_2}$ , and $S_{\beta}$                                                                      | 141 |

|   |      | A.2.1 Case 1: $ S_{c_1}  = 3$ and $ S_{\alpha}  = 2 \dots \dots$ | 142 |

|   |      | A.2.2 Case 2: $ S_{c_1} =2$ and $ S_{\alpha} =3$                                                                                                                 | 143 |

|   | A.3  | Characterization of Redundant Binary Number Addition Schemes                                                                                                     | 144 |

|   | A.4  | Equivalence of Redundant Binary Number Addition Schemes                                                                                                          | 145 |

|   | A.5  | Conclusion                                                                                                                                                       | 150 |

# List of Figures

| 1.1 | Typical DSP System                                                                                   | 2   |

|-----|------------------------------------------------------------------------------------------------------|-----|

| 2.1 | 4-Bit LSD-First Bit-Serial Binary Adder                                                              | 26  |

| 2.2 | Bit Number in a 4-Bit Bit-Serial Data Stream                                                         | 27  |

| 2.3 | 4-Bit LSD-First Digit-Serial Binary Adder $(D=3)$                                                    | 28  |

| 2.4 | Bit Number in a 4-Bit Digit-Serial Data Stream ( $D=3$ )                                             | 28  |

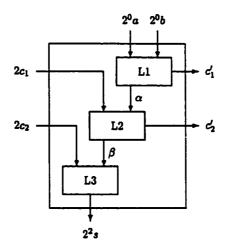

| 2.5 | Limited Carry Adder Unit                                                                             | 38  |

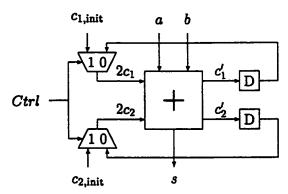

| 2.6 | Architecture for Bit-Serial Online Limited-Carry Addition                                            | 44  |

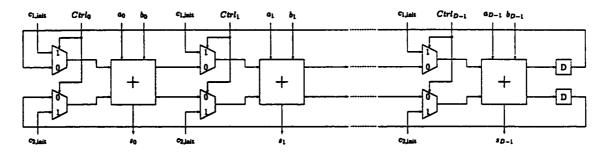

| 2.7 | Architecture for Digit-Serial Online Limited-Carry Addition                                          | 47  |

| 3.1 | Bound on $P_{\rho}$ as a function of $\delta$ and $i_c$ for $\beta = 2$ , $\gamma = 4$ and $l_a = 1$ | 56  |

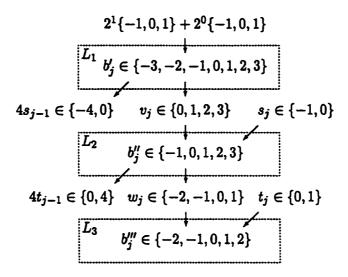

| 3.2 | Three-Level Signed-Binary to Radix-4 Digit Set Conversion                                            | 66  |

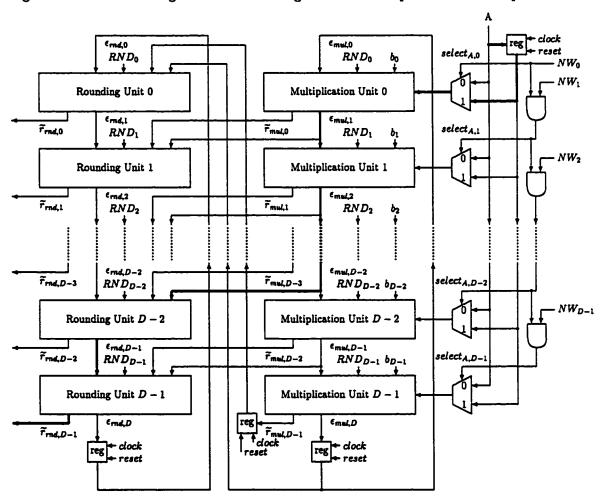

| 4.1 | Architecture for Digit-Serial Online Multiply-and-Round Operation                                    | 99  |

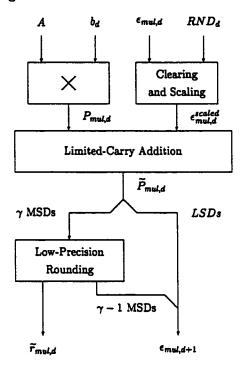

| 4.2 | Architecture of an Online Multiplication Unit                                                        | 102 |

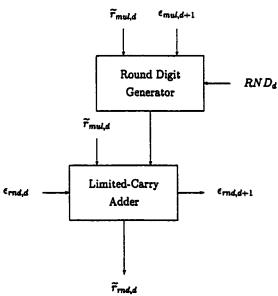

| 4.3 | Architecture of an Online Rounding Unit                                                              | 103 |

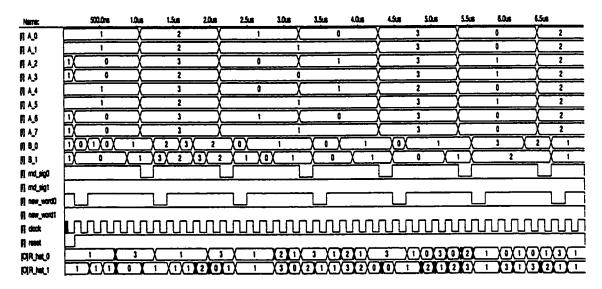

| 4.4 | Simulation Results for $D=2$ and $W_a=W_b=8$                                                         | 105 |

| 4.5 | Simulation Results for $D=3$ and $W_a=W_b=8$                                                         | 106 |

| 4.6 | Re-Pipelined Architecture for MAC Operation and IEEE 754 RNE Rounding,                               |     |

|     | with $W_a = 5$ and $D = 4$                                                                           | 108 |

| 4.7 | Throughput Versus Digit-Size of Proposed and Existing Digit-Serial Multi-                            |     |

|     | plication Architectures                                                                              | 111 |

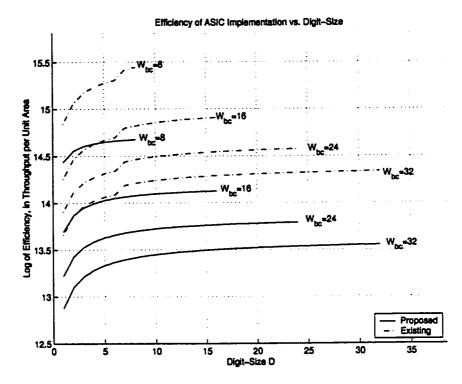

| 4.8 | Log of Efficiency Versus Digit-Size of Proposed and Existing Digit-Serial                            |     |

|     | Multiplication Architectures                                                                         | 112 |

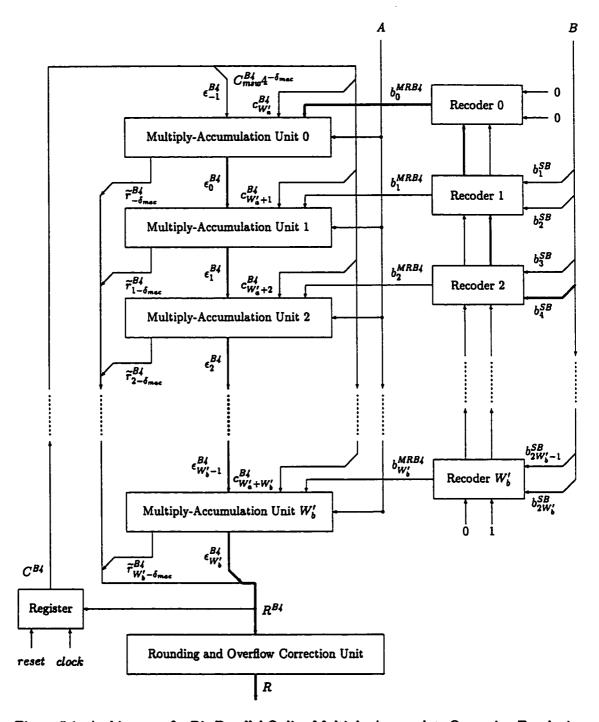

| 5.1 | Architecture for Bit-Parallel Online Multiply-Accumulate Operation Em- |     |

|-----|------------------------------------------------------------------------|-----|

|     | ploying SB to MRB4 Recoding                                            | 123 |

| 5.2 | Simulation Results for $W_a = W_b = 8$                                 | 126 |

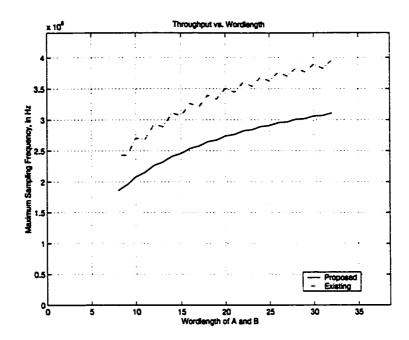

| 5.3 | Throughput Versus Wordlength of Proposed and Existing Bit-Parallel MAC |     |

|     | Architectures                                                          | 129 |

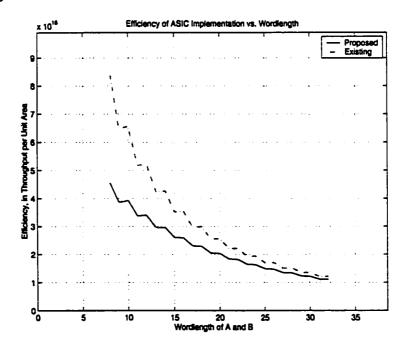

| 5.4 | Efficiency Versus Wordlength of Proposed and Existing Bit-Parallel MAC |     |

|     | Architectures                                                          | 129 |

## List of Tables

| 1.1 | Classification of Signals                                                               | 2   |

|-----|-----------------------------------------------------------------------------------------|-----|

| 2.1 | Set Cardinalities in Redundant-Binary Addition Schemes                                  | 39  |

| 2.2 | Parametrized Digit Sets of Redundant Binary Addition Schemes                            | 40  |

| 2.3 | Coding the Set Values                                                                   | 42  |

| 2.4 | Code for $c_1$ and $c'_1$                                                               | 45  |

| 3.1 | Signed-Binary Encoding                                                                  | 67  |

| 3.2 | Conventions for MRB4 Digit Encoding                                                     | 68  |

| 3.3 | Low-Precision Rounding of SB Numbers                                                    | 77  |

| 3.4 | Conversion of $OVF_{\rho}$ , $POVF_{\rho}$ , and $S_{\rho}$ into $\epsilon_{\rho}$      | 87  |

| 4.1 | Test Vectors for Digit-Serial Multiply-Round Operation in Decimal                       | 105 |

| 4.2 | ${\bf Test\ Vectors\ for\ Digit-Serial\ Multiply-Round\ Operation\ in\ Signed-Binary}.$ | 105 |

| 4.3 | Hexadecimal to Signed-Binary Conversion Table                                           | 106 |

| 4.4 | Area Requirement for the Multiplication Architecture                                    | 110 |

| 5.1 | Test Vectors for Parallel MAC Operation in Decimal                                      | 125 |

| 5.2 | Test Vectors for Parallel MAC Operation in Signed-Binary                                | 126 |

| 5.3 | List of Delays of Architectural Units                                                   | 127 |

| 5 1 | List of Areas of Units Constituent in the MAC Architecture                              | 128 |

## List of Symbols

A/D analog-to-digital

ASIC application-specific integrated circuit

BCS binary carry-save

BS bit-serial

BSD balanced (ordinary) signed-digit

D/A digital-to-analog converter

DFG data-flow graph

DS digit-serial

DSP digital signal processing/processor

FA full adder

FPGA field-programmable gate-array

GSD generalized signed-digit

GSDNS generalized signed-digit number system

IEEE Institute of Electrical and Electronics Engineers

LSD least significant digit

MAC multiply-accumulate (arithmetic operation)

MRB4 minimally redundant base-4

MSD most significant digit

OSD ordinary (balanced) signed-digit

OSDNS ordinary signed-digit number system

RNE round to nearest/even

RNU round to nearest/upper

SB signed-binary

TC two's complement

USD unbalanced signed-digit

USDNS unbalanced signed-digit number system

VHDL Very large scale integrated circuit Hardware Description Language

A multiplicand word

$a_i$  multiplicand digit of index i

B multiplier word

$B_{\rho}$  partially formed multiplier word at iteration  $\rho$

$b_i$  multiplier digit of index i

C addend word

$C_{\rho}$  partially formed addend word at iteration  $\rho$

$c_i$  addend digit of index i

$l_x$  attainable upper limit/ bound of a representation

$P_{\rho}$  off-line partial operation update word at iteration  $\rho$

$\widetilde{P}_{

ho}$  online partial operation result word at iteration ho

$\overline{\tilde{P}}_{\rho}$  truncated (to its  $\gamma$  MSDs) online partial operation result word at iteration  $\rho$

$\widetilde{p}_{\rho,i}$  online partial operation result digit of index i at iteration  $\rho$

$R_{\rho}$  off-line operation result word at iteration  $\rho$

$\widetilde{R}_{

ho}$  online operation result word at iteration ho

$\tilde{r}_i$  online partial operation result digit of index i

- $W_x$  wordlength of X

- β radix/base of a number representation/system

- $\beta^{-i}$  weight of a digit of index i

- $\gamma$  internal wordlength (of  $\overline{\widetilde{P}}_{

ho}$ )

- $\Delta$  offset parameter

- $\delta$ ,  $\delta_{op}$  latency of an online operation

- $\epsilon_{\rho}$  online error at iteration  $\rho$

- $\eta$  redundancy index (OSD number system)

- ρ iteration number

- + addition

- logic OR operation

- ÷ addition of sets

- × multiplication of a set by a scalar

- ⊕ XOR logic operation

- ~ AND logic operation

- . NOT logic operation

- N set of positive integers

- Q set of rational

- R set of reals

- R equivalence relationship between additions

- **Z** set of signed integers

- Z set of negative integers

- **Z**<sup>+</sup> set of positive integers

### Chapter 1

### Introduction

#### 1.1 Digital Signal Processing

Most living creatures need to communicate in order to survive. Signals, which are sounds, gestures, or objects, convey the necessary pieces of information to perform communication.

The first man-made devices using electrical signals to convey information are the telegraph (invented by Morse in 1844), and the telephone (invented by Bell in 1876). The fundamental difference between telegraph and telephone is the type of signals they handle. To send a message by telegraph, one needs to write it on a sheet of paper. Then, a telegrapher translates every letter into Morse code. A letter is represented by a sequence of two symbols, which is called a binary representation of the letter. Then, the symbols are transmitted in sequence over a wire as short and long impulses of electricity. The message is decoded on the other side by another telegrapher and handed over to the recipient of the message or forwarded to another place if necessary. By contrast, to send a message by telephone one speaks in a mouthpiece which translates the air vibrations into electrical signals. Of course, these signals are not a binary representation of the message. The electrical signals propagate through a wire, and are translated back to air vibrations through an ear-piece so that the receiver can hear what was said on the other end.

In electrical engineering, a signal is represented as an amplitude that varies as a function of time. In other words, the domain of a signal is an interval of time, and its range an interval of amplitude. An interval is discrete if it contains only a finite number of values (as opposed to a continuous interval). Therefore, there are four classes of signals, as listed in Table 1.1. Discrete-time discrete-amplitude signals are frequently referred to as digital,

Table 1.1: Classification of Signals

|                 | Continuous Amplitude | Discrete Amplitude |

|-----------------|----------------------|--------------------|

| Continuous Time | temperature          | street light       |

| Discrete Time   | precipitations       | paycheque          |

whereas continuous-time continuous-amplitude signals are referred to as analog.

In nature, signals are usually analog, whereas man-made machines usually generate digital signals. Digital signals are handled by digital signal processors. A main important practical advantage of digital processors is their programmability, permitting various operations to be performed by using the same processor, and their cost-effectiveness. Fortunately, Nyquist determined that if certain conditions apply, analog signals can be digitized, i.e. represented using corresponding digital signals, and recovered perfectly. Several factors have contributed to the widespread use of the digital processing of analog and digital data, often called digital signal processing (DSP). First, the inventions of microprocessors and application-specific integrated circuits (ASICs) have permitted the custom design of digital signal processors. Second, the ever-decreasing size of silicon-based transistors has made possible the doubling of the speed of digital circuits every 18 months, and the reduction of their cost, the silicon area of a digital circuit largely determining its cost.

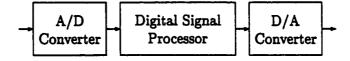

A typical DSP system is made of analog-to-digital (A/D) and digital-to-analog (D/A) converters, and of a digital signal processor, as shown in Figure 1.1. The A/D and D/A

Figure 1.1: Typical DSP System

converters perform the same kind of operation as the translation of a message into their Morse code in the telegraph. The digital signal processor performs arithmetic operations, which most often comprise numerous additions and multiplications. The number of calculations to perform thereby determines the maximum speed at which the DSP system can

operate. Moreover, the area of the digital signal processor is a dominant component in the cost of the DSP system. Both these factors, speed and area, depend greatly on how the addition and multiplication operations are implemented.

Of particular interest is an arithmetic operation capable of multiplying two numbers, and adding the result to a third number. Such an operation can be performed by a multiply-add or by a multiply-accumulate (MAC) arithmetic operation. The multiply-add arithmetic operation calculates the result and rounds it, whereas the MAC arithmetic operation calculates the full-precision result.

Example 1 Let us multiply 0.01 by 0.02. The result is obtained as 0.0002 in a MAC arithmetic operation, whereas it is rounded to 0.00 in a multiply-add arithmetic operation.

In this way, the use of MAC arithmetic operations is preferable in digital signal processors which are sensitive to calculation accuracy.

Consider a digital signal processor employing only addition and multiplication operations. A MAC modularization technique was developed in (Rao, 1996) to modify such a processor in order for it to use exclusively MAC arithmetic operations. Therefore, in a situation where area is the dominant factor, it is sufficient to build a digital signal processor having a single MAC arithmetic operator, and to perform multiplex all the operations onto that operator (c.f. the Motorola DSP56002).

A typical digital signal processor using addition, multiplication, and unit-delays is called a digital filter. Its primary objective is to selectively attenuate or boost certain frequency components of a signal. This is usually performed by adding weighted present and past input and past output samples, where the weights are constant. This corresponds to an inner product of a vector of constant weights by a vector of delayed input and output samples, which can be translated to a number of MAC arithmetic operations.

#### 1.2 Arithmetic for Digital Signal Processing

Digital signals are sampled and quantized analog signals, and are represented at each sample time instant by a number. Many different number systems can be used, where the algebraic value of a number is represented by a succession of digits referred to as a word. The

mapping from word to algebraic value can be performed by assigning each digit a weight. In this way, the algebraic value is obtained by summing the digit values multiplied by their corresponding weights. In most number systems, the weights are expressed as consecutive powers of a radix which will be denoted by  $\beta$  (also referred to as the base). Therefore, most number systems are characterized by their digit set and radix.

Example 2 The radix of the decimal number system is 10, and the digit set is  $\{0, 1, 2, 3, 4, 5, 6, 7, 8, 9\}$ . Consider the decimal number 5, which can be represented by the decimal word  $005_{10}$ , where  $005_{10} = 0 \times 10^2 + 0 \times 10^1 + 5 \times 10^0$ . Consider now the binary number system: it has a radix 2, and a digit set  $\{0, 1\}$ . The decimal number 5 can now be represented in the binary number system by  $101_2$ , where  $1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0 = 005_{10}$ .

Radix- and digit set-based number systems can be classified into two categories, namely, the fixed-point and floating-point number systems. In a fixed-point number system, the weights have fixed values, i.e. the largest weight can always be made equal to, for example,  $\beta^{-1}$ . The digit related to the smallest weight is called the least significant digit (LSD), and the digit related to the largest weight is called the most significant digit (MSD). Moreover, the number of digits constituting the word is called the wordlength. In a floating-point number system, the word is split into two components, namely, the fractional and exponent parts f and e, respectively. The fractional part is a fixed-point representation of a number N, and the algebraic value of the desired number is obtained by multiplying N by  $\beta^e$ , which is referred to as scaling up by  $\beta^e$ . The increased range of a floating-point representation compared to that of a fixed-point representation is obtained at the expense of additional precision digits. Consequently, floating-point-based calculations are more prone to accuracy-related errors than fixed-point-based calculations. The fixed-point binary number system is the dominant number system in computers, mainly because its digit set has only two elements, logic 0 and logic 1.

This thesis is concerned with ordinary signed-digit (OSD) number systems, which are radix- $\beta$  fixed-point number systems having a digit set  $\{-\eta, \ldots, 0, \ldots, \eta\}$  such that  $\left\lceil \frac{\beta}{2} \right\rceil \le \eta \le \beta$  (Avizienis, 1961; Parhami, 1990). These number systems are called redundant, because a given algebraic value may have several different representations.

Example 3 The signed-binary (SB) number system has a radix 2, and a digit set  $\{\bar{1},0,1\}$ , where  $\bar{1}$  represents -1. The decimal number 3 can then be represented either by  $011_2$ , where  $0 \times 2^2 + 1 \times 2^1 + 1 \times 2^0 = 3_{10}$ , by  $10\bar{1}_2$ , where  $1 \times 2^2 + 0 \times 2^1 - 1 \times 2^0 = 3_{10}$ , or even by  $1\bar{1}1_2$ , where  $1 \times 2^2 - 1 \times 2^1 + 1 \times 2^0 = 3_{10}$ .

In high-speed arithmetic operations, the time required to perform an operation, i.e. the delay, must be minimized. Consider the addition of the words A and B of equal wordlength, yielding a sum S. If A, B, and S are words expressed in a non-redundant number system, then the delay to obtain S is, at best, proportional to the logarithm of the common wordlengths of A and B (Kornerup, 1994). This is mainly due to the fact that the value of the MSD of S depends on the value of the LSDs of A and B, thereby requiring the propagation of a carry along the full length of A and B. However, if the number system is redundant, then the delay can be made independent of the wordlength of A and B, because the value of the MSD is no longer dependent upon the values of all the digits of A and B (Avizienis, 1961; Parhami, 1990; Kornerup, 1994). Redundant number system hardware implementations exhibit larger areas relative to those of non-redundant number systems for equivalent operations, mainly because their digit sets contain more values. As a result, the absolute areas of redundant number system hardware implementations have represented a hindrance in the past. This hindrance has been overcome with the advent of sub-micron technologies.

In other number systems, such as in the logarithmic, residue, and rational number systems (Hwang, 1979), the mapping between the word and its algebraic value takes on different forms, but these forms are beyond the scope of this thesis.

#### 1.3 Data Processing Techniques

A digital signal must be transmitted as a word from an A/D converter to a digital signal processor, and from the digital signal processor to a D/A converter. At a given time instant, one, several, or all digits of a word can be transmitted, i.e. in a bit-serial, digit-serial, or bit-parallel fashion, respectively. Of course, the bit-serial and bit-parallel fashions are subsumed by the digit-serial arithmetic technique. However, the digit-serial arithmetic technique can

be derived from the bit-serial arithmetic technique.

Moreover, a bit-serial data stream can be processed, (a) the LSD first, which is the conventional arithmetic technique, or (b) the MSD first, which is the online arithmetic technique. The digit-serial and online arithmetic techniques are described in the following.

#### 1.3.1 The Digit-Serial Arithmetic Technique

Let us consider an architecture having input data streams consisting of successions of words having a common wordlength W. By definition, the bit-serial arithmetic technique only requires to process one bit at a time (as opposed to W for the bit-parallel arithmetic technique). In addition, the number of wires required for transmission increases from 1 to W. Consequently, the bit-serial technique results in smaller processing units (which is area-effective), but the bit-parallel technique permits the design of faster architectures. The speed of an architecture is measured by its throughput, i.e. the number of samples it can process per time instant.

The main principal trade-off in the design of electronic systems involves achieving the highest execution speed at the smallest area and the lowest power. The digit-serial arithmetic technique proposes that the given architecture may process D digits of each of the input data streams per time instant, where the digit-size D may or may not be a divisor of W. In this way, a balance can be struck between the area efficiency of bit-serial systems and the speed efficiency of bit-parallel systems. It is important to note that the bit-serial and bit-parallel arithmetic techniques are special cases of the digit-serial arithmetic for a digit-size of 1 and W, respectively.

Any bit-serial architecture can be transformed into its unique digit-serial counterpart of digit-size D (Parhi, 1991). Then, the bit-serial data stream is sectioned into sets of D consecutive digits. Of course, digits from two consecutive words may be present in that set. Therefore, an arithmetic operation on digits coming from two different words/numbers may occur at a given time instant in a digit-serial architecture, but, of course, must not interfere.

#### 1.3.2 Online Arithmetic Technique

Current practical A/D and D/A converters generate and consume digits one by one, from the MSD first to the LSD last. However, in the conventional arithmetic techniques, the carry propagates from the LSD first to the MSD last. Therefore, unless operations can be performed the MSD first, delays due to changes in the flow of digits occur. The online arithmetic technique performs arithmetic operations digit by digit, the MSD first. The result of such an operation must be expressed in a redundant number system<sup>1</sup> (Owens, 1983). Therefore, online arithmetic operations have been seldom used because of the large area in the corresponding hardware implementations.

The online arithmetic technique finds its roots in 1961, when Avizienis introduced the notions of signed-digit arithmetic and constant-delay addition (Avizienis, 1961). In 1977, Irwin introduced online algorithms for several arithmetic operations (Irwin, 1977). In the past two decades, the increase in transistor density has permitted the very large scale integration of corresponding architectures to take place. As a result, online algorithms have gained plenty of interest. The most popular online algorithms perform arithmetic operations iteratively, the MSD first.

Let us consider an algorithm performing an arithmetic operation. The inputs are referred to as the operands, and the output as the result. Formally speaking, the *online* property can be defined in terms of the input to, or the output from, an arithmetic operation (Owens, 1981). The algorithm is online with respect to its inputs when at a given iteration  $\rho$ , the first  $\rho + k_{in}$  MSDs of the operands are required for calculation, where  $k_{in}$  is a small constant. Similarly, the algorithm is online with respect to its output when, at a given iteration  $\rho$ , the first  $\rho - k_{out}$  MSDs of the result have been generated by the algorithm (Owens, 1981), where  $k_{out}$  is again a small constant. Finally, the algorithm is online when it is both online with respect to its inputs and with respect to its output. The constant  $k_{in} + k_{out}$  is referred to as the *latency* of the online algorithm. The latency represents the number of iterations elapsing between the arrival time for the input MSD and the departure time for the result digit having the same weight as the input MSD. It is important to note that, in general, the

<sup>&</sup>lt;sup>1</sup>If one assumes that the result word is expressed in a non-redundant number system, then the MSD cannot be output at the first iteration, because it depends on the values of the LSDs of the inputs.

weight of the MSD of the result is larger than the weight of the MSD of the input, resulting in a non-zero latency.

The flow of digits in online arithmetic operations corresponds to that in current practical A/D and D/A converters (unlike the conventional LSD-first arithmetic operations). The resulting advantages are that, (a) the delay due to a change in the flow of digits is eliminated, and (b) the LSDs can be discarded when full-precision computation is not required. Then, the result must be expressed in a redundant number system. If redundant representations are used both for the input words and the output words, then addition within online arithmetic processors can be performed in constant time.

The hardware implementations of online arithmetic processors require large areas, because redundant number systems require larger boolean functions which are more difficult to develop (Carter and Robertson, 1990; Ercegovac and Lang, 1990; Chow and Robertson, 1978); given the rapid decrease in transistor size, the area becomes less important.

In online arithmetic operations, the propagation of the carry toward the MSD must be stopped. This is accomplished by introducing a latency between the weight of the online input operand digit(s) and that of the output result digit. As a result, online algorithms result in slower parallel architectures than LSD-first algorithms for a given number system.

#### 1.4 Open Problems

#### 1.4.1 Online Processing

Numerous online algorithms performing arithmetic operations, including addition, subtraction, multiplication, division, and multiply-accumulate arithmetic operation (MAC arithmetic operation), have been developed (Irwin, 1977; Owens, 1981; Irwin and Owens, 1987; Guyot and Kusumaputri, 1991; Brackert et al., 1989; Sips and Lin, 1990; Lapointe et al., 1993; McQuillan and McCanny, 1995). The development of such algorithms is commonly based on the function approximation, the immediate evaluation, or the recursion-based approaches. The function approximation is employed for the approximation of complicated functions as polynomials. Two E-model approaches have been described, in (Ercegovac, 1984) and in (Sips and Lin, 1990). In (Ercegovac, 1984), a function value is calculated via an equivalent system of linear equations, for which efficient online architectures

exist. In (Sips and Lin, 1990), an exact function value is fetched from a table by using the partially known inputs, and an output digit is estimated by taking into account the previous output digits. These two approaches can be employed for any function. The recursion-based approach can be employed for any polynomial which includes addition, MAC operation, and inner product (Irwin, 1977; Ercegovac, 1984; Sips and Lin, 1990).

So far, none of these techniques have separated the mechanism of the online process from the calculation of the function under study. In particular, finding an internal mechanism common to all recursion-based online algorithms remains an open problem for arithmetic operations. The main advantage of such a mechanism would be its applicability to the calculation of several different operations: in the industry, a corresponding hardware implementation would be common to a number of arithmetic operations, and design re-use could be applied, saving substantial design time and capital.

#### 1.4.2 Constant-Delay Addition

In a redundant number system with large radix value, arithmetic operations require large boolean functions which are difficult to optimize for hardware implementation. As a result, the redundant binary system remains the most suitable for hardware implementation. Multiplications and MAC operations using redundant-binary number systems are implemented as nested additions of redundant-binary numbers. Architectures for constant-delay hardware implementations of redundant-binary addition have been reported in (Chow and Robertson, 1978; Parhami, 1988; Thornton, 1997). A systematic enumeration of such architectures for redundant-binary addition has not been undertaken. Such an approach may result in novel, small, and high-speed hardware implementations. Moreover, interrelation-ships between the existing developments of architectures for redundant binary addition may be discovered, saving design time.

#### 1.4.3 Digit-Serial Online Operations

The hardware implementations of architectures for online arithmetic operations often result in large areas, implying high cost. Therefore, despite their outstanding features (including MSD-first processing, and low latency), online arithmetic operations are seldom used

in practical applications. However, the digit-serial arithmetic technique, which permits a trade-off between the speed and area of an architecture for arithmetic operation, has been applied to some online operations only for the special case of the digit-size being a divisor of the wordlength (Irwin and Owens, 1988). The general digit-serial technique has not to been applied yet to the development of architectures for online MAC arithmetic operations.

#### 1.5 Overview of the Thesis

The purpose of this thesis is twofold, namely, (a) to introduce the necessary background for the development of architectures for digit-serial online signed-digit arithmetic operations, and (b) to develop digit-serial and digit-parallel purely signed-digit multiply-accumulate operations.

Chapter 2 is concerned with an introduction to the mathematical framework necessary for digit-serial online fixed-point arithmetic operations, with a thorough description of limited-carry addition architectures. Discussions concerning number systems and the digit-serial and online arithmetic techniques are given. A simplification of the existing digit-serial unfolding algorithm is provided along with an introduction of a new dynamically changing wordlength technique. A systematic enumeration of architectures permitting the constant-delay addition of redundant binary numbers is presented. This is required for the design of high-speed signed-binary MAC operations as nested additions.

Chapter 3 introduces the necessary background for the development of industry-standard multiplication architectures. The development of bit-serial online MAC arithmetic operations is first discussed in detail, leading to the description of the recursion-based online mechanism, which can be used for the calculation of any affine function. Then, description of single-digit signed-binary multipliers is given, followed by the development of a novel technique for signed-binary to minimally redundant base-4 conversion. Such a conversion permits the design of faster and smaller architectures for MAC arithmetic operations. Also, an online signed-binary algorithm is given for IEEE 754 round-to-nearest/even, together with an online algorithm for signed-digit overflow handling.

Chapter 4 develops an algorithm for digit-serial online multiply-and-round arithmetic operation for general digit-size and input wordlength values. The algorithm employs the

IEEE 754 RNE industry standard. An architecture for subsequent FPGA or ASIC hardware implementation is given, which is re-pipelined for throughput maximization and proven functionally correct through simulation. The throughput and efficiency (throughput per unit area) performances of this architecture are compared unfavorably to those of an existing LSD-first digit-serial two's complement multiply-and-round operation employing signed-binary intermediate partial products. However, the architecture is shown to be viable for high-speed applications.

In Chapter 4, an algorithm is developed for signed-binary parallel online MAC arithmetic operation employing signed-binary to minimally redundant base-4 multiplier conversion, IEEE 754 RNE rounding, and overflow detection and correction. A corresponding architecture for subsequent FPGA or ASIC hardware implementation is given, and proven functionally correct through simulation. The throughput and efficiency figures are compared unfavorably to those of an existing architecture for signed-binary parallel LSD-first MAC arithmetic operation employing signed-binary to minimally redundant base-4 multiplier conversion and IEEE 754 RNE rounding.

### Chapter 2

# Theoretical Background for High-Speed Digit-Serial Online Arithmetic Operations

#### 2.1 Introduction

Presently, digital signal processing finds numerous applications in many areas, such as virtual image synthesis, data transmission and reception, and database management. A digital signal is seen as time-dependent data, and is represented as a sequence of numbers (frequently referred to as samples), where each sample is represented as a sequence of digits arranged in a given format. Consequently, digital signal processing requires many arithmetic operations, predominantly additions and multiplications. The performance of an arithmetic operation depends heavily on the choice of the digit sets, how many digits to process at a time, and in which order the digits are processed.

The present chapter provides the necessary background for the design and development of architectures for online arithmetic operations in general, and for the multiplication operation in particular. In Section 2.2, the corresponding fixed-point number representations are discussed with an emphasis on generalized signed-digit number representations and their properties. Then, the digit-serial and online arithmetic techniques are introduced in Section 2.3. An improved digit-serial unfolding algorithm and an example of an online algorithm are also provided in that section. In addition, a new digit-serial unfolding technique for architectures performing operations where the wordlength of the input changes dynamically is proposed. Finally, in Section 2.4, limited-carry addition schemes that yield

architectures whose delays are independent of the lengths of their inputs are explored. A characterization of these schemes permits one to link the design and development of several kinds of addition architectures, so as to reduce their design and development time.

#### 2.2 Fixed-Point Arithmetic

#### 2.2.1 Introduction

Arithmetic operations are the building blocks of digital signal processors. This section is concerned with a discussion of the impact of generalized signed-digit number representation, (a) on the range of permissible digital data, and (b) on the area and speed of the corresponding DSP hardware architecture.

#### 2.2.2 Number Representation and Number Systems

**Definition 4** Number representation: consider a number N that belongs to a set S (e.g. N, Z, or  $\mathbb{Q}$ ). A representation of N consists of

- 1. a digit set D (e.g.  $\{0, ..., 9\}$ ),

- 2. an integer length L,

- 3. a sequence  $n_{i_{\min} \le i \le i_{\max}}$  of digits that belong to D, where  $i_{\max} i_{\min} + 1 = L$ , and

- 4. a mapping M defined in accordance with

$$M: d_{i_{\min \leq i \leq i_{\max}}} \in D^L \mapsto s \in S$$

Then, N is represented by the sequence  $n_{i_{\min} \le i \le i_{\max}}$  through the mapping M if

$$M\left(n_{\dot{\eta}_{i_{\min} \le i \le i_{\max}}}\right) = N \tag{2.1}$$

holds.

The digits  $n_i$  are constrained to a certain digit set D. For example, the decimal representation of N requires that  $n_i$  belongs to the set  $\{0, 1, ..., 9\}$ . The sequence of digits is commonly referred to as a word.

A system in which number representations share the same mapping is called a number system. Number systems can be classified into two categories, namely complete and incomplete number systems. In a complete number system, any number from S can be represented by using the digit set D and the mapping M (Kornerup, 1994). This thesis is concerned with complete number systems only.

#### Fixed- and Floating-Point Number Representations

Usually, the digits of a number representation are assigned weights, denoted by the sequence  $w_{i_{\min} \le i \le i_{\max}}$ , and the mapping is the obtained as the inner product of the digit and the weight sequences in accordance with

$$M\left(n_{i_{\mid i_{\min} \leq i \leq i_{\max}}}\right) = \sum_{i=i_{\min}}^{i_{\max}} n_{i} w_{i}. \tag{2.2}$$

Most often, such a representation is either referred to as fixed-point or as floating-point. Certain representation mappings do not use weights in this way (e.g. the logarithmic, residue, and rational number systems (Hwang, 1979)).

In a fixed-point representation, the weights are calculated in accordance with

$$w_i = \beta^{-i} \quad \forall i \in \{i_{\min}, \dots, i_{\max}\},\tag{2.3}$$

where  $\beta$  represents the radix (or base). In this thesis, a digit with index i is always associated with a weight  $\beta^{-i}$ . The digit of smallest weight is referred to as the least-significant digit, or LSD, and the digit of largest weight is referred to as the most-significant digit, or MSD.

In a floating-point representation, the number N is represented by a fixed-point mantissa m and a fixed-point exponent e such that  $N = m\beta^e$ . Part of the word is therefore reserved for m, and the other part is reserved for e.

This thesis is only concerned with fixed-point number representations. An important feature of such a representation is that a fixed-point number can always be multiplied by a power of the radix (scaled up) to yield an integer. A number system using weights in this way can thus be characterized by the radix  $\beta$  and the digit set D. The decimal number system ( $\beta = 10$  and  $D = \{0, ..., 9\}$ ) is the one humans use to learn to count and add, and the binary number system ( $\beta = 2$  and  $D = \{0, ..., 1\}$ ) is used by digital computers and other digital electronic devices.

Example 5 The radix of the decimal number system is 10, and the digit set is  $\{0, ..., 9\}$ . Consider the decimal number 25, which can represented by the decimal word  $025_{10}$ , where  $025_{10} = 0 \times 10^2 + 2 \times 10^1 + 5 \times 10^0$ . Consider now the binary number system: it has a radix 2, and a digit set  $\{0, ..., 1\}$ . The decimal number 5 can now be represented in the binary number system by  $11001_2$ , where  $1 \times 2^4 + 1 \times 2^3 + 0 \times 2^2 + 0 \times 2^1 + 1 \times 2^0 = 025_{10}$ .

#### Redundant Number Systems

A number system is said to be redundant when a given algebraic value can have several representations (Avizienis, 1961; Parhami, 1990; Kornerup, 1994).

**Example 6** The signed-binary (SB) number system has a radix 2, and a digit set  $\{\bar{1}, 0, 1\}$ , where  $\bar{1}$  represents -1. The decimal number 3 can then be represented either by  $011_2$ , where  $0 \times 2^2 + 1 \times 2^1 + 1 \times 2^0 = 3_{10}$ , or by  $10\bar{1}_2$ , where  $1 \times 2^2 + 0 \times 2^1 - 1 \times 2^0 = 3_{10}$ .

The key point with redundant number systems rests with the addition of two redundant words. In fact, when using redundant number systems it is possible to develop constant-delay architectures for addition In fact, if the result is expressed in a redundant number system, it is possible to stop the carry propagation, leading to constant-delay architectures for addition (Avizienis, 1961; Chow and Robertson, 1978; Parhami, 1990; Kornerup, 1994; Rao, 1996; Thornton, 1997).

Let us describe the conventional addition. One adds two digits at a given digit position, yielding a sum digit for that digit position and a carry. Then, one adds the carry to the digits of the next higher digit position, yielding a sum digit and a new carry, and so on. Let us now describe constant-delay addition in redundant number systems. At any digit position, the two digits are combined to yield a carry for the next higher digit position, regardless of the value of the carry generated at the previous lower digit position. Then, the remaining value is combined with the incoming carry, yielding a sum digit. This process is also referred to as weight-transfer decomposition. As a consequence, the carry is absorbed immediately, and does not ripple along the length of the input words, justifying the term constant-delay. Specific number representations have been developed to stop the carry propagation at fixed digit position intervals (Phatak and Koren, 1994).

For some number systems, two consecutive weight-transfer decompositions are required for addition as their digit set does not allow sufficient redundancy in the sum word. In this way, the addition process can still be referred to as either constant-delay, or limited-carry, since the carry is absorbed after two digit positions instead of one. This is the case for the signed-binary number system (Avizienis, 1961; Parhami, 1990; Kornerup, 1994). The performances of the architectures and corresponding hardware implementations developed in this thesis rely greatly on this constant-delay property.

## 2.2.3 Similarities Between Addition Schemes in Generalized Signed-Digit Number Systems

Generalized signed-digit (GSD) number systems were formally introduced in (Parhami, 1990). They are radix- $\beta$  number systems having a digit set of the form  $\{-\eta_-, \ldots, \eta_+\}$ , where  $\eta_- \geq 0$ , where  $\eta_+ \geq 0$ , and where  $\eta_+ + \eta_- + 1 > \beta$ . These number systems are redundant, and were proven to allow constant-delay addition (Parhami, 1990). In the following, a relationship between GSD number systems is introduced to prove that their addition mechanisms are very similar. The exploitation of these similarities results in substantial design time savings by using architecture re-use.

#### Relationships Between GSD Number Systems

A subset of GSD number systems, ordinary signed-digit (OSD) number systems, was also introduced in (Parhami, 1990). Their digit set is balanced, i.e.  $\eta_{+} = \eta_{-} \stackrel{\triangle}{=} \eta$ , leading to the added advantage that if x belongs to the digit set  $\{-\eta, -\eta + 1, \dots, \eta - 1, \eta\}$ , then -x belongs to the same digit set. Unless otherwise stated, this thesis is concerned with OSD number systems only. Often,  $\eta$  is constrained as follows

$$\left\lceil \frac{\beta}{2} \right\rceil \le \eta \le \beta - 1,\tag{2.4}$$

where the lower bound is required in order for the corresponding number system to be complete and redundant (Kornerup, 1994), whereas the upper bound is required for the representation of 0 in the corresponding number system to be unique.

Let us introduce unbalanced signed-digit (USD) number systems, where one can choose  $\eta_{+} = \eta_{-} + 1 \stackrel{\triangle}{=} \eta$ . One could have equivalently chosen  $\eta_{-} = \eta_{+} + 1$ . Similarly, one can

constrain  $\eta$  as follows

$$\left\lfloor \frac{\beta}{2} \right\rfloor + 1 \le \eta \le \beta - 1. \tag{2.5}$$

As shown in the following, any GSD number system can be related to a unique OSD/USD number system, and thus inherits the same addition mechanisms. This property is at the heart of various techniques for limiting the carry propagation in arithmetic operations (referred to as "tricks of the trade" in (Kornerup, 1994)).

Let us define the addition of two sets in accordance with

$$S_1 + S_2 = \{a \text{ such that } a = a_1 + a_2, \text{ where } a_1 \in S_1 \text{ and } a_2 \in S_2\},$$

(2.6)

and the multiplication of a set by a scalar in accordance with

$$n \times S = \{y \text{ such that } y = n \times x, \text{ where } x \in S\}.$$

(2.7)

Let us give an example:

$$\{1,4\} \dotplus \{0,3\} = \{1,4,7\},$$

(2.8)

and

$$3 \times \{1,4\} = \{3,12\}.$$

(2.9)

The relationship R between two GSD number systems can now be defined as follows:

**Definition 7** Denote by  $T_{\epsilon,\Delta}$  a digit set transformation such that

$$T_{\epsilon,\Delta}$$

:  $D \in \Sigma \mapsto (\epsilon \times D + \{\Delta\}) \in \Sigma$ ,

where  $\Sigma$  represents  $\{D = \{-\eta_-, \dots, \eta_+\} | (\eta_-, \eta_+) \in \mathbb{N}^{*2} \}$ . Then, consider a radix- $\beta$  GSD number system NS of digit set  $D = \{-\eta_-, \dots, \eta_+\}$ , and another radix- $\beta$  GSD number system NS' of digit set  $D' = \{-\eta'_-, \dots, \eta'_+\}$  such that  $\eta'_+ + \eta'_- + 1 = \eta_+ + \eta_- + 1$ . NS is related through  $\mathcal{R}$  to NS' if and only if there exist  $\epsilon \in \{-1,1\}$  and  $\Delta \in \mathbb{Z}$  such that  $D' = T_{\epsilon,\Delta}(D)$ . This relationship is equivalently denoted by NSRNS'.

It can be noted that the reverse transformation  $T_{\epsilon,\Delta}^{-1}$  exists, and that

$$T_{\epsilon,\Delta}^{-1} = T_{\epsilon,-\epsilon\Delta}.\tag{2.10}$$

It can be proven that R is an equivalence relationship, i.e. that R is reflexive, symmetric, and transitive.

Let us denote the cardinality of a set S by |S|. There are two types of GSD number systems: those for which |D| is odd, and those for which |D| is even (referred to as odd and even GSD number systems, respectively).

**Theorem 8** Any odd GSD number system is related through R to a unique OSD number system, and any even GSD number system is related through R to a unique USD number system.

**Proof.** The proof of the theorem consists of two parts, the first for odd GSD number systems, and the second for even GSD number systems.

Let us consider an odd GSD number system GSDNS of digit set D = {-η<sub>-</sub>,...,η<sub>+</sub>}.

A necessary condition for an OSD number system OSDNS of digit set D' = {-η,...,η} to be related through R to GSDNS is expressed by

$$|T_{\epsilon,\Delta}(D)| = |D'|, \tag{2.11}$$

which implies that

$$\eta + \eta + 1 = \eta_{+} + \eta_{-} + 1 \quad \Leftrightarrow \quad \eta = \frac{\eta_{-} + \eta_{+}}{2},$$

(2.12)

with  $\eta$  being a positive integer (because GSDNS is odd). Therefore, only one unique OSD number system can be related to GSDNS. Let us prove that GSDNS is related through  $\mathcal{R}$  to OSDNS. If one chooses  $\epsilon = -1$ , then  $\Delta = \eta_+ - \eta$  leading to

$$T_{\epsilon,\Delta}(D) = -\{-\eta_-, \dots, \eta_+\} + \{\eta_+ - \eta\}$$

(2.13)

$$= \{-\eta_+, \dots, \eta_-\} + \{\eta_+ - \eta\}$$

(2.14)

$$= \{0, \dots, \eta_{+} + \eta_{-}\} + \{-\eta\}$$

(2.15)

$$= \{0, \dots, 2\eta\} + \{-\eta\} \tag{2.16}$$

$$= \{-\eta, \dots, \eta\} \tag{2.17}$$

$$=D'. (2.18)$$

Therefore,  $GSDNS \mathcal{R} OSDNS$ . Similarly, one can prove that  $\epsilon = 1$  and  $\Delta = \eta_- - \eta$  implying that  $GSDNS \mathcal{R} OSDNS$ . Consequently,  $GSDNS \mathcal{R} OSDNS$ , where OSDNS is unique.

• Let us consider an even GSD number system GSDNS of digit set  $D = \{-\eta_-, \ldots, \eta_+\}$ . Similar to the previous discussion, a necessary condition for a USD number system USDNS of digit set  $D' = \{-\eta + 1, \ldots, \eta\}$  to be related by  $\mathcal{R}$  to GSDNS is expressed by

$$\eta + \eta - 1 + 1 = \eta_{+} + \eta_{-} + 1 \quad \Leftrightarrow \quad \eta = \frac{\eta_{-} + \eta_{+} + 1}{2},$$

(2.19)

with  $\eta$  being a positive integer (because GSDNS is even). Therefore, only one unique USD number system can be related to GSDNS. Let us prove that GSDNS is related through  $\mathcal{R}$  to USDNS. If one chooses  $\epsilon = -1$ , then  $\Delta = \eta_+ - \eta + 1$  leading to

$$T_{\epsilon,\Delta}(D) = -\{-\eta_-, \dots, \eta_+\} + \{\eta_+ - \eta + 1\}$$

(2.20)

$$= \{-\eta_+, \dots, \eta_-\} + \{\eta_+ - \eta + 1\} \tag{2.21}$$

$$= \{0, \dots, \eta_+ + \eta_-\} + \{-\eta + 1\}$$

(2.22)

$$= \{0, \dots, 2\eta - 1\} + \{-\eta + 1\} \tag{2.23}$$

$$= \{-\eta + 1, \dots, \eta\} \tag{2.24}$$

$$=D'. (2.25)$$

Therefore, GSDNS  $\mathcal{R}$  USDNS. Similarly, one can prove that  $\epsilon=1$  and  $\Delta=\eta_--\eta+1$  implying that GSDNS  $\mathcal{R}$  USDNS. Consequently, GSDNS  $\mathcal{R}$  USDNS, where USDNS is unique.

The above two bulleted points establish the proof.

Theorem 8 implies that by assigning the same hardware code to an element of D and to its counterpart in D' via  $T_{\epsilon,\Delta}$ , the addition of two numbers expressed in these two different number systems can be performed by using the same architecture. Moreover, all the GSD number systems of a given class shares the addition mechanisms of a unique corresponding OSD or USD number system. Therefore, a lot of design time can be saved by considering these similarities in the internal addition mechanisms in GSD number systems.

An application of this theorem will be given in Section 2.4, where addition schemes will be characterized in the binary case leading to architectural similarities. Numerous studies of the properties of OSD number systems can now be applied to odd GSD number systems (Chow and Robertson, 1978; Irwin and Owens, 1987; Irwin and Owens, 1988; Parhami, 1988; Srinivas and Parhi, 1983; Thornton, 1997).

## 2.3 Data Processing Techniques

This section is concerned with the presentation of the digit-serial and the online arithmetic techniques as data processing methods. The former technique permits the processing of "several" digits at a time, from one to the full wordlength. An extension of the digit-serial technique to a dynamically changing wordlength situation is also introduced. The latter technique permits the processing of data the MSD first. An introduction to the approaches to the development of resulting arithmetic operations is given, followed by an example.

## 2.3.1 Digit-Serial Arithmetic Technique

The bit-serial arithmetic technique processes a digital signal one digit at a time, whereas the bit-parallel arithmetic technique processes it one word of length W at a time. The bit-serial technique is area-efficient because only one wire and one single-digit arithmetic unit are required to process the input data. Conversely, a bit-parallel transmission requires W wires and W single-digit arithmetic units, but allows the design of faster architectures by introducing as much concurrency between the internal operations as possible.

The digit-serial arithmetic technique processes words D digits per time instant, where the digit-size D may or may not be a divisor of W. The bit-serial and bit-parallel arithmetic are special cases of the digit-serial arithmetic technique for digit-sizes of 1 and W, respectively. Therefore, this technique allows a trade-off between the area-efficiency of bit-serial systems and the time-efficiency of bit-parallel systems by adjusting the parameter D.

#### Digit-Serial Unfolding Algorithm

Any bit-serial architecture can be represented by combinatorial units, unit-delays, switches, and wires. This representation can be translated into a data-flow graph, which is a directed

graph whose nodes represent combinatorial units, and whose arcs represent either communication involving a non-negative integer number of delays or zero-delay communication at specific time instances. The digit-serial unfolding algorithm (Parhi, 1991) transforms a data-flow graph DFG of a bit-serial architecture into its corresponding unfolded data-flow graph UDFG of digit-size D, processing D bits of the original bit-serial stream at a time, where D may or may not be a divisor of W.

An arc is denoted by  $U \to V$ , where node U represents its source, and where node V represents its destination. If the arc introduces i delays, then the result of node U obtained at time instant  $n_0$  is used at time instant  $n_0 + i$  in node V. If the arc provides zero-delay communication at a specific time instance, then the time instance is given by Ww + u, where W represents the wordlength of the bit-serial stream, where u belongs to the set  $\{0, 1, \ldots, W-1\}$ , and where w represents the word number in the bit-serial stream.

Let us denote L as the least common multiple of W and D. The digit-serial unfolding algorithm below was presented in (Parhi, 1991).

## Algorithm 9 Digit-Serial Unfolding Algorithm

- Step 1. For each node U in DFG, draw D nodes in UDFG, and label them  $U_0, \ldots, U_{D-1}$ .

- Step 2. For each arc  $U \to V$  in DFG having 0 delay, draw the arcs  $U_q \to V_q$  with 0 delay for all  $q \in \{0, \ldots, D-1\}$ .

- Step 3. For each arc  $U \rightarrow V$  in DFG having i delays,

- Step 3a). If 0 < i < D, draw the arcs  $U_{D-i+q} \rightarrow V_q$  with 1 delay for all  $q \in \{0,1,\ldots,i-1\}$ , and draw the arcs  $U_{q-i} \rightarrow V_q$  with 0 delay for  $q \in \{i,i+1,\ldots,D-1\}$ .

- Step 3b). If  $i \geq D$ , draw the arcs  $U_{q-i+D\left\lceil \frac{q-i}{D}\right\rceil} \to V_q$  with  $\left\lceil \frac{i-q}{D}\right\rceil$  delay(s) for all  $q \in \{0,1,\ldots,D-1\}$ .

- Step 4. For each switch  $U \to S$  having a switching instance Wl + u, calculate the bit-serial switching instance as Ll + u + wW, where  $w \in \{0, \dots, \frac{L}{W} 1\}$ , and where the corresponding digit-serial switching instance  $U_{(u+wW) \bmod D}$  are calculated as  $\frac{L}{D}l + \lfloor \frac{u+wW}{D} \rfloor$ ,  $\forall w \in \{0, \dots, \frac{L}{W} 1\}$ .

Then, the following algorithm is a modification of Algorithm 9.

## Algorithm 10 Modified Digit-Serial Unfolding Algorithm

- Step 1'. For each node U in DFG, draw D nodes in UDFG, and label them  $U_0, \ldots, U_{D-1}$ .

- Step 2'. For each arc  $U \to V$  in DFG having i delays, draw the arcs  $U_{(q-i) \bmod D} \to V_q$  with  $\left\lceil \frac{i-q}{D} \right\rceil$  delay(s) for all  $q \in \{0, \dots, D-1\}$ .

- Step 3'. For each switch  $U \to S$  having a switching instance Wl + u, calculate the bit-serial switching instance as Ll + u + wW, where  $w \in \{0, \dots, \frac{L}{W} 1\}$ , and where the corresponding digit-serial switching instance  $U_{(u+wW) \bmod D}$  are calculated as  $\frac{L}{D}l + \lfloor \frac{u+wW}{D} \rfloor$ ,  $\forall w \in \{0, \dots, \frac{L}{W} 1\}$ .

**Theorem 11** Algorithm 9 and Algorithm 10 perform the same data-flow graph unfolding operation.

**Proof.** One can remark that Steps 1' and 3' of Algorithm 10 correspond exactly to Steps 1 and 4 of Algorithm 9, respectively. Therefore, one has to prove that Step 2' in Algorithm 10 performs the operations of Steps 2, 3(a) and 3(b) in Algorithm 9. This is achieved by successively considering the cases i = 0, 0 < i < D, and  $i \ge D$ .

• Let us assume that i = 0, as in Step 2. One can readily observe that for q in  $\{0, \ldots, D-1\}$ ,

$$(q-i) \mod D = q$$

and  $\left\lceil \frac{i-q}{D} \right\rceil = 0$  (2.26)

hold. Therefore, for all q in  $\{0, \ldots, D-1\}$ , one arc  $U_q \to V_q$  is drawn with 0 delays, which is the definition of Step 2: Step 2' and Step 2 are equivalent.

- Let us assume that 0 < i < D, as in Step 3(a). Then, q belongs either to  $\{0, \ldots, i-1\}$  or to  $\{i, \ldots, D-1\}$ .

- Let us consider  $q \in \{0, \ldots, i-1\}$ , which implies that

$$(q-i) \bmod D = (D-i+q) \bmod D, \tag{2.27}$$

or equivalently

$$(q-i) \bmod D = D - i + q, \tag{2.28}$$

because

$$D - i \le D - i + q \le D - 1, \tag{2.29}$$

where D - i > 0. Moreover,

$$\left\lceil \frac{1}{D} \right\rceil \le \left\lceil \frac{i-q}{D} \right\rceil \le \left\lceil \frac{i}{D} \right\rceil \tag{2.30}$$

holds, which yields

$$\left\lceil \frac{i-q}{D} \right\rceil = 1. \tag{2.31}$$

In this case, Step 2' draws the arcs  $U_{D-i+q} \to V_q$  with 1 delay for all q in  $[0, \ldots, i-1]$ . Therefore, for 0 < i < D and  $q \in [0, i-1]$ , Step 2' and Step 3(a) are equivalent.

- Let us consider  $q \in \{i, \ldots, D-1\}$ , which implies that

$$(q-i) \bmod D = q-i. \tag{2.32}$$

Moreover,

$$\left\lceil \frac{i-D+1}{D} \right\rceil \le \left\lceil \frac{i-q}{D} \right\rceil \le \left\lceil \frac{0}{D} \right\rceil \tag{2.33}$$

holds, yielding

$$\left[\frac{i-q}{D}\right] = 0, (2.34)$$

because

$$\left\lceil \frac{i-D+1}{D} \right\rceil = \left\lceil \frac{i+1}{D} \right\rceil - 1, \tag{2.35}$$

where  $\lceil \frac{i+1}{D} \rceil = 1$ . In this case, Step 2' draws the arcs  $U_{q-i} \to V_q$  with 0 delay for all q in  $\{i, \ldots, D-1\}$ . Therefore, for 0 < i < D, Step 2' and Step 3(a) are also equivalent when  $q \in \{i, \ldots, D-1\}$ .

From these two points, 0 < i < D implies that Step 3(a) and Step 2' are equivalent.

• Let us now assume that  $i \ge D$ . Firstly, one has to prove that Step 2' and Step 3(b) create the same arcs. By recalling the definition of the modulo operation,

$$a \mod b = a - b \left\lfloor \frac{a}{b} \right\rfloor,$$

(2.36)

one can write

$$(q-i) \bmod D = q-i-D\left[\frac{q-i}{D}\right], \tag{2.37}$$

which becomes

$$(q-i) \bmod D = q-i+D\left\lceil \frac{i-q}{D}\right\rceil. \tag{2.38}$$

Therefore, Step 2' creates the arcs  $U_{q-i+D\left\lceil\frac{i-q}{D}\right\rceil} \to V_q$  for  $q \in \{0, \ldots, D-1\}$ , which is the definition of the creation of the arcs in Step 3(b). Secondly, each arc created by using Step 2' must be shown to have the same number of delays than if created by Step 3(b), which holds immediately. Therefore, for  $i \geq D$ , Step 2' and Step 3(b) are equivalent.

These above three bulleted cases establish the proof.

As a result of Theorem 11, digit-serial unfolding can be performed by using Algorithm 10, thereby avoiding the multiple delay-based cases for the instantiation of arcs.

Theorem 12 One can write Step 2' equivalently as follows: for each arc  $U \to V$  in DFG having i delays, draw the arcs  $U_{q'} \to V_{(q'+i) \bmod D}$  with  $\left\lfloor \frac{q'+i}{D} \right\rfloor$  delay(s) for all  $q' \in \{0, \ldots, D-1\}$ .

**Proof.** The proof is established by proving that, given i in  $\mathbb{N}$ , and given q' in  $\{0, \ldots, D-1\}$ , any arc  $U_{q'} \to V_{(q'+i) \bmod D}$  with  $\left\lfloor \frac{q'+i}{D} \right\rfloor$  delay(s) is the same arc as  $U_{(q-i) \bmod D} \to V_q$  with  $\left\lceil \frac{i-q}{D} \right\rceil = \left\lfloor \frac{q'+i}{D} \right\rfloor$  delay(s), where  $q = (q'+i) \bmod D$ .

Given i in N, and given q' in  $\{0, \ldots, D-1\}$ , defining

$$q = (q' + i) \bmod D \tag{2.39}$$

implies that

$$(q-i) \bmod D = ((q'+i) \bmod D - i) \bmod D \tag{2.40}$$

$$= (q' + i - i) \bmod D \tag{2.41}$$

$$= q' \bmod D \tag{2.42}$$

$$=q', (2.43)$$

because  $q' \in \{0, \ldots, D-1\}$ . Of course,  $q \in \{0, \ldots, D-1\}$  by definition. Therefore,  $U_{q'} \to V_{(q'+i) \mod D}$  is the same arc as  $U_{(q-i) \mod D} \to V_q$  when q is defined in accordance with Eqn. 2.39.

One has to prove that if i belongs to N, and if q' belongs to  $\{0, \ldots, D-1\}$ , then

$$\left\lceil \frac{i-q}{D} \right\rceil = \left\lfloor \frac{q'+i}{D} \right\rfloor. \tag{2.44}$$

Firstly, by definition of the modulo operation, one can write

$$q = q' + i - D \left\lfloor \frac{q' + i}{D} \right\rfloor. \tag{2.45}$$

From Eqn. 2.43 and by modulo operation,

$$q' = q - i - D \left\lfloor \frac{q - i}{D} \right\rfloor. \tag{2.46}$$

By adding Eqns. 2.45 and 2.46, and by recalling that  $-\lfloor a \rfloor = \lceil -a \rceil$ , one obtains

$$q' + q = q + q' - i + i + D\left(\left\lceil \frac{i - q}{D} \right\rceil - \left\lfloor \frac{q' + i}{D} \right\rfloor\right), \tag{2.47}$$

which readily leads to

$$\left|\frac{q'+i}{D}\right| = \left\lceil\frac{i-q}{D}\right\rceil. \tag{2.48}$$