# **High Mobility MIS Interfaces with Wide Bandgap Semiconductors**

# Eric Milburn

A thesis submitted in partial fulfillment of the requirements for the degree of

Masters of Science

in

Microsystems and Nanodevices

Department of Electrical and Computer Engineering

University of Alberta

#### Abstract

As communications technologies continue to grow, the role of gallium nitride (GaN) transistors for high-frequency applications continues to grow as the speed requirements of more and more applications exceed the abilities of silicon. Today the vast majority of commercial GaN devices use HEMT architectures which are far more complicated to manufacture and have inferior offstate performance in comparison to standard MOSFET architecture. The primary cause for this is the lack of dielectric materials capable of forming an interface with GaN that does not dramatically degrade carrier mobility due to interface traps. In this research I demonstrate that atomic layer deposited (ALD) silicon nitride (SiN) forms an interface with GaN that bypasses any deleterious effects of interface traps and allows for high mobility of carriers within a simple three-layer MOSCAP device. The GaN-SiN-ruthenium system used in these MOSCAPs is analyzed through materials and electronic characterization to describe the chemical makeup and band structure of the system. These findings suggest a promising path of research for developing architecturally simple lateral GaN MOSFETs with speeds comparable to commercial HEMTs with superior off-state performance.

# **Preface**

I, Eric Milburn, am the principal contributor to all chapters of this thesis. Chapter 4 of this thesis is based substantially off of Conference Proceeding #1.

Triratna Muneshwar and Alex Ma assisted with the deposition of all ruthenium contacts and SiN ALD films in throughout Chapters 4 and 5.

# Conference Proceedings Resulting from This Thesis Work

Plasma Enhanced Atomic Layer Deposited Silicon Nitride on GaN MISCAPs with High Charge and Mobility, CS Mantech 2020 Digital Digest.

## Acknowledgements

One of the greatest lessons I learned in undertaking this research was the value of great advisors, mentors, collaborators, and supporters. I have been incredibly lucky to have had many amazing people fill these roles around me, and they have made the experience all the richer.

My gratitude to my supervisor Doug Barlage is immeasurable. His willingness to answer my endless stream of questions made the transition from a Materials Engineering undergraduate degree to an Electrical Engineering Masters program seamless. Under his mentorship I have watched myself develop from someone who was simply looking for an interesting research topic into a truly confident researcher with a strong understanding of the limits of knowledge and how they can be pushed.

Without the help of my colleagues my research would not have progressed nearly as far as it did. Alex Ma's experience with lithography and etching processes, Triratna Muneshwar's expertise in ALD, Ken Cadien for his ALD lab (which provided the SiN films which were a cornerstone of this research), and Gem Shoute's help with data analysis and modelling were all invaluable to this thesis. An honorable mention is also mandatory for the staff in Nanofab, whose friendliness and endless knowledgeability have allowed me to attain a high level of proficiency in a vast array of fabrication techniques.

I owe eternal thanks to my friends and family for all their support, which during the tumultuous months during which this thesis was completed kept me grounded and focused when the world was bleak. My mother, father, and sister's endless curiosity in my work forced me to understand it better myself, and inspired me to continue asking the hard questions of my findings. Finally, to my love Lindsay, the welcoming set of arms there for me at the end of every day, and the set of eyes that meticulously proofread everything within these pages, I am perpetually grateful.

# **Table of Contents**

| 1 – Wide Bandgap Semiconductors: Foundation of Future Electronics |    |

|-------------------------------------------------------------------|----|

| 1.0 – The Wide Bandgap Advantage                                  | 1  |

| 1.1 – Wide Bandgap Semiconductor Materials Throughout History     | 4  |

| 1.2 – State of the Art Wide Bandgap Technology                    | 6  |

| 2 – Theory of Interfaces in MIS Structures                        | 10 |

| 2.0 – Structural Considerations                                   | 10 |

| 2.0.0 – Interface Topography                                      | 10 |

| 2.0.1 – Interfacial Stress and Strain                             | 11 |

| 2.1 – Electronic Considerations                                   | 12 |

| 2.1.0 – Band Structure                                            | 12 |

| 2.1.1 – Interface States and Traps                                | 14 |

| 2.1.2 – Interface Polarization and Band Bending                   | 15 |

| 3 – Fabrication and Materials Characterization of MIS Structures  | 16 |

| 3.0 – Sputtering of Metals                                        | 16 |

| 3.1 – Atomic Layer Deposition                                     | 16 |

| 3.1.0 – Deposition process                                        | 16 |

| 3.1.1 – Plasma Enhanced ALD                                       | 16 |

| 3.1.2 – Film Thickness Monitoring                                 | 18 |

| 3.2 – Lift-Off Processing                                         | 19 |

| 3.3 – Characterization                                            | 19 |

| 3.3.0 – Atomic Force Microscopy                                   | 19 |

| 3.3.1 – X-Ray Photoelectron Spectroscopy                          | 20 |

| 4 - Oxide-Semiconductor Interfaces in Crystalline GaN MISCAPs     | 23 |

| 4.0 - Device Fabrication and Physical Characterization            | 23 |

| 4.1 – Electronic Characterization                                 | 27 |

| 4.2 – Extraction of Capacitance Density and Effective Mobility    | 43 |

| 5 – GaN MISFETs with SiON Gate Dielectrics                        | 52 |

| 5.0 – Device Fabrication                                          | 52 |

| 5.1 – Mobility Analysis Theory                                    | 54 |

| 5.2 – Mobility Analysis                                           | 55 |

| 6 – Conclusions and Future Work                                   | 58 |

| 6.0 – Conclusions                                                 | 58 |

| 6.1 – Future Work                                                 | 59 |

| Appendix B: CV Data and Comparison of Leakage Current                                 | 7( |

|---------------------------------------------------------------------------------------|----|

| Appendix A: JV Data                                                                   | 69 |

| References                                                                            | 61 |

| 6.1.3 – Investigation of Role of Ga <sub>2</sub> O <sub>3</sub> in GaN MIS Interfaces | 60 |

| 6.1.2 – Improvement of ALD SiN Films                                                  | 60 |

| 6.1.1 - Optimization of Contacts to Semi-Insulating GaN                               | 59 |

| 6.1.0 – Conversion of Highly Doped Wafers to Semi-Insulating GaN                      | 59 |

# **List of Figures and Tables**

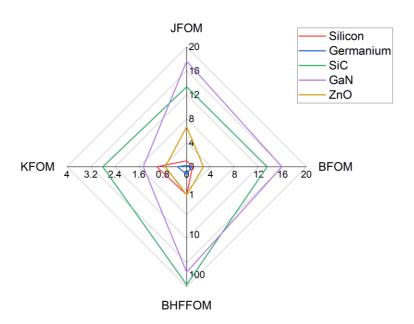

| <b>Figure 1.1</b> – Comparison of common Figures of Merit for various semiconductors                                       | 2  |

|----------------------------------------------------------------------------------------------------------------------------|----|

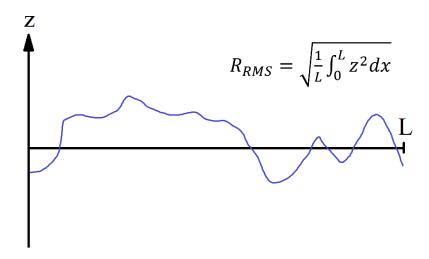

| Figure 2.1 – Representation of RMS roughness.                                                                              | 11 |

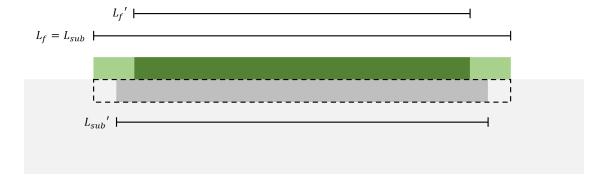

| Figure 2.2 – Visualization of basic thermal contraction strain for the case where $\alpha_f > \alpha_{sub}$                | 12 |

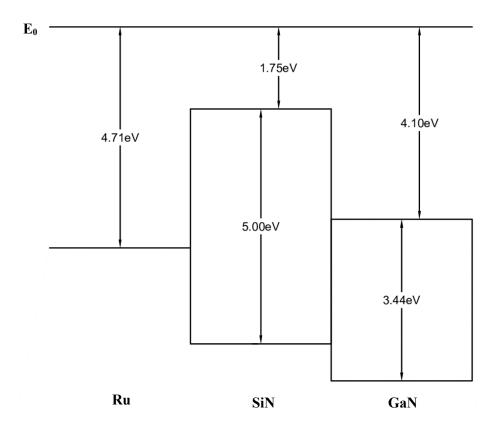

| Figure 2.3 – Theoretical band diagram of a Ru-SiN-GaN MISCAP under flat-band conditions                                    | 13 |

| Figure 2.4 – Modified band diagram including Fermi level pinning from interface traps                                      | 14 |

| Figure 2.5 – Polarization induced band bending at an AlGaN/GaN interface                                                   | 15 |

| Figure 3.1 – Circuit representation of ICP discharge source                                                                | 17 |

| Figure 3.2 – Schematic of AFM mode of operation                                                                            | 19 |

| Figure 3.3 – Schematic from Zhao et al. showing the energy levels associated with measuring                                |    |

| band bending                                                                                                               | 21 |

| Figure 3.4 – Position of VBM from XPS data                                                                                 | 21 |

| Figure 4.1 – Process flow for fabrication of SiN/GaN MISCAPs                                                               | 24 |

| Figure 4.2 – AFM images of a.) SiN and b.) ruthenium film topography.                                                      | 25 |

| Figure 4.3 – EXP Depth profiling of Kyma n <sup>+</sup> SiN/GaN MISCAPs                                                    | 26 |

| Figure 4.4 – Elemental XPS spectra for a.) gallium 2p3, b.) silicon 2p c.) silicon 2s d.) nitrogen                         |    |

| 1s and e.) oxygen 1s taken from Kyma n <sup>+</sup> SiN/GaN MISCAPs                                                        | 27 |

| Figure 4.5 – Fowler-Nordheim plots demonstrating the two most common slopes                                                | 30 |

| Figure 4.6 – Normalized capacitance-voltage plots for a.) 3 nm and b.) 5 nm SiON films                                     | 32 |

| Figure 4.7 – Capacitance vs. area plot for 3 nm and 5 nm films                                                             | 33 |

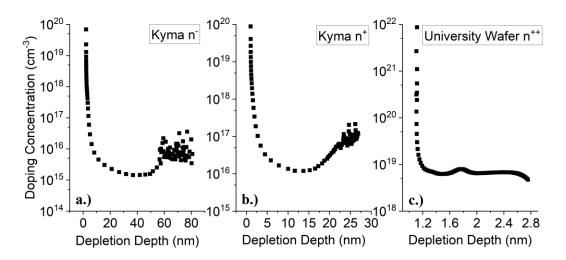

| Figure 4.8 – Extracted dopant density profiles from a.) Kyma n <sup>+</sup> , b.) Kyma n <sup>-</sup> , and c.) University |    |

| $n^{++}$ wafers                                                                                                            | 34 |

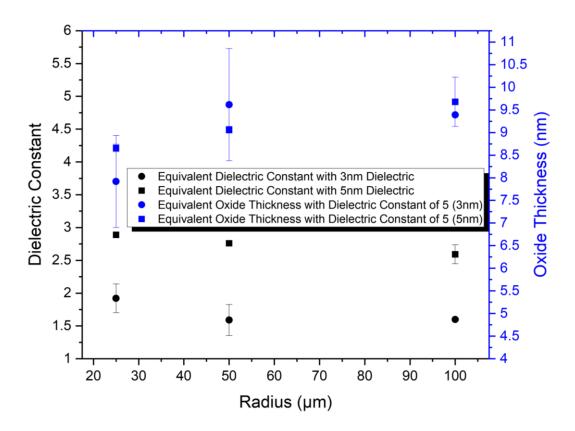

| Figure 4.9 – Dielectric constant assuming accurate dielectric thickness and dielectric thickness                           |    |

| assuming theoretical dielectric constant of SiON                                                                           | 36 |

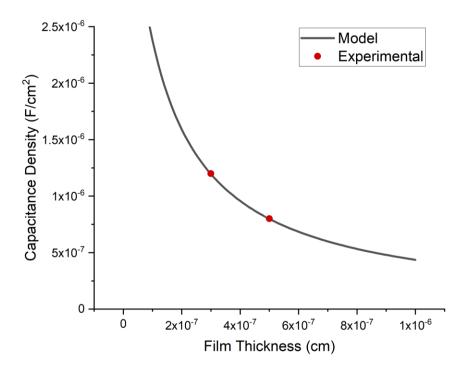

| Figure 4.10 - Fitted capacitance data based off series capacitance model                                                   | 37 |

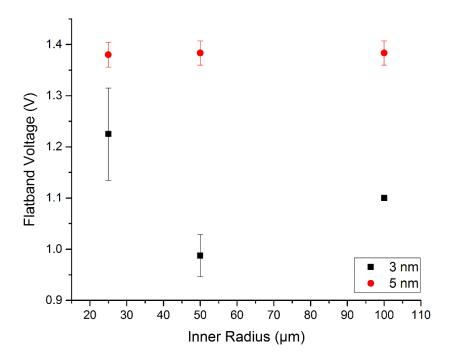

| Figure 4.11 – Change in flatband voltage with contact size                                                                 | 39 |

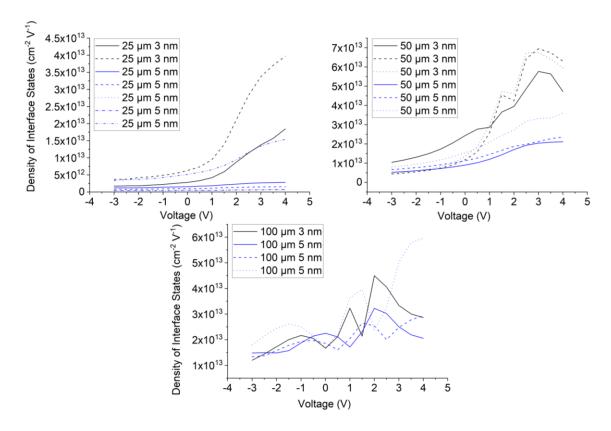

| Figure 4.12 – Trap density vs. voltage for each device size                                                                | 40 |

| Figure 4.13 – Correlation between frequency dependence of traps and frequency dependence of                                |    |

| capacitance for 3 nm and 5 nm devices                                                                                      | 41 |

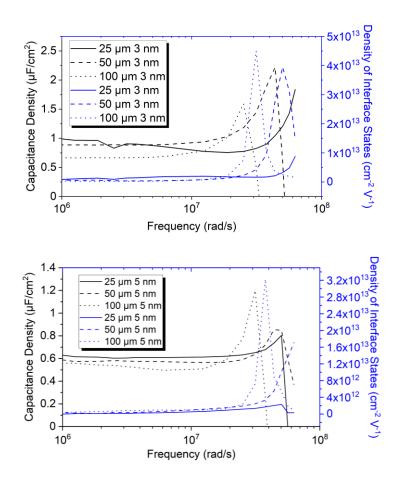

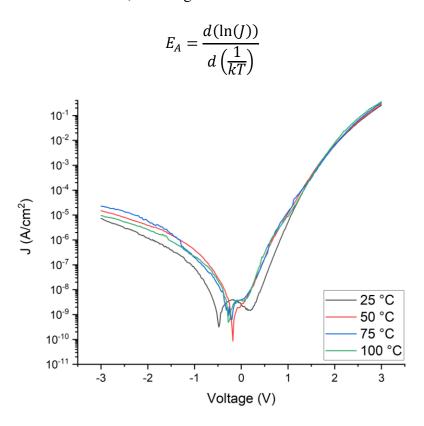

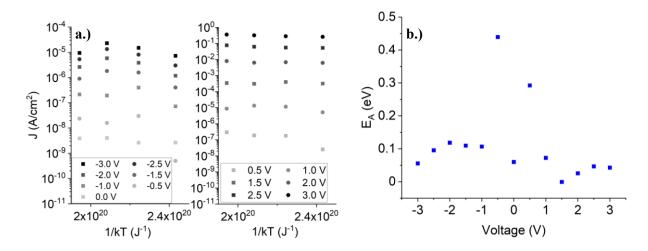

| Figure 4.14 – Change of IV characteristic with temperature for a 3 nm n <sup>++</sup> MISCAP.                              | 42 |

| Figure 4.15 – a.) Current vs. 1/kT in depletion and accumulation, b.) calculated activation                                |    |

| energy vs. bias voltage                                                                                                    | 43 |

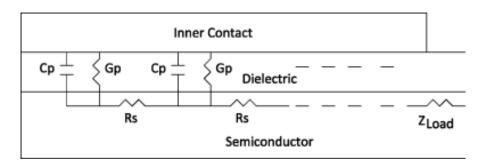

| Figure 4.16 – Distributed model of planar capacitor                                                                        | 44 |

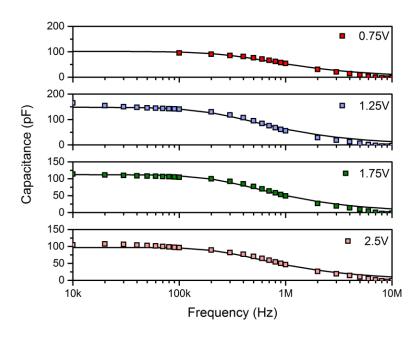

| Figure 4.17 - Cf curves fitted according to distributed model                                            | 44 |

|----------------------------------------------------------------------------------------------------------|----|

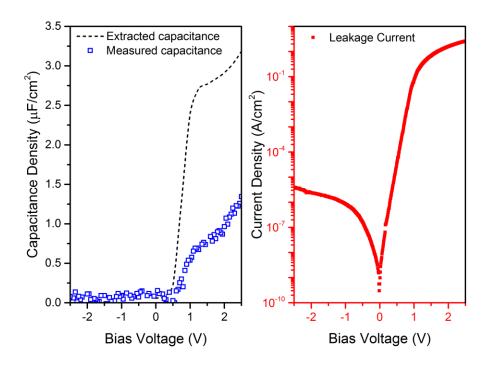

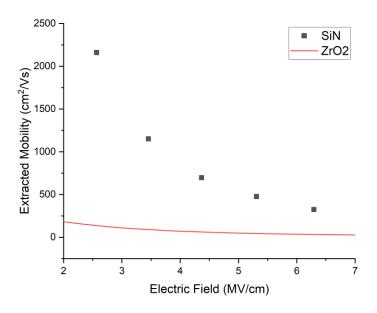

| Figure 4.18 – Extracted CV curve                                                                         | 45 |

| Figure 4.19 – Extracted effective mobility vs. electric field compared with values from ZrO <sub>2</sub> | 46 |

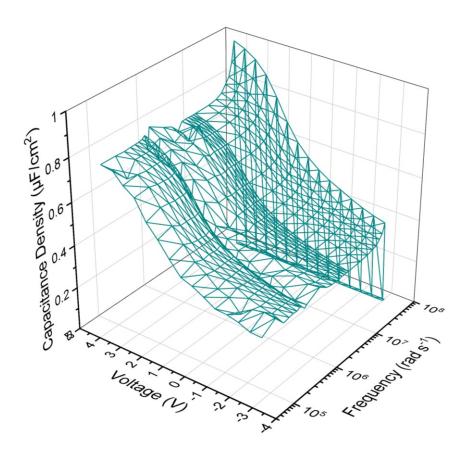

| Figure 4.20 – Capacitance-frequency curves for n <sup>++</sup> 5 nm MISCAPs at different voltages        | 47 |

| Figure 4.21 – Summary of GaN-SiON MISCAP structure including all experimentally                          |    |

| supported features                                                                                       | 48 |

| Figure 4.22 – Band diagram of GaN-SiON MISCAP including experimentally supported                         |    |

| features under flat-band conditions                                                                      | 49 |

| Figure 4.23 – Comparison of IV and CV curves for 3 nm SiON film 25 μm and 50 μm samples                  |    |

| with differing contact preparation, solid lines correspond to samples where the                          |    |

| breaking voltage was applied to the contact, dotted lines correspond to samples                          |    |

| where the contact was grounded                                                                           | 51 |

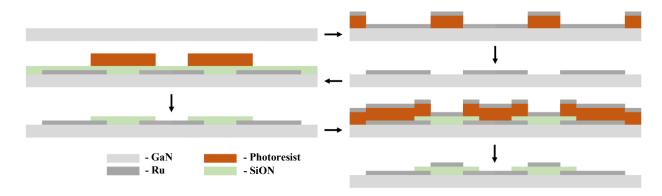

| Figure 5.1 – Process flow for fabrication of GaN-SiON MISFETs                                            |    |

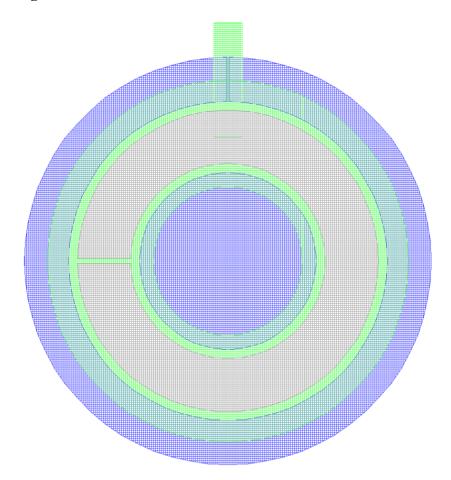

| Figure 5.2 – Top down schematic of MISFET. The ruthenium source/drain is given in blue, the              |    |

| SiON film is given in green, and the ruthenium gate is given in grey                                     | 53 |

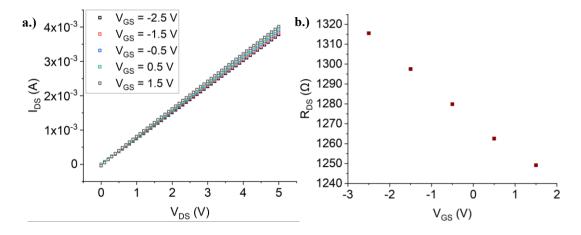

| Figure 5.3 – Variable resistor behaviour of MISFET under varying gate voltages                           | 55 |

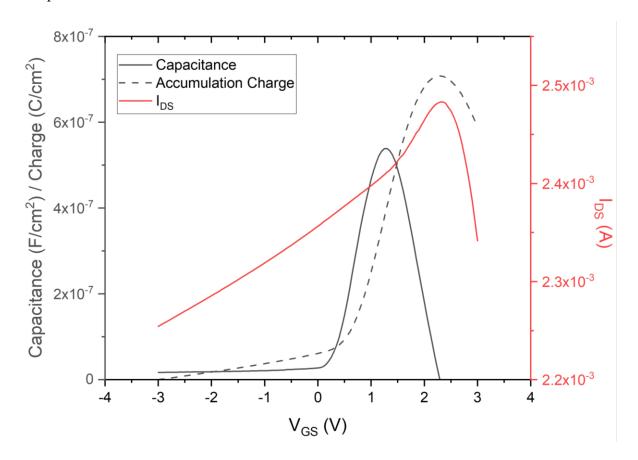

| Figure 5.4 – Comparison of the gate capacitance, gate charge, and channel current vs. gate               |    |

| voltage                                                                                                  | 56 |

|                                                                                                          |    |

| Table 1I – Summary of GaN and ZnO material Benchmarks                                                    | 9  |

| Table 4I – ALD parameters used for deposition of SiN films                                               |    |

| <b>Table 4II</b> – Processing steps for AZ5214E                                                          | 24 |

| Table 4III – Ruthenium sputtering parameters                                                             |    |

| <b>Table 4IV</b> – Three regimes of barrier heights with standard deviations                             |    |

| Table 4V – Fitted parameters from MISCAP capacitance model                                               |    |

| Table 5I – Process parameters for slow SiON anisotropic etch                                             | 52 |

| Table 5II – Results of MISFET mobility analysis.                                                         |    |

| Table 5III – Comparison with literature values                                                           | 57 |

# 1 - Wide Bandgap Semiconductors: Foundation of Future Electronics

### 1.0 – The Wide Bandgap Advantage

As the demands of modern semiconductor devices continue to drift upwards, the incumbent material of choice in nearly all spheres of electronics – silicon – has over the past 20 years begun to stagnate as physical limits restrict the size and performance of devices<sup>1</sup>. In extremely small devices such as complementary metal oxide semiconductor (CMOS) circuits, electric fields in the channel become high and the low critical field ( $E_c$ ) of silicon allows sub-threshold conduction through the channel. A similar challenge arises in high-frequency and high-power devices where high voltages – rather than small dimensions – are responsible for the high electric fields necessary to drive high frequency switching or high power outputs. With a small bandgap of 1.1 electron volts (eV), silicon inherently generates a relatively large concentration of intrinsic charge carriers, particularly at elevated temperatures, which can lead to high off currents and poor high temperature performance<sup>2</sup>. Low thermal conductivity exacerbates this issue, particularly in high-frequency devices where power dissipation generates heat that must be removed from the circuit, requiring extensive dedicated cooling systems to boost switching frequency.

In order to meet these challenges, wide bandgap semiconductors have been investigated since the middle of the  $20^{th}$  century as potential replacements for electronic components where smaller device footprint, higher frequency operation, higher power output, higher temperature operation, or any combination of these specifications are desired. Evaluation of an arbitrary semiconductor to perform well in these categories is typically achieved by aggregating the semiconductor's material properties into various figures of merit. For power applications, the Baliga Figure of Merit (BFOM) expresses the inherent tradeoff between a vertical power transistor's power usage (due to ON resistance  $r_{on}$ ) and the transistor's breakdown voltage ( $V_{bd}$ )<sup>3</sup>; materials that can minimize a transistor's power use while maximizing breakdown voltage have a high BFOM.

$$BFOM = \epsilon \cdot \mu \cdot E_g^3$$

The Johnson Figure of Merit (JFOM) expresses the product of two parameters relevant to high-frequency transistors, the critical electric field ( $E_c$ ) and the saturation velocity of carriers in the semiconductor<sup>4</sup> to evaluate theoretical switching speed limits.

$$JFOM = \frac{E_c \cdot v_s}{2\pi}$$

Another popular figure of merit for high-frequency switching applications is the Baliga High Frequency Figure of Merit (BHFFOM)<sup>5</sup>, which assigns a characteristic frequency (not to be mistaken for the true switching frequency limit<sup>6</sup>) to a given semiconductor.

$$BHFFOM = \mu \cdot E_c^2$$

Finally, a figure of merit that evaluates the suitability of a semiconductor for high frequency applications that also considers the material's ability to dissipate heat is the Keyes Figure of Merit  $(KFOM)^7$ , which includes the material's thermal conductivity  $(\Phi_k)$ .

$$KFOM = \lambda \cdot \sqrt{\frac{c \cdot v_s}{4\pi\epsilon}}$$

When comparing all figures of merit for several semiconductors and normalizing the results to silicon using values from literature<sup>8–17</sup> as shown in Figure 1.1, popular wide bandgap semiconductors 4H-SiC and GaN clearly outperform silicon in suitability for high-frequency and high-power applications, additionally ZnO, which is considerably less developed than SiC and GaN in high voltage electronics research can also be seen to show potential for similar application areas.

**Figure 1.1** – Comparison of common Figures of Merit for various semiconductors.

It is also worth noting that although the figures of merit described above provide a good rough guideline on the suitability of various semiconductors for use in high voltage applications, they are less useful in guiding the actual design of high-frequency and high-power devices<sup>6</sup>. Just as Dennard scaling drove the development of CMOS devices to achieve higher device densities and performance, more consequential device performance metrics have been proposed to drive the development of high voltage transistors. These parameters are the quality factor  $(Q_{F2})^{18}$ , the gate charge  $(Q_G)$ , and the maximum junction temperature between the device substrate and the packaging it is assembled with  $(T_{j,max})$ .  $Q_{j2}$  can be calculated from the device material's thermal conductivity  $(\lambda)$ , specific conductivity  $(\sigma)$ , and  $E_c$  while  $T_{j,max}$  can be calculated from the case temperature  $(T_c)$ , on current/resistance, and thermal resistance between the substrate and casing  $(R_{jc})$ .

$$Q_{f2} = \lambda \cdot \sigma_{sp,ON} \cdot E_c$$

$$T_{j,max} = T_c + I_{ON}^2 R_{ON} R_{jc}$$

The formulation for  $T_{j,max}$  demonstrates that devices with lower ON resistance will have lower device-case junction temperatures due to lower power dissipation ( $I_{ON}^2R_{ON}$ ), and that materials with strong thermal conductivity will have similar performance due to a decrease in  $R_{ic}$ .

In recent years, the motivation for development of wide bandgap semiconductor electronics has begun to shift away from prototyping and towards competitive commercial goals as wide bandgap devices begin to challenge traditional materials in power and radio frequency (RF) applications. As wide bandgap technologies mature, silicon based power devices are being replaced by 4H-SiC equivalents (market share projected as 27.3% by 2024)<sup>19,20</sup> while GaN RF devices are increasingly being used in favor of common GaAs components (market share projected as 7.5% by 2025)<sup>21,22</sup>. Several markets are responsible for the recent growth in the wide bandgap market, primarily energy and utility (power devices), communication technology and consumer electronics (RF, LEDs, and power devices), automotive technology (power devices) and aerospace/defense (RF, optical, and power devices<sup>23</sup>). As these markets adopt wide bandgap technologies – particularly with the advent of high frequency 5G cellular technology and electric vehicles (EVs) – the total wide bandgap market has increased from \$210M in 2015<sup>19</sup> to around \$600M in 2019 with a compound annual growth rate (CAGR) of ~30% and is expected to continue growing with an average CAGR of ~22% to nearly \$3B by 2027<sup>23</sup>.

#### 1.1 – Wide Bandgap Semiconductor Materials Throughout History

The history of wide bandgap semiconductor materials is diverse, ranging from ancient minerals that grew into electronic materials to space age inventions grown specifically for electronic uses. Of the popular wide bandgap semiconductors popular in research today (SiC, GaN, ZnO), the oldest is ZnO which occurs naturally as a white, powdery mineral that saw use in antiquity as a wound dressing, for skin treatment, and in the production of brass, paints, enamels, and rubbers. In 1890 the discovery of SiC crystals would be made by Edward Goodrich Acheson while passing a current through a graphite rod embedded in silica sand. Scaled up, this Acheson process<sup>24</sup> would be applied to the mass manufacture of SiC crystals for the abrasives industry. The early 1900s would see ZnO expand into new uses in cosmetics and pharmaceuticals<sup>25</sup>, meanwhile a relatively new field of scientists investigating the interaction of crystals with electricity would yield some of the most groundbreaking discoveries of the 20<sup>th</sup> century. In 1906 Henry Dunwoody would invent a crystal radio using SiC<sup>26</sup> and in 1907 English engineer Henry Joseph Round would inadvertently create the first reported light emitting diode<sup>27</sup> when he passed a current through a crystal of SiC and observed luminescence at the anode. That same year, American physicist George Pierce would conduct similar research, developing a SiC rectifier<sup>28</sup> which he would patent two years later<sup>29</sup>. These discoveries would kickstart scientific interest in SiC and its crystal properties, and in 1915 German mineralogist Heinrich Baumhauer would coin the term "polytypie" to refer to the various lattice stacking patterns, or polytypes displayed by SiC crystals<sup>30</sup>, polytypes of SiC would be found to have drastically different properties and would be investigated thoroughly later in the century. In 1931 James Bayard Parsons would synthesize the first GaN powder at the University of Chicago<sup>31</sup> by passing ammonia gas over liquid gallium (this technique would be repeated by Harry von Hahn at the University of Gdansk in 1940<sup>32</sup>). Compound semiconductor development would slow to a halt during World War II as focus shifted to more established technologies that could be rapidly developed for wartime technologies, however it is worth noting that SiC crystal radios saw heavy use during the war due to their resistance to interference from external vibration, ZnO also saw some use in the War as a component of zinc chloride smokescreen mixtures.

Interest in compound semiconductors would begin again in earnest in the 1950s. Research on the physical properties of GaN including conductivity<sup>33</sup>, dielectric constant<sup>34</sup>, magnetic susceptibility, band gap<sup>35</sup>, emission and photoluminescence<sup>36,37</sup>, and crystal parameters<sup>38</sup> would be conducted between 1956 and 1964. Fabrication technology for SiC would also receive a big boost in 1958

with the invention of the Lely sublimation method for SiC crystal formation<sup>39</sup>, developed by Jan Lely at Phillips. With higher quality material, the development of SiC devices was rapid, with the development of the first SiC bipolar junction transistor (BJT) in 1959 by Robert Hall at General Electric<sup>40</sup> and the first SiC FET at Westinghouse<sup>41</sup>. The interest in SiC around this time would be bookmarked in particular by the holding of the first International Conference on Silicon Carbide<sup>42</sup>, which featured sessions focused on the silicon-carbon binary system, crystal growth, crystal structure, solid-state physics, and SiC devices, and which featured esteemed presenters such as the aforementioned Robert Hall as well as William Shockley. In the frenzy of research on all semiconductors around this time it should come as no surprise that ZnO also saw heavy development, with research on optical, band, and transport properties being conducted starting in 1959 and stretching into the 1960s<sup>43-45</sup>. The early 1960's would also see developments in less prominent compound semiconductors with the development of the first intentionally designed optical spectrum LED by Nick Holonyak in 1962, which was made out of gallium arsenide and gallium phosphide and produced red light<sup>46</sup>. The late 1960s would see a number of further developments in LED technology, the first ZnO LED was built in 1967 and used copper (I) oxide as the p-type semiconductor of the junction<sup>47</sup>. In 1968 Herbert Maruska (who would later pioneer the use of Mg as a p-type dopant in GaN), would synthesize the first GaN crystals using halide vapor phase epitaxy while working at RCA labs<sup>48</sup>. These crystals had lower defect concentrations than those produced using previous processes and would result in the first GaN blue LEDs produced in 1971<sup>48</sup>. No significant milestones during this period would be achieved in SiC technology, although the material began to see use in UV detection systems<sup>49</sup>. So little work was being done on SiC that in 1982 the essay "Whatever Happened to SiC?" was published in IEEE Transactions<sup>50</sup>, lamenting the fact that interest in high temperature SiC devices had tapered off over the previous decades. This lack of interest was attributed to the advent of integrated circuits and the scaling race taking place in silicon technology, as well as difficulty in SiC fabrication and the conclusion of many government programs that had been aimed at the exploration of SiC technologies. However, SiC would see a resurgence in the late 1980s as interest in SiC FETs using the 3C and 6H polytypes would surge<sup>51-53</sup> and the search for the superior SiC polytype for electronics would commence. The 1980s would also see one of the most critical processes in the development of GaN in 1983 when metal organic chemical vapour deposition (MOCVD) (which

was pioneered in the early 1970s by Harold Manasevit<sup>54</sup>) would be used to create high purity GaN crystals that would serve as a basis for GaN development in the following decades.

The 1990s would mark the beginning of the modern age of wide bandgap transistor technology. Transistor technology using GaN would be spearheaded largely by M. Asif Khan at APA Optics of Infineon, with documented demonstrations of both metal semiconductor FETs (MESFETs )and heterojunction FETs (HFETs) in 1993<sup>55–57</sup>. The following year would see the first SiC MESFET using the 4H-SiC polytype<sup>58</sup> which has become the contemporary standard for all SiC commercial devices, as well as J. Bayant Baliga filing patent for the SiC vertical power MISFET<sup>59</sup>, an architecture that has driven a significant portion of SiC's modern market share in the power electronics industry. Work done in 1995 at Naval Research Labs would also yield the first work on GaN MISFETs, which used Si<sub>3</sub>N<sub>4</sub> as the gate dielectric<sup>60</sup>, integration of p-GaN would be achieved at Sandia National Lab in 2000 with the demonstration of a GaN junction FET (JFET)<sup>61</sup>. The first ZnO thin film transistors (TFTs) would be published in 2001<sup>62</sup>, giving new life to the ZnO field that had focused primarily on optoelectronic devices for the previous several decades. The remainder of the 2000s would be focused on refinement of new wide bandgap technologies, and further material studies on polytypes<sup>63</sup> and electronic architectures such as the integration of JFET structures into power MISFETs (aka the "Baliga Pair" and self-alignment techniques 65 would carry wide bandgap semiconductors to the current state-of-the-art.

#### 1.2 - State of the Art Wide Bandgap Technology

While silicon carbide continues to undergo considerable research, it is in general a more mature materials system than GaN and ZnO<sup>66</sup>. Several material properties pertaining to quality of semiconductor material, quality of semiconductor-oxide interfaces, and full device characteristics serve as good benchmarks to assess the current state-of-the-art with respect to GaN and ZnO material technologies.

When depositing wide bandgap semiconductors the primary factors that will affect material performance are the crystal quality and dopant activation fractions. Crystal quality is critical for ensuring the minimization of defects that can scatter charge carriers, lowering their mobility, as well as allowing for uniform distribution of electric potential throughout the material, maximizing

breakdown strength. Single crystal growth of GaN is relatively well explored, and various deposition methods have been developed for different applications. High nitrogen pressure solution growth (HNPS) produces the highest quality films with dislocation densities as low as 2.2x10<sup>2</sup> cm<sup>-2</sup>, however it is an extremely slow process, growing around 1 μm/h<sup>67</sup>. Ammonothermal growth and sodium-flux methods provide similar dislocation densities but also have very low growth rates<sup>67</sup>, leaving a need for methods of deposition for device grade (dislocation densities <10<sup>5</sup> cm<sup>-2</sup>) GaN at more scalable deposition rates. Deposition of ZnO is still a highly debated area of research, and no one technology has emerged as dominant for producing high quality ZnO; among current research approaches which include epitaxial growth, sputtering methods, and solution processing, the current benchmark for dislocation density in ZnO comes from a deposition technology that hasn't traditionally been known for crystallinity: atomic layer deposition (ALD). Paired with rapid thermal annealing (RTA), ALD ZnO has reached dislocation densities as low as 5.2x109 cm<sup>-2</sup>, which while much higher than current GaN technologies is a big step forward for ZnO<sup>68</sup>. Dopant activation in semiconductors is important for reasons similar to high crystallinity, low dopant activation requires higher concentrations of dopant atoms to be added to the semiconductor, each of which serves as a scattering center for charge carriers. A considerable engineering problem in both GaN and ZnO over the past two decades has been finding p-type dopants that activate sufficiently to provide both high p-type mobility and conductivity. In particular, GaN p-doping with magnesium has only reached around 8% activation, and studies on the activation energy required for Mg dopants suggest that the theoretical maximum activation of Mg in GaN is only 8.2%<sup>69</sup>. Clearly further efforts into alternative p-doping strategies in GaN are required to maximize p-type or bipolar GaN device performance. A promising new doping strategy being applied to produce p-type ZnO is co-doping. This approach uses multiple dopants to simultaneously suppress native n-type defects in the ZnO while introuducing acceptor type states to provide hole conductivity. This approach using AlN co-doping has allowed for p-type activation up to  $56.8\%^{70}$ .

In order to assess material combinations suitable for device fabrication, several benchmarks measure a semiconductor's ability to interact favorably with other materials. Interface state density  $(D_{it})$  is one of the most critical measures of the quality at a semiconductor-insulator interface. In GaN systems, ALD Al<sub>2</sub>O<sub>3</sub> has shown the lowest D<sub>it</sub> at  $1 \times 10^{10}$  cm<sup>-2</sup> eV<sup>-1</sup>, although interfaces with high- $\kappa$  dielectrics have shown D<sub>it</sub> values on the same order of magnitude<sup>71,72</sup>. Studies on interfaces

between ZnO and dielectrics has been limited relative to GaN, the current Dit benchmark in ZnO systems is between ZnO and plasma enhanced chemical vapour deposition (PECVD) SiO<sub>2</sub>, with a value of 8.37x10<sup>11</sup> cm<sup>-2</sup> eV<sup>-1</sup>, which is almost 2 orders of magnitude higher than for GaN<sup>73</sup>. Next, of all semiconductor properties, carrier mobility  $(\mu)$  is arguably one of the most important, and pursuit of ever higher values of mobility (along with device scaling) has been one of the top drivers of faster devices in the semiconductor industry. Although mobility is typically cited as an inherent material property, it is quite often dependent on the architecture of the structure it is being measured in (except for Hall effect mobility, but even this can depend on metal-semiconductor contacts). In heterostructure devices like high electron mobility transistors (HEMTs), the mobility is a property of the 2D electron gas (2DEG) at the semiconductor-semiconductor interface, in metal insulator semiconductor (MIS) devices the field effect mobility is strongly affected by interface states. The highest GaN mobilities are seen in 2DEGs at GaN/AlGaN interfaces, with the room temperature benchmark at 3215 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, while the benchmark for field-effect mobility is lower at 375 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> with a HfO<sub>2</sub>-GaN MIS structure<sup>74,75</sup>. In ZnO systems, bulk mobilities as high as 245 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> have been achieved through boron doped melt growth<sup>76</sup>, while field effect mobilities have been limited to 110 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> in SiO<sub>2</sub> based TFTs<sup>77</sup>. Finally, gate capacitance in MIS structures is clearly dependent on the dielectric used. As such, both gate capacitance benchmarks for GaN and ZnO are from MIS structures using HfO2, which has a high dielectric constant of around 25. The benchmarks are 6.49  $\mu F$  cm<sup>-2</sup> and 1.75  $\mu F$  cm<sup>-2</sup> for GaN and ZnO respectively<sup>72,78</sup>.

Finally, some benchmarks are properties of full devices, and demonstrate the state of the material technology in addressing particular applications. The unity-current-gain frequency ( $f_t$ ) for transistors is a good measure of the ability of a material to fill high speed applications. High speed GaN transistors are already commercially viable, so it is no surprise that highly scaled GaN HEMTs have managed to achieve incredibly high  $f_t$  values up to 454 GHz<sup>79</sup>. On the other hand, ZnO TFTs have shown promising results given their relative immaturity, and  $f_t$  values up to 2.45 GHz<sup>80</sup> have been reported, suggesting ZnO TFTs may find space in the high frequency applications space. In the power electronics industry where high voltages are a requirement, another device benchmark defines the ability of a material system to hold up under strong potentials, the critical breakdown field ( $E_c$ ). Once again, the more developed technology GaN devices have achieved the higher  $E_c$  between GaN and ZnO with a value of 2.3 MV cm<sup>-1</sup> in high quality GaN epilayers<sup>81</sup>,

however in recent years ZnO vertical devices have begun to benefit from better voltage distribution strategies, and critical field values up to 800 kV cm<sup>-1</sup> have been achieved<sup>82</sup>. Theoretical calculations place the maximum  $E_c$  of both GaN and ZnO around 5 MV cm<sup>-1</sup>, so the following decades of research may yet see many breakthroughs in these benchmarks.

**Table 1I** – Summary of GaN and ZnO material benchmarks.

| Material/Device Property:                                    | GaN:                      | ZnO:                     |

|--------------------------------------------------------------|---------------------------|--------------------------|

| Defect density (V <sup>-1</sup> cm <sup>-2</sup> )           | $2.2x10^2$                | $5.2x10^9$               |

| Activation of p-dopants (%)                                  | 8                         | 57                       |

| Interface state density (cm <sup>-2</sup> eV <sup>-1</sup> ) | $1.0 \times 10^{10}$      | $8.37x10^{11}$           |

| Mobility (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> )  | 3215 (μ <sub>2DEG</sub> ) | 245 (µ <sub>bulk</sub> ) |

|                                                              | $375~(\mu_{eff})$         | $110~(\mu_{eff})$        |

| Gate capacitance (μF cm <sup>-2</sup> )                      | 6.49                      | 1.75                     |

| f <sub>t</sub> (GHz)                                         | 454                       | 2.45                     |

| Critical electric field (MV cm <sup>-1</sup> )               | 2.3                       | 0.8                      |

## 2 – Theory of Interfaces in MIS Structures

#### 2.0 – Structural Considerations

#### 2.0.0 – Interface Topography

When depositing thin films of materials on top of one another, one of the most basic variables to consider when evaluating the quality of the interface is the interface topography. Irregular topography at the interface between two materials can have a number of consequences. The effect of surface roughness on breakdown behavior in MIS structures has been studied thoroughly both experimentally<sup>83,84</sup> as well as through simulation<sup>85</sup>, and it is generally accepted that the field enhancements caused by surface roughness at the oxide-semiconductor interface can cause significant variance in the breakdown of the dielectric in MIS structures. Studies on sputtered HfO<sub>2</sub> dielectric films have also shown a correlation between topological roughness and the density of interface states and oxide charges, with higher sputtering voltages resulting in higher surface roughness and a shift in the flatband voltage of the MISCAP corresponding to traps in the oxide and at the interface<sup>86</sup>. This phenomenon is intuitive, since the majority of traps result from structural defects it is easy to imagine how a surface with irregular topology would increase the likelihood of material discontinuities that could manifest as electronic traps. Similarly, high surface roughness has been linked to high leakage currents through dielectric layers<sup>86</sup>.

Evaluation of surface roughness is generally carried out using atomic force microscopy (AFM) which will be described in detail in Chapter 3. In order to truly measure the roughness of the oxide-semiconductor interface the measurements should be made on the bottom material, depending on deposition order, since the top material may either reduce the measured roughness as it fills the dips in the surface or enhance the measured roughness due to factors like high deposition rate which reduce uniformity. Usually to extract the most representative measure of surface roughness the AFM is scanned over a small area and the surface roughness is calculated as the root-mean-square (RMS) of the AFM tip position.

**Figure 2.1** – Representation of RMS roughness.

#### 2.0.1 – Interfacial Stress and Strain

When two materials are in contact with one another, shear stresses and strains can develop at the interface between the two materials. Stress and strain at material interfaces in semiconductor devices are of interest for two different reasons. Firstly, excessive strain at material interfaces can degrade the quality of the interface, leading to dislocations and other defects that can affect breakdown behavior, increased trap densities, and increased leakage current. Secondly, interfacial strain can lead to polarization and an induced piezoelectric voltage due to the separation of positive and negative nuclei near the interface. This is the operating principle of GaN/AlGaN HEMTs, where piezoelectric voltages lead to a well of electrons known as a 2DEG, which demonstrates very high electron mobilities allowing for very fast devices. Interfacial stress and strain can be caused by a number of factors. In epitaxially grown layers such as AlGaN on GaN lattice mismatch between the two crystal structures generates the strain that leads to polarization. The other most common source of strain, particularly in films deposited by non-epitaxial methods is thermal expansion during deposition. Thermal stresses arise from a mismatch in the thermal expansion coefficient between the substrate material and the deposited material. If the deposited film is formed at elevated temperatures, both the film and substrate will undergo contraction upon cooling, but if the thermal expansion coefficients of the two materials are considerably different

this contraction will introduce strain at the material interface. For example, if a feature of length  $L_f$  with thermal expansion coefficient  $\alpha_f$  is deposited on a substrate with expansion coefficient  $\alpha_{sub}$  at some temperature  $T_{dep}$  before cooling down to room temperature (298 K) the feature will contract to a new length given as:

$$L_f' = L_f \left( 1 + \alpha_f (298 - T_{dep}) \right)$$

Simultaneously, the substrate under the feature will contract in a similar fashion, but with a different thermal expansion coefficient:

$$L'_{sub} = L_f \left( 1 + \alpha_{sub} (298 - T_{dep}) \right)$$

Taking the difference between the two equilibrium lengths and assuming the substrate will remain undeformed by the film, the strain introduced by the contraction  $\varepsilon$  can be derived:

$$\Delta L = L'_f - L'_{sub} = L_f (\alpha_f - \alpha_{sub})(298 - T_{dep})$$

$$\varepsilon = \frac{\Delta L}{L'_{sub}} = \frac{(\alpha_f - \alpha_{sub})(298 - T_{dep})}{1 + \alpha_{sub}(298 - T_{dep})}$$

**Figure 2.2** – Visualization of basic thermal contraction strain for the case where  $\alpha_f > \alpha_{sub}$ .

#### 2.1 – Electronic Considerations

#### 2.1.0 – Band Structure

Easily the strongest tool in evaluating electronic thin film devices is the band diagram, which gives an intuitive picture of the electron energy levels within the device.

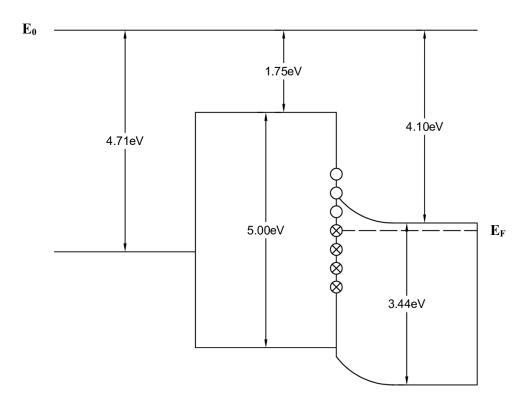

**Figure 2.3** – Theoretical band diagram of a Ru-SiN-GaN MISCAP under flat-band conditions.

In Figure 2.3 above, the theoretical band diagram for a Ru-SiN-GaN MISCAP is constructed from literature values for the work function ( $\varphi_m$ ), bandgap ( $E_g$ ), and electron affinity ( $\chi$ ) relative to the vacuum level  $E_0$  for each material<sup>8,87</sup>. The diagram reveals a theoretical 2.35 eV electron barrier from the GaN to the Ru, this barrier is the primary controller of tunneling current which will be analyzed later. The diagram also reveals the fact that at flat-band conditions and at zero-bias conditions there is no barrier to hole-flow from GaN to Ru, however since all devices in this thesis are fabricated on n-type GaN substrates, and since GaN has an extremely small intrinsic carrier concentration to begin with ( $\sim 10^{-19}$  cm<sup>-3</sup>), there will be virtually no holes present in the GaN and hole conduction will be negligible.

As will be investigated in this thesis, there are several non-idealities that can exist in MIS devices that cause deviation from the ideal band diagram. These include interface states or traps, as well as band-bending which can arise from several sources.

#### 2.1.1 – Interface States and Traps

An unavoidable non-ideality in thin film structures is the presence of intrinsic and extrinsic defects at the interfaces between materials. Intrinsic defects form as a result of the termination of the material crystal structure, which results in a distribution of energy states within the material's (either semiconductor or insulator) bandgap, extrinsic defects result from dislocations, impurities, and other crystal defects near the surface, and result in a similar distribution of states. Depending on the exact position of these states they can be either positively charged (donor states) when empty or negatively charged (acceptor states) when occupied. This leads to an equilibrium point at which the charge from negatively charged acceptor states is equal to the positive charge from positively charged donor states, the Fermi level at the material surface will fix itself to this point provided there are sufficient carriers to fill the acceptor states. This fixation of the Fermi level is known as Fermi level "pinning" and results in energy barriers within thin film devices that deviate strongly from theory. Figure 2.4 below shows the band diagram from Figure 2.3 with the Fermi level pinned, leading to a different electron barrier from GaN to Ru.

Figure 2.4 – Modified band diagram including Fermi level pinning from interface traps.

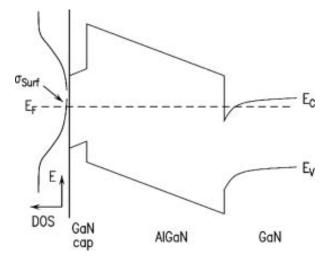

#### 2.1.2 – Interface Polarization and Band Bending

Many factors can lead to bending of the energy bands in an MIS device. Some of these factors occur in all devices, for example all real devices will experience band bending at zero bias due to the difference in work functions between the metal contact and the semiconductor. Other causes, such as the Fermi level pinning described earlier are non-ideal and more difficult to predict. One particularly important factor, and an inherent factor in GaN devices that can further enhance this bending is polarization charge. Polarization charge occurs when the strain in a III-V semiconductor forms displaced regions of charge leading to a piezoelectric potential. This polarization charge leads to band bending at each side of the semiconductor interface, and in cases where this band bending creates a potential well that reaches below the Fermi level under equilibrium conditions, leads to the formation of a 2DEG. This 2DEG is the fundamental characteristic of GaN/AlGaN HFETs discussed in Chapter 1. Polarization in GaN can take two forms, spontaneous and piezoelectric polarization. Spontaneous polarization occurs naturally even on unprocessed GaN surfaces and arises directly from the equilibrium surface structure of the GaN crystal. Piezoelectric polarization occurs at GaN interfaces as a result of interfacial strain, and depending on whether the strain is compressive or tensile can enhance or dampen the spontaneous polarization already present at the GaN surface. A strong tool for evaluating band bending in equilibrium devices is the use of x-ray photoelectron spectroscopy (XPS), a simple method for this evaluation is given in Chapter 3.

Figure 2.5 – Polarization induced band bending at an AlGaN/GaN interface<sup>88</sup>.

#### 3 – Fabrication and Materials Characterization of MIS Structures

#### 3.0 – Sputtering of Metals

Deposition of ruthenium and any other metals deposited in these studies was performed using standard sputtering techniques. The sputtering chamber used for deposition uses argon as the sputtering gas which is ionized and accelerated with a basic RF capacitively coupled circuit, the bombarding ions are confined near the target surface using a standard magnetron source. The chamber pressure, RF power, and sputtering time used are all provided in the fabrication section of Chapter 4.

#### 3.1 - Atomic Layer Deposition

#### 3.1.0 – Deposition process

The defining characteristic of ALD processing when compared to other similar methods such as chemical vapor deposition (CVD) is the use of precursors that undergo self-limiting reactions with the deposition surface to ensure that only one atomic layer is deposited at a time. The exact precursors used in this thesis for SiN films are covered in Chapter 4. By choosing ALD as the deposition method for this thesis, common thin film issues such as pin holing which can lead to excess leakage through the dielectric can ideally be avoided. ALD should also enable better control over the film thickness, allowing for more accurate analysis of dimension dependent quantities such as electric field.

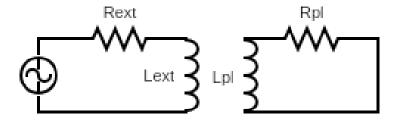

#### 3.1.1 – Plasma Enhanced ALD

The films fabricated in this thesis take advantage of another technique in ALD: the use of a remote plasma source to provide the energetic nitrogen atoms required for the nitride films. The reactor used was set up with an inductively coupled plasma (ICP) source to produce these species. A remote plasma is a plasma set up such that the target is not within or in the vicinity of the discharge, which can prevent damage from high energy particles ejected from the plasma. Inductively coupled plasmas are also referred to as transformer coupled plasmas (TCP) because the mechanism of energy transfer from the external circuit to the plasma within the discharge chamber can be

modelled very accurately as a transformer circuit where and external inductive circuit couples to the inductance of charged carriers within the plasma discharge itself as shown in Figure 3.1 below.

**Figure 3.1** – Circuit representation of ICP discharge source.

This circuit can be used to design the necessary driving circuit based on the desired plasma discharge size. To begin it is necessary to know the rate of electron-neutral collisions ( $\nu_e$ ), the density of charged species in the plasma sheath ( $n_{sh}$ ), as well as the desired discharge radius ( $\rho$ ) and length ( $\lambda$ ). The measurement of the collision rate and sheath concentration is outside the scope of this project, but they can be found in basic plasma characterization literature. Once these parameters have been determined, the plasma skin layer where current flows ( $\delta$ ) can be calculated as<sup>89</sup>:

$$\delta = \sqrt{\frac{m_e}{e^2 \mu_0 n_{sh}}}$$

And the plasma resistance  $(R_{pl})$  and capacitance  $(L_{pl})$  can be found as:

$$R_{pl} = \frac{2\pi\rho}{\lambda\delta} \frac{m_e \nu_e}{e^2 n_{sh}}$$

$$L_{pl} = \frac{\mu_0 \pi \rho^2}{\lambda}$$

Where  $m_e$  is the electron mass. The external circuit characteristics can be calculated from these values as long as the number of inductive windings  $(N_{wind})$  and the radius of the external windings  $(R_{wind})$  (different than the radius of the discharge) are known, and the external resistance  $(R_{ext})$  and inductance  $(L_{ext})$  are given as:

$$R_{ext} = N_{wind}^2 R_{pl}$$

$$L_{ext} = \left(\frac{R_{ext}^2}{\rho^2} - 1\right) N_{wind}^2 L_{pl}$$

Which fully describes the necessary circuit for achieving the plasma, the required input currents  $(I_{ext})$  and voltages  $(V_{ext})$  are then given as:

$$I_{ext} = \sqrt{\frac{2P_{abs}}{R_{ext}}}$$

$$V_{ext} = I_{ext} \sqrt{R_{ext}^2 + \omega^2 L_{ext}^2}$$

Where  $P_{abs}$  is the desired power absorption within the plasma, and is a design choice made based on the desired performance of the discharge in terms of plasma temperature, plasma energy distribution function, and other considerations.

#### 3.1.2 – Film Thickness Monitoring

In-situ monitoring of the ALD film thickness was achieved using a fixed angle J. A. Woolam ellipsometer. By placing a reference substrate (silicon) in the middle of the deposition platen during deposition, and training the ellipsometer's source on this reference substrate, the film thickness and deposition rate can be determined for all substrates within the reactor. Ellipsometry works through the application of a beam of linearly polarized light onto a thin film deposited on a substrate. A model predicting the amplitude and phase of the reflected signal is used to fit the measured signal which can then be used to estimate film thickness and permittivity, among other parameters. This starts with calculating the reflectance and transmittance at each material barrier using Fresnel's equations, as well as the "phase distance" ( $\beta$ ) of the film given as  $^{90}$ :

$$\beta = 2\pi \left(\frac{d_1}{\lambda}\right) n_1 \cos(\theta_1)$$

Where  $d_I$  is the film thickness,  $\lambda$  is the wavelength of the incident light,  $n_I$  is the refractive index of the film and  $\theta_1$  is the angle of refraction into the film. Using these equations for the repeated internal reflections and transmissions leads to the model for total reflected amplitude and phase, which can be fitted to experimental data to determine film qualities.

#### 3.2 – Lift-Off Processing

Patterning of all metal layers in this thesis was performed using lift-off processing. Lift-off processing involves the use of an image reversal photoresist during lithography, this exposes only the regions of the substrate where metal deposition is desired after development. Metal is sputtered as described previously and when the photoresist is dissolved in acetone the metal deposited on top of the photoresist is released, leaving only the patterned metal on the substrate. Lift-off processing has a number of advantages, the most important of these is it avoids use of etchants, so consideration of the substrate chemistry in any chemical agents is not required.

#### 3.3 – Characterization

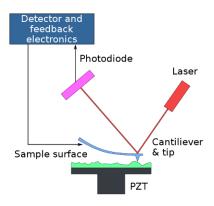

#### 3.3.0 – Atomic Force Microscopy

In order to ensure material surfaces were sufficiently smooth, and to analyze step heights on fabricated devices, atomic force microscopy (AFM) was employed. The working principle of AFM is the use of a laser which is reflected off a cantilever with a probe tip on the bottom. This tip is placed atomically close to the surface and a potential is applied to it which causes it to oscillate with a characteristic frequency which is detected in the movement of the reflected laser. As the tip is moved across the sample surface changes in distance between the tip and the surface cause changes in the vibrational frequency of the cantilever and measured signal, this information is transformed into a profile of the surface. This profile can be applied in a straight line to measure step heights of thin film features or can be applied to an area of a film to find the surface roughness as explained in Chapter 2.

Figure 3.2 – Schematic of AFM mode of operation.

#### 3.3.1 - X-Ray Photoelectron Spectroscopy

Elemental and energy level analysis of thin film devices can be carried out using XPS. When completing low level elemental analysis, use of XPS is quite straightforward, as only a simple qualitative picture is needed. More advanced analysis and in-depth knowledge of the XPS system setup is required to transform the raw counts-per-second (cps) data into accurate composition% data. Approximate depth profiling however is quite simple and a suitable method to confirm that all expected components of each film are present. Limitations on depth-resolution in XPS – which are only capable of being lowered to approximately 5 nm – are the primary limiting factor of depth profiling, although deconvolution of the data can be performed to estimate values with greater resolution, as will be explained below.

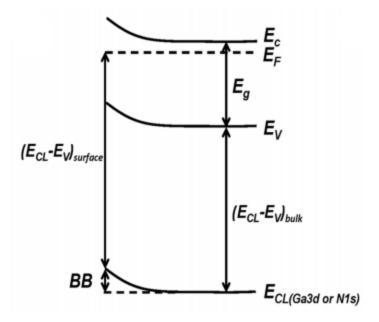

XPS can also be used as a tool to evaluate the band structure of thin film devices, and in this thesis XPS data will be used to make inferences about band bending behaviour near the GaN-SiN interface. In Zhao et al.<sup>91</sup> angle resolved XPS is used to estimate the band bending near the surface of plain GaN substrates as shown in Figure 3.3 (where the GaN surface is the left boundary of the diagram), where it is assumed that a glancing angle incident signal will probe mostly the GaN surface while more normal angle signals will probe deeper into the sample. This result is improved in the reference by modelling the detected signal as the integral of a continuum of signals coming from differing depths into the sample, by fitting the experimental data to this model they were able to estimate more accurately what the true value of  $(E_{CL}-E_V)_{surface}$  is for Ga<sub>3d</sub> orbitals. In this thesis this technique will be used in the more approximate form and using a slightly different method. Since samples in this thesis will consist of three material layers, measurement of the GaN-SiN interface is not possible directly. However, since the samples were sputtered to achieve depth profiling, the measured signal as the probe depth approaches the GaN-SiN interface will begin to represent the interface and then eventually pass through the interface once the metal layer and some of the SiN layer has been sputtered away. With this under consideration it becomes clear that as the material is sputtered away the GaN energy bands at the interface will relax, and the difference in measured values (which correspond to  $(E_{CL} - E_V)_{surface}$ ) will represent the surface band bending induced by the SiN interface with GaN.

**Figure 3.3** – Schematic from Zhao et al.<sup>91</sup> showing the energy levels associated with measuring band bending.

**Figure 3.4** – Position of VBM from XPS data<sup>91</sup>.

The reference gives the band bending equation as:

$$BB = (E_{cl} - E_V)_{bulk} + E_g - E_c - (E_{cl} - E_V)_{surface}$$

$$= \Delta(E_{cl} - E_V) + E_g - E_c$$

Where  $(E_{cl} - E_V)_{bulk}$  is the energetic distance of the peak of interest (either Ga<sub>3d</sub> or N<sub>1s</sub>) with respect to the valence band minimum (VBM) as shown in Figure 4.4,  $E_g$  is GaN's bandgap, and  $E_c$  is the conduction band position relative to the Fermi level  $(E_F)$ . This distance can be found through the relation:

$$E_c = -kT ln\left(\frac{n}{N_c}\right)$$

Where n is the dopant concentration in the GaN and  $N_c$  is the conduction band edge density of electron states in GaN<sup>8</sup>.

## 4 - Oxide-Semiconductor Interfaces in Crystalline GaN MISCAPs

Parts of this chapter are adapted from an extended conference abstract which was published in the CS Mantech 2020 Digital Digest.

#### 4.0 - Device Fabrication and Physical Characterization

Identical MISCAPs were fabricated on three different types of GaN wafers which included n<sup>+</sup> and n<sup>-</sup> wafers from Kyma as well as n<sup>++</sup> wafers from University Wafer. All wafers were cleaned with piranha etch solution consisting of a 3:1 ratio of sulphuric acid to hydrogen peroxide to remove any organic matter or metallic contaminants on the surface<sup>92</sup>. Silicon nitride was deposited as the dielectric layer via ALD and was deposited without patterning on top of the GaN wafer, electronic methods of breaking the outer contacts of the devices are discussed in Section 4.1 to compensate for the un-patterned SiN at the outer contacts. Silicon nitride films were deposited using ALD with tris(dimethylamino)silane as the precursor for silicon and a forming gas ICP plasma consisting of 95% N<sub>2</sub> and 5% H<sub>2</sub> as the precursor for nitrogen. Further information on the ALD process as well as the ICP plasma can be found in a related study by Triratna Muneshwar<sup>93</sup>, the fabrication parameters used during the deposition are listed in Table 4I below.

**Table 4I -** ALD parameters used for deposition of SiN films.

| Parameter:              | Value:  |

|-------------------------|---------|

| Substrate temperature   | 100 °C  |

| Reactor pressure        | ~1 Torr |

| 3DMAS pulse time        | 0.1 s   |

| 3DMAS purge time        | 10 s    |

| Forming gas plasma time | 10 s    |

| Forming gas purge time  | 10 s    |

| GPC                     | ~0.35 Å |

The device contacts were patterned using a lift-off process along with sputtered ruthenium. For lift-off, the negative photoresist AZ5214E was used as it possesses a tendency to form a slight undercut during exposure which enhances the lift-off process. The photoresist was spun, baked,

and exposed according to the parameters outlined in Table 4II and the ruthenium contacts were then sputtered using inputs described in Table 4III.

**Table 4II** – Processing steps for AZ5214E.

| <b>Process Step:</b> | <b>Description:</b>                          |  |

|----------------------|----------------------------------------------|--|

| Spin coat            | 10 s @ 500 rpm + 40 s @ 4000 rpm             |  |

| Soft bake            | 90 s @ 90 °C                                 |  |

| Pattern exposure     | $1.0 \text{ s} @ 60.7 \text{ mW/s}^2$        |  |

| Hard bake            | 120 s @ 110 °C                               |  |

| Flood exposure       | $60 \text{ s} @ 60.7 \text{ mW/s}^2$         |  |

| Development          | Submersion and agitation in MF CD 319 x 35 s |  |

**Table 4III** – Ruthenium sputtering parameters.

| Parameter:          | Value:    |

|---------------------|-----------|

| Sputter input power | 200 W     |

| Chamber pressure    | 1.8 mTorr |

| Sputter time        | 500 s     |

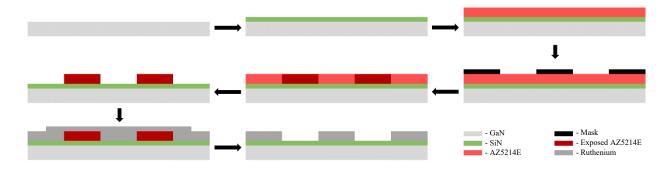

Finally, the lift-off step was completed by sonicating the samples in an acetone bath, taking care to not use too high a power setting to avoid damaging both the ruthenium and underlying SiN films. The full process flow is illustrated in Figure 4.1, starting from clean GaN wafers.

Figure 4.1 – Process flow for fabrication of SiN/GaN MISCAPs.

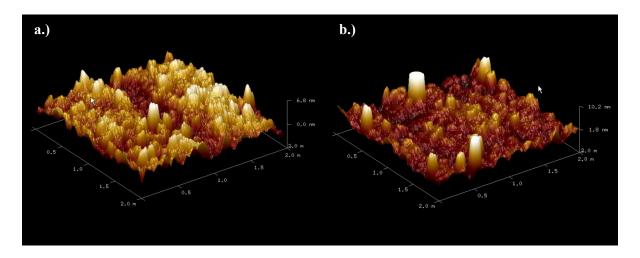

During fabrication and after electronic testing, physical characterization methods were used to gain insight into the quality of the fabricated devices. During fabrication, AFM was employed to monitor the surface roughness and topology of the deposited films since high surface roughness can enhance electrical breakdown effects and otherwise contribute to inconsistent device behaviour as discussed in Chapter 2. Images taken from AFM scans on top of the SiN and ruthenium films during fabrication of the Kyma n<sup>+</sup> devices are shown in Figure 4.2, AFM data also allows for direct measurement of the RMS roughness which was measured as 1.92 nm and 2.17 nm for the SiN and ruthenium films respectively. These values are low enough that surface roughness was not considered to be a significant factor in the electronic performance of the devices.

Figure 4.2 – AFM images of a.) SiN and b.) ruthenium film topology.

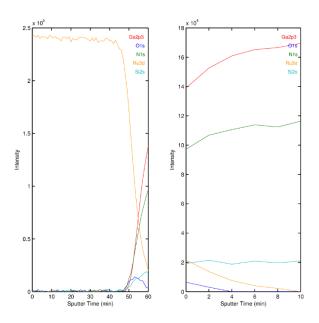

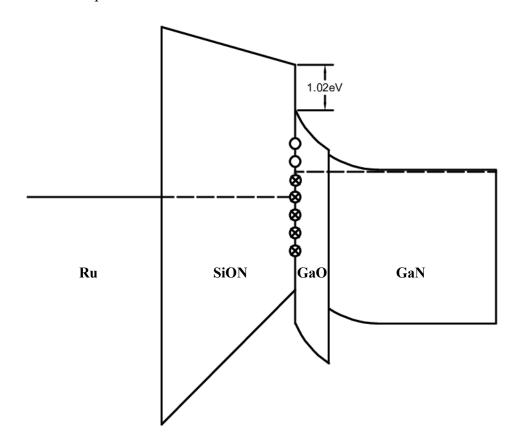

After full electronic characterization of the Kyma n<sup>+</sup> MISCAPs, they were subjected to XPS depth profiling to analyze the film composition as well as investigate the electronic band structure of the MISCAPs. In Figure 4.3 the expected depth profile is seen, with the ruthenium contact showing little oxidation while the SiN film at the interface between the ruthenium contact and GaN substrate shows substantial oxidation with a distinct hump in the oxygen signal. This result makes a clear case that the thin SiN films are oxidizing considerably after deposition, and hence for electronic analysis the dielectric will be treated as a silicon oxynitride (SiON) rather than pure SiN.

**Figure 4.3** – XPS Depth profiling of Kyma n<sup>+</sup> SiN/GaN MISCAPs.

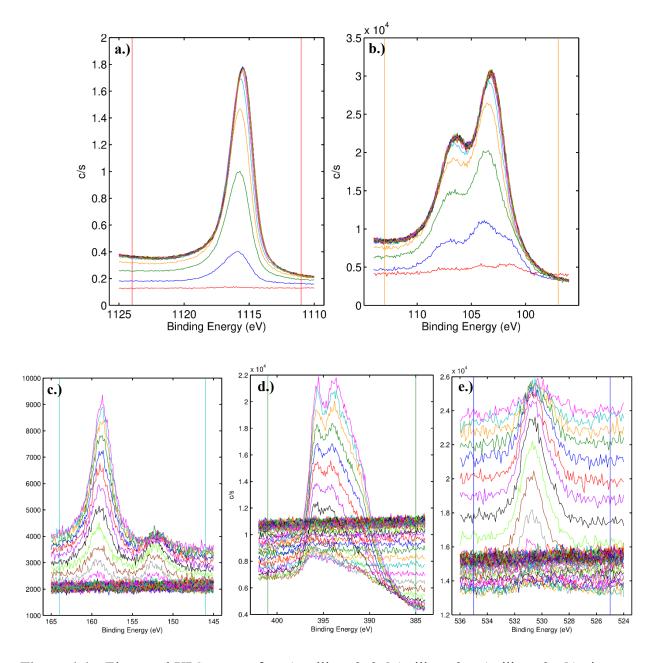

Full spectra results for several elements of interest were also measured using XPS, and Figure 4.4 includes the spectra for gallium, silicon, nitrogen, and oxygen. Peaks in the gallium 2p3 and nitrogen 1s XPS spectra appear at the expected positions for GaN crystals. Silicon 2s orbital peaks appear at the theoretical locations corresponding to Si dopants in GaN as well as Si-O and Si-N bonds in the 150-152.6 eV range, and 2p peaks corresponding to elemental Si and Si-O bonds. Surprisingly, the oxygen 1s peaks showed up around 530.7 eV, far from the 534.5 eV expected for Si-O bonds. This peak location is actually likely to result from Ga-O bonds<sup>94</sup>, suggesting a degree of oxidation of the GaN wafer surface. The sequential peaks in Figure 4.4 result from repeat measurements as material is sputtered away, and using techniques described in Chapter 3 it is possible to make some hypotheses about the electronic band structure near the dielectric-semiconductor interface. The band-bending near the SiON-GaN interface is calculated to be approximately 1.81 eV. This result could suggest some degree of polarization, induced by the SiON film, by the natural polarity of the GaN surface, or by a combination of both.

**Figure 4.4** – Elemental XPS spectra for **a.**) gallium 2p3, **b.**) silicon 2p **c.**) silicon 2s **d.**) nitrogen 1s and **e.**) oxygen 1s taken from Kyma n<sup>+</sup> SiN/GaN MISCAPs.

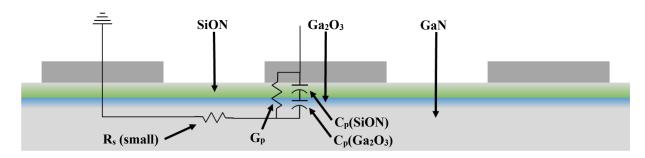

#### 4.1 - Electronic Characterization

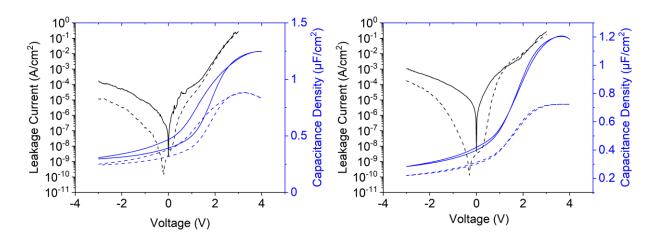

Current-voltage analysis was carried out on the MISCAPs to evaluate their behaviour as well as to investigate conduction mechanisms throughout the device. Prior to measurement, breaking of the SiON films under the outer contacts of the devices was required in order to remove the current

barrier and series capacitance that would otherwise arise from the MIS structure. Various methods for breaking this film were employed, with the most common methods involving either using large voltage pulses with very short ramp-up time or applying high voltages up to 100 V across adjacent outer contacts until avalanche breakdown occurred.

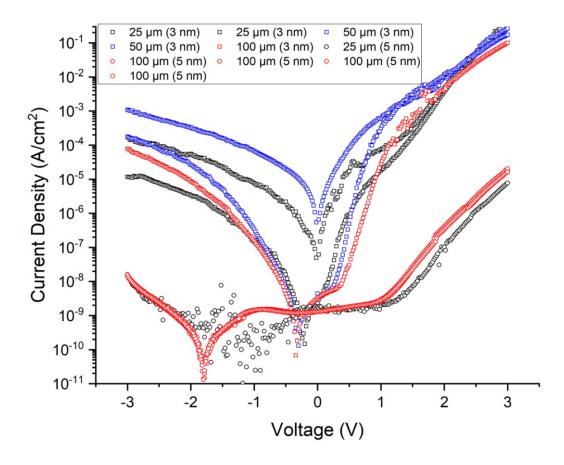

From standard IV curves (See Appendix A) a variety of curves were observed which complicated the analysis of which conduction mechanisms were dominating the device behaviour. Some devices showed nearly ideal diode behaviour with current switching from negative to positive at 0 V while many other devices transitioned from negative to positive current at a *negative* voltage before plateauing at voltages around 0 V and rising again at higher voltages. In order to gain a clearer understanding of the conduction mechanisms taking place in the devices, the current-voltage data was transformed to the form of a Fowler-Nordheim plot. The Fowler-Nordheim equation, under the famous Wentzel-Kramers-Brillouin approximations for tunneling current through a triangular barrier, takes the exponential form:

$$J = AE^2 \cdot e^{-\frac{4}{3} \frac{\sqrt{2qm^*}}{\hbar} \frac{\phi_{\overline{b}}^{\frac{3}{2}}}{E}}$$

This equation can then be modified into a linear equation in logarithmic scale as:

$$\ln\left(\frac{J}{E^2}\right) = \ln(A) - \frac{4}{3} \frac{\sqrt{2qm^*}}{\hbar} \frac{\phi_b^{\frac{3}{2}}}{E}$$

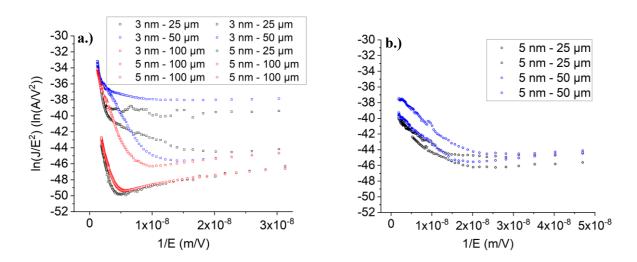

This form allows for the simple identification of Fowler-Nordheim tunneling current regimes by normalizing the current by area into the current density (J), normalizing the voltage across the dielectric barrier into the electric field (E), and plotting  $\ln \left(\frac{J}{E^2}\right)$  against  $\frac{1}{E}$ . If Fowler-Nordheim tunneling occurs, there will be a region of this plot with a distinct linear form with negative slope. This slope can then be used to calculate the tunneling barrier height ( $\phi_b$ ) using experimental values of the electron effective mass ( $m^*$ ) in SiON. When formulating these plots, it is also important to consider the distribution of potential throughout the device as only the potential difference across the dielectric is considered in the Fowler-Nordheim equation. In Figure 4.5 Fowler-Nordheim plots for devices fabricated on University Wafer  $n^{++}$  wafers are shown. Away from the high  $\frac{1}{E}$  region discrepancies in the shape of several of the  $\ln \left(\frac{J}{E^2}\right)$  curves (primarily in the 3 nm devices of 4.5a

and all devices in 4.5b) continue to suggest that other conductivity mechanisms such as trap assisted tunneling are responsible for the variance in standard current-voltage characteristics observed across all samples. It is also worth making note of the distinctly lower values of  $\ln\left(\frac{J}{E^2}\right)$  for the 5 nm SiON samples vs the 3 nm samples, which should be similar since the electric field normalizes film thickness. This can be explained if one considers that most defects in a deposited film occur close to the interfaces; if defects contributed conductivity in parallel to other tunneling mechanisms it is expected that as the SiON film becomes thicker, a better current barrier will begin to form and lower current will flow even at similar values of E. Ambiguity over the primary conduction mechanism disappears, however, at low values of  $\frac{1}{E}$  as a consistent pattern begins to emerge and most samples demonstrate the expected negative-slope linear behaviour characteristic of Fowler-Nordheim tunneling. Moreover, the slopes in these linear regimes appear to be remarkably similar, suggesting a consistent tunneling barrier across all devices, even for different thicknesses of SiON.

In order to quantitatively analyze this observed pattern, we can numerically calculate the slopes in the linear regime after making suitable corrections to the voltage across the dielectric. For these devices, the high doping of the substrate removes most series resistance in the device, and the voltage distribution can then be established by treating the system as two capacitors in series, one corresponding to the oxide capacitance ( $C_{ox}$ ) and the other corresponding to the capacitance across the electron layer immediately adjacent to the oxide in the semiconductor ( $C_D$ ), which has a characteristic thickness of the Debye length ( $\lambda_D$ ). Since the total charge held by both the oxide and the electron layer are equal, the potential distribution can be given as:

$$V_a = V_{ox} + V_D$$

$$V_a = \frac{Qt_{ox}}{\epsilon_{ox}} + \frac{Q\lambda_D}{\epsilon_s}$$

Where  $V_a$  is the applied voltage,  $t_{ox}$  is the oxide thickness, and  $\epsilon_{ox}$ ,  $\epsilon_s$  are the permittivity values for SiON and GaN, respectively. Taking the ratio of  $V_{ox}$  to  $V_D$  we get:

$$V_D = \frac{\lambda_D \epsilon_{ox}}{t_{ox} \epsilon_s} \cdot V_{ox}$$

Substituting into the first equation for V<sub>a</sub> the relation between V<sub>a</sub> and V<sub>ox</sub> becomes:

$$V_a = \left(1 + \frac{\lambda_D \epsilon_{ox}}{t_{ox} \epsilon_s}\right) V_{ox}$$

The Debye length for GaN can be calculated using the classical formula:

$$\lambda_D = \sqrt{\frac{\epsilon_s kT}{N_d q^2}}$$

Where  $N_d$  is the dopant density which is extracted from the capacitance analysis later in this chapter to be approximately  $10^{19}$  cm<sup>-3</sup> for the University Wafer n<sup>++</sup> wafers. Alternatively, a quantized capacitance where  $\lambda_D$  is replaced with the centroid of the electron wave function away from the barrier can also be used, this value has previously been calculated to be approximately 2 nm<sup>95</sup>. A calculated  $\lambda_D$  value of 1.11 nm was used in combination with literature values for the permittivity of GaN and SiON (8.9 and 5 respectively for SiON with approximately 50% oxidation<sup>8,96</sup>) and values of SiON thickness determined during deposition to calculate the correction factor for  $V_{ox}$ .

**Figure 4.5** – Fowler-Nordheim plots demonstrating the two most common slopes.

With  $V_{ox}$  and therefore E corrected, the slope (S) of the Fowler-Nordheim plots can be converted to a value of barrier height  $(\phi_h)$  using:

$$\phi_b = \left(-\frac{3}{4} \frac{\hbar}{\sqrt{2qm^*}} S\right)^{\frac{2}{3}}$$

Where q is the elementary charge and  $m^*$  for SiON is taken as  $0.4 \text{m}_e^{96}$ . Calculating these values for all curves shown in Figure 4.5, three classes of barrier height are found. Within the samples displayed in Figure 4.5a nearly all curves have the same slope and therefore barrier height within the linear regime, with the exception of the 3 nm thick,  $25 \, \mu \text{m}$  radius devices and one of the 3 nm thick,  $50 \, \mu \text{m}$  radius devices which demonstrated a slightly higher barrier height. Within samples from Figure 4.5b a lower barrier height is determined, this may be a sign of a barrier that has been lowered through some physical process, but considering these curves' lower degree of convergence and linearity compared to the devices in Figure 4.5a it is more likely that these slopes are an artifact of other competing conduction mechanisms. It is also worth noting that the slopes in Figure 4.5b are very similar to the secondary slope (corresponding barrier of 0.206 eV) of the lower 3 nm thick,  $25 \, \mu \text{m}$  radius data in Figure 4.5a, further suggesting that these slopes come from a conduction mechanism other than classical Fowler-Nordheim tunneling or a much lower barrier height.

**Table 4IV** – Three regimes of barrier heights with standard deviations.

| Number of Samples: | Barrier Height (meV): | σ (meV): |

|--------------------|-----------------------|----------|

| 4                  | 222                   | 12.32    |

| 7                  | 953                   | 6.95     |

| 3                  | 1184                  | 42.42    |

The testing of MISCAPs typically focuses primarily on assessing a material system's suitability for use in MISFETs. The primary characteristics that can be extracted from MISCAPs that translate to MISFETs are capacitance density, which dictates how much charge can be held under a device gate and consequently how much current can be generated from source to drain, as well as effective mobility which limits the operating frequency of the device. Capacitance measurements were carried out on the MISCAP structures to ascertain these properties from devices with outer contacts with broken SiON films as described prior in this chapter.

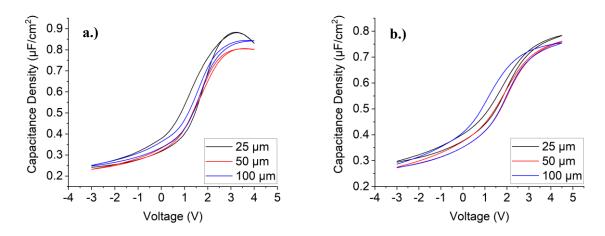

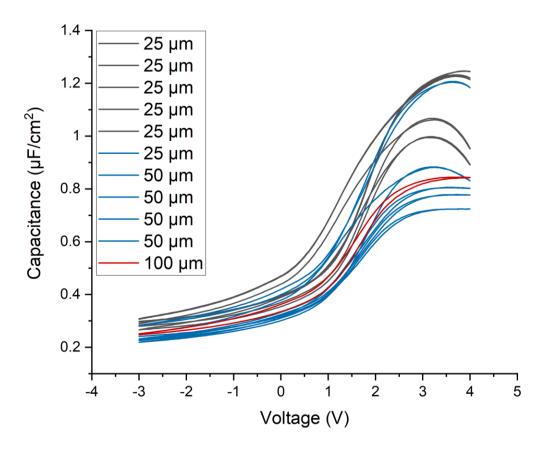

Figure 4.6 – Normalized capacitance-voltage plots for a.) 3 nm and b.) 5 nm SiON films.

Capacitance-voltage measurements were taken from test structures with inner contact radii of 25, 50 and 100  $\mu$ m and outer contacts with varying area in order to verify that the outer contacts were not having any appreciable effect on the capacitance measurements. Measurements were made at a variety of frequencies to get a picture of the frequency dependence prior to full spectrum capacitance-frequency measurements. Dual sweep measurements were also taken to measure the degree of hysteresis in the devices. The measurements were normalized by the inner radius area to extract the capacitance density in common units of  $\mu$ F/cm², normalized curves from devices with SiON thickness of 3 nm and 5 nm on University Wafer n<sup>++</sup> wafers are shown in Figure 4.6. For both thicknesses the normalized curves align nicely with each other, demonstrating that the inner contact area is the primary source of the capacitance rather than the outer contact.

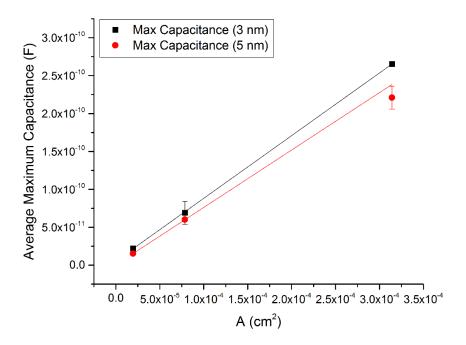

The good area dependence is also observed over larger sample sizes, Figure 4.7 shows averaged capacitance values from all devices with 3 nm and 5 nm SiON thicknesses vs. their inner contact area. The capacitance vs. area trend is linear, which once again demonstrates the good area dependence of the devices, as well as allowing extraction of the average capacitance density through linear regression of the series. Using this method the capacitance densities for both the 3 nm and 5 nm devices were found to be  $0.827 \, \mu\text{F/cm}^2$  and  $0.757 \, \mu\text{F/cm}^2$  respectively. It is worth noting that the capacitance density doesn't scale exactly as would be expected, since the oxide capacitance should scale inversely proportional to SiON thickness ( $C_{ox} = \frac{\epsilon_{ox}}{t_{ox}}$ ) the capacitance density for the 3 nm films should in theory be  $\frac{5}{3}$  times greater than the capacitance density of the 5

nm films, but in reality the ratio  $\frac{C_{ox,3nm}}{C_{ox,5nm}}$  is calculated to be 1.092, considerably lower. However, this can be explained through consideration of leakage effects in the 3 nm films, which reach leakage current densities of 1 A/cm<sup>2</sup> where these effects become important<sup>97</sup> (the 5 nm films do not reach this current density). It has been demonstrated<sup>97</sup> that as gate length (which in a planar MISCAP structure is equivalent to the inner radius) shrinks the leakage correction factor is significantly reduced. Therefore, the 3 nm data with inner radius 25  $\mu$ m and the lowest qualitative "droop" of the capacitance-voltage curve at high voltages (>2 V) is considered the best representation of capacitance density for the 3 nm films. This data is presented in Appendix B and it is seen that the data fulfilling the above criteria shows capacitance density of around 1.2  $\mu$ F/cm<sup>2</sup>.

Figure 4.7 – Capacitance vs. area plot for 3 nm and 5 nm films.

A key piece of material characterization that can be performed using capacitance-voltage data is the calculation of dopant density plots. The relevant equations from Schroder<sup>98</sup> are as follows:

$$N_d(W_{dep}) = \frac{2}{q\epsilon_s A^2 \frac{d\left(\frac{1}{C^2}\right)}{dV}}$$

$$W_{dep} = \frac{\epsilon_s A}{C}$$

However, it is also worth correcting the capacitance term in the depletion width to reflect only the depletion capacitance. The total measured capacitance in an ideal MISCAP is given by:

$$\frac{1}{C_{meas}} = \frac{t_{ox}}{\epsilon_{ox}} + \frac{\lambda_D}{\epsilon_s} + \frac{1}{C_{dep}}$$

Using this breakdown  $W_{dep}$  can be reformulated as:

$$W_{dep} = \epsilon_s A \left( \frac{1}{C_{meas}} - \frac{t_{ox}}{\epsilon_{ox}} - \frac{\lambda_D}{\epsilon_s} \right)$$