National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Service

Services des thèses can-

innes

Ottawa, Canada K1A 0N4

## CANADIAN THESES

# THÈSES CANADIENNES

#### NOTICE

The quality of this microfiche is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Previously copyrighted materials (journal articles, published tests, etc.) are not filmed.

Reproduction in full or in part of this film is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30. Please read the authorization forms which accompany this thesis.

#### **AVIS**

La qualité de cette microfiche dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

Les documents qui font déjà l'objet d'un droit d'auteur (articles de revue, examens publiés, etc.) ne sont pas microfilmés.

La reproduction, même partielle, de ce microfilm est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30. Veuillez prendre connaissance des formules d'autorisation qui accompagnent cette thèse.

THIS DISSERTATION

HAS BEEN MICROFILMED

EXACTLY AS RECEIVED

LA THÈSE A ÉTÉ MICROFILMÉE TELLE QUE NOUS L'AVONS REÇUE

NL-91 (4/77)

National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Division

Division des thèses canadiennes

Ottawa, Canada K1A 0N4

# PERMISSION TO MICROFILM — AUTORISATION DE MICROFILMER

| Please print or type → Écrire en lettres moulées ou dactylograp                                                                                                                     | hier                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Full Name of Author — Nom complet de l'auteur                                                                                                                                       |                                                                                                                                                                                                 |

| DONNA JEAN FREMONT                                                                                                                                                                  | •                                                                                                                                                                                               |

| Date of Birth — Date de naissance                                                                                                                                                   | Country of Birth — Lieu de naissance                                                                                                                                                            |

| APRIL 13, 1948                                                                                                                                                                      | CANADA                                                                                                                                                                                          |

| Permanent Address — Résidence fixe  2839 - 63 Avenue S.W.                                                                                                                           |                                                                                                                                                                                                 |

| CALGARY, ALTA T3E 5J6                                                                                                                                                               |                                                                                                                                                                                                 |

| Title of Thesis — Titre de la thèse                                                                                                                                                 |                                                                                                                                                                                                 |

| ARCHITECTURES                                                                                                                                                                       | TLUATION OF DATAFLOW COMPUTER                                                                                                                                                                   |

|                                                                                                                                                                                     |                                                                                                                                                                                                 |

| University — Université  UNIVERSITY OF ALBERTA                                                                                                                                      |                                                                                                                                                                                                 |

| Degree for which thesis was presented — Grade pour lequel cette                                                                                                                     | thèse fut présentée                                                                                                                                                                             |

| M. Sc.                                                                                                                                                                              |                                                                                                                                                                                                 |

| Year this degree conferred — Année d'obtention de ce grade                                                                                                                          | Name of Supervisor — Nom du directeur de thèse                                                                                                                                                  |

| 1983                                                                                                                                                                                | DR. J. TARTAR                                                                                                                                                                                   |

|                                                                                                                                                                                     |                                                                                                                                                                                                 |

| Permission is hereby granted to the NATIONAL LIPRARY OF CANADA to microfilm this thesis and to lend or sell copies of the film.                                                     | L'autorisation est, par la présente, accordée à la BIBLIOTHE QUE NATIONALE DU CANADA de microfilmer cette thèse et oprêter ou de vendre des exemplaires du film.                                |

| The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission. | L'auteur se réserve les autres droits de publication; ni la thès<br>ni de longs extraits de celle-ci ne doivent être imprimés o<br>autrement reproduits sans l'autorisation écrite de l'auteur. |

| Date //                                                                                                                                                                             | Signature                                                                                                                                                                                       |

| July 22, 1983                                                                                                                                                                       | Il Fremont                                                                                                                                                                                      |

# The University of Alberta

# A METHODOLOGY FOR THE EVALUATION OF DATAFLOW COMPUTER ARCHITECTURES

by

Donna J. Fremont

A thesis

submitted to the Faculty of Graduate Studies and Research

in partial fulfillment of the requirements for the degree

of Master of Science

Department of Computing Science

Edmon. ...berm.

#### THE UNIVERSITY OF ALBERTA

#### RELEASE FORM

NAME OF AUTHOR: Donna J. Fremont

TITLE OF THESIS: A Methodology for the Evaluation of Dataflow Computer Architectures

DEGREE FOR WHICH THIS THESIS WAS PRESENTED: Master of Science

YEAR THIS DEGREE GRANTED: 1983

Permission is hereby granted to The University of Alberta Library to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly or scientific research purposes only.

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.

(Signed)

Permanent Address:

2839 - 63 Avenue S.W.

Calgary, Alberta

Canada T3E 5J6

Dated 19 July 1983

#### THE UNIVERSITY OF ALBERTA

#### FACULTY OF GRADUATE STUDIES AND RESEARCH

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies and Research, for acceptance, a thesis entitled A Methodology for the Evaluation of Date flow Computer Architectures submitted by Donna J. Fremont in partial fulfillment of the requirements for the degree of Master of Science.

Supervisor

Date July 19, 1983

#### **ABSTRACT**

Dataflow computer architectures are a new class of architectures which employ parallel processing and are based on a data driven computation model. Although these novel architectures promise increased power and speed, they complicate an already difficult task, the design of computer systems. The development of tools to manage and simplify the design process important because data flow architectures are both untried and inherently more complex than traditional uniprocessor computers.

Presented here is a methodology used to investigate properties of proposed dataflow architectures based on their estimated performance. Fundamental to the methodology are a formal language to describe the architecture and a data-driven simulator to generate performance statistics. The methodology is tested on two dataflow architecture designs taken from the current literature, showing sufficient experimental results to demonstrate its applicability to divergent designs within the class of architectures. This work also contributes to the S<sub>A</sub>\* (an architecture description language) design environment by extending its use to the class of dataflow computer architectures.

#### Acknowledgements

I would like to thank my supervisor, John Tartar, for his constant guidance and support throughout this research. Jeff Sampson, Alan Wagner and Lisa Higham read a rough draft of the thesis and contributed helpful suggestions for improvements. Steve Sutphen assisted in the use of text and picture processing facilities during the production of this thesis. Thanks to Darrel Makarenko for his previous work on the simulator and his help during the programming of the modifications.

# TABLE OF CONTENTS

|                                          | Page |

|------------------------------------------|------|

| Chapter 1 Introduction                   | 1    |

| 1.1 The Problem                          | 1    |

| 1.2 Froposed Methodology                 | 1    |

| 1.3 Part Work                            | 2    |

| 1.4 Outline of Thesis                    | 3    |

| Chapter 2 Dataflow Computer Architecture | 5    |

| 2.1 Design Goals                         | 5    |

| 2.2 Dataflow Computing Model             | 7    |

| 2.3 Implications of the Dataflow Model   | 9    |

| 2.3.1 Program Organization               | 9    |

| 2.3.2 Execution Cycle                    | 10   |

| 2.3.3 Machine Organization               | 11   |

| 2.3.4 Summary                            | 12   |

| 2.4 Survey of Dataflow Architectures     | 13   |

| 2.4.1 MIT Machine                        | 13   |

| 2.4.2 DDM1 Machine                       | 15   |

| 2.4.3 Id (Irvine Dataflow) Machine       | 17   |

| 2.4.4 Systeme LAU                        | 18   |

| 2.4.5 Manchester University (MU) Machine | 21   |

| Chapter 3 Evaluation Methodology         | 23   |

| 3.1 Evperimental Model                   | 23   |

| 3.2 Performance Measures and Parameters                    | 25 |

|------------------------------------------------------------|----|

| 3.3 Architecture Description                               | 28 |

| 3.4 The Simulation Facility                                | 32 |

| Chapter 4 Experimental Validation                          | 37 |

| 4.1 Examples Using the Proposed Methodology                | 37 |

| 4.1.1 Construction of an S* Descri                         | 38 |

| 4.1.2 Id Design                                            | 38 |

| 4.1.3 MIT Design                                           | 40 |

| 4.1.4 Test Program                                         | 42 |

| 4.2 Results                                                | 46 |

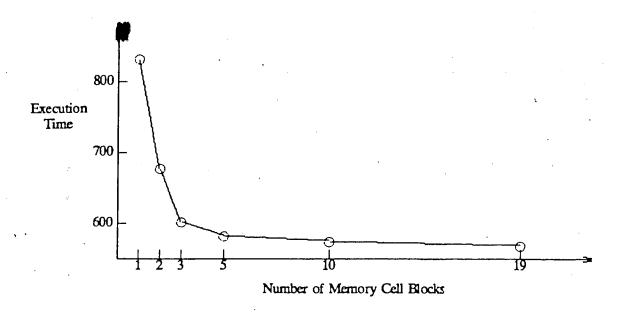

| 4.2.1 Id Design                                            | 46 |

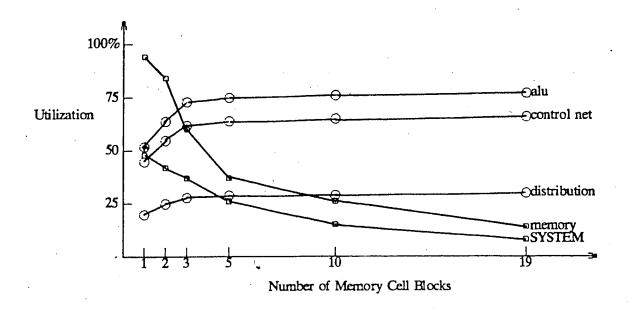

| 4.2.2 MIT Design                                           | 50 |

| 4.2.3 A Comparison                                         | 54 |

| 4.3 Comments on S <sup>*</sup> and the Simulation Facility | 58 |

| Chapter 5 Conclusions                                      | 61 |

| References                                                 | 64 |

| Appendix A S*A Description of Id Machine                   | 66 |

| Appendix B S*A Description of MIT Machine                  | 82 |

# LIST OF TABLES

| Table Table                                              | Page |

|----------------------------------------------------------|------|

| 4.1 Id Instruction Format                                | 39   |

| 4.2 Id Functional Unit Execution Times                   | 39   |

| 4.3 MIT Functional Unit Execution Times                  | 41   |

| 4.4 Examples of Machine Code Instructions                | 45   |

| 4.5 MIT Allocation of Test Program to Memory             | 50   |

| 4.6 MIT Average Queue Wait Time                          | 52   |

| 4.7 MIT Average Queue Wait Time with Two Operation Units | 53   |

# LIST OF FIGURES

| Figu      | ure .                                           | Page |

|-----------|-------------------------------------------------|------|

| 2.1       | Computation as a Directed Graph                 | - 8  |

| 2.2       | MIT Machine                                     | 14   |

| 2.3       | DDM1 Machine                                    | 16   |

|           | Id Machine                                      | 17   |

| 2.5       | Id Processing Element                           | 19   |

| 2.6       | LAU Machine                                     | 20   |

| 2.7       | MU Machine                                      | 22   |

| 3.1       | The Modeling Process                            | 24   |

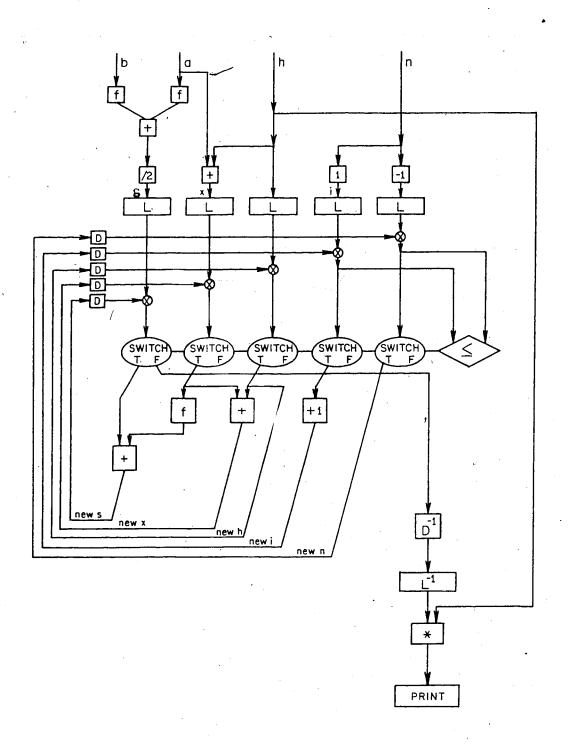

| 4.1       | Id Machine Language Program: Integration        | 43   |

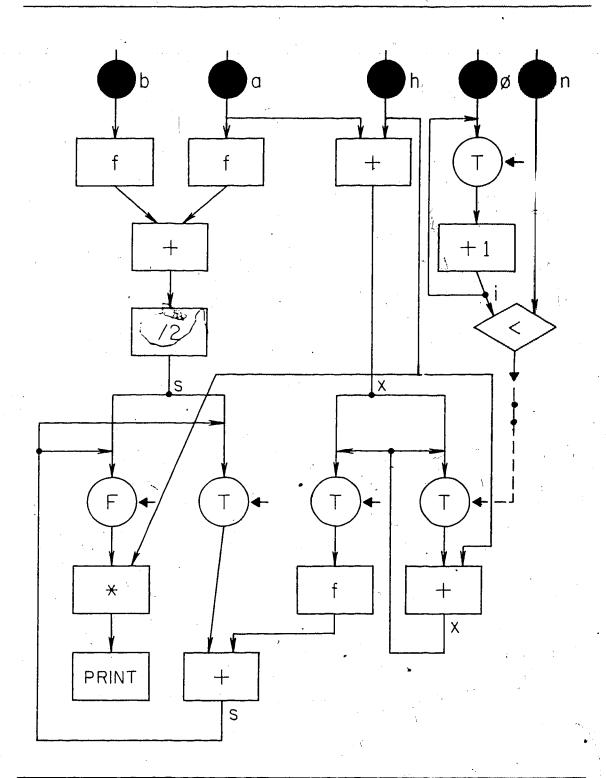

| 4.2       | MIT Machine Language Program: Integration       | 44   |

| 4.3       | Id Execution Time                               | 47   |

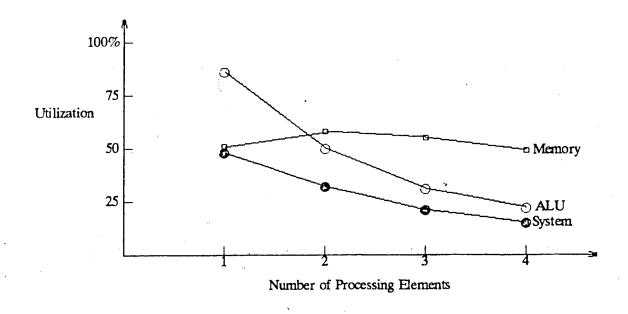

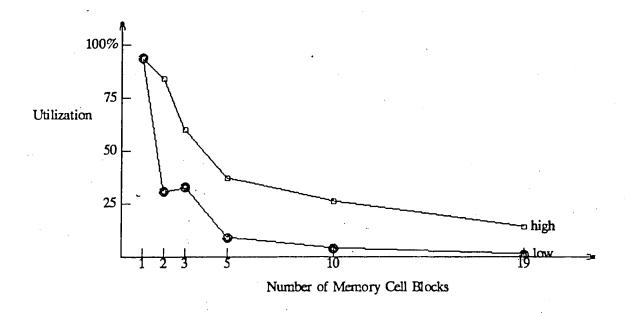

| 4.4       | Id Utilization                                  | 48   |

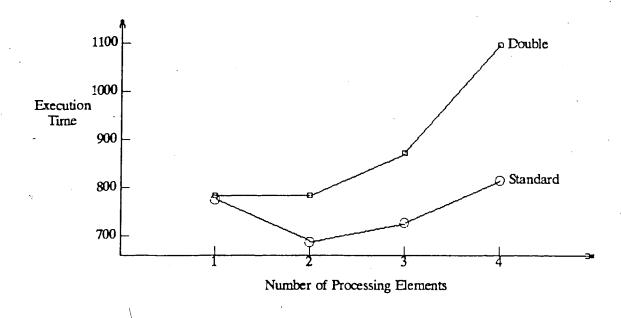

| 4.5       | Id Execution Time with Doubled Bus Time         | 49   |

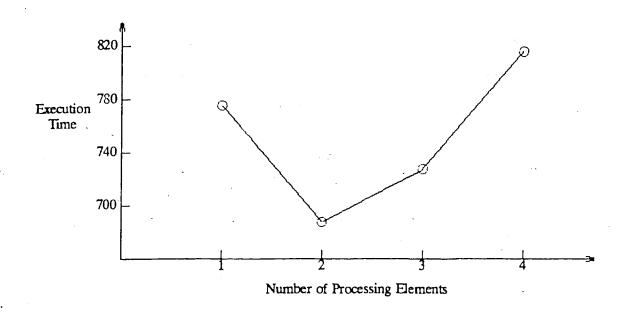

| 4.6       | MIT Execution Time                              | .51  |

| 4.7       | MIT Utilization                                 | 52   |

|           | MIT Execution Time with Two Operation Units     | 53   |

|           | MIT Memory Utilization                          | 54   |

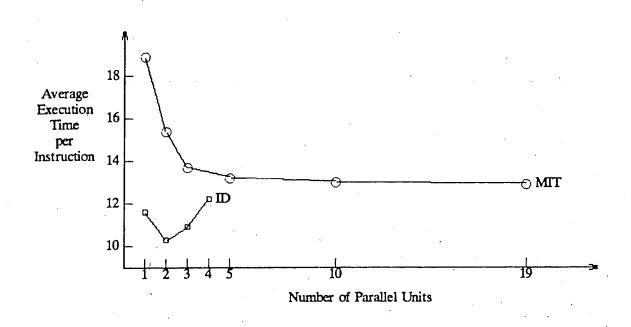

| 4.10      | Average Execution Time per Instruction Executed | 56   |

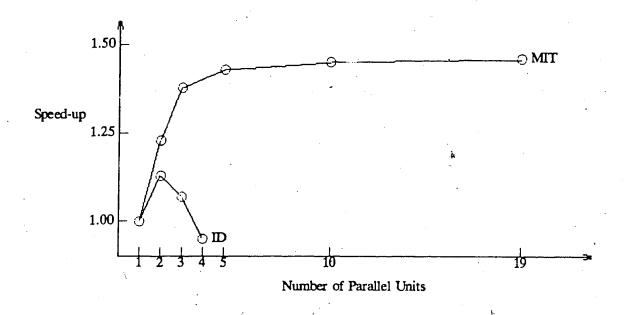

| -<br>4.11 | Speed-Up in Execution Time                      | 57   |

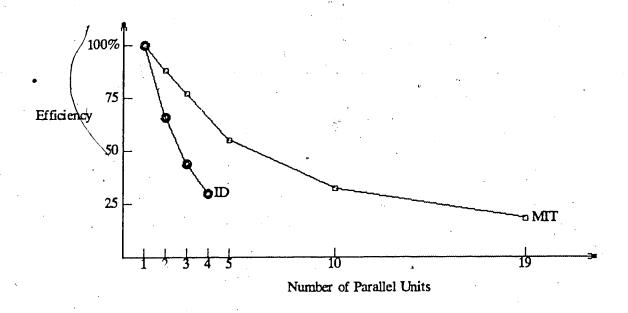

| 4.12      | Efficiency of MIT and Id Designs                | 58   |

#### CHAPTER 1

#### Introduction

#### 1.1. The Problem

Computer architecture design is a complex and expensive process. Multiprocessor computer systems are now being used to experiment with a variety of homogeneous and heterogeneous processing units, allowing simultaneous use of many resources. Dataflow computer architectures are a newer class of architectures which utilize the multiprocessor concept and are based on a data driven computation model. Although these new architectures promise increased power and speed, they complicate an already difficult task, the design of new computer systems. These architectures are both untried and inherently more complex than the traditional uniprocessor computers. What tools can be developed to manage and simplify the design process of such complex and non-traditional machines?

The increased complexity of computer systems demands a systematic and structured approach to design, and requires the use of automated tools. One desired element in the computer architecture design process is the evaluation and comparison of different proposals. Architects wish to investigate the properties of proposals based on estimated performance.

#### 1.2. Proposed Methodology

The goal of this thesis is to contribute towards a methodology for the evaluation and comparison of dataflow computer architectures. The proposed methodology

- (1) identifies parameters and performance measures appropriate to the class of dataflow computer architectures,

- (2) describes the candidate architecture using a formal language, and

0

# (3) performs a deterministic simulation of the candidate architecture.

Evaluation implies the selection of a set of performance measures and a set of parameters, both appropriate to the common characteristics and to the design goals of the class of architectures under investigation. Since, the major goal of a dataflow architecture is an increase in processing power through the exploitation of parallelism, the quantifiers must measure achieved parallelism and lost processing power due to increased communication activity. Since evaluation can be conducted only if the architecture designs are rigorously and unambiguously specified, the architecture is described using a formal language.

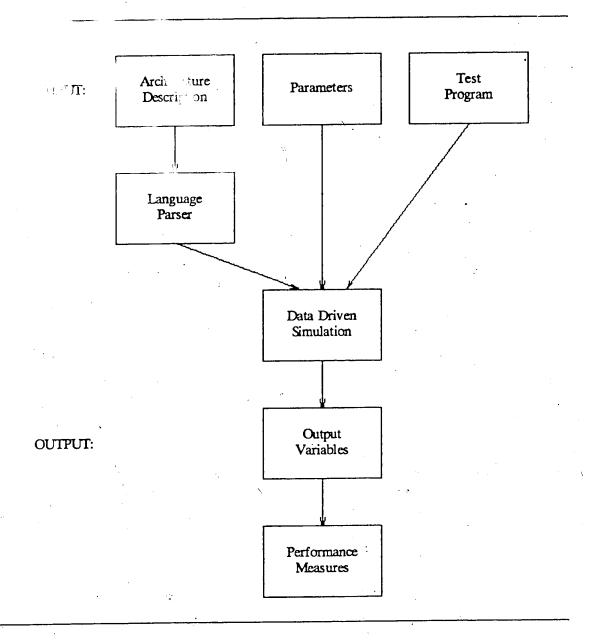

A deterministic simulation requires the selection of appropriate test programs (coded in machine language) and a simulation of the execution of these test programs. Input to this simulation will be the architecture description, test program code and parameter values. Output variables will be used to calculate defined performance measures. A data-driven simulation, along with a report generator and test recording facility, forms an automated environment for the specification and evaluation of proposed dataflow architectures.

This thesis attempts to validate the proposed methodology by applying it to the evaluation of two dataflow architecture proposals described in the current literature.

#### 1.3. Past Work

Performance measures used to evaluate traditional uniprocessor computer architectures [FuB77] are not appropriate to dataflow architectures. Two studies [GoT80,Pla76] of proposed dataflow architectures identify relevant quantifiers, some of which are included in the set of measures used in this methodology.

There are different approaches to evaluation of architectures: analysis, simulation and construction. Construction has been used to evaluate dataflow architectures [DBL80], but is expensive and therefore cannot be used to investigate decisions such as one thousand versus one hundred processing units. Construction is not feasible until late in the design process. Analytical studies have

1.3 Past Work

been performed to evaluate dataflow architectures [Jen81, Mey76, Mis76]. Analysis is difficult for complex and irregular systems and cannot react to specific input data. Simulation at the architecture level cannot predict actual performance and cost but can be used to study throughput of a system [DBL80]. Simulation is a very flexible tool applicable at many levels throughout the design process. Data-driven simulation allows experimentation with the machine instruction set as well as system structure and behavior.

Probably the most complete data-driven simulation facility is the ISPS [Bar79] architecture simulation facility at Carnegie-Mellon University. It is part of a large automated design environment which has been used for the comparison, evaluation and design of computer architectures [BaS77, VBH81]. The ISPS facility has not been used for dataflow architectures.

Gostelow and Thomas report results of experiments on a simulated version of a particular dataflow architecture executing programs written in a high level dataflow language called Id [GoT80]. The simulator is custom built for this particular machine and thus cannot be used to evaluate other designs.

A data-driven simulation facility, based on the architecture description language  $S_A^*$  [Das81] has been developed at this university.  $S_A^*$  is one member of a family of languages which attempts to cover the different levels of abstraction possible in architecture descriptions. Since  $S_A^*$  can describe asynchronous concurrent processes, a few restrictions on the use of constructs permit its application to dataflow architectures. This research uses the  $S_A^*$  language and simulator (with modifications and extensions), as the core of an experimental environment for the evaluation of dataflow architectures.

#### 1.4. Outline of Thesis

In order to define the problem further, Chapter 2 discusses in more detail dataflow architectures. Besides a description of the dataflow model of computation, resultant implications for dataflow architectures are discussed and dataflow architecture proposals from the current research

#### 1.4 Outline of Thesis

are surveyed.

, Chapter 3 proposes a methodology for evaluation of dataflow architectures. The components of the method are discussed in turn, first the choice of performance measures and parameters, second the use of a formal language for architecture description and finally the data-driven simulation facility.

The practicality of the methodology is tested and assessed in Chapter 4, where two dataflow architecture proposals from the literature are evaluated.

Concluding remarks are presented in Chapter 5.

#### CHAPTER 2

#### **Dataflow Computer Architecture**

#### 2.1. Design Goals

The demand for higher performance in computer systems has in the past been met by increasing the speed and bandwidth of uniprocessor computer systems. Speed has been increased through design solutions such as instruction pipelining, I/O channels and cache memories. Further increases in speed are becoming more difficult to achieve and manufacturers are seriously considering alternative machine architectures. Jean-Loup Baer expresses the opinion,

In order to achieve computational rates of the order of 100 Mflops with adequate precision, the architecture of supercomputers will have to depart from the strict von Neumann concept. ... Therefore, the decomposition of computations into tasks which can be executed concurrently will be mandatory. [Bae80]

Parallel processing computer systems, including multiprocessor and distributed systems, are a recognized solution to the search for more computing power. Unfortunately a multiprocessor system constructed simply by connecting multiple von Neumann uniprocessors encounters difficult problems where synchronization is concerned.

New VLSI technology is promising greater speed, reduced cost, increased reliability and reduced power consumption; therefore the constraints of VLSI technology must be considered when designing new architectures. Because of the high design cost of VLSI chips, an economic advantage is attained only if a chip is produced in large volumes. This is achieved either if the chip is widely used in a variety of products or if one computer system incorporates many identical chips. These economic factors encourage the design of computer systems using many identical complex-logic chips connected together in simple, regular structures. Traditional uniprocessor designs do not exhibit these features, hence more emphasis is being placed on multiprocessor designs.

2.1 Design Goals

John Backus [Bac78] writes forcefully of the problems inherent to conventional programming languages based on the von Neumann architecture. Besides being large and inflexible, procedural languages are difficult to prove (involve side effects) while parallel procedural languages are even worse. In short, "conventional languages create unnecessary confusion in the way we think about programs" [Bac78,p. 614]. By contrast, functional languages are simpler, more powerful and possess mathematical properties which can be used to prove programs. Unfortunately, the main drawback has been that implementation of functional languages on von Neumann architectures is grossly inefficient. Therefore Backus concludes that alternate architectures specifically designed for functional languages should be developed. Since dataflow computation is functional by nature, dataflow architectures would directly support functional languages.

The above mentioned trends in computer design are consistent with current interest in the dataflow computer as an alternative to the von Neumann uniprocessor. Research is presently being conducted in the United States, Great Britain, France and Japan. The goals of dataflow architecture as seen by these researchers are:

- (1) increased computer performance through concurrency;

- (2) exploitation of VLSI through a computer organization consisting of identical complex functional units connected together in a regular structure with little off-chip communication;

- (3) direct support of functional programming languages resulting in increased reliability due to easier verification of functional programs.

Research in Japan towards Fifth Generation Computer Systems is concentrating on four topics: knowledge-based expert systems, very-high level programming languages, decentralized and parallel computing, and VLSI technology [TrL82]. Knowledge-based expert systems will require high computer performance. It is likely that a dataflow or reduction architecture will be employed in the Fifth Generation computers as they directly support functional programming languages and pursue higher performance through exploitation of concurrency and VLSI.

### 2.2. Dataflow Computing Model

A computer system is based on an underlying computing model. The components of the system, namely programming languages, operating system and machine architecture, maintain consistency with one another because they are all based on the same computing model [DaD80].

The von Neumann computer architecture is the most prevalent computing model on which computer systems are based. Work began in 1946 at Harvard University to design the IAS computer. It is now considered the prototype of all subsequent general purpose computers [Hay78]. John von Neumann headed the design team of the IAS, hence the term von Neumann architecture is implicitly defined by the characteristics of the IAS computer. Those characteristics are:

- (1) Instructions and data are stored in main memory (stored program concept).

- (2) The computer is organized with one main memory and one central processing unit (CPU). A fixed number of bits form a word (IAS had forty bits to one word) and one word at a time is transferred between main memory and the CPU.

- (3) The CPU initiates all control signals which are synchronized by a central clock.

- (4) The instruction cycle consists of two consecutive steps: instruction fetch and instruction execute.

- (5) An instruction does not explicitly contain the address of the next instruction to be executed.

Unless otherwise directed the next instruction to be executed is the next sequential instruction of the program. A program counter maintains the address of the next instruction and this program counter is one of a number of registers within the CPU.

- (6) Two's complement arithmetic is used.

- (7) Instructions are composed of an opcode and an operand address.

Computer systems have certainly advanced since the IAS but the seven characteristics cited above remain the basis of most computer systems.

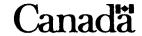

The dataflow computing model [DaD80, TEH82] is derived from a program representation, not from a computer architecture as is the von Neumann model. A dataflow program can be mapped to a directed graph where the nodes represent operations to be performed and the arcs represent the data paths between nodes. A node (operation, activity) acts (fires) only when each of its input arcs contains data values (tokens). On firing of a node, all input tokens are destroyed and a result token is produced and placed on all outgoing arcs. An arc operates as a first-in-first-out queue, delivering one data token at a time to the consuming node. A node may have any number of input and output arcs. All data flows forward in the directed graph and each node fires when all of the data required by its input arcs is available. It is not possible to determine the absolute order of node firing; but nodes requiring input data tokens produced by other nodes always fire after the latter. Therefore the sequencing required is solely determined by data dependencies within the program. An example of a computation represented as a directed graph is shown in Figure 2.1.

Figure 2.1 Computation as a Directed Graph

z - (a + b) \* (c - 5)

#### 2.3. Implications of the Dataflow Model

This abstract dataflow computing model forms the basis for the design of dataflow computer architectures. Computer architecture may be informally defined as the structure and behavior of a computer, but a computer architecture can be examined at many levels from the detailed circuit-level to the processor-memory-switch (PMS) level of Bell and Newell [BeN71]. An appropriate abstraction level during the initial design process is the endo-architecture level.

Endo-architecture typically includes the functional capabilities of a machine's physical components, their interconnections, the nature of the information flow between components, and the means whereby this flow is controlled. [Das81]

The following discussion considers computer architecture at the endo-architecture level and is organized into three topics similar to those examined by Treleaven [TBH82]: program organization, execution cycle and machine organization. Program organization includes the representation of machine language programs. The execution cycle describes the sequencing and results of execution. Machine organization refers to the configuration of machine resources and their allocation to support program organization.

#### 2.3.1. Program Organization

In the von Neumann model a variable is synonymous with a storage location, and an operation normally involves fetching data values, performing a computation and updating a storage location. In contrast, dataflow data values are not stored, but exist only as tokens in transit from producer to consumer node. Theoretically, the value of a variable is never updated, therefore high level dataflow programming languages uphold a single-assignment rule whereby a variable can be assigned a value only once. With no updating possible, synchronization of access to variables is not a problem, and all instructions which are not data dependent can be executed simultaneously thus allowing concurrent computation within one process.

As well as a value, a data token must contain the name or address of its destination instruction along with other information such as processor address, unique code block identifier, iteration number, argument number, number of arguments required and the name of the producing instruction. Therefore data tokens require more space in transit than the equivalent data value would require in the memory of a von Neumann machine. If dynamic concurrency as well as static concurrency<sup>1</sup> is desired then more information is required to insure uniqueness of destination addresses.

Results of computations can be used as input by more than one instruction, hence a machine language instruction must include names and information for all destinations. Other information required in instructions includes: opcode, opcode dependent information (decision flags, alternate routes), value of a constant and operand number, number of destinations, number of operands, operand flags, acknowledgement signals, number of acknowledgement signals required. As indicated, dataflow instructions are complex and lengthy.

Since dataflow programs do not explicitly control the sequence of execution, high level language programs are simpler to construct. Data flow program organization is very efficient for evaluation of simple expressions and support of procedures and functions with call by value parameters [TBH82]. On the other hand dataflow program organization is not good at manipulation of shared data structures.

#### 2.3.2. Execution Cycle

Logically, every instruction in a data flow program is active and has a processing element allocated to it, waiting for arguments to arrive. When all arguments have arrived the computation is performed, the arguments are destroyed and the result sent to each of its destinations. The processing element then becomes idle. If all instructions are data-independent, then theoretically all instructions could execute simultaneously. No control information is needed because execution is initiated asynchronously upon the arrival of data. No program counter is needed because all

<sup>&</sup>lt;sup>1</sup>Static concurrency refers to the concurrency made possible by data-independence. This concurrency is evident at compile time. Dynamic concurrency refers to the concurrent execution of different loop iterations or function invocations. Dynamic concurrency is determined during execution.

sequencing is implicit through data dependency. A result token is the only result of execution. It would appear then that the execution cycle of a dataflow architecture is extremely simple and since no clock or synchronized activity is required a distributed environment is possible.

#### 2.3.3. Machine Organization

As previously stated, each instruction is in principle active with a processing element allocated to it. In reality, it would be wasteful of computing resources to allocate one processing element to each instruction. Rather, the essential task of a dataflow computing system is to find executable instructions and then to allocate them to the appropriate resources.

Treleaven describes two ways of solving the problem of finding an executable instruction: token storage and token matching. In token storage the values of the operands are stored with the instruction in memory. Production of a result token will cause an update of all destination instructions (i.e. the program itself is changed). Some mechanism must search memory to find complete instructions and fetch them to a processor for execution. Alternately, token matching requires a separate memory for result tokens. Each new result token is matched up with other tokens bound for the same destination. When a set of instruction operands is complete, the set of operands is released and activates execution of that instruction. Program code is not modified as it is in token storage, therefore token matching supports reentrant code.

The asynchronous concurrent nature of dataflow programs suggests a computer system composed of more than one processor, where each processor acts independently and the whole system has no central control. A distributed system of independent processors can be realized in many ways. If each processor is specialized then a communication network is needed to route an instruction to the appropriate processing element. If all processing elements are identical then an idle processor must be found.

Instead of each processor performing all decision making and computation, it is possible to separate the processor into many units each with a particular function to perform within the

instruction cycle. Some functions to be performed are: token matching, insertion of operands into instructions, determining if an instruction is executable, fetching instructions, composing operation packets, performing computation and constructing tokens from results. Separate units performing different functions on different instructions can operate concurrently.

#### 2.3.4. Summary

The data flow computing model suggests certain characteristics in a data flow architecture. The independent concurrent nature of instructions implies many processors (either identical or specialized) performing arithmetic and logical computations. The asynchronous aspect of the execution cycle suggests specialized functional units (e.g. token matching, token production, token routing, memory updating) operating concurrently and communicating with each other asynchronously. Since the results of computation are local and memory need not be shared, distributed control and memory are possible. Therefore a dataflow architecture is likely to be a multiprocessor system with asynchronous communication and distributed control.

- More specifically, the representation of programs must be concerned with:

- (1) the set of primitive operations (e.g. arithmetic, logical, data structure manipulation, token selection and routing);

- (2) machine language instruction format;

- (3) data token format;

- (4) use of control tokens;

- (5) appropriate high level languages and their translation to machine level instructions.

The structure of the architecture must reflect decisions concerning:

- (1) functional units required;

- identical or specialized functional and computing units;

2.3.4 Summary 13

- (3) communication paths between units;

- (4) distribution of program and data storage.

The behavior of the architecture must solve the following problems:

- (1) determining if a node is ready to fire (token storage and token matching are two current solutions);

- (2) mapping of instructions to computing elements and programs to storage;

- (3) dynamic node replication.

#### 2.4. Survey of Dataflow Architectures

Researchers are currently investigating the feasibility of the dataflow computing model.

Many dataflow architectures have been proposed. The following is a brief description of five proposals, which are often cited and reveal the variety of approaches to the problem. Both Treleaven [TBH82] and Davis [DaD80] have produced comprehensive surveys of the current research.

#### 2.4.1. MIT Machine

Extensive dataflow research has been conducted at the Massachusetts Institute of Technology (MIT) Computer Structures Group under Jack Dennis. Topics of research include high level dataflow programming languages and translators, decomposition of programs, architecture, routing networks and logic simulators [Mas80].

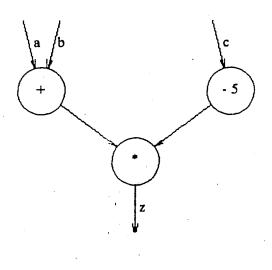

The Dennis/Misunas proposed dataflow architecture [DeM75, DLM80] is composed of a memory subsystem, a operation subsystem and three communications networks (see Figure 2.2). The memory subsystem stores instructions and their operands in instruction cells. The operation subsystem is composed of special purpose processing elements which perform arithmetic and logical computations. The arbitration network is a switching network which receives executable instruction packets from the memory subsystem and sends them to the appropriate processing element in the operation subsystem. The distribution network is a switching network which receives data

2.4.1 MIT Machine

Figure 2.2 MIT Machine

packets and sends them to the memory subsystem. The control network performs a function similar to the distribution network, except that the control packets are either data values of type boolean bound for conditional or iterative control instructions or are acknowledgement signals sent to producing instructions. The memory subsystem receives data and control packets through the respective networks, and stores these into appropriate instruction cells as they arrive. If the receipt of a token makes an instruction executable, an instruction packet is created and sent to the operation unit through the arbitration network. All communication between the five units is

asynchronous.

The structure of this dataflow architecture introduces parallelism by allowing each cell in memory concurrent access to the operation unit through the arbitration network. Parallelism is also introduced by the specialized processing elements in the operation subsystem which allow concurrent execution of different primitive operations.

A unique feature of the MIT machine is the firing rule. A node fires when it has received its complete specified firing set and its output arc is empty. Therefore each arc holds only one token, an arc is not a queue. If an instruction cell has received its complete firing set and it has received an acknowledgement signal signifying consumption of its previous result token, then it is executable and will send an instruction packet to the arbitration network. The acknowledgement signal is necessary to enforce the one token per arc rule.

#### 2.4.2. DDMI Machine

The DDM1 (Data-Driven Machine #1) project resides at the University of Utah under the direction of A.L. Davis [DaD80].

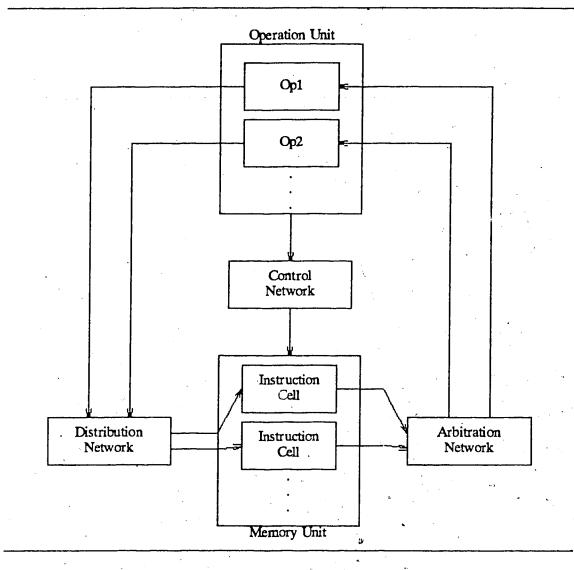

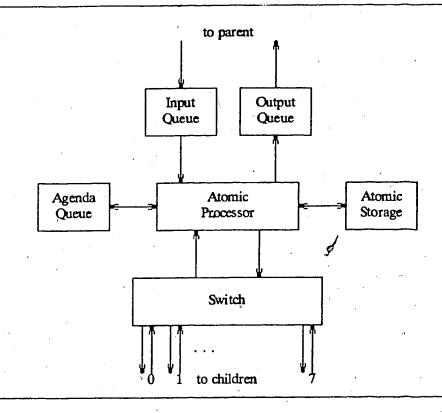

This machine is a tree-structured multiprocessor composed of identical processors each having up to eight child processors. Communication between processors is asynchronous. No control tokens are used in the system and arcs act as first-in-first-out queues. A processor (see Figure 2.3) is composed of an atomic storage unit (stores instructions and operands), an atomic processor (performs operations), an agenda queue (stores messages), an input and output queue (communicates with the parent processor) and a switch (communicates with child processors).

Program instructions are allocated to processors based on the following principle. A processing element receives a subprogram from its parent. If the subprogram cannot be further decomposed, it is stored in the local atomic storage unit. Otherwise the subprogram is divided and sent to the child processors.

Figure 2.3 DDM1 Machine

The atomic processor performs arithmetic, list structuring and routing operations. The atomic processor takes messages from the switch, the agenda queue and the input queue in that order of priority. A received data token is either routed to another processor or if its destination instruction is in the local atomic storage unit it is inserted into the instruction. If the instruction is executable, the appropriate operation is performed and the result token is placed in the output queue, switch or agenda queue. Concurrency is achieved through identical processing elements.

A unique feature of this architecture is its hierarchical structure. Data tokens are list structures and storage is organized as a list structured file. Also, programs are decomposed to subprograms, not to individual instructions.

#### 2.4.3. Id (Irvine Dataflow) Machine

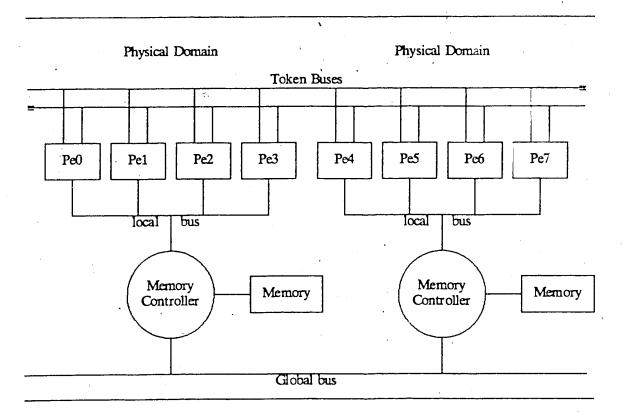

The Id machine [AGP78, GoT80] is composed of many identical processing elements which communicate through two token buses (see Figure 2.4, the processing elements are labeled Pe0, Pe1, ...). An arbitrary number of processing elements (4) are grouped together to form a physical domain. As well as processing elements, the physical domain contains a memory controller and memory store. Each processing element communicates with its local memory, but all local memories are connected by a global memory bus. The address space of the whole system is unified.

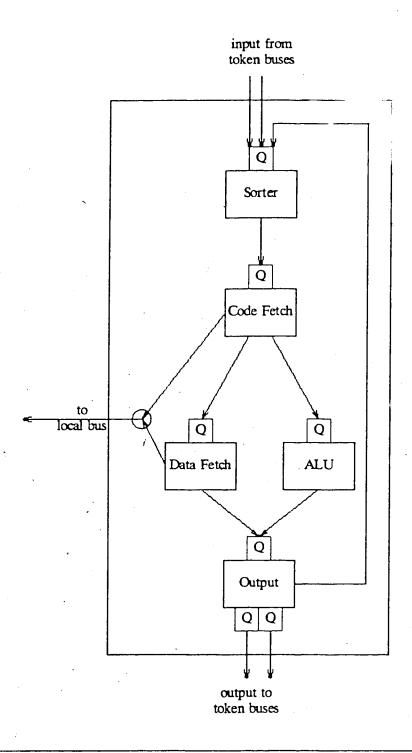

Each processing element (see Figure 2.5) consists of special purpose functional units which communicate asynchronously through data tokens. There are no control tokens. The token buses act as shift registers and rotate in opposite directions. Each processing element accesses one slot of

Figure 2.4 Id Machine

cach token bus. The processing element examines are data token in the slot and if it has its address, the data token is removed from the slot and placed in an input queue to the sorter. The sorter matches this data token with others bound for the same instruction and if the required number of operands have arrived, the operands are packaged and sent to the code fetch unit. The required instruction is fetched from local memory and the stated operation is performed by the arithmetic-logical unit (ALU). An output unit takes results from the ALU and forms result tokens including the addresses of the destination processing elements. These result tokens are placed in slots on the token buses. All functional units within the processing element maintain first-in-first-out input and output queues.

A unique feature of this architecture is the unfolding interpreter which dynamically replicates program loops (iterations, procedures) to achieve more concurrency. More complex token identification (tags) and operators which alter tags are needed to support this interpretation. This identification scheme is used to assign activities to processing elements with locality in mind, (i.e. a block of program code is assigned to a physical domain) so that result tokens need not be transferred great distances. This machine also supports structured data types and accesses these by reference rather than by value.

The Id machine achieves concurrency through the many identical processing elements, independent functional units within each processing element, and through the unfolding interpreter.

#### 2.4.4. Systeme LAU

Research on the Systeme LAU dataflow architecture is pursued at the CERT Laboratory in Toulouse, France. The architecture is based on a high level language LAU which is almost directly executed.

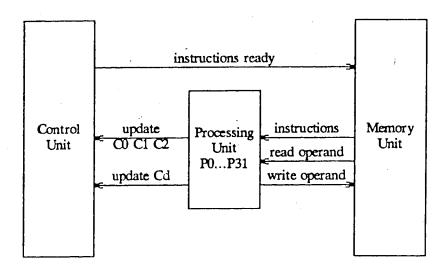

The machine [Pla76, SCH77] is composed of a processor subsystem (thirty-two identical processing units), a memory unit and a control unit (see Figure 2.6). The memory unit stores instruc-

Figure 2.5 Id Processing Element

Figure 2.6 LAU Machine

Memory and uses these to determine which instructions are executable. The Instruction Control Memory is served by two functional units which update and search the Instruction Control Memory. The Instruction Control Memory contains three control bits for each instruction in memory and when these bits are set to all ones, indicating that all data operands are available, the address of the corresponding instruction is sent to the memory unit and the control bits are reset. The memory unit fetches the instruction and puts it on the input queue to the processor subsystem. An idle processor accesses this input queue and fetches the required operands and executes the instructions. Afterwards, results are written to memory and the appropriate bits in the control memory are set.

The unique feature of this architecture is the control unit which controls the mabling of instructions. Concurrency is supported through the thirty-two identical processing elements and the independent control, memory and processor subsystems.

21

#### 2.4.5. Manchester University (MU) Machine

The Manchester University (MU) dataflow computer is described in Watson [WaG79]. Research has included the design of a high level dataflow language called LAPSE, which is directly supported by the architecture.

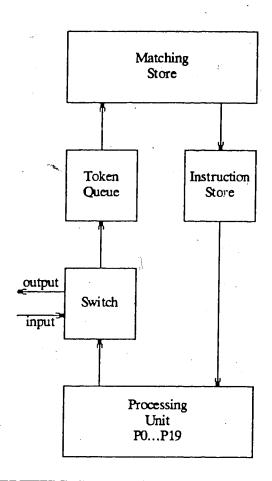

The machine is a ring composed of three units: matching store, instruction store and processing unit. A switch manages external communications, and a token queue acts as a buffer to the matching store (see Figure 2.7).

The matching store takes a token from the token queue and if this token is the only input required for an instruction, it passes it directly to the instruction store. If the token is one of a pair, the matching store searches for its partner and packages them together and sends them to the instruction store. If the partner is not present, the token is stored in the matching store. Upon receipt of a token packet the instruction store fetches the instruction and passes the packet to the processor unit. A distribution system within the processor unit sends the instruction packet to any idle processing element (a twenty-processing element unit is under construction). The processing element performs arithmetic, comparison and token management operations. After execution the arbitration system within the processing unit produces one or two result tokens. The tokens proceed through a switch which also manages input and output with external sources and passes tokens on to the token queue.

All units operate asynchronously, thus parallelism is achieved through the independence of these units and through the identical processing elements within the processor unit.

Besides the value and destination field, tokens also specify the process, argument number, and iteration of the token. This tagging is similar to the Id machine and permits reentrant code. The token matching scheme is also similar to the Id machine but the matching and instruction stores are centralized rather than distributed.

Figure 2.7 MU Machine

#### **CHAPTER 3**

#### Evaluation Methodology

Although the dataflow computing model is conceptually simple, the dataflow architecture proposals are often complex, involving separation and replication of function to an unusual extent. This complexity increases the need for evaluation during the early design stages.

#### 3.1. Experimental Model

Presented here is an experimental design for the evaluation of dataflow computer architectures. In a more general sense the object is to study a proposed computer architecture with the intent of optimizing its predicted performance. To optimize performance, quantitative performance measures must be established and hypotheses made concerning which elements of the architecture (i.e. parameters) have a causal effect on those measures. With parameters and performance measures defined, experiments to study the architecture must be designed. The most direct way to study the architecture would be to implement the architecture as a physical machine and conduct tests by varying parameters. This approach is neither feasible nor desirable, because it would introduce another variable, the implementation. A more practical approach is the construction of a model whose behavior can be examined by simulating it on a computer.

A model is a representation of the behavior and structure of a system. A computer program uses this representation to generate behavior consistent with the model. This method of study is repeatable and many tests can be conducted in a short period of time. Models can be expressed in various ways: mathematical relationships, logical rules, formal languages, statistical probabilities.

The model which is proposed here (see Figure 3.1), describes the components of a computer architecture and their interaction using an architecture description language. The components of a computer architecture are the functional units and the data paths between them, while component interactions refer to the data exchange and means of controlling communication between

components. The architecture description is not at the gate or latch level but at the logical functional component level (i.e. endo-architecture).

The input variables of the model are a test computer program coded in the instruction set of reticular architecture, data required by that program and parameter values. The input variance of the model, consequently this model

Figure 3.1 The Modeling Process

is data driven and deterministic, rather than stochastic.

A computer simulation program simulates the behavior of the computer architecture (i.e. it executes the program code). This is the simulation of the execution of a single job on a computer architecture not a multiprogramming job stream on a computer system. The simulation is monitored to produce statistics which summarize the behavior of the architecture and are used to produce performance measures.

#### 3.2. Performance Measures and Parameters

The choice of performance measures and parameters for this study was based on both a review of previous research and an examination of the characteristics of dataflow architectures as discussed in the preceding chapter.

The United States Army/Navy Computer Family Architecture (CFA) Committee [FuB77] developed a methodology for quantifying relative performance of alternative architectures. They wanted to compare architectures independent of existing implementations. The comparison consisted of three phases: an initial ranking based on a set of absolute and quantitative criteria, a test program evaluation and consideration of software support and life-cycle costs. The first step reduced the set of nine candidate architectures to three acceptable architectures: IBM 370, PDP11 and Interdata 8/32. Those were evaluated using twelve test programs written in machine code. The following measures of performance were used:

S- number of bytes required for the test program in main memory

M- number of bytes transferred between main memor/ and the CPU.

R- number of bytes transferred among internal registers of the central processor.

The rationalization for these measures was that a higher S implied a higher cost for more hardware, a higher M or R implied a longer execution time. Implementation details (cache memory, instruction pipelining) can of course affect these conclusions but they are not characteristic of the architecture. Since a dataflow architecture achieves greater speed through simultaneous

execution of instructions, the CFA study assumption of sequential execution is violated. Therefore, M and R measures would not be indicative of execution time in a dataflow architecture.

It is important that any performance measures used to evaluate dataflow architectures consider concurrency. A standard von Neumann computer architecture does not specify instruction execution time, because this is normally considered part of the implementation. But it is impossible to evaluate dataflow architectures without estimates of relative time required by each functional unit (cycle time). It is necessary to incorporate the concept of time to determine which functions are being performed concurrently. Using these relative cycle times as parameters, the designer can determine an optimal set of cycle times, which can then be sought during the hardware design phase.

Ruby Lee [Lee80] of Stanford University describes an experiment which investigates the optimal number of processors in a parallel processing system. The measures of performance used by Lee were of four types: speed of execution of a test program, utilization of resources, compression of the computation and quality of processing. Speed of execution was measured by the parallel index (i.e. ratio of number of operations in the computation to execution time in steps) and by speed-up (i.e. ratio of execution time of the serial computation to that of the parallel computation). Utilization was measured by utilization (i.e. ratio of processor busy time to execution time) and efficiency (i.e. ratio of number of operations in the serial computation to the product of execution time and number of processors). Compression was measured by redundancy (i.e. ratio of number of operations in the parallel computation to number of operations in the serial computation) and compression (i.e. inverse of redundancy). Quality was a composite of other measures, defined as the product of speed-up, efficiency and compression. The parameters used by Lee were number of processors and configuration of the system.

Gostelow and Thomas [GoT80] report results of experiments conducted by simulating a proposed dataflow architecture. The performance measures used were execution time of a program, processor efficiency (busy time / execution time) and mean cycle time. The parameters were number of processing elements, memory bus speed, problem size, different problems and assignment functions (i.e. mapping of operations to processing elements). With these performance measures and parameters it was possible to investigate optimal number of processing elements and bottlenecks in the system.

Results of simulation tests on the LAU dataflow architecture are reported by Plas [Pla76]. The performance measures used were execution time and average parallelism achieved. The parameters used were number of functional units (processors, memory units), cycle time of functional units, parallelism of the problem and varying source programs.

The choice of performance measures and parameters is of course dependent on the purpose of the investigation. The present purpose is to help make decisions regarding the endo-architecture of a proposed dataflow architecture. By re-examining the characteristics and architecture attributes presented in Chapter 2, it can be seen that the object is to help answer questions about the structure, behavior and program representation of the architecture. These are rather arbitrary divisions since all elements of the endo-architecture are interdependent. Usually the designer makes decisions about the program representation first and then attempts to find an appropriate structure. Experimental investigation is required first at the structural and behavioral levels, where relevant questions are:

- (1) What functional units are required? A decision on the separation of function implicitly defines the execution cycle. The distribution of program and data storage determines the nature of memory (central versus distributed).

- (2) How many of each functional unit are required? The replication of function determines how parallelism is achieved through the structure. Are identical or specialized functional and computing elements desired?

- (3) What communication paths will connect the units? Are control paths included as well as data paths?

- (4) How will dynamic mapping of instructions to computing elements and static mapping of programs to storage be determined?

- (5) What will be the relative cycle times of functional units and speed of buses?

- (6) What problems are best suited to the architecture?

- (7) Is there a specific amount of concurrency which best fits the architecture?

Performance measures and parameters which are appropriate to both the class of dataflow architectures and the goals of this thesis are listed below.

# Performance Measures

- (1) execution time (ET)

- (2) utilization (U)

- of one functional unit (U=busy time/ET)

- of system (U=total busy time/n\*ET where n=number of functional units)

- (3) speed-up (ET sequential/ET parallel)

- (4) efficiency (ET sequential/n\*ET parallel)

- (5) average wait time (the average time a token waits for a functional unit)

### **Parameters**

- (1) configuration: what and how many functional units

- (2) relative cycle times of functional units

- (3) test programs

- (4) degree of concurrency of the problem

### 3.3. Architecture Description

An important decision to make in the modeling process is how to represent the computer architecture. The choice of a representation depends on both the purpose of the modeling process

and the level being investigated. The purpose here is to represent an evolving design within the class of dataflow computer architectures, where modeling results will indicate possible improvements to the design. These alterations will then be incorporated into the current design for reexamination. Given this purpose, what characteristics are desired in a representation?

The representation must be suitable for all proposals within the class of dataflow architectures, therefore a simulator developed for one particular architecture which implicitly describes the architecture through its behavior is not appropriate. The representation must be explicit, objective and suitable to the whole class of dataflow architectures.

In order for a description to be easily changed it must be readable by humans. Humans find it easier to understand descriptions which are represented familiarly, are modular in structure and are presented in more than one manner (e.g. visually using diagrams and logically using notation). Various points of view and levels of abstraction (e.g. overall structure and the detailed behavior of one unit) also contribute to understanding.

Precision is another required characteristic since an optimizing process hopes to identify precisely the factors affecting performance.

As the optimizing phase is only one phase in an overall design process, it is reasonable to expect the description in this phase to contribute to the construction of descriptions at later stages. This description should translate into more detailed designs at the hardware level and therefore should be understood by hardware designers as well as computer architects. Also the representation should be machine readable so that translations and changes can be performed by machine thus contributing to an automated design process.

Computer architectures are often informally described through block diagrams showing structure and interconnections (as in Chapter 2) with accompanying natural language descriptions. Although this method is appropriate for overall understanding of general principles, it is not precise and fails for complex designs. A more formal representation would use mathematical or logical notation or a programming language.

Especially appealing is a computer programming language since computing professionals are already familiar with this form of representation. The block structured programming languages encourage modularity and allow alternate levels of abstraction. Computer programming languages are machine readable thus allowing easy translation to other design levels. Creating or changing a description using a programming language is facilitated by many tools such as compilers and editors, which promote automated development. General purpose programming languages have been used to describe computer architectures, but a better mapping between architectural components and language constructs can be achieved using an architecture description language (alternately called computer hardware description language or computer design and description language). An architecture description language is an appropriate representation for an architecture description in an optimizing design process.

Since the endo-architecture is to be examined, it must be determined how this level affects the choice of architecture description language. Within a single user dataflow computer system or subsystem, under examination are the functional units, communication paths and execution cycle behavior. The basic entities [Mak82] of such a system are: instruction set, data tokens, control tokens, and a set of cooperating processes. A dataflow instruction set will contain ordinary arithmetic, relational and logical operators, control constructs to control execution paths and data structure manipulation operators. Data and control tokens may be of variable length, accessed by bit rather than by word.

A dataflow architecture is fundamentally a set of cooperating processes, executing concurrently, initiated asynchronously by the flow of data tokens. A dataflow process abstracts easily to the concept of an asynchronous module as discussed by Keller [Kel74]. An asynchronous module is independent and its "activity is regulated by initiation and completion signals, with no clocks being present" [Kel74, p. 21]. This abstraction to a set of asynchronous modules exists at many levels, but the concern here is with the system architecture level where a processing element (e.g. ALU, sorter, memory controller) is activated upon receipt of a data token. The result of this

activation is a new data token sent to another processing element. The results of computation are not affected by the order of arrival of tokens. Theoretically, there are no side effects and all global variables are represented as data abstractions (i.e. protected within a monitor).

Processes are likely distributed throughout the system on independent physical components. Token passing may therefore require external communication paths such as buses. Since processes operate concurrently, and independently send messages to other processes, facilities must exist for queuing messages upon arrival. A dataflow architecture is often a collection of identical processors or subsystems, and processes may contain complex data objects such as associative memories, queues and stacks.

In summary, a description of a dataflow architecture at the endo-architectural level must describe instruction set, tokens and processes executing concurrently. Particular properties of these have been cited above. Can existing architecture description languages accommodate such a description?

architecture description languages have been developed. A comparison of computer scription languages is presented by Makarenko [Mak82] and a general discussion of description language research is presented by Dasgupta [Das82]. ISPS [Bar79] is the best known hardware description language and was developed from ISP, first proposed in 1971 [BeN71]. It is a general purpose language and forms the base of a computer-aided design facility at Carnegie-Mellon University. ADL [Leu79] is a specialized language designed to describe packet communication systems which are systems composed of modules communicating by sending information packets to each other. An ADL description is organized into modules, each with a specified input and output and further division into sub-modules which contain behavioral descriptions. Sharing of data is controlled by monitors within a module. Sub-modules are easily replicated and the number of replications can be based on a parameter data type. Since a dataflow architecture is a packet communication system, ADL would have been an acceptable choice for this study.

The architecture description language used in this study is SA, a general purpose language developed as part of a family of description languages [Das81, Das82, Das83]. SA was chosen because an S\* simulation facility exists at this university, thus providing an opportunity to test and extend the use of these tools to the class of dataflow computer architectures. Sa is a block structured language in the likeness of Pascal, whose highest level modularization construct is the system. A system may be composed of other systems but at the lowest level it is composed of mechanisms. The mechanism is the most important structuring construct. It acts as a critical section and as a data abstraction block, such that variables declared within the mechanism are accessible only to procedures within that mechanism. Mechanisms are initiated through calls to their public procedures; the calls are queued if the mechanism is already active. Although  $S_A^*$  is basically procedural, mechanisms can be initiated at start up and can continue execution without waiting for the completion of other mechanisms which they have activated. Consequently, mechanisms will execute concurrently. The primitive data type is the bit, but user defined types are allowed and can be composed of the following data structures: sequence, array, tuple, stack and associative usual Algol-like constructs,  $S_A^*$  includes an operator which denotes conarray. As well as 🗀 current execution of statements. Although synchronization constructs are available, there is no way to refer to absolute time or to associate delay time with any construct. The mapping of S\* constructs to dataflow components is discussed in Chapter 4.

### 3.4. The Simulation Facility

The  $S_A^*$  simulation facility was developed by Makarenko in 1982 [Mak82] and has not previously been used as a research tool. Although the simulator does not implement all  $S_A^*$  constructs, it does provide an adequate subset. The simulator produces the following statistics: the number of times a sequence variable is read or written, and the number of times a mechanism is activated. As a first step in the simulation process, an  $S_A^*$  description is input to the compiler which produces a parse tree. The parse tree is used as input to the simulator, whose execution is controlled by user commands. Thus the user can assign values to variables within the description and introduce

the code of a test program. During a simulation, concurrent execution of mechanisms is achieved by executing each active mechanism in turn for one tinestep. The scheduler simply advances cyclicly through the list of mechanisms, and whenever an active mechanism is encountered, the first executable statement on that mechanism's executable statement list is executed. In this manner, an appearance of concurrency is achieved. All calls to a procedure whose encompassing mechanism is already active are queued in incoming order.

The simulator described above did not provide statistics which could be used to calculate the measures specified previously as desirable for the evaluation of dataflow architectures. The statistics required were: test program execution time, system and functional unit busy time and average wait time for each functional unit. Also, the simulator implementation of the S\* activate construct was not appropriate to dataflow asynchronous processes. Extensions and modifications to the simulation facility were undertaken to incorporate the above requirements. The changes involved new input and data collection within the simulator, a new implementation of the activate construct, and a new scheduling algorithm. As well, the simulator command language was extended to generate a report. The modifications made to the simulator are described in the remainder of this section.

All of the performance measures mentioned above require the concept of time and require the maintenance of cumulative elapsed time of each parallel execution path during the simulation. Time can be introduced by associating an execution time with each statement, procedure or mechanism. Because a mechanism contains procedures, it is too gross for accurate timing. Associating execution time with each statement would provide more detail than is needed at the endoarchitecture level and would require information too specific for this phase of the design process. The procedure appears to be the right level for timing because it provides a suitably flexible block which the designer can subdivide if more detail is desired.

The next consideration is how to incorporate time into this facility. Should the language itself be extended to associate a delay time with each procedure declaration or should the simulator

be modified to accept procedure execution times? Since relative cycle times are to be used as parameters in the evaluation, it is reasonable that procedure times should be an input to the simulator. Changing the times for tests will then be convenient since they will be together in a separate input file rather than distributed throughout the  $S_A^*$  description. There are, it was decided to associate a fixed execution time with each procedure and input this data as a separate file to the simulator.

In order to collect execution time, busy time and wait time statistics, it was necessary to add data structures and variables within the simulator. First an extra field was added to the procedure record to store procedure execution time. Next the mechanism record was extended to store the mechanism total busy time, total wait time, real time and earliest pending call (of current queued calls). Every time the mechanism is activated (i.e. one of its procedures is invoked) the total busy time is increased by the execution time of the called procedure. Total wait time is also updated at this point to include the length of time the procedure call waited for this mechanism. Real time is calculated by selecting the larger of the mechanism's current real time and the time this procedure was called, and adding the procedure time. The real time is therefore the cumulative elapsed time of that execution path. The earliest pending call field is updated only when a new call is queued for that mechanism or when a call is removed. The queued calls are a list of pending calls sorted by time called, except that private procedure calls are always put on the front of the list. The execution of a call or activate statement inserts the real time of that mechanism as the time called field on the pending call record attached to the called mechanism. When execution of a test program is complete and simulation stops, statistics can be collected for reporting. Each mechanism record is examined to determine the maximum real time, for this is the longest time required by any execution path and hence is the execution time of the test program. Mechanism busy time is directly available and average wait time is calculated by dividing total wait time by number of activations.

A new method of scheduling mechanisms was required since the previously used round robin method would execute mechanisms in the wrong order and invalidate the real time of mechanisms. For example, if two mechanisms each queued a call at five and ten time units respectively, then the call at time five must be executed first because during its execution it could call the other procedure and this call should be put on that queue before the previous call at time ten. The new scheduling algorithm maintains the list of mechanisms sorted in ascending order of earliest pending call, those mechanisms with no pending calls are on the end of the list. The list is updated when a procedure terminates and also when a new call is queued for any mechanism. Mechanisms are selected from the front of the list for execution.

Another alteration to the internal operation of the simulator involves the implementation of the activate construct. The call construct was implemented such that the caller became inactive and waited for completion of the called routine which might return results through parameters. In contrast, the activate construct suspended the caller until allocation (passing arguments and activating the mechanism) of the called routine, at which time the caller became active again and resumed execution. No results could be passed back at completion of the called routine. In both cases, the caller was required to wait for allocation of the called routine. This implementation was not compatible with the asynchronous initiation and concurrency of processes in the dataflow model, which requires that the caller not wait for any length of time. Consequently, the activate implementation was changed so that the caller does not wait for allocation. Instead, execution of the activate statement creates a new record to hold the values of the arguments passed. This argument list record is attached to the queued call and execution of the caller continues. In effect, the actual parameter is now bound to the formal parameter at the time of the call rather than at invocation. Makarenko chose to bind parameters at the time of invocation because

There are very few hardware components that operate in a fashion where they can be activated from a number of different spots, with no acknowledgement given to the caller. [Mak82,p. 91]

However, this form of activation is precisely that of data flow processes, consequently binding must be done at the time of the call so that the caller can be released to continue execution. Otherwise, mechanisms would not be executed in the correct order.