# Large-Scale Nonlinear Device-Level Power Electronic Circuit Simulation on Massively Parallel Graphics Processing Architectures

Shenhao Yan, Member, IEEE, Zhiyin Zhou, Student Member, IEEE, and Venkata Dinavahi<sup>10</sup>, Senior Member, IEEE

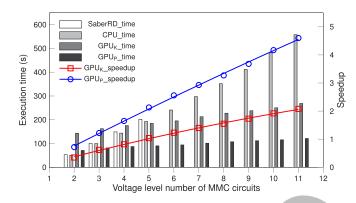

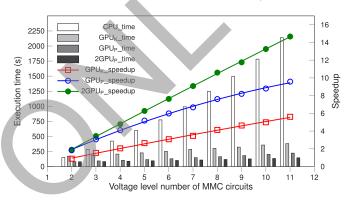

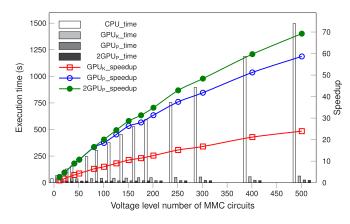

Abstract—Device-level power electronic circuit simulation is so cumbersome that engineers are forced to make model simplification or reduce circuit size to obtain a reasonable execution time for repeated simulation runs. This paper proposes a massive-thread parallel simulation of large-scale power electronic circuits employing device-level modeling on the graphics processors (GPUs) to obtain higher data throughput and lower execution times. Parallel massive-thread modules are proposed for the nonlinear physicsbased insulated gate bipolar transistor and power diode components. The nonlinear solution algorithm comprised of Newton-Raphson iterations and partial LU decomposition is fully parallelized on the GPU. Furthermore, the commonly used behavioral model with reduced computational complexity is also employed to represent the switches. The developed simulation codes are used to run large-scale test cases of the modular multilevel converter (MMC) system. The accuracy and efficiency of the GPU-based parallel simulation are compared with sequential CPU-based codes and the SaberRD program to show the advantages of the parallelized simulation; execution time speedups of 15 times and 70 times are reported for the MMC system using the nonlinear physicsbased modeling and behavior-based modeling, respectively.

*Index Terms*—Device-level modeling, graphics processors, insulated gate bipolar transistor (IGBT), large-scale circuits, massive-thread, modeling, numerical analysis, parallel algorithms, parallel architectures, power diode, power electronics, simulation software.

# I. INTRODUCTION

**C** OMPUTATIONAL speed is an overriding concern in large-scale power electronic circuit simulation using device-level circuit simulators. Modeling complex systems composed of power electronic subsystems, such as HVDC grids, transportations, renewable energy, and smart grid technologies, can often be very challenging as the system modeler is faced with a difficult compromise between system size, modeling complexity, and simulation duration to obtain a reasonable execution time for the application. Computational bottlenecks arise during

Z. Zhou and V. Dinavahi are with the Department of Electrical and Computer Engineering, University of Alberta, Edmonton, AB T6G 2V4, Canada (e-mail: zhiyin@ualberta.ca; dinavahi@ualberta.ca).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPEL.2017.2725239

repeated nonlinear transient simulations, which are quite frequently required in many studies that include but are not limited to the following:

- robust design of power electronic systems involving optimization to fine-tune parameters at the circuit and component levels requiring several design iterations and hundreds of simulation runs;

- in addition to transient analysis, simulation-based statistical and sensitivity analysis of the system hierarchy to reduce design costs and time;

- comprehensive fault analysis of systems using a matrix of faults representing possible device/component failures requiring multiple simulation runs to evaluate system performance and improve reliability;

- data visualization and analysis of large sets of postsimulation results to extract meaningful system performance indices;

- detailed modeling of complex mixed-signal and multidomain subsystems with widely different time constants, for e.g., electronic, electrical, magnetic, thermal, and hydraulic systems.

There are a variety of device-level simulators available for power electronic circuit simulation, both commercial and noncommercial [1]-[3]. A partial listing of such tools include SaberRD, Orcad, PSIM, PLECS, LTSpice, PECS, PETS, DesignLab, etc. All of these simulation tools provide a plethora of models for semiconductor devices such as diodes, bipolar junction transistor (BJTs), JFETs, MOSFETs and insulated gate bipolar transistor (IGBTs) and fundamental circuit components such as linear/nonlinear resistors, capacitors, inductors, and independent/dependent voltage and current sources. These software tools are also capable of performing an assortment of studies such as nonlinear dc, transient, linear ac (small signal), and Monte Carlo analyses. Furthermore, since many design projects may include analog, digital, and mixed-signal simulations, most of these tools either possess native mixed-signal capabilities or they provide cosimulation interfaces to leverage the features of an external toolset [4]–[7]. A key attribute shared by currently available simulation tools in terms of program execution is that they are single-thread programs designed to run sequentially on the CPU. Although some modifications have been made for distributed processing on multiple CPUs, such as the distributed iterative analysis in SaberRD [8], the actual execution of program code on individual CPUs is still sequential. Therefore, the

0885-8993 © 2017 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Manuscript received February 15, 2017; revised April 20, 2017; accepted July 6, 2017. Date of publication July 11, 2017; date of current version February 22, 2018. This work was supported by the Natural Science and Engineering Research Council of Canada. Recommended for publication by Associate Editor J. A. Oliver. (*Corresponding author: Venkata Dinavahi.*)

S. Yan is with Tesla, Inc., Shanghai 201108, China (e-mail: shyan@ tesla.com).

attained *task parallelism* is coarse grained at best. The resulting computational efficiency of device-level circuit simulators was primarily derived from an increase in CPU clock speed, which until the mid-2000s could be relied upon to provide the necessary acceleration. However, computer chip manufactures no longer rely on clock speed for higher processing power; they have implemented multicore CPU and many-core GPU architectures to increase chip performance. While multiple thread concepts on CPUs such as hyperthreading were introduced early on, they were hardly taken advantage of by circuit simulators mainly due to the cumbersome task of rewriting the program code to enable multiple threads of execution.

Model order reduction is the usual course for improving computational speed in device-level circuit simulators. Model simplifications include circuit size reduction and using averaged or linearized models for the switching devices to observe only the system-level behavior. However, evaluating the system's comprehensive behavior entails maintaining many different models of varying size and complexity on different simulation tools. It would be far more effective if the same simulation tool could efficiently show both the system-level and device-level results over long time frames. Taking IGBT as an example, there are several models ranging from detailed physics-based model to ideal switch model. Hefner brought up the first complete analytical physics-based model available for a device-level circuit simulator, which is implemented in SaberRD [9], [10]. As the most common voltage source converter for HVdc applications, modular multilevel converter (MMC) is normally simulated using simplified IGBT and diode models because of its complex structure consisting of a series of submodules (SM); device-level details of IGBT and diode cannot be observed using simplified system-level models of the MMC.

Since GPU offers a massively parallel architecture composed of thousands of cores grouped into streaming multiprocessors though its clock frequency is relevantly lower than CPU, it has a higher compute power and throughput in floating point calculations than traditional CPUs, as compared in Table III. The attained data parallelism is fine-grained, which conforms the single instruction, multiple data (SIMD) format; therefore, to fully exploit GPU acceleration, the device models and the numerical algorithms have to be rewritten into the SIMD format [11]. Mature application programming interfaces are available for SIMD abstraction such as CUDA, DirectCompute, and OpenCL. The user develops C/C++ code interlaced with special constructs and functions to access the parallel cores and distributed memories on the GPU. Furthermore, optimized numerical libraries such as CUBLAS [12] and CUFFT [13] are available for linear solvers and data processing. GPU-based massively parallel processing has been used worldwide for myriad applications, such as computational fluid dynamics, life sciences, medical imaging, game physics, seismic simulations, etc., and impressive acceleration has been reported [14]-[17]. For power system computation, GPUs have been used for various studies, such as transient stability simulation [18], electromagnetic transient simulation [19], dynamic state estimation [20], [21], ionized field computation [22], and power flow calculation [23].

TABLE I GPU SPECIFICATIONS

| Chip                             | GK110<br>(Kepler) | GP104<br>(Pascal) |

|----------------------------------|-------------------|-------------------|

| Fabrication                      | 28 nm             | 16 nm             |

| Number of single precision cores | 2880              | 2560              |

| Memory bandwidth                 | 336 GB/s          | 320 GB/s          |

| Memory size                      | 6 GB              | 8 GB              |

| Memory type                      | GDDR5             | GDDR5X            |

| Core clock                       | 837 MHz           | 1607 MH           |

In this paper, a massively parallel simulation of large-scale power electronic circuits using nonlinear physics-based devicelevel models on the GPU architecture is proposed. The massivethread implementation of physics-based IGBT and power diode utilize the Hefner's IGBT model and Lauritzen's diode model [24]. The numerical solution modules including the Newton-Raphson iterative method, matrix equation solution using partial LU decomposition are implemented in the massive-thread framework. Based on the MMC circuit characteristic, a mathematical method is proposed to decompose the semiblock Jacobian matrix. In addition, a variable time-stepping scheme using the predictor-corrector method is adopted to increase simulation efficiency. The GPU-based massive-thread simulation is compared with SaberRD simulator as well as a complete CPU implementation, in terms of accuracy and computational efficiency.

This paper is organized as follows. Section II briefly describes the GPU hardware architecture and CUDA abstraction for parallel computation. Section III describes the details of the developed massive-thread parallel modules for the IGBT, power diode, and the numerical algorithms. Section IV shows the case studies of MMC with simulation results and discussion. Finally, Section V gives the conclusion of this paper.

## II. BACKGROUND ON GPU ARCHITECTURE AND PROGRAMMING INTERFACE

Two GPU architectures, NVIDIA Kepler GK110 (2012) and Pascal GP104 (2016), whose specifications are given in Table I, are used to implement the massively parallel power electronic circuit simulation codes. In hybrid computational systems, CPU and GPU cooperate as *host* and *device*, respectively. The host sends all essential instructions and data to the device through PCIe  $3.0 \times 16$  interface up to 15.754 GB/s. Instructions are distributed through GigaThread interface to each streaming multiprocessor and data are transferred to global memory on the GPU board. Every 32 threads in the streaming multiprocessor are distributed into one *warp* as an execution unit, which operate simultaneously, while other threads are parallelized by the pipeline automatically. Finally, results saved in global memory are transferred back to host through PCIe 3.0 bus again.

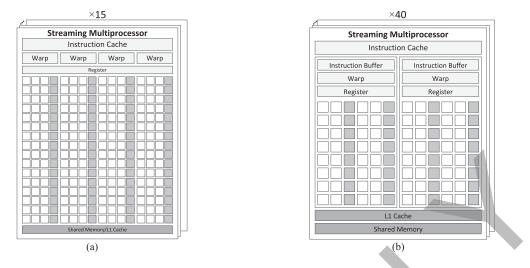

Growing from NVIDIA's Fermi architecture, the Kepler architecture has 15 streaming multiprocessors with registers, caches, and shared memory, shown in Fig. 1(a) [25]. Each multiprocessor contains 192 CUDA cores, which is  $3 \times$  that

Fig. 1. Stream microprocessor structure of NVIDIA Kepler and Pascal architectures. (a) Kepler. (b) Pascal

of its predecessor, Fermi. A CUDA core is an instruction executing floating point operation in one thread. As the successor of NVIDIA Kepler architecture, the Pascal architecture contains more powerful, programmable, and power-efficient stream multiprocessors, shown in Fig. 1(b) [26]. Although each stream multiprocessors only has 64 CUDA cores, there are 40 stream multiprocessors in total for the Pascal architecture with much higher clock frequency, larger memory size, and wider bandwidth, as listed in Table I, thanks to its more advantageous 16 nm fabrication. There are several types of memories on board that includes global memory, shared memory, and registers.

The global memory is larger with access to the entire device but has a higher latency; the shared memory can be accessed by all cores inside the streaming multiprocessor with low latency; and there are a few registers inside a streaming multiprocessor that are the fastest. In the Kepler architecture, shared memory can be configured in the sizes of 16, 32, or 48 kB, which shares the 64 kB on-chip memory with L1 Cache, while in the Pascal architecture, the amount of shared memory is up to 96 kB. The memory management, including allocation and organization, is the key to programming efficiency. CUDA offers both a platform and programming model for NVIDIA's GPU [27]. The function involving data parallelism is referred to as a *kernel*, which organizes massive *threads* into blocks inside a grid. All threads inside a kernel must be synchronized before the end of execution. The block-level barrier, a synchronization point ensures that all threads inside a block have reached the command line and are ready for next instruction. The device-level synchronization barrier synchronizes all thread procedures inside a grid before the next kernel execution.

## III. MASSIVE-THREAD PARALLEL MODULES FOR POWER ELECTRONIC CIRCUIT SIMULATION

#### A. Nonlinear Power Diode

1) Model Formulation: Detailed device-level modeling of power diodes covers a wide range of circuit operating conditions

since it includes equations for drift and diffusion of electrons and holes. However, different from conventional detailed models, which are too complicated to simulate, this paper employs a simplified physics-based model containing p-i-n structure suitable for power diode operating condition of high voltage and fast switching [28].

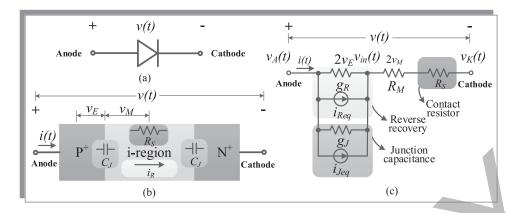

The physical structure of a power diode is shown in Fig. 2(b). The reverse recovery happens when turning off a forward conducting diode rapidly, as described by the following equations:

$$i_R(t) = \frac{q_E(t) - q_M(t)}{T_M}$$

(1)

$$0 = \frac{dq_M(t)}{dt} + \frac{q_M(t)}{\tau} - \frac{q_E(t) - q_M(t)}{T_M}$$

(2)

$$q_E(t) = I_S \tau \left( e^{\frac{v_E(t)}{V_T}} - 1 \right)$$

(3)

where  $i_R(t)$  is the diffusion current in *i*-region,  $q_E(t)$  represents charge variable in the junction area,  $q_M(t)$  represents charge variable in the middle of *i*-region,  $T_M$  is the diffusion transit time across *i*-region,  $\tau$  is the lifetime of recombination,  $I_S$  is the diode saturation current constant,  $v_E$  is the junction voltage, and  $V_T$  is the thermal voltage constant. The voltage drop across *i*-region  $v_M(t)$  is described as

$$v_M(t) = \frac{V_T T_M i(t)}{q_M(t)}.$$

(4)

The voltage across diode v(t) is expressed as

$$v(t) = 2v_M(t) + 2v_E(t) + R_S\left[i_E(t) + \frac{dq_J(t)}{dt}\right]$$

(5)

where  $R_S$  is the contact resistance presented as an internal resistance and the charge of junction capacitance in the capacitance  $C_J$  is given as

$$q_J(t) = \int C_J(t) d(2v_E).$$

(6)

Fig. 2. (a) Power diode symbol. (b) Physical structure of power diode. (c) Discretized and linearized equivalent circuit of power diode (Diode-DLE).

The expression of junction capacitance  $C_J(t)$  is given as follows:

$$C_{J}(t) = \begin{cases} \frac{C_{J0}}{\left(1 - \frac{2v_{E}(t)}{\phi_{B}}\right)^{m}}, & v_{E} < \frac{\phi_{B}}{4} \\ \left[\frac{2^{m+2}mv_{E}(t)}{\phi_{B}} - (m-1)2^{m}\right]C_{J0}, v_{E} \ge \frac{\phi_{B}}{4} \end{cases}$$

(7)

where  $C_{J0}$  is the zero-biased junction capacitance,  $\phi_B$  is the built-in potential, and m is the junction grading coefficient.

2) Model Discretization and Linearization: After discretization by trapezoidal rule, the differential term  $dq_M(t)/dt$  in (2) is expressed as

$$q_M = \frac{\Delta t \cdot q_E(t)}{2T_M \left(1 + \frac{k_1 \Delta t}{2}\right)} + \frac{q_{\text{hist}}(t - \Delta t)}{1 + \frac{k_1 \Delta t}{2}}$$

(8)

where the history term is given as

$$q_{\rm hist}(t-\Delta t) = \frac{\Delta t}{2T_M} q_E(t-\Delta t) - \frac{k_1 \Delta t}{2} q_M(t-\Delta t).$$

(9)

The equivalent reverse recovery current  $i_{Req}$ , as shown in Fig. 2(c), is given as

$$i_{Req} = k_2 I_S \tau (e^{\frac{v_E(t)}{v_T}} - 1) - \frac{q_{\text{hist}}(t - \Delta t)}{T_M (1 + \frac{k_1 \Delta t}{2})} - 2v_E(t)g_R \quad (10)$$

where  $g_R$  is the dynamic conductance defined as

$$g_R = \frac{1}{2v_T} k_2 I_S \tau e^{\frac{v_E(t)}{V_T}}.$$

(11)

Similarly, the equivalent junction capacitance current  $i_{Jeq}$  is obtained as

$$i_{Jeq} = i_J(t) - 2v_E(t)g_J$$

(12)

where the equivalent junction conductance  $g_J$  is given as

$$g_J = \frac{2}{\Delta t} C_J(t). \tag{13}$$

The discretized and linearized system (Diode-DLE) shown in Fig. 2(c) can be obtained as follows:

$$G^{\text{Diode}} \cdot V^{\text{Diode}} = I_{\text{eq}}^{\text{Diode}}$$

(14)

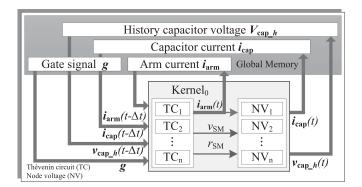

Node voltage v(t)Global Memory  $q_{\rm hi}$ Kernel Kernel  $q_{\rm hist}(t)$  $q_{\text{hist}}(t-\Delta t)$ Reverse recovery & Nonlinear Junction capacitance  $g_R(t)$ solution Yes  $RJ_1$  $NS_1$  $i_{Req}(t)$ v(t) $v_E(t)$ converge?  $RJ_2$  $g_J(t)$  $NS_2$  $v_E(t)$ ÷ :  $i_{Jeq}(t)$ No  $RJ_n$  $NS_n$

Fig. 3. Massive-thread parallel implementation of power diode.

where

$$\boldsymbol{G}^{\text{Diode}} = \begin{bmatrix} g_R + g_J & -g_R - g_J & 0\\ -g_R - g_J & g_R + g_J + \frac{1}{R_M + R_S} & -\frac{1}{R_M + R_S}\\ 0 & -\frac{1}{R_M + R_S} & \frac{1}{R_M + R_S} \end{bmatrix}$$

(15)

$$\boldsymbol{V}^{\text{Diode}} = [\boldsymbol{v}_A, \quad \boldsymbol{v}_{in}, \quad \boldsymbol{v}_K]^T \text{ and }$$

(16)

$$\boldsymbol{I}_{\text{eq}}^{\text{Diode}} = \begin{bmatrix} -i_{R\text{eq}} - i_{J\text{eq}}, & i_{R\text{eq}} + i_{J\text{eq}} & , 0 \end{bmatrix}^{T}.$$

(17)

Applying the massive-thread parallel Newton–Raphson method, which is detailed in Section III-D, the next iterate values  $V^{\text{Diode}(n+1)}$  can be updated by previous *n*th iterate values until the solution is converged.

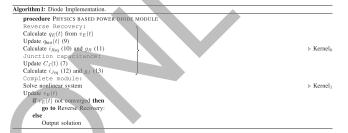

*3) Parallel Massive-Thread Mapping:* As shown in Fig. 3 and described in Algorithm 1, there are two kernels in the massive-thread parallel diode model. The dynamic conductance

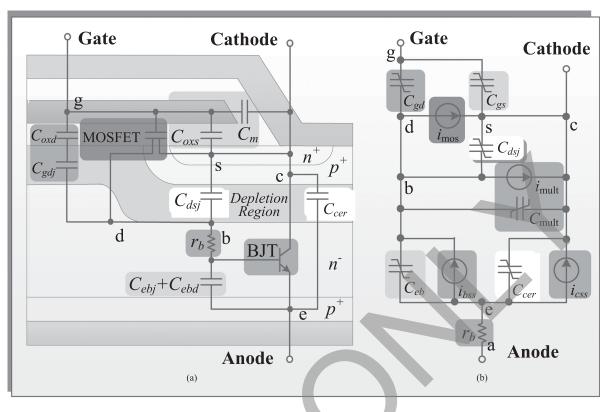

Fig. 4. (a) Phenomenological structure of IGBT. (b) Analog equivalent circuit of IGBT (IGBT-AE).

$g_R$  and equivalent reverse recovery current  $i_{Req}$  are updated by the junction voltage  $v_E$ , and the equivalent conductance  $g_J$ and current source  $i_{Jeq}$  are updated by the junction capacitance  $C_J$  in reverse recovery and junction capacitance units (RJs) of Kernel<sub>0</sub>. The nonlinear system is solved using the massivethread parallel Newton–Raphson iteration method in nonlinear solution units (NSs) of Kernel<sub>1</sub>. The convergence of  $v_E(t)$  is checked and it determines whether the process will move to the next time step.

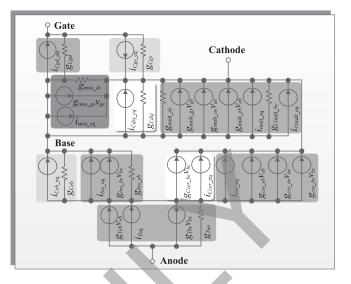

#### B. Nonlinear Physics-Based IGBT

1) Model Formulation: Based on Hefner's physics-based model [10], the IGBT is described as the combination of a bipolar transistor and a MOSFET. Since these internal devices are differently structured from standard microelectronic devices, a regional approach is adopted to identify the phenomenological circuit of IGBT, as shown in Fig. 4(a). An analog equivalent circuit, shown in Fig. 4(b), makes it possible to implement the model in circuit simulators by replacing the BJT with base and collector current sources and MOSFET with a current source, which represents the currents between each of the terminals and internal nodes in terms of nonlinear functions.

*a)* Currents: The steady-state collector current  $i_{css}$  of BJT is formulated as

$$i_{css} = \frac{i_T}{1+b} + \frac{4bD_pQ}{(1+b)W^2}$$

(18)

where b is the ambipolar mobility ratio,  $D_p$  is the hole diffusivity, W is the quasi-neutral base width, Q is the instantaneous excesscarrier base charge, and the anode current  $i_T$  is shown as follows:

$$i_T = \frac{v_{ae}}{r_b}.$$

(19)

The base resistance  $r_b$  in (19) is expressed as

$$r_b = \begin{cases} \frac{W}{q\mu_n A N_B} & v_{eb} \le 0\\ \frac{W}{q\mu_{\text{eff}} A n_{\text{eff}}} & v_{eb} > 0 \end{cases}$$

(20)

where  $\mu_n$  and  $\mu_{\text{eff}}$  stand for electron mobility and effective mobility,  $n_{\text{eff}}$  is the effective doping concentration, q is the electron charge,  $N_B$  is the base doping concentration, and Ais the device active area. The steady-state base current  $i_{bss}$  is caused by the decay of excess base charge of recombination in the base and electron injection in the emitter, and is expressed as

$$i_{bss} = \frac{Q}{\tau_{\rm HL}} + \frac{4Q^2 N_{scl}^2 i_{sne}}{Q_B^2 n_i^2}$$

(21)

where  $\tau_{\rm HL}$  is the base high-level lifetime,  $N_{scl}$  is the collector-base space concentration,  $i_{sne}$  is the emitter electron saturation current,  $n_i$  is the intrinsic carrier concentration, and  $Q_B$  represents the background mobile carrier base charge. The MOSFET channel current  $i_{\rm mos}$  is expressed as

$$i_{\rm mos} = \begin{cases} 0, & v_{gs} < v_T \\ K_p (v_{gs} - v_T) v_{ds} - \frac{K_p v_{ds}^2}{2} & v_{ds} \le v_{gs} - v_T \\ \frac{K_p (v_{gs} - v_T)^2}{2}, & v_{ds} > v_{gs} - v_T \end{cases}$$

(22)

where  $K_p$  is the MOSFET transconductance parameter,  $v_{gs}$  is the gain-source voltage, and  $v_T$  is the MOSFET channel threshold voltage [29]. In addition, due to thermal generation in the depletion region and carrier multiplication, which is a key factor to determine the avalanche breakdown voltage and the leakage current, the avalanche multiplication current  $i_{mult}$ , shown in Fig. 4(b), is given as

$$i_{\text{mult}} = (M - 1)(i_{\text{mos}} + i_{css} + i_{c\_cer}) + Mi_{\text{gen}}$$

(23)

where M stands for the avalanche multiplication factor.

b) Charges and capacitances: The gate-source capacitance  $C_{gs}$  in the analog model is a constant, and its charge  $Q_{gs}$ is given as

$$Q_{gs} = C_{gs} v_{gs}. aga{24}$$

The gate–drain capacitance  $C_{qd}$  is expressed as

$$C_{gd} = \begin{cases} C_{oxd}, & v_{ds} \le v_{gs} - v_{Td} \\ \frac{C_{gdj}C_{oxd}}{C_{gdj} + C_{oxd}} & v_{ds} > v_{gs} - v_{Td} \end{cases}$$

(25)

where  $v_{Td}$  is the gate–drain overlap depletion threshold voltage,  $C_{oxd}$  is the gate–drain capacitance. The gate–drain overlap depletion capacitance  $C_{qdj}$  is given as

$$C_{gdj} = \frac{A_{gd}\epsilon_{si}}{W_{gdj}} \tag{26}$$

where  $A_{gd}$  is the gate–drain overlap area,  $\epsilon_{si}$  is the silicon dielectric constant, and  $W_{gdj}$  is the gate–drain overlap depletion width. The charge of  $C_{gd}$  has the expression as (27) shown at the bottom of this page. Similarly, the drain–source depletion capacitance  $C_{dsj}$ , related to the active area  $(A - A_{gd})$  and drain–source depletion width  $W_{dsj}$ , is given as

$$C_{dsj} = \frac{(A - A_{gd})\epsilon_{si}}{W_{dsj}}$$

(28)

and its charge  $Q_{ds}$  is expressed as

$$Q_{ds} = A_{ds} \sqrt{2\epsilon_{si}(v_{ds} + 0.6)q} \overline{N_{scl}}.$$

(29)

The emitter-base capacitance  $C_{eb}$  is solved from  $\frac{\partial Q_{eb}}{\partial V_{eb}}$  as

$$= -\frac{qN_B\epsilon_{si}A^2}{Q-Q_{bi}}.$$

(30)

The collector–emitter redistribution capacitance  $C_{cer}$  is solved from the ambipolar diffusion equation as

$$C_{cer} = \frac{QC_{bcj}}{3Q_B} \tag{31}$$

where  $Q_B$  is the background mobile carrier base charge and  $C_{bcj}$  is the base–collector depletion capacitance. The carrier multiplication charge and capacitance relating to  $C_{cer}$  are given as

$$Q_{\text{mult}} = (M-1)Q_{ce} \text{ and } C_{\text{mult}} = (M-1)C_{cer}.$$

(32)

Fig. 5. Discretized and linearized equivalent circuit of IGBT (IGBT-DLE).

2) Model Discretization and Linearization: After applying the Newton–Raphson method on four current sources and the conductivity-modulated base resistance  $r_b$ , the analog equivalent circuit model (IGBT-AE) shown in Fig. 4(b), containing five nonlinear and time-varying elements, is transferred into discretized and linearized equivalent circuits (IGBT-DLE), as shown in Fig. 5. The iterative equations of  $i_{mos}$ ,  $i_T$ ,  $i_{css}$ ,  $i_{bss}$ ,  $i_{mult}$  for the (n + 1)th iteration are obtained as follows:

$$i_{\rm mos}^{n+1} = i_{mos\_eq}^n + g_{\rm mos\_gs}^n v_{gs}^{n+1} + g_{\rm mos\_ds}^n v_{ds}^{n+1}$$

(33)

$$i_T^{n+1} = i_{Teq}^n + g_{Tae}^n v_{ae}^{n+1} + g_{Tbc}^n v_{bc}^{n+1} + g_{Teb}^n v_{eb}^{n+1}$$

(34)

$$i_{css}^{n+1} = i_{css\_eq}^{n} + g_{css\_bc}^{n} v_{bc}^{n+1} + g_{css\_ae}^{n} v_{ae}^{n+1}$$

$$+g^n_{css\_eb}v^{n+1}_{eb} \tag{35}$$

$$i_{bss}^{n+1} = i_{bss\_eq}^n + i_{bss\_eb}^n v_{eb}^{n+1} + g_{bss\_bc}^n v_{bc}^{n+1}$$

(36)

$$\begin{aligned} & + g_{\text{mult\_ee}}^{n+1} = i_{\text{mult\_ee}}^{n} + g_{\text{mult\_ds}}^{n} v_{ds}^{n+1} + g_{\text{mult\_ds}}^{n} v_{ds}^{n+1} \\ & + g_{\text{mult\_ae}}^{n} v_{ae}^{n+1} + g_{\text{mult\_eb}}^{n} v_{eb}^{n+1}. \end{aligned}$$

(37)

Applying KCL to the nodes gate, collector, base and emitter, results in the following nodal equation:

$$\boldsymbol{G}^{\mathrm{IGBT}} \cdot \boldsymbol{V}^{\mathrm{IGBT}} = \boldsymbol{I}_{eq}^{\mathrm{IGBT}}$$

(38)

where

$$\boldsymbol{V}^{\text{IGBT}} = \begin{bmatrix} v_c & v_g & v_a & v_d & v_e \end{bmatrix}^T$$

(39)

$I_{eq}^{\text{IGBT}}$  is given in (40) as shown at bottom of the next page and the 5 × 5 conductance matrix is given in (41) as shown at bottom of the next page.

Applying the Newton–Raphson method to solve the nonlinear matrix equation (38),  $\Delta V^{IGBT}$  is obtained to update  $V^{IGBT}$

$$Q_{gd} = \begin{cases} C_{oxd} v_{dg}, & v_{ds} \le v_{gs} - v_{Td} \\ \frac{qN_B \epsilon_{si} A_{gd}^2}{C_{oxd}} \left[ \frac{C_{oxd} W_{gdj}}{\epsilon_{si} A_{gd}} - \ln(1 + \frac{C_{oxd} W_{gdj}}{\epsilon_{si} A_{gd}}) \right] - C_{oxd} v_{Td}, v_{ds} > v_{gs} - v_{Td} \end{cases}$$

(27)

Fig. 6. Massive thread parallel implementation of the physics-based IGBT model.

iteratively. Therefore, the iterative equation is given as

$$\boldsymbol{G}^{\mathrm{IGBT}(\mathrm{n})} \Delta \boldsymbol{V}^{\mathrm{IGBT}(\mathrm{n}+1)} = -\boldsymbol{I}^{\mathrm{IGBT}(\mathrm{n})}$$

(42)

where

$$\boldsymbol{I}^{\text{IGBT}(n)} = \boldsymbol{G}^{\text{IGBT}(n)} \boldsymbol{V}^{\text{IGBT}(n)} - \boldsymbol{I}_{eq}^{\text{IGBT}(n)}.$$

(43)

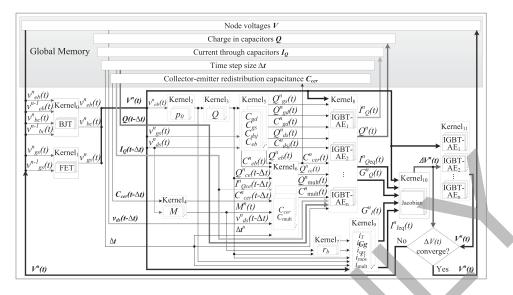

3) Parallel Massive-Thread Mapping: For a system containing n IGBTs, the massive-thread parallel implementation is shown in Fig. 6 and is described in Algorithm 2. Among the 12 kernels involved in the module, Kernel<sub>0</sub> and Kernel<sub>1</sub> check p-i-n junction and MOSFET junction voltage limitation within successive Newton–Raphson iterations; intermediate parameters  $p_0$ , Q, and M are processed in Kernel<sub>2</sub>, Kernel<sub>3</sub> and Kernel<sub>4</sub>; six nonlinear capacitors  $C_{gd}$ ,  $C_{gs}$ ,  $C_{dsj}$ ,  $C_{mult}$ ,  $C_{eb}$ , and  $C_{cer}$  are updated in Kernel<sub>5</sub> and Kernel<sub>6</sub>; with those capacitances, the equivalent conductance  $G_Q$  and parallel current source  $I_{Qeq}$

$$\mathbf{I}_{eq}^{\text{IGBT}} = \begin{bmatrix} i_{e,eq} \\ i_{g,a,q} \\ i_{e,eq} \end{bmatrix} = \begin{bmatrix} i_{\text{mult.eq}} + i_{C\,\text{mult.eq}} + i_{c,se,eq} + i_{C,cer,eq} + i_{C,ge,eq} + i_{C,dej,eq} + i_{mos,eq} \\ -i_{Teq} \\ i_{c,seb,eq} + i_{bss,eq} - i_{C,dej,eq} - i_{C\,dej,eq} - i_{C\,\text{mult.eq}} - i_{C\,\text{mult.eq}} \end{bmatrix}$$

$$\mathbf{G}^{\text{IGBT}} =$$

$$\begin{bmatrix} g_{\text{mult.ds}} + g_{\text{mult.gs}} + \\ g_{\text{mult.bc}} + g_{cs,b,c} + \\ -g_{\text{mult.bc}} + g_{cs,b,c} + \\ g_{\text{mult.bc}} + g_{cs,b,c} + \\ g_{\text{mult.bc}} + g_{cs,b,c} + \\ g_{\text{must.bc}} + g_{cs,s,eq} + g_{cs,s,eq} - g_{\text{mult.ae}} - g_{cs,ae} \\ g_{cs,b,c} + g_{cs,b,c} + \\ g_{mos,gs} - \\ -g_{Tbc} & 0 \\ g_{Tac} \\ g_{mult.ab} + g_{mult.eb} \\ g_{mos,ds} + g_{Cdsj} - g_{mos,gs} - g_{Cdg} + \\ g_{mult.ab} - g_{mult.ab} \\ g_{mult.ab} - g_{mult.ab} \\ g_{mult.ab} - g_{mult.ab} \\ g_{mult.ab}$$

### Algorithm 2: IGBT Kernel.

| 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| procedure Physics-based IGBT module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       |

| Check p-n junction voltage $v_{eb}(t)$ and $v_{bc}(t)$ from the second | om last                               |

| iteration value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $\triangleright$ Kernel <sub>0</sub>  |

| Check MOSFET junction voltage $v_{gs}(t)$ from las                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | t iteration                           |

| value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\triangleright$ Kernel <sub>1</sub>  |

| Solve $p_0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $\triangleright$ Kernel <sub>2</sub>  |

| Calculate $Q, Q_1$ and $Q_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $\triangleright$ Kernel <sub>3</sub>  |

| Update intermediate parameter $M$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $\triangleright$ Kernel <sub>4</sub>  |

| Calculate $C$ and $Q$ in $C_{qd}$ , $C_{qs}$ , $C_{dsj}$ , and $C_{eb}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\triangleright$ Kernel <sub>5</sub>  |

| Calculate $C$ and $Q$ in $C_{cer}$ and $C_{mult}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $\triangleright$ Kernel <sub>6</sub>  |

| Calculate $r_b$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ⊳ Kernel <sub>7</sub>                 |

| Update $I_Q$ , $I_{Qeq}$ , and $G_Q$ in all capacitors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\triangleright$ Kernel <sub>8</sub>  |

| Calculate $G_I$ and $I_{Ieq}$ for all current sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\triangleright$ Kernel <sub>9</sub>  |

| Build matrix equation (42) and solve for $\Delta V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $\triangleright$ Kernel <sub>10</sub> |

| Update $V^{IGBT}(t)$ for current iteration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\triangleright$ Kernel <sub>11</sub> |

| Check convergence of $\Delta V^{\mathrm{IGBT}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                       |

| if $\Delta V^{\mathrm{IGBT}}$ converges then                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       |

| Store $V^{\mathrm{IGBT}}$ to global memory and upd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | late $t$                              |

| else                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                       |

| Start from checking junction iteration lin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nit                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                       |

are updated in Kernel<sub>8</sub>; Kernel<sub>7</sub> calculates the base resistance  $r_b$  for Kernel<sub>9</sub>, where  $G_I$  and  $I_{Ieq}$  are updated with the approximation to current sources  $i_{mos}$ ,  $i_T$ ,  $i_{css}$ ,  $i_{bss}$ , and  $i_{mult}$ . Using all the resistances, charges, currents, equivalent conductances, and parallel current sources calculated above, Kernel<sub>10</sub> builds the iterative Jacobian matrix equation in (42) and solves for  $\Delta V^{IGBT}$  using Gaussian elimination and backward substitution, and Kernel<sub>11</sub> assigns *n* CUDA blocks containing five threads per block to update the voltage vector for each IGBT. When  $\Delta V^{IGBT}$  converges, the iterative solution for the current time step is accomplished and node voltages (NVs)  $V^{IGBT}$  are stored into global memory and used as the initial values for the next time step; otherwise, the iteration is repeated from checking junction limit as the initial value.

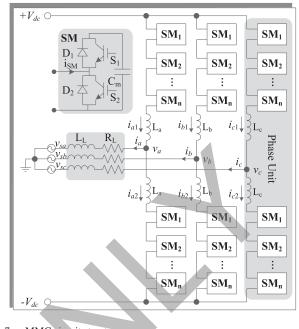

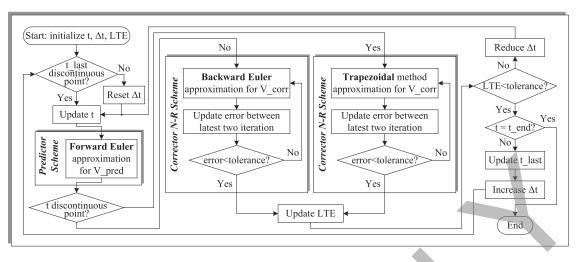

#### C. MMC and Control Strategy

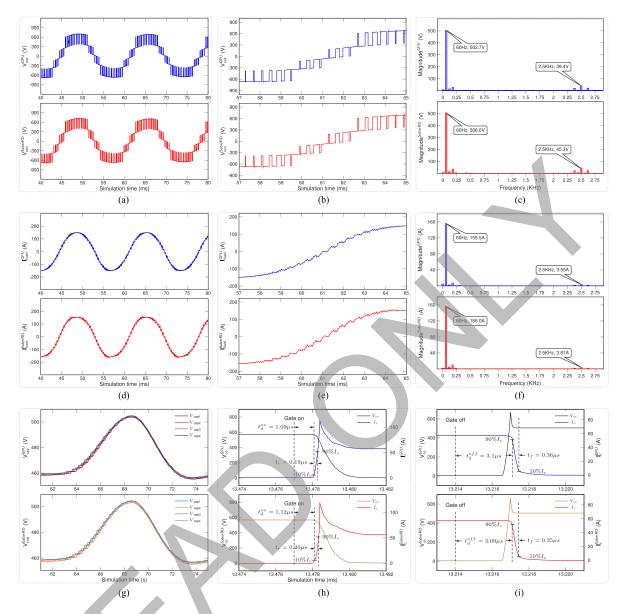

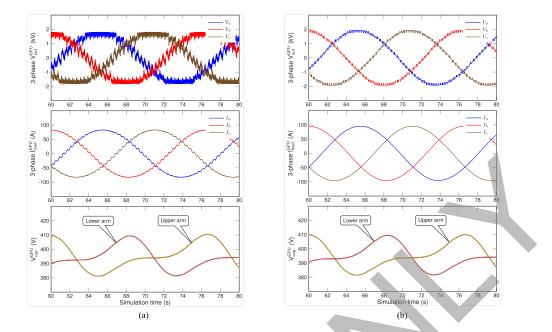

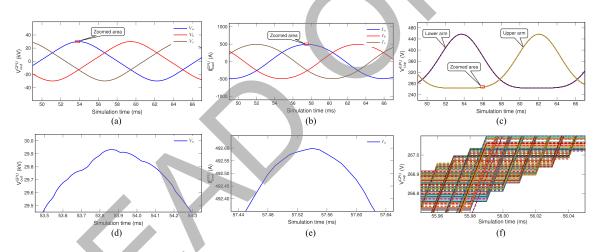

1) Circuit Structure: Commonly utilized in HVdc systems, the MMC circuit consists of SMs, which contains two IGBTdiode units, as shown in Fig. 7. The MMC circuit has been modeled by different types of models that include equivalent circuit based model, switching function model, and averaged value model [30]–[33]. Due to the most detailed information inside every device and the nanosecond time step, the physicsbased model requires so much computational burden that it is not frequently used in simulation. However, the application of GPU makes its application feasible in both accuracy and speed.

Fig. 7 shows a three-phase cascade MMC circuit structure consisting of n half-bridge submodules (SM) in each arm, with each SM containing two IGBTs, two antiparallel diodes, and an energy storage capacitor. Based on the gate signal combination and current direction of each IGBT, the SMs have different operating states. Once S<sub>1</sub> gate has ON signal and S<sub>2</sub> gate has OFF signal, C<sub>m</sub> will be charged and discharged according to

Fig. 8. MMC control scheme: (a) active and reactive power control of the MMC; (b) averaging and balancing control of the MMC.

the direction of  $i_{SM}$ ; when S<sub>1</sub> gate has OFF signal and S<sub>2</sub> gate has ON signal,  $C_m$  will be discharged regardless of the current direction. Furthermore, when gate signal combination is "00," the SM is blocked and not used in normal operation; and the gate signal combination "11" causes a short circuit of the SM capacitor.

The control strategies of MMC circuit adopted in this paper include the active and reactive power control, capacitor voltage averaging, and balancing control [35]–[37]. The outer loop in Fig. 8(a) is the active power controller; and the inner loop is the current controller. Given a fixed power reference, the difference of active and reactive powers is input to proportional-integral controllers to produce reference dq currents. After producing

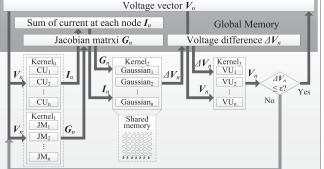

The Jacobian matrix  $J_F(X)$  is a  $k \times k$  matrix of first-order partial derivatives of F given as

$$\boldsymbol{J}_{F} = \frac{d\boldsymbol{F}}{d\boldsymbol{X}} = \begin{bmatrix} \frac{\partial F_{1}}{\partial X_{1}} \cdots \frac{\partial F_{1}}{\partial X_{k}} \\ \vdots & \ddots & \vdots \\ \frac{\partial F_{k}}{\partial X_{1}} \cdots \frac{\partial F_{k}}{\partial X_{k}} \end{bmatrix}.$$

(45)

Solving for the root of F(X) is numerically replaced by solving (44) for  $(X_{n+1} - X_n)$  and updating  $X_{n+1}$  from  $X_n$  The solution process is repeated until the difference  $||X_{n+1} - X_n||$  is converged.

According to KCL,

$$\Sigma \boldsymbol{I}(\boldsymbol{V}) = 0 \tag{46}$$

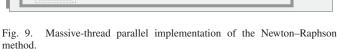

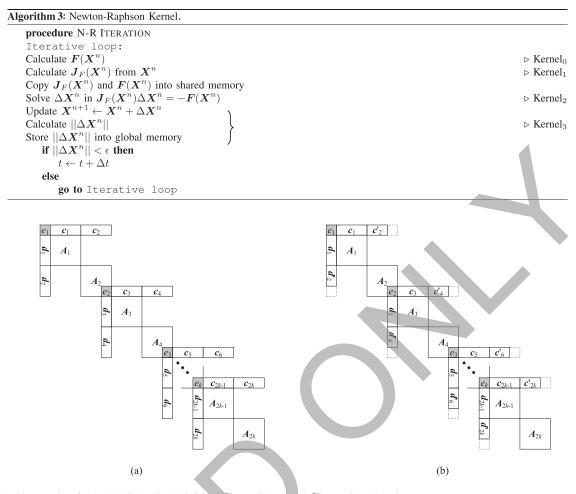

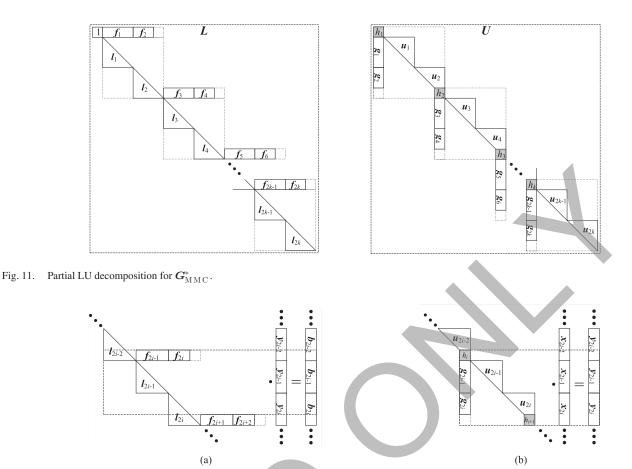

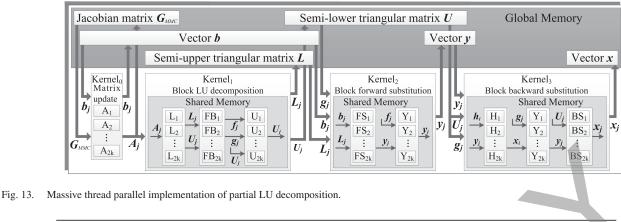

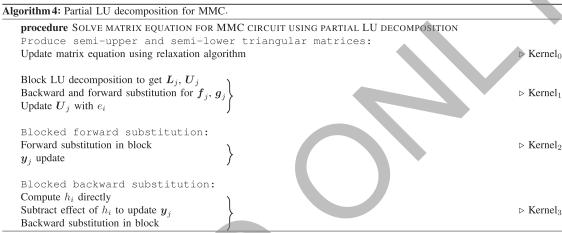

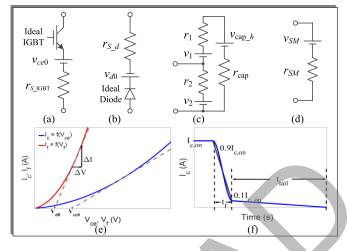

where I(V) refers to the sum of currents leaving each node. Applying (44) to (46) results in