### University of Alberta

Shared-Memory Optimizations for Virtual Machines

by

A. Cameron Macdonell

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Department of Computing Science

©A. Cameron Macdonell Fall 2011 Edmonton, Alberta

Permission is hereby granted to the University of Alberta Libraries to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly or scientific research purposes only. Where the thesis is converted to, or otherwise made available in digital form, the University of Alberta will advise potential users of the thesis of these terms.

The author reserves all other publication and other rights in association with the copyright in the thesis and, except as herein before provided, neither the thesis nor any substantial portion thereof may be printed or otherwise reproduced in any material form whatsoever without the author's prior written permission.

To Nadine

### Abstract

Virtual machine environments are becoming more common due to the increased performance of commodity hardware and the emergence of cloud computing for large scale applications. As the use of virtual machines continues to grow, performance critical applications will require efficient mechanisms to achieve their tasks.

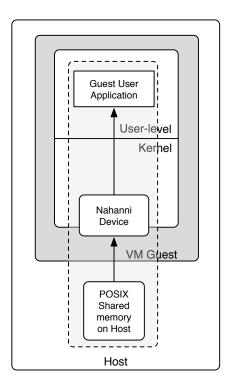

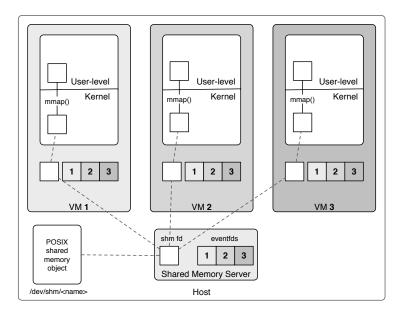

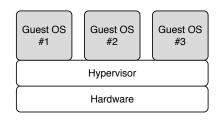

We introduce *Nahanni* as a mechanism for shared memory communication in virtual machine environments. Nahanni allows virtualized applications, those running inside virtual machines, to communicate through shared memory for both data movement and synchronization when VMs are co-located on the same host machine. We describe the design, implementation, and evaluation of Nahanni as part of the QEMU/KVM virtualization platform.

We have modified existing communication layers to measure the performance benefit of Nahanni. Through microbenchmarks and applications, we demonstrate that shared memory is a useful and efficient communication mechanism in virtualized environments. Further, we discuss how the design and implementation of Nahanni enables a new class of applications, ones that use structured data, to benefit from the use of shared memory.

# Acknowledgements

Although this work is published under my name, I would be remiss not to mention the key contributions and support of several people. Most notably, I must thank my supervisor Paul Lu for providing unending guidance, advice, and motivation in helping me to achieve this degree.

As well, I would like to thank the QEMU/KVM development community, in particular Avi Kivity, Anthony Liguori, Christian Borntraeger, Alexander Graf and all others that provided constructive feedback as Nahanni was developed.

Finally, thank you to my family, especially my parents and siblings for their support and most of all to my wife Nadine for her unflinching support to help me achieve this degree.

# Contents

| 1 | Intr |                                                                    | 1 |

|---|------|--------------------------------------------------------------------|---|

|   | 1.1  | Contributions                                                      | 3 |

| 2 | Ove  | rview                                                              | 5 |

|   | 2.1  | Nahanni                                                            | 6 |

|   | 2.2  | Motivation and Use Cases                                           | 7 |

|   | 2.3  | Caveats                                                            | 9 |

| 3 | Bac  | kground and Related Work 11                                        | 1 |

|   | 3.1  | Virtualization Basics                                              | 1 |

|   |      | 3.1.1 Hardware Virtualization                                      | 1 |

|   | 3.2  | The Task of the Hypervisor                                         | 2 |

|   |      | 3.2.1 Privileged Instructions                                      | 3 |

|   |      | 3.2.2 The x86 Architecture                                         | 4 |

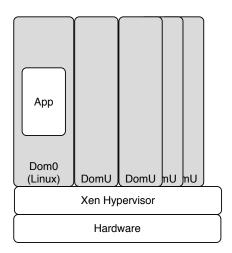

|   |      | 3.2.3 Paravirtualization and Xen                                   | 5 |

|   |      | 3.2.4 Redefining Paravirtualization                                | 7 |

|   |      | 3.2.5 Hardware-supported Virtualization in the x86 architecture 18 | 3 |

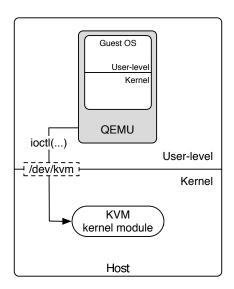

|   | 3.3  | QEMU and KVM                                                       | 3 |

|   |      | 3.3.1 The KVM Project                                              | 9 |

|   | 3.4  | Interprocess Communication                                         | 1 |

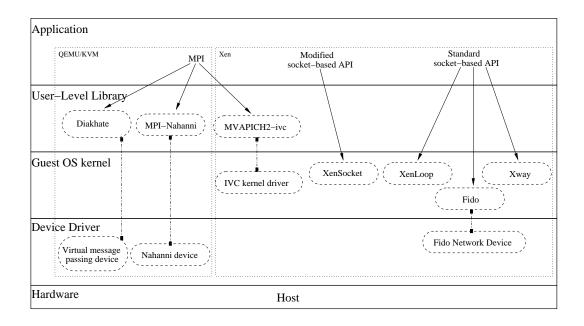

|   | 3.5  | Inter-VM IPC                                                       | 4 |

|   | 3.6  | The Linux Kernel                                                   | 3 |

|   |      | 3.6.1 Device Drivers                                               | 9 |

|   |      | 3.6.2 PCI and UIO                                                  | 9 |

|   | 3.7  | Concluding Remarks                                                 | ) |

| 4 | Desi | gn and Implementation 31                                           | 1 |

|   | 4.1  | Design of Nahanni                                                  | 1 |

|   | 4.2  | Design Alternatives                                                | 3 |

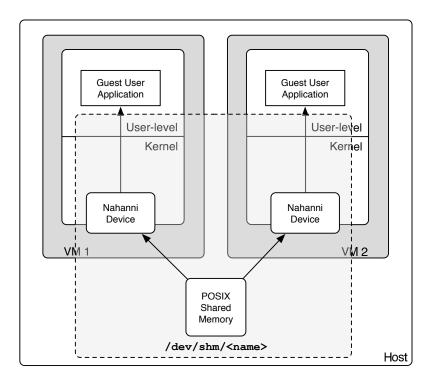

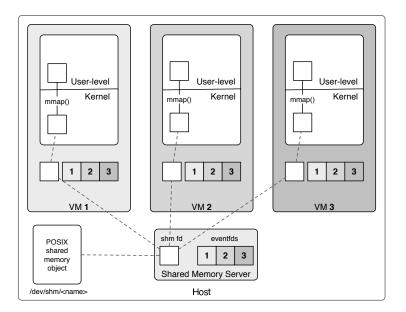

|   | 4.3  | Component 1: POSIX Shared Memory                                   | 5 |

|   | 4.4  | Component 2: A Modified QEMU                                       | 7 |

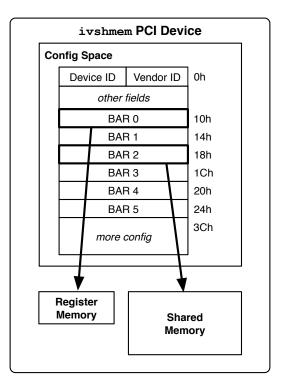

|   |      | 4.4.1 ivshmem: The Nahanni PCI device                              | 7 |

|   |      | 4.4.2 Mapped Memory Allocation                                     | 1 |

|   |      | 4.4.3 New Command-line Option                                      | 2 |

|   | 4.5  | Component 3: Guest OS Device Driver                                | 3 |

|   |      | 4.5.1 Brief Summary                                                |   |

|   | 4.6  | Inter-VM Notifications                                             |   |

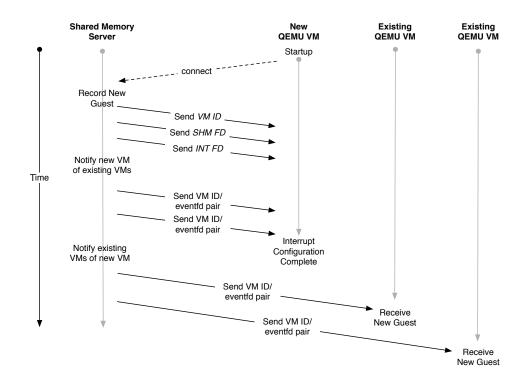

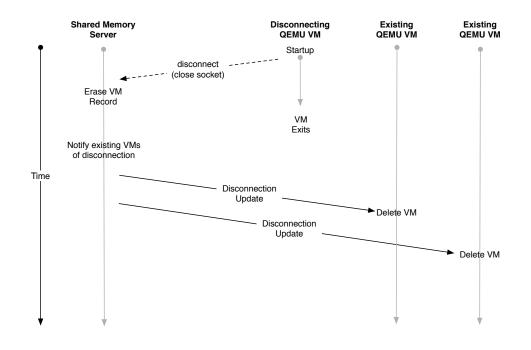

|   |                                                | 4.6.1                                                                                                                                                                                                 | The Shared-Memory Server                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               | 48                                                                                                                                             |

|---|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

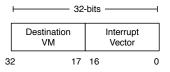

|   |                                                | 4.6.2                                                                                                                                                                                                 | Identifying Guest VMs                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               | 50                                                                                                                                             |

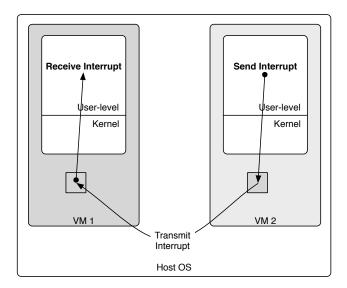

|   |                                                | 4.6.3                                                                                                                                                                                                 | Interrupt Transport                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               | 51                                                                                                                                             |

|   |                                                | 4.6.4                                                                                                                                                                                                 | Shared-Memory Server Protocol                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               | 52                                                                                                                                             |

|   |                                                | 4.6.5                                                                                                                                                                                                 | Nahanni Device Registers                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               | 54                                                                                                                                             |

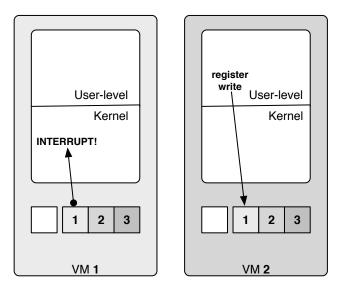

|   |                                                | 4.6.6                                                                                                                                                                                                 | Interrupt Transport                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               | 56                                                                                                                                             |

|   |                                                | 4.6.7                                                                                                                                                                                                 | Sending an Interrupt from User-level          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               | 57                                                                                                                                             |

|   |                                                | 4.6.8                                                                                                                                                                                                 | Receiving an Interrupt to User-level          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               | 59                                                                                                                                             |

|   | 4.7                                            | The Bi                                                                                                                                                                                                | g Picture                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               | 61                                                                                                                                             |

|   |                                                | 4.7.1                                                                                                                                                                                                 | Using KVM to Accelerate Interrupt Delivery    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               | 63                                                                                                                                             |

|   | 4.8                                            |                                                                                                                                                                                                       | ing Nahanni Shared Memory from Applications . |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               | 63                                                                                                                                             |

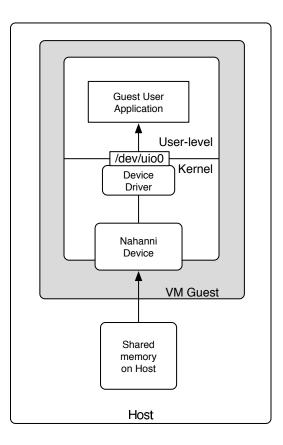

|   |                                                | 4.8.1                                                                                                                                                                                                 | Access From Within a Guest VM                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               | 64                                                                                                                                             |

|   |                                                | 4.8.2                                                                                                                                                                                                 | From Host Applications                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               | 66                                                                                                                                             |

|   | 4.9                                            |                                                                                                                                                                                                       | ni Memory as Dynamic Memory                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               | 67                                                                                                                                             |

|   |                                                | 4.9.1                                                                                                                                                                                                 | Dynamic Memory Allocation with Nahanni        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               | 67                                                                                                                                             |

|   |                                                | 4.9.2                                                                                                                                                                                                 | Avoiding Pointer Swizzling                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               |                                                                                                                                                |

|   | 4 10                                           |                                                                                                                                                                                                       | onization                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               | 70                                                                                                                                             |

|   | 4.10                                           |                                                                                                                                                                                                       | Atomic Operations in Assembly Language        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               | 71                                                                                                                                             |

|   |                                                |                                                                                                                                                                                                       | GCC Atomic Operations                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               | 71                                                                                                                                             |

|   | 1 1 1                                          |                                                                                                                                                                                                       | y                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               | 72                                                                                                                                             |

|   | 4.11                                           |                                                                                                                                                                                                       | Host security                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               | 72                                                                                                                                             |

|   | 1 12                                           |                                                                                                                                                                                                       | Security                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               | 74                                                                                                                                             |

|   |                                                |                                                                                                                                                                                                       | sion                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               |                                                                                                                                                |

|   | 4.13                                           |                                                                                                                                                                                                       | A Virtio-based Nahanni Device                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               |                                                                                                                                                |

|   |                                                | 4.13.1                                                                                                                                                                                                |                                               | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | • •                                                                                                      | • •                                                                                                                                                                                                                                                                                                                                                            | •                                                                                           | • •                                                                           |                                                                               |                                                                                                                                                |

|   | 1 11                                           | Conclu                                                                                                                                                                                                | ding Remarks                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               | 76                                                                                                                                             |

|   | 4.14                                           | Conclu                                                                                                                                                                                                | ding Remarks                                  | • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                | •                                                                                           | • •                                                                           | •                                                                             | 76                                                                                                                                             |

| 5 |                                                | Conclu<br>uation                                                                                                                                                                                      | ding Remarks                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                | •                                                                                           |                                                                               |                                                                               | 76<br><b>77</b>                                                                                                                                |

| 5 |                                                | uation                                                                                                                                                                                                |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               |                                                                                                                                                |

| 5 | Eval                                           | <b>uation</b><br>Experii                                                                                                                                                                              | ding Remarks                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               | 77                                                                                                                                             |

| 5 | Eval<br>5.1                                    | <b>uation</b><br>Experii<br>Definit                                                                                                                                                                   | mental Methodology                            | <br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <br>                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |                                                                               |                                                                               | <b>77</b><br>77                                                                                                                                |

| 5 | <b>Eval</b><br>5.1<br>5.2                      | <b>uation</b><br>Experii<br>Definit                                                                                                                                                                   | mental Methodology                            | <br><br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <br><br>                                                                                                 | <br>                                                                                                                                                                                                                                                                                                                                                           |                                                                                             | <br>                                                                          | · ·                                                                           | <b>77</b><br>77<br>78<br>81                                                                                                                    |

| 5 | <b>Eval</b><br>5.1<br>5.2                      | <b>uation</b><br>Experin<br>Definit<br>Microb                                                                                                                                                         | mental Methodology                            | <br><br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <br><br>                                                                                                 | <br><br>                                                                                                                                                                                                                                                                                                                                                       |                                                                                             | <br><br>                                                                      | · ·                                                                           | <b>77</b><br>77<br>78<br>81<br>82                                                                                                              |

| 5 | <b>Eval</b><br>5.1<br>5.2                      | uation<br>Experin<br>Definit<br>Microb<br>5.3.1<br>5.3.2                                                                                                                                              | mental Methodology                            | · ·<br>· ·<br>· ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | · ·<br>· ·<br>· ·                                                                                        | · ·<br>· ·<br>· ·                                                                                                                                                                                                                                                                                                                                              |                                                                                             | · ·<br>· ·                                                                    | · •                                                                           | <b>77</b><br>77<br>78<br>81<br>82<br>83                                                                                                        |

| 5 | <b>Eval</b><br>5.1<br>5.2<br>5.3               | uation<br>Experin<br>Definit<br>Microb<br>5.3.1<br>5.3.2<br>5.3.3                                                                                                                                     | mental Methodology                            | · ·<br>· ·<br>· ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <br><br><br><br>                                                                                         | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                          |                                                                                             | · · ·                                                                         | · •                                                                           | 77<br>77<br>78<br>81<br>82<br>83<br>88                                                                                                         |

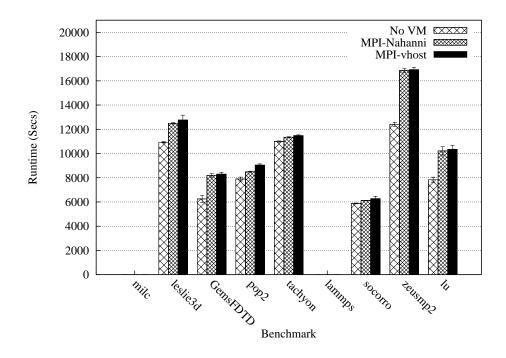

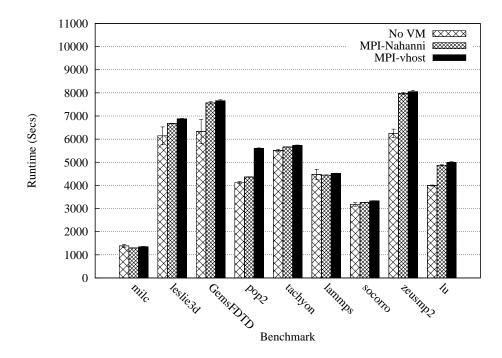

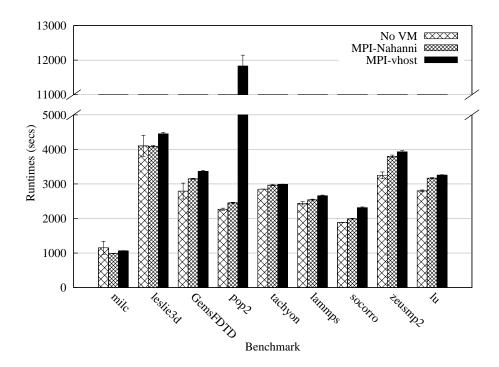

| 5 | <b>Eval</b><br>5.1<br>5.2<br>5.3               | uation<br>Experin<br>Definit<br>Microb<br>5.3.1<br>5.3.2<br>5.3.3<br>Benchr                                                                                                                           | mental Methodology                            | · ·<br>· ·<br>· ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <br><br><br><br><br>                                                                                     | · · ·<br>· · ·<br>· · ·                                                                                                                                                                                                                                                                                                                                        |                                                                                             | · · · · · · · · · · · · · · · · · · ·                                         | · •<br>· •<br>· •                                                             | 77<br>77<br>78<br>81<br>82<br>83<br>88<br>88                                                                                                   |

| 5 | <b>Eval</b><br>5.1<br>5.2<br>5.3               | uation<br>Experin<br>Definit<br>Microb<br>5.3.1<br>5.3.2<br>5.3.3<br>Benchr<br>5.4.1                                                                                                                  | mental Methodology                            | · · ·<br>· · ·<br>· · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | · · ·<br>· · ·<br>· · ·                                                                                  | · · ·<br>· · ·<br>· · ·                                                                                                                                                                                                                                                                                                                                        |                                                                                             | · · · · · · · · · · · · · · · · · · ·                                         | · • •<br>· • •<br>· • •<br>· • •                                              | 77<br>77<br>78<br>81<br>82<br>83<br>88<br>88<br>88<br>88                                                                                       |

| 5 | <b>Eval</b><br>5.1<br>5.2<br>5.3               | uation<br>Experin<br>Definit<br>Microb<br>5.3.1<br>5.3.2<br>5.3.3<br>Benchr<br>5.4.1<br>5.4.2                                                                                                         | mental Methodology                            | · · ·<br>· · ·<br>· · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | · · ·<br>· · ·<br>· · ·                                                                                  | · · ·<br>· · ·<br>· · ·                                                                                                                                                                                                                                                                                                                                        |                                                                                             | · · ·<br>· · ·<br>· · ·                                                       | · • •<br>· • •<br>· • •<br>· • •<br>· • •                                     | 77<br>77<br>78<br>81<br>82<br>83<br>88<br>88<br>88<br>88<br>89<br>90                                                                           |

| 5 | <b>Eval</b><br>5.1<br>5.2<br>5.3<br>5.4        | uation<br>Experin<br>Definit<br>Microb<br>5.3.1<br>5.3.2<br>5.3.3<br>Benchr<br>5.4.1<br>5.4.2<br>5.4.3                                                                                                | mental Methodology                            | · · ·<br>· · ·<br>· · ·<br>· · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | · · ·<br>· · ·<br>· · ·<br>· · ·                                                                         | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                          | ·<br>·<br>·<br>·                                                                            | · · ·<br>· · ·<br>· · ·                                                       | · • •<br>· • •<br>· • •<br>· • •<br>· • •                                     | 77<br>77<br>78<br>81<br>82<br>83<br>88<br>88<br>88<br>88<br>90<br>90                                                                           |

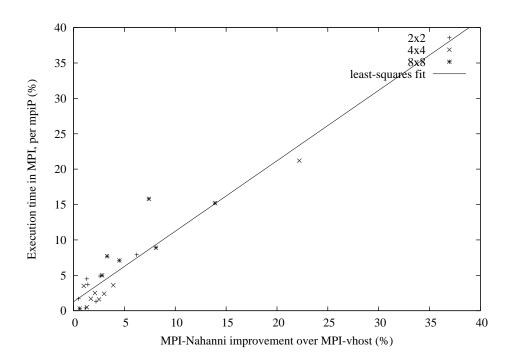

| 5 | <b>Eval</b><br>5.1<br>5.2<br>5.3               | uation<br>Experin<br>Definit<br>Microb<br>5.3.1<br>5.3.2<br>5.3.3<br>Benchr<br>5.4.1<br>5.4.2<br>5.4.3<br>Applica                                                                                     | mental Methodology                            | · · ·<br>· · ·<br>· · ·<br>· · ·<br>· · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | · · ·<br>· · ·<br>· · ·<br>· · ·                                                                         | · · ·<br>· · ·<br>· · ·<br>· · ·<br>· ·                                                                                                                                                                                                                                                                                                                        | ·<br>·<br>·<br>·<br>·                                                                       | · · ·<br>· · ·<br>· · ·<br>· · ·                                              | · • •<br>· • •<br>· • •<br>· • •<br>· • •<br>· • •<br>· • •                   | 77<br>77<br>78<br>81<br>82<br>83<br>88<br>88<br>88<br>89<br>90<br>90<br>90                                                                     |

| 5 | <b>Eval</b><br>5.1<br>5.2<br>5.3<br>5.4        | uation<br>Experin<br>Definit<br>Microb<br>5.3.1<br>5.3.2<br>5.3.3<br>Benchr<br>5.4.1<br>5.4.2<br>5.4.3<br>Applica<br>5.5.1                                                                            | mental Methodology                            | · · ·<br>· · ·<br>· · ·<br>· · ·<br>· · ·<br>· · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | · · ·<br>· · ·<br>· · ·<br>· · ·<br>· · ·                                                                | · · ·<br>· · ·<br>· · ·<br>· · ·<br>· · ·                                                                                                                                                                                                                                                                                                                      | ·<br>·<br>·<br>·<br>·                                                                       | · · ·<br>· · ·<br>· · ·<br>· · ·<br>· · ·                                     | · • •<br>· • •<br>· • •<br>· • •<br>· • •<br>· • •<br>· • •                   | 77<br>78<br>81<br>82<br>83<br>88<br>88<br>88<br>89<br>90<br>90<br>91<br>92                                                                     |

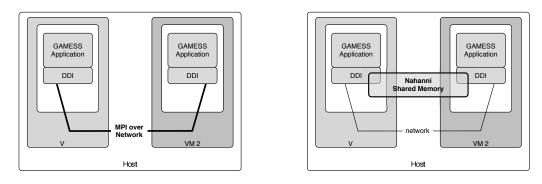

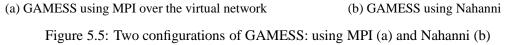

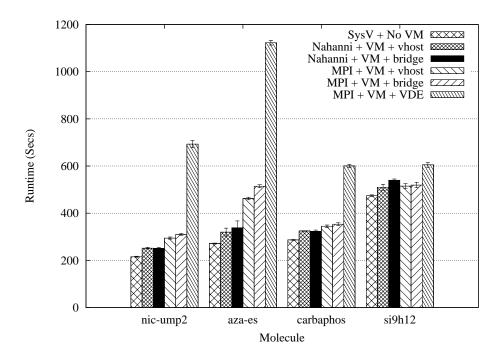

| 5 | <b>Eval</b><br>5.1<br>5.2<br>5.3<br>5.4        | uation<br>Experin<br>Definit<br>Microb<br>5.3.1<br>5.3.2<br>5.3.3<br>Benchr<br>5.4.1<br>5.4.2<br>5.4.3<br>Applica<br>5.5.1<br>5.5.2                                                                   | mental Methodology                            | · · ·<br>· · ·<br>· · ·<br>· · ·<br>· · ·<br>· · ·<br>· · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | · · ·<br>· · ·<br>· · ·<br>· · ·<br>· · ·<br>· · ·                                                       | · · ·<br>· · ·<br>· · ·<br>· · ·<br>· · ·<br>· · ·                                                                                                                                                                                                                                                                                                             | ·<br>·<br>·<br>·<br>·<br>·                                                                  | · · ·<br>· · ·<br>· · ·<br>· · ·<br>· · ·                                     | · • •<br>· • • | 77<br>77<br>78<br>81<br>82<br>83<br>88<br>88<br>88<br>89<br>90<br>90<br>90<br>91<br>92<br>96                                                   |