National Library of Canada

Bibliothèque nationale du Canada

**Canadian Theses Service**

Service des thèses canadiennes

Otawa, Canada K1A 0N4

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# The University of Alberta

# MANAGING DESIGN INTERACTIONS WITH CONSTRAINT PROPAGATION IN AN OBJECT-ORIENTED IC DESIGN ENVIRONMENT

by

Tai A. Ly

#### A thesis

submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Master of Science

Department of Electrical Engineering

Edmonton, Alberta Spring, 1989

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

> The author has granted an irrevocable nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

> The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-52842-7

# THE UNIVERSITY OF ALBERTA

#### RELEASE FORM

NAME OF AUTHOR: Tai A. Ly

TITLE OF THESIS:

Managing Design Interactions With Constraint Propagation in an Object-Oriented IC Design Environment

DEGREE FOR WHICH THIS THESIS WAS PRESENTED: Master of Science

YEAR THIS DEGREE GRANTED: 1989

Permission is hereby granted to The University of Alberta Library to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly or scientific research purposes only.

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.

Dated 6 April 1989

#### THE UNIVERSITY OF ALBERTA

#### FACULTY OF GRADUATE STUDIES AND RESEARCH

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies and Research, for acceptance, a thesis entitled Managing Design Interactions with Constraint Propagation in an Object-Oriented IC Design Environment submitted by Tai A. Ly in partial fulfillment of the requirements for the degree of Master of Science.

Supervisor

Jock havelynber Due Lyfu

Date

April 6, 1989

#### **ABSTRACT**

In IC designs, hierarchical design techniques are widely used to manage the complexity of the design tasks. However, purely top-down or bottom-up design approaches often lead to poor designs because low-level characteristics and high-level specifications do not interact. Better designs are achieved if the bottom-up characteristics of critical components of a design are used to guide the top-down specifications of the other components in the design. This has been referred to as the "least-commitment" strategy of design. To support least-commitment designs, an IC design environment must manage complex interactions among different components in a design.

This thesis investigates constraint propagation as a mechanism for managing such design interactions. Specifically, an object-oriented framework of constraint propagation which manages arbitrary design interactions and supports a least-commitment IC design is presented.

There are two major contributions in this constraint propagation framework. First, it is hierarchical. Constraint networks are organized in hierarchies that parallel the design hierarchies to take advantage of inherent structures in IC designs. As soon as design characteristics become available, they are propagated up the design hierarchy and compared with specifications at various levels. This provides design checking in a global context. Second, this constraint propagation framework is object-oriented. Propagation knowledge is encoded in procedures of abstract data types and inherited by other types in the system. New kinds of constraints are easily added to this framework and arbitrary propagation behavior can be defined by redefining the default procedures.

This framework has been implemented in an integrated design environment named STEM (SmallTalk Environment for Module design) which was developed under a related project. Three sample applications making use of constraint propagation have also been implemented. These are presented in this thesis to demonstrate that constraint propagation is a powerful mechanism for managing arbitrary design interactions in an object-oriented IC design environment.

# **Acknowledgements**

I would like to thank my supervisor, Emil Girczyc, for his guidance and support, and for his heroic work on STEM that provided the platform for this research. I would like to thank Ron Miller, who implemented the Spice interface in STEM and cleaned up a lot of code in the system, and Kent Richardson, who helped implement the initial version of STEM. Last but not least, I thank my wife Christina for her love and support through my graduate school years.

# **Table of Contents**

| Chapter 1. Introduction                                   | Page<br>1 |

|-----------------------------------------------------------|-----------|

| 1.1. The Least-Commitment Strategy of Design              | . 2       |

| 1.2. Integrated IC Design Environments                    | . 3       |

| 1.3. Constraint Propagation                               | . 4       |

| 1.4. Overview of Thesis                                   | . 5       |

| Chapter 2. Related Work                                   | 6         |

| 2.1. Constraints in IC Designs                            | . 6       |

| 2.1.1. Electric                                           | 6         |

| 2.1.2. VEXED                                              | . 7       |

| 2.2. Constraint Propagation in Al                         | 9         |

| 2.2.1. EL                                                 | 9         |

| 2.2.2. MOLGEN                                             | 10        |

| 2.2.3. ThingLab                                           | 11        |

| 2.2.4. CONSTRAINTS                                        | 12        |

| Chapter 3. STEM: an Object-Oriented IC Design Environment | 13        |

| 3.1. Introduction                                         | 13        |

| 3.2. Related Work                                         | 14        |

| 3.3. STEM                                                 | 15        |

| 3.3.1. Model-View-Controller                              | 15        |

| 3.3.2. Design Representation in STEM                      | 16        |

| Chanter 4 Constraint Propagation                          | 10        |

| 4.1. Constraint Networks                           | 19 |

|----------------------------------------------------|----|

| 4.1.1. Variable Objects                            | 19 |

| 4.1.2. Cc.nstraint Objects                         | 22 |

| 4.2. Constraint Propagation                        | 24 |

| 4.2.1. Propagation Scheduling                      | 26 |

| 4.2.2. Termination Criteria                        | 29 |

| 4.2.3. Constraint Violation                        | 31 |

| 4.2.4. Justification for Variable Values           | 32 |

| 4.2.5. Addition and Deletion of Constraints        | 35 |

| Chapter 5. Integration of Constraints in STEM      | 38 |

| 5.1. Hierarchical Constraint Propagation           | 39 |

| 5.1.1. Implicit Constraint Variables               | 42 |

| 5.1.2. Scheduling of Implicit Constraint Variables | 44 |

| 5.2. Violation Handling                            | 45 |

| 5.3. Constraint Creation                           | 46 |

| 5.4. Constraint Editor                             | 47 |

| Chapter 6. Consistency Maintenance                 | 49 |

| 6.1. Introduction                                  | 49 |

| 6.2. Application Interface: Related Work           | 50 |

| 6.3. STEM's Approach to Application Interface      | 51 |

| 6.4. Application Interface                         | 53 |

| 6.4.1. Internal Application Programs               | 54 |

| 6.4.2 External Application Programs                | 56 |

| 6.5. Change Management                              | 59 |

|-----------------------------------------------------|----|

| 6.5.1. Internal Consistency Maintenance             | 59 |

| 6.5.2. External Consistency Maintenance             | 61 |

| 6.6. Summary                                        | 62 |

| Chapter 7. Incremental Design Checking              | 63 |

| 7.1. Signal Types                                   | 64 |

| 7.2. Bounding Box                                   | 70 |

| 7.3. Delay                                          | 74 |

| 7.4. Summary                                        | 78 |

| Chapter 8. Module Validation                        | 80 |

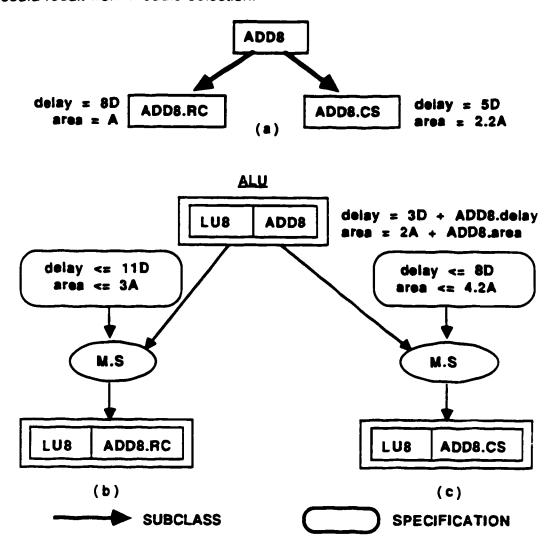

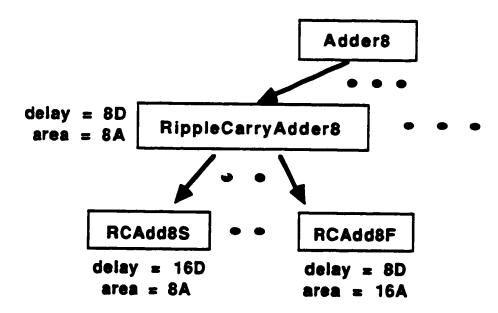

| 8.1. Module Selection by Generate and Test          | 82 |

| 8.2. Techniques for Efficiency Improvement          | 83 |

| 8.3. Summary                                        | 87 |

| Chapter 9. Conclusion                               | 88 |

| 9.1. Summary                                        | 85 |

| 9.2. Discussions                                    | 89 |

| 9.2.1. Distinctions from Previous Work              | 91 |

| 9.2.2. Comments on STEM                             | 92 |

| 9.2.3. Limitations of STEM's Constraint Propagation | 93 |

| 9.3. Suggestions for Future Work                    | 94 |

| Defendance                                          | 97 |

# List of Figures

| Figu<br>3.1  | The Model-View-Controller Concept                           | Page<br>15 |

|--------------|-------------------------------------------------------------|------------|

| 3.2          | STEM's two-level model of the design hierarchy              | 17         |

| 3.3          | Dual instance variables in cell classes and cell instances  | 18         |

| 4.1          | Variable structure                                          | 20         |

| 4.2          | Code segments for setTo:justification:                      | 21         |

| 4.3          | Code segment for setTo:constraint:justification:            | 22         |

| 4.4          | Propagation and satisfaction methods for EqualityConstraint | 23         |

| 4.5          | Constraint propagation in a simple network                  | 25         |

| 4.6          | Code segment of constraint checking for visited constraints | . 26       |

| 4.7          | Scheduling of functional constraints                        | . 27       |

| 4.8          | Code segment for propagating scheduled constraints          | . 28       |

| 4.9          | Cyclic constraints and their propagation                    | . 30       |

| 4.10         | Code segments for the default violation handler             | . 32       |

| <b>4.1</b> 1 | 1 Code segments for antecedents                             | . 34       |

| 4.12         | 2 Code segments for consequences                            | . 35       |

| 4.13         | 3 Code segment for adding a constraint                      | . 36       |

| 4.14         | 4 Code segment for removing a constraint                    | . 37       |

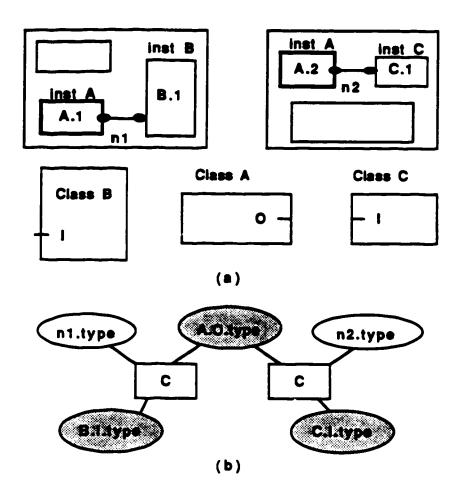

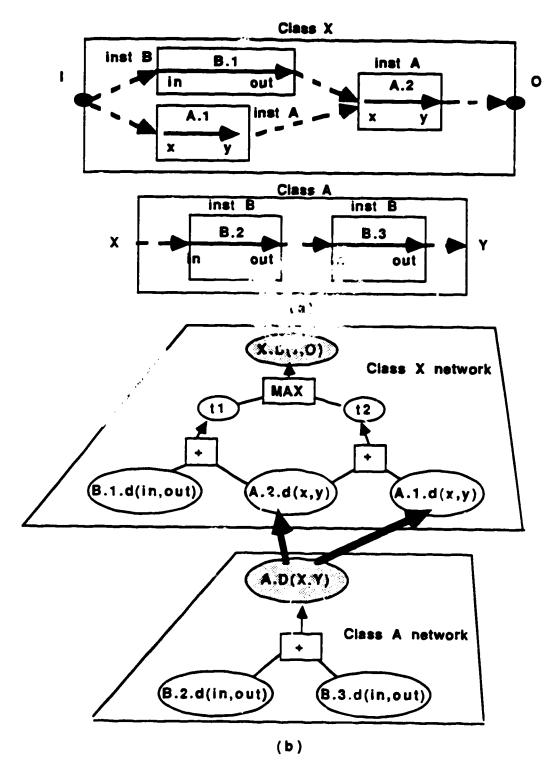

| 5.1          | Two level hierarchical constraint networks                  | . 39       |

| 5.2          | Example of a hierarchical constraint network                | . 41       |

| 5.3          | Code segments for implicit constraints propagation          | . 44       |

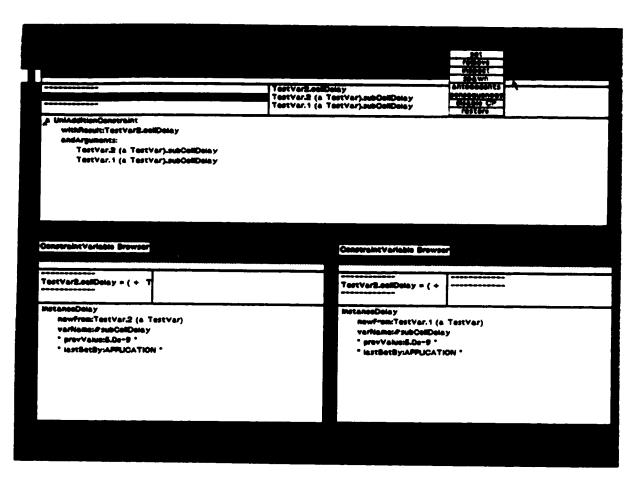

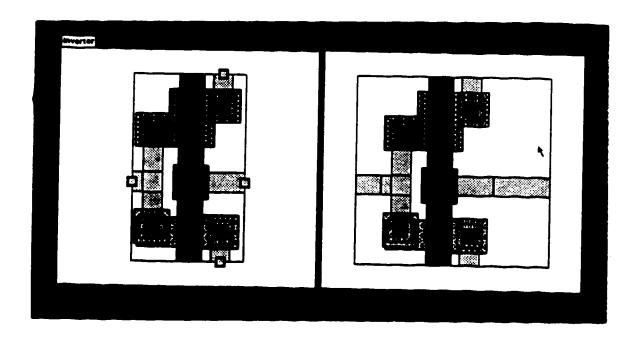

| 5.4          | Screendump of Constraint Editors                            | . 48       |

| 6.1  | Declaration and methods for PropertyVariable               | 52 |

|------|------------------------------------------------------------|----|

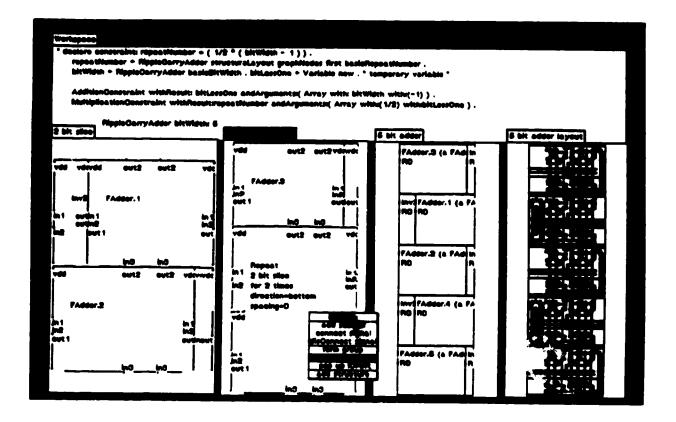

| 6.2  | Building a 5-bit Adder with a GraphCompiler                | 55 |

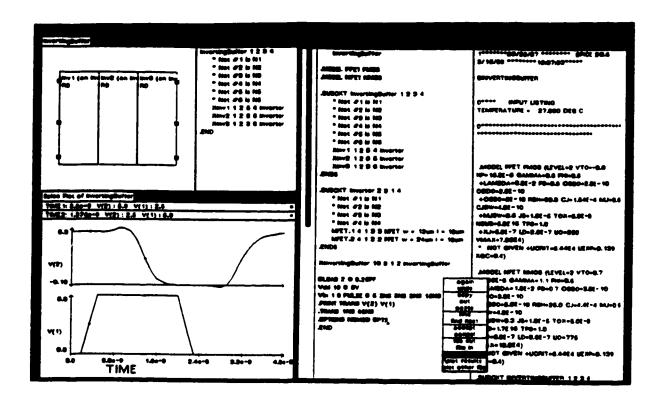

| 6.3  | SpiceNet, SpiceSimulation and SpicePlot                    | 58 |

| 6.4  | User-specified EqualityConstraint in initialization method | 60 |

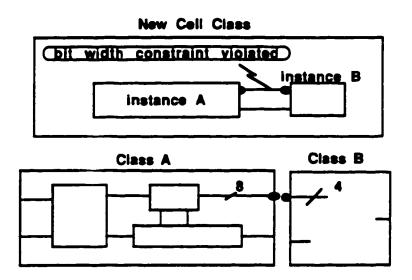

| 7.1  | Example of bit width constraint violation                  | 66 |

| 7.2  | Signal type hierarchies                                    | 66 |

| 7.3  | Type hierarchy test methods                                | 67 |

| 7.4  | Code segments showing signal variable overwrite rule       | 68 |

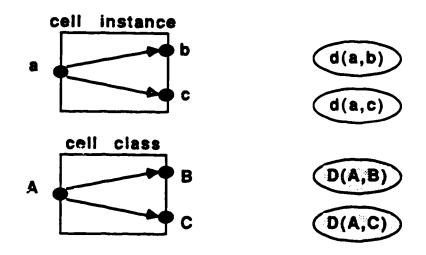

| 7.5  | Signal type constraints due to different cell instances    | 69 |

| 7.6  | Screendump showing stretching of io-pins to bounding box   | 70 |

| 7.7  | Code segments for bounding box                             | 71 |

| 7.8  | Subcell bounding box updates parent bounding box           | 72 |

| 7.9  | AspectRatioPredicate Definition                            | 73 |

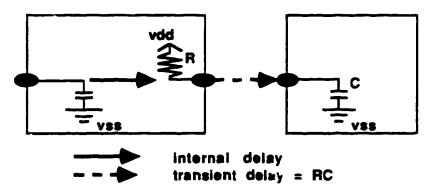

| 7.10 | The delay model                                            | 74 |

| 7.1  | 1 Dual delay variables in cell class and instances         | 75 |

| 7.12 | 2 Hierarchical delay paths and delay constraints           | 7  |

| 8.1  | Example of module selection                                | 8  |

| 8.2  | Test methods                                               | 84 |

| 8.3  | Code for Module Selection                                  | 8  |

| 8.4  | Generic class with properties for search pruning           | 8  |

| 9.1  | Two level hierarchical constraint networks                 | 9  |

# Chapter 1. Introduction

In integrated circuit (IC) designs, hierarchical design techniques are widely used to partition a design task into several smaller tasks, each of which is similarly partitioned in turn. In a purely top-down approach, designers start with initial cell specifications, successively decompose the cell into smaller cells and define their interfaces by additional specifications, until the leaf cells of the design hierarchy consist of simple components which can either be designed directly or implemented using library cells. In a purely bottom-up approach, small cells are successively combined into larger cells, whose characteristics are functions of their component cells and interconnects, until a cell which satisfies all design specifications is obtained. These hierarchical design techniques reduce the complexity of design tasks by limiting the interactions among components in the design. This trades off design quality against design time.

ter and easier to iterate the design process and explore different design alternatives. This in turn increases the demand for design environments to do more than traditional design management tasks and provide more methodology support. Most design environments support and encourage hierarchical design methodologies, especially top-down hierarchical design, which offers flexibility in high-level design decisions and is therefore advantageous for design explorations. Unfortunately, these high level decisions are often poorly evaluated because hierarchical designs limit interactions among design components. Specifically, low level design characteristics of components are not considered in higher level specifications of interacting components. This increases the number of design iterations, in which design characteristics are used to correct previous high-level decisions, resulting in new specifications that often require

major redesigns. A better design process would use low-level design characteristics much earlier in the design cycle.

The main motivation behind this research is to provide design environment support for an alternative design methodology, the "least-commitment" strategy of design, in which low-level design characteristics interact with higher level design specifications. In order to do this, the design environment must manage complex interactions among characteristics and specifications of different design components. Towards this end, this thesis investigates a framework of constraint propagation for managing such design interactions in an object-oriented IC design environment.

The following sections provide background information on the least-commitment design strategy, IC design environments and constraint propagation.

# 1.1. The Least-Commitment Strategy of Design

Mixing top-down specifications with bottom-up design uses low-level characteristics early in the "esign cycle to guide high-level design decisions. The critical parts of a cell are designed first in considerable detail, which then guide the refinement of design specifications for the rest of the cell. This strategy of deferring design decisions for as long as possible has been referred to as the "least commitment" strategy of design ([Stef81] [Mitc85]).

For example, if the critical delay path of a cell has two subcells, top-down design would assign estimated delay specifications to each of the two subcells such that their sum satisfies the overall delay specification. The two subcells are then designed independently. The fact that the delay of one subcell may be less than its specified delay is not used to relax the delay specification for the

other subcell until design backtracking, when some specifications cannot be r.net. On the other hand, the "least-commitment" strategy of design would only require that the sum of delays of these subcells satisfy the overall delay specification. The delay specification of each subcell is not "committed" until the characteristic delay of the other subcell is known. The bottom-up characteristics of a subcell are used as soon as they become available to refine (implicit) specifications of other, related subcells.

#### 1.2. Integrated IC Design Environments

Integrated IC design environments aim to provide systems in which design tools can be easily integrated. Most design environments manage a central design database, from which different tools obtain their required data. Due to the different design representations required by different design tools, multiple views of a design must be provided by the environment. For example, while a design rule check (DRC) tool views a design as a set of rectangles in different layers, an electrical simulation tool views a design as a set of interconnected electrical components (e.g., transistors, capacitors, resistors). The interface between the design database and design tools must maintain data consistency among different representations of a design, allow concurrent execution of design tools in the environment (e.g., concurrent editing of a design in two separate windows), and facilitate the development and integration of new design tools.

In order to support a least-commitment design strategy, an integrated IC design environment must manage interactions among specifications and characteristics of different designs. One approach to managing these interactions is to declare explicit constraints among cells, and use propagation of con-

straints to resolve design interactions.

#### 1.3. Constraint Propagation

Constraints are representations of relations that must be true. The power of constraints lies in their capacity to specify consistent value sets for variables. For example, while one equality-constraint can specify that three variables have equal values, the procedural representation of the same relationship is more involved (e.g., checking for equality in the access functions for each variable). Whenever values are assigned to variables, constraints on these variables are checked to ensure that these value assignments maintain a consistent set of variable values. Inconsistent variable values manifest themselves as constraint violations, which require either constraint satisfaction routines, or user intervention, to restore consistency in these variable values.

Constraint propagation is a process in which knowledge about a constraint is used to infer variable values from the values of other variables in the constraint. For example, in order to maintain an equality constraint among a set of variables when a value is assigned to one of these variables, one can simply set all other variables to the same value. These value assignments in turn trigger further value assignments by other constraints, and the effects of the initial value assignment may be propagated to arbitrary distance. This propagation of constraints is inherently an incremental process, in the sense that only those parts of the constraint networks that are affected participate in the propagation. This data directed computation is an important property in an interactive design environment, in which design feedback and system response are both important.

#### 1.4. Overview of Thesis

This thesis presents an object-oriented, hierarchical framework of constraint propagation in an integrated IC design environment. The framework manages arbitrary design constraints, and supports a least-commitment strategy of IC design. It is implemented in STEM (SmallTalk Environment for Module design) [Girc87] using Smalltalk-80 [Gold83]. Sample applications of constraint propagation have been implemented to demonstrate the feasibility of the propagation framework.

The organization of this thesis is as follows. Chapter 2 surveys related work in the fields of integrated design environments and artificial intelligence. Chapter 3 presents a background overview of STEM, with emphasis on STEM's model-view-controller construct and its two level model of the design hierarchy. Chapter 4 describes the details of the constraint propagation framework. Chapter 5 discusses STEM's integration of this propagation framework and the hierarchical implementation of constraint propagation. Chapters 6, 7 and 8 each present a different type of sample application that makes use of constraint propagation in STEM. Finally, chapter 9 summarizes this thesis and concludes with suggestions for future research.

## Chapter 2. Related Work

This chapter discusses past research in two major areas related to this thesis. Section 2.1 surveys the use of constraints in IC designs. Section 2.2 surveys constraint propagation systems in artificial intelligence (AI) research.

## 2.1. Constraints in IC Designs

Many design problems can be formulated as constraint satisfaction problems. Low-level IC designs routinely use linear inequality constraints on positions of layout objects. For example, graph-based compaction algorithms build vertical and horizontal constraint graphs, solve for the maximally constrained paths in the graphs, and then assign node positions to satisfy all constraints in the graphs. Constraint layout languages like Igloo [Pulv87] also incorporate similar linear inequality constraints in procedural layout languages to facilitate the definition of technology independent, parameterizable layouts. Two notable IC design systems that make use of constraints are Electric [Rubi87] and VEXED [Mitc85].

#### 2.1.1. Electric

Electric [Rubi87] is an integrated IC design environment which incorporates many tools for (primarily) tayout design. Electric contains a hierarchical, linear inequality constraint system that supports manual design layout. In this system, the user textually or graphically enters linear relations for X, Y coordinates of different geometric objects in the layout. For example, to keep center points of two rectangles at the same "height" in a layout, an equality constraint can be specified on the Y coordinates of these two points. These constraints are treated as properties of wires in the layout, and are stored in the design

database as design data. As the layout is manipulated, a constraint satisfaction routine incrementally solves the constraint networks in a hierarchical manner, performing compaction or decompaction of cells to satisfy connectivity constraints, layout design rules, and layout constraints specified by the designer. A textual report of the constraints on selected objects and the present values that satisfy these constraints is generated on demand. This combines quick, graphical layout entry with flexible, textual parameterization of these layouts using constraints.

However, while layout constraints involving only linear inequalities can be solved with constraint satisfaction, constraints in general include many other types of relations that are not easily solved by any single satisfaction algorithm. For example, the constraint that a component must be centered between two others cannot be expressed in terms of linear inequality constraints in Electric's constraint system [Rubi87].

Electric also provides a Prolog language interface through which users can access a Prolog interpreter. While this provides a gateway for user defined constraints and (Prolog) propagation of these constraints, it does not provide a system wide support for integrating constraint propagation into other design tools in the environment.

#### 2.1.2. **VEXED**

VEXED [Mitc85] is a knowledge-based consultant for VLSI design. The system makes recommendations for design refinements based on functional specifications. VEXED embodies three categories of knowledge: implementation, control, and causal knowledge. Implementation knowledge encodes the legal implementations for typical design specifications, and control knowledge

guides the design process by ranking the merits of alternative design steps at any given stage. The causal knowledge is used to propagate information about circuit behavior and design constraints from one part of the circuit to another. This causal knowledge is embodied in CRITTER [Kell84], which propagates and checks constraints on value, encoding, and timing of signals.

The CRITTER system is a knowledge-based system for automated critiquing of digital circuit designs. The system works with signal specifications and behaviors that are represented by functional mappings on data-streams. CRITTER analyzes only functional correctness, timing robustness, and speed of a circuit. The input/output mappings of circuit modules are represented as explicit equations for each "feature", and propagation of signal behaviors is accomplished by substitution operations with algebraic simplification. Signal behaviors are propagated forward, while specifications can be propagated backward, by the equation substitution process. The signal behaviors are compared with their specifications and a critique of the circuit is generated.

Besides incorporating CRITTER for managing signal constraints, VEXED also incorporates the BULLDOG [Roac84] system to manage constraints on design layouts. VEXED supports a least-commitment strategy of design by propagating design specifications and behaviors. However, it does not appear to have a unified framework of constraint propagation by which arbitrary extensions to the constraint system may be easily implemented. As a result, each separate subsystem in VEXED would have to replicate general knowledge about constraint propagation, and interactions among different subsystems would require additional knowledge about different constraint systems in these subsystems.

#### 2.2. Constraint Propagation in Al

Propagation of constraints as a general analysis method has been used in both analysis programs (EL [Suss 75, Stall77]) and synthesis programs (SYN [Klee78], MOLGEN [Stef81]). ThingLab [Born77] uses constraint propagation in interactive, graphical simulations of systems. Constraint-based programming languages like CONSTRAINTS [Suss80] facilitate the explicit modeling of interactions among components in "nearly-decomposable" systems.

#### 2.2.1. EL

EL [Stall77] is a knowledge-based system for analysis of electronic circuits. It solves the voltage and current values of electrical nodes in a circuit by the method of constraint propagation. Initially, the system picks a node and introduces variables to be the node's voltage and current. Forward chaining of rules determines the voltages and currents of some other nodes in the circuit in terms of these variables. Whenever there is no more applicable rules, the system picks another "unknown" node and introduces new variables. A "coincidence" occurs when a node which already has a voltage (current) is assigned a new voltage (current). The equation involved in a coincidence can be a tautology, a contradiction, or neither. If it is a tautology, nothing is done; if it is a contradiction, backtracking is invoked to change some assumed states of non-linear devices; if it is neither a tautology nor a contradiction, the system solves for one variable, possibly in terms of other variables, and eliminates this variable throughout the circuit.

Constraint propagation in EL involves the derivation of algebraic expressions for electrical voltages and currents across circuit elements. By propagating expressions with variables, solving local systems of equations, and then

eliminating solved variables throughout the circuit, the system imitates the way human experts analyze electrical circuits without being bogged down by an intractable system of algebraic equations. Furthermore, EL stores dependencies of propagated values for the purpose of explanation as well as dependency-directed backtracking.

#### 2.2.2. **MOLGEN**

MOLGEN [Stef81] is a hierarchical planner that plans experiments in molecular genetics. It uses constraint posting to manage the interactions among its nearly independent subproblems during the planning process. Constraint posting involves three major operations on constraints: constraint formulation, constraint propagation and constraint satisfaction. MOLGEN dynamically formulates constraints as commitments of the design process. These constraints are propagated by the creation of new constraints. Constraint satisfaction in MOLGEN is achieved either by searching its database for an object that satisfies the constraints, or by solving a subproblem of building such an object.

MOLGEN's constraint propagation operators rely on syntactic matching of the constraints, which leads to its inability to handle constraints other than those in its limited vocabulary. Again, general propagation knowledge is buried in knowledge about specific constraints, making it difficult to incorporate new types of constraints in the system.

# 2.2.3. ThingLab

ThingLab [Born77] is an interactive system, written in Smalltalk-72 [Gold76], that provides an environment for constructing simulation systems. Each ThingLab object has a list of properties, which describe both the object's internal state and its protocols for sending and receiving messages. Constraint properties of a ThingLab object restrict the behavior of the object. The constraints of an object, like all other properties, are inherited by descendents of the object. When a constraint is added or edited. ThingLab finds those constraints that may be affected, and sends messages to them requesting methods for satisfying them. The system chooses and sets up these methods, and orders the constraints and the objects to which they apply in such a way that each object can be updated in turn to satisfy its constraints in one pass (the "one-pass method") [Born77]. For more complex constraints not directly solvable with this method, the method of assumed states and the relaxation method are tried.

ThingLab provides facilities for incrementally compiling constraints, and a graphic interface controlled by the constraint network. However, since ThingLab does not distinguish between classes and instances, it apparently does not permit the abstraction of constraint networks. Although ThingLab objects inherit properties in an arbitrary abstraction hierarchy, the constraint networks in ThingLab are flat.

#### 2.2.4. CONSTRAINTS

CONSTRAINTS [Suss80] is a language for expressing almost-hierarchical descriptions. It is an interactive system organized around hierarchical networks of constraints. Constraint propagation involves the propagation of values in the constraint networks. The system provides a set of primitive constraints from which compound constraints can be constructed. Each compound constraint then serve as a syntactic abstraction of its corresponding network of constraints. Dependency information is kept with propagated values so that dependency analysis can be used to track down all antecedents of a propagated value as well as all consequences of a value. When simple constraint propagation falls, algebraic manipulation and the method of multiple redundant viewpoints (the slices) [Suss80] are used to resolve the networks of constraints.

However, CONSTRAINTS does not allow definition of new primitive constraints, thus seriously limiting the kinds of constraint networks that can be constructed in the system. Furthermore, while compound constraints provide a concise notation for complex constraint networks, they do not really reduce the computational complexity of the underlying networks. Just before propagation, each compound constraint is dynamically expanded to its component networks of primitive constraints.

# Chapter 3. STEM: an Object-Oriented IC Design Environment

This chapter<sup>1</sup> gives an overview of STEM (SmallTalk Environment for Module design) [Girc87], which serves as the platform for this research. STEM is an on-going project at the Electrical Engineering Department in the University of Alberta directed by Dr. Emil F. Girczyc. Its goal is to integrate design tools with manual IC designs using the object-oriented programming paradigm. Interested readers should refer to [Girc87] for additional details on STEM.

#### 3.1. Introduction

IC design environments [Brow83, Girc87] integrate design tools in a uniform and flexible framework for IC design as well as the development of new design tools. Object-oriented programming [Gold83] paradigms are well suited to the development of such design environments because of their abstract data typing and hierarchical inheritance facilities. Abstract data types allow grouping related data and operations on these data into logical entities (classes). This offers a high degree of program modularity, and is well suited to rapid prototyping of software systems. Abstract data types are often organized in a hierarchy of inheritance, by which data and routines may be shared among similar data types. This encourages incremental refinement of abstract data types and facilitates code reuse.

<sup>&</sup>lt;sup>1</sup> This chapter is taken out of the paper on STEM [Girc87]

#### 3.2. Related Work

Typically, an object-oriented IC design environment represents the library version of a cell as a "class" object, which encapsulates all information about the cell such as its characteristics, simulation files, and layout. Individual placements of the cell are represented by instances of this class, and contain fields to represent only that information which differs for each placement of the cell (e.g., location, orientation, and connectivity).

One of the early work in integrated environments, Palladio [Brow83] is an integrated environment that supports different programming paradigms for the development of IC CAD tools. Palladio allows the definition and refinement of "perspectives", which are explicit design representations for different sets of tools. Perspectives are independent design data in the sense that designs in Palladio are defined by a (consistent) set of perspectives, and that each perspective can be part of more than one design.

Fred [Wolf86] is an object-oriented, procedural database designed for the support of VLSI designs. Fred accommodates incomplete modules by storing default values, approximate functions, and dynamic calculations of module properties. Relations are provided as a means to group modules that satisfy certain properties. For example, generic relations specify different implementations of a generic module. Fred also features user defined "dependency", which executes a method whenever a particular message is sent to some modules.

#### 3.3. STEM

STEM (SmallTalk Environment for Module design) [Girc87] is written in Smalltalk-80 [Gold83], and differs from other object-oriented environments primarily in its emphasis on integrating calculated views with user entered views.

#### 3.3.1. Model-View-Controller

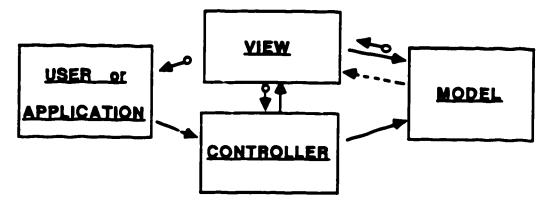

STEM is based on the Smalltalk Model-View-Controller (MVC) construct (see Fig. 3.1). A cell in STEM is represented by a single Smalltalk class, which encapsulates all the essential information about the cell. This serves as the model. In order to conserve database storage, it is desirable to have as compact a representation of the model as possible. Views and controllers are unidirectional paths implementing the interface between the user and the model.

- indicates message (direction) of requests for service or information

- o- indicates data or status information

- --> indicates message notifying view of change in model

Figure 3.1 The Model-View-Controller Concept

Controllers manage user input. A controller determines the appropriate response to keyboard or mouse input given the current states of the controller.

the model and the connected view. Due to the object-oriented nature of Smalltalk, context dependent response to user input is easily achieved. For example, when the user selects a menu item, the system response is context dependent in two ways: the associations between messages and menu items in the controller and between methods and messages in the model.

Views are representations of the model calculated from data contained in the model. Views translate a portion of the data contained in a model to a format suitable for further processing or display to the user. To accommodate different representations, different views can be employed to format the information contained in a model in different ways. This separation of data (model) and representation (view) allows new views to be added independent of existing views. The model needs to be changed to accommodate a new view only if new data is required to calculate the view.

Views and controllers are linked to the model and to each other through instance variables. This allows views and controllers to obtain data from their model, and context information from each other.

#### 3.3.2. Design Representation in STEM

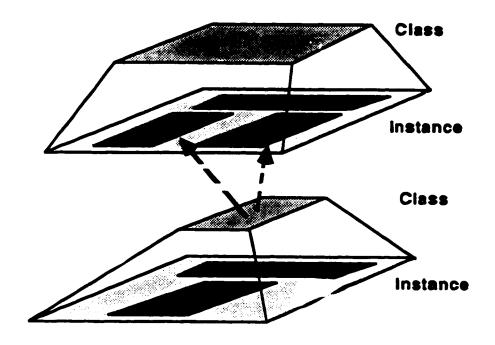

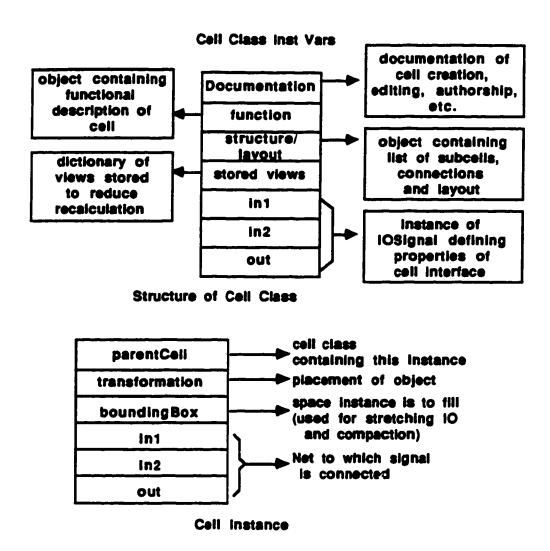

Viewed from a higher level in the design hierarchy, a cell in STEM is a black box which performs a particular function with a certain interface. The cell interface is defined by a dual declaration of instance variables for each signal, parameter and property defined for the cell. The first variable is declared as an instance variable of instances of the cell class. The value of these variables represent the net connected to a signal or the value of a parameter or property for a particular cell instance used as a component in a larger design. The second instance variable is an instance variable of the class object. This is

Figure 3.2 STEM's two-level model of the design hierarchy

used to store generic information defining the characteristic limitations of the variable in this cell. For each parameter, this instance variable contains constraints on the range of the parameter, and possibly the default value for that parameter. For each signal, this instance variable contains the data type, electrical type, bit width, and internal connectivities of the signal. This dual declaration of instance variables allows checking to insure that a cell is correctly used within larger designs, and plays an important role in STEM's implementation of hierarchical constraint propagation (Chapter 5).

The Smalltalk inheritance hierarchy is used in STEM to define specialized versions of a cell as subclasses of the cell (e.g., a ciass ADDER may have many subclasses, each of which being an adder design with a different carry propagation scheme). A subclass inherits all instance variables and methods of

Figure 3.3 Dual instance variables in cell class and cell instances

its superclass (STEM does not use multiple inheritance), and may declare additional instance variables and/or overwrite inherited methods with specialized routines. By using instance variables of classes instead of class variables, values of the inherited variables can be different among different subclasses and their parent class.

#### Chapter 4. Constraint Propagation

The constraint propagation system incorporated in STEM is organized around constraint and variable objects. The system is designed to provide background coordination for high-level design interactions such as changes in delay, area and signal types among related cells. At present no facility is provided for constraint satisfaction if simple propagation fails. Constraints can be used by both designers and design tools to evaluate alternatives and make design decisions. This chapter describes a general framework for non-hierarchical constraint propagation. While this is developed with STEM in mind, it is general enough to be implemented in any object-oriented integrated design environment. The next chapter describes STEM specific extensions to this general framework that implement hierarchical constraint propagation.

#### 4.1. Constraint Networks

A constraint network is a directed graph in which the nodes consist of "variable" objects and the edges consist of "constraint" objects. Throughout this thesis, "variables" will be depicted with oval shapes and "constraints" will be depected as rectangles with possibly arrowed lines connected to other "variable" objects.

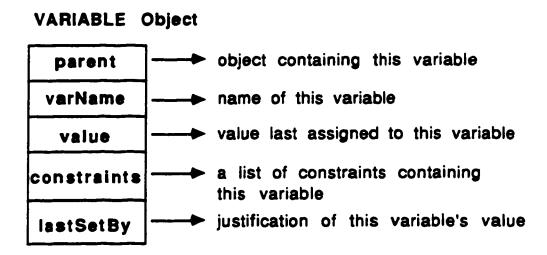

#### 4.1.1. Variable Objec物

A "variable" object (from now on simply "variables") implements an active storage, or "handle", for data so that constraints may be specified on variables independent of their values. Each variable object has a parent field, a name field, a value field, a constraints field, and a lastSetBy field (Fig. 4.1). The parent field of a variable points to the object that contains the variable, and the

name of the variable identifies the field (instance variable) of its parent that points to the variable. For example, the variable representing the boundingBox (an instance variable) of the class ADDER has ADDER as its parent and "boundingBox" as its name. The parent field and the name field of a variable provide a unique path for identification of the variable object.

Figure 4.1 Variable struc =

The value field of a variable provides storage for the value (or a pointer to the value) of the variable; the constraints field of a variable lists all constraints that reference the variable object; and the lastSetBy field of a variable records the source and possibly dependencies of the current value of the variable (see Section 4.2.4). Variable objects are instantiated during the initialization of their parent objects, and are only removed when their parent objects are removed from the system.

Two basic messages assign values to a variable object: "setTo:justification:"<sup>2</sup> (Fig. 4.2) and "setTo:constraint:justification:" (Fig. 4.3).

<sup>&</sup>lt;sup>2</sup> this is a message denotation of Smalltalk's. The colons in the message indicates the insertion of arguments, "setTo:justlfication:" accepts two arguments, one following

The first message is used by every object in the system that is not a constraint. The internal method corresponding to this message checks whether constraint propagation is enabled in the system. If it isn't, the method simply sets the variable value to the new value. On the other hand, if constraint propagation is enabled, the method initializes data structures, sets the variable value to the new value, and triggers constraint propagation. A variable propagates by sending the message "propagate variable:" (using itself as the argument) to all constraints in its constraints field.

Figure 4.2 Code segments for setTo:justification:

The second message, "setTo:constraint:justification:" is used by constraint objects to assign propagated values to variables during constraint propagation. The internal method corresponding to this message first checks whether any of the termination criteria (see Section 4.2.2) is met. If it is, control is returned; otherwise the method sets the variable value to the new (propagated) value.

<sup>&</sup>quot;set o:", and another following "justification:".

and triggers further propagation by sending the message "propagateVariable:" to all its constraints except that constraint which propagated the value to the variable in the first place (Fig 4.3).

```

Variable methodFor:'assignment'

setTo:value constraint:aConstraint justification:justification

... "check for termination criteria" ...

self tastSetBy:(Association key:aConstraint value:justification).

self prevValue:value.

self allConstraints do:[ :constraint |

constraint == aConstraint

ifFalse:[ status ← constraint propagateVariable:self.

... ]]

↑ self

```

Figure 4.3 Code segment for setTo:constraint:justification:

#### 4.1.2. Constraint Objects

The "constraint" objects (from now on simply "constraints") specify assertions on variable objects. Each constraint has an "arguments" field, which lists at least one argument which is a variable object. The semantics of a constraint are collectively defined by two methods: "immediateInferenceByChanging" and "isSatisfied". The first method takes the changed variable that activated the constraint as the argument. Generally, this method examines the changed variable and assigns inferred values to other variable arguments in the constraint. The second method tests if a constraint is satisfied by the values of its arguments. For example, for an equality-constraint (Fig. 4.4), the "isSatisfied" method tests that all non-NIL argument values are equal, and the "immediateInferenceByChanging:" method sets all arguments in the constraint (except the source variable) to the value of the source variable.

When the message "propagateVariable:" is sent to a constraint, the constraint is activated. An activated constraint propagates by sending itself the message "immediateInferenceByChanging:" with the changed variable as the argument. Subclasses of constraints customize propagation behavior primarily by redefining the methods "immediateInferenceByChanging:" and "isSatisfied".

```

Constraint methodFor:'propagate'

propagateVariable:aVariable

1 self immediateInferenceByChanging:aVariable

EqualityConstraint methodFor:'test'

immediateinferenceByChanging:aVariable

I newValue I

newValue - aVariable value.

self arguments do:[ :arg |

arg == aVariable

ifFalse:[ status - arg setTo:newValue

constraint:self

justification:aVariable.

status isNii ifTrue:[ 1 nii ]]].

IsSatisfied

| oldValue |

"check all argument values are equal"

oldValue ← arguments first value.

2 to:arguments size do:[:index |

newValue ← (arguments at:index) value.

newValue = oldValue ifFalse:[ 1 false]].

1 true

```

Figure 4.4 Propagation and satisfaction methods for EqualityConstraint

#### 4.2. Constraint Propagation

Constraint propagation is actually the propagation of value changes through a constraint network. The value changes occur when a constraint executes a propagation method (procedure) that assigns values to the constraint's argument variables (based on the values of other arguments in the constraint). The propagation comes about when an active variable activates its connected constraints and these active constraints in turn activate their argument variables. Through constraint propagation, the value change in one variable can cause changes in remote parts of the constraint network containing the variable.

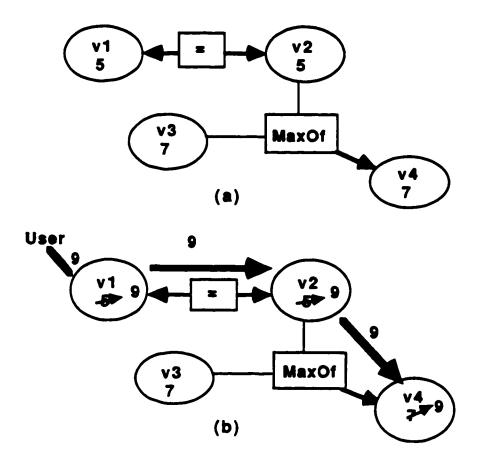

For example, Fig. 4.5(a) shows a constraint network containing the variables V1, V2, V3, V4, an equality-contraint and a maximum-constraint. In this diagram, variables are represented by circles and constraints are represented by rectangles. The arrows in the edges indicate directionality of propagation. In this constraint network, the value of V1 must be equal to that of V2, and the value of V4 must equal the maximum of the values of V2 and V3. In the diagram, all variable values satisfy their constraints.

In Fig. 4.5(b), user changes the value of V1 to 9. This triggers constraint propagation (indicated by thick arrow). The variable V1 activates the equality-constraint, which propagates by assigning V2 the value 9. This activates V2, which in turn propagates by activating the maximum-constraint. Finally, the maximum-constraint recalculates the maximum of V3 and V2 and assigns V4 the value 9.

The basic process of constraint propagation implemented in this thesis can be characterized as a depth-first traversal of a constraint network. Depth-first traversal is used instead of breadth-first to reduce the amount of intermediate state information that must be kept during the traversal. The traversal starts

Figure 4.5 Constraint propagation in a simple network

with the (external) assignment of a variable by the message "setTo:justification:", and successively spreads to all constraints of the variable. Each of these constraints in turn performs its inferences ("immediateInference-ByChanging:"), and assigns values to additional variables by the message "setTo:constraint:justification:". Each of these value assignments may trigger further constraint propagation. Throughout the propagation process, control

alternates between variables responding to the message "setTo:constraint:justification", and constraints responding to the message "propagateVariable:". All visited variables and constraints are recorded during propagation. When propagation ends without error, all visited constraints are checked for constraint violations by sending the message "isSatisfied" to each visited constraint (Fig. 4.6).

Figure 4.6 Code segment of constraint checking for visited constraints

# 4.2.1. Propagation Scheduling

When a changed variable sends the message "propagateVariable:" to a constraint, the constraint usually propagates inferred values of other argument variables as soon as possible. This is because the direction of propagation is dependent on the changed variable that initiated this propagation. In an equality-constraint involving A and B, for example, the value of the changed variable is propagated to the other variable. If A changes, B is set to A's new value; if B changes, A is set to B's new value. Propagation is performed in the first-come-first-served manner, in order that the directionality of constraint propagation be correct.

However, there are constraints whose direction of propagation is independent of the variable that changed. These are the functional-constraints, so named because they can often be expressed as a mapping of a tuple of

variables onto another tuple of variables. For example, a unidirectional, arithmetic constraint expresses one variable (the functional variable) as an arithmetic function of other variables or constants. The inference method of the constraint calculates the functional value from values of the argument variables, and assigns the resulting value to the functional variable in the constraint. For these constraints, propagation can be delayed until all argument variables have had a chance to change. This reduces redundant calculations of transient results.

An agenda object schedules the propagation of these constraints. In response to the message "propagateVariable:", a functional constraint schedules itself for propagation by adding itself to an agenda named #functionalConstraints (Fig. 4.7).

FunctionalConstraint methodFor:'propagate'

propagateVariable:aVariable

visitedConstraints add:self.

(self permitChangesByVariable:aVariable)

ifTrue:[

agendaScheduler scheduleConstraint:self

variable:nif

onAgendaNamed:#functionalConstraints]

FunctionalConstraint methodFor: test'

permitChangesByVariable:aVariable

"returns false iff aVariable is my result variable"

↑ (aVariable == self resultVariable) not

Figure 4.7 Scheduling of functional constraints

An agenda is implemented as a first-in-first-out queue that does not have duplicate elements. New entries are added to the end of an agenda provided similar entries are not already in the queue.

In general, there may be more than one agenda in the system, each with a different, fixed priority. Constraints scheduled in agendas are propagated one at a time, according to the priorities of the agenda they are scheduled in. This multi-queue, fixed priority scheduling is implemented in the variable method "setTo:justification:", which, after initial propagation of un-scheduled constraints, iteratively selects a scheduled constraint from the highest-priority agenda that is not empty and propagates it, until all agendas are empty (Fig. 4.8). Each propagation of a scheduled constraint may trigger additional propagation and schedule more constraints in the agenda. With this additional degree of control, propagation can be made more efficient by assigning higher priorities to critical constraint types such as equality-constraints and update-constraints.

```

propagate

self allConstraints do:[ :constraint

status - constraint propagateVariable;self.

...]

[scheduledEntry \( \) agendeScheduler removeHighestPriorityScheduledEntry.

scheduledEntry isNil]

whileFalse:

status ← (scheduledEntry key)

propagateScheduledVariable:(scheduledEntry value).

... ].

AgendaScheduler methodFor:'access'

removeHighestPriorityScheduledEntry

l agenda i

"returns first entry of the highest priority non-empty agenda"

(self priorityList) do:[ :agendaNa.ne |

agenda - self agendaNamed:agendaName.

agenda isEmpty ItFalse: 1 agenda removeFirst]].

1 nl

```

Variable methodFor: propagation scheduling:

Figure 4.8 Code segment for propagating scheduled constraints

### 4.2.2. Termination Criteria

The wavefront of constraint propagation may stop at one of two cases:

- 1. The propagation method of a constraint does not assign values to any variable.

- 2. in a current value of a variable agrees with the propagated value of the variable,

Constraint propagation terminates as soon as a constraint violation is detected. A constraint violation is detected during propagation in one of two cases:

- 1. The variable to be assigned a value has already been visited in the current propagation, but has a different value than the propagated value,

- 2. The current value is user-specified and cannot be modified by constraint propagation, but has a different value than the propagated value.

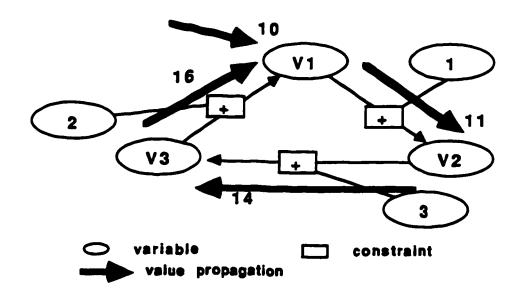

If no violation is detected during constraint propagation, then the process of constraint propagation terminates when the non-functional constraint propagation is exhausted and the agenda is empty. This termination is guaranteed in STEM by requiring that no variable be allowed to change its value twice during propagation. With this rule, STEM prohibits cyclic propagation of constraints but not the use of cyclic constraints. For example, in Fig 4.9, three addition constraints form a cyclic constraint network which cannot be satisfied. Suppose V1 is assigned a value of 10, constraint propagation (indicated by bold arrows) assigns a value of 11 to V2 and then a value of 14 to V3, and tries to assign a value of 16 to V1. However, since V1 has already changed its value once during this round of constraint propagation, this triggers a constraint violation.

This one-value-change rule is enforced with a global dictionary, VisitedCon-

Figure 4.9 Cyclic constraints and their propagation

straintsAndVariables, of all visited constraints and variables during the propagation. This global dictionary is emptied in the initialization phase of the method "setTo:justification:". Subsequently, every time a constraint propagates a value to a variable with a value different than the propagated value, the variable checks in the dictionary to see if the variable has been visited previously. If it has, a constraint violation is detected, and propagation is terminated. On the other hand, if the variable has not been visited previously, the variable adds its current state to the dictionary of visited variables, changes its value, and initiates further constraint propagation. The global dictionary records the previous state of all visited variables so that these variables can be restored to their original states if a constraint violation is detected in the new variable values.

#### 4.2.3. Constraint Violation

Although propagation methods in the constraints generally maintain consistency of the constraints, constraint violations are inevitable because only local information (in the constraint arguments) is considered in constraint propagation, and because invalid user-assigned variable values manifest themselves as constraint inconsistencies. Properly managed, constraint violations provide valuable feedback to the designers, not only on the present of design violations, but on the causes of these violations as well.

Constraint violation may be detected in the course of propagation, as soon as a propagated value disagrees with a variable value and an overwrite is not possible (either because the propagated value has no overwrite privilege over the existing value, or because the variable has been visited earlier in the propagation). Even if constraint propagation finishes without any violation, constraint violations can still exist. As a final check, the message "isSatisfied" is sent to all visited constraints to detect violations.

When a constraint violation is detected, the violation handler of the constraint is executed. The default (inherited) handler issues warning messages in a default text window, and restores the constraint networks to their original states (i.e., before constraint propagation) by restoring the states of all visited variables (Fig 4.10). However, different types of constraints may replace this with different violation handlers. For example, a constraint editor in STEM may be invoked to help designers examine and debug the constraint networks.

```

Variable methodFor:'violation handling'

violation

"restore prev values"

self restore.

...

restore

"restores prev values for all variables"

visitedVariables associationDo:[:assoc|

var ← assoc key.

var lastSetBy:assoc value key.

var prevValue:assoc value value ].

```

Figure 4.10 Code segments for the default violation handler

#### 4.2.4. Justification for Variable Values

When variables are assigned values, the justification of these values are recorded in the "lastSetBy" field of the variables. The justification of a value assignment is formulated by the sender of the assignment message and is passed to the variable as one of the arguments in the assignment message (i.e., the argument following "justification:" in both "setTo:justification:" and "setTo:constraint:justification:"). A justification can either be a symbol indicating a source external to the constraint networks or a key-value pair for a propagated value. The symbols #USER and #APPLICATION are currently used as justifications for user specified and calculated values respectively. The justification of a sariable's value determines if constraint propagation can overwrite the variable with a different propagated value. The default overwrite rule in the system is that user specified values have higher priority over propagated and calculated values. However, subclasses of variables can recegnize different strengths of constraints, and allow one type of constraints to overwrite values

from another type of constraints, but not the other way around. This is not done currently.

For propagated values, the justification is a key-value pair of two elements. The first element is the source constraint which propagated the value to this variable. The second element is a dependency record for this propagated value. This dependency record is formulated by the source constraint during propagation and analyzed by the same constraint during dependency analysis. Each dependency record contains data that enable the source constraint to trace all variable values that are responsible for the propagated value. Since dependency records are only interpreted by the constraints that formulate them, they vary greatly among different types of constraints. For example, an equality-constraint sets up a dependency record containing only the single variable that activated the constraint, but a functional constraint sets up a null dependency record since it is implicitly understood that the functional variable depends on every arguments of the . ional constraint.

With source constraints and dependency records, dependency graphs in the constraint networks can be constructed for dependency analysis. Dependency analysis can be used to search for all variables and constraints responsible for a propagated value. This is achieved primarily with two methods: "antecedents:" in variables, and "antecedents:ofVariable:" in constraints (Fig. 4.11). These two routines recursively call each other, performing a backward traversal of the dependency graphs, until all antecedent variables and constraints of a variable are found.

Dependency analysis can also be used to search for all variables that depend on a specific variable value. This is achieved with two similar methods: "consequences:" in variables, and "consequences:ofVariable:" in constraints

Variable methodFor:'dependency analysis' antecedents:aSet (aSet includes:self) liTrue:[ 1 aSet ]. aSet add:self. self isDependent liTrue: aConstraint - self lastSetBy key. aConstraint antecedents:aSet of Variable:self 1. 1 aSet Constraint methodFor:'dependency analysis' antecedents:aSet ofVariable:aVariable aSet add:self. "default method will just test all arguments one by one" dependencyRecord ← aVariable lastSetBy value. self allConstraintVariables do:[ :arg | arg == aVar #False1 (self testMembershipOf:arg inDependency:dependencyRecord) IfTrue: arg antecedents:aSet ]]]. 1 aSet testMembershipOf:aVar InDependency:dependencyRecord

"each subclass redefines its own"

self subclassResponsibility

Figure 4.11 Code segments for antecedents

(Fig. 4.12). These two routines also recursively call each other, performing a forward traversal of the dependency graphs, until all consequences of a variable's value are found.

While dependency analysis is useful in examining the constraint networks, it is essential in erasing inferences invalidated by deletion of constraints in the networks. When a constraint (variable) is removed from a network, all variable values dependent on the constraint (variable) become unjustified, and should be erased. This erasure is facilitated by dependency analysis, which finds all consequent variables of the constraint (variable). In an interactive design environment, constraint networks are frequently edited. The efficiency with which constraint (variable) removals can be accomplished with dependency analysis

justifies the storage overhead for dependency records in variables.

```

Variable methodFor:'dependency analysis'

consequences:aSet

(aSet includes:self) ifTrue:[ TaSet ].

aSet add:self.

self constraints do:[ :aConstraint |

aConstraint consequences:aSet of Variable:self].

1 aSet

Constraint methodFor: dependency analysis'

consequences:aSet ofVariable:aVariable

self allConstraintVariables do: : arg |

arg == aVariable ifFalse:

arg lastSetBy key == self "arg is set by me"

ifTrue: "then test if aVar is in dependencyRecord of arg"

dependencyRecord - arg lastSetBy value.

(self testMembershipOf:aVar inDependency:dependencyRecord)

#True: arg consequences: a Set ]]]]

```

Figure 4.12 Code segments for consequences

#### 4.2.5. Addition and Deletion of Constraints

When constrain networks are edited (i.e., when constraints or variables are added to or removed from the networks), constraint propagation must be performed to adjust variable values to changes in the networks. However, since no variable has changed value by network editing, the normal propagation trigger is not activated. Therefore, a separate triggering mechanism is developed for constraint editing.

When a constraint is added to a variable, the constraint re-initializes its variable arguments (Fig. 4.13). The argument variables are grouped into three lists: "usorSpecified", "constraintDependent", and "otherIndependents". The first and second lists contain variables whose justifications are #USER and a

```

Variable methodFor: add-remove constraints'

addConstraint:aConstraint

self constraints add:aConstraint.

aConstraint basicAddArgument:self.

status 	aConstraint reInitializeVariables.

Constraint methodFor:'add-remove arguments'

reinitializeVariables

status - self rePropagate.

rePropagate

... organize argument variables into three lists ...

list addAll: userSpecified.

list addAll: dependents.

list addAll: otherInDependents.

list do: arg

keyAbsent ← visitedVariables at:arg

putlfAbsent:(Association key:arg lastSetBy

value: arg prevValue).

keyAbsent ifTrue: status ← arg propagateAlongConstraint:self.

status isNil lfTrue: 1 nil ]]]

Variable methodFor: propagation scheduling

propagateAlongConstraint:aConstraint

status - aConstraint propagate Variable:self.

[scheduledEntry \( \) agendaScheduler removeHighestPriorityScheduledEntry.

scheduledEntry isNill

whileFalse:

status ← (scheduledEntry key)

propagateScheduledVariable:(scheduledEntry value).

status isNil ifTrue: 1 self inPropagationViolation ]].

1 self

```

Figure 4.13 Code segment for adding a constraint

constraint object, respectively, while the third list contains variables with other types of justifications (e.g., #APPLICATION). Beginning with "userSpecified" and ending with "otherIndependents", these argument variables are successively sent the message "propagateAlongConstraint:" with the edited constraint

as the argument. In response to this message, each variable propagates its value to the edited constraint. This gives a chance to all variable arguments in the edited constraint to assert and propagate their values, in order of their precedence. If constraint propagation finishes without violations, all visited variables are explicitly checked for constraint violation by sending the message "isSatisfied" to them.

When a constraint is removed from a variable, all propagated values that depend on this constraint/variable pair are reset to NIL. This is accomplished by dependency analysis (Fig. 4.14). If the variable's value is changed by removing the constraint, then all consequences of the variable have to be reset. If the variable's value does not change when the constraint is removed, then all consequences of the constraint that depend on this variable have to be reset. In either case, the removed constraint then re-initializes its remaining argument variables.

removeConstraint:aConstraint self constraints remove:aConstraint. aConstraint basicRemoveArgument:self. self lastSetBy key == aConstraint ITrue: "my value is last set by aConstraint. reset me and all my consequences" self variableConsequences do:[ :aVar | aVar reset ]] IfFalse: "reset all variables that are consequences of me propagating through aConstraint" set ← Set new. aConstraint consequences:set of Variable:self. set do:[ :aVar | aVar reset ]. "rePropagate aConstraint" aConstrair: reinitializeVariables

Variable methodFor: 'add-remove constraints'

Figure 4.14 Code segment for removing a constraint

## Chapter 5. Integration of Constraints in STEM

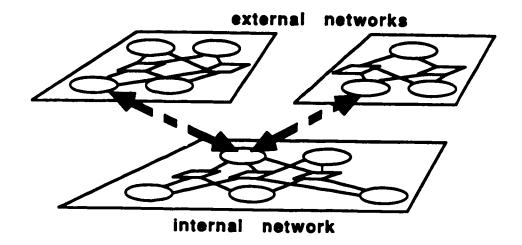

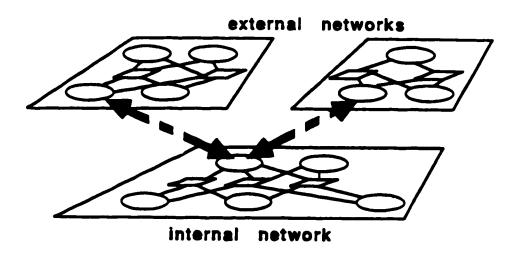

This chapter presents the way in which the constraint propagation framework is integrated with design objects in STEM. In order to take full advantage of inherent structures in these design objects, STEM specific extensions are added which implement hierarchical constraint propagation. With hierarchical constraint propagation, constraint networks in each cell class are separate from those in other cell classes, and yet constraint propagation can spread from one network to another up and down a hierarchy which parallels that of the design objects. Basically, hierarchical constraint propagation occurs when propagation in the constraint network of one cell activates additional propagation in constraint networks of cells containing instances of the original cell or cells whose instances are part of the original cell.

Hierarchical constraint propagation is achieved with STEM's dual instance variables in the class and instance definitions of cells. These dual variables provide the implicit propagation links between otherwise isolated constraint networks at the cell class level and cell instance levels. Hierarchical constraint propagation reduces the amount of redundant computation in composite networks. For example, Fig 5.1 shows three isolated constraint networks that are linked by implicit constraints (indicated by the bold dotted arrows) between dual instance variables in the cell class and cell instances. When constraint propagation in the lower network changes the value of the variable in the cell class, hierarchical propagation changes the variable values in the two cell instances and triggers additional propagation in the two upper level networks. Without hierarchical constraint propagation, the lower level constraints in Fig. 5.1 would be propagated twice: once for each of the two upper level networks containing them.

Figure 5.1 Two level hierarchical constraint networks

In order to incorporate constraint propagation in STEM cells, all instance variables of cell classes and instances are initialized to appropriate variable objects on instantiation and all access methods of instance variables are modified accordingly. Constraint creation and violation handling are also modified for STEM, and a simple constraint editor is added to improve the user interface.

# 5.1. Hierarchical Constraint Propagation

Constraint networks in STEM are organized around the design hierarchy to take advantage of STEM's power of abstraction. The dual declaration of instance variables in STEM forms the basis of hierarchical constraint networks. The values assigned to variables of a cell class represent the characteristics of the internal structure of the cell. The constraints on these variables represent conditions imposed by designers and the cell's internal structure on the corresponding characteristics of the cell. On the other hand, constraints on

variables of the cell instances represent conditions on the cell imposed by the environments in which these cell instances are used.

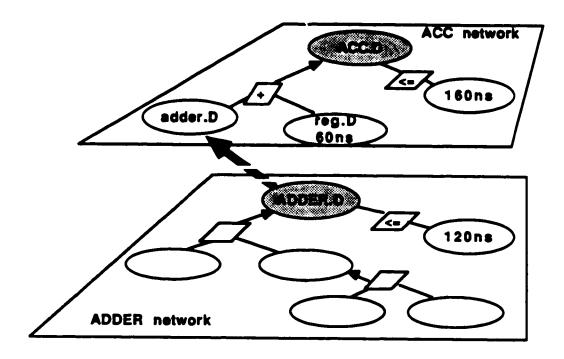

For example (Fig. 5.2) when a designer first designs an eight-bit ADDER, a delay constraint of "120ns or less" may be specified on the appropriate delay variable of the cell class. As the internal structure of the ADDER is designed, constraint violation is triggered if a delay value greater than 120ns is propagated to this delay variable. The delay constraint at the class level therefore constrains the internal design of this cell. Subsequently, an instance of the ADDER cell may be used in an ACCUMULATOR cell, built by cascading an 8-bit REGISTER to an ADDER, which has a overall delay constraint of "160ns or less". From the interconnects of the ADDER instance, a constraint network involving the delay variable of the ADDER instance is instantiated. If the characteristic delay of the REGISTER instance is 60ns and that of the ADDER instance is 110ns (after adjustment for loading), then a constraint violation is triggered.

There are therefore two levels of constraint networks for a cell: the internal and external constraint networks (Fig 5.1). These correspond to the internal and external views of a cell. Internal constraint networks of a cell involve variables of the cell class, and represent conditions that the cell's internal structure must satisfy. The external constraint networks of a cell generally involve variables of cell instances, and represent (indirectly) conditions which the instances must satisfy to be used in their respective environments. Whenever design characteristics become available in a cell class, they are checked with internal constraint networks of the cell and then propagated to the instances and their corresponding external constraint networks. This updates characteristics of larger designs and triggers further constraint propagation. Hierarchical con-

Figure 5.2 Example of a hierarchical constraint network

straint propagation reduces the amount of computation since internal constraint networks are propagated only once even though there may be a large number of cell instances. This takes advantage of the hierarchical structures of IC designs in STEM.

To implement this hierarchical constraint propagation, the concept of an implicit constraint is introduced. An implicit constraint is a procedural implementation of a constraint, or a "hard coded" constraint. For the purpose of hierarchical constraint propagation, implicit constraints are embedded in the dual variables of cell classes and cell instances. These variables respond to propagation messages as if they were constraint objects. This is implemented in a subclass of Variable named "ImplicitConstraintVariable". Two subclasses of ImplicitConstraintVariable are defined for use as instance variables of STEM objects.

Instances of class "InstanceInstVar" are used for instance variables of cell instances, and those of the class "ClassInstVar" are used for instance variables of cell classes. In addition, a new agenda named #implicitConstraints is added to schedule these variable-constraints for hierarchical constraint propagation. The next two sections describe implicit constraint variables and the scheduling of their propagation.

### 5.1.1. Implicit Constraint Variables

A constraint can be made implicit if the links between the constraint and its argument variables are sufficiently well defined that these links can be proceduralized. Due to the dual declaration of instance variables in STEM cells, an instance of "InstanceInstVar" is an implicit constraint on its corresponding instance of "ClassInstVar"; and an instance of "ClassInstVar" is an implicit constraint on all of its corresponding instances of "InstanceInstVar". These variable-constraints play the roles of both variable and constraint, by being the descendents of "Variable" and responding to propagation messages like "isSatisfied" and "propagateVariable:" that constraint objects respond to.

Whenever a value assignment is made to an instance of "InstanceInstVar" or "ClassInstVar", the variable object sends the message "propagateVariable:" to all of its explicit constraints (i.e., constraint objects in its list of constraints), as well as all of its implicit constraints (as returned by the method "implicitConstraints"). All visited constraints, including the implicit constraints, are then sent the message "isSatisfied" to check for constraint violation. Descendents of "ClassInstVar" and "InstanceInstVar" may or may not propagate to their implicit constraints. Two categories of descendents of these variables can be identified: parameters and properties.

For parameters in a cell, the instance variables in the cell class characterize the range of the parameter values that can be handled by the cell. The corresponding instance variables in the cell instances specify the actual parameter values in each use of the cell. Whenever a parameter variable in a cell instance is assigned a new value, it checks with its corresponding variable in the cell class that the value is valid for that parameter of this cell. On the other hand, whenever a parameter variable in a cell class is assigned a new range, it checks with all of its corresponding parameter values in the cell instances that these values satisfy the new range for this parameter. Except for default values of parameters that may be propagated from class parameter variables to instance parameter variables, no constraint propagation is performed between corresponding ::a \*meter variables.