Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

You hie Aphin reference

Outher Notes reference

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

### UNIVERSITY OF ALBERTA

Routing in Blocking and Non-Blocking Multi-Stage Networks for Parallel Systems

BY

Chin-Hung Lam

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

DEPARTMENT OF COMPUTING SCIENCE

Edmonton, Alberta Spring 1995

National Library of Canada

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your ten. Notice reference

Cloud in Notice reterence

THE AUTHOR HAS GRANTED AN IRREVOCABLE NON-EXCLUSIVE LICENCE ALLOWING THE NATIONAL LIBRARY OF CANADA TO REPRODUCE, LOAN, DISTRIBUTE OR SELL COPIES OF HIS/HER THESIS BY ANY MEANS AND IN ANY FORM OR FORMAT, MAKING THIS THESIS AVAILABLE TO INTERESTED PERSONS.

L'AUTEUR A ACCORDE UNE LICENCE IRREVOCABLE ET NON EXCLUSIVE PERMETTANT A LA BIBLIOTHEQUE NATIONALE DU CANADA DE REPRODUIRE, PRETER, DISTRIBUER OU VENDRE DES COPIES DE SA THESE DE QUELQUE MANIERE ET SOUS QUELQUE FORME QUE CE SOIT POUR METTRE DES EXEMPLAIRES DE CETTE THESE A LA DISPOSITION DES PERSONNE INTERESSEES.

THE AUTHOR RETAINS OWNERSHIP OF THE COPYRIGHT IN HIS/HER THESIS. NEITHER THE THESIS NOR SUBSTANTIAL EXTRACTS FROM IT MAY BE PRINTED OR OTHERWISE REPRODUCED WITHOUT HIS/HER PERMISSION.

ISBN 0-612-01715-X

L'AUTEUR CONSERVE LA PROPRIETE DU DROIT D'AUTEUR QUI PROTEGE SA THESE. NI LA THESE NI DES EXTRAITS SUBSTANTIELS DE CELLE-CI NE DOIVENT ETRE IMPRIMES OU AUTREMENT REPRODUITS SANS SON AUTORISATION.

### UNIVERSITY OF ALBERTA

#### RELEASE FORM

NAME OF AUTHOR: Chin-Hung Lam

TITLE OF THESIS: Routing in Blocking and Non-Blocking Multi-Stage Networks

for Parallel Systems

DEGREE: Doctor of Philosophy

YEAR THIS DEGREE GRANTED: 1995

Permission is hereby granted to the University of Alberta Library to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly or scientific research purposes only.

The author reserves all other publication and other rights in association with the copyright in the thesis, and except as hereinbefore provided neither the thesis nor any substantial portion thereof may be printed or otherwise reproduced in any material form whatever without the author's prior written permission.

#3A-8915, 112 Street Edmonton, Alberta

T6G 2C5 Canada

Date: Jan 30 1895

"The greatest happiness you can have is knowing that you do not necessarily require happiness."

- William Saroyan

### UNIVERSITY OF ALBERTA

## FACULTY OF GRADUATE STUDIES AND RESEARCH

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies and Research for acceptance, a thesis entitled Routing in Blocking and Non-Blocking Multi-Stage Networks for Parallel Systems submitted by Chin-Hung Lam in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

Ehab Elmallah (Supervisor)

Frank Hwang (External)

Joseph Culberson (Examiner)

Janelle Harms (Examiner)

Werner Joerg (Examiner)

Pawel Gburzynski (Examiner)

Duane Szafron (Chair)

Date: Dec. 14 , 1.594

## **Abstract**

Interconnection networks (INs) are critical components of high performance parallel and distributed systems. Multi-stage INs (MINs) are made of links and switches that are arranged in stages. MINs are attractive because of their superior scalability, regularity, and cost/performance ratio. However, many routing problems, mostly related to multi-path MINs, are still open. We study routing problems on four recursively decomposable networks that are of practical and theoretical interest.

After adding k extra stages to a Generalized Cube Network (GCN),  $2^k$  paths become available to each input/output pair of the resulting network, called the k-GCN. Useful symmetry properties of the k-GCN are shown. Given a traffic matrix and a 1-GCN, we prove that using the 2 alternative paths between any input/output pair with equal probabilities minimizes the average packet delay, under a wide range of practical traffic patterns and some restrictions. A simulation study that verifies our probabilistic analysis is presented.

We next consider the class of Augmented Data Manipulator (ADM) networks. ADM networks can realize many useful permutations but no known algorithm can efficiently identify and route all admissible permutations. By exploiting the regularity of the topology, we devise a deterministic, backtracking algorithm for routing permutations on the ADM network at compile time. The algorithm requires  $O(N^3)$  time in the worst case and its average time complexity is almost linear, as indicated by simulation. An upper bound on the average time complexity is also derived.

High speed multiprocessor systems demand nonblocking networks, but cost considerations typically force the architect to adhere to rearrangeable or blocking MINs.

The notion of a k-nonblocking network is introduced to provide a framework for bridging the gap between blocking and nonblocking networks with a spectrum of new networks. k-nonblockingness conveniently quantifies the power of MINs, especially under unspecified traffic. A systematic scheme for constructing k-nonblocking networks is presented; together with efficient parallel and sequential routing algorithms. When k = N, our construction gives a network cheaper than an existing strictly nonblocking network.

Define the width of a MIN to be the maximum number of 1 ks running between any 2 adjacent stages. We show that all strictly nonblocking MINs of size N must have width > N. The lower bound on the width of wide-sense nonblocking MINs was unknown, except for N=4. By proving that a new network, called the Quadruplet, is wide-sense nonblocking, we conclude that N is a tight lower bound on the width of wide-sense nonblocking MINs. By cascading a sufficient number of any rearrangeable MINs of width N, a wide-sense nonblocking MIN can be obtained. An upper bound on the number of shuffle/exchange stages needed to attain wide-sense nonblockingness is also derived. Finally, a new implication of the notion of universality is shown.

## **Preface**

This dissertation documents pare results obtained during my study in the department of Computing Science. The University of Alberta. Each of Chapters 3 to 6 concentrates on a sub-topic. They are roughly arranged in the order of increasing depth. (Interestingly, the weight of mathematics decreases while the weight of computer science increases in that order.) As these sub-topics are "loosely-coupled." Chapters 3 to 6 can be read in any order, although Chapter 6 refers to the k-nonblocking network concept introduced in Chapter 5. The four sub-topics reveal different facets of a central issue in the study of MINs, namely routing, which is the main theme of this dissertation. The emphasis is on routing problems in multi-path MINs, especially those that allow recursive decomposition. It is hoped that our efforts would help build a unified theory of routing in MINs.

Preliminary versions of Chapters 3, 4 and 5 have appeared in conference proceedings.

# Acknowledgements

I received two research topics, which correspond to Chapters 3 and 4 of this dissertation, from my supervisor Dr. Ehab Elmallah. As members of my supervisory committee, Dr. Joseph Culberson and Dr. Janelle Harms are my major sources of constructive comments at all stages of this research. I am in debt to other members of my examination committee, including Dr. Frank Hwang from AT&T and Prof. Werner Joerg, for their careful reading of drafts of this dissertation. Dr. Anup Basu kindly served on my candidacy examination committee. Dr. Christopher Smyth at the University of Edinburgh reviewed drafts of Chapters 2, 5 and 6 and gave useful suggestions (and I should also thank Prof. Nicholas Pippenger at the University of British Columbia for putting me in contact with Dr. Smyth). Discussions with my fellow graduate students has always been rewarding.

This work is partially supported by NSERC Canada under grant number OGP 36899. The Department of Computing Science at the University of Alberta also financed the author through graduate assistantships.

My stay in Edmonton would not have been an enjoyable one without the company of good friends such as Alice Chan, Ben Wong, and Clement Kwok.

# Contents

| 1 | Intr | roduction                                 | 1  |

|---|------|-------------------------------------------|----|

|   | 1.1  | Why Multi-Stage Interconnection Networks? | 1  |

|   | 1.2  | Architectural Models                      | 3  |

|   | 1.3  | Routing Problems                          | -1 |

|   | 1.4  | Overview of Our Research                  | 5  |

|   | 1.5  | Organization of This Thesis               | 9  |

| 2 | Pre  | liminaries                                | 10 |

|   | 2.1  | Notation and Terminology                  | 10 |

|   | 2.2  | Switch and Network Models                 | 11 |

|   | 2.3  | Classification                            | 13 |

|   |      | 2.3.1 Beneš' Classification               | 13 |

|   |      | 2.3.2 Feng's Classification               | 15 |

|   | 2.4  | Some Existing Networks                    | 17 |

|   |      | 2.4.1 Clos Network                        | 17 |

|   |      | 2.4.2 The Shuffle-Exchange Network        | 18 |

|   |      | 2.4.3 Cube-Type Networks                  | 19 |

|   |      | 2.4.4 Benes' Rearrangeable Network        | 23 |

|   |      | 2.4.5 The Data Manipulator Network        | 24 |

|   | 2.5  | Equivalence of Networks                   | 25 |

|   | 2.6  | Figures of Merits                         | 26 |

|   | ·) 7 | Complexity of Permutation Routing         | 27 |

| 3 | Rou | iting o | n Extra Stage Networks                 | 32 |

|---|-----|---------|----------------------------------------|----|

|   | 3.1 | Introd  | uction                                 | 32 |

|   | 3.2 | Switch  | Model and Notation                     | 35 |

|   | 3.3 | Prope   | rties of the k-GCN                     | 36 |

|   | 3.4 | Load    | Balancing on the 1-GCN                 | 39 |

|   |     | 3.4.1   | Basic Concepts and Definitions         | 40 |

|   |     | 3.4.2   | Probability Assignment                 | 41 |

|   | 3.5 | Simula  | ation Study                            | 44 |

|   |     | 3.5.1   | Experiment and Simulator Design        | 44 |

|   |     | 3.5.2   | Results and Interpretations            | 45 |

|   | 3.6 | Conclu  | uding Remarks                          | 50 |

| 4 | Per | mutati  | ion Routing on the ADM Network         | 54 |

|   | 4.1 | Introd  | luction                                | 54 |

|   | 4.2 | The N   | Tetwork, the Notation, and the Problem | 56 |

|   | 4.3 | Routin  | ng on the ADM                          | 59 |

|   |     | 4.3.1   | Routing One Connection Request         | 59 |

|   |     | 4.3.2   | Permutation Routing                    | 60 |

|   |     | 4.3.3   | The Routing Algorithm                  | 64 |

|   | 4.4 | Simul   | ation Experiment                       | 67 |

|   |     | 4.4.1   | Program Verification                   | 68 |

|   |     | 4.4.2   | Performance Study                      | 69 |

|   | 4.5 | Appro   | oximate Time Complexity Analysis       | 72 |

|   |     | 4.5.1   | Classification of Permutations         | 72 |

|   |     | 4.5.2   | Cardinality of $W_t^s$                 | 74 |

|   |     | 4.5.3   | Number of Nodes Searched               | 77 |

|   |     | 4.5.4   | An Upper Bound                         | 79 |

|   |     | 4.5.5   | Worst-Case Performance                 | 81 |

|   | 4.6 | Concl   | usion                                  | 81 |

| 5 | On    | a Class of k-Nonblocking Networks                 | 84  |

|---|-------|---------------------------------------------------|-----|

|   | 5.1   | Introduction                                      | 85  |

|   | 5.2   | k-Nonblockingness                                 | 86  |

|   |       | 5.2.1 Definition                                  | 86  |

|   |       | 5.2.2 k-Nonblockingness of Some Existing Networks | 87  |

|   | 5.3   | Constructing a k-Nonblocking Network              | 89  |

|   |       | 5.3.1 Interpretation and Application              | 93  |

|   |       | 5.3.2 A Special Case: N-Nonblocking               | 94  |

|   | 5.4   | Routing Algorithms                                | 95  |

|   |       | 5.4.1 MLP                                         | 95  |

|   |       | 5.4.2 FirstFit                                    | 96  |

|   | 5.5   | Removing Dummy Switches                           | 98  |

|   | 5.6   | Conclusion                                        | 99  |

| 6 | Wie   | dth N Wide-Sense Nonblocking Networks             | 101 |

|   | 6.1   | Introduction                                      | 101 |

|   | 6.2   | Width of Strictly Nonblocking MINs                | 105 |

|   | 6.3   | Definitions and Notations                         | 105 |

|   | 6.4   | Basic Properties of the Q Network                 | 107 |

|   | 6.5   | The $Q$ Network is Wide-Sense Nonblocking         | 111 |

|   | 6.6   | More About $Q_N \dots \dots \dots \dots \dots$    | 112 |

|   | 6.7   | Transforming $Q_N$ into a Proper MIN $\ldots$     | 114 |

|   | 6.8   | Advanced Results                                  | 118 |

|   | 6.9   | Concluding Remarks                                | 120 |

| 7 | Cor   | nclusion                                          | 122 |

| В | iblio | graphy                                            | 124 |

| A | Per   | mutation Routing Complexity: 3-stage INs          | 135 |

| В            | Row Data from the Simulation of the 1-GCN                   | 138 |

|--------------|-------------------------------------------------------------|-----|

| $\mathbf{C}$ | Maple Source Code for Computing $\widetilde{\mathcal{S}_N}$ | 145 |

# List of Figures

| 1.1  | A simple classification of INs                                            | 2          |

|------|---------------------------------------------------------------------------|------------|

| 1.2  | Two multiprocessor configurations: a) PE-PE, b) P-M                       | 4          |

| 1.3  | Three key elements in the study of INs                                    | 5          |

| 1.4  | Scopes of the 4 research sub-topics                                       | 6          |

| 2.1  | States of a 2x2 crossbar switch                                           | 12         |

| 2.2  | Graph models for MINs; a) switches as nodes, b) links as nodes            | 12         |

| 2.3  | Beneš' classification scheme.                                             | 15         |

| 2.4  | Two alternative paths in a 3x3 crossbar network                           | 15         |

| 2.5  | Topologies of INs under Feng's classification                             | 17         |

| 2.6  | Three-stage Clos network $v(m,n,r)$                                       | 17         |

| 2.7  | A shuffle-exchange network of size 8 (a) and its graph model (b)          | 19         |

| 2.8  | An Omega network of size 8                                                | 20         |

| 2.9  | The baseline network (b) and its recursive model (a)                      | 21         |

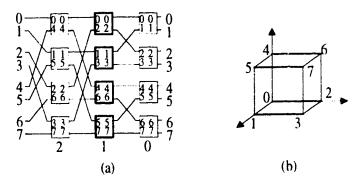

| 2.10 | A GCN of size 8 (a) and its corresponding 3-cube (b)                      | 22         |

| 2.11 | A size 8 GCN serving a request from input 2 to output 4                   | 23         |

| 2.12 | An ESC network of size 8                                                  | 23         |

| 2.13 | Beneš' rearrangeable network (b) and its recursive model (a)              | 24         |

| 2.14 | An 8-node PM2I network (a) and the corresponding DM network (b).          | <b>2</b> 5 |

| 2.15 | Special 2x2 switch allowing only one connection                           | 28         |

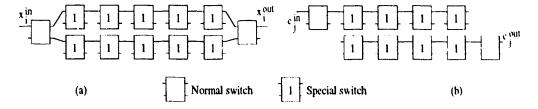

| 2.16 | Constructing the MIN for (a) the variables, (b) the clauses               | 29         |

| 2.17 | An example for $c_i = \overline{x_1} + x_2 + x_n + \dots + \dots + \dots$ | 30         |

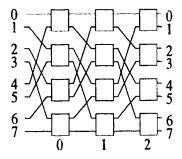

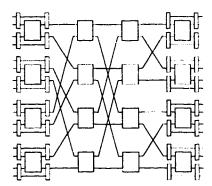

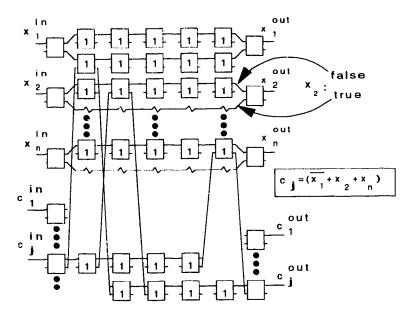

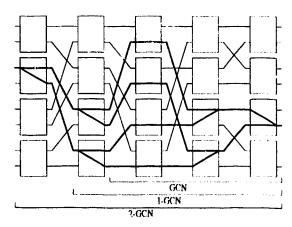

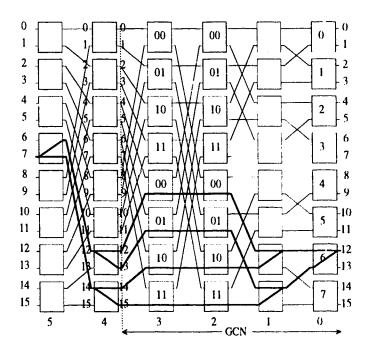

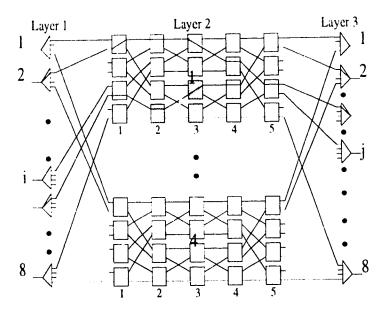

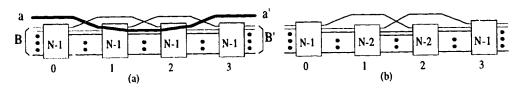

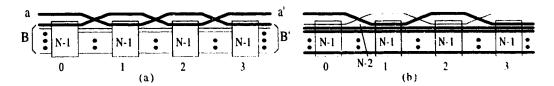

| 3.1  | 1-GCN and 2-GCN of size 8                                                   | 33 |

|------|-----------------------------------------------------------------------------|----|

| 3.2  | 2x2 switch with unlimited buffer queues                                     | 35 |

| 3.3  | Partitioning switches in a 2-GCN of size 16 into 4 classes                  | 37 |

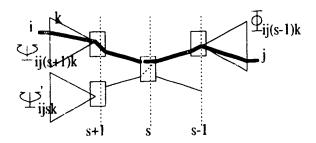

| 3.4  | The scenario in which a conflict may occur                                  | 42 |

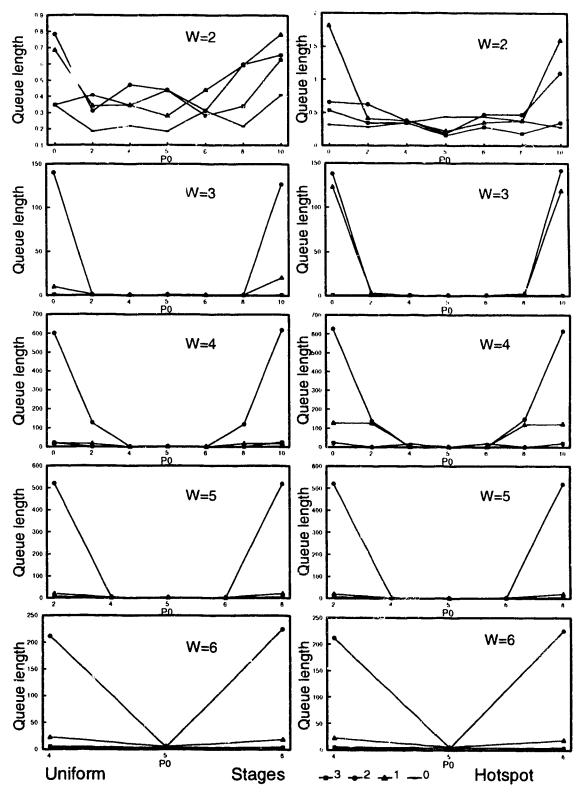

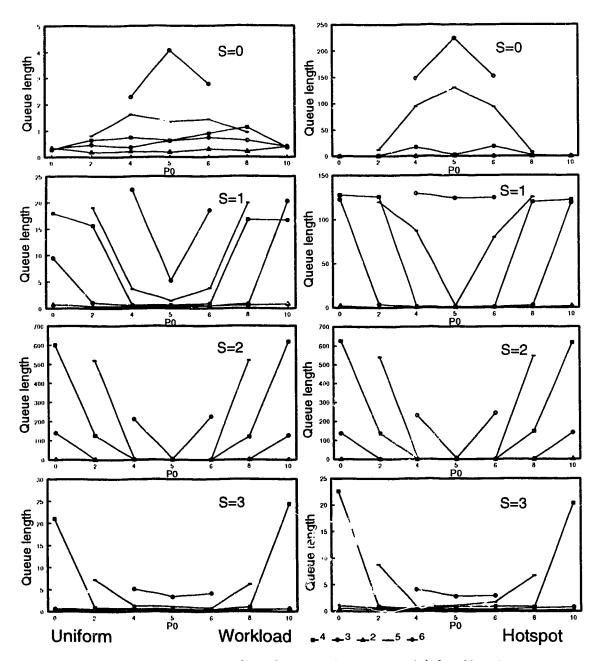

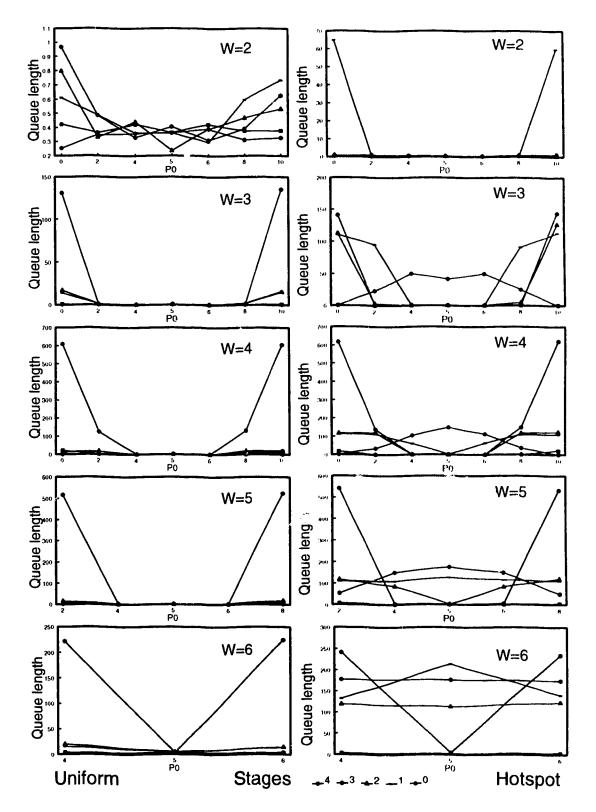

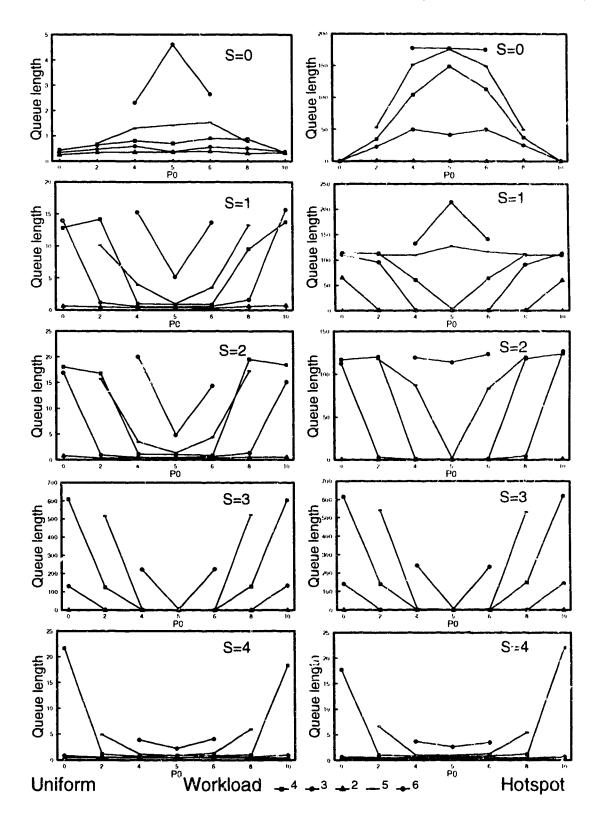

| 3.5  | Effect of workload $(w)$ on queue lengths for $N=8$                         | 47 |

| 3.6  | Queue lengths at various stages (s) for $N = 8. \dots \dots \dots$          | 48 |

| 3.7  | Effect of workload $(w)$ on queue lengths for $N = 16$                      | 49 |

| 3.8  | Queue lengths at various stages (s) for $N = 16$                            | 51 |

| 3.9  | Screen dump of simulation run that contains a hotspot at output 10.         | 52 |

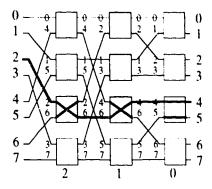

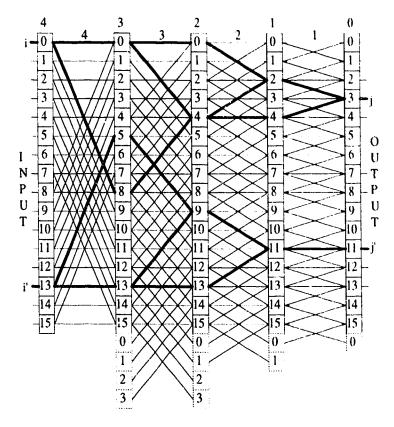

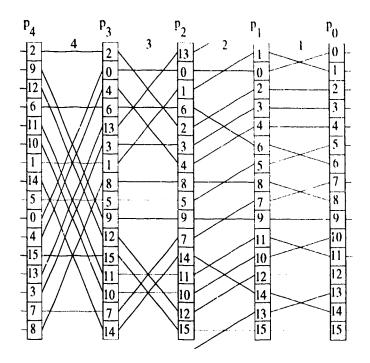

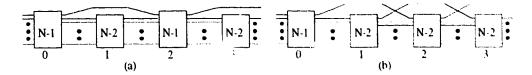

| 4.1  | An ADM of size 16 (redundant links in stage 4 removed for simplicity).      | 57 |

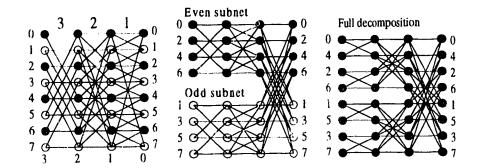

| 4.2  | A size 8 ADM split into even and odd sub-networks                           | 58 |

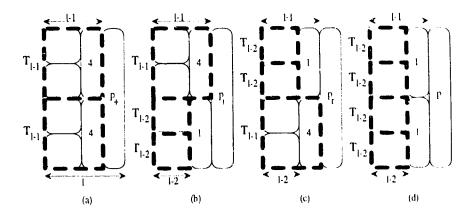

| 4.3  | a) A component, b) 2 components, c) $p$ , d) $p_+$ , e) $p_\tau$ , f) $p_i$ | 58 |

| 4.4  | Intermediate permutations for a given admissible permutation                | 59 |

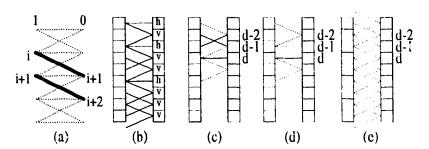

| 4.5  | a) Case $p_+$ in $A_1$ . b-e) Various scenarios in $A_1$                    | 61 |

| 4.6  | Worst case search tree                                                      | 66 |

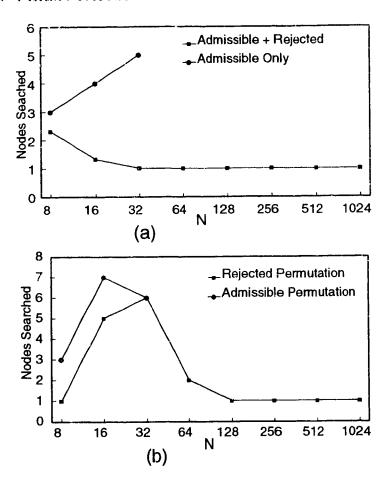

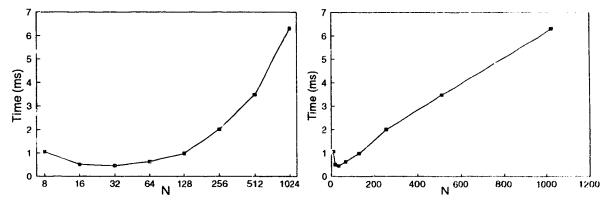

| 4.7  | Average (a) and maximum (b) number of nodes searched per permu-             |    |

|      | tation                                                                      | 70 |

| 4.8  | Average time to process each permutation; logarithmic and linear scale.     | 71 |

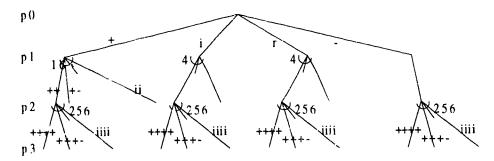

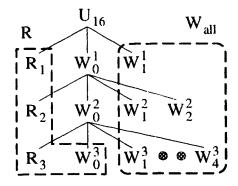

| 4.9  | A classification of permutations for $N = 16. \dots \dots \dots$            | 74 |

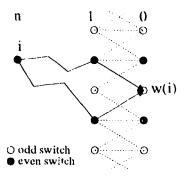

| 4.10 | A v-case switch in stage 0                                                  | 75 |

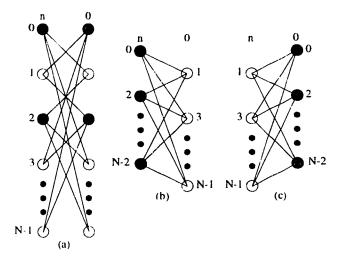

| 4.11 | Bipartite graphs showing stage 0 and $n$                                    | 76 |

| 4.12 | Explanation for the terms in $T_l$                                          | 78 |

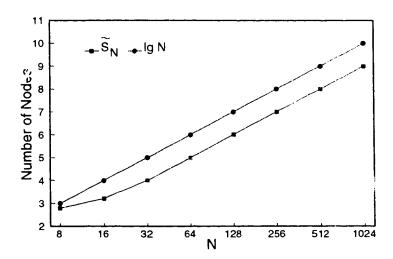

| 4.13 | $\widetilde{\mathcal{S}_N}$ and $\lg N$ versus $N$                          | 80 |

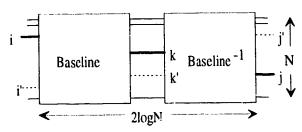

| 5.1  | Beneš' network. Existing request: $(i,j)$ . New request: $(i',j')$          | 87 |

| 5.2  | The third request (6,1) is blocked in Beneš network                         | 88 |

| 5.3  | Highlighted switches in $C(4,8)$ are unusable by any path from $i$ to $j$ . | 91 |

| 5.4  | Constructing an exactly 3-nonblocking network of size $N$                   | 94 |

| 5.5  | Three bit encoding of the state of a switch                                 | 97 |

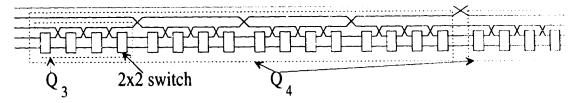

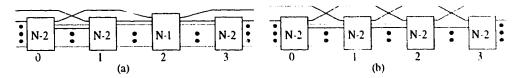

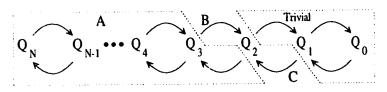

| 6.1  | $Q_N$                                                                          | 106 |

|------|--------------------------------------------------------------------------------|-----|

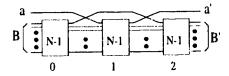

| 6.2  | The first quarter of a $Q_5$                                                   | 106 |

| 6.3  | a) Terminal labeling of a $Q_N$ , b) Busy path $(a, a')$ removed from graph.   | 107 |

| 6.4  | Network graphs resulting from the 2 ways to realize $(a, b')$                  | 108 |

| 6.5  | Network graphs resulting from the 2 ways to realize $(b,b')$                   | 108 |

| 6.6  | a) BPPs $(a, b')$ and $(b, a')$ . b) $N-2$ $(b, b')$ requests using their LPPs | 110 |

| 6.7  | State transition diagram for $Q_N$                                             | 111 |

| 6.8  | After removing 1 stage from $Q_N$                                              |     |

| 6.9  | Beneš' size 4 wide-sense nonblocking network                                   | 113 |

| 6.10 | Using dummy switches to eliminate links that bypass stages in $Q_4$            | 115 |

| 6.11 | The twist in a) involves 2 switches while b) involves 4. $i$ and $j$ are       |     |

|      | integers, where $i \ge 1$ and $0 < j < m$                                      | 116 |

| 6.12 | Elimination of multiple connections using 2 types of switches                  |     |

| 6.13 | Elimination of multiple connections using 1 type of switches                   | 117 |

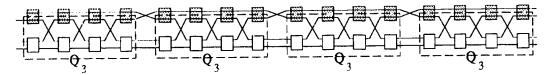

| 6.14 | An extended Clos network                                                       | 119 |

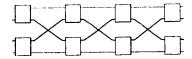

|      | SE as a building block for width $N$ wide-sense nonblocking MINs               |     |

| A.1  | Possible cases for a request $(i, j)$                                          | 136 |

# List of Tables

| 4.1         | Number of ADM-admissible permutations: Leland's versus our results.    | 69  |

|-------------|------------------------------------------------------------------------|-----|

| 4.2         | Numerical results produced by Maple V                                  | 79  |

| 4.3         | Comparison of the ADM and $\Omega$ networks                            | 82  |

| 4.4         | $N!$ , $(N!)^{0.694}$ , and $(N!)^{0.5}$ versus $N$                    | 82  |

| 5.1         | $m$ verses $k_{	ext{max}}$                                             | 93  |

| 5.2         | Minimum depth necessary to be k-nonblocking                            | 100 |

| 6.1         | Minimum depth required for width $N$ MINs of various capabilities      | 102 |

| 6.2         | Some results in the study of iterated MINs                             | 103 |

| 6.3         | Priority assignment for the 4 types of requests                        | 109 |

| 6.4         | Switch(es) shared by any 2 requests                                    | 109 |

| 7.1         | An overview of new results (marked by *) in Chapters 5 and 6           | 123 |

| <b>B</b> .1 | Uniform traffic: average queue length (over 4 runs) at each stage      | 139 |

| <b>B.2</b>  | Uniform traffic and $N=8$ : average queue length, variance, and confi- |     |

|             | dence interval                                                         | 140 |

| <b>B.3</b>  | Uniform traffic and $N=16$ : average queue length, variance, and con-  |     |

|             | fidence interval                                                       | 141 |

| <b>B.4</b>  | Hotspot traffic: average queue length (over 4 runs) at each stage      | 142 |

| <b>B.</b> 5 | Hotspot traffic and $N=8$ : average queue length, variance, and confi- |     |

|             | dence interval                                                         | 143 |

| <b>B.6</b> | Hotspot traffic and $N = 16$ : average queue length, variance, and con- |     |

|------------|-------------------------------------------------------------------------|-----|

|            | fidence interval                                                        | 144 |

# Chapter 1

## Introduction

This chapter first gives motivations for the study of multi-stage interconnection networks (MINs) in § 1.1. The role of a MIN in a multiprocessor system is examined in § 1.2. In § 1.3, we highlight the significance of a central issue: routing in MINs, especially multi-path MINs that are recursively decomposable. An overview of our research is given in § 1.4. The organization of this dissertation is summarized in § 1.5.

### 1.1 Why Multi-Stage Interconnection Networks?

Efficient transfer of data between communicating parties is a major challenge shared by telecommunication and multiprocessor systems [46, 48]. The design of effective interconnection networks (INs) proves to be a critical part of such high performance systems (e.g., [88]). Although we will concentrate on INs for multiprocessor systems, note that many INs serve telecommunication and multiprocessor systems equally well. For instance, the shared-bus has been widely used on local area networks as well as multiprocessor systems. The star topology is another example. With the advent of distributed computing, the border between communication and computation has become blurred. In fact, the study of INs is rooted in research in telephony [10, 24].

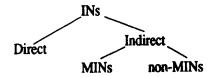

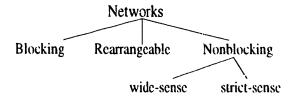

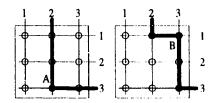

We now examine the role of multi-stage INs (MINs) using the simple classification tree in Figure 1.1. In *direct* networks (a.k.a. static [41] or point-to-point networks),

communicating parties are directly connected by links. Examples include the star and the hypercube network [26, 41, 51] (comparative simulation studies can be found in [104, 105]). Special graphs [47] and groups [35] have been proposed as directed networks. In indirect networks (a.k.a. dynamic networks [41]), switches are employed such that paths between communicating parties involve alternating links and switches.

Figure 1.1: A simple classification of INs.

If the switches in an indirect network can be arranged into stages such that switches in one stage are only connected to switches in subsequent stages, then it is a MIN. Examples are given in Chapter 2. Switches in indirect networks that are not MINs (denoted non-MINs) cannot be arranged into stages. Existence of feedback loops (e.g., [74]) and mixing of traffic directions (e.g., [49]) are typical features in non-MINs. Simplicity, or ease of analysis, makes MINs more popular than non-MINs in the literature. Other attractive virtues of MINs include:

Scalability: It is relatively easy to expand an existing MIN to accommodate a heavier workload (e.g., a larger number of terminals). In the worst case, the expansion process requires redesigning the entire backbone network or its supporting software component. In this regard, MINs usually exhibit enough structural symmetry to make the expansion task relatively simple.

Modularity/regularity: MINs can be implemented as separate modules in the system.

They can be upgraded/replaced/repaired independently of other components.

Cost/performance ratio: The cost of the switches in MINs is justified by the large increase in power (measured by, say, connection power<sup>1</sup> or bandwidth).

<sup>&</sup>lt;sup>1</sup>The term connection power generally means the capability of satisfying arbitrary 1-to-1 requests.

MINs have been used in a number of multiprocessor systems. For instance, the butterfly network is used in the BBN system [107]. A number of multi-stage cube networks have been used in or proposed for real systems [114]. It is expected that MINs will remain a critical component of high performance multiprocessor systems, especially those that operating in SIMD (single-instruction-stream-multiple-data-stream) mode. MINs have been proposed for high speed telecommunication systems, such as integrated services digital networks (ISDNs). See [4, 121] for good surveys. MINs are also suitable for ATM (Asynchronous Transfer Mode) switching [91].

Some MINs have corresponding direct networks. For instance, the generalized cube network (GCN) [112, Ch. 5] and the data manipulator network [40] are multistage versions of the direct networks hypercube and plus-minus-2-i (PM2I) [41], respectively. For a brief introduction to the study of MINs see [6, 113].

#### 1.2 Architectural Models

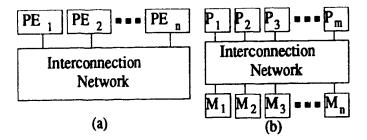

This section examines the role of an IN as the primary communication infrastructure in multiprocessor systems. Two typical configurations are considered [18, 56, 112]:

Processor-to-memory (P-M): A number of processors are connected to a number of memory units via the IN (Figure 1.2b). Since a party on either side of the IN never communicates with other parties on the same side, these INs are also called 2-sided networks [20]. If a uni-directional IN (e.g., an IN operating in packet-switching mode) is used, then typically 2 identical INs are employed to facilitate duplex communication.

Processing-element-to-processing-element (PE-PE): A number of processing elements (PEs) are connected by an IN (Figure 1.2a). Each PE consists of a processor and local memory. Since every party can communicate with any other party, these INs are also called 1-sided networks [20, 89] and they are understood to be bi-directional. However, a uni-directional 2-sided IN can serve as a 1-sided network if the ith input and the ith output are both connected to the ith PE.

Figure 1.2: Two multiprocessor configurations: a) PE-PE, b) P-M.

See [112, Ch. 2] for more details and examples. Hybrid configurations (e.g., the partitionable SIMD/MIMD<sup>2</sup> system called PASM in [114]) evolved from the 2 basic configurations exist but they will not be covered. Some multiprocessor systems have a dedicated IN for cache coherency [83].

## 1.3 Routing Problems

In this section, motivations for the study of routing problems in MINs are presented. We believe that in the study of MINs, a long term goal shared by both computer scientists and engineers is the complete resolution of the relationship between 3 key elements: network, routing, and traffic. By traffic we broadly mean a permutation to be satisfied, or a set of 1-to-1 connections to be made (includes broadcasting), or a group of packets to be transmitted that satisfy some distribution. Loosely speaking, a routing algorithm controls the underlying hardware, using full knowledge of the network topology and current state, so that either the given traffic requirement is satisfied, or the traffic requirement is rejected as not satisfiable. Figure 1.3 depicts the central position of routing. A unified theory of the 3 key elements should be able to solve typical research problems such as:

- Given network A, what routing algorithm can satisfy traffic requirement C?

- Given network A and routing algorithm B, what kind of traffic can be handled?

<sup>&</sup>lt;sup>2</sup>MIMD means Multiple-Instruction-stream-Multiple-Data-stream.

Figure 1.3: Three key elements in the study of INs.

- Given traffic requirement C, what network and routing algorithms are needed?

- Given a new network A, what kind of traffic can be handled and what routing algorithms are applicable?

Now, the central role of routing in the unified theory becomes clear. Note that some routing problems are intractable (e.g., permutation routing on arbitrary MINs is an NP-complete problem as shown in § 2.7). We should identify such cases, and accordingly focus more on tractable routing problems that arise in practice. To construct such a unified theory, we not only need to study the routing algorithms for individual networks and the kind of traffic they can handle, we also need to generalize existing network models and routing algorithms to cover a larger class of networks. These 2 directions can be pursued simultaneously. Chapter 3 and 4 of this dissertation study routing problems in individual networks while Chapter 5 and 6 attempt to generalize network models and routing algorithms. Unique-path MINs have been studied extensively in the literature; so this dissertation focuses on multivalia MINs, especially those that allow recursive decomposition. Therefore, although our 4 sub-topics seem to be loosely-coupled and have different depths, routing on recursively decomposable multi-path MINs forms the backbone of this dissertation.

The importance of routing has been recognized in the literature. [75] contains a comprehensive survey of the subject and a substantial bibliography.

### 1.4 Overview of Our Research

Based on the above discussions, our research goal is to design, study, and generalize routing algorithms such that eventually a unified theory of routing can be derived.

This thesis emphasizes multi-path MINs that are recursively decomposable.

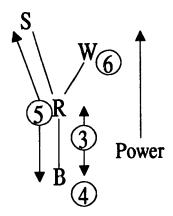

Although Beneš' classification [13] will not be discussed in detail until Chapter it is convenient to illustrate the broad coverage of our work using his scheme. In order of increasing connection power, INs (of N inputs/outputs) are classified into:

Blocking (B) networks: unable to realize all N! permutations,

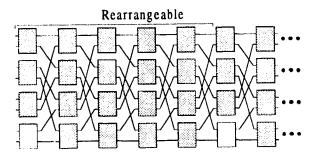

Rearrangeable (R) networks: able to realize all N! permutations,

Wide-sense nonblocking (W) networks: can realize any request/release sequence if path-selection is guided by a rule, and

Strict-sense nonblocking (S) networks: can realize any request/release sequence even when paths are randomly selected.

Figure 1.4 depicts the relationship between them. The coverage of the 4 sub-topics are labeled by its corresponding chapter numbers in the figure.

Figure 1.4: Scopes of the 4 research sub-topics.

Now, we briefly review each of the sub-topics:

Routing on Extra-Stage Networks (Chapter 3): This work deals with MINs with capabilities ranging from blocking to rearrangeable. Our study is motivated by a more general problem: given a MIN that provides multiple paths between its input and output terminals, and a certain traffic distribution, what packet routing strategy minimizes the average delay of the network? We focus on traffic

patterns that can be described by a matrix L, in which element  $l_{ij}$  represents the probability of generating a packet from input i to output j in a time unit. A specific network, the 1-GCN, formed by adding an extra stage to the input side of a Generalized Cube Network (GCN) [112], is considered. The 1-GCN provides 2 alternative paths between every input/output pair. By identifying some symmetry properties of the 1-GCN, we show that the average network delay is minimized when the 2 alternative paths are used with equal probabilities, regardless of the traffic patterns, under some restrictions. This argument is verified by simulation. The symmetry properties we identified generalize to k-GCNs, in which k extra stages are added to the input side of a GCN.

Permutation Routing on the ADM Network (Chapter 4): This work concentrates on a blocking. In called the Augmented Data Manipulator (ADM) Network [112, Ch. 6]. It known algorithm can efficiently route permutations through the ADM [76]. The set of permutations admissible by the ADM have not been characterized. We devise a deterministic, backtracking algorithm for routing admissible permutations and rejecting inadmissible permutations. Although in the worst case, the algorithm takes  $O(N^3)$ , in most cases it apparently takes linear time. Simulation is used to demonstrate its good performance. An upper bound on its average time complexity is also derived. The algorithm is suitable for compile-time routing on SIMD machines.

On a Class of k-nonblocking Networks (Chapter 5): This work basically involves MINs with capabilities ranging from blocking, rearrangeable, to strict-sense nonblocking. Although nonblocking networks can satisfy the communication demand in high performance systems, their high complexity typically forces the architect to adhere to rearrangeable or even blocking networks. We introduce the notion of k-nonblocking networks as one that never blocks an incoming request whenever there are < k existing connections in an N input network, where  $1 \le k \le N$ . On the theoretical side, the general concept of k-nonblockingness

bridges the complexity gap between blocking and nonblocking networks by a spectrum of new networks. It also provides a convenient way to quantify the connection power of a network under unspecified traffic. On the practical side, we present a systematic scheme for constructing k-nonblocking networks in the strict sense. Efficient parallel and sequential algorithms for the proposed networks are given. For the case k = N, the constructed network is cheaper than an existing nonblocking network [79] that is, like ours, based on Beneš rearrangeable network [12, 11].

- Wide-Sense Nonblocking Networks Made of Square Switches (Chapter 6): This work focuses on the class of wide-sense nonblocking networks. The following 2 related open problems have motivated this research:

- 1. The width of a MIN is the maximum number of links running between any 2 adjacent stages. It can be derived from [14] that the width of any strict-sense nonblocking MIN of N inputs/outputs must be > N. In contrast, the width of any rearrangeable MIN (e.g., Beneš' rearrangeable network [12, 11]) must be ≥ N. Although Beneš has given a 4x4 wide-sense non-blocking MIN of width 4 in [14], it is not known whether wide-sense non-blocking MINs can generally have width N because Beneš' network does not generalize to N > 4.

- 2. Empirically, increasing the number of stages in a MIN increases its connection power (mentioned briefly in [61]). For instance, a single stage shull exchange (SE) network [117] is very limited in connection power. But when there are log<sub>2</sub> N SE stages, the resulting Omega (Ω) network [73] supports many useful permutations although it is still a blocking network. As the number of SE stages reaches 3 log<sub>2</sub> N=4, the network becomes rearrangeable [80]. It is natural to ask what is the most powerful network obtainable by merely adding more stages to a MIN. The previous paragraph eliminates the possibility of obtaining a strict-sense nonblocking

MIN. The case for wide-sense nonblocking MINs is still open.

To declare a network as wide-sense nonblocking one must give, or at least prove the existence of, a routing algorithm that satisfies any request/release sequence. This is in general very difficult. We first propose a width N, recursive network called the Quadruple (Q). Then we prove that it is wide-sense nonblocking by giving a routing algorithm. Afterwards, we transform the Q network, which is not a proper MIN, into a proper one. The open problems are thus solved. A fundamental difference between wide- and strict-sense nonblocking MINs that is not obvious from their definitions is identified: the former can have width N while the latter must have width N. We also show that by cascading a finite number of any rearrangeable MINs of width N, a wide-sense nonblocking MIN can be obtained. An iterated [43] MIN uses a single permutation repeatedly to connect all adjacent stages. We prove that the set of permutations out of which rearrangeable iterated MINs can be built is identical to the set of permutations out of which wide-sense nonblocking iterated MINs can be built.

## 1.5 Organization of This Thesis

Chapter 1 of this dissertation introduces the reader to the general area of MINs and routing problems. The emphasis is on multi-path MINs that are recursively decomposable. Chapter 2 provides some background information on MINs. We cover notations, terminologies, models, classification schemes, outstanding results, and complexity of permutation routing on arbitrary MINs. Material specific to each sub-topic is delayed to their respective chapters. Each of Chapter 3 to 6 discusses a particular sub-topic as mentioned before. Although they are roughly sorted by increasing depth, and Chapter 6 uses the k-nonblocking concept introduced in Chapter 5, these 4 chapters can be read in any order. Each chapter includes its own concluding remarks. Chapter 7 summarizes this dissertation and discusses some future directions.

# Chapter 2

## **Preliminaries**

This chapter presents some background information required throughout the thesis. Some notation and terminology are introduced in § 2.1, followed by a description of common switch and network models in § 2.2. Two well known network classification schemes are reviewed in § 2.3. Important results on five representative networks in the literature are highlighted in § 2.4. In § 2.5, we examine the problem of equivalence of networks. § 2.6 reviews the major factors to be considered in the design of MINs. In § 2.7, we show that the general problem of permutation routing on an arbitrary MIN is NP-complete.

## 2.1 Notation and Terminology

MINs are generally modeled by graphs or digraphs (directed graphs) so we will use standard graph and network terminology (see for example [21]). An  $N_i$ -by- $N_o$  (denote  $N_i \times N_o$ ) MIN has  $N_i$  inputs and  $N_o$  outputs. When  $N_i = N_o = N$ , we say the network has size N. A MIN is made of switches and links arranged into stages, as in Figure 2.8. All MINs can be modeled by directed acyclic graphs (DAGs). For ease of analysis, most MINs proposed are layered, in which switches in one stage are only connected to those in the next stage [67]. All MINs considered in this thesis are layered. Furthermore, most MINs have at most 1 link between any 2 switches in 2 adjacent stages. If there

are multiple physical links between some pairs of switches, it is called a multi-network [7]. A dilated network provides multiple links either logically or physically [118].

A path is an alternating sequence of links and switches that connect an input and an output. An input (output) is *idle* if it is not used in any existing connections. A path is *idle* if it can be allocated to an incoming request without disturbing existing connections, otherwise, it is *busy*. A MIN is *idle* if all the paths are idle.

The depth [39] is the maximum number of switches in any path in a non-layered MIN, or simply the number of stages in a layered MIN. The cross-section width, or width [8] for short, between 2 stages is the number of links running between them. The width of a MIN is the maximum width between any 2 stages. The hardware cost, or just cost, of a MIN is usually measured by the total number of switches, or more broadly, the total number of cross-points [10] if the switches are not uniform. By definition, an axb crossbar switch has ab cross-points.

We denote  $\log_2 N$  by  $\lg N$ .  $n = \lg N$  is the depth of size N cube-type networks (§ 2.4.3). The binary representation of an r-bit number b is  $(b_{r+1} \dots b_1 b_0)$ . Concerning traffic patterns, this thesis deals with 1-to-1 requests only and ignores broadcasting and multicasting. Moreover, all incoming requests are assumed to be valid; that is, both the input and output in a request are currently idle.

Many applications on SIMD machines involve alignment of data and processors. A set of simultaneous connections between memories and processors, corresponding to a 1-to-1 mapping of inputs to outputs, is called a permutation. Permutation networks are specifically designed to handle this kind of traffic [57, 60, 78].

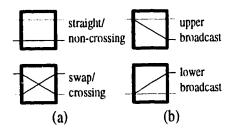

### 2.2 Switch and Network Models

MINs are sometimes designed with 2x2 crossbar switches as basic building blocks. Each switch provides 2 states for 1-to-1 connections (Figure 2.1a) and 2 states for 1-to-2 connections (Figure 2.1b). The *straight* (a.k.a. *non-crossing*) state is usually the initial, or the "inactive," state of a switch in permutation networks. The *swap*

(a.k.a. crossing or exchange) state is typically the "active" state. The upper- and lower-broadcast states are used in broadcast operations. (One variant of this model provides an additional state for 1-to-1 connections [128].)

Figure 2.1: States of a 2x2 crossbar switch.

The above switch model is suitable for MINs operating in circuit-switching mode. In packet-switching mode, the model should be augmented to account for delays due to buffering and queuing. A number of models have been proposed for this purpose [81]. A typical one is used in Chapter 3. Basic tools for analyzing systems constructed from these models, under a given traffic distribution, include queuing theory [19, 29], petri net, mean value analysis (MVA) and approximate MVA [59, 126].

Two graph-theoretic models are frequently used for studying the topology of MINs. In the first model, nodes correspond to switches while edges correspond to links. Input and output terminals become nodes if they need to be modeled. Figure 2.2a shows the graph-theoretic model of a typical MIN under this scheme. In the second model,

Figure 2.2: Graph models for MINs; a) switches as nodes, b) links as nodes.

a link becomes a node in the graph. Each crossbar switch is modeled by a group

of edges that fully interconnect the nodes, each of which corresponds to a link that is connected to the switch. Figure 2.2b exemplifies this second model. A typical application of these graph-theoretical models is for solving flow problems [34, 36]. Recently, group-theoretic models have been proposed for exploring the symmetry in the topologies of MINs [5].

#### 2.3 Classification

Two IN classification schemes are reviewed below. (Other good classification schemes exist, such as that in [86].) Beneš' classification is suitable for theoretical studies while Feng's classification allows practical issues to be considered.

#### 2.3.1 Beneš' Classification

Beneš' classification scheme [13] is concerned with the permutation power of INs. Although this scheme is extensible to broadcast traffic, this dissertation focuses on 1-to-1 requests. If we denote the number of permutations realizable by a size N network by  $S_N$ , then the combinatorial power (a.k.a. permutation power) of the network is  $r = \frac{S_N}{N!}$ , where  $0 \le r \le 1$ . In the order of increasing connection power, Beneš classifies INs into 3 categories:

Blocking networks have r < 1. Thus, some of the N! permutations cannot be realized even when routing is done off-line (i.e., all N 1-to-1 connection requests are known at the time routing decisions are made). For on-line routing (i.e., a connection request is served immediately upon arrival, putting the network into a new state), some incoming requests cannot be accommodated because of conflicts with existing connections. In this case, the system is in a blocking state and the incoming request must wait until some existing connections are released. The Omega network [73] is an example.

Rearrangeable networks have r=1, but the permutation must be known in advance (i.e., off-line routing). For on-line routing, any incoming request can be accommodated if the routing algorithm is allowed to rearrange existing connections when necessary. The system may reach a blocking state, but by rearranging existing connections it jumps to a safe state that can accommodate the request. Beneš' rearrangeable network [11, 12] is a classical example (Figure 2.12).

Nonblocking networks<sup>1</sup> have r = 1. Routing can be done either off-line or on-line. The system never enters a blocking state and rearrangement is not needed. Two sub-classes are identified:

Nonblocking networks in the wide sense: When multiple paths are available to an incoming request, a path-selection algorithm chooses one such that no blocking states can be reached. More details can be found in [14]. A 4x4 example network is in Figure 6.9. Interestingly, routing on this class of networks can be conceptualized as a 2-player (router/blocker) game [39].

Nonblocking networks in the strict sense: When multiple paths are available to an incoming request, any one can be chosen randomly. That is, there is no blocking state. Examples can be found in [79, 109] and Chapter 5.

Figure 2.3 illustrates Beneš' classification. It is worthwhile to mention the notion of self-routing networks, which is not in Benešs classification. In a self-routing network, a message can be routed to its target once the destination address is given. For instance, the Omega network [73] is self-routing (Figure 2.8). If the network is not self-routing, the routing algorithm needs to know the state of the network to decide the path. Beneš' rearrangeable network is an example (Figure 2.12) [102].

Furthermore, a standard-path network (SPN) [49] is a self-routing network in which the standard path (determined by source and target addresses) is always idle, provided that all existing connections are using their standard paths. A crossbar [134] is a

Note that some authors, e.g. [20], use the term "nonblocking networks" to refer to all permutation networks that have r = 1. Such networks may only be rearrangeable under Beneš' classification.

Figure 2.3: Beneš' classification scheme.

wide-sense nonblocking SPN. Figure 2.4 exemplifies the reason. Two of the many alternative paths between input 2 and output 3 in an idle 3x3 crossbar are shown. If path B is randomly chosen, then clearly some subsequent requests will be blocked. So the crossbar is not strictly nonblocking. By using path A, no subsequent requests will be blocked. In general, a request to connect input i and output j can be satisfied by a tivating cross-point (i, j), so the path can be computed without considering the current state of the network.

Figure 2.4: Two alternative paths in a 3x3 crossbar network.

#### 2.3.2 Feng's Classification

While Beneš's classification concentrates on permutation power, Feng takes design issues into account [41]. In his classification, the cross-product of 4 key design decisions, namely operation mode, control strategy, switching methodology, and network topology, form a space of INs. Now we discuss the 4 decisions:

Operation mode: Synchronous communication is suitable for SIMD machines while asynchronous communication is suitable for MIMD (multiple-instruction-stream-multiple-data-stream) machines and ISDN systems. A combination of these 2 modes is also a viable alternative.

Control strategy: In centralized control, switch states can be set either by signals from a central controller or by retrieving bits from the globally computed routing tag that guides a packet through the network. In distributed control, each switch determines its action based solely on the source/destination addresses in incoming packets, without consulting other switches or packets.

Switching methodology: Circuit-switching [61, 84] is suitable for bulk data transmission while packet-switching [100, 121] is efficient for short messages. Integrated-switching combines these 2 techniques. Also, circuit-switching and packet-switching can simulate each other. Recently, wormhole routing, which attempts to incorporate the advantages of circuit- and packet-switching, has gained popularity (e.g., [33]). Circuit-switched fixed routing [135], which means using a simple heuristic rule to select paths, is another new alternative.

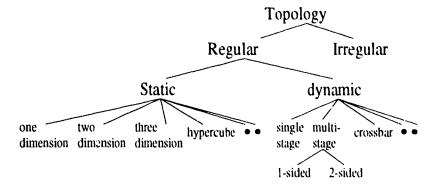

Network topology: This is a key factor in determining a suitable architectural structure. The numerous topologies proposed can be categorized into the tree structure shown in Figure 2.5. Irregular topologies (e.g., [9]) are common for telecommunication systems while regular topologies are popular with multiprocessor systems. Examples of 1-dimensional, 2-dimensional, and 3-dimensional static networks are the ring, the mesh, and the binary 3-cube network (Figure 2.10b), respectively. A single stage dynamic network is also called a recirculating network because several passes through the network may be necessary before a data item reaches its target. The shuffle-exchange network (§ 2.4.2) is an example.

## 2.4 Some Existing Networks

This section reviews some MINs that have been studied extensively in the literature. Good surveys of more INs can be found in [4, 20, 41, 86, 121].

Figure 2.5: Topologies of INs under Feng's classification.

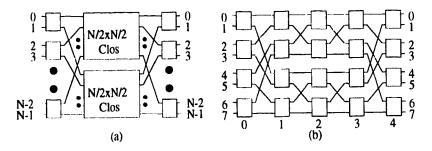

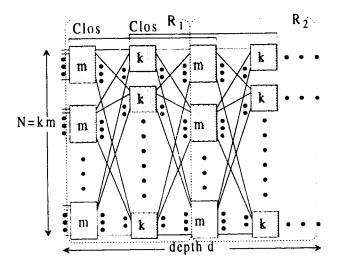

### 2.4.1 Clos Network

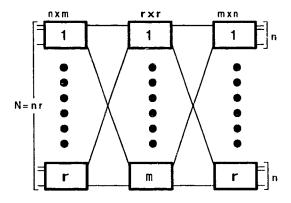

Clos introduced a 3-stage MIN in [24]. It is the basis of many other well known networks such as Cantor's network [23] and Beneš' rearrangeable network [11, 12]. A size N = nr Clos network is denoted by v(m, n, r), where m is a parameter indicating the number of rxr switches used in the middle stage (Figure 2.6).

Figure 2.6: Three-stage Clos network v(m, n, r).

Every switch in the input stage is connected to every switch in the middle stage by a link. This gives a full-access pattern. The interconnection between the middle and output stages mirrors that between the input and middle stages. There are m alternative paths, each corresponding to a distinct switch in the middle stag. Detween every input/output pair. Theorem 2.1 relates m to the power of the network:

**Theorem 2.1 [24]:** The 3-stage Clos network v(m, n, r) is rearrangeable for  $m \ge n$ , and is strictly nonblocking for  $m \ge 2n - 1$ .

The permutation routing problem on a rearrangeable Clos network is equivalent to an m-coloring problem on a bipartite multigraph. Given a permutation  $\pi$  to be routed on a v(m, n, r) network, construct a bipartite multigraph G = (V, E) where  $V = \{u_1, u_2, \ldots, u_\tau\} \cup \{v_1, v_2, \ldots, v_\tau\}$ . For each request (i, j) in the permutation, add an edge  $(u_{\lceil i/n \rceil}, v_{\lceil j/n \rceil})$  to E. Then, an m-coloring of G corresponds to a feasible switch setting for realizing  $\pi$ . This equivalence to coloring problems extends to a larger class of networks that contains the Clos [64, 78].

A variants of Clos's network can be found in [32].

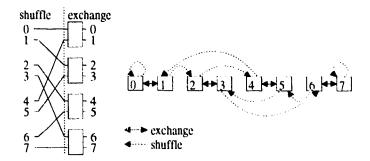

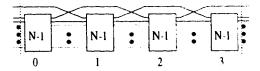

### 2.4.2 The Shuffle-Exchange Network

This important network has received much attention since its introduction by Stone [117]. It is the basic building block for many MINs such as the Omega network [73]. Define the perfect shuffle and exchange functions of an n-bit number  $(b_{n-1}, b_0)$  as:

$$shuffle(b_{n-1} \dots b_0) = (b_{n-2} \dots b_0 b_{n-1})$$

and  $exchange(b_{n-1} \dots b_0) = (b_{n-1} \dots \overline{b_0}).$

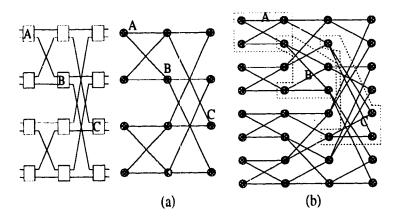

A size  $N=2^n$  shuffle-exchange (SE) network (Figure 2.7a) is formed by cascading a stage of links implementing the shuffle function (on the terminal labels) with a stage of  $\frac{N}{2}$  2x2 switches for implementing the exchange function. Each switch performs an identity function if it is set to the straight state and performs an exchange function when it is in the swap state. Every switch is controlled independently. Figure 2.7b shows a graph-theoretic model for the SE network.

The permutation power of the SE network is very limited, but as shown in [117] it can perform many useful permutations when used repeatedly. The SE topology can easily be generalized to all even  $N \neq 2^n$ . Several other generalizations of the original SE network can be found in the literature (e.g., [68]).

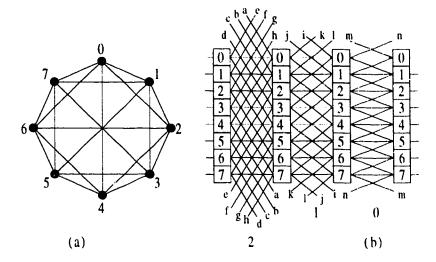

Figure 2.7: A shuffle-exchange network of size 8 (a) and its graph model (b).

### 2.4.3 Cube-Type Networks

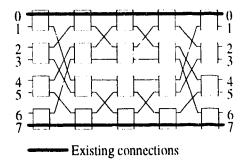

The Generalized Cube Network (GCN) proposed by Siegel [112, Ch. 5] represents a class of topologically equivalent (§ 2.5) no works including the GCN, the Omega, the flip, the indirect binary n-cube, the baseline, the regular SW-banyan (S=F=2), and their inverse networks. These networks are now collectively known as cube-type or hypercubic networks. They have been used in several production systems [114].

Each of the cube-type networks has  $n = \lg N$  stages. There are  $\frac{N}{2}$  2x2 crossbar switches in each stage. From any given input, there is exactly one path to any given output. This is called the *banyan* property [67]. Since each network can realize only  $2^{\frac{N}{2} \lg N}$  distinct permutations, which is less than N! for all  $N \geq 4$ , cube-type networks are self-routing, blocking networks.

Networks in this class share many properties. However, it is still instructive to examine individual networks because they are derived in quite different ways and they accept different sets of permutations (although the total number of acceptable permutations are the same). Below we review the Omega network, the baseline network, and the GCN.

#### The Omega Network

The Omega  $(\Omega)$  network is proposed by Lawrie [73] as an alternative to using the single stage SE network iteratively [117]. Having  $\lg N$  SE stages (Figure 2.8), the  $\Omega$  provides full-access capability (any output can be reached from any input in 1 pass)

at optimal cost. It is an iterated network [43] because one single permutation is used between all stages. The modularized structure of the  $\Omega$  simplifies its fabrication.

Figure 2.8: An Omega network of size 8.

The  $\Omega$  network can realize many useful<sup>2</sup> permutations. A hierarchical classification of the permutations admissible by  $\Omega$ -type networks is presented in [27]. Routing schemes and other properties can be found in [73]. A formal description of the  $\Omega$  topology follows:

- 1. the inputs to each stage are labeled 0 to N-1 from top to bottom. Thus, each switch has a pair or inputs of the form (x, exchange(x)) for  $x \in \{0, ..., N-1\}$ ,

- 2. the label of the upper (lower) output of each switch is identical to the label of its upper (lower) input, and

- 3. stages are numbered from left to right starting from 0. Output y of stage k, is connected to input shuffle(y) of stage k+1, where  $0 \le k < \lg N$ .

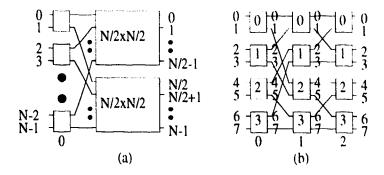

#### The Baseline Network

While the  $\Omega$  is an iterated network, the baseline proposed by Wu and Feng [128] is a recursive network. It is constructed by interconnecting a stage of  $\frac{N}{2}$  2x2 switches and  $2 \frac{N}{2} x \frac{N}{2}$  sub-networks by an inverse perfect shuffle (Figure 2.9a). The fully expanded network is shown in Figure 2.9b. An efficient routing algorithm can be found in [128].

<sup>&</sup>lt;sup>2</sup>E.g., useful for the manipulation of matrices and computing fast Fourier transforms [73].

Figure 2.9: The baseline network (b) and its recursive model (a).

#### The GCN

The GCN is proposed by Siegel [112, Ch. 5] as a multi-stage version of the well known hypercube network. Let the *i*th binary cube function be  $cube_i(b_{n-1} \ldots b_0) = (b_{n-1} \ldots \overline{b_i} \ldots b_0)$ . The GCN topology can then be described as follows:

- 1. the label of the upper (lower) output of each switch is identical to the label of its upper (lower) input,

- 2. the two inputs of a typical switch at the *i*th stage, where  $0 \le i \le n-1$ , has the form  $(x, cube_i(x))$  for  $x \in \{0, ..., N-1\}$ .

Note that a perfect shuffle pattern arises on the input side of the network from the above 2 rules. The *i*th stage simulates data transfers along the *i*th dimension of a hypercube (Figure 2.10). The inverse GCN (IGCN), which is a GCN traversed in reverse, is equivalent to the indirect binary n-cube network introduced by Pease III [97]. He also gives a remarkable characterization of the permutations admissible (realizable in 1 pass) by this network: Let P be a permutation on the set  $\{0, 1, \ldots, N-1\}$  of labels that maps an input address  $X = (x_1 \ldots x_n)$ , where  $n = \lg N$ , to output address  $Y = (y_1 \ldots y_n)$ . Now P can be described by n functions  $f_1, f_2, \ldots, f_n$  such that  $y_i = f_i(x_1, \ldots, x_n)$  for  $i = 1, 2, \ldots, n$ .

**Theorem 2.2 [97]:** A permutation P that maps X to Y is admissible by the indirect binary n-cube network if and only if  $y_i = x_i + f_i(y_1, \ldots, y_{i-1}, x_{i+1}, \ldots, x_n)$  for  $1 \le i \le n$ . Modulo 2 arithmetic is used. (i.e.,  $+ \equiv \oplus$ )

Figure 2.10: A GCN of size 8 (a) and its corresponding 3-cube (b).

Composition of networks is defined before we present the next theorem.

**Definition 2.1** Let G and H be networks of size N. A new network denoted  $G \cdot H$  is obtained by connecting output i of G to input i of H for i = 0, 1, ..., N-1.

**Theorem 2.3 [97]:** The composite network  $GCN \cdot GCN^{-1}$  is rearrangeable, where  $GCN^{-1}$  is the inverse of GCN.

Theorem 2.3 has been used to prove the following important result:

**Theorem 2.4** [97]: The composite network GCN · GCN · GCN is rearrangeable for  $\lg N \geq 3$ .

A generalization of Pease III's work is in [106]. At least 2 well known routing tag schemes<sup>3</sup> for the GCN exist [112, Ch. 5]:

- 1. Exclusive-Or Tags: To go from a source  $S = (s_{n-1} \dots s_0)$  to a destination  $D = (d_{n-1} \dots d_0)$  of a size  $N = 2^n$  GCN, the switch in stage i in the path from S to D must be set to swap if  $s_i \neq d_i$ , and to straight if  $s_i = d_i$ . For instance, if  $s_2s_1s_0 = 010$  and  $d_2d_1d_0 = 100$ , then  $S \oplus D = 110$ . The switches should be set to swap, swap, and straight (Figure 2.11).

- 2. Destination Tags: Regardless of the source, a packet can reach its destination  $D = (d_{n-1} \dots d_0)$  if the packet leaves a switch in stage i using the upper (lower) output when  $d_i = 0$  ( $d_i = 1$ ).

<sup>&</sup>lt;sup>3</sup>A routing tag scheme computes routing tags, which guide the packets through the network.

Figure 2.11: A size 8 GCN serving a request from input 2 to output 4.

More properties of the GCN can be found in [112, Ch. 5]. Note that if the switches labeled (1,3) and (4,6) in stage 1 are swapped without disconnecting any links, the  $\Omega$  network is obtained (Figure 2.8 and 2.10). This immediately proves that for N=8, the GCN and the  $\Omega$  network are functionally equivalent (§ 2.5). Interestingly, they are derived in quite different ways. Siegel introduced fault tolerance to the GCN by adding an extra stage to the input side [112, Ch. 5]. The Extra Stage Cube (ESC) network in Figure 2.12 is obtained. Additional hardware is needed in order to select one of the 2 alternative paths between any input/output pair. Although the ESC is still blocking, most single faults can be tolerated.

Figure 2.12: An ESC network of size 8.

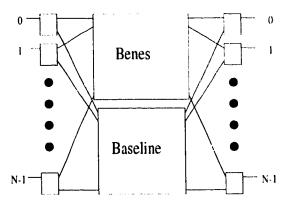

### 2.4.4 Beneš' Rearrangeable Network

Beneš derives this important rearrangeable network from a rearrangeable v(n, m, r) Clos network [11, 12]. He shows that the use of small switches, such as the 2x2 crossbar, can reduce the cost. Large crossbar switches in a size  $N = nr = 2^k$  (for some integer k) rearrangeable Clos network should be recursively replaced by rearrangeable Clos networks of smaller sizes (Figure 2.13a). The resulting network has  $2 \lg N - 1 \lg N \lg N = \frac{N}{2}$  switches (Figure 2.13b). Note that its left-most (right-most)  $\log N$  stages form a baseline (inverse baseline) network.

Figure 2.13: Beneš' rearrangeable network (b) and its recursive model (a).

There are  $\frac{N}{2}$  alternative paths from any input to any output. The optimal sequential routing algorithm, the *looping algorithm* [41], takes  $O(N \log N)$  time. Permutation routing on Beneš' network is closely related to 2-coloring problems on bipartite multi-graphs (§ 2.4.1). There are several generalizations of Beneš' rearrangeable network in the literature (e.g., [87, 132]).

### 2.4.5 The Data Manipulator Network

The Data Manipulator (DM) network is proposed by Feng [i0] as a multi-stage version of the static network plus-minus-2-i (PM2I). A PM2I network is a chordal ring of N nodes  $\{0, 1, \ldots, N-1\}$ , in which chords connect each node j to nodes  $(j \pm 2^i)$  mod N, for  $0 \le i < \lg N$  (Figure 2.14a). All networks in the class of DM networks, including the Augmented Data Manipulator (ADM), the inverse ADM (IADM), and the Gamma network, are topologically equivalent ( $\S$  2.5).

Figure 2.14: An 8-node PM2I network (a) and the corresponding DM network (b).

There are  $\lg N$  stages of links and  $\lg N+1$  stages of switches in the DM network (Figure 2.14b). Stages of links/switches are numbered from right to left starting from 0. Switches in each stage are numbered from 0 downwards. Switch i in stage s+1 is only connected to switches numbered  $(i-2^s) \mod N$ , i, and  $(i+2^s) \mod N$  in stage s, where  $0 \le i < N$ . Every switch in the network, including 1x3, 3x3, and 3x1 switches, allows at most 1 connection at any time. Furthermore, several switches share one common control line. The DM can perform many "data manipulation" functions, including all GCN-admissible permutations [40].

The ADM network proposed by Siegel [112, Ch. 5] allows every switch to be controlled independently. Efficient algorithms for routing 1-to-1 and broadcast requests can be found in [112, Ch. 5]. Although the number of distinct ADM-admissible permutations is known [76, 77], the set of admissible permutations has not been characterized and no polynomial-time routing algorithm was available.

The IADM network studied by McMillen and Siegel [85] is an ADM network traversed in reverse. The Gamma network presented by Parker and Raghavendra [94] is an IADM in which every 3x3 switch allows 3 connections to coexist. Regarding combinatorial power, we have: Gamma > ADM = IADM > DM. The performance of DM type networks operating in packet-switching mode is studied in [133].

## 2.5 Equivalence of Networks

There are two kinds of equivalence relations we want to distinguish [124, Ch. 4]:

Topological equivalence: The corresponding graphs (i.e., switches modeled as nodes and links modeled as edges) of two networks are isomorphic.

Functional equivalence: Two networks are able to perform exactly the same set of permutations, after relabeling the inputs and outputs of a network if necessary.

More formal treatments of equivalence problems of networks appear in [16, 17, 67, 136]. Most studies of equivalence relations among networks concentrate on the class of  $\log N$ -stage banyan networks. Using the GCN as the benchmark, Siegel and Smith [115] show that the Flip, Omega, GCN, and Indirect Binary n-cube networks are topologically equivalent. Wu and Feng [127] introduce the baseline and prove that the Flip, Omega, Indirect Binary n-cube, SW-banyan (S=F=2), and inverse baseline are all topologically equivalent. Pradhan and Kodandapani [101] define an equivalence relation and show that the Flip, Omega, Indirect Binary n-cube, SW-banyan, and all of their inverses are equivalent under the defined relationship. Thus, most of the proposed  $\log N$ -stage banyan networks are topologically equivalent. However, they are in general functionally non-equivalent because of the differences in their admissible permutations, switch architectures, and control schemes (e.g., all DM type networks are topologically equivalent but they admit different sets of permutations).

Agrawal [3] initially studied the necessary and sufficient condition for topological equivalence among  $\log N$ -stage banyan networks. Bermond and Fourneau gave a concise solution in [15]. Note that, by definition, every rearrangeable, wide-sense nonblocking, and strict-sense nonblocking network is functionally equivalent to any other network in the same class. Hardware cost and routing complexity (§ 2.6) become the primary concerns when selecting networks within such classes.

### 2.6 Figures of Merits

Like many other engineering exercises, the design of MINs typically involves tradeoffs between conflicting factors. This section presents a collection of typical areas and questions of interest for evaluating MINs. More details can be found in [41, 82].

- Capability: Is the network blocking, rearrangeable, or nonblocking? What is the set of admissible permutations? How many passes through the network are needed to route a given packet? What is the stage latency (stage-to-stage delay)? Is the bandwidth high enough to handle full traffic load and avoid congestion? How many transfers can proceed in parallel? Can the network be pipelined? (Layered MINs are relatively easy to pipeline.) Is it easy to simulate other networks?

- Functionality: Can broadcasting be supported easily? Can the network combine packets targeting for the same destination to aheviate hot-spot problems? Is the routing algorithm deadlock- and starvation-free [33]? Can the network be partitioned into independent sub-networks?

- Reliability: Is the network fault tolerant? How many faults can be tolerated? Can graceful degradation be achieved and how much disruption will it cause?

- Cost: Is the number of switches (or links) required acceptable? Is the topology area-efficient when implemented using VLSI technology? (e.g., cellular INs [62] are easier to fabricate.) Is the routing algorithm easy to implement and fast?

- Flexibility: Can the network adapt to various traffic loads and patterns? Is it possible to grow the network incrementally? Is the network reconfigurable?

- Regularity: Does the network possess a symmetric structure that can be exploited to solve routing problems? Can the regularity in the topology simplify fabrication?

## 2.7 Complexity of Permutation Routing

Before we close this chapter, it is instructive to examine the complexity of permutation routing in MINs. This problem has practical significance because one way of maximizing the throughput of a clocked packet-switching network is to route each set of traffic requests that constitute a permutation (between the inputs and outputs) in 1 pass through the network, whenever possible. A parallel argument holds for MINs operating in circuit-switching mode where the traffic pattern is a permutation.

An efficient algorithm for deciding whether a given permutation  $\pi$  is admissible by a network G would be invaluable to the design of an efficient routing algorithm for that network. A direct solution to the above decision problem, however, does not seem to exist explicitly in the literature. We argue in the following theorem that it is unlikely that the above problem can be solved efficiently for any arbitrary MIN G. The 3-SAT problem [44], where each variable appears in at most 5 clauses, will be reduced to the above permutation routing problem. The reduction uses a special type of 2x2 switch that allows exactly 1 connection to be made (thus, leaving one output idle). A special switch can be constructed by cascading 2 conventional 2x2 switches (Figure 2.15).

Figure 2.15: Special 2x2 switch allowing only one connection.

**Theorem 2.5** The problem of deciding whether a given permutation  $\pi$  is admissible by an arbitrary MIN G made of 2x2 (ordinary and special) switches is NP-complete.

**Proof:** Given an instance of the 3-SAT problem, we construct a corresponding MIN G such that G admits the identity permutation if and only if the given boolean formula is satisfiable. For each variable  $x_i$ ,  $1 \le i \le n$ , we have an input  $x_i^{in}$  and an output  $x_i^{out}$ . Connect 2 rows of 5 special switches between  $x_i^{in}$  and  $x_i^{out}$  such that 2 disjoint paths exist between  $x_i^{in}$  and  $x_i^{out}$ , corresponding to the true and false values of the variable  $x_i$  (Figure 2.16a). Call this part the x-network.

Figure 2.16: Constructing the MIN for (a) the variables, (b) the clauses.

For each clause  $c_j$  in the given formula,  $1 \leq j \leq m$ , connect a thread of 4 special and 1 normal switches to input  $c_j^{in}$ , and another thread of 4 special and 1 normal switches to  $c_j^{out}$ . These 2 threads are separated (Figure 2.16b). Call this part the c-network. In both the x- and c-network all switches are numbered from left to right.

Since each variable appears at most 5 times, 5 iterations are needed to finish the connections. First, construct an undirected bipartite graph  $\Gamma$  with variables  $x_1, x_2, \ldots, x_n$  as nodes on the left side and clauses  $c_1, c_2, \ldots, c_m$  as nodes on the right side. Insert an edge between  $x_i$  and  $c_j$  for each occurrence of variable  $x_i$  in clause  $c_j$ . By coloring  $\Gamma$  using 5 colors (Vizing's theorem [21, p. 98]), we can decompose it into 5 connected components, say  $\gamma_1, \gamma_2, \ldots, \gamma_5$ . Each connected component consists of edges bearing the same color number and all the nodes in  $\Gamma$ . In the sth iteration, we process  $\gamma_s$ . If there is an edge between  $x_i$  and  $c_j$  in  $\gamma_s$ , connect the output of the sth switch of the thread associated with  $c_j^{in}$  to the input of the (s+1)-th switch in the upper (lower) row of  $x_i^{in}$  if the occurrence is  $x_i$  ( $\overline{x_i}$ ). Also connect the output of this switch back to the input of the sth switch of the thread associated with  $c_j^{out}$ .

In the example in Figure 2.17, the literals  $\overline{x_1}$ ,  $x_2$ , and  $x_n$  in  $c_j$  are the 1st, 2nd and 5th occurrence of the variables  $x_1$ ,  $x_2$ , and  $x_n$ , respectively. Finally, connect all the unused inputs and outputs to the ground. The MIN is now complete.

Suppose that the given formula  $F = \bigwedge_{j=1}^{m} c_j$  has a satisfying assignment, then it is easy to see that G admits the identity permutation. This is true since satisfying a general clause  $c_j$  can be mapped to a path from  $c_j^{in}$  to  $c_j^{out}$ .

For the other direction suppose that G admits the identity permutation, then F is satisfiable because a truth assignment is directly readable from the routes. For

Figure 2.17: An example for  $c_j = \overline{x_1} + x_2 + x_n$ .

example, if the path between  $x_2^{in}$  and  $x_2^{out}$  passes through the upper (lower) thread associated with variable  $x_2$ , then  $x_2$  is false (true). This completes the proof.  $\square$

Corollary 2.1 The above decision problem is NP-complete even if every switch is a 2x2 crossbar and the network has depth 12.

**Proof:** If every special switch is replaced by an equivalent pair of normal switches (Figure 2.15), then we get a MIN made of normal 2x2 switches. Clearly, the resulting MIN has depth 12. □

It is then natural to ask: what is the maximum depth d such that the above decision problem can be solved efficiently on any arbitrary MIN of depth  $\leq d$ ? This problem seems to be open. In Theorem 2.6 we give a direct solution for d=2. Appendix A proves that O(N) time is enough for d=3.

**Theorem 2.6** For a 2-stage MIN of size N, made of  $2x^2$  switches, it takes O(N) time to determine whether a given permutation can be satisfied in 1 pass.

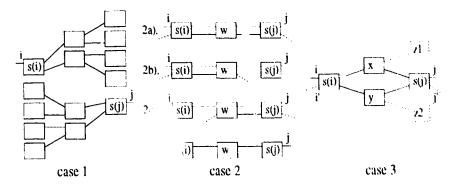

**Proof:** Denote the switch that is directly connected to input/output t by s(t). Assume all switches are initially set to a state called unknown (U). Given a permutation

$\pi$ , it takes O(1) time to identify any of the following 3 exclusive cases for each 1-to-1 request (i,j) in  $\pi$ :

- 1. s(i) and s(j) are not connected by any link: so  $\pi$  cannot be realized in 1 pass.

- 2. One link connects s(i) to s(j): if both s(i) and s(j) are in the U state then set them to straight or swap as required. Therewise, if the required setting conflicts with the current state(s), then terminate with failure. If there is no conflict, set the switch in state U to the required state and proceed to the next request.

- 3. Two links connect s(i) to s(j): set s(i) and s(j) as required if they are in the unknown state. Otherwise, proceed to the next request.

Hence, the routing time and storage requirement are both O(N).  $\square$

In light of the above discussion, it is interesting to settle the complexity of routing permutations on arbitrary MINs of depth d where  $4 \le d \le 11$ .

## Chapter 3

## Routing on Extra Stage Networks

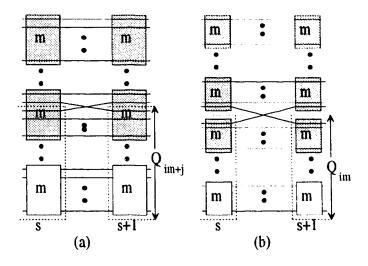

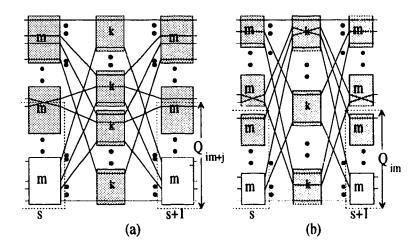

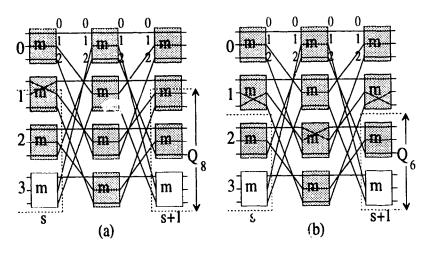

In this chapter we introduce the class of k-extra-stage Generalized Cube Networks (k-GCNs) obtained by adding k extra stages to the class of Generalized Cube Networks (GCNs). Networks of this type provide  $2^k$  alternative paths between each input/output pair. Given such a multi-path MIN and a prescribed traffic pattern, we ask what path-selection strategy minimizes the network delay. § 3.1 gives an introduction to this research area. Switch model and notation are covered in § 3.2. Useful symmetry properties of the k-GCN are derived in § 3.3. § 3.4 proves that under some assumptions, distributing the packets evenly over the 2 alternative paths minimizes the average delay in a 1-GCN for all traffic patterns. The simulation experiment presented in § 3.5 verifies our argument. § 3.6 gives some concluding remarks.\(^1

### 3.1 Introduction

Multi-path MINs provide more than one path for some input/output pairs. For example, the ESC network (Figure 2.12) provides 2 alternative paths between any input/output pair. The C2SC network [1] has 2 extra stages added to a GCN (§ 2.4.3) so 4 alternative paths are available. Under the control of fault tolerant routing algo-

<sup>&</sup>lt;sup>1</sup>A preliminary version of this chapter was presented at the Seventh Annual Canadian High Performance Computing Symposium in Calgary, Canada [71].

rithms, such multi-path MINs can tolerate single or multiple switch or link failures depending on their capabilities.