Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file Votre référence

Our file Notre rélérence

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

**AVIS**

If pages are missing, contact the university which granted the degree.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments. La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

#### UNIVERSITY OF ALBERTA

# A MULTIPROCESSOR DESIGN FOR A PHOTODIODE ARRAY DIRECT READER

bу

TED MC GOWAN

A THESIS SUBMITTED TO THE FACULTY OF GRADUATE STUDIES AND RESEARCH IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

**DEPARTMENT OF CHEMISTRY**

EDMONTON, ALBERTA FALL 1992

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file Votre référence

Our lile Notre rélérence

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive la Bibliothèque permettant à nationale du Canada reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette disposition à la personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement produits sans son autorisation.

# UNIVERSTITY OF ALBERTA RELEASE FORM

NAME OF AUTHOR: Ted Mc Gowan

TITLE OF THESIS: A Multiprocessor Design for a Photodiode

Array Direct Reading Emission

Spectrometer

DEGREE FOR WHICH THIS THESIS WAS PRESENTED: Pt.D.

YEAR THIS DEGREE GRANTED: 1992

Permission is hereby granted to THE UNIVERSITY OF ALBERTA LIBARY to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly or scientific research purposes only.

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permisssion.

(Signed) Jal Mic Gaman

PERMANENT ADDRESS:

Department of Applied Science.

Regional Technical College.

Sligo.

Republic of Ireland.

#### UNIVERSITY OF ALBERTA

#### FACULTY OF GRADUATE STUDIES AND RESEARCH

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies and Research for acceptance, a thesis entitled A MULTIPROCESSOR DESIGN FOR A PHOTODIODE ARRAY DIRECT READING EMISSION SPECTROMETER submitted by THADDEUS (TED) MCGOWAN in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

Dr. G. Horlick (supervisor)

Indered 2 Cantive

Dr. F. F. Cantwell

Ofomer a Planback

Dr. J. A. Plambeck

Scorge Ketorych

Dr. G. Kotovych

R.F. Egerton

Dr. R. Egerton

Dr. J. D. Ingle, Jr. (external examiner)

Dans D'Angle, hi

Date: Sept. 10, 1992

# **DEDICATION**

To

my parents,

my wife Noreen,

and my children Stephen and Nicole.

#### ABSTRACT

The photodiode array is a linear solid state imaging device. As a spectrochemical detector it allows the simultaneous measurement of spectral information from several resolution elements as opposed to the single resolution element measurements of photomultiplier tubes.

In particular, when a number of short segment photodiode arrays are used to replace photomultiplier tubes in a direct reader, its spectral measurement power is greatly enhanced, allowing it to record simultaneously both analyte spectral line intensity and the background intensity in the immediate vicinity of the line. Access to this information about the background against which the intensity of a spectral line is measured, is a major advantage a photodiode array direct reader has over the more conventional photomultiplier based design. Furthermore, this additional background information is available for several analyte lines in a multielement

A single microprocessor or microcomputer is incapable of supporting several photodiode arrays, all of which require high speed signal conversion and control operations. Furthermore, any successful computer system for a spectrometer based on several photodiode arrays, each of which not only generates

spectra consisting of several data points but several such spectra per analytical measurement, requires highly developed data manipulation capabilities.

The design and construction of a photodiode array signal acquisition and control system based around a network of single board computers is described. The hardware and software developed and the underlying design concept for a networked system of signal acquisition, control, and high-level data processing computers for a photodiode array direct reader is described.

The ability of the system to acquire spectra simultaneously on all channels at integration times as low as 10 milliseconds is demonstrated. This contrasts with a single processor based system which was limited to sequential monitoring of individual photodiode array channels with minimum integration times of 0.1 second.

The performance of the system is shown to be greatly superior to a single computer based design. The reproducibility and quality of the spectra generated show significant improvement. Detection limits compare well with the original photodiode array direct reader system and to photomultiplier based direct readers.

Finally, innovative techniques for the correction of spectral interferences using simulated interference spectra are explored.

#### ACKNOWLEDGEMENTS.

I would like to express my grateful thanks to my wife Noreen for all the encouragement, love and support she offered me during my graduate studies. To my children, Stephen and Nicole, I acknowledge their silent but all-important role in this achievement.

Words cannot express my heart felt gratitute to the many wonderful friends and colleages I was so fortunate to encounter. Their friendship, patience and guidance helped bring this thesis to a fruitful end.

To Dr. Gary Horlick, my supervisor and friend, I say a special thank you for the years of advice, patience and guidance.

Last but certainly by me means least, I would like to thank the Department of Chemistry for their support and the electronic shop for their invaluable input to this project.

## TABLE OF CONTENT?

| CHAPTER   | Page                                                                                     |

|-----------|------------------------------------------------------------------------------------------|

| CHAPTER 1 | 1                                                                                        |

| INTRO     | DDUCTION1                                                                                |

|           | 1.1 Photomultiplier Tube Based                                                           |

|           | Spectrometers for ICP Spectrometry1                                                      |

|           | 1.1.1 The Background Correction Problem6                                                 |

|           | 1.1.2 Current Background Correction Methods used with Photomultiplier Direct Readers     |

|           | 1.2 A Photodiode Array based Direct Reader9                                              |

|           | 1.3 Advantages and Limitations of Single  Computer Based Photodiode Array Direct  Reader |

|           | 1.4 Alternative System Concept                                                           |

| 5.1.2 Control Pulses for Data              |

|--------------------------------------------|

| Acquisition38                              |

| 3.1.3 The Analogue Filter and Pre-         |

| amplifier4 1                               |

| 3.1.4 The Track-and-Hold Amplifier and     |

| Analogue-to-Digital Convertor              |

| System4 1                                  |

| 3.2 The Apple II+/Single-Board Computer    |

| Serial Interface (Dual-processor System)46 |

| 3.3 Power Supplies and System Bus5         |

| 3.4 Hardware Features on the Apple II+     |

| "Front-end"5                               |

| 3.4.1 16K Memory Expansion Board54         |

| 3.4.2 The Printer Interface Board54        |

| 3.4.3 The Input/Output Board5              |

| 3.4.4 The Disk Operating System            |

| Controller5                                |

|                                            |

| CHAPTER   | Page                                    |

|-----------|-----------------------------------------|

|           | 3.4.5 The Serial Cards5 6               |

|           | 3.4.6 The Digital Oscilloscope56        |

| 3.5       | The Networked Multiple Processor        |

|           | Photodiode Array System57               |

|           | 3.5.1 The Computer Network5 7           |

|           | 3.5.2 RS232C Serial Communication58     |

|           | 3.5.3 RS232C Standard59                 |

|           | 3.5.4 Connecting Computers Directly     |

|           | using RS232C63                          |

| 3.6       | Networking Single Board Computers using |

|           | a Multiplexer/Demultiplexer Interface   |

|           | Circuit67                               |

|           | 3.6.1 Control Signals72                 |

| CHAPTER 4 | 7 6                                     |

| SOFTWAF   | RE DESIGN7 6                            |

| 4.1       | Dual-Processor System7 6                |

|           | 4.1.1 Introduction                      |

| CHAPTER | Page                                                                                      |

|---------|-------------------------------------------------------------------------------------------|

|         | 4.1.2 General Description of Software76                                                   |

|         | 4.1.3 Modes of Operation7 9                                                               |

|         | 4.1.4 Operating System Programs81                                                         |

|         | 4.1.5 Programming the John Bell  Computer                                                 |

|         | 4.1.6 Memory Organization of the  Apple II+86                                             |

| 4.2     | Multiple processor system86                                                               |

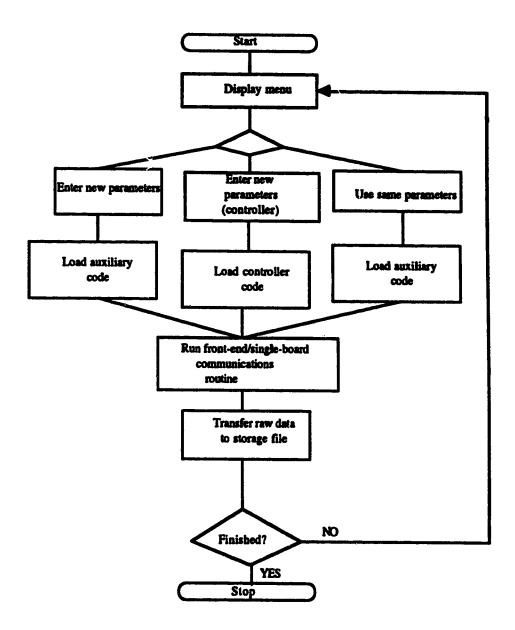

|         | 4.2.1 General Functional Description of the "Front-end" and Data  Acquisition Computers86 |

|         | 4.2.2 Software Design Concepts88                                                          |

|         | 4.2.3 Description of Apple II+  Software89                                                |

|         | 4.2.3.1 Organization of Apple II+                                                         |

| Memory Space90                              |

|---------------------------------------------|

| 4.2.3.2 Storage and Filing of Data94        |

| 4.2.3.3 Entering Parameters and             |

| Control Data9 5                             |

| 4.3 Software Concepts for Network Control95 |

| 4.3.1 General Description of Network        |

| Operation9 7                                |

| 4.4 Overview of Network Control Software101 |

| 4.5 Software/Hardware Integration102        |

| 4.6 Software for the Controller104          |

| 4.6.1 Memory Organization104                |

| 4.6.2 Developing an Automatic               |

| Bootstrap Program for the                   |

| Controller105                               |

| 4.6.3 Interactive Communication with        |

| the Controller106                           |

| 4.6.4 Modifications to the Original John    |

| Bell Monitor107                             |

| CHAPTER                                | Page |

|----------------------------------------|------|

| 4.6.5 Controller Operating System      |      |

| Design                                 | 108  |

| 4.6.6 Control of Integration Times by  |      |

| the Controller                         | 109  |

| 4.6.7 Passing Parameters to the        |      |

| Controller                             | 111  |

| 4.6.8 Control of Data Transmission to  |      |

| the "Front-end"                        | 113  |

| 4.6.9 Access via the Controller to the |      |

| Monitor Program of Auxiliary           |      |

| Processors                             | 115  |

| 4.7 Software for the Auxiliary Data    |      |

| Acquisition Unit                       | 117  |

| 4.7.1 Memory Organization              | 117  |

| 4.7.2 Development of a Stand-alone Pl  | DA   |

| Spectral Acquisition Unit              | 117  |

| 4.7.3 Modifications to the John Bell   |      |

| Monitor used in the Auxiliary          | 118  |

| 4.7.4 Program Design                   | 119  |

| CHAPTER        |          | Page                           |

|----------------|----------|--------------------------------|

| 4.7.5          | Main     | Program120                     |

| 4.7.6          | Passir   | ng Parameters from the         |

|                | "Fron    | t-end" to the Auxiliary        |

|                | Proce    | essor120                       |

| CHAPTER 5      | ******** | 123                            |

| SYSTEM CONFIGU | JRATI    | ON AND ALIGNMENT123            |

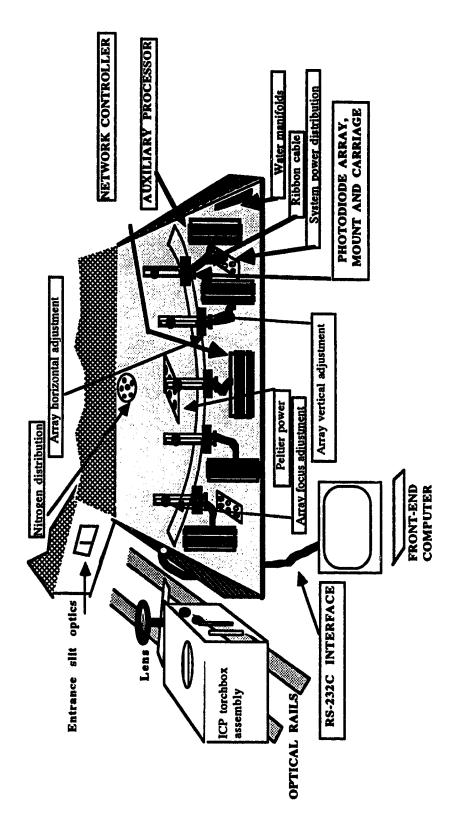

| 5.1 Layout     | of M     | Iultiple Processor System123   |

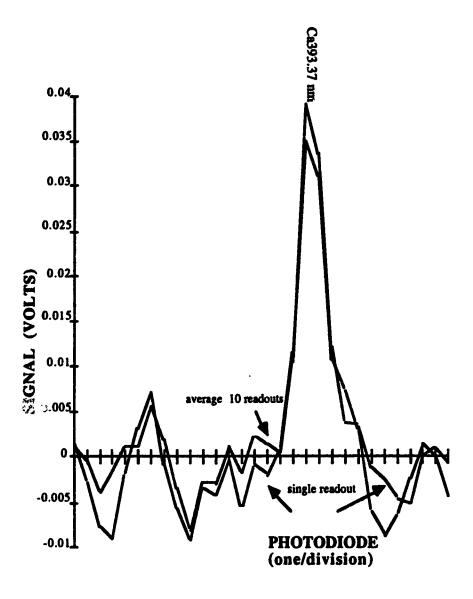

| 5.2 Locatin    | g Spe    | ectral Lines125                |

| CHAPTER 6      | *******  | 128                            |

| PERFORMANCE E  | VALU     | JATION OF THE SYSTEM128        |

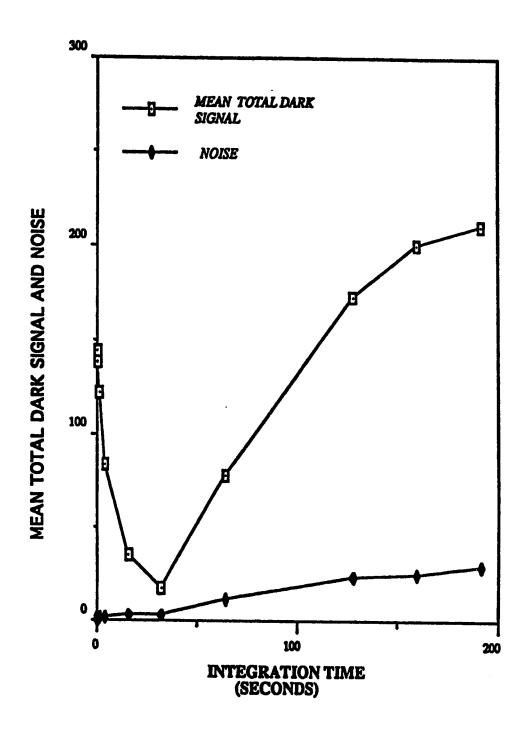

| 6.1 Photod     | iode /   | Array Noise Characteristics128 |

| 6.1.1          | Introd   | luction128                     |

| 6.1.2          | Expe     | rimental131                    |

| 6.1.3          | Discu    | ussion of Results131           |

| 6.1.4          | ICP      | Noise Characteristics136       |

| 6.1.5          | Photo    | odiode Array/ICP Detection     |

|                | Syste    | ms137                          |

| CHAPTER Page                             |

|------------------------------------------|

| 6.1.6 Compromise Conditions for          |

| Photodiode Array Spectral                |

| Measurements137                          |

| 6.2 Performance Evaluation using the ICP |

| Source140                                |

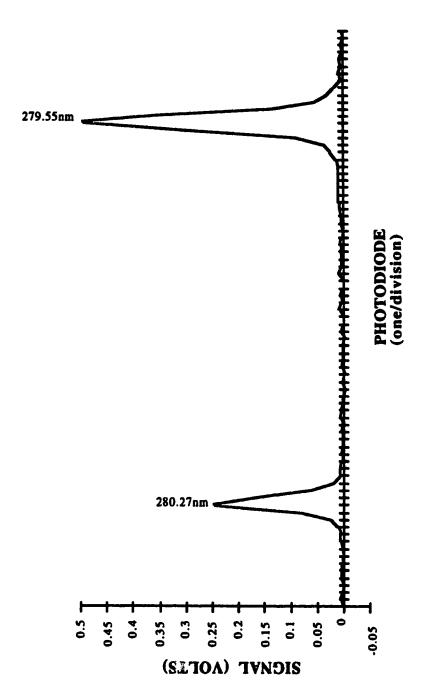

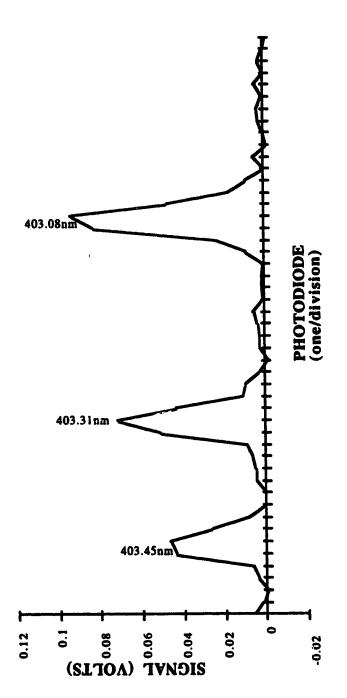

| 6.2.1 Signal-to-Noise Ratios141          |

| 6.2.2 Effect of Integration Time and     |

| Signal Averaging on Signal-to-           |

| Noise Ratios149                          |

| 6.2.3 Detection Limits150                |

| 6.2.4 Decreasing Detection Levels using  |

| Long Integration Times151                |

| CHAPTER 7153                             |

| BACKGROUND AND SPECTRAL INTERFERENCE     |

| CORRECTIONS153                           |

| 7.1 Introduction153                      |

| 7.2 Instrument Generated Background153   |

| CHAPTER   | Page                                       |

|-----------|--------------------------------------------|

|           | 7.3 Source Generated Spectral and          |

|           | Background Interference156                 |

|           | 7.4 Line Broadening Phenomena and Spectral |

|           | Corrections160                             |

|           | 7.5 Background and Spectral Interference   |

|           | Correction Methods in Modern ICP           |

|           | Spectrometers162                           |

|           | 7.6 Background and Spectral Interference   |

|           | Correction Features of the PDA Direct      |

|           | Reading Spectrometer165                    |

|           | 7.7 Signal-to-Noise Ratio Spectra192       |

|           | 7.8 Final System Anaysis and Comments198   |

|           | 7.9 Conclusion and Update205               |

| BIBLIOGRA | РНҮ209                                     |

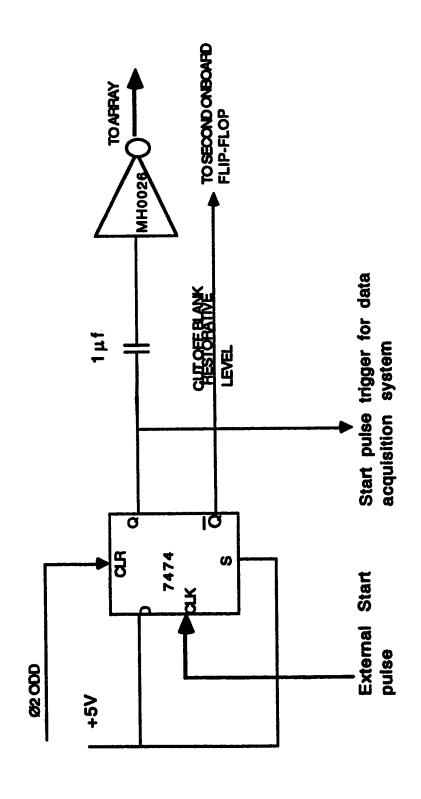

| APPENDIX  | 1 The Start Pulse Circuit on the RC1024S   |

|           | Photodiode Array Driver Board217           |

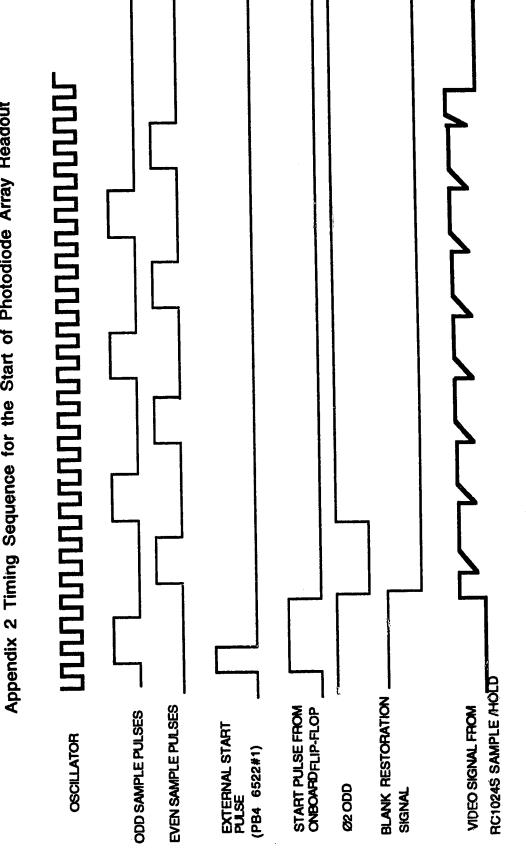

| APPENDIX  | 2 Timing Sequence for the Start of         |

|           | Photodiode Array Readout219                |

| Appendix | Page |

|----------|------|

|----------|------|

| APPENDIX 3  | Timing Sequence for the End of Photodiode  |

|-------------|--------------------------------------------|

|             | Array Readout222                           |

|             |                                            |

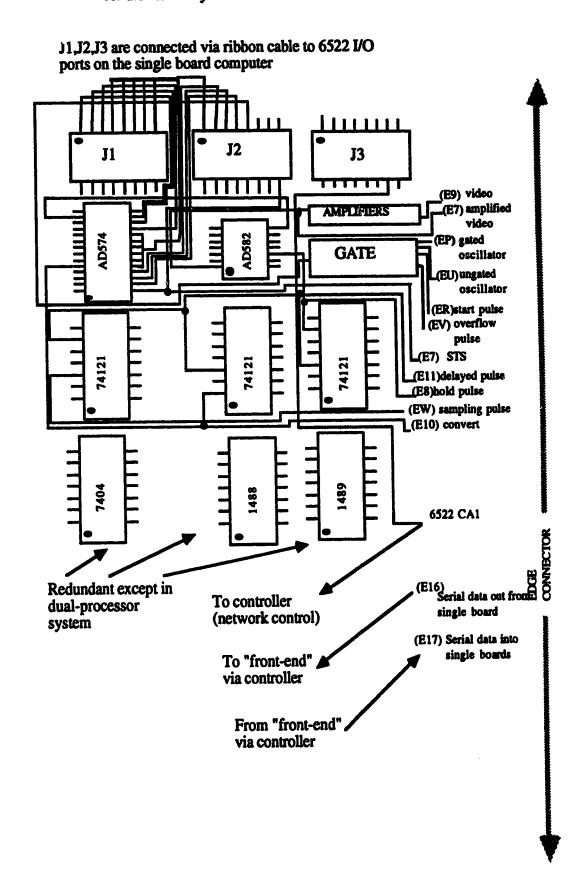

| APPENDIX 4  | Detailed Schematic of Custom Designed      |

|             | Circuit Board for the Auxiliary224         |

|             |                                            |

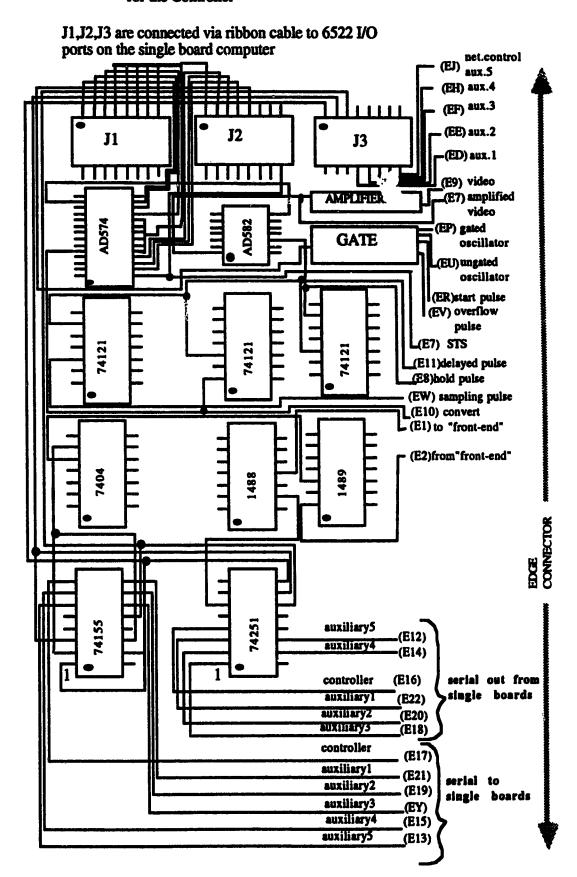

| APPENDIX 5  | Detailed Schematic of Custom Designed      |

|             | Circuit Board for the Controller226        |

|             |                                            |

| APPENDIX 6  | Programs for the Controller228             |

|             |                                            |

| APPENDIX 7  | Programs for the Auxiliary Processors243   |

|             |                                            |

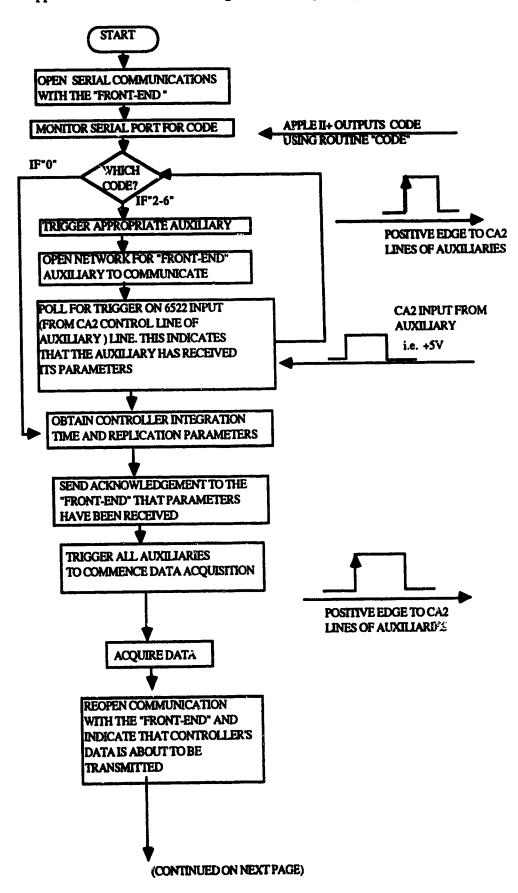

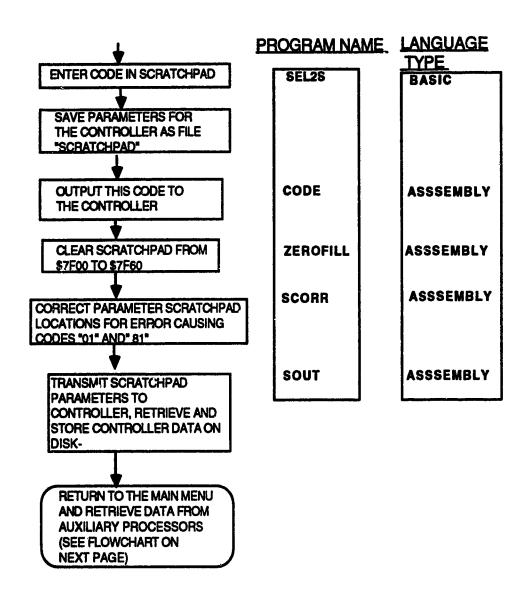

| APPENDIX 8  | Flowchart Describing Controller Operating  |

|             | System Program256                          |

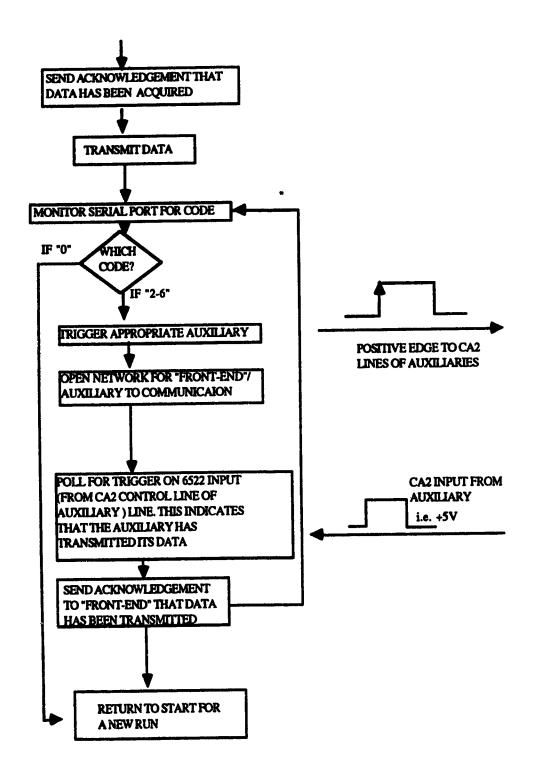

|             |                                            |

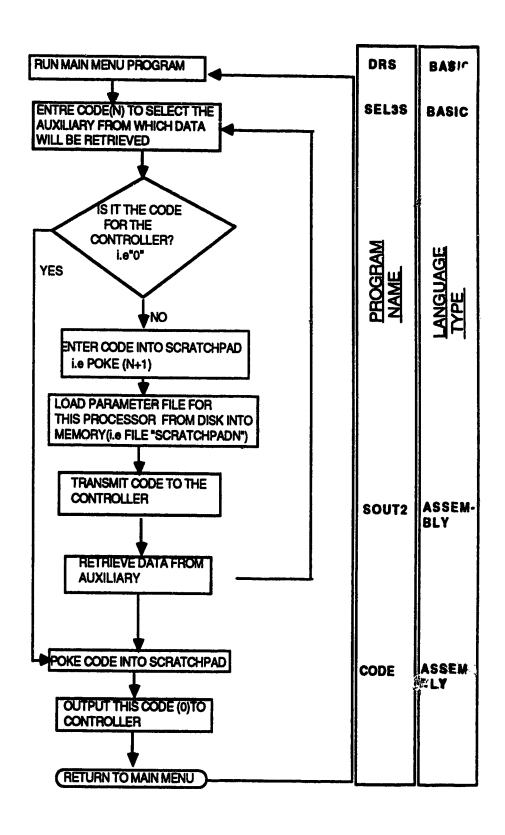

| APPENDIX 9  | Flowchart Describing Auxiliary Operating   |

|             | System Program259                          |

|             |                                            |

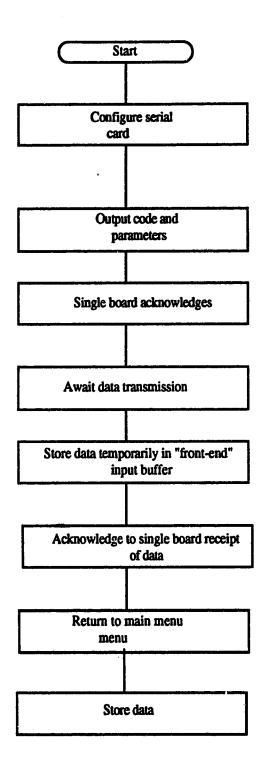

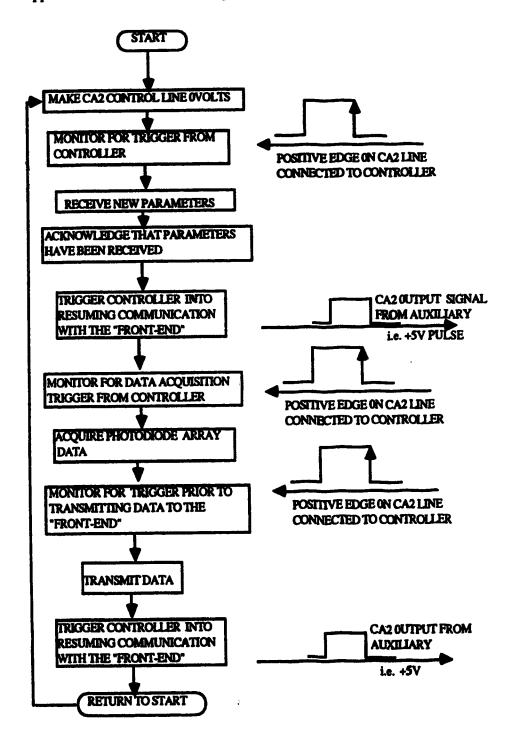

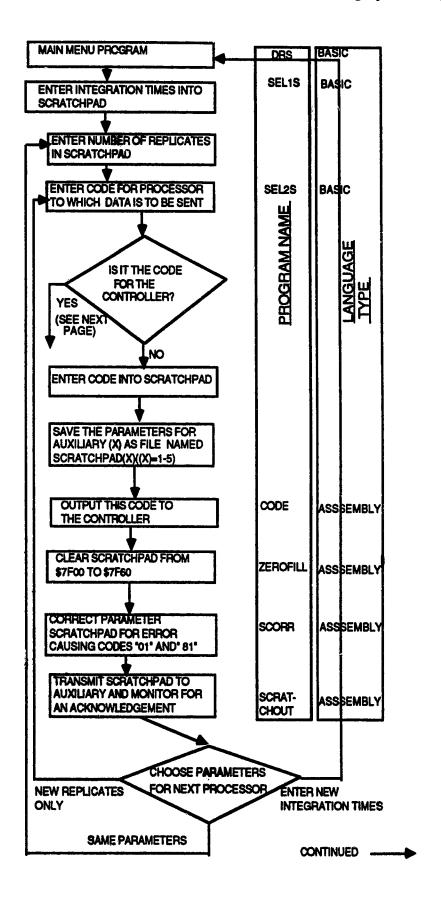

| APPENDIX 10 | Flowchart Describing "Front-end" Operating |

|             | System Program261                          |

|             |                                            |

| APPENDIX 11 | Plasma Operating Conditions265             |

|             |                                            |

# LIST OF TABLES

Page No.

| TABLE 1 | Features of the John Bell Single Board          |     |

|---------|-------------------------------------------------|-----|

|         | Computer                                        | 31  |

| TABLE 2 | Memory Utilization in the John Bell             |     |

|         | Computer                                        | 84  |

| TABLE 3 | Allocation of Memory in the Single Board        |     |

|         | Computer when used in the Dual-processor        |     |

|         | Mode.                                           | 86  |

| TABLE 4 | Memory Utilization in the Apple II+             |     |

|         | Microcomputer                                   | 93  |

| TABLE 5 | Memory Map for Binary Data and Programs         |     |

|         | for the Apple II+ when used in the              |     |

|         | Dual-processor Configuration                    | 99  |

| TABLE6  | Data in Controller EPROM Memory Locations       |     |

|         | used for the Selection and Control of Auxiliary | ,   |

|         | Processors                                      | 103 |

| TABLE 7 | Utilization of RAM and ROM in the Controller    | 105 |

# Page No.

| TABLE 8  | Hexadecimal Codes used in \$FF12 to facilitate |     |

|----------|------------------------------------------------|-----|

|          | Software Control of Baud Rates                 | 108 |

| TABLE 9  | Utilization of RAM and ROM in the Auxiliary    |     |

|          | Processors                                     | 118 |

| TABLE 10 | Signal-to-Noise Ratios for Selected Elements   | 145 |

| TABLE 11 | Detection Limits of Selected Elements          | 151 |

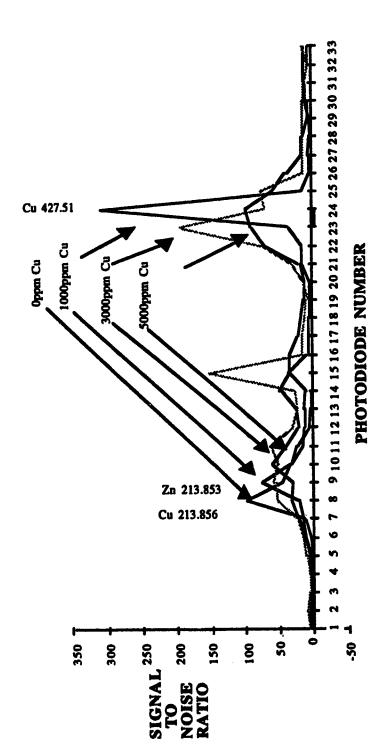

| TABLE 12 | Detection Limits for Zinc at 213.85 nm as a    |     |

|          | Function of Integation Times                   | 152 |

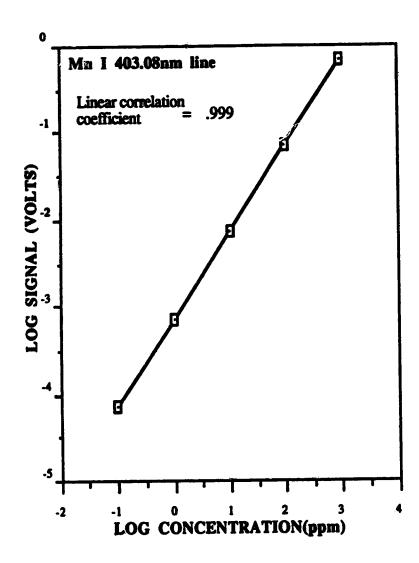

| Table 13 | Dynamic Range Data for Manganese               |     |

|          | at 403.08 nm                                   | 175 |

### LIST OF FIGURES

| FIGUI | KE Page                                                                                    |

|-------|--------------------------------------------------------------------------------------------|

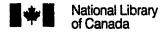

| 1     | The photomultiplier tube based direct reader3                                              |

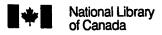

| 2     | Single processor based multiple photodiode array direct reader11                           |

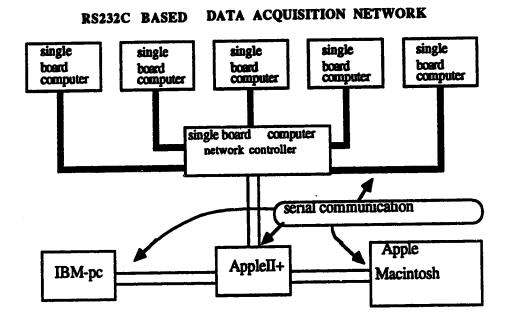

| 3     | Network concept for multiple photodiode array direct reader                                |

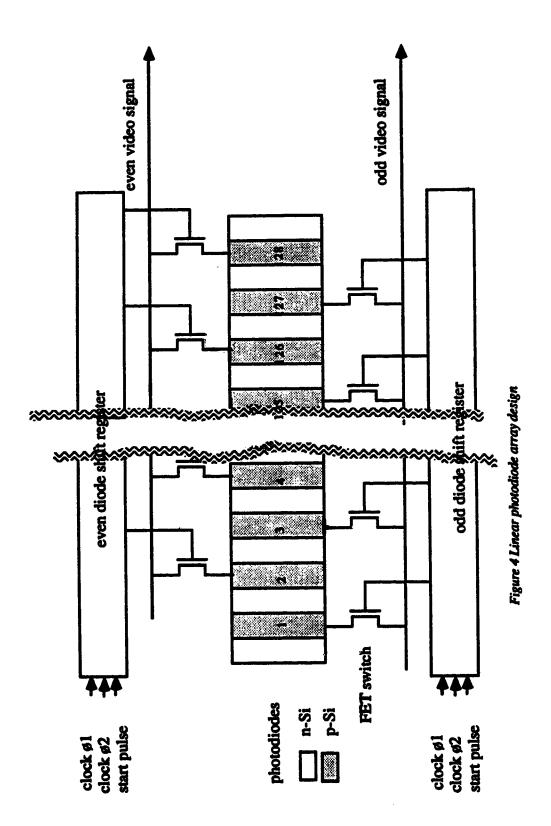

| 4     | Linear photodiode array design24                                                           |

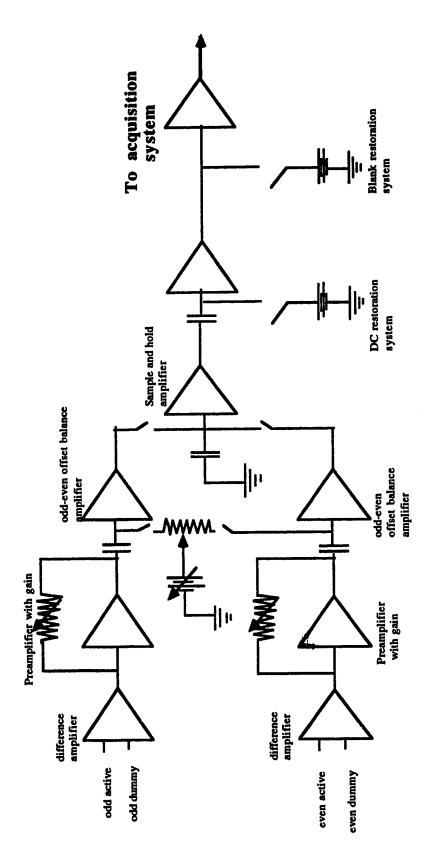

| 5     | The RC1024S analogue video processing circuitry for the photodiode arrray                  |

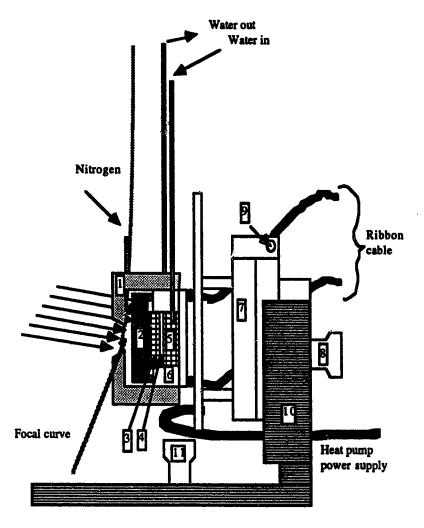

| 6     | The photodiode array, its carriage and cooling system as configured in the direct reader29 |

| 7     | Gating circuit for the RC1024S onboard oscillator                                          |

| 8     | Interface of single-board computer to the gating circuit                                   |

| 9     | Control pulse modification circuit39                                                       |

| FIGURI | E Page                                           |

|--------|--------------------------------------------------|

| 10     | Timing sequence for photodiode array readout42   |

| 11     | Analogue filter and preamplifier circuit43       |

| 12     | The track-and-hold amplifier and analogue-to-    |

|        | digital converter interface45                    |

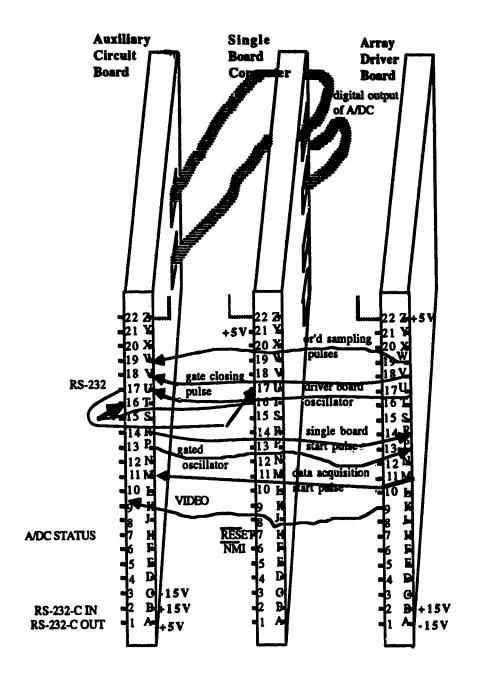

| 13     | Layout of the auxiliary circuit board47          |

| 14     | Serial interface between the "Front-end"         |

|        | processor and the John Bell single-board         |

|        | computer4 9                                      |

| 15     | Interconnection bus for individual modules of    |

|        | the single board computer based data acquisition |

|        | system5 1                                        |

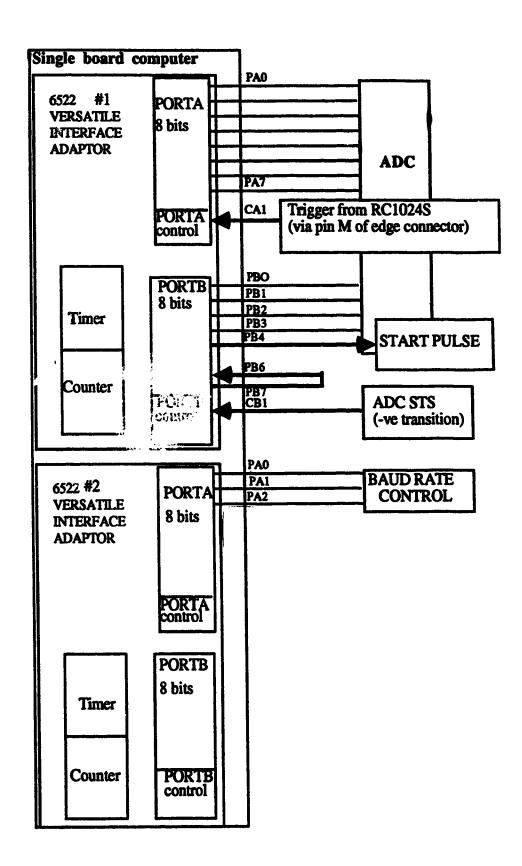

| 16     | Utilisation of I/O ports on the John Bell single |

|        | board-computer53                                 |

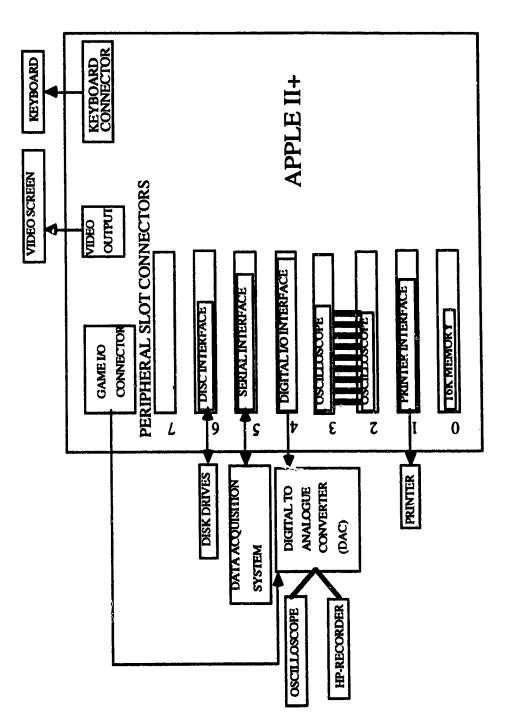

| 17     | Utilisation of the Apple II+ backplane55         |

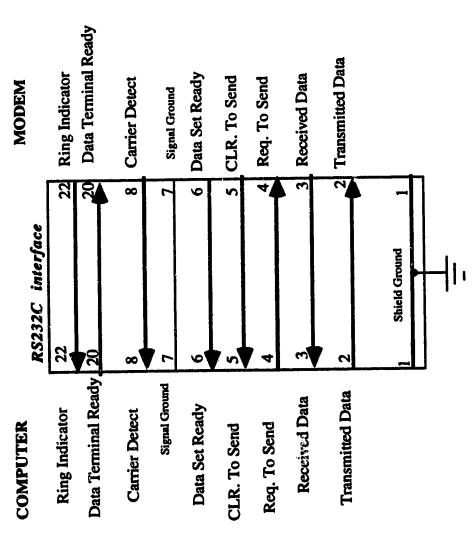

| 18     | RS232C Interface with communication              |

|        | equipment 60                                     |

| FIGUR | FIGURE Page                                    |  |

|-------|------------------------------------------------|--|

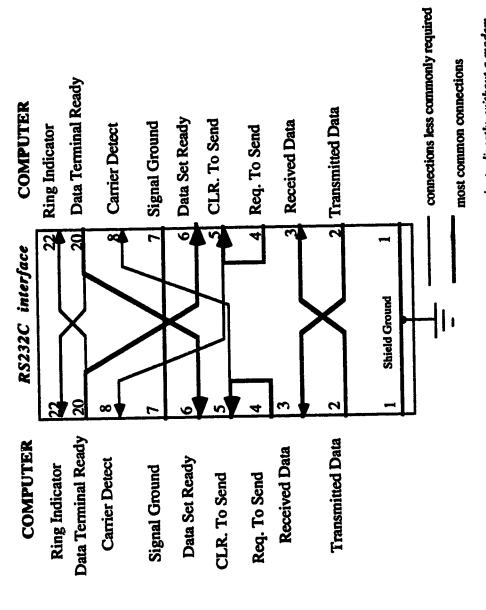

| 19    | Configuration of RS232C lines to allow two     |  |

|       | computers to communicate directly without a    |  |

|       | modem64                                        |  |

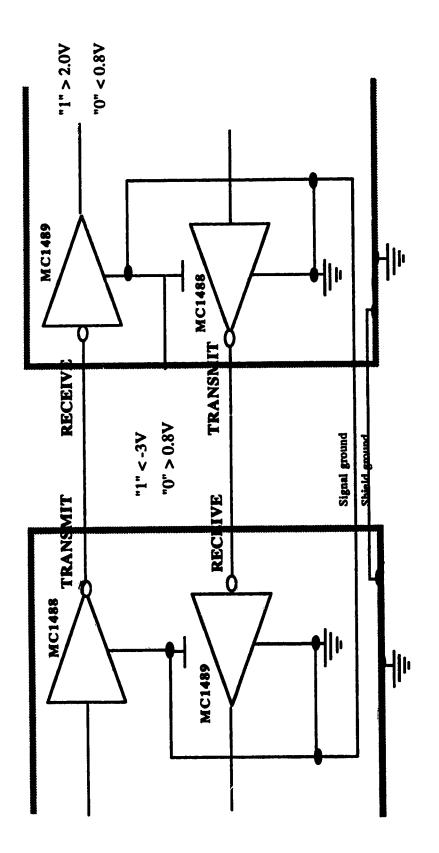

| 20    | Electrical conventions for RS232C interfaces66 |  |

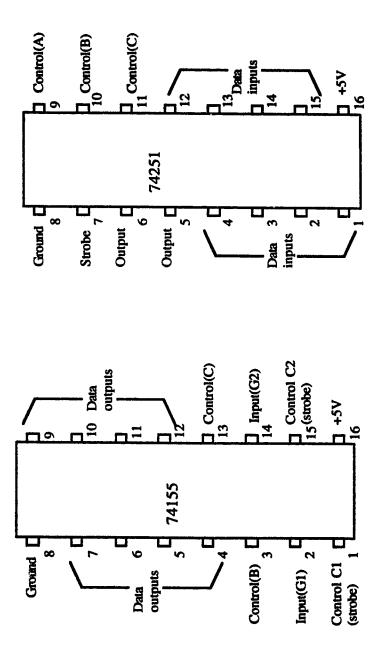

| 21    | The 74251 multiplexer and the 74155            |  |

|       | demultiplexer6 8                               |  |

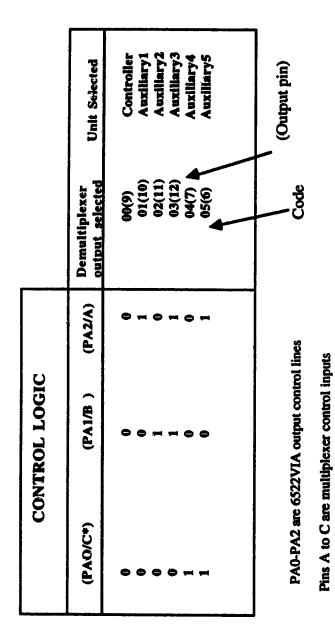

| 22    | Logic diagriam for channel selection using the |  |

|       | 74155 demultiplexer7 1                         |  |

| 23    | Logic diagriam for channel selection using the |  |

|       | 74251 multiplexer73                            |  |

| 24    | Schematic of network control for serial        |  |

|       | communication between "Front-end" and          |  |

|       | auxiliary processors74                         |  |

| 25    | Dual-processor data acquisition system77       |  |

| 26    | Flowchart of the operating system program for  |  |

|       | the single-board data acquisition computer82   |  |

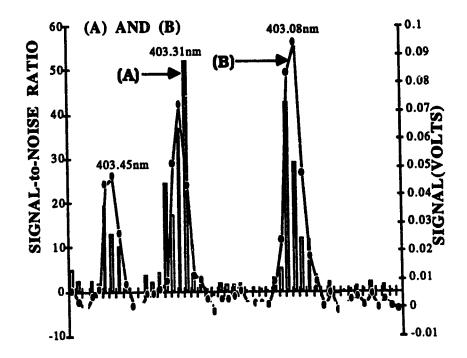

subtracted spectrum)......146

| FIGURI | Page                                             |

|--------|--------------------------------------------------|

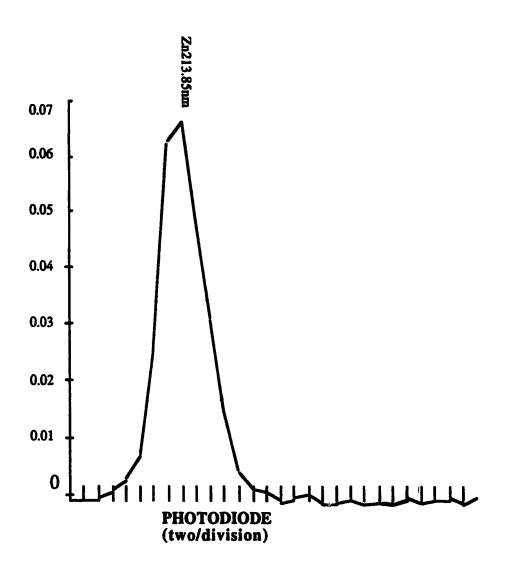

| 35     | The Zn 213.85 nm spectral line, 10 ppm solution, |

|        | second order spectrum148                         |

|        |                                                  |

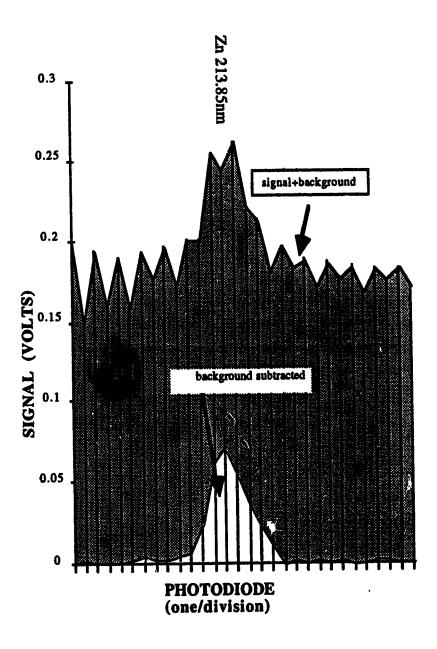

| 36     | Raw and water background subtracted spectrum     |

|        | of 10 ppm Zinc169                                |

|        | (10 m) (10 m) (10 m) (10 m)                      |

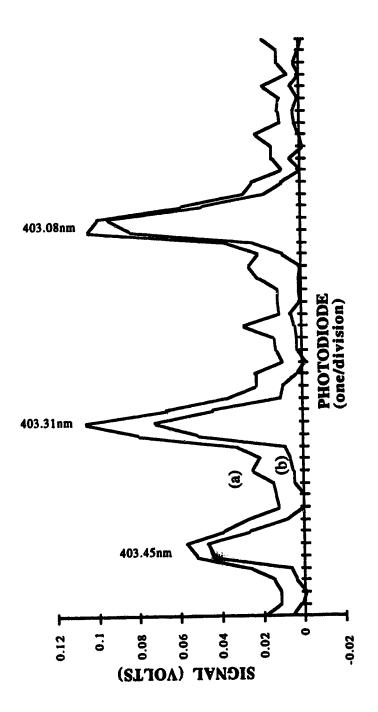

| 37     | (a) Raw signal spectrum of 10 ppm Manganese.     |

|        | (b) Background subtracted spectrum of 10 ppm     |

|        | Manganese170                                     |

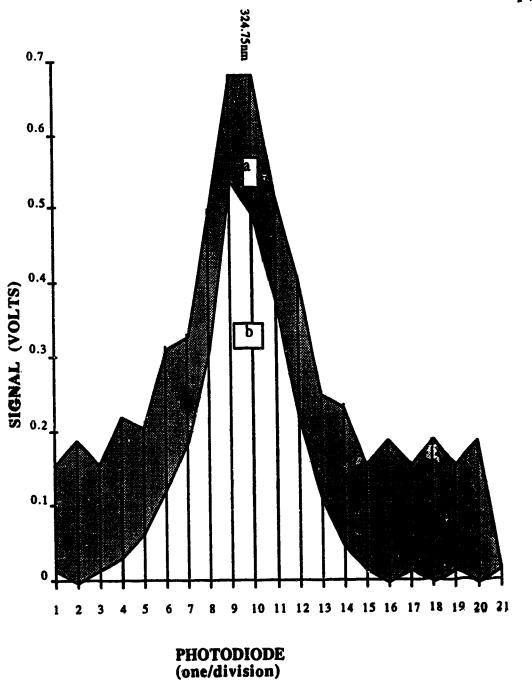

| 38     | (a) Raw signal spectrum of 10 ppm Copper.        |

| 30     | (b) Background subtracted spectrum of 10 ppm     |

|        |                                                  |

|        | Copper171                                        |

| 39     | Calibration plot for Manganese demonstrating     |

|        | the dynamic range achievable with the PDA        |

|        | direct reader176                                 |

|        |                                                  |

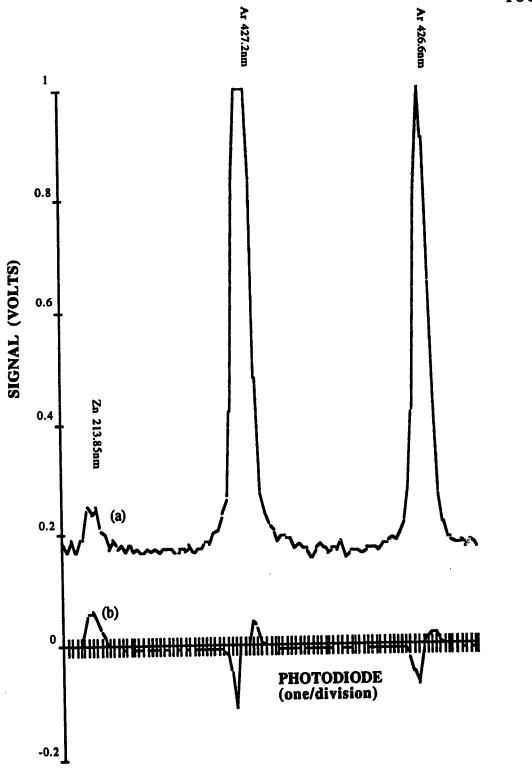

| 40     | Spectrum of 10 ppm Zn and the adjacent Argon     |

|        | emissions                                        |

|        | (a) before background subtraction and            |

|        | (b) after the water background is subtracted180  |

|        |                                                  |

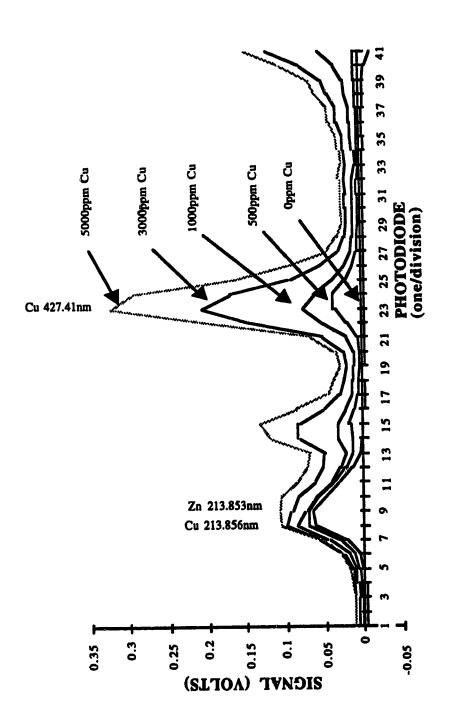

| 41     | Water background subtracted spectra of 10 ppm    |

|        | Zn with variable copper matrix181                |

| FIGURE | Page                                              |

|--------|---------------------------------------------------|

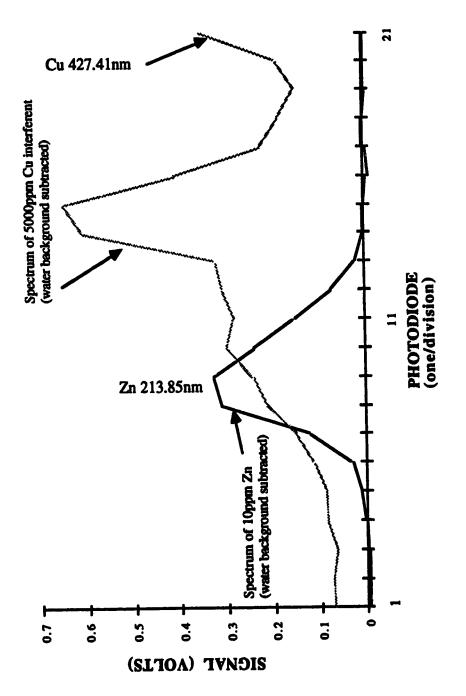

| 42     | Water background subtracted spectra of 10 ppm     |

|        | Zn and 5000 ppm Cu in vicinity of zinc            |

|        | 213.85nm spectral emission183                     |

| 43     | Recovery of Zn signal at 213.85 nm by direct      |

|        | subtraction of spectrum of 5000 ppm copper        |

|        | interference184                                   |

| 44     | Calibration plots for copper at (a) 324.7 nm (b)  |

|        | 427.5 nm and (c) the copper interference at Zn    |

|        | 213.86 nm expressed as ppm Zn186                  |

| 45     | Graphical display of copper spectral interference |

|        | and corrected signals at Zn 213.85 nm, as a       |

|        | function of copper concentration188               |

| 4 6    | Corrected spectra following subtraction of        |

|        | simulated spectra of copper interference from     |

|        | raw signal spectra191                             |

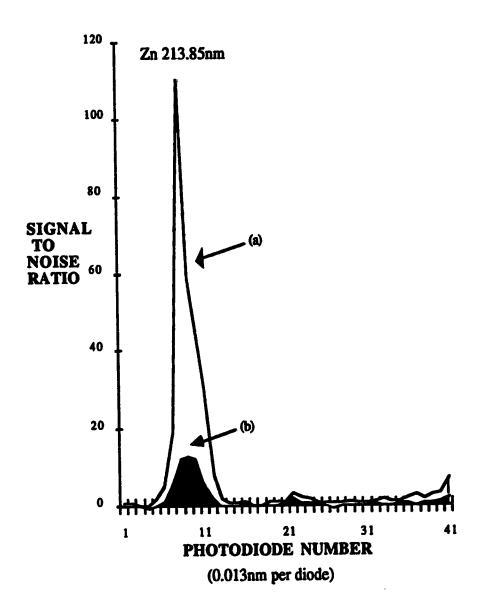

| 47     | Complete a) signal-to-noise ratio b) signal and   |

|        | c) standard deviation spectra for 10 ppm          |

|        | Manganese193                                      |

| FIGUR | E Page                                                                                         |

|-------|------------------------------------------------------------------------------------------------|

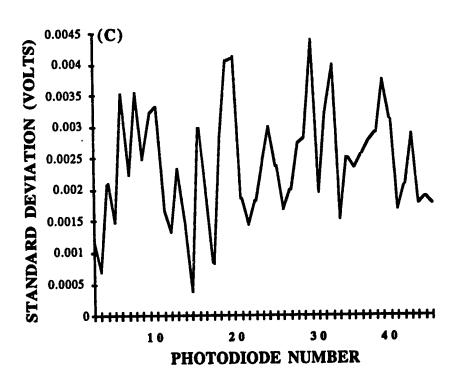

| 48    | Signal-to-noise ratio spectra for 10 ppm Zn having variable concentrations of copper as matrix |

| 49    | Signal-to-noise ratio spectra for zinc signal with                                             |

#### CHAPTER 1

#### INTRODUCTION

1.1 Photomultiplier Tube Based Spectrometers for ICP Spectrometry

The development of reliable and sensitive photomultiplier tubes led to their use in spectrometric instrumentation as far back as 1945 (1). The electronic recording of spectral data offered several advantages over the previous technology which employed photographic plates as detectors. Some of these advantages were superior accuracy, precision and sensitivity, less tedious manual involvement and greatly increased dynamic range (2).

Many types of spectrometers are available to record emissions from spectral sources. Off these, two distinct categories have been developed for determining the concentrations of several elements by the direct measurement of the intensities of their atomic emission spectra. These are:

- (i) Sequential spectrometers and

- (ii) Simultaneous spectrometers.

Sequential spectrometers used for atomic emission measurements are generally monochromators incorporating an entrance slit, a diffraction grating, an exit slit and a single photomultiplier tube.

Light from the spectral source enters through the entrance slit and is dispersed by the diffraction grating. The diffraction grating can be rotated so that a distinct spectral band incorporating the specific wavelength of an analyte is passed

through the exit slit. The intensity of the emission is measured by the photomultiplier tube.

To accurately measure the emission intensity for an atomic species it is important that the background upon which the emission appears is also measured.

The scanning monochromator can obtain some information about this background by scanning across a narrow wavelength range on either side of the spectral line. Its main disadvantage is that the recording of this background signal is sequential rather than simultaneous i.e., ideally both the analyte signal and the background in its vicinity should be recorded simultaneously. For multielement determinations this type of spectrometer will also have to sequentially record the intensities of spectral emissions for all elements.

Various manufacturers have developed what are termed "slew-scanning" spectrometers employing this sequential approach to multielement atomic emission measurements. These spectrometers allow fast rotation of the grating (slew) from one analyte line to the next and then slowly scan the line profile and background in its vicinity. Similar to other sequential spectrometers, a constant analyte signal is required and these spectrometers are generally unsuitable if used with solid sample introduction devices which generate transient signals.

The photomultiplier tube based direct reader has become the standard simultaneous instrument for multielement quantitative atomic spectroscopy. A well known configuration for this type of spectrometer is shown schematically in Figure 1. This configuration is known as the Paschen - Runge mount and is based on the Rowland circle principle. This uses a concave reflective diffraction grating with a radius of curvature equal to the

Figure 1. The photomultiplier tube based direct reader

diameter of the Rowland circle. Light from a slit on the circumference of the Rowland circle is dispersed and re-focused by the concave grating to images along the circumference of the same circle. Exit slits and secondary optics are used to isolate and transfer specific spectral lines to the individual photomultiplier tubes (PMTs). Each exit slit-PMT combination is frequently referred to as a channel.

This is a simple optical system which has a concave grating as the single optical device within the instrument. The focal circle is therefore free, allowing for the dicretionary positioning of detection devices.

A commercial direct reader having this configuration is the Compact Atomcounter which was manufactured by the Jarall-Ash company prior to 1961. This direct reader had a focal curve opposite the grating of 1.5m. The reciprocal dispersion is give by:

$$\frac{d\lambda}{-} = \frac{a \cos \beta}{nr}$$

where:  $d\lambda$  rate of change of light wavelength

— with change in position around

the Rowland circle

a = grating ruling interval

n = spectral order

r = radius of curvature of the grating

β = angle of dispersion of a particular wavelength of light

This is a medium resolution instrument with a typical reciprocal dispersion of approximately 0.55 nm per mm in the first order.

With such a direct reader spectral line intensities can be measured with relative standard deviations of about 1% (3) and a linear dynamic range of about seven orders of magnitude.

Despite the capabilities of the photomultiplier tube based direct reader, it still lacks many of the features desired for an ideal atomic emission measurement system, especially when used with an inductively coupled plasma (ICP) atomic emission source. Chiefly among these are it's lack of versatility and its inability to record the total spectrum or continuous wavelength information. The latter is of great importance when the spectral background in the vicinity of the analyte line is unknown or variable.

The versatility problem arises when it is desirable to observe an alternative spectral line to the one the manufacturer originally designed the instrument to monitor, or, to record intensities of a number of spectral lines which are in very close proximity to each other. The initial task (to add to or alter a channel in the field) is achievable but requires a lot of expertise and perhaps even the assistance of the manufacturer, while the latter is almost impossible to carry out. To select an alternative spectral line requires placing the exit slits, mirrors and wavelength selection filters with great accuracy since the actual entrance slit images are of the order of tens of micrometers in width. For spectral lines occurring very close together the only remedy is to use a system of mirrors, this is both extremely difficult and not always successful. Some manufacturers attempt to increase the versatility of the direct reader by including a scanning monochromator (4) with the system (sometimes called an n+1 channel).

## 1.1.1 The Background Correction Problem

This lack of versatility makes the direct reader interquate for many applications, especially as a non-routine general propose spectrometer. Also difficulties in quantifying background radiation which originates in a spectroscopic system (i.e., either in the source or in the spectrometer) is a major impediment to the computation of accurate analytical measurements. This background radiation is a particular problem in an atomic emission source such as the ICP which produces a wealth of populated higher energy atomic levels and thus numerous spectral lines. The ICP also emits a continuum which tends to complicate measurements for some elements. This excitation of a large number of spectral lines naturally gives rise to situations where two or more lines overlap, leading to spectral interferences.

To achieve an accurate measurement of the intensity of an analyte spectral line in the presence of a variable spectral background, it is necessary to obtain the complete background signal in the vicinity of the line. Obviously, the acquisition of both the spectral line and its background signal simultaneously is an advantage.

In situations where direct spectral overlaps occur, accurate measurements of the spectral intensity of the analyte line can only be made after subtraction of the signal component due to the interferent. This can only be achieved if the interferent itself can be quantified accurately and preferably simultaneously in another measurement channel. This of course means that the the spectral line intensity of the interferent and its background signal are both required. Therefore ideally, in cases of direct spectral overlaps, two measurements of signal plus background (that of analyte and interferent) must be made simultaneously.

Current photomultiplier based direct readers are incapable of making such simultaneous measurements of analyte signal plus background. Therefore the accuracy of corrections in cases of spectral overlaps is poor. A detailed discussion of the sources of various spectral interference is given in Chapter 7 of this thesis.

1.1.2 Current Background Correction Methods used with Photomultiplier Tube Direct Readers.

Current background correction methods for PMT based direct readers can be catogerized as either on-peak of off-peak methods.

On-peak corrections can be very accurate but require that the interfering concomitant has its own measurement channel on the direct reader. Prior to ordering the instrument, all the matrices to be tested must be specified so that the necessary detection channels are placed in the focal plane or curve.

Before an analysis, the response of each of the channels of the spectrometer to the individual matrix elements is obtained. Interferent calibration curves of apparent concentration of the analyte against the actual concentration of the interfering matrix element are prepared. During analysis, measurements of the interfering matrix elements are made in separate channels and using this data corrections are made to the analyte concentrations. The corrections are determined from the working calibration curve (i.e., of apparent concentration of analyte caused by the interferent in the analyte channels).

On-peak correction is the only way to correct for direct spectral overlaps in PMT-based direct readers. It requires that the positions of all the exit slits be established with respect to the

diffraction grating and the entrance slit. This is achieved by thermostatic control of the instrument.

Off-peak correction methods are used to correct for background radiation in the vicinity of the spectral line. Using these methods the spectral bandpass falling on the exit slit is shifted slightly so that the background on either side of a spectral line is measured by the detector.

To achieve an off-poak measurement two approaches have been taken, both of which involve an effective shifting of the angle at which the incident light meets the diffraction grating. One of these methods involves physically shifting the entrance slit. This requiires a high degree of precision. It has also the disadvantage that it changes the position of the slit with respect to the spectral source. It is well known that the intensity profile of spectral lines emitted from the ICP is position dependent and therefore background measurements may be inaccurate.

The other method for off-peak measurements involves rotating a quartz refractor plate located just behind the entrance slit. The rotation of the refractor plate causes an effective shift in the position of the entrance slit with reference to the grating. This method once again requires a very precise movement to change the angle of rotation. There may also be changes in reflectivity at the plate surface (6) with rotation angle.

Off-peak measurements can correct for continuum radiation and stray light but not for spectral overlaps. It requires a stable source and would therefore not be successful if used with ICP sample introduction systems which generate transient emission signals.

To conclude therefore, continuum, wing (close encounters) and direct spectral interferences can be major problems in ICP emission spectrometry. As a result, simultaneous multiple wavelength monitoring of several spectral lines and of the background in the vicinity of these lines, is often required in order to arrive at an accurate analytical result for the analyte.

The use of photodiode arrays as detector elements in direct reading spectrometers may offer solutions to many of the above problems.

## 1.2 A Photodiode Array Based Direct Reader

Evans (5) designed a photodiode array direct reader to overcome some of the major disadvantages of PMT based systems.

These disadvantages, as already described included limited versatility and inadequate simultaneous spectral information measurement, especially in the vicinity of the spectral line of the analyte. A photodiode array offers a spatially continuous detector to tackle these problems.

Self scanning linear photodiode arrays (PDAs) have been utilized in many areas where spectrochemical measurements (7-10) are required. These range from astronomy for very low light level measurements (11) to a plethora of laboratory spectrochemical measurement systems.

Detailed discussions on the use of photodiode arrays for atomic spectrochemical measurement are given by both Horlick (12) and McGeorge (13).

Photodiode arrays are fabricated on a silicon chip. The physical length of the array itself is about 1 cm for a 1000 element photodiode array unit. The height of an individual

photodiode element of the array is no greater than 2.5 mm. All the commercial arrays are linear and therefore some problems could be envisaged when attempting to focus all pixels of the array in the curved focal plane of a direct reader. This problem can be alleviated if not elimated by using short 128-element arrays.

The 2.5 mm height of the photodiode is also much less than the image of the entrance slit (1 cm) in the focal plane and as a result not all the light reaching the focal plane of the spectrometer is utilized. It would be possible to resort to some form of secondary optics to condense the beam.

In the photodiode array direct reader developed by Evans and Horlick (5) the original secondary optics used with the photomultipier tube design, including the exit slits on the direct reader focal plane have been removed. These have been replaced by the short 128 element photodiode arrays on a moveable carriage (Figure 2).

The photodiode arrays are positioned on a carriage along the focal plane so that each one detects a window of spectral information. Additionally, the photodiode array is mounted so that each diode is parallel to the entrance slit and therefore samples a unique wavelength range of the dispersed light.

The integration times and readout triggering signals for each array are controlled by a single microcomputer which also stores, processes and displays the acquired spectra.

Figure 2 Single processor based multiple photodiode array direct reader

# 1.3 Advantages and Limitations of the Single - Computer Based Photodiode Array Direct Reader

The successful construction of the initial photodiode array direct reader proved that image sensor technology could be adapted and applied successfully to overcome the unique measurement problems associated with standard PMT based direct readers.

Evaluation of the system indicated that moving the photodiode array window about the focal curve was relatively easy and that choosing a new spectral line was greatly simplified. This removed to some extent the versatility problem associated with direct readers. Spectral backgrounds, measured simultaneously with the analyte signal, indicated that backgrounds from the same array readout could be used to correct for the effect of spectral background features. Signals due to interferent (recorded on other photodiode arrays in the system), when used to correct for direct spectral overlaps proved reasonably successful. For the photomultiplier based direct reader temperature dependent changes in alignment resulted in drifting of the spectral line across the exit slit. This was much less of a problem here since multichannel measurements are taken.

Despite the success of the prototype when applied to relatively simple measurements, it was found to have many major limitations when utilized as a general purpose direct reading spectrometer. Most of these limitations arose from the original design concept utilizing a single microcomputer to perform all the necessary tasks for the entire system. This greatly over extended the available resources of the computer system involved, as indeed it would of any currently commercially available microcomputer system.

A 64K Apple II+ microcomputer was used to handle all the control tasks. These included setting the integration times, sending trigger pulses and capturing data from all six photodiode arrays involved. It also stored, graphically displayed, and processed the spectral data. This burden of tasks on a small microcomputer led to limitations in both flexibility and performance. Also, the use of additional photodiode arrays to expand the system could not be accommodated without total system redesign.

Ideally, the simultaneous readout of all the spectral windows is desired rather than the sequential readout performed by this system. Arising from this sequential array readout, there was a 0.1 second lower limit forced on the possible integration times which could be used. This eliminated the possibility of measuring a number of relatively strong signals (which would require shorter integration times) simultaneously.

Data handling and display facilities were both inadequate and inflexible due to the limited random access memory (RAM) and poor quality graphics. Additionally, the graphical display locked the user into a general data display format for all spectra. No capability for expanding spectra to highlight minor spectral features was available.

Noise problems also arose on readout of arrays leading to a frequent overranging of the signal at the output of the video amplifiers. This prevented signal averaging and often slowed down data processing since each spectrum had to be viewed individually beforehand. This limited confidence in the data acquired and was therefore a serious problem. It is probable that this noise arose from the use of three separate power supplies in the system. The analogue-to-digital converter (ADC) and the preamplifiers were powered by a different power supply than the

array driver board. As a result frequent differences in ground potentials were measured.

Besides inadequate grounding, serious problems arose from inadequate shielding of the analogue signals. These were transferred, by both BNC and Ribbon cable from inside the spectrometer to the external Apple II+ based digitization board. The actual ADC itself, which was located on a circuit board inside the Apple II+ was not shielded from transitions occurring nearby.

Several other areas for improvement were noted by the original designer (5), including the need for a better diffraction grating and an improved, more stable array cooling system.

In order to eliminate its major drawbacks and deficiencies, it was evident that the system based on a single microcomputer was inadequate and a totally new system design concept was necessary.

## 1.4 Alternative System Concept

It has already been demonstrated that a single microcomputer, cannot satisfactorily handle the complex array control and signal acquisition requirements of a multiple photodiode array direct reader. An alternative expandable system, based on a single microprocessor would require the capability of performing parallel analogue-to-digital conversions on several channels simultaneously. This type of system is not available commercially and would virtually be impossible to build from scratch. The ability to store, file and manipulate the large amount of data generated by the multiple PDA direct reader would require an easy to use microcomputer system with powerful graphics and data processing capabilities.

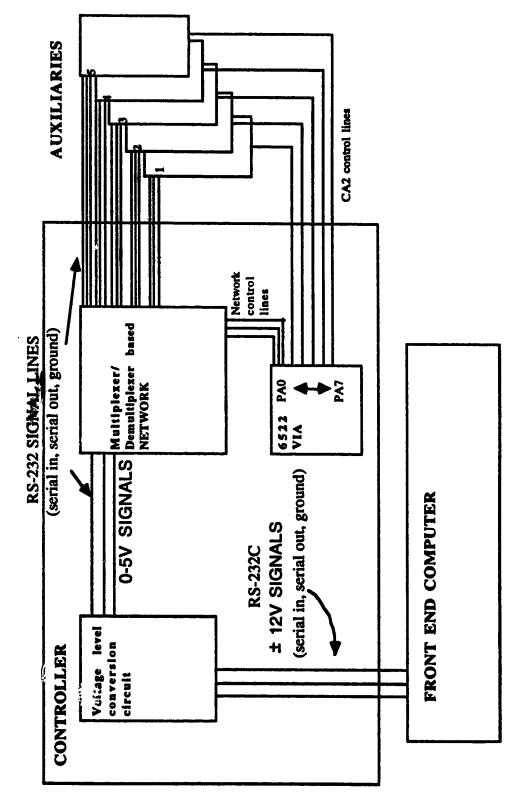

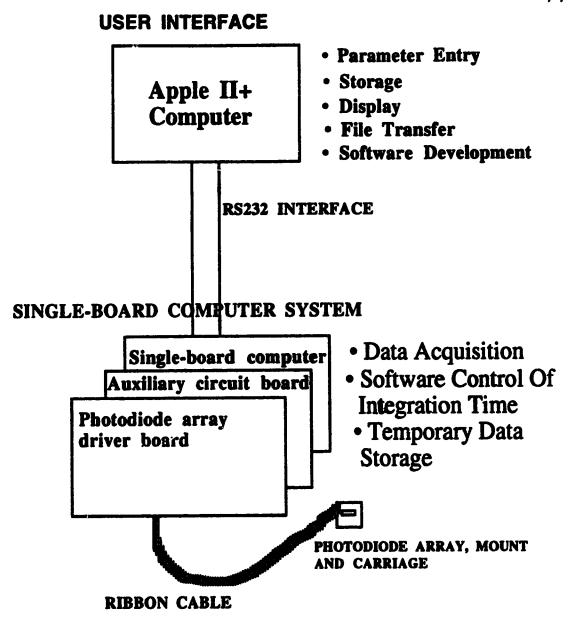

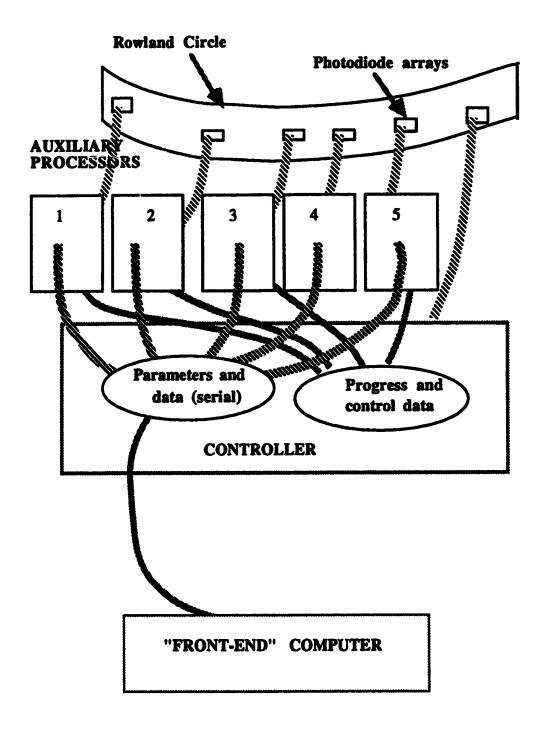

To satisfy all these requirements, an alternative design concept for the system is one that would involve the use of a single computer and digitization system for each array. This subsystem would handle signal pre-treatment, acquisition and control for a single array, and ideally would also perform temporary storage/accumulation of the array signal(s). Additionally, each signal acquisition computer could independently perform signal averaging and take multiple spectra of a transient signal. A number of these single board computers could be networked together, to a "front end" or "host" processor (Figure 3).

The "front-end" processor functions as the user interface for permanent storage, processing, reduction and display of signals.

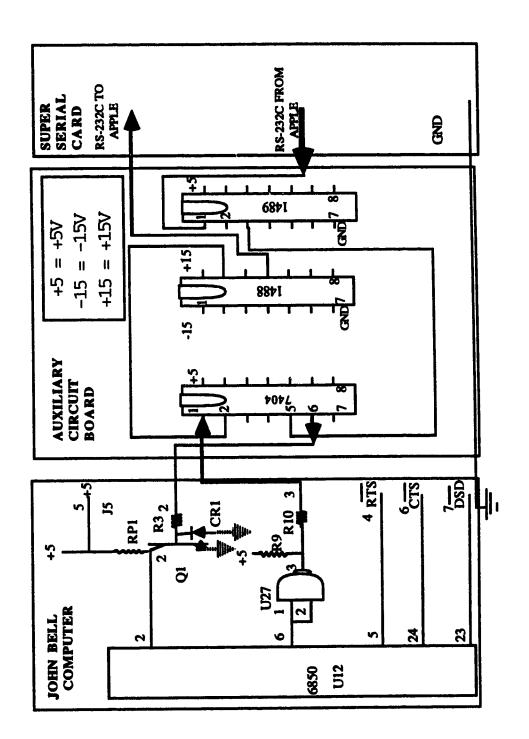

The acquired data would be transferred digitally, via an RS232C serial interface from the temporary storage on the acquisition computer to the "front-end". Since all analogue signal pre-treatment and conversion would occur inside the grounded light proof box of the spectrometer, a great degree of noise immunity to the RF from the ICP and other external noise sources would be possible. The RS232C standard therefore would be adhered to for communications throughout the networked system. It is probably the most common standard interface supported on computers and it is well understood.

This modular approach would if necessary allow the replacement of the "front-end" or "host" as technology developed, while maintaining the high performance data acquisition component of the system.

The input of parameters such as the integration times for each array by the user, would be accomplished via this "frontend". A file of these parameters could subsequently be

Figure 3 Network concept for multiple photodiode array direct reader.

transmitted over the network to the individual acquisition computers. A controller would serve to control access to the network and trigger all systems for simultaneous spectral acquisition etc.

Data could after acquisition, be transferred serially from the "front-end" to other computer systems if desired, for further processing or to exploit more powerful graphic facilities. The system would also be designed around a single power supply, thus reducing noise from this source (experienced with the previous system).

In summary, what is desired is an ideal single board or "slave" processor to perform all present and projected control and data-acquisition tasks involving the photodiode array, and an ideal "front-end" processor for interaction with the user. A network design incorporating a controller, would facilitate flexible and transparent communication between these two functionally different ends of the system.

The specification required for the single board data acquisition and control computers could therefore be summarized as follows:

- 1. It should have a large number of Input/Output and control lines.

- 2. It requires a large amount of onboard RAM (Random Access Memory) for the temporary, sequential storage of several signals.

- 3. Onboard timers and counters are necessary for the control of integration times.

- 4. An onboard RS232 communications interface is necessary.

- 5. An onboard monitor for program development and debugging is required.

- 6. It should be compact ie. capable of being located together with several other similar systems, inside the dark box of the spectrometer.

- 7. It should be capable of acquiring and storing data at speeds of 10KHz or greater.

- 8. It should be relatively inexpensive.

The "front-end" processor would preferably have the following features:

- 1. Menu or icon-driven

- 2. User friendly

- 3. A range of data-processing and graphics software

- 4. Capable of efficient file handling

- 5. Permanent data storage facilities

- 6. Hardcopy and report facilities

- 7. Software development tools (e.g. cross-assembler) for the development of software for the signal acquisition and control computers.

The goal of this work is to design, build and characterise, such a multiple PDA direct reading spectrometer in the concept of Figure 3, with the above listed features. The hardware and software aspects of the system are presented in Chapters 3, 4 and 5 and a basic evaluation of the resulting system is presented in Chapters 6 and 7. But first, in the next chapter (Chapter 2) the old system is briefly overviewed and summarised.

#### CHAPTER 2

#### PRELIMINARY SYSTEM DESCRIPTION

#### 2.1 System Components

The original multiple photodiode array direct reader was designed around a single processor. It was a sophisticated instrument consisting of a number of individual components having varying degrees of complexity. In the development of the new system, some components had to be discarded and replaced, while others were kept intact and incorporated into the new design.

The following components/sub-assemblies which were part of the original design were modified for inclusion in the multiple processor photodiode array direct reader:

- A direct reading spectrometer based on the Rowland circle (Compact Atomcounter).

- The 128 element photodiode arrays.

- The photodiode array carriages and ribbon cables.

- The modified RC1024S photodiode array driver board.

The following additional hardware sub-systems are necessary as part of the multiple-processor design:

- A single board computer interfaced to each individual photodiode array.

- Separate analog-to-digital converter/track-and-hold amplifiers for each photodiode array/computer system.

- Separate analogue filters and pre-amplifiers for each photodiode array.

- Level conversion circuitry for the serial interface.

- A suitable network which would allow each single board computer access to a common host.

- Hardware for a network controller.

- A suitable computer to act as host.

The choice and subsequent integration of these hardware sub-systems into a functional direct reading spectrometer is described in the next chapter (Chapter 3). Additionally, to have an operational multiple processor photodiode array direct reader, three major software modules are required. These are:

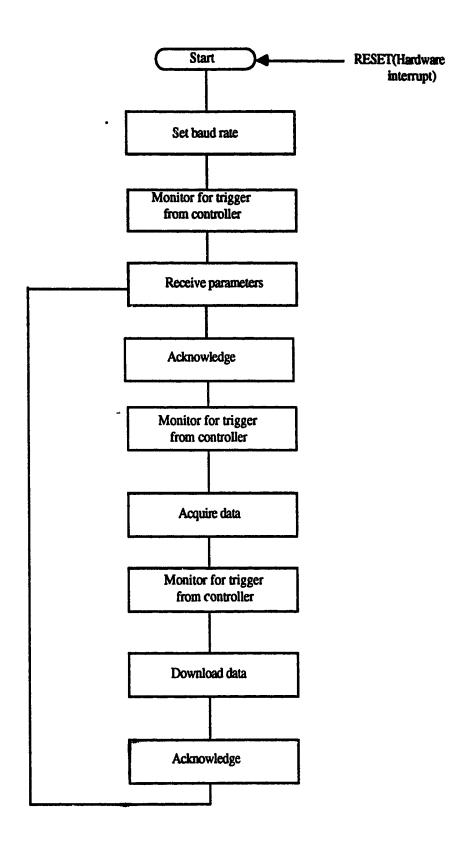

- (a) ROM based software in each acquisition computer. For communication with the host, to set integration times, control acquisition of the signal and to both store and accumulate the acquired signal.

- (b) ROM based software in the computer which functions as network controller. This software controls triggering and sensing of multiple processor operations while also acting as a data acquisition computer for an attached photodiode array.

- (c) Floppy disk based software in the host or "front-end" computer. This software facilitates communication with the user, thereby allowing parameter transmission too, and data retrieval from, the single board computers. Front-end software for performing a variety of other functions such as data transmission to other microcomputers, data reduction and display is also required.

A detailed description of the software and its design for the system is given in Chapter 4.

The following computer systems were used either as part of, or as software development aids for the multiple processor based photodiode array direct reader;

- The John Bell single board computer (John Bell Engineering, Inc. 1014 Center Street, San Carlos, CA 94070)

- The Apple II+ and the Apple Macintosh (Apple Computer, 20525 Mariani Avenue, Cupertino, CA95014)

- •The Rockwell AIM65 microcomputer (Rockwell Inc., 3310 Miraloma Ave., P.O. Box 3669, Anaheim, CA92803) was used for EPROM programming.

#### 2.2 The Modified Direct Reading Spectrometer

The direct reader (Jarrell-Ash Company, pre 1961 Compact Atomcounter) and accompanying concave diffraction grating is the same as that originally used by Evans (5).

The original photomultiplier tube detectors, exit slit assemblies and electronics had been discarded. The light proof box had been mounted on a steel frame and the entrance slit is 51.5 cm above the floor making it compatible with spectral sources mounted at this height on rail beds in the laboratory. The configuration of the spectrometer is known as the Paschen-Runge (14) mount and is based on the Rowland Circle principle (15).

The spectrometer uses a concave diffraction grating with a radius of curvature equal to the diameter of the Rowland Circle. The focal length of the grating is 1.5 meters. Images of the

entrance slit are focused as spectral lines along the circumference of the circle.

Photodiode arrays can be placed along the exit focal plane (Figure 2), limited only by the manouverability of the photodiode mounting stands within the spectrometer. The length of circumference of the useful focal plane is about 1 meter. Therefore many locations are available for detection of spectral lines. Whenever it is physically impossible to place two arrays close enough together then spectra can be be accessed in different spectral orders at other positions on the focal plane. This provides an extra degree of flexibility.

The accessible spectral range is from 200 nm to 600 nm in the first order. The instrument has a reciprocal dispersion ranging from 5.65 nm per centimetre directly opposite the grating, to 5.40 nm per centimetre at the maximum accessible angles of dispersion (first order).

## 2.3 The Reticon RL128 Photodiode Array.

The Reticon "S" Series linear self scanning photodiode arrays have been specially designed for spectroscopic work. They have an aspect ratio of 100:1 (i.e., 2.5 mm high and set on 25  $\mu$ m spacing). In most previous arrays the photodiode elements were not as high and therefore could not sample as large a portion of the slit image.

Each 128 element array is capable of sensing a spectral window of 1.4 to 1.8 nm (in the first order) depending on whether it was mounted directly opposite the grating or at the maximum angle of dispersion. Although not used in this design, PDA's of 64, 256, 512, 1024, 2048 and 4096 elements are available.

PDA's consist of parallel rows of p-type silicon on a substrate of n-type silicon (Figure 4). Hole electron pairs can be generated by light falling on both the n and p-type silicon. The diodes operate in a charge storage mode i.e. the p-n junctions are reverse biased and therefore act like small capacitors and store charge. To recharge a photodiode to full reverse bias the p-type bars are grounded while the n-type substrate is maintained at a positive potential.

The acquisition of a spectrum using this photodiode array is carried out electronically. Initially a positive start pulse is sent to the shift register on the array. This "high" logic level opens a FET switch which connects the p-type bar to a previously grounded video line thereby recharging the photodiode to full reverse bias. The recharging process takes about 1 µs following which the ptype bars are again isolated from ground. A clock shifts the bit in the shift register therefore addressing the FET switch for the next photodiode and it is recharged in a similar fashion. This process continues until all of the 128 photodiodes are recharged. The freshly charged photodiodes can now be discharged at a rate proportional to the intensity of the light impinging on them. After a period during which discharge is allowed to take place (known commonly as the integration time), the photodiodes are again recharged to full reverse bias in exactly the same fashion as previously described. This time, the amount of discharge which is registered by the video signal line is converted by the analogue circuitry to a voltage which is digitized by the computer system.

These Reticon arrays have additional features including both dummy diodes (16) and separate shift registers for readout of the odd and even photodiodes. The dummy diodes serve to generate a signal on a separate video line, therefore generating the equivalent capacitively coupled switching transients as the active

photodiodes. Differential processing of both dummy and active video signals is used to diminish the effect of these transients.

Separate shift registers and video outputs for odd and even photodiodes, have to be accompanied by separate signal processing circuitry. This often leads to an odd-even pattern which adds to fixed pattern signal generated by other sources. This can be minimized by control potentiometers on the analogue driver board but can be directly subtracted by the computer using a background or "dark current" spectrum.

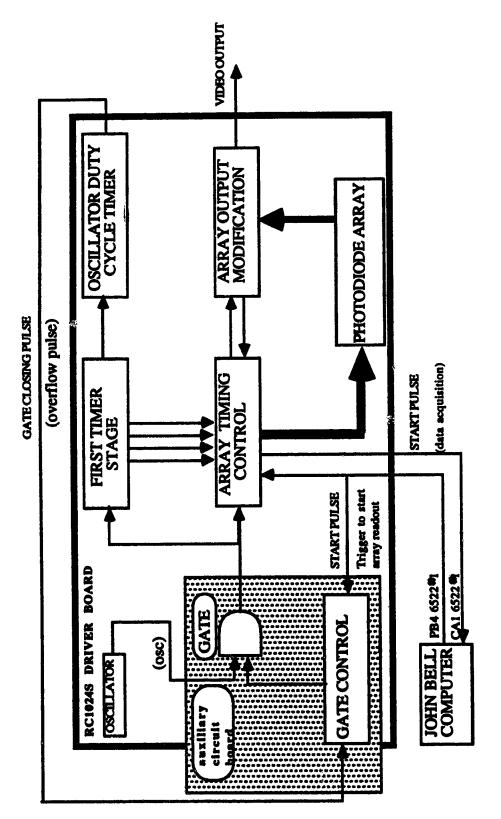

#### 2.4 The RC1024S Printed Circuit Drive Board.

The RL128 photodiode array was originally received from the manufacturer mounted on the RC1024S printed Circuit Board (24 cm wide by 12 cm high).

This circuit board provides both the complete digital circuitry for clocking and readout of the array in addition to analogue circuitry to process the video signals (Figure 5). An onboard oscillator provides the time base with which the integration time and all the clock signals required for readout of the array are generated. The board performs a number of control functions ranging from regulation of input drive voltages, synchronization of clock signal edges, differential readout of active and dummy photodiodes and the combining of the odd and even video signals to produce a single video output.

Circuitry on this board converts the TTL based signals to the MOS levels required to drive the array shift registers and also provides the DC restorative level against which all the video signals were measured.

Figure 5 The RC1024S analogue video processing circuitry for the photodiode arrray

Analogue signal conditioning includes charge to voltage conversion and amplification of the signal to provide a 3 Volt output.

In order to use the photodiode array in the direct reader and extend its versatility, several modifications were made to circuitry on the original RC1024S driver board (5). Some of these modifications were left unchanged and the board was incorporated into the redesigned multiple processor system.

Previous features, left unchanged but integrated into the redesigned spectrometer, are the following:

- a) Onboard (RC1024S) semi-automated control over the integration times had been removed and replaced by fully automated microcomputer control.

- b) External (computer) generation of a start pulse to initiate readout of the array.

- c) The relocated photodiode array. It had been removed from the main driver board for mounting in the focal plane of the spectrometer.

- d) The gating circuit designed to gate clocking pulses to the array. In the previous system (5) it was found that fixed pattern background signal saturated the array. This gating circuit reduced this background considerably.

- e) The signal connections to the edge connector of the RC1024S board were maintained as described in reference 5.

f) Reduction of the frequency of the onboard oscillator to facilitate signal acquisition and conversion by a microcomputer

## 2.5 Photodiode Array Cooling

PDA's require cooling to reduce their integrated dark current. Four Peltier (17) heat pumps are used for this purpose. These are attached to the array and electrically connected in series (5). Each array cooling system draws 2 amps at 6V. Cooling water is used to remove 18.24 Watts or 4.4 calorie/sec of heat from the hot side of the Peltiers. To keep the array temperature fluctuations less than 1°C a water flowrate of at least 5 ml/s is required. To supply this flow to several arrays simultaneously, without creating high back pressure, the water is drawn in parallel from a manifold (5).

## 2.6 Photodiode Array Mount and Carriage

The photodiode array and cooling system is mounted on a carriage (Figure 6). This carriage clamps to the mounting rack which previously carried the exit slits for the PMT detection system.

Using this carriage and mounting rack the photodiode array has three degrees of freedom on the Rowland circle, all of which are essential for finding and optimizing the spectral signal. The array can be moved vertically to allow it to be positioned for maximum spectral line intensity and horizontally towards and away from the grating to achieve focus. There is also a rotational adjustment about the axis normal to the Rowland circle. This latter adjustment, is used to align the photodiodes with the images of the entrance slit in the direct reader focal plane.

The array is kept tangential to the Rowland circle by two steel pins which are held in contact with the edge of the mounting rack.

- 1. Mask to control dry nitrogen

- 2. Photodiode array

- 3. Peltier cooled copper plate

- 4. Peltier cooler.

- 5. Water cooled copper plate

- 6. DIP socket

- 7. Array mount and stand-offs

- 8. Vertical adjustment

- 9. Rotation adjustment

- 10. Original exit slit mounts

- 11. Horizontal Focussing adjustment

Figure 6 The photodiode array, its carriage and cooling system as configured in the direct reader

#### CHAPTER 3

#### HARDWARE DESIGN

3.1 Interfacing the Photodiode Array to the Single-Board Computer.

The system incorporates a Reticon 128 element photodiode array. The photodiode array was originally mounted on and driven by the RC1O24S driver board. The board was supplied with the array by Reticon (18).

This driver board had been modified (5) to allow the photodiode array to operate a short distance away from the RC1024S board. In this configration he photodiode array is connected to the driver board by a ribbon cable. This allowed the photodiode array to be placed in the focal plane of the spectrometer as is shown schematically in Figure 2.

The new data acquisition system (Figure 3) is based on an appropriate single-board (John Bell 64K) computer functioning as a "slave" intelligent peripheral to the Apple II+ "master" or "frontend" computer. The Apple II+ "front-end" computer functions as the user interface and system controller. The features of the single-board computer are listed in Table 1.

The single-board computer was interfaced to both a high speed successive approximation analogue-to-digital converter and to the Apple II+. This prototype system was used to determine the operating characteristics of a dual processor system (i.e., "front end" microcomputer user interface plus the single-board computer based data acquisition system) for data intensive applications such as, the sequential acquisition of multiple

photodiode array generated spectra and for the acquisition of the spectra of transient signals.

The construction of this prototype was the essential first step in the development of the multiple processor based PDA spectrometer. From the start it was endeavoured to put all PDA operating parameters and its control requirements under software control.

| 1. | AIM 65 bus (Rockwell Corporation).            |

|----|-----------------------------------------------|

| 2. | 6502 central processing unit.                 |

| 3. | Two user available 6522 PIAs.                 |

| 4. | 6850 ACIA and an RS232 serial interface.      |

| 5. | 8K of erasable programmable read only memory. |

| 6. | 55K of random access memory.                  |

| 7. | 1K of user address space.                     |

TABLE 1 Features of the John Bell Single-Board Computer.

The detection and data collection systems include the following components:

- 1. The photodiode array.

- 2. The photodiode array carriage and its ribbon cable.

- 3. The photodiode array driver board RC1024S.

- 4. The supplementary circuits to gate the oscillator, modify the data acquisition control pulses and to convert RS232 signals to RS232C levels.

- 5. The analogue filter and pre-amplifier.

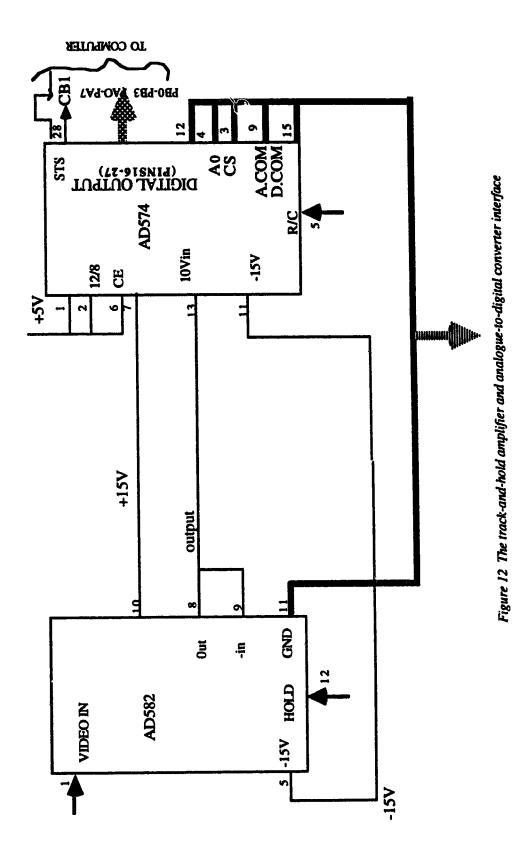

- 6. The analogue-to-digital converter complete with track-and-hold amplifier.

- 7. The single-board, 64K computer.

The removal of the photodiode array from its driver board and the construction of the photodiode array carriage has been previously described (5). In the following sections, the additional interfaces and modifications required to make the dual processor system functional, are described.

## 3.1.1 Interfacing the Gating Circuit to the Single-Board Computer

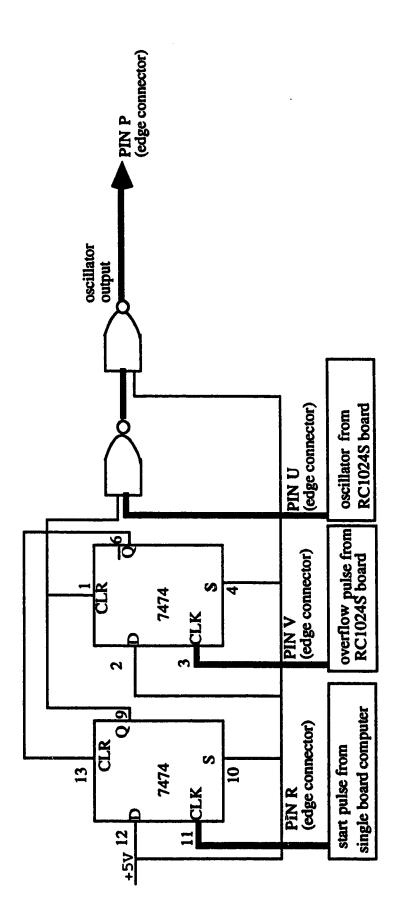

In the previous photodiode array direct reader (5), it was found that due to the photodiode array being operated some distance away from the RC1024S driver board, an unusual interfering background signal appeared. The magnitude of this background signal was almost proportional to the number of oscillator periods which made up the integration time. After this conclusion was reached a gating circuit (Figure 7) was designed to stop these pulses reaching the array during the integration time. This gating circuit reduced the background problem significantly.

This gate consists of a dual edge triggered D type flip-flop and a quad NAND gate 7400. The D and S inputs of both flip-flops are held at a high logic level. In this mode, a rising edge at the clock input of either flip-flop causes the respective Q output of that flip-flop to go high. The Q output of the first flip-flop is the gate control. It goes high and opens the gate when the flip-flop is clocked by a rising edge of the start pulse input from the sirgle-board computer. When readout has been completed the overflow pulse from the RC1024S board clocks the second flip-flop sending its Q output high and its complementary Q output low. This Q output clears the first flip-flop which closes the gate and then closes the second flip-flop.

Figure 7 Gating circuit for the RC1024S onboard oscillator.

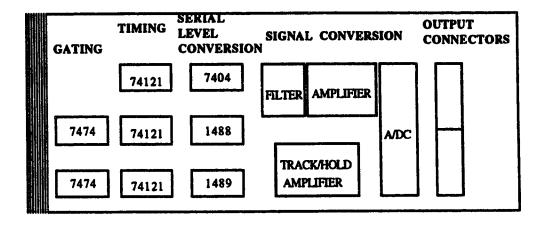

This gating circuit was integrated with the new data-acquisition system (Figure 8). It was built on a separate circuit board and piggy-backed onto the auxiliary circuit board. The auxiliary circuit board also housed the circuits for the analogue filters and preamplifier, the analogue-to-digital converter, the sample-and-hold amplifier and monostables for the treatment and generation of control signals required for the analogue-to-digital conversion.

This gating technique limits to some extent, the flexibility of the photodiode array acquisition system. This is due to its utilisation of the RC1024S onboard oscillator. This oscillator produces a fixed frequency, independent of the data acquisition and control computer. It was a goal of the present work that the oscillator for the system would be placed under the software control of the single-board computer. This it was hoped would facilitate variable frequency clocking and clock stopping (13) techniques with with the arrays.

A new oscillator gating technique was implemented which eliminated the use of the onboard oscillator and replaced its function with timer T1 of 6522 VIA#2 on the single-board computer. One software programmable mode of operation for the above timer is a free running mode, whereby the 1.22MHz oscillator on the single-board computer is utilized to produce a variety of programmable output frequencies.

The frequency of the new oscillator could be varied, under software control and using parameters transmitted to the single-board computer from the Apple II+ user interface. The software was designed to allow clocking of the array during readout. The oscillations were terminated when the computer sensed that the array had been read out (i.e., when data from 128 diodes has been

digitized). The hardware based oscillator gate for the RC1024S onboard oscillator (Figure 7) now became unneccessary.

Interfacing the new oscillator to the photodiode array system involved connecting the programmable oscillator output on PB7 of the 6522 VIA#2, to the clock input on the RC1024S array driver board. Timer 1 on this VIA generates a square wave, which is output on PB7 and used as the oscillator.

Regretably, although this computer generated oscillator functioned satisfactorily in the dual processor system, the software neccessary for this mode of operation was not adequately debugged when the multiple processor system was finally constructed. Therefore it was decided to delay the introduction of this method of array clocking for the entire system and to rely, temporarily at least, on the hardware gated oscillator, previously described.

Software subroutines which initiate the 6522 based oscillator, thereby providing a 10kHz square wave on PB7 are nevertheless included in the main EPROM program for all data acquisition units. To reactivate this clocking method, it is simply neccessary to call these subroutines from the main program, to reconnect PB7 to pin P of the RC1024S edge connector and to disconnect the gated oscillator which is output from the hardware gate. These subroutines can start the oscillator just before data acquisition commences, and stop it after the array has been read out.

It is necessary to provide a start pulse for the photodiode array before readout commences. This serves both to connect the control section of the RC1024S board to the oscillator and to cut off the blank restorative signal (i.e., the signal that is sent out over the video lines when no photodiodes are being read out).

Figure 8 Interface of single board computer to the gating circuit.

After the integration time has elapsed this start pulse is generated through PB4 of 6522 #1. This pulse clocks the output of a 7474 flip flop high on the RC1024S board (Appendix 1). This pulse also connects the gated oscillator to the control system on the RC1024S board (Figure 7). The readout control system of the driver board then generates the sampling and control pulses from this clock. As soon as one of these timing pulses, called \$2 ODD goes low for the first time it clears the onboard 7474 flip-flop sending its output low. This high-to-low transition is used as the trigger for the computer to start data acquisition. On the array driver board this pulse is simultaneously, inverted and converted to MOS logic levels by the MH0026 and acts to trigger readout of the photodiode array. The complementary output of this onboard 7474 flip-flop goes high and clocks a second RC1024S 7474 flip-flop which cuts of the blank restorative signal.

Two sampling pulses are generated before readout of the photodiodes commence but these are ignored by the data acquisition system, since they occur prior to the trigger signal from the RC1024S board.

When the last photodiode is read out, the photodiode array sends out an end of line signal. This is transferred to a shift register on the RCi024S board where it remains until the next even sample pulse is generated. This sample pulse clocks the shift register, thereby clearing the 7474 flip-flop which controls the blank restorative level. This takes a further two sampling pulses implying that 132 sampling pulses must be generated in total to read out the 128 element photodiode array. The signal timing sequences for the start and at the end of readout, are given in Appendices 2 and 3 respectively.

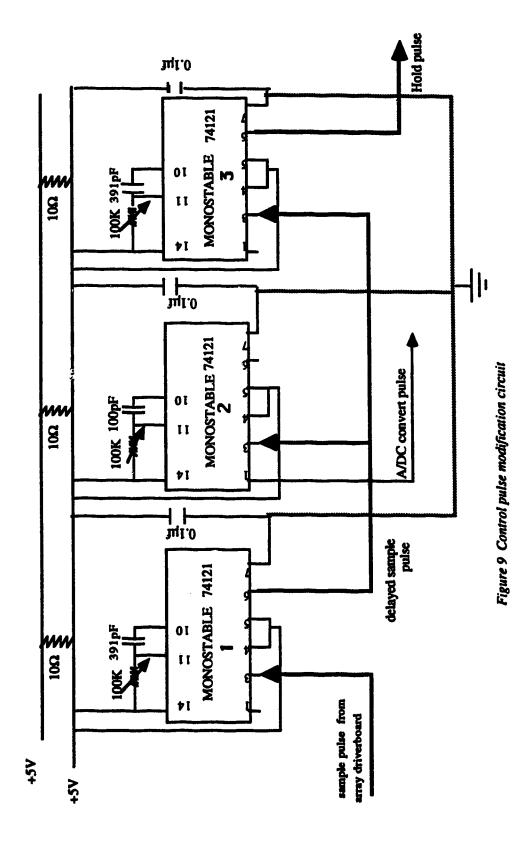

## 3.1.2 Control Pulses for Data Acquisition.

Due to modifications previously made to the photodiode array driver board, the differential readout of active and dummy photodiodes does not function well. This differential readout attempts to minimize switching transients as photodiodes are coupled in turn onto the video output lines. Therefore it is necessary to delay the data acquisition pulse to allow the signal to be digitized and acquired when these switching spikes have passed. The pre-amplifier and the low - pass filter amplifier tend to dampen the sharp transitions in the analogue signal (e.g., switching spikes). Evans (5) gave an example for a photodiode array sampled at 50kHz or 20 µs per photodiode. Of this 20µs, the switching spike takes up about 7 µs. The present filter/amplifier circuit is similar in design to that described by Evans (5) and therefore exhibits similar features. Allowance for an adjustable delay to be applied to the signal sampling and conversion pulses of greater than 10 µs is designed into the present system.

Separate trains of sampling pulses are generated on the RC1024S circuit board for the odd and even photodiodes. These are logically OR'd together and appear on an edge connector tab (W) on the circuit board. The period of these pulses is dependent on the frequency of the oscillator. These are the pulses which are modified to eliminate switching transients by providing a delayed "hold" signal for the track-and-hold amplifier and a delayed convert pulse for the analogue-to-digital converter (ADC). The delays imposed on these pulses allow the system to perform analogue-to-digital conversions only when the video signal is stable.

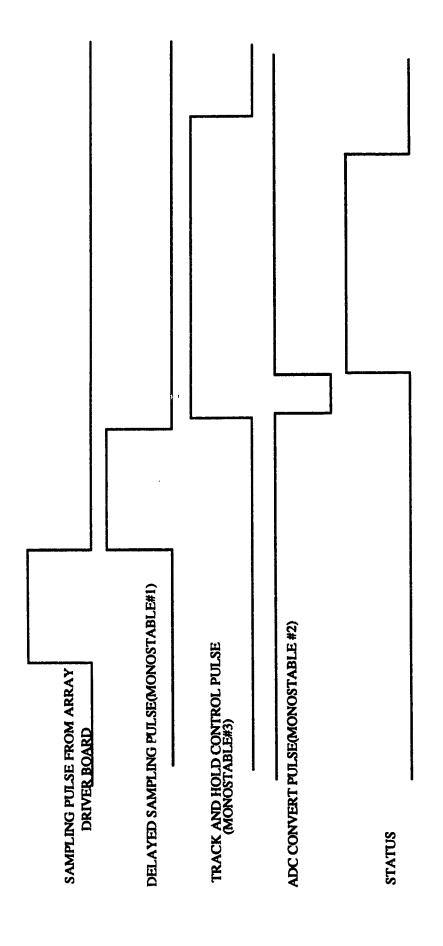

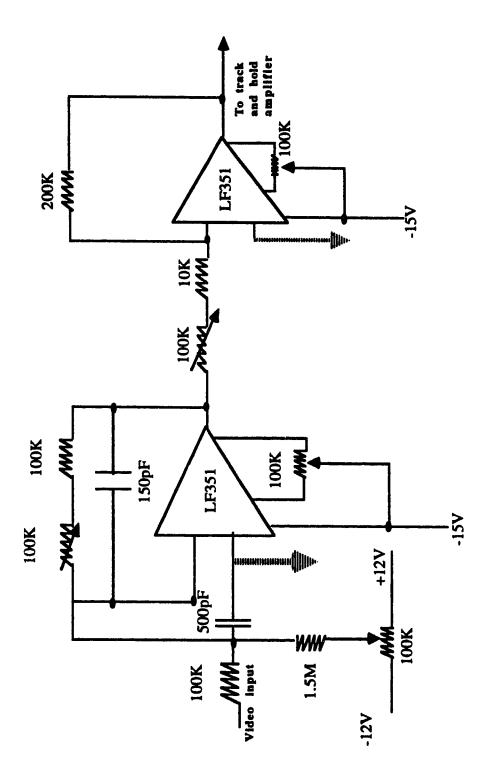

The timing circuit (Figure 9) used to modify the sampling pulses and generate the required "hold" and "convert" signals for data conversion consists of three 74121 monostables.

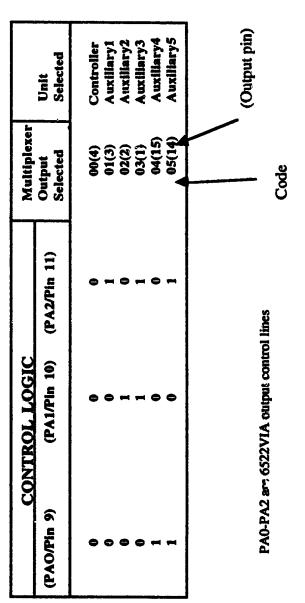

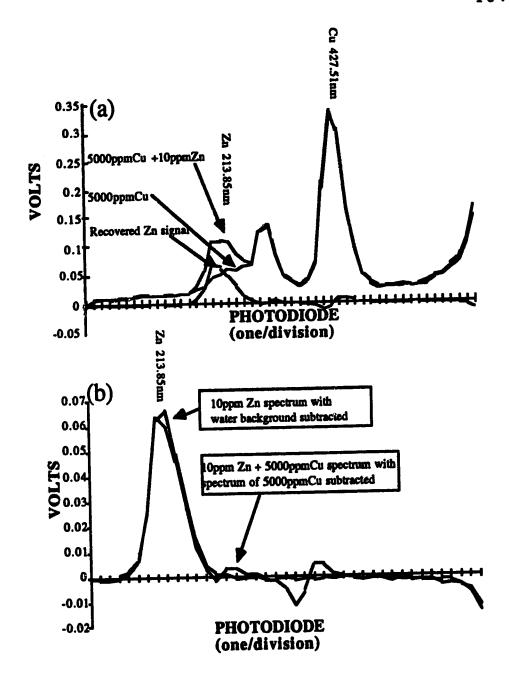

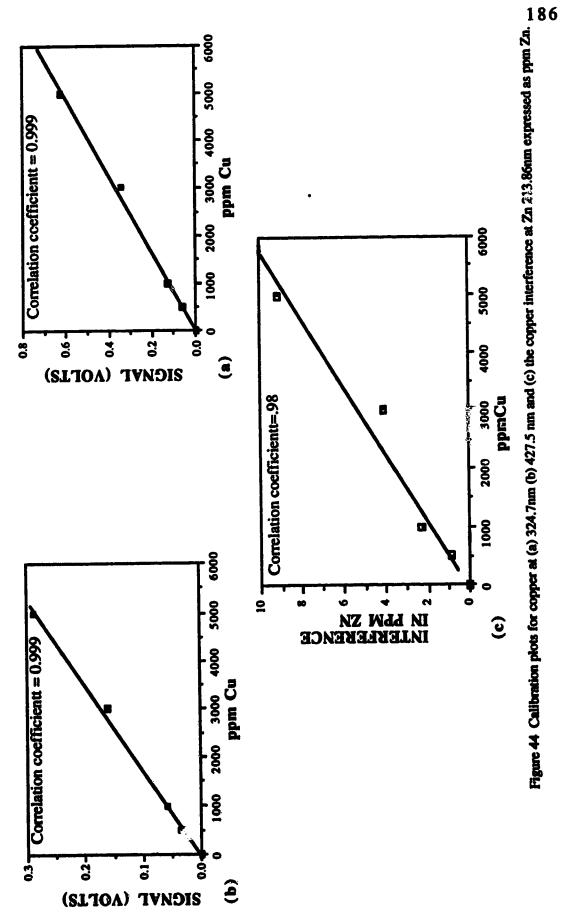

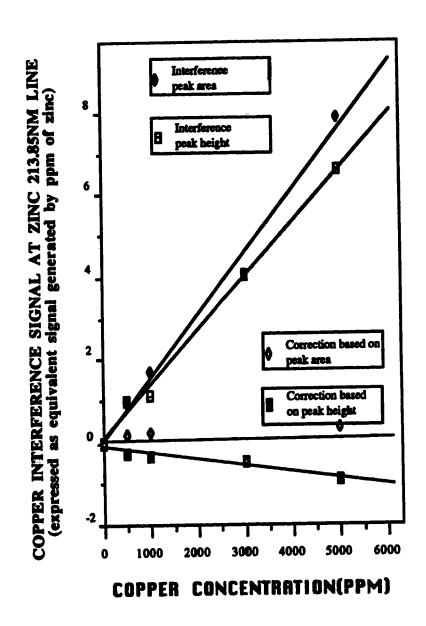

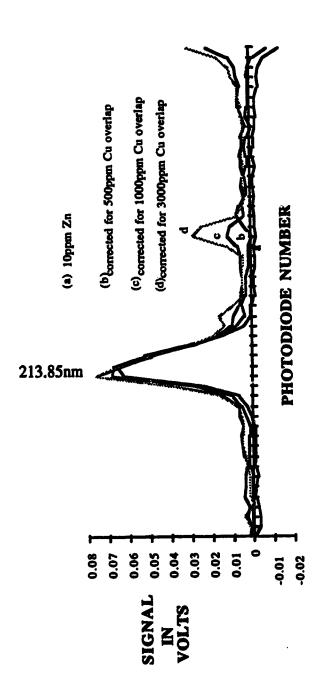

On receipt of a negative transition on the sampling pulse originating from the RC1024S board, the output of the delay monostable (#1) goes high, it remains high for a duration determined by the 391 pF capacitor and the timing resistors. The variable resistance used here allows control over the delay time which can be adjusted and optimised.