## **University of Alberta**

A Power Evaluation Study for an 802.16e LDPC Encoder Implementation with Wireless Implantable Medical Devices

by

Samer Chomery

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of

Master of Science

Department of Electrical and Computer Engineering

Edmonton, Alberta Fall 2008

Library and Archives Canada

Published Heritage Branch

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque et Archives Canada

Direction du Patrimoine de l'édition

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 978-0-494-47190-6 Our file Notre référence ISBN: 978-0-494-47190-6

#### NOTICE:

The author has granted a non-exclusive license allowing Library and Archives Canada to reproduce, publish, archive, preserve, conserve, communicate to the public by telecommunication or on the Internet, loan, distribute and sell theses worldwide, for commercial or non-commercial purposes, in microform, paper, electronic and/or any other formats.

The author retains copyright ownership and moral rights in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

#### AVIS:

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, publier, archiver, sauvegarder, conserver, transmettre au public par télécommunication ou par l'Internet, prêter, distribuer et vendre des thèses partout dans le monde, à des fins commerciales ou autres, sur support microforme, papier, électronique et/ou autres formats.

L'auteur conserve la propriété du droit d'auteur et des droits moraux qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

# To My Parents

#### Abstract

Low-density parity-check (LDPC) codes are forward error control (FEC) codes that are being increasingly adopted in emerging communication systems due to their ability to provide capacity approaching coding performance and the availability of practical VLSI implementations. Low-time-complexity encoding of LDPC block codes has been a challenge. The LDPC codes supported in the 802.16e (mobile WiMAX) standard are designed to take advantage of efficient time and circuit encoding techniques. This thesis explores the design and implementation of an LDPC encoder that is compatible with the 802.16e standard.

Wireless implantable medical devices (IMDs) are an important emerging communications application. One design challenge of IMDs is the low-power consumption required to achieve the necessary battery life. This thesis evaluates the power consumption of the implemented LDPC encoder for use in implant wireless transmit data links. To achieve the necessary power efficiency we need a lower power implementation than the FPGA encoder presented.

## Acknowledgments

First and foremost, I would like thank the Lord for blessing me and for providing me with a wonderful life, and especially for the opportunity to pursue my education and career in Canada.

Second, I am grateful to my parents, Esam and Aysar Chomery, for the love and support they've given me all my life, and for their sacrifices without which I wouldn't be where I am today. I thank my brother Ziyad who was always there for me to talk to and watch sports with. I am very thankful to my fiancé Dima Oweis, who stood by me every step of my graduate program and helped and encouraged me during the difficult times. Thank you for your love.

Third, I wish to express my immense gratitude to my supervisors, Dr. Stephen Bates for his guidance, advice, patience, and for sharing his knowledge and technical insights with me. I am also grateful to my co-supervisor Dr. Duncan Elliott, who provided guidance and many contributions to my learning experience.

Fourth, I would like to show my appreciation to everyone at TRLabs; Dr. John Nielsen, Dr. Robert (Bob) Davies, Dr. Grant McGibney, and the support staff at the Calgary lab who helped introduce me the field of wireless communications and encouraged me to pursue further research opportunities. I thank everyone at the Edmonton lab for providing all the learning resources I needed and an excellent working environment. An additional thank-you goes to Luke Chong for making sure my computing experience always ran smoothly.

Fifth, my appreciation goes out to all my friends and colleagues at the Department of Electrical and Computer Engineering at the University of Alberta and TRLabs for the many helpful discussions and late night work-and-pizza sessions.

I'll finish by giving thanks to the organizations and institutions whose financial aid has been instrumental in allowing me to do this work. To NSERC, TRLabs, and the University of Alberta I am humbly grateful.

# Table of Contents

| 1 Introduction and Thesis Overview                             |

|----------------------------------------------------------------|

| 1.1 Project Overview1                                          |

| 1.2 Thesis Overview                                            |

| 2 Background and Literature Review                             |

| 2.1 Information Theory and Channel Coding                      |

| 2.2 Low-Density Parity-Check Codes                             |

| 2.2.1 Introduction                                             |

| 2.2.2 Overview of LDPC codes                                   |

| 2.2.2.1 LDPC Code Structure                                    |

| 2.2.2.2 Decoding and Current Implementations15                 |

| 2.2.2.3 Encoding and Current Implementations                   |

| 2.3 Wireless Communications and Low-Density Parity-Check Codes |

| 2.3.1 Brief Overview of Wireless Communications                |

| 2.3.2 The IEEE 802.16 wireless networking standard (WiMAX)26   |

| 2.3.3 LDPC codes in Wireless Communications                    |

| 2.4 Wireless In-Body Medical Communications                    |

| 2.4.1 Overview of In-Body Medical Communications31             |

| 2.4.2 Design and Implementation Challenges of In-Body Wireless |

| Communications                                                 |

| 2.4.3 Current In-body Communication Solutions                  |

| 3.1 Introduction                                                                               |     |

|------------------------------------------------------------------------------------------------|-----|

| 3.2 802.16e LDPC Code Structure                                                                | 51  |

| 3.3 802.16e LDPC Code Performance  3.4 The 802.16e LDPC Encoder Core  3.4.1 Encoding Algorithm | 52  |

| 3.4 The 802.16e LDPC Encoder Core                                                              | 54  |

| 3.4.1 Encoding Algorithm                                                                       | 54  |

|                                                                                                |     |

| 3.4.2 Encoder Design and Implementation Flow                                                   | 5   |

|                                                                                                |     |

| 3.4.3 Encoder Top-Level Design                                                                 | 59  |

| 3.4.4 Software Implementation and Modeling                                                     | 63  |

| 3.4.5 Hardware System Components                                                               | 69  |

| 3.4.5.1 The Block Multiplier                                                                   | 72  |

| 3.4.5.2 The Full Matrix-Vector Multiplier                                                      | 78  |

| 3.4.5.3 The $ET^{I}$ , $T^{I}$ Matrix Multiplier                                               | 81  |

| 3.4.5.4 Memory Storage and Controllers                                                         | 85  |

| 3.4.5.5 The Master Finite State Machine                                                        | 90  |

| 3.5 Summary                                                                                    | 94  |

| 4 Encoder Verification and Performance Analysis                                                | 96  |

| 4.1 Encoder IP Core - Description and Usage                                                    | 90  |

| 4.2 Simulation and Testing Method                                                              | 101 |

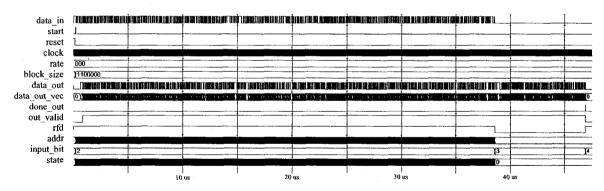

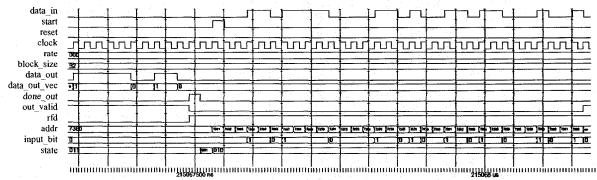

| 4.3 Behavioral Simulations                                                                     | 103 |

| 4.4 Timing Simulations                                                                         | 105 |

| 4.5.1 Hardware Resource Utilization                                 | 108 |

|---------------------------------------------------------------------|-----|

| 4.5.2 System Throughput                                             | 109 |

| 4.6 Hardware on-chip Testing                                        | 110 |

| 4.7 Summary                                                         | 115 |

| 5 LDPC Encoders for In-Vivo RF Communications                       | 116 |

| 5.1 Introduction                                                    | 116 |

| 5.2 Power Measurement Tools                                         | 116 |

| 5.3 Power Measurements of the 802.16e LDPC Encoder                  | 119 |

| 5.4 The Convolutional LDPC Encoder                                  | 121 |

| 5.4.1 Introduction to the Convolutional Encoder Implementation      | 121 |

| 5.4.2 Power Measurements of the Convolutional LDPC Encoder          | 125 |

| 5.5 Power Consumption Comparison of the LDPC-BC and LDPC-CC         |     |

| encoders                                                            | 126 |

| 5.6 LDPC Encoders Analysis for Wireless Implantable Medical Devices | 130 |

| 5.6.1 Power Efficiency of LDPC Encoders for Wireless In-Body        |     |

| Communications                                                      | 130 |

| 5.6.2 Comparisons with Industry Leading IMDs                        | 140 |

| 5.7 Power Consumption Improvements                                  | 142 |

| 5.8 Summary                                                         | 143 |

| 6 Conclusions and Future Work                                       | 145 |

| 6.1 Project Results and Analysis                                    | 145 |

| 6.2 Future Work                                                     | 147 |

| Bibliography                                                        | 149 |

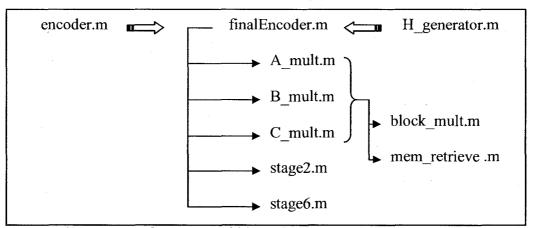

| A MATLAB Modules for Software Modeling and Processing | 161 |

|-------------------------------------------------------|-----|

| A.1 Encoder.m                                         | 161 |

| A.2 finalEncoder.m                                    | 162 |

| A.3 stage2.m                                          | 165 |

| A.4 stage6.m                                          | 165 |

| A.5 A_mult.m                                          | 166 |

| A.6 block_mult.m                                      | 167 |

| A.7 mem_retrieve.m                                    | 167 |

| A.8 H_generator.m                                     | 169 |

| A.9 Accuracy_driver.m                                 | 172 |

| A.10 verify_accuracy.m                                | 172 |

| A.11 check_allvalues_script.m                         | 173 |

| A.12 A_firstcol_maker.m                               | 174 |

| A.13 A_other_col_maker.m                              | 176 |

| A.14 AB_mem_checker.m                                 | 177 |

| A.15 input_generate.m                                 | 179 |

| A.16 packet_compare.m                                 | 179 |

| A.17 Encoder_script.m                                 | 179 |

| B Testing and Verification VHDL Modules               | 181 |

| B.1 Encoder_tb.vhd                                    | 181 |

| B.2 Encoder_tb_packet.vhd                             | 185 |

| B.3 TopLevel.vhd                                      | 187 |

| C Comprehensive Behavioral Simulation Waveforms       | 194 |

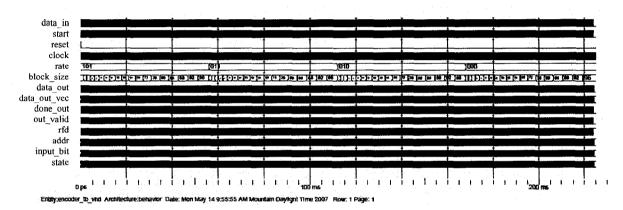

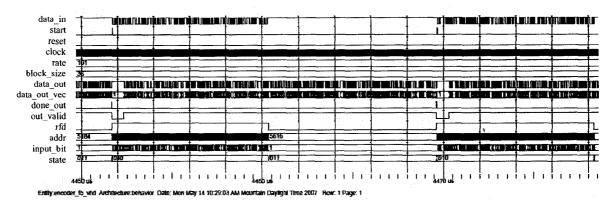

|   | C.1 Waveform of the full behavioral simulation test                     | . 194 |

|---|-------------------------------------------------------------------------|-------|

|   | C.2 Waveform illustrating the encoder working with rate 1/2             | . 194 |

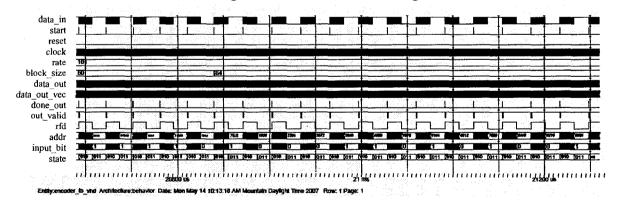

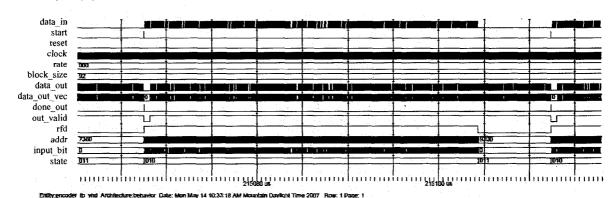

|   | C.3 Waveform of full packet encoding at code rate 1/2 and block size 36 | . 195 |

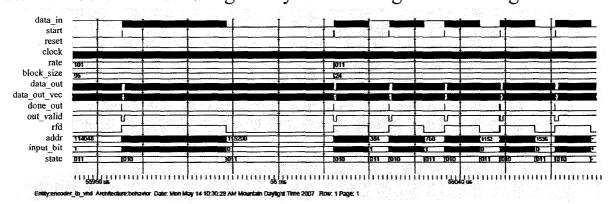

|   | C.4 Waveform of full packet encoding at code rate 5/6 and block size 92 | . 195 |

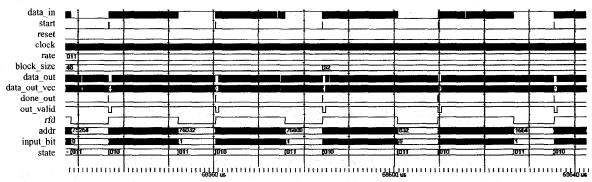

|   | C.5 Waveform illustrating the dynamic change of encoding rate           | .195  |

|   | C.6 Waveform illustrating the dynamic change of block size              | . 196 |

|   | C.7 Waveform illustrating a packet-to-packet transition                 | . 196 |

| Г | C++ Hardware Test and Control File                                      | . 197 |

## List of Tables

| Table 3.1: 802.16e supported LDPC code rates and lengths                             |

|--------------------------------------------------------------------------------------|

| Table 3.2: Three approaches to storing the A, B, and C sub-matrices                  |

| Table 3.3: Summary of the encoder's Block RAM memory components                      |

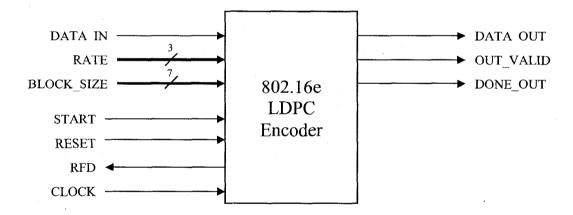

| Table 4.1: System signal pinout                                                      |

| Table 4.2: Spartan-3 XC3S1500 device utilization for LUT-based implementation 108    |

| Table 4.3: Spartan-3 XC3S1500 device utilization for multiplier-based implementation |

|                                                                                      |

| Table 4.4: Maximum clock frequency as reported by implementation stages              |

| Table 4.5: 802.16e LDPC encoder throughput for all supported packet lengths at 80MHz |

| clock rate                                                                           |

| Table 5.1: 802.16e LDPC encoder power estimates, power in (mW)                       |

| Table 5.2: LDPC-CC encoder power estimates, power in (mW)                            |

| Table 5.3: LDPC-CC vs. 802.16e LDPC encoder power results for rate 1/2, power in     |

| (mW)                                                                                 |

| Table 5.4: Convolutional encoder power gain (savings) based on dynamic power         |

| consumption                                                                          |

| Table 5.5: FPGA resource utilization comparison, Spartan 3 – package 3s1500fg320 128 |

| Table 5.6: Parameters used in power calculations                                     |

# List of Figures

| Figure 2.1: Simplified model of a communication system                                  |

|-----------------------------------------------------------------------------------------|

| Figure 2.2: Codeword structure of a systematic block code                               |

| Figure 2.3: Example of a parity-check matrix [5]                                        |

| Figure 2.4: Parity-Check matrix for (20, 3, 4) LDPC code                                |

| Figure 2.5: An example of a (2,3) regular LDPC code and its bipartite (Tanner) graph 16 |

| Figure 2.6: A matrix in almost lower triangular (ALT) form                              |

| Figure 2.7: An example of the internal structure of a matrix composed of circulant      |

| identity matrices, modified from [36]                                                   |

| Figure 2.8: Spectral efficiency and sector throughput comparison of HSPA, EVDO-Rev.     |

| B, and Mobile WiMAX under the same traffic conditions [52]27                            |

| Figure 2.9: Performance of un-coded and LDPC coded OFDM and spread OFDM                 |

| (SOFDM) systems in Typical Urban wireless channel, BPSK, $R = 1/2$ , $N = 1024$ [54] 28 |

| Figure 2.10: 802.16e supported FEC codes comparison, $R = 1/2$ , $N = 576$ [59]30       |

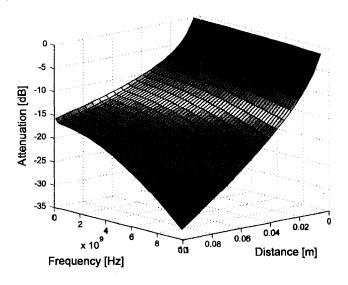

| Figure 2.11: Measured body attenuation data vs. frequency and distance [69]35           |

|                                                                                         |

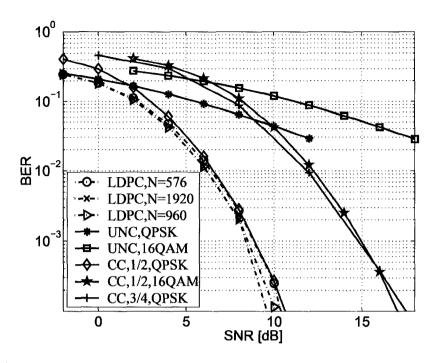

| Figure 3.1: FEC codes comparison, BER, AWGN, R=1/2, N=576 [59]52                        |

| Figure 3.2: FEC codes comparison, BER/FER , TU30, R=3/4, N=576 [59]52                   |

| Figure 3.3: FEC codes comparison, BER, TU30, various code rates and lengths [59] 53     |

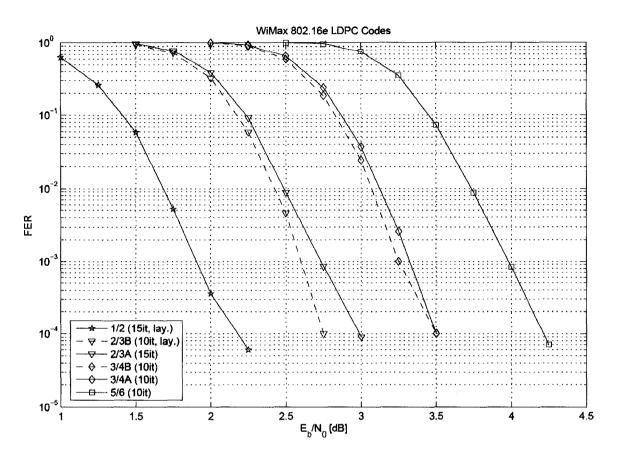

| Figure 3.4: FER performance of WiMAX LDPC decoder implementation from [83] 54           |

| Figure 3.5: The parity-check matrix H in almost lower triangular form                   |

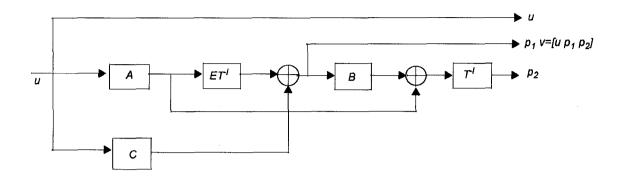

| Figure 3.6: Block diagram of the encoding algorithm for the block LDPC code [10] 57     |

|   | Figure 3.7: Encoder design flow chart                                                              | 57   |

|---|----------------------------------------------------------------------------------------------------|------|

|   | Figure 3.8: Top-level block diagram of 802.16e LDPC Encoder                                        | 59   |

|   | Figure 3.9: Software model hierarchy for 802.16e LDPC encoder                                      | 63   |

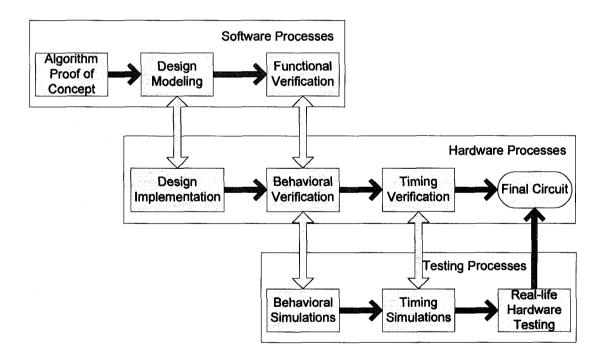

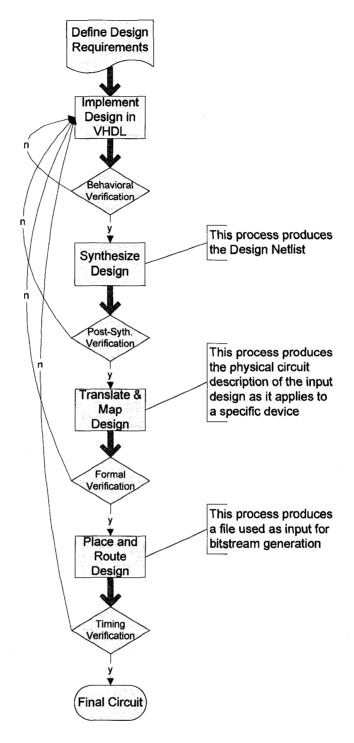

|   | Figure 3.10: The VHDL design flow                                                                  | 70   |

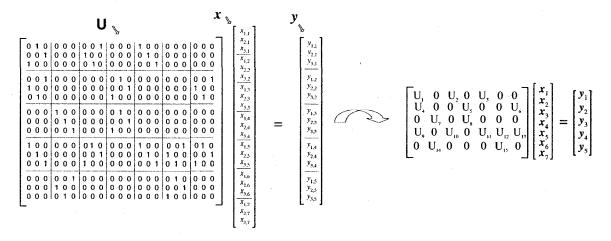

|   | Figure 3.11: Matrix-vector multiplication illustration [36]                                        | 72   |

|   | Figure 3.12: An identity matrix shifted once, produces a vector that is shifted once               | 73   |

|   | Figure 3.13: After the intermediate vectors are shifted, they are compounded through               | n    |

| · | addition to produce the row result                                                                 | 73   |

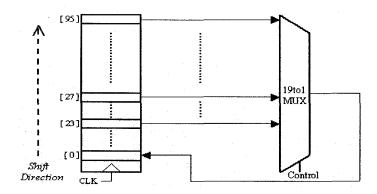

|   | Figure 3.14: Shift-register based block multiplier                                                 | 74   |

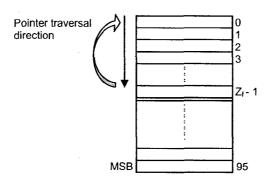

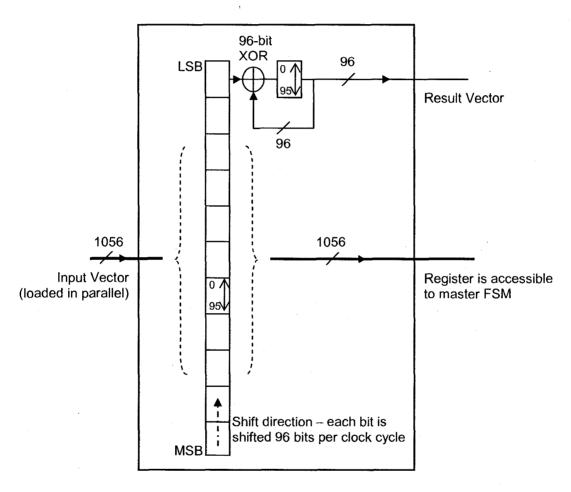

|   | Figure 3.15: 96-bit register with a circular pointer                                               | 75   |

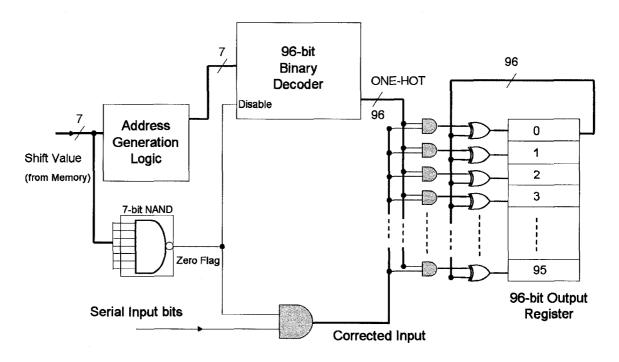

|   | Figure 3.16: The circular-pointer based block multiplier                                           | 77   |

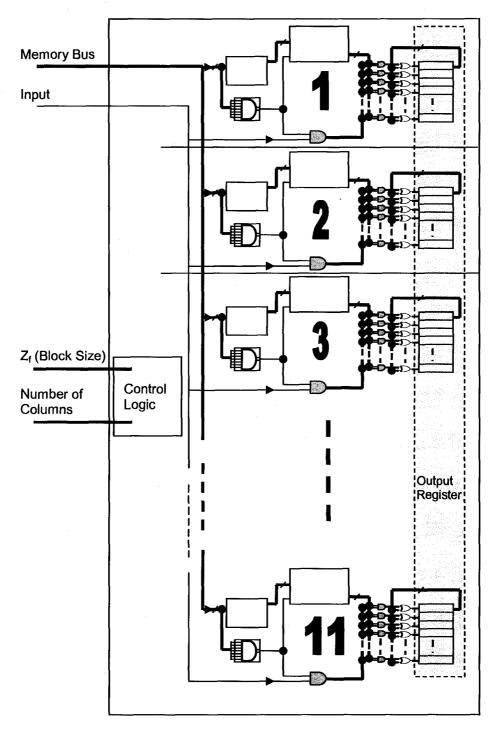

|   | Figure 3.17: The full matrix-vector multiplier                                                     | 79   |

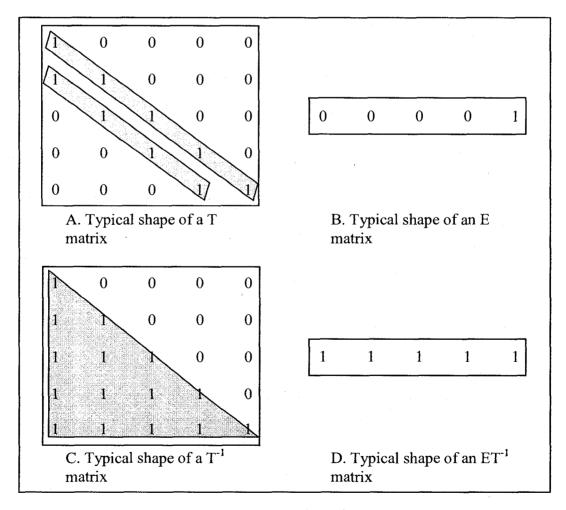

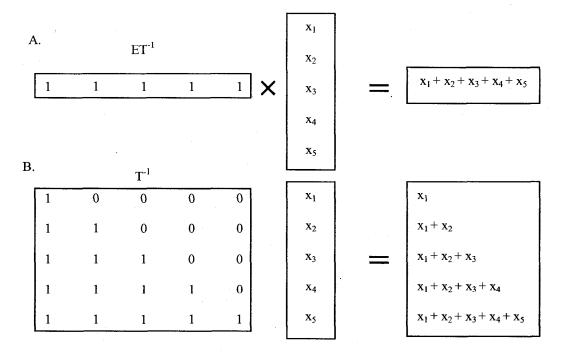

|   | Figure 3.18: Typical shapes of T, E, T <sup>-1</sup> , ET <sup>-1</sup> matrices for code rate 3/4 | 81   |

|   | Figure 3.19: Multiplying a vector by each of ET <sup>-1</sup> and T <sup>-1</sup>                  | 82   |

|   | Figure 3.20: The large-shifter multiplier.                                                         | 83   |

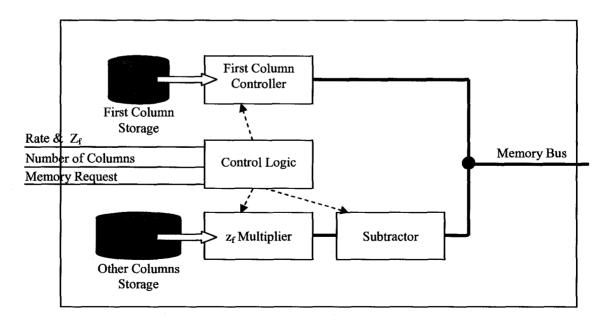

|   | Figure 3.21: The memory controller component                                                       | 87   |

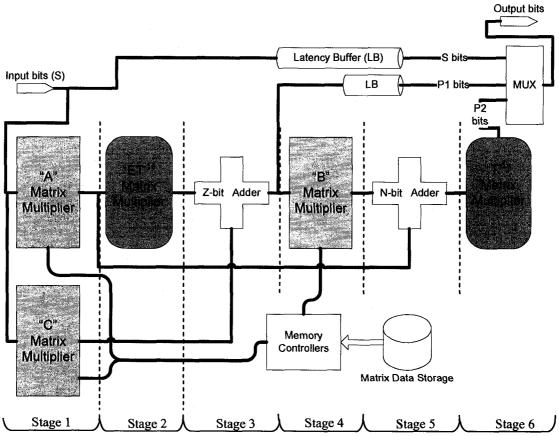

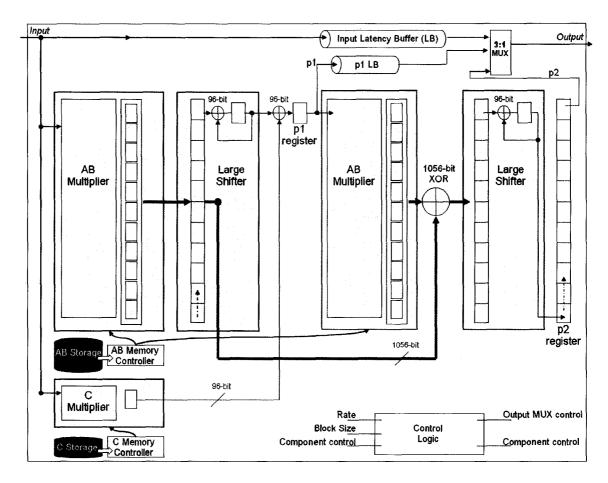

|   | Figure 3.22: 802.16e LDPC Encoder System (top-level) Diagram                                       | 91   |

|   |                                                                                                    |      |

|   | Figure 4.1: 802.16e LDPC encoder core block diagram                                                | 96   |

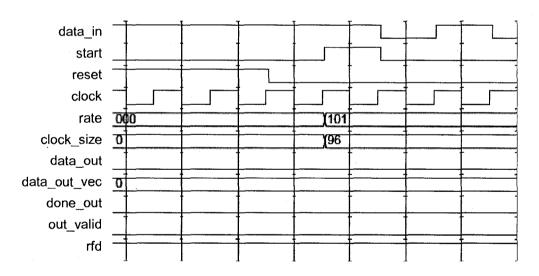

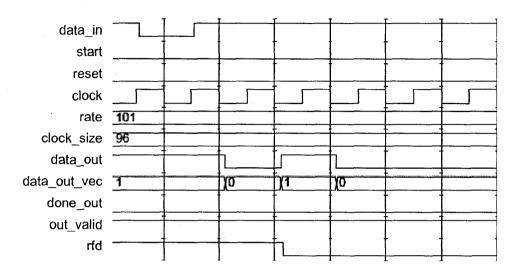

|   | Figure 4.2: Behavior of START signal during encoding of a rate 1/2, block size 96 i                | nput |

|   | packet                                                                                             | 98   |

|   | Figure 4.3: RFD Signal on end of input packet, code rate 1/2, block size 96                        | 99   |

|   | Figure 4.4: OUT_VALID Signal and the 32-cycle latency, code rate 5/6, block size                   | 92   |

|   |                                                                                                    | 100  |

| Figure 4.5: DONE_OUT asserted on end of data output, code rate 1/2, block size 96.  | . 100 |

|-------------------------------------------------------------------------------------|-------|

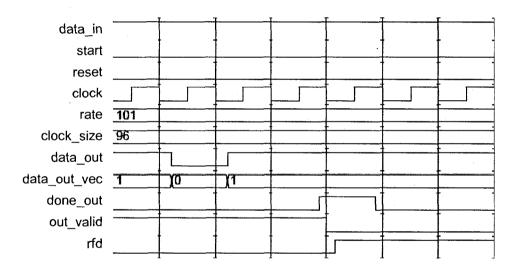

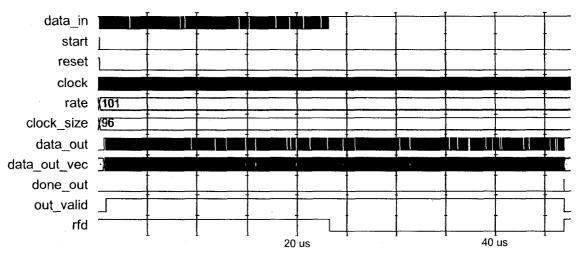

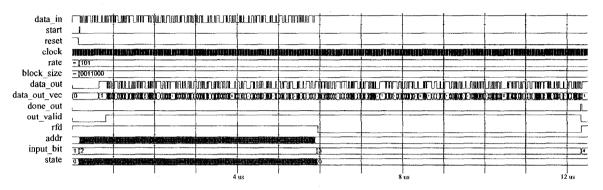

| Figure 4.6: Encoding of one packet with code rate 1/2 and block size 96             | . 101 |

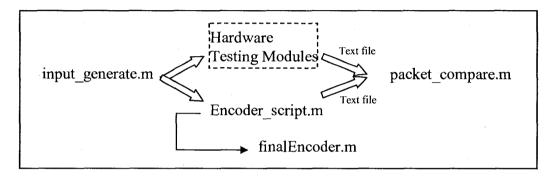

| Figure 4.7: MATLAB testing structure                                                | . 102 |

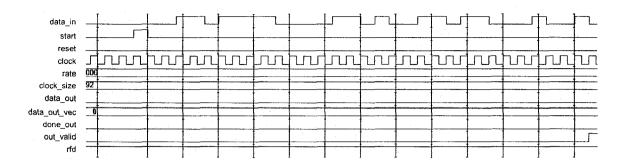

| Figure 4.8: Post place-and-route simulation with code rate 1/2 and block size 24    | . 107 |

| Figure 4.9: Post place-and-route simulation with code rate 5/6 and block size 96    | . 107 |

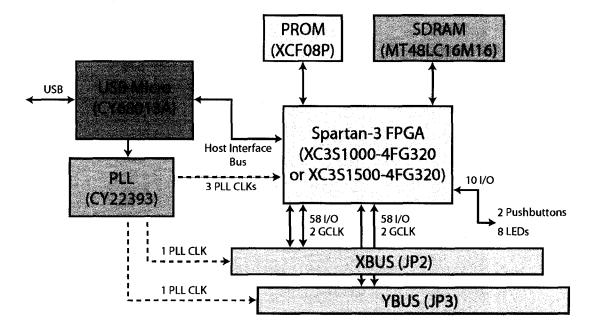

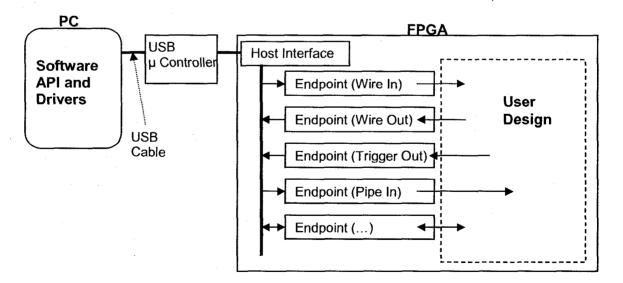

| Figure 4.10: Functional block diagram of the XEM board [88]                         | . 111 |

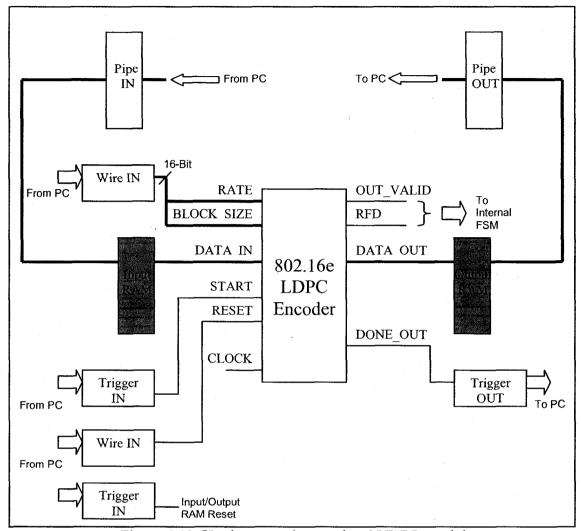

| Figure 4.11: Opal Kelly interface structure                                         | . 112 |

| Figure 4.12: Hárdware testing top-level VHDL module                                 | . 114 |

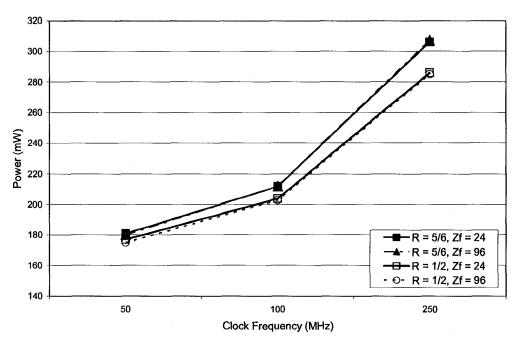

| Figure 5.1: 802.16e LDPC encoder power estimates with rates 1/2 and 5/6, block size | s 24  |

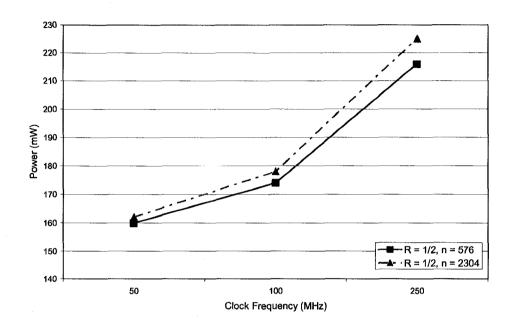

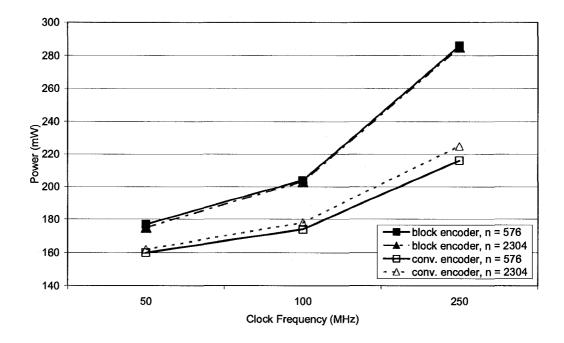

| and 96 at several clock frequencies                                                 | . 121 |

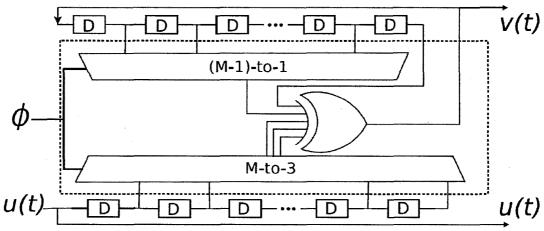

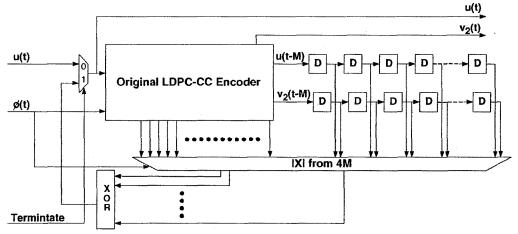

| Figure 5.2: Block diagram of LDPC-CC encoder [91]                                   | . 122 |

| Figure 5.3: Block diagram of termination sequence generation circuit of LDPC-CC     |       |

| encoder [92]                                                                        | . 123 |

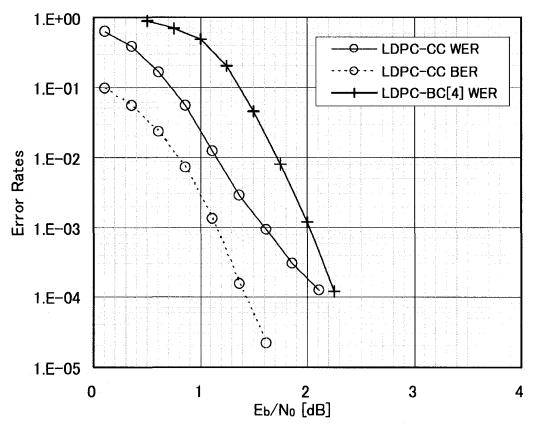

| Figure 5.4: 802.16e LDPC-BC vs. LDPC-CC performance example. (Information bit       |       |

| length = 600 bits), modified from [93]                                              | . 124 |

| Figure 5.5: LDPC-CC encoder power estimates with rates ½ at several clock frequence | cies  |

| · · · · · · · · · · · · · · · · · · ·                                               | . 126 |

| Figure 5.6: LDPC-CC vs. 802.16e LDPC Encoder power results at rate 1/2              | . 127 |

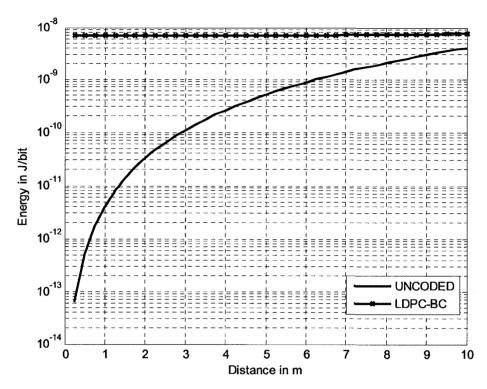

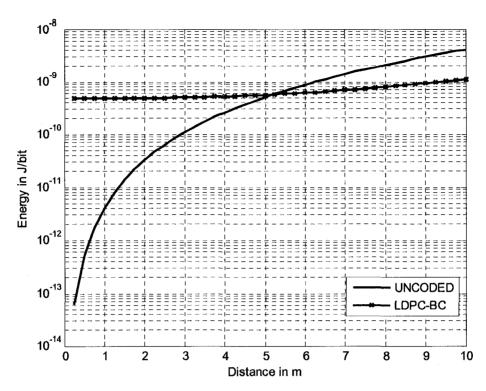

| Figure 5.7: Minimum transmit energy per bit for 802.16e LDPC encoder (FPGA core     | )     |

| compared to an uncoded system, at rate 1/2, frequency 50 MHz                        | . 136 |

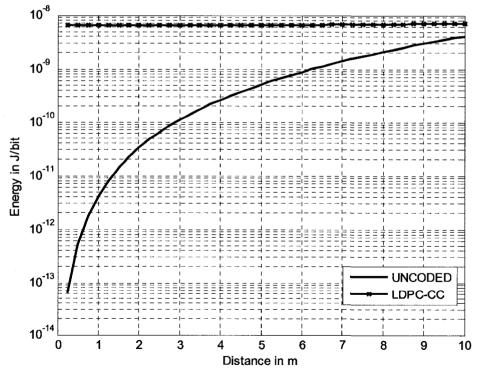

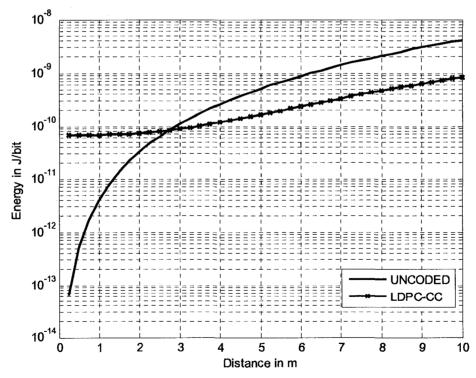

| Figure 5.8: Minimum transmit energy per bit for LDPC-CC encoder (FPGA core)         |       |

| compared to an uncoded system, at rate 1/2, frequency 50 MHz                        | . 136 |

|                                                                                     |       |

|                                                                                     |       |

| Figure 5.9: Minimum transmit energy per bit for LDPC-BC encoder (ASIC estimate)  |  |

|----------------------------------------------------------------------------------|--|

| compared to an uncoded system, at rate 1/2, frequency 50 MHz                     |  |

| Figure 5.10: Minimum transmit energy per bit for LDPC-CC encoder (ASIC estimate) |  |

| compared to an uncoded system, at rate 1/2, frequency 50 MHz                     |  |

## List of Abbreviations

| Symbol | Description                                                   |

|--------|---------------------------------------------------------------|

| 3G     | Third Generation of development in wireless communication     |

|        | networks, especially mobile phone networks                    |

| ALT    | Almost Lower Triangular Form of a Matrix                      |

| ANSI-C | The C language programming standard published by the American |

|        | National Standards Institute                                  |

| API    | Application Programming Interface                             |

| ARQ    | Automatic Repeat-Request Codes                                |

| ASIC   | Application-Specific Integrated Circuit                       |

| AWGN   | Additive White Gaussian Noise Information Channel             |

| BAN    | Body Area Network                                             |

| ВСН    | Bose-Chaudhuri-Hochquenghem Code                              |

| BER    | Bit Error Rate                                                |

| BP     | Belief Propagation                                            |

| BPL    | Body Path-Loss Factor                                         |

| BRAM   | Block Read Access Memory                                      |

| BW     | Bandwidth                                                     |

| CC     | Convolutional Code                                            |

| CDMA   | Code-Division Multiple-Access                                 |

| CRC    | Cyclic Redundancy Check                                       |

| CTC    | Convolutional Turbo Code                                      |

DL

Downlink

**DLL**

Dynamic Link Library

DUT

Device Under Test

DVB-S2

Digital Video Broadcast - Satellite - Second Generation

**ECC**

**Error Control Codes**

**EIRP**

Effective Isotropic Radiation Power

**EM**

Electromagnetic

EVDO-Rev. B

Evolution-Data Optimized - Revision B, a 3G wireless standard

**FCC**

Federal Communications Commission

**FDTD**

Finite-Difference Time-Domain

**FEC**

Forward Error Correction

**FER**

Frame Error Rate

FF

Flip-Flop

**FIFO**

First-In First-Out

**FPGA**

Field-Programmable Gate Array

FSM

Finite State Machine

GF

Galois Field

GUI

Graphical User Interface

**HDL**

Hardware Description Language

**HSPA**

**High-Speed Packet Access**

**IEEE**

Institute of Electrical and Electronics Engineers

**IMD**

Implantable Medical Device

ΙP

Internet Protocol

ISM the Industrial, Scientific and Medical Frequency Band

LAN Local Area Network

LDPC Low-Density Parity-Check Code

LDPC-BC Low-Density Parity-Check Block Code

LDPC-CC Low-Density Parity-Check Convolutinal Code

LLR Log-Likelihood Ratio

LNA Low-Noise Amplifier

LSB Least-Significant Bit

LUT Lookup Table

MAN Metropolitan Area Network

MEMS Microelectromechanical system

METAIDS Meteorological Aids Service

MICS Medical Implants Communication Service

MIMO Multiple-Input Multiple-Output

MSB Most-Significant Bit

MUX Multiplexer

NCD Native Circuit Description File

NICT National Institute of Standards and Technology

OFDM Orthogonal Frequency Division Multiplexing

PAN Personal Area Network

PDA Personal Digital Assistance

PLE Path-Loss Exponent

PLL Phase Lock Loop

QC

Qausi-Cyclic

QoS

Quality of Service

**QPSK**

Quadrature Phase-Shift Keying

RAM

Random Access Memory

RF

Radio Frequency

**RICA**

Reconfigurable Instruction Cell Architecture

**RNF**

Receiver Noise Figure

**SNR**

Signal-to-Noise Ratio

TG6

The WPAN Task Group 6 for Body Area Networks

**TU30**

Typical Urban 30 Information Channel

UL

Uplink

**USB**

Universal Serial Bus

**UWB**

Ultra-Wide Band

**VCD**

Value Change Dump

**VHDL**

VHSIC Hardware Description Language

**VHSIC**

Very High Speed Integrated Circuit

**VLSI**

Very Large-Scale Integration

WAN

Wide Area Network

WiMAX

Worldwide Interoperability for Microwave Access

**WMAN**

Wireless Metropolitan Area Network

**WPAN**

Wireless Personal Area Network

**XOR**

Exclusive-OR

## Chapter 1

#### Introduction and Thesis Overview

### 1.1 Project Overview

Channel coding is a technique used to mitigate the effects of noise on the transfer of information in communication systems. The development of channel codes that achieve good coding performance has been the focus of researchers since the late 1940s. Several code families have been developed that provide effective performance in various communication systems and applications [3]. In today's expanding market of portable wireless communications, it is important for communication vendors to develop low-circuit-complexity channel codes for hardware implementation. Several channel coding classes have recently emerged as high-performance, low-complexity codes such as turbo codes and low-density parity-check (LDPC) codes [4]. These codes are quickly becoming the coding techniques of choice for emerging wireless communication systems.

LDPC codes provide comparable coding performance to the widely adopted turbo codes while being more suited for high-throughput, low-latency applications. In addition, LDPC codes offer a wider range of tradeoffs between performance and decoding complexity [13]. The low-complexity decoding of LDPC codes is one of the main reasons for their popularity. This is due to the utilization of the belief propagation (BP) algorithm, which is an iterative decoding algorithm that is well suited for efficient VLSI implementations.

The encoding of the block version of LDPC codes has been criticized because of the apparent high time complexity involved. Direct encoding of LDPC block codes requires the multiplication of vectors with dense matrices, and hence is of O(n²) complexity. The complexity increases further with larger packets (code lengths). However, the code's performance also improves with larger code lengths. Thus, several code construction methods and algorithms have been proposed in the literature that aim to achieve linear time-complexity encoding of LDPC block codes [30, 31, 32, 34]. This issue highlights one of our project motivations; to gain further insight into efficient encoding algorithms for LDPC block codes and their hardware implementations.

One approach to investigating LDPC encoding implementation and its practicality is to explore the use of LDPC codes in a defined communication system. For our project, we chose the IEEE 802.16e (WiMAX) standard [10]. WiMAX is an emerging wireless metropolitan area network standard that provides fixed and mobile broadband wireless access. WiMAX employs several new technologies such as multiple-input multiple-output (MIMO) antenna arrays, space-time coding, and bandwidth and network scalability. The mobile version of WiMAX adopts LDPC block codes as optional channel coding schemes. The standard supports a set of block codes with six code rates and nineteen code lengths per rate. The supported codes are designed for efficient encoding and present a suitable technology platform for our LDPC encoder implementation project.

The above discussion frames the main goal of this project; to design and implement a low-time-complexity low-circuit-complexity LDPC block encoder, while maintaining compatibility with the IEEE 802.16e standard. The encoder is implemented as an

intellectual property (IP) core on an FPGA device. This provides the ability to use the encoder as a "drop-in" module for various digital designs, as well as provides a working hardware platform for future research into new implementation ideas. Several design challenges exist:

- Taking advantage of the proposed efficient encoding algorithm and the compact structure of the adopted codes in the standard.

- Incorporating all supported code rates and lengths into a single low-circuitcomplexity encoder design, with the ability to switch between code rates and lengths during operation.

- Minimizing hardware utilization and memory requirements.

- Developing a low and consistent latency encoder.

Beyond implementation, another research opportunity exists in studying the performance and suitability of LDPC encoders in emerging applications. One such application is the use of high performance codes with implantable medical devices (IMDs). Wireless IMDs are not a new technology; however, the potential treatment benefits that could be gained through utilizing high-throughput wireless transceivers in IMDs are significant [60]. An example of such benefits is the ability to produce non-invasive "swallow-able" imaging devices that are able to capture and transmit images of a patient's gastrointestinal tract for better diagnosis and treatment. The main challenge facing implant designers is the requirement to build low-power transceivers that are able to provide high-throughput with high data reliability [67]. Therefore, another goal for this project is to characterize the power consumption of the implemented 802.16e encoder, as well as a convolutional LDPC encoder, and evaluate their suitability for low-power

medical implant use. We consider the encoder-only scenario at the implant. Furthermore, since designs on FPGA devices are known to consume higher power than the same designs on power-efficient ASICs [101]. We also estimate the power consumption of these encoders when implemented on ASIC devices. In order to conduct this evaluation study, several issues must be addressed:

- Identifying a mathematical model for evaluating the power efficiency of

LDPC encoders for medical implant applications.

- Researching reasonable approximations for the scaling of FPGA power consumption levels to ASIC levels.

- Identifying possible power improvement options for our 802.16e LDPC encoder.

#### 1.2 Thesis Overview

In Chapter 2, we elaborate on the concepts mentioned in Section 1.1. Key concepts in information theory and channel coding are briefly reviewed. LDPC codes are introduced with a discussion of decoding and encoding algorithms and implementations. The IEEE 802.16e standard is introduced with a focus on LDPC codes' performance. The last section of Chapter 2 discusses the main challenges faced by wireless IMD designers including low power consumption and the modeling of wave propagation through the human body.

In Chapter 3, we discuss our implementation of the 802.16e LDPC encoder. The structure of the supported LDPC codes and the proposed encoding algorithm by the standard are presented. We describe the design and verification processes applied and

expand on the software modeling process. The hardware components of the design are detailed and they include the matrix-vector multipliers, memory storage and controllers, and the master Finite State Machine (FSM).

Chapter 4 mainly describes the form and usage of the encoder as an IP core illustrating the various input/output ports used to interface with it. In addition, Chapter 4 describes the behavioral, timing, and hardware verification processes used to confirm the functionality of the design. The throughput and hardware utilization of the encoder are also recorded.

Chapter 5 conducts a wireless medical implant power consumption study. The software tools used to estimate the power consumption of the encoders are presented. We also introduce a convolutional LDPC encoder design based on [91]. The power consumption of both the block and convolutional encoders is estimated and analyzed. We derive a mathematical model to evaluate the minimum encoder transmit energy required to achieve a certain coding performance level. The FPGA designs are evaluated against an uncoded system. ASIC approximations of the same designs are performed and evaluated for IMD use. Additionally, the encoders' power estimates are compared to industry-leading devices and possible power improvement options are presented.

Finally, the results are summarized and the future work for this project is discussed in Chapter 6.

## Chapter 2

## Background and Literature Review

### 2.1 Information Theory and Channel Coding

In communication systems information is transmitted from a source to a destination. The transmitter converts the information into a form suitable for transmission through the physical medium be it a copper wire, a fiber optic link, or radio frequency waves propagating through space. The receiver detects the transmitted signal and converts it back to the original information message. These physical media are information channels that carry the transmitted information messages. Ensuring the integrity of the transmitted messages in these channels would be a trivial task if it wasn't for the presence of noise that may corrupt the information during transmission. In this context, noise can be defined as any unwanted signal or effect in addition to the transmitted signal in the channel. The sources of noise vary from one channel to the other; interference from other transmissions, thermal effects generated by the electronic devices being used, environmental interference, etc. When the transmitted information messages are corrupted by noise, the receiver may not be able to recover the original information and may interpret these messages in error. Information Theory and Channel Coding are the fields of engineering that deal with the definition and analysis of information in communication systems as well as the various techniques used to combat the effects of noise on these systems.

It was Claude Shannon's revolutionary 1948 paper "A mathematical theory of communication" [1] that laid the foundations for the field of *Information Theory*. In his work, Shannon quantified the information that is transferred from source to destination in a communication system. He was particularly concerned with defining or measuring the information-carrying capacity of a channel. Realizing that the presence of noise in a channel reduces its information-carrying capacity, Shannon presented one of his most significant contributions; Theorem 17 in his paper, known as the *Information Capacity* Theorem. In it he defined the channel's capacity as the rate of discrete information units (or bits) that can be transmitted reliably (i.e. without error) over the channel measured in bits per second. While many mathematical models have been developed to describe the behavior of transmissions through various noisy information channels, the Gaussian channel is a fundamental and useful channel model for various communication channels such as wireless links and fiber optic cables [2]. This channel models the noise as a zeromean Gaussian random variable, which means that it assumes a Gaussian distribution of noise amplitude with a constant noise power over a limited channel bandwidth. The output of the channel is defined to be the addition of the noise and the channel's input. That is the channel output is perturbed by additive white Gaussian noise (AWGN). Shannon used the AWGN channel model to state and prove the famous theorem mentioned above. In it [1], he stated that the information capacity of a channel of bandwidth W hertz, subjected to AWGN of power N watt, when the average transmitter power is limited to P watt is given by:

$$C = W \log_2 \left( 1 + \frac{P}{N} \right) \text{ [bits per second]}$$

(2.1)

P/N is the ratio of the transmitter signal power to the noise power, hence called the signal-to-noise ratio (SNR), and is one of the most important parameters communication engineers must consider when designing a communication system. With this closed form equation, Shannon asserted that it was theoretically possible to reliably transmit information bits with rates upper-bounded by channel capacity in the presence of noise in an information channel. However, he gave no constructions of schemes that could achieve or approach this capacity.

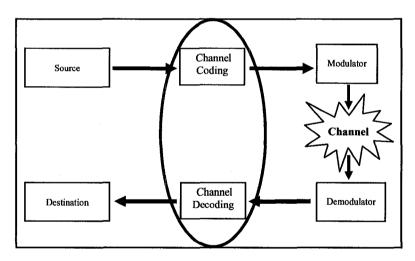

In order to mitigate the effects of noise on the transmitted information, communication systems use *Channel Coding* techniques. Figure 2.1 illustrates a simplified model of a communication system with the channel coding components highlighted.

Figure 2.1: Simplified model of a communication system

Channel coding involves the adding of redundancy to the transmitted messages (or symbols) in order to minimize the probability of interpreting these messages in error at the receiver. The process of adding redundancy at the transmitter is known as *encoding* and is reversed by a *decoding* process at the receiver. The receiver's failure to interpret a transmitted symbol correctly is termed a *decoding error*. Simple addition of redundancy,

such as repetition of transmitted symbols, is not the most efficient channel coding technique as it wastes channel bandwidth and system resources. Hence, channel coding goes beyond that, and attempts to encode the transmitted messages with the minimum number of symbols while still providing adequate protection against decoding errors.

Understanding the notion of channel capacity, and channel coding techniques, Shannon proceeded to state and prove his most famous result: the *Channel Coding Theorem*. This is theorem 11 in his 1948 paper [1]. In it he explained that there exist channel codes that make it possible to achieve reliable transmission, with as small an error probability as desired, if the rate of transmitted information is less than the channel capacity. Furthermore, he explained that it is not possible, with any code, to achieve such a low error probability if the rate of information transmission exceeds the channel capacity. This bound became known as the *Shannon limit*.

Finding codes that attempt to achieve channel capacity is only part of the problem of channel coding. Developing practical algorithms for encoding and decoding such codes is another challenging part. The search for "good codes" which provide performance approaching the Shannon limit with reasonable encoding/decoding complexity, has occupied the research community for years. Many channel code families have been developed and implemented [3]. However, certain classes of channel codes have emerged as superior ones in terms of their coding performance and implementation complexity. Turbo codes are one example of such codes [4]; Low-Density Parity-Check codes are another example. Both of these codes benefit from the advances of integrated circuits technology, and can now be constructed and implemented as high-performance and practical channel coding schemes.

#### 2.2 Low-Density Parity-Check Codes

#### 2.2.1 Introduction

Low-Density Parity-Check (LDPC) codes are a class of forward error control codes, and were first proposed by Gallager in the 1960s [5, 6]. However, in order to be simulated and implemented, they required processing resources that were impractical at the time. Despite their coding potential they were largely forgotten until their rediscovery in 1996 by MacKay and Neal [7]. They noticed that their work with sparse random matrices reinvented Gallager's codes. In their paper, they also mentioned that the general assumption regarding concatenated codes' superiority in practical systems may have contributed to the slow development of LDPC codes. Their results, however, showed that LDPC codes outperform the classical convolutional and concatenated codes, and provide performance very close to that achieved by turbo codes.

In recent years, LDPC codes have received a tremendous amount of research focus and popularity. They have been adopted into several communication standards such as the Digital Video Broadcasting standard for Satellite Television (DVB-S2) [8], IEEE's 802.3an [9], 802.16e (WiMAX) [10], and 802.11n [11]. One of the reasons for their popularity is that LDPC codes are *capacity-approaching* which means they provide performance that approaches the Shannon limit. Some studies have shown that LDPC codes can get to within 0.0045 dB of the Shannon limit [12]. This result far exceeds any figures achieved with classical forward error control (FEC) codes of the same decoding complexity. Turbo codes are the other class of FEC codes that provides similar results. However, as discussed in [13], LDPC codes are more suited for high-throughput low-latency applications than turbo codes. And LDPC codes offer a wider range of tradeoffs

between performance and decoding complexity. In addition, unlike turbo codes which are heavily patented by France Telecom [14], LDPC codes provide a relatively more open technology access for both industry and academia. Another reason for LDPCs' popularity is that they could be decoded with a low-complexity iterative algorithm known as the *Belief Propagation (BP) algorithm*, which is suited for efficient VLSI implementations. Therefore with excellent performance versus costs of implementation, LDPC codes represent an important option for emerging and next-generation communication systems.

#### 2.2.2 Overview of LDPC codes

#### 2.2.2.1 LDPC Code Structure

There are two different yet related types of LDPC codes, Block and Convolutional LDPCs. The original LDPC codes proposed by Gallager are block LDPC codes. Convolutional LDPC codes were proposed in 1999 by Felström and Zigangirov [15], and are receiving increasing research focus. However, since the convolutional codes are out of the scope of this project, we will focus on the block codes' structure and relevant encoding and decoding architectures in the following sections.

Before describing the code structure, it is important to define several relevant terms from information theory. In block FEC codes, the encoder accepts a block of message bits and generates a block of coded bits at the output. The resultant bit sequence is termed a *codeword*. If a user information message of length k bits is to be encoded to generate a codeword of length n bits, the number of added redundancy bits (termed code bits) is equal to n - k bits. The *code rate* (R) can be defined as the ratio of the number of original information bits to the total number of codeword bits. And since the codeword is always larger than the un-coded bit-sequence, this number must always be between zero and one.

$$R = \frac{k}{n} \tag{2.2}$$

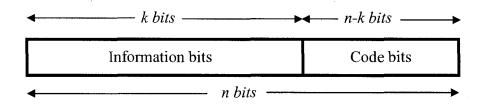

A block code is termed systematic if the output codeword contains the original information bits in an unaltered form. Therefore, the codeword of a systematic block code may take the form presented in Figure 2.2.

Figure 2.2: Codeword structure of a systematic block code

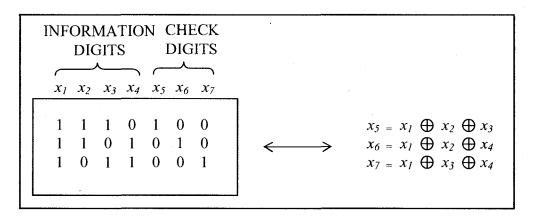

As the name of LDPC codes indicates, the *parity-check* is a key concept involved in their structure. In fact, Gallager introduced them as a special case of the general family of parity-check codes [5]. To form an LDPC codeword, k information bits are combined with (n - k) *parity bits*. Each parity bit is generated by performing a modulo-2 sum operation (XOR) on several pre-specified information bits. Parity-check works through detecting and correcting single-bit errors in transmission. Taking Gallager's example, Figure 2.3 shows a simple *parity-check* matrix. As indicated on the figure, parity bit 5 is generated by XOR-ing information bits 1, 2, 3 of a length n = 7 codeword. If bit 3 is corrupted by noise and arrives in error at the receiver, the decoder will be able to *correct* this error knowing the other errorless bits, namely bits 1, 2, and 5. This could be done by performing another XOR operation on these bits. It could immediately be seen that a *parity-check* matrix is a compact way of defining which bits participate in which parity-check operation according to the position of the ones. This means that the parity-check matrix defines all the parity-check equations.

Figure 2.3: Example of a parity-check matrix, figure taken from [5]

In the previous example if a parity-check operation is considered alone, an error in more than one transmitted bit could not be corrected and would result in a decoding error. The parity-check matrix attempts to solve this by specifying each bit to participate in several parity-check operations so that if one failed the others may not. This greatly increases the strength of the parity-check code in combating bit errors. Supported by these concepts, LDPC codes are defined as the *set of codewords* that satisfy all the parity-check equations defined by the parity-check matrix. Algebraically, this means that for any codeword vector x of length n bits, and its parity-check matrix H:

$$x \cdot H^T = 0 \tag{2.3}$$

Where H<sup>T</sup> is the transposed version of the matrix H. Another matrix could be defined through manipulations of H as the dual or the *null* of H, and is called a *generator matrix* G satisfying:

$$G \cdot H^T = 0 \tag{2.4}$$

The generator matrix of a code is used to generate all the codewords of that code. Therefore, the LDPC encoding process of a user information bit vector u can then be reduced to the following matrix multiplication:

$$x^T = u^T \cdot G \tag{2.5}$$

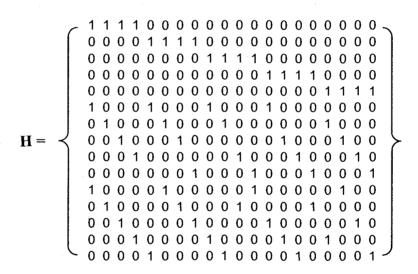

Where x<sup>T</sup> is the transpose of the codeword vector x. So it can be concluded that both a parity-check matrix and its dual generator matrix, can completely specify an associated LDPC code. Figure 2.4 illustrates an example of a parity-check matrix. This matrix defines an (n,j,k) code, where n is the code length, and j and k are the number of ones in each row and column, respectively. It is important to note that if the number of ones in each row and column – also termed the *weight* – stays constant across the matrix, it is then a *regular* LDPC code. An *irregular* LDPC code has a matrix where the number of ones is not fixed in all rows or columns.

Figure 2.4: Parity-Check matrix for (20, 3, 4) LDPC code

Sparseness is an important characteristic of an LDPC code's parity-check matrix. A sparse matrix is one that has a small number of nonzero entries. When dealing with regular LDPC codes, increasing the block length while keeping the number of ones per row and column constant lowers the density of the ones. This is where the *low-density* part of the name originates. It has been shown that as n is made large, the density of the ones approaches zero and the performance of the code increases [4, 6]. The sparseness

and low-density concepts have their implications on encoding and decoding, and translate into efficient decoding algorithms, as will be discussed further in section 2.2.2.2.

In order to produce "good codes" that have a low probability of decoding errors, several construction methods were proposed, and could be categorized as *randomly constructed* codes and *algebraically structured* codes. Randomly constructed LDPC codes were proposed first, such as the ones in [5, 7, 12, 16], and they work through randomly placing 1's and 0's in the parity-check matrix subject to some constraints. For example the number of 1's in each row and column could be required to be constant. These studies show that powerful randomly-constructed codes demonstrating excellent theoretic performance thresholds can be found. However, randomly-constructed LDPC codes are often hard to implement with low time complexity. Therefore, a wealth of algebraically-structured LDPC codes have been developed to tackle the complexity issue; examples include [17]-[20]. These codes use algorithmic structures and aim to strike a balance between the low-complexity encoding/decoding needed for hardware implementations and the performance expected from LDPC codes.

#### 2.2.2.2 Decoding and Current Implementations

Decoding of LDPC codes has its roots in the work of Gallager [6]. In particular, he demonstrated that an iterative algorithm could be used to decode LDPC codes. LDPC decoding algorithms could be explained more easily with the help of elegant graphical representations known as *bipartite* graphs.

A bipartite graph contains two disjoint sets of nodes where there are no connections (edges) between nodes of the same set. Tanner used bipartite graphs to graphically represent the parity-check matrix of an LDPC code [21], which is why bipartite graphs

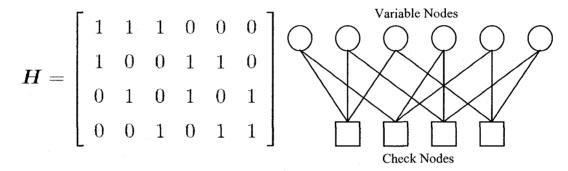

for LDPC codes are sometimes referred to as  $Tanner\ graphs$ . A Tanner graph features two sets of nodes named  $variable\ nodes$  and  $check\ nodes$ . Each bit in the codeword of length n is represented by a variable node, and each row of the parity-check matrix H is represented by a check node. An edge exists between the  $i^{th}$  variable node and the  $j^{th}$  check node if and only if the parity-check matrix entry  $h_{ij}=1$ . It can be immediately seen that the Tanner graph can completely specify an LDPC code. The same sparseness principle is transferred over from the parity-check matrix to the Tanner graph and allows for algorithmic efficiency of LDPC codes. Figure 2.5 illustrates an example for a (6,2,3) LDPC code that is graphically represented with a Tanner graph.

Figure 2.5: An example of a (2,3) regular LDPC code and its bipartite (Tanner) graph

The main algorithm used for decoding LDPC codes is the *Belief Propagation* Algorithm. The BP algorithm is a subclass of *message passing algorithms*. To visually describe the BP algorithm, we use the Tanner graph representation. The BP algorithm attempts to correctly decode the received codeword through several iterations. During each iteration of the algorithm, *messages* are passed between check nodes and variable nodes along the connecting edges. The passed messages are the probabilities or *beliefs* of the logical bit values at the variable nodes. The algorithm takes advantage of the interdependencies that exist in the graph (i.e. the parity-check matrix) and adjusts the *beliefs*

of the values at the variable nodes. Therefore, during each iteration, variable nodes learn more about their values from other nodes and the parity-check relations.

The algorithm starts by initializing the variable nodes' values with a metric called the log-likelihood ratio (LLR). The log-likelihood ratio is an advantageous metric since it is used to quantify the level of confidence in the value of the received bit being a logical 1 or logical 0. So if the probability of the received bit  $x_r$  being a logical one given the actual received value y is denoted as  $P(x_r = 1 \mid y)$  and the probability of it being a logical zero is denoted as  $P(x_r = 0 \mid y)$ , then the LLR  $\Lambda(x_r)$  is defined as the logarithm of the ratio between these two probabilities:

$$\Lambda(x_r) = \log\left(\frac{P(x_r = 1 \mid y)}{P(x_r = 0 \mid y)}\right)$$

(2.6)

It is noted that the LLR value largely depends on the noise power of the channel. The higher the noise power, the lesser the confidence we have in the received value.

After the initialization, the rest of the BP algorithm can be divided into two stages.

Stage 1: The check nodes construct and send their messages to the variable nodes. The check nodes utilize their knowledge of parity-check relations to adjust the LLRs and send them back to the participating variable nodes. Mathematically, this means all check nodes connected to variable node i send the adjusted LLR value Λ<sub>i</sub> to variable node i:

$$\Lambda_i = 2 \tanh^{-1} \left( \prod_{j \neq i} \tanh \left( \frac{\Lambda_j}{2} \right) \right)$$

(2.7)

Here the notation j/i indicates that the product includes all the LLRs except the one of the target variable node i.

• Stage 2: At the variable node, the incoming adjusted LLRs are summed together and are ready for use by the check node in the following iteration.

The algorithm proceeds until the decoded codeword correctly satisfies all the parity-check equations or a fixed number of iterations is reached. The BP algorithm is a powerful algorithm, and its time complexity grows linearly with the block length of the code [7, 9] which makes it feasible to build decoders for reasonably large code lengths.

High-performance, low-complexity implementations of LDPC decoders have been achieved and make these codes an increasingly compelling choice for emerging communications systems. The first published implementation was the Howland and Blanksby decoder [22] where a 690-mW and 1-Gbps throughput decoder was implemented on an ASIC chip for a rate-1/2 LDPC code. Since then, a wealth of decoder architectures and implementations has been published. The decoder proposed in [23] and implemented on an FPGA chip in [24], utilizes an architecture-aware LDPC code design approach to achieve various savings in the message-transport interconnect and memory overhead. A group at Rensselaer Polytechnic Institute, NY, proposed a decoder architecture that is designed for fast VLSI implementations [25]. Their design utilizes the partially-parallel decoder structure where a certain number of variable nodes or check nodes are mapped to single decoding unit. These decoding units are then multiplexed using time-division to achieve better decoding speed while keeping the decoder interconnect complexity low. In [26] flexible decoder architectures were proposed for the family of irregular LDPC codes. While in [27], a decoder architecture for array-codebased LDPC codes was described. Some implementations have targeted specific channel types such as magnetic recording channels [28]. Almost all variations of the decoders

proposed employ the BP algorithm and offer tradeoffs in throughput, complexity, scalability, and hardware flexibility.

#### 2.2.2.3 Encoding and Current Implementations

While the decoding of LDPC codes is a major advantage for these codes over other error-control codes, the encoding side has received criticism because of the apparent high time complexity involved. In this context, complexity is measured by the number of mathematical operations required to encode a bit. As noted by equation 2.5, a straightforward encoding of LDPC codes requires matrix-vector multiplication and hence is *quadratic* in the block length. This makes practical hardware implementations of the encoder almost impossible at large packet lengths (usually on the order of few thousand bits). By contrast, turbo codes can be encoded in linear time. Another problem with traditional encoding of LDPC codes is the fact that to encode an information bit which arrives at time t, the encoder may require an information bit which arrives at time  $t + \Delta$  adding *latency* to the encoding process. This also means that while the total number of output codeword bits is constant, the rate of bit production may not be even, requiring the buffering of output bits.

Early implementations of LDPC encoders, such as the one proposed in [29], used straight forward techniques, where a vector of information bits is multiplied by a dense generator matrix resulting in quadratic encoding complexity in the block length of the code. However, several researchers and information theorists worked through various algebraic methods to address this issue and several solutions have been proposed.

One approach used the idea of cascaded codes, where several levels of bipartite graphs are cascaded in a tree structure [30]. By choosing the number of cascaded codes

and the size of each code carefully, it is possible to construct codes for which low complexity encoding and decoding are achievable in linear time. A disadvantage with this approach is the fact that the individual cascaded stages are codes with smaller lengths than the overall code. This results in a loss of performance when compared with a standard LDPC code of the same total length.

In [31] another approach was presented. While constructing the code and in addition to the normal constraints set for the row and column weights of the parity-check matrix, another constraint is set that forces the matrix into the *lower triangular* form. This matrix leads to faster encoding times. However, since some of the "randomness" of the code is lost due to this constraint, a loss of performance is present.

Another construction of LDPC codes was presented in [32] that enables low-time-complexity encoding. In this approach, half the parity-check matrix is generated randomly while the other half is deterministic; the resulting codes are called semi-random LDPC codes. The authors of [32] propose a recursive encoding method with complexity growing linearly with the block length of the code. They further claim that semi-random LDPC codes perform comparably to fully random regular codes of similar dimensions. More recently, further research is focusing on studying semi-random LDPC codes for wireless applications. For instance in [33], methods of constructing semi-random LDPC codes that support various code rates are investigated, and their application to newer diversity-based communication systems is explored.

A significant step towards achieving linear-time LDPC encoding was realized through the work of Richardson and Urbanke [34]. They noted that although direct encoding seems to have a quadratic complexity, the actual number of operations required

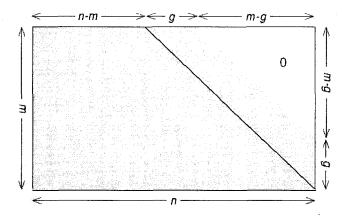

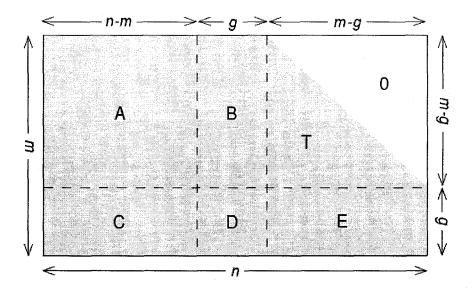

is manageable even for long block lengths. Furthermore, they managed to take advantage of the sparseness of the parity-check matrix through "optimization" steps to achieve efficient encoding. These steps require *preprocessing* the parity-check matrix via row and column permutations to achieve an *almost lower triangular* (ALT) form. Illustrated in Figure 2.6, this form is *almost* lower triangular since the matrix features a distance from *true* lower triangular form, and this distance is termed the *gap* (g). It is important to know that these preprocessing steps are applied after constructing the code, thereby preserving the sparseness and randomness of the matrix, and the strength of the code. The detailed steps of the algorithm are presented in [34].

Figure 2.6: A matrix in almost lower triangular (ALT) form

The proposed algorithm involves splitting the parity-check matrix into smaller submatrices and performing several matrix multiplication steps. Most of the multiplications use sparse matrices and have linear time complexity except the multiplication by the dense sub-matrices  $\Phi$  and  $T^{-1}$  (see [34] for details). The complexity of the overall algorithm is upper bounded by  $O(n+g^2)$ , and the smaller the gap the better the encoding time efficiency. In fact, the authors of [34] show that for sufficiently large n, the gap is

smaller than  $\sqrt{n}$  resulting in linear time complexity. In practical systems, g is usually a small constant allowing for efficient encoding implementations.

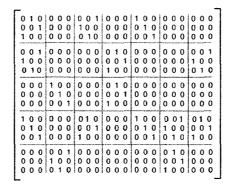

An algebraic structure useful for improving the computational efficiency of LDPC encoding is Quasicyclic (QC) codes. QC LDPC codes perform very well when decoded using the BP algorithm [18], and as discussed in [35], these codes have structures that can achieve computational efficiency and good hardware implementations. A QC code is one where each codeword is a "quasicyclic" shift of another. That is, if a codeword is segmented into strings of length z bits, and all segments are circularly shifted by the same amount, the resulting vector is also a codeword. An ingenious method of constructing QC LDPC codes is through the use of *circulant* matrices [17, 18]. A circulant matrix is a z x z square matrix where each row is a circular shift of the row above it, and the first row is a circular shift of the last. Therefore, QC LDPC codes may be defined by a parity-check matrix H that is composed of blocks of circulant matrices and zero matrices, as shown in Figure 2.7. Such a code is termed a *block-circulant* LDPC code.

Figure 2.7: An example of the internal structure of a matrix composed of circulant identity matrices, figure taken from [36]

Important advantages could be realized by using block-circulant parity-check matrices. Particularly, the time efficiency of the encoding algorithm of [34] can be improved. The multiplication with sub-matrix  $\Phi$ , which is proportional to  $g^2$ , is made

faster by minimizing the size of the gap g while preserving the strength of the code. The authors of [36] propose that picking g equal to the size of the circulant matrix z is enough for practically good code performance, while at the same time, the size of g can be made small to reduce the computational complexity. The block-circulant approach is especially advantageous in the case of multiplication with sub-matrix T<sup>-1</sup>. Using this approach, T is a lower triangular matrix composed of smaller block matrices with the diagonal made of identity matrices. Thus according to [36], the direct multiplication with T<sup>-1</sup> can be replaced with a multi-stage back substitution operation. This effectively converts the dense multiplication into a series of sparse vector-matrix multiplications and additions which significantly reduces the computational complexity.

Unlike the decoding side, where the BP algorithm has become the standard decoding technique, the encoding side exhibits more variations that incorporate the methods discussed earlier. In [37] an FPGA implementation of an LDPC encoder based on the ALT algorithm was created and achieves 44 Mbps output rate running on 143 MHz clock frequency. Encoder designs based on block-circulant matrices were presented in [35], along with a hardware implementation achieving a rate of a 100 million symbols/second. A hardware implementation based on the semi-random technique is presented in [38] and achieves low computational complexity with 99.5 Mbps output rate.

More recent implementations of LDPC encoders combine both the ALT algorithm and the block-circulant ideas to achieve high-efficiency high-throughput encoders. Furthermore, since LDPC codes are quickly becoming the codes of choice in most emerging communication standards, new implementations focus on building *standard-compliant* encoders. In [39], a CMOS implementation of a second-generation digital

video broadcast (DVB-S2) compliant codec is presented. This codec supports BCH codes as well as LDPC codes with code lengths up to 64800 bits and achieves up to 135 Mbps throughput. Another example is the 480 Mbps throughput LDPC codec built for ultrawide band (UWB) transceivers and presented in [40].

A main focus of our work is the implementation of an IEEE 802.16e compatible LDPC encoder. However, it is worth noting that the next-generation wireless local area network standard, 802.11n, features LDPC codes of a somewhat similar structure to those supported by the 802.16e standard. Therefore, LDPC encoder implementations that support the 802.11n standard are of particular importance to our study. In [41] an LDPC encoder implementation was presented and is compatible with the 802.11n standard. This implementation exploits the structure of the supported LDPC code to achieve efficient encoding with barrel-shifter based multipliers. Another 802.11n compatible encoder architecture is presented in [42], where the encoder multiplication steps are handled via random-access memory (RAM) registers. While not entirely similar to the 802.16e standard, these implementations provide us with useful insights into techniques leveraging the efficient structure of the supported LDPC codes.

More directly related to the 802.16e standard, a group at the University of Edinburgh developed a real-time programmable LDPC encoder for the 802.16e standard [43]. The encoder is implemented on Reconfigurable Instruction Cell Architecture (RICA) processor which executes ANSI-C code of the encoding algorithm. This implementation achieves a throughput of 10 to 19 Mbps. A hardware implementation of a fully compatible 802.16e encoder is produced by Xilinx Inc. as an Intellectual Property (IP) core [44]. The Xilinx encoder core's throughput depends on the FPGA chip and the clock

frequency used. This IP core targets the Xilinx FPGA chip family only, and the internal encoder structure is not released for public access.

# 2.3 Wireless Communications and Low-Density Parity-Check Codes

#### 2.3.1 Brief Overview of Wireless Communications

Wireless communications are the transfer of information over a distance without the use of electrical conductors such as copper wires or fiber optic cables. The information is transferred via the controlled propagation of *electromagnetic waves* through space. The distance of transfer may be as little as a few meters and as large as millions of kilometers depending on the frequency and power of the waves, as well as the technology that utilizes them.

Due to the open and un-controlled nature of the wireless communication channel, there exist several sources of interference and effects that tend to disturb the transmission and processing of wireless signals. The wireless channel experiences large-scale effects such as path loss (attenuation of signal with distance), and small-scale effects such as multipath fading and the Doppler Effect (for details see [45, 46, 47]). These effects cause degradation of the quality of the received signal which leads to higher probability of transmission errors. The characteristics of the wireless channel, together with additive noise and interference, need to be mitigated by various techniques such as diversity and channel coding.

Though there are many types of wireless communications, our focus is on wireless networking. Modern communication networks, where data is transmitted and accessed by

multiple network clients, are categorized based on coverage area to Personal Area Networks (PANs), Local Area Networks (LANs), Metropolitan Area Networks (MANs), and Wide Area Networks (WANs) [48]. Wireless versions of such networks exist and continue to evolve through technology innovations.

#### 2.3.2 The IEEE 802.16 wireless networking standard (WiMAX)

The computer networking industry has many network vendors, carriers, and suppliers. Typically, various vendors have different ideas and strategies on network implementations and usage. In order to coordinate technology efforts, many networking standards have been developed and adopted by industry [48].

IEEE's 802.16 standard (also known as WiMAX) is a wireless metropolitan area network (WMAN) standard. This standard was first introduced to provide fixed broadband wireless access, and was ratified by IEEE in 2004 to be formally numbered 802.16-2004 [49]. The standard was later modified to include support for mobile broadband access in an amendment which was ratified in 2005, and formally numbered 802.16e-2005 [10]. WiMAX employs several new technologies such as multiple-input multiple-output (MIMO) antenna arrays, space-time and LDPC codes, quality of service (QoS) algorithms, and channel bandwidth and network scalability. Further details of the 802.16 standard can be found in [49, 50, 51].

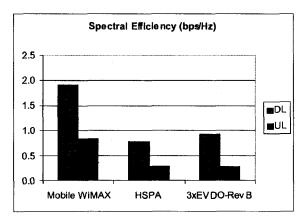

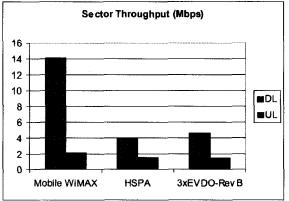

The 802.16 standard supports theoretical data rates of 70 Mbps over a distance of 50 Km [49]. However, under typical network traffic conditions these limits are rarely achieved. In a comparison study done by the WiMAX forum in [52], WiMAX's performance was compared to existing and evolving third-generation (3G) mobile networks. Figure 2.8 presents the comparison results where DL is the *downlink*

connection from the base station to the mobile device, and UL is the *uplink* connection from the mobile device back to the base station. The study shows the distinct advantage that WiMAX has over other 3G metropolitan wireless networks in both throughput and spectral efficiency.

Figure 2.8: Spectral efficiency and sector throughput comparison of HSPA, EVDO-Rev. B, and Mobile WiMAX under the same traffic conditions, figure taken from [52]

In our project, we will be implementing an encoder system that is compatible with the LDPC codes supported in the mobile WiMAX standard.

#### 2.3.3 LDPC codes in Wireless Communications

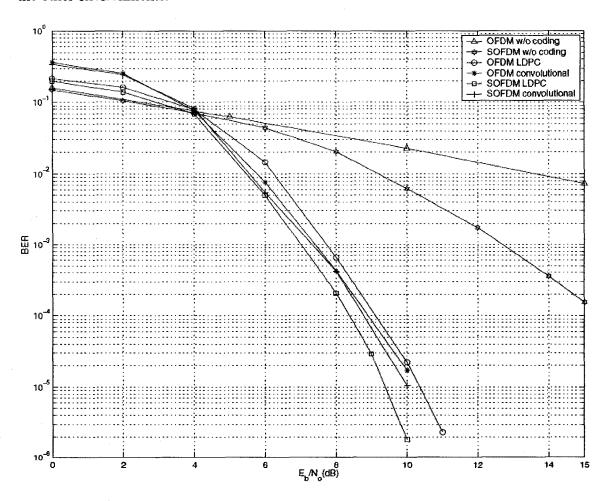

Several research studies have evaluated aspects of using LDPC codes in wireless communications. In [53] an information theory approach was taken to study the performance of LDPC codes in several types of wireless channel models such as a basic linear Gaussian channel, a partial-band jamming channel, and a Raleigh fast fading channel. The authors of [53] demonstrated that properly designed LDPC codes can be used to achieve reliable transmission over these channels making these codes an appropriate class for various kinds of wireless channels. And in [54] a group at Kansas State University explored the performance gains obtained from combining LDPC coding

with spread spectrum techniques in conventional orthogonal frequency division multiplexing (OFDM) systems. The authors simulated the performance of an un-coded OFDM system versus a convolutional coded system as well as an LDPC coded system in typical outdoor wireless environments including urban, rural and hilly terrain. The effects of code spreading were considered. Figure 2.9 presents their results in the typical urban environment. It can be seen that LDPC coded systems require less SNR to achieve a similar bit error rate (BER) over un-coded ones. Similar coding gains were recorded for the other environments.

Figure 2.9: Performance of un-coded and LDPC coded OFDM and spread OFDM (SOFDM) systems in Typical Urban wireless channel, BPSK, R = 1/2, N = 1024, figure taken from [54]

On the wireless networking front, LDPC codes represent a viable option for most next-generation networks and standards. Hence many studies were conducted to evaluate the design and performance of LDPC codes for specific networking applications. Wireless sensor networks is one such application where studies such as [55, 56] have demonstrated that LDPC codes accomplish their typical coding gains and perform much better that other channel codes. In addition, LDPC codes provide the appropriate platform for low power implementations required for these networks. Other studies focused on wireless LANs such as the next-generation IEEE 802.11n [11] standard, and WMANs such as CDMA networks [57].

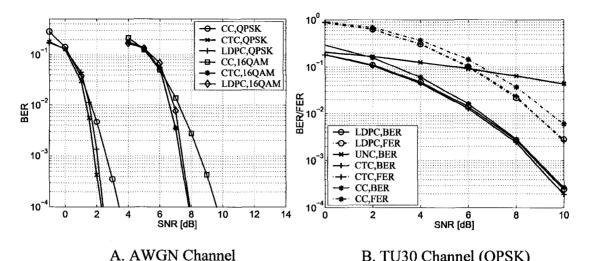

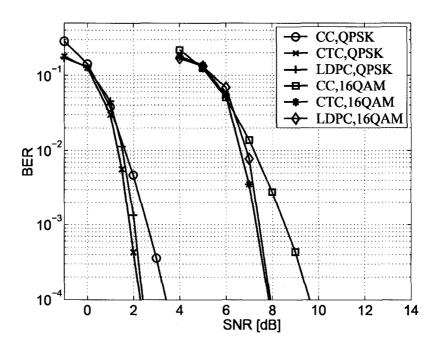

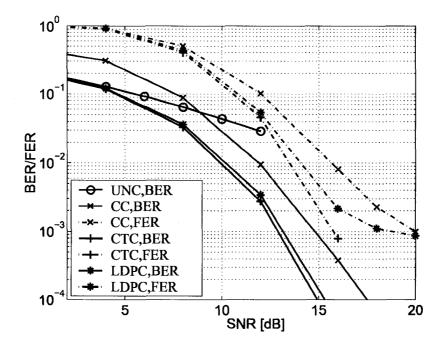

The use of LDPC codes in WiMAX networks has been studied extensively, and several designs, variations, and enhancements have been proposed to achieve various performance targets and tradeoffs. For example the study in [58], compares the performance of the supported LDPC codes from the 802.16e-2005 standard to a slightly optimized version. In [59], simulations were carried out to plot the performance of the 802.16e LDPC codes against other important FEC codes supported by the standard, namely convolutional codes and convolutional turbo codes. Figure 2.10 presents the study's results, where the code's BER performance was plotted using different modulation techniques. In part A, a codeword length of 576 bits and a code rate of 1/2 were used to simulate the codes on an AWGN wireless channel model. In part B, the same parameters were used to simulate the performance on the TU30 channel, modeling a mobile user in a *typical urban* environment moving with a velocity of 30 Km/h, while communicating with a base station on a carrier frequency of 3.5 GHz. Part B also includes the *frame error rate* (FER) performance curves.

A. AWGN Channel B. TU30 Channel (QPSK) Figure 2.10: 802.16e supported FEC codes comparison, R = 1/2, N = 576, figure taken from [59]

It can be seen from the figure that the LDPC code achieved the best performance results. While comparable to the convolutional turbo code's (CTC) performance, a big advantage of the LDPC codes over their counterparts is their decoder's low circuit-complexity. Moreover, increasing the block length would provide further coding gains. However, long block lengths require more processing time which could prove challenging for systems requiring low latency codecs. The structure of these standard supported LDPC codes will be further described in Chapter 3. It is worth noting that these results correlate well with the results of Figure 2.9 demonstrating the good performance of LDPC codes in practical wireless systems.

The studies recorded in literature build a solid base for the LDPC coding choice in wireless networking, and the results encourage further investigation of these codes for next-generation technologies.

## 2.4 Wireless In-Body Medical Communications

#### 2.4.1 Overview of In-Body Medical Communications

Advances in integrated circuit technology have expanded the options of modern medicine to provide new and innovative treatments. Such treatments include the use of sensor devices to monitor a patient's health data (i.e. cardiac data, blood parameters, etc.), imaging devices to monitor and evaluate parts of a patient's gastrointestinal tract and other organs, and various other temperature and muscle sensing devices. Monitoring and sensing devices may require the patient to spend a considerable amount of time in a medical facility while being treated by health professionals. In addition, expensive and invasive operations may be required to capture and transfer the data out of the human body using such links as flexible cables. These reasons were among the motivations behind the design and implementation of miniaturized portable as well as implantable medical devices. *Implantable medical devices* (IMDs) have been widely used in the treatment of many diseases such as heart diseases and neurological disorders. Pacemakers, implantable defibrillators, and hearing aids are examples of such devices.

The increasing need for IMDs that can provide ongoing and cost-effective monitoring and treatment, highlights the need for wireless solutions. Typically, a wireless-enabled medical implant may be remotely controlled from an external station while transmitting diagnostic or monitoring data during operation. The integration of wireless communications with IMDs holds several advantages over wired solutions such as enhanced patient convenience, ease of data capturing and collection, reduced risk of infection, lower costs, and enhanced mobility, all of which contribute to an improved overall healthcare experience. Traditionally, wireless IMDs used inductive RF links to

carry the data out of the human body. This required the use of a magnetic wand in the proximity of the IMD to inductively power-up the device then capture the transmitted data [60]. These devises typically operated in low-frequency ranges (i.e. 10s to 100s of kilohertz) providing data rates of less than 50 kb/sec. While proving robust and reliable, the practical antenna sizes and the inductive structure of these implants provided limited power ranges resulting in short range RF links; often requiring external receivers to have contact with the skin of the patient directly on top of the IMD's location.