#### Optimizing Task Distribution and Shared-Variable Accesses in an Asynchronous-Partitioned-Global-Address-Space Programming Model

by

Jeeva S. Paudel

A thesis submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Department of Computing Science

University of Alberta

© Jeeva S. Paudel, 2015

### Abstract

High-performance programming systems employ a wide range of techniques to improve the performance of parallel and distributed applications on large-scale machines. Such techniques include load balancing to reduce machine idle times, colocating tasks and related data to leverage data locality, and optimizing sharedvariable accesses to reduce communication costs. These goals result in complex performance trade-offs that typically require programming systems to prioritize one over the others, thereby limiting opportunities for optimization.

This dissertation identifies a novel opportunity for load balancing, proposes a new approach for workload distribution, and presents a profiling-based framework to automatically select coherence protocols aimed at specific patterns of shared-variable accesses. These approaches strike a balance between the tight budgets for run-time optimization and the exposition of new opportunities to improve the running time of applications. A prototype designed to evaluate these ideas is integrated into the X10 programming system. An empirical evaluation of these ideas, using large applications with diverse patterns of parallelism and communication, indicates that they can be applied widely and that they have significant performance merits.

## Preface

Parts of Chapter 3, 4, and 5 have previously appeared in workshop, conference and journal publications. These are collaborative work with authorship shared among myself, José Nelson Amaral, Olivier Tardieu, and Levi H. S. Lelis. I did most of the artifact implementation, experimental evaluation, data analysis, and writing for the papers. The other co-authors provided significant inputs for designing the experimentations, for developing the algorithms, and for improving the presentation of the papers.

This research was conducted over a period of five years, during which the X10 programming system went through several changes. The quality of the code generated by the X10 compiler and the ability of the X10 runtime to harness the computing power also evolved significantly. Therefore, the execution time for the baseline execution of several benchmarks and applications used in this thesis vary across different implementations used in different chapters. However, the baseline for the experiments within each chapter is consistent. To my parents.

## Acknowledgements

This dissertation is an outcome of continued support from many people. I express my sincere gratitude to you all.

- 1. My wife and my family, for your warm love and invaluable inspiration.

- 2. CDOL members Paul, Matthew, You, Ricardo, Carolina, Iain, Arnamoy, and Xunhao, for your lively paper discussions.

- 3. Steve Sutphen, for your substantial effort in setting up the computing platform for my experimental evaluations.

- 4. Christopher Dutchyn, for instilling in me the love of compilers and programming systems.

- 5. Levi Lelis, for your collaboration on the idea of workload distribution. Thank you for helping me design the experiments, validate the results, and refine the writing.

- 6. Olivier Tardieu, for your excellent insights that form the mainstay of the research ideas investigated herein.

- 7. Keshav Pingali, Duane Szafron, Paul Lu, and Bruce Cockburn, for agreeing to be on my examining committee and for your support in completing and delivering this dissertation.

- 8. Last and most important, my advisor, José Nelson Amaral, for your excellent mentorship. Thank you for teaching me the rigorous process of scientific research. Your questions and insights have been instrumental in producing this dissertation.

Funding for parts of this work have been provided by the Natural Sciences and Engineering Research Council of Canada, Alberta Innovates: Technology Futures (formerly iCORE and Alberta Ingenuity), and by the IBM Center for Advanced Studies at the IBM Toronto Software Laboratory.

# Contents

| 1.1       Research Goals         1.2       Contributions         1.3       Outline         1.3       Outline         2       Preliminaries         2.1       The APGAS Model         2.2       X10         2.2.1       Places         2.2.2       Activities         2.2.3       Global References         2.2.4       Distributed Arrays         2.2.5       Load Balancing         2.3       Shared-Variable Coherence         2.3.1       The X10Protocol | 1               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 1.3       Outline                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2               |

| 2 Preliminaries         2.1 The APGAS Model         2.2 X10         2.2.1 Places         2.2.2 Activities         2.2.3 Global References         2.2.4 Distributed Arrays         2.2.5 Load Balancing         2.3 Shared-Variable Coherence                                                                                                                                                                                                                | 3               |

| 2.1       The APGAS Model         2.2       X10         2.2.1       Places         2.2.2       Activities         2.2.3       Global References         2.2.4       Distributed Arrays         2.2.5       Load Balancing         2.3       Shared-Variable Coherence                                                                                                                                                                                        | 4               |

| 2.1       The APGAS Model         2.2       X10         2.2.1       Places         2.2.2       Activities         2.2.3       Global References         2.2.4       Distributed Arrays         2.2.5       Load Balancing         2.3       Shared-Variable Coherence                                                                                                                                                                                        | 5               |

| 2.2       X10                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5               |

| 2.2.1Places2.2.2Activities2.2.3Global References2.2.4Distributed Arrays2.2.5Load Balancing2.3Shared-Variable Coherence                                                                                                                                                                                                                                                                                                                                       | 5               |

| 2.2.2Activities2.2.3Global References2.2.4Distributed Arrays2.2.5Load Balancing2.3Shared-Variable Coherence                                                                                                                                                                                                                                                                                                                                                  | 6               |

| 2.2.3       Global References                                                                                                                                                                                                                                                                                                                                                                                                                                | 6               |

| 2.2.4       Distributed Arrays                                                                                                                                                                                                                                                                                                                                                                                                                               | 6               |

| 2.2.5Load Balancing2.3Shared-Variable Coherence                                                                                                                                                                                                                                                                                                                                                                                                              | 7               |

| 2.3 Shared-Variable Coherence                                                                                                                                                                                                                                                                                                                                                                                                                                | 7               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8               |

| 2.4 Related APGAS Languages                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8               |

| 3 Locality-Aware Task Migration                                                                                                                                                                                                                                                                                                                                                                                                                              | 10              |

| 3.1 Selection of Tasks for Migration                                                                                                                                                                                                                                                                                                                                                                                                                         | 10              |

| 3.1.1 Locality-Flexible Tasks in Applications                                                                                                                                                                                                                                                                                                                                                                                                                | 11              |

| 3.2 Migration of Locality-Flexible Tasks                                                                                                                                                                                                                                                                                                                                                                                                                     | 13              |

| 3.2.1 Work Dealing                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14              |

| 3.2.2 Work Stealing                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15              |

| 3.3 Experimental Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17              |

| 3.3.1 Experimental Setup                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17              |

| 3.3.2 Results and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                 | 18              |

| 3.4 Limitations                                                                                                                                                                                                                                                                                                                                                                                                                                              | 23              |

| 3.5 Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24              |

| 3.6 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25              |

| 4 Optimizing Shared-Variable Accesses                                                                                                                                                                                                                                                                                                                                                                                                                        | 26              |

| 4.1 Shared-Variable Access Patterns                                                                                                                                                                                                                                                                                                                                                                                                                          | 26              |

| 4.2 Directory-based Coherence Protocol for X10                                                                                                                                                                                                                                                                                                                                                                                                               | 20<br>28        |

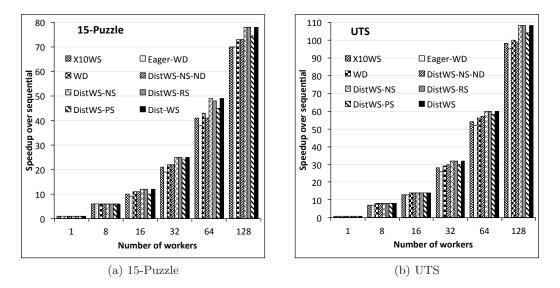

| 4.2.1 Directory and Shared-Variable States                                                                                                                                                                                                                                                                                                                                                                                                                   | 28<br>28        |

| 4.2.2 DirCoPX Optimization Strategies                                                                                                                                                                                                                                                                                                                                                                                                                        | 20<br>29        |

| 4.2.2 DirCoPX Protocol Operation                                                                                                                                                                                                                                                                                                                                                                                                                             | $\frac{29}{30}$ |

| 4.2.4 Augmented DirCoPX for Migratory Data                                                                                                                                                                                                                                                                                                                                                                                                                   | 31              |

| 4.3    | Framework for Pattern Detection and Optimization                                                             |  |

|--------|--------------------------------------------------------------------------------------------------------------|--|

|        | 4.3.1 Profiling Variable Accesses                                                                            |  |

|        | 4.3.2 Coherence-Policy Manager                                                                               |  |

|        | 4.3.3 Switching Between Coherence Protocols                                                                  |  |

|        | 4.3.4 Relieving Programmers from the Coherence Burden                                                        |  |

| 4.4    | Experimental Evaluation                                                                                      |  |

|        | 4.4.1 Experimental Setup                                                                                     |  |

|        | 4.4.2 Results and Discussion                                                                                 |  |

| 4.5    | Related Work                                                                                                 |  |

| 4.6    | Summary                                                                                                      |  |

| 5 Stra | atified Sampling for Even Workload Partitioning                                                              |  |

| 5.1    | Preliminaries                                                                                                |  |

|        | 5.1.1 Problem Formulation                                                                                    |  |

|        | 5.1.2 Chen's Stratified Sampling                                                                             |  |

| 5.2    | WPS: Workload Partitioning & Scheduling                                                                      |  |

|        | 5.2.1 Sampling                                                                                               |  |

|        | 5.2.2 Estimating $\ldots$                                                                                    |  |

|        | 5.2.3 Partitioning $\ldots$ |  |

|        | 5.2.4 Distributing $\ldots$ |  |

| 5.3    | WPS Accuracy                                                                                                 |  |

| 5.4    | Application Problem: An Example                                                                              |  |

| 5.5    | Experimental Evaluation                                                                                      |  |

|        | 5.5.1 Experimental Setup                                                                                     |  |

|        | 5.5.2 Results and Discussion $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$         |  |

|        | 5.5.3 Asynchronous IDA <sup>*</sup>                                                                          |  |

| 5.6    | Related Work                                                                                                 |  |

| 5.7    | Summary                                                                                                      |  |

| 6 C    | alusions and Future Work                                                                                     |  |

| 0 001  | iciusions and future work                                                                                    |  |

| יווים  | graphy                                                                                                       |  |

|        | nclusions and Future Work                                                                                    |  |

# List of Figures

| 2.1 | An example using GlobalRef                                | 6  |

|-----|-----------------------------------------------------------|----|

| 2.2 | Activities, places and global references                  | 7  |

| 3.1 |                                                           | 12 |

| 3.2 | Deques for locality-flexible and locality-sensitive tasks | 16 |

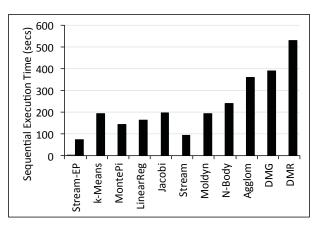

| 3.3 | Sequential execution time using X10WS                     | 19 |

| 3.4 | Speedup over sequential execution time                    | 20 |

| 3.5 | Speedup on applications with small task granularities     | 22 |

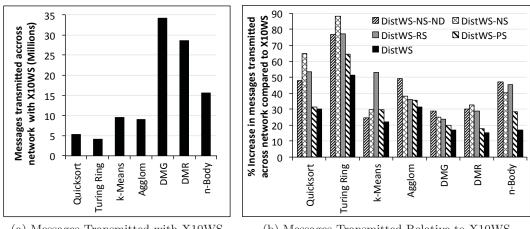

| 3.6 | Messages transmitted across network                       | 22 |

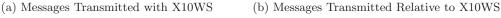

| 3.7 | Speedup on 15-Puzzle and UTS applications                 | 23 |

| 3.8 | An example illustrating the use of the at statement       | 24 |

| 4.1 |                                                           | 29 |

| 4.2 | DirCoPX operations.                                       | 30 |

| 4.3 | Shared variables in different applications.               | 36 |

| 4.4 | Sequential execution time using the X10Protocol           | 36 |

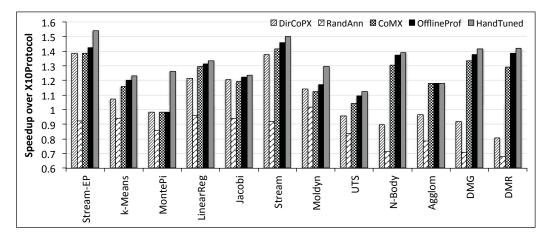

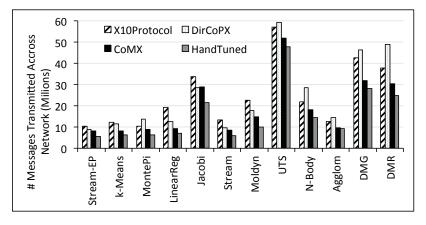

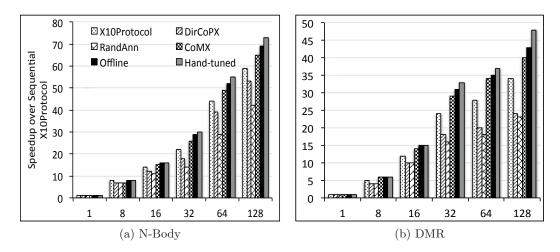

| 4.5 | Speedup over the X10Protocol                              | 37 |

| 4.6 | Messages transmitted across the network                   | 38 |

| 4.7 | Speedup on N-Body and DMR applications                    | 40 |

| 5.1 | $(3\times3)$ -Sliding-Tile Puzzle.                        | 43 |

| 5.2 | Sequential execution time                                 | 52 |

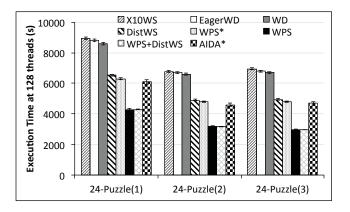

| 5.3 | Execution times of 24-Puzzle at 128 workers               | 52 |

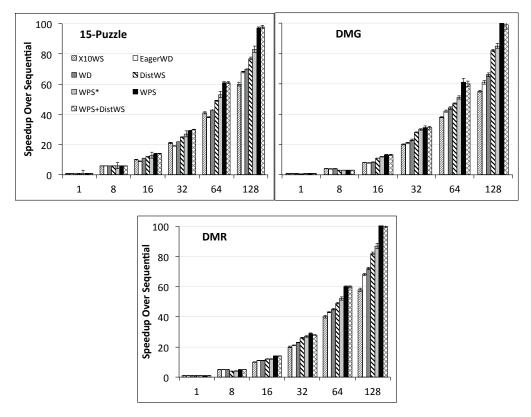

| 5.4 | Speedup over sequential execution time                    | 53 |

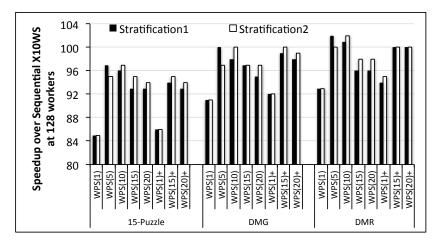

| 5.5 | 1 0                                                       | 54 |

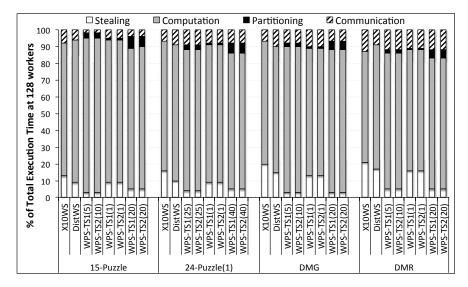

| 5.6 | Breakdown of total execution time                         | 55 |

| 5.7 | Average node utilization.                                 | 56 |

| 5.8 | WPS and AIDA* performance on 15- and 24-Puzzles           | 57 |

# List of Tables

| 3.1 | Task granularities (in ms)              | 21 |

|-----|-----------------------------------------|----|

| 4.2 | Applications and their input data set   | 37 |

|     | Instances of 24-Puzzle solved optimally |    |

# List of Acronyms

| PGAS                 | Partitioned Global Address Space                |

|----------------------|-------------------------------------------------|

| APGAS                | Asynchronous Partitioned Global Address Space   |

| UPC                  | Unified Parallel C                              |

| MPI                  | Message Passing Interface                       |

| IDA*                 | Iterative Deepening A <sup>*</sup>              |

| UTS                  | Unbalanced Tree Search                          |

| AMD                  | Advanced Micro Devices                          |

| DMG                  | Delaunay Mesh Generation                        |

| DMR                  | Delaunay Mesh Refinement                        |

| MCP                  | Matrix Chain Multiplication                     |

| RA                   | Random Access                                   |

| SLAW                 | Scalable Locality-Aware Work-Stealing Scheduler |

| DirCoPX              | Directory Based Coherence Protocol for X10      |

| CoMX                 | Coherence-Policy Manager for X10                |

| GR                   | GlobalRef                                       |

| X10RT                | X10 Runtime                                     |

| API                  | Application Program Interface                   |

| HPC                  | High Performance Computing                      |

| $\operatorname{STM}$ | Software Transactional Memory                   |

| AMR                  | Adaptive Mesh Refinement                        |

| WPS                  | Workload Partitioning and Scheduling            |

| WIT                  | Work-item Tree                                  |

| StraSa               | Stratified Sampling                             |

| BLDM                 | Balanced Largest-First Differencing Method      |

| AIDA*                | Asynchronous Iterative Deepening $A^*$          |

| TDS                  | Transposition-table-driven Scheduling           |

### Chapter 1

### Overview

Efficient execution of data and compute-intensive applications on large-scale parallel and distributed machines is challenging. Tasks and data referenced by the tasks must be co-located in a node to localize data accesses. Tasks spawned by an application must be evenly partitioned to ensure even utilization of available nodes. Efficient data-access policies are essential to minimize communication across the nodes. Manually orchestrating data layout, task execution and communication, to address such challenges, hampers programming productivity. To this end, high-performance programming systems, such as Partitioned Global Address Space (PGAS) and Asynchronous PGAS (APGAS), provide a uniform programming model for local, shared and distributed-memory computing machines. They provide mechanisms to distribute data across address partitions, to create parallel tasks, to map the tasks to the address partitions, and to manage the consistency of shared data. The address partitions may belong either to the shared-memory nodes or to the distributed-memory nodes.

Existing PGAS and APGAS models bind parallel tasks, or threads, of computation to programmer-specified address partitions in order to exploit affinity between tasks and data allocated at the address partitions. However, not all tasks benefit from such a binding because they may be agnostic to the location of data. A good example is a task that encapsulates the data necessary for its execution. The tasks that are sensitive to the location of data are called *locality-sensitive* tasks and tasks that are either agnostic or that do not bear strong affinity to the location of data are called *locality-flexible* tasks. The lack of a distinction between locality-sensitive and locality-flexible tasks enforces a one-to-one mapping between tasks and address partitions. Such a mapping over-constrains the execution of tasks and precludes opportunities for balanced distribution of work across address partitions. This inherent limitation of PGAS and APGAS models is evident in languages, such as UPC, X10, Chapel and Habanero-Java. The lack of load-balancing mechanisms across address partitions in these languages further compounds the problem of even utilization of computing resources.

Many applications recursively process different data elements to generate additional data of substantially different sizes. A good example is state-space search. A mechanism for evenly partitioning data in such applications must account for the size

of dynamically generated data. Both modern and conventional high-performance programming models, such as the Message Passing Interface (MPI) programming models, PGAS and APGAS, lack such a mechanism, and cause unbalanced distribution of data. Techniques to dynamically alleviate load imbalances do exist in PGAS and APGAS systems. However, they initiate actions only after the occurrence of a load imbalance and operate only within address partitions. The motivation for this restriction is in part to encourage tasks to exploit their affinity to data allocated within the address partitions.

Shared variables are fundamental abstractions in high-performance programming systems. They typically encapsulate a significant amount of frequently accessed data. Efficient coherence protocols are essential to ensure consistency of sharedvariable accesses. Implementations of popular PGAS and APGAS languages, such as UPC, X10, and Chapel, typically maintain a single global copy of each shared variable at the site of allocation. The tasks co-located with the shared variables in the same address partition can access the variables directly. However, such a protocol incurs the overhead of message transfers for all accesses to shared variables in remote address partitions. Alternative coherence protocols that employ replication of shared variables across address partitions are known to address this limitation. Although such protocols have been extensively studied in traditional distributedmemory systems, they have not been investigated in PGAS and APGAS systems.

#### 1.1 Research Goals

A preliminary investigation offered us insights into these limitations inherent in the PGAS and APGAS models. These insights led us to pursue the research questions listed below in the context of interesting real-world applications. This study investigates the problems in the context of a specific programming system, *i.e.*, X10 — a popular realization of the APGAS model.

- Would a flexible mapping between locality-flexible tasks and address partitions yield performance gains by enabling task migration across address partitions? Task migration for load balancing entails identifying tasks to migrate, the timing of migration, and the remote node that is starving for work. Migrating locality-sensitive tasks hinders locality of data access and only adds to these overheads, potentially leading to serious performance degradations. Therefore, an efficient task-migration strategy must selectively migrate only locality-flexible tasks, and must amortize these overheads through improved utilization of computing resources.

- By accounting for the variances in the size of dynamically generated data, can a domain decomposition yield an even distribution of data throughout program execution? A static partitioning scheme specified at the start of program execution may soon result in largely imbalanced data across address partitions. Dynamically re-distributing data after each phase of data generation incurs large execution-time overheads. Thus, an efficient distribution mechanism must be able to predict the amount of data generated upon processing

initial data elements with reasonable accuracy without actually running an application. If the prediction is feasible, can such a strategy be encoded into the programming system for use in a diverse range of applications?

• Can replication of data across address partitions yield better performance than maintaining a unique copy of the data at the site of allocation? Replication enables concurrent reads and local accesses to data, but requires complex mechanisms to ensure consistency. Maintaining a unique copy of data does not require coherence mechanisms, but incurs expensive message transfers for all remote data accesses. Therefore, an efficient data-management technique must adaptively employ one or more of these strategies depending upon how the data is accessed.

#### **1.2** Contributions

The primary contributions of this dissertation include:

- A careful study of the interplay between parallel tasks and the scheduling framework in the X10 programming system leading to the key observation that locality-flexible tasks are key to efficient inter-node load balancing in distributed-memory systems. We investigate two orthogonal strategies for load balancing. The first is a *work-stealing* strategy where a node starving for work attempts to steal work from a node with surplus work. The second is a *work-dealing* strategy where a node with surplus work to nodes searching for work. We devised an effective heuristic to identify a node that is starving for work and also to determine the timing of task migration. This heuristic approximates the work-load status of a node by analyzing its history of searching for work among its peers. Experimental evaluation indicates that permitting only locality-flexible tasks for work stealing and work dealing significantly alleviates load imbalances while minimizing the performance penalty of migration itself.

- A novel adaptation of an existing approach to sampling for partitioning data. This technique systematically accounts for data recursively generated upon processing initial data. This approach processes a small amount of data to predict, with reasonable accuracy, the amount of data that will be generated by an application at runtime. Programmers do not need to manually code this solution for individual applications. A prototype implementation in X10 demonstrates that the approach can be integrated into the runtime of a programming system to support diverse applications. The even data distribution resulting from this approach yields significant performance gains.

- A practical framework for the automatic selection of a high-performing protocol among available ones to manage accesses to shared data. The framework underlying this study monitors and analyzes reads and updates of each shared data in an application to make the selection. We incorporate a directory-based protocol into the runtime system of X10. The protocol replicates shared data at the accessing nodes and maintains consistency of data copies. This pro-

tocol complements the existing protocol in X10 that keeps a unique copy of shared data and relies on message transfers for all remote accesses. Empirical evidence suggests that coordinating strategies that replicate data with the one that maintains a unique copy of the data is essential to improve the performance of shared data exhibiting diverse access behaviours. Experimental evaluation also suggests that this approach yields performance comparable to that of carefully hand-tuned applications.

#### 1.3 Outline

The rest of this dissertation is organized as follows: Chapter 2 presents a primer on the Asynchronous-Partitioned-Global-Address-Space model, the X10 programming system, and the coherence of shared variables in multiprocessor systems. Chapter 3 proposes selective locality-aware task migration and investigates its feasibility and performance merits. Chapter 4 describes a framework for the selection of augmented coherence protocols for optimizing different patterns of shared-variable accesses. Chapter 5 presents a novel adaptation of an existing statistical technique of stratified sampling for workload partitioning. Chapter 6 summarizes the contributions and presents avenues for future work.

### Chapter 2

## Preliminaries

This chapter discusses important concepts underlying the Asynchronous-Partitioned-Global-Address-Space model, the X10 programming language, and the coherence of shared variables in multiprocessor systems.

#### 2.1 The APGAS Model

The Partitioned-Global-Address-Space (PGAS) model offers a unified concurrency mechanism for both intra- and inter-node parallelism. It allows distribution of data and mapping of tasks to different address partitions. It also offers mechanisms to encode affinity between tasks and location of data. However, the PGAS model suffers from two major drawbacks. First, all existing languages in the PGAS family — Titanium [39], UPC [30], and Co-Array Fortran [57] — follow the Single Program Multiple Data model of execution, where all tasks execute the same program across machines. They implicitly assume that all processes run on similar hardware. Second, they lack support for dynamically spawning multiple parallel threads of computation. Consequently, handling non-data-parallel applications, which requires dynamic load balancing, is difficult in the PGAS model.

The Asynchronous PGAS (APGAS) model addresses such limitations by extending the PGAS model with the notions of asynchronous parallel tasks and abstractions for location of data. The work underlying this dissertation is in the context of X10 [22] — a popular realization of the APGAS model. Therefore, the next section discusses the core APGAS concepts of the X10 programming system.

#### 2.2 X10

X10 is a high-performance, high-productivity programming system developed at IBM as part of the "Productive, Easy-to-use, Reliable Computing System" project. The X10 programming model is organized around the notions of *places* and *activities*.

#### 2.2.1 Places

A place is an abstraction of shared, mutable data and threads operating on the data. It encodes the affinity between tasks and memory partitions. The number n of places available to an X10 program (0 to n-1) and the mapping from places to nodes is specified by the user at launch time. The program starts by executing its main method at Place(0). Other places are initially idle.

#### 2.2.2 Activities

Every computation in X10 is an asynchronous activity, *akin* to a light-weight task, and runs in a place. The activities running in a place may access data located at that place with the efficiency of local access. An access to a remote place may take orders of magnitude longer and is performed using the **at** (**p**) **S** statement. An **at** statement shifts the control of execution of the current activity from the current place to place **p**, copies any data that is required by the statements **S** to **p**, and, at the end, returns the control of execution to the original place. The necessary data copying is done through runtime system calls inserted by the compiler.

X10's finish statement identifies the bounds of concurrency. All activities enclosed by a finish statement, including all nested activities, must complete before any statement subsequent to the finish can execute. X10's atomic blocks coordinate the mutation of shared data. The statement atomic S executes S in a single uninterrupted step. The conditional form of atomicity, when(c) S, executes S atomically when the condition c evaluates to true. X10 also supports dynamic barriers, called *clocks*, for synchronizing different phases of computation.

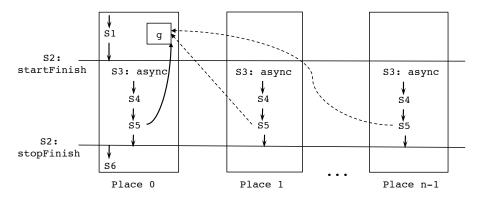

Figure 2.1 shows a snippet of X10 code. The statement **at** (**p**) **async** creates a new activity at place **p** to execute statements 4 and 5. The **for** loop ensures the creation of activities in all available places, as shown in Figure 2.2. The **finish** construct ensures termination of all activities before execution can proceed to statement 6.

```

S1: val g = GlobalRef[Cell[Double]](new Cell[Double](0));

S2: finish for (p in Place.places())

S3: async at (p) {

S4: val x = computeLocal();

S5: at (g) atomic g()() += x;

S2: }

S6: val y = g()();

```

Figure 2.1: An example using GlobalRef.

#### 2.2.3 Global References

An X10 variable resides in a single location: the place where it was allocated. A place cannot use or even directly refer to a variable in a different place. A special type, GlobalRef[T], allows explicit cross-place references. The data encapsulated in GlobalRef is intended to be shared by all threads of computation across different

Figure 2.2: Activities, places and global references.

places. In Figure 2.1, g (line 1) is a GlobalRef containing a reference to a value a of type Cell[Double]. GlobalRef[T] is the only way to produce or manipulate crossplace references in X10. The atomic construct guarantees isolation from concurrent activities through a mutually exclusive access to g.

#### 2.2.4 Distributed Arrays

X10 provides DistArrays to partition arrays across places. An underlying Dist object specifies which elements, or a range of elements should be allocated at different places. Dist uses subsidiary Region objects to abstract over the shape and dimensionality of arrays.

#### 2.2.5 Load Balancing

X10 employs a work-stealing scheduler to address any runtime load-imbalances within places. The work-stealing scheduler uses a pool of threads, called *workers*, to run programs. Each worker maintains a private double-ended queue – a deque – of pending tasks. A worker primarily operates on its own deque, pushing one activity to the bottom of the deque for each **async** construct it encounters. When a worker completes one activity, it pops the next activity to run from its deque. If the deque is empty, the worker attempts to steal a pending activity from the deque of a randomly selected worker. Since each worker primarily interacts with its own deque, contention is minimal and only arises with load imbalance. Moreover, a thief tries to grab an activity from the top of the deque whereas the victim always pushes and pops from the bottom, further reducing contention.

Available X10 releases do not yet support work stealing across places.

#### 2.3 Shared-Variable Coherence

Shared memory is integral to many high-performance programming systems. In a shared-memory system, processors may read and write to a single shared variable.

Unless care is taken, a processor may read a stale value of a variable, if multiple processors have access to multiple copies of the shared variable and at least one access is a write. Programming systems provide a set of rules, called *coherence protocols*, to ensure that multiple cached copies of shared variables are kept up-to-date. A read (or a write) access to a shared variable by a processor is referred to as a read hit (or a write hit) if the variable is available in the processor's local memory. If a processor cannot find the variable in its local memory, then the accesses is referred to as a read miss or a write miss.

Coherence protocols come in many variants but follow one of the following two policies when a processor writes to a shared variable.

Write Invalidate In the write-invalidate policy, a processor attempting to write to a shared variable initiates a coherence transaction to invalidate the copies in all other processors. Once the copies are invalidated, the requestor writes to the shared variable without the possibility of another processor reading the variable's old value. If another processor wishes to read the variable after its copy has been invalidated, it must initiate a new coherence transaction to obtain the variable, and it will obtain a copy from the processor that wrote it, thus preserving coherence.

Write Update In the write-update policy, a processor attempting to write to a shared variable initiates a coherence transaction to update the copies in all other processors to reflect the new value it wrote to the variable.

#### 2.3.1 Coherence Protocol for X10's Global References

The X10 coherence protocol that manages accesses to shared data in GlobalRefs is herein called the *X10Protocol*. Values protected in GlobalRefs are retrieved by the application operation g(). The X10Protocol maintains a unique copy of a GlobalRef and dictates guarded access to g(); it can only be called when g.home == here, where here is the *id* of the referencing place. The GlobalRef g, shown in Figure 2.2, is directly accessible to activities in Place 0 as shown by the solid black arrow.

Any operation, other than passing around a global reference or comparing two of them for equality, requires a place shift back to the home place of g, often with at(g.home), or simply at(g) (line 5). For instance, all accesses to g in Figure 2.2 from places 1 to n-1 requires shifting the activity to shift to Place 0, as indicated by the dashed arrows. For all remote accesses that occur as a result of place-shifting at-clause, the X10Protocol exchanges messages between places.

#### 2.4 Related APGAS Languages

Habanero-Java [17] and Chapel [19] belong to the same family of APGAS languages as X10. These languages differ in terms of their syntax and their support for different programming constructs. For instance, the syntax of Habanero-Java and X10 explicitly distinguish accesses to remote data from accesses to local data in order to keep the programmer aware of the costs involved. However, Chapel tends to make this distinction less explicit. If a Chapel task running on locale 0 (akin to a *place* in X10) wants to access a variable stored on locale 1, it can do so simply by naming the variable, relying on the compiler and runtime to provide the communication necessary to implement the remote reference. In contrast, X10 and Habanero-Java require programmers to explicitly specify the place of the remote data while accessing them.

Despite such differences, the fundamental mechanisms for mapping tasks, for managing the consistency of shared variables, and for workload partitioning are similar in these languages. They all suffer from the three fundamental limitations identified in this dissertation. Namely, the lack of a distinction between locality-flexible and locality-sensitive tasks limiting opportunities for load balancing, the support for naïve workload distribution resulting in a dynamic load imbalance, and the failure to employ augmented coherence-protocols to manage shared variables with different access patterns. As such, the conclusions drawn in this dissertation should be equally applicable to Chapel and Habanero-Java in addition to X10.

### Chapter 3

### Locality-Aware Task Migration

Balancing the computational workload of an application amongst available processors is critical for performance. A popular technique used to balance workload is task migration. Task migration assigns work to threads that are in idle or underloaded states for lack of work. An even distribution of workload reduces the number of processor cycles that are wasted on idle threads and improves performance. The resulting performance improvements are especially pronounced for tasks that perform significant amounts of computations and recursively generate more work for peer workers in a processor.

Task migration may have an adverse impact on performance. Migrating tasks may incur significant overhead. This overhead is due to bookkeeping and computation needed to determine the timing of task migration, the most favourable tasks for migration, and the best node to which a task should migrate [12, 29, 46]. The state explorations needed to make these decisions often require expensive data movement across the network and synchronization among multiple workers. Furthermore, task migration may also disrupt the affinity between tasks and data by launching tasks at idle or underloaded nodes rather than at nodes to which the tasks bear affinity. Therefore, many programming systems, including PGAS and APGAS, restrict task migration within shared-memory nodes to prioritize locality over load balance, and to minimize these overheads.

This chapter describes a novel insight that is key for the implementation of scalable task-migration strategies in distributed-memory systems: selective migration of tasks that are agnostic to the location of data strikes a balance between locality and load balance. We demonstrate this idea by implementing distributed work-stealing and work-dealing approaches to task migration in the X10 programming system.

#### 3.1 Selection of Tasks for Migration

Completely avoiding the overheads of task migration in distributed-memory systems is impractical. However, there are measures that can help reduce and mitigate these overheads and thereby reduce the amount of time that processors are idle. The processors may remain idle because of memory or input-output operations, or for lack of work. Migration of some tasks contributes more toward minimizing these idle times than others. This section describes a task model to identify such tasks. A task is favourable for migration to a remote processor if the task meets any of the following conditions:

- i) The processor's cache is warm for that task because the related data is already in its local memory. Therefore, there is no additional overhead in reloading a cold cache, or in copying the data from the remote processor.

- ii) The task is local to the remote processor because it is a subtask of some task migrated to that processor. Thus, no extra cost needs to be paid.

- iii) The task is coarse enough to overcome the cost of migration by keeping the target node busy for sufficient time to prevent frequent migrations.

- iv) The task encapsulates the data necessary for its computation.

A task that qualifies for migration is a *locality-flexible* task. A task that bears strong affinity to a processor is a *locality-sensitive* task. This distinction frees a runtime scheduler from making load-balancing decisions for expensive locality-sensitive tasks and focus only on locality-flexible tasks. The designation of tasks as sensitive or flexible can be done in multiple ways: by an optimizing compiler, or by a runtime based on execution histories of similar tasks. It can also be done by a programmer using the algorithmic details and the semantic knowledge of the application, which may not be readily available through static or dynamic program analyses.

The proposition that locality information is beneficial is agnostic as to where such annotations come from. The prototype for the evaluation of this idea, presented in this chapter, relies on programmer-specified locality hints to identify locality-flexible tasks. This approach requires minimal changes to the X10 programming system.

#### 3.1.1 Locality-Flexible Tasks in Applications

Following is a description of two parallel applications, Delaunay Mesh Generation and Turing Ring. These applications illustrate the existence of locality-flexible tasks in applications and the need for distinguishing such tasks from locality-sensitive tasks. Then a discussion of Iterative Deepening A<sup>\*</sup> (IDA<sup>\*</sup>) and Unbalanced Tree Search (UTS) provides examples of applications where all tasks are locality-flexible.

A task's designated node, as specified in its source code, is herein called the *source* node. The node where the task is launched after migration is called the *target* node.

**Delaunay Mesh Generation** A Delaunay mesh generator creates a mesh of Delaunay triangles from a given set of points. The algorithm starts by initializing a work-list with the points to be processed, and by initializing the mesh with a single large triangle encompassing all the points. A triangulation procedure then picks a new point from the work-list, determines the triangle containing the point, creates a *cavity* by splitting the triangle into three new triangles that share the point, and performs re-triangulation until all the new triangles are valid Delaunay triangles. Initially, there is only one large triangle. However, as the triangulation process unfolds, the mesh gets populated with several new triangles. The points in these newly formed triangles can be processed in parallel because the final mesh is the same regardless of the order in which the points are processed. Thus, the intermediate triangles can be distributed among different nodes for parallel and distributed processing. The triangles allocated in each node create other Delaunay triangles using the points they enclose. Therefore, allocating triangles and their encapsulated points at the same node is crucial to minimize remote memory references.

An even distribution of the initially generated triangles among nodes does not guarantee a balanced workload throughout the mesh-generation process. The number of points encapsulated by different triangles, and the number of re-triangulations needed for processing different points could be different. Some nodes might have to perform more triangulations than others. Therefore, a natural question arises: If a node is idle after processing all the points in its work-list, then would it be beneficial, performance-wise, to migrate a triangle with unprocessed points from other nodes?

The triangulation procedure is a task with the following properties: i) it encapsulates all the data necessary for its computation, eliminating the need for repeated remote memory references; ii) copying of the triangle and its points from the source node to the target node is necessary only once; iii) all the new triangles created by the target node have local access to other points in the triangle because they are already copied to the target node's local memory; and iv) it is coarse enough to keep the target node busy for sufficient time because it spawns several new tasks to process its points in parallel. Therefore, such a task is locality flexible and is favourable for migration to remote nodes.

**Turing Ring** The Turing ring problem simulates the interactions between predators and preys in a ring of cells. The algorithm (shown in Figure 3.1) initializes each cell with a number of predators and preys, and evenly distributes the ring across nodes. The algorithm iteratively updates the predator and prey populations accounting for their death, birth and migration. The population of predators and preys in each cell can be processed in parallel using async activities as shown in lines 5 and 7.

```

S1:

/* wl is a distributed ring of cells */

S2:

Worklist wl <- DistArray<Cell>

S3:

wl.initialize();

S4:

finish {

for each Cell c in wl async at (c.place) {

S5:

S6:

finish {

S7:

async c.updatePreyPop();

S8:

c.updatePredatorPop();

S9:

3

S10:

BodiesToMigrate mBodies = c.updateCellIDs();

S11:

wl.update(mBodies);

}

S12:

S13:

}

```

Figure 3.1: Pseudocode for the Turing Ring problem.

The populations of the cells can change by as much as two orders of magnitude in a

single iteration resulting in a load imbalance. There are two types of tasks that can be migrated to alleviate the load imbalance: i) the task that updates predator or prey populations (lines 7 or 8). Migration of such tasks requires copying all information about predators/preys in the cell — including their birth, death and migration rates — to the target node to compute the new population. The new population must then be copied back to the source node to permit re-distribution of bodies; ii) the outer task that performs all operations in a cell, including population update and migration of predators and preys. Migration of such tasks requires copying of entire cells to the target node. However, once the cell is copied, there is no need to copy the results back to the source node because all other operations (lines 5 - 8) on the cell are now local to the target node. Hence, no more remote memory references will be needed. Further, the migrated task makes work available for other co-located workers in the target node. Thus, the outer **async** that processes an entire cell is a locality-flexible task that is suitable for migration during load balancing.

The costs of executing async (line 7), and async at(p) (line 5) are different. The async construct works on data that is already in the place where the task is created and does not need to create data copies. However, the execution of async at (p) creates copies of all the values used in S to the place p. The locality-flexible approach applies to async at (p), *i.e.*, the scheduler is meant to migrate tasks operating on copies of data rather than place-resident data. Such tasks are precisely the ones that have poor locality, and hence, are annotated as *locality flexible*.

**IDA\* and UTS** Not all applications possess easily distinguishable *locality-flexible* and *locality-sensitive* tasks. Consider IDA\* and UTS algorithms for example. IDA\* performs a cost-bound depth-first search of a state-space from a given start state using a heuristic function and finds the optimal solution path to a goal state. The disjoint parts of the state space in IDA\* can be searched in parallel. The expansion of a state in IDA\* requires only the cost-bound and can occur independent of expansions of other states. Thus, all parallel tasks in IDA\* are *locality flexible*. Similarly, all tasks processing the nodes in UTS are also locality flexible because they do not bear affinity to data allocated at any single processor. However, the size of the subtrees generated upon expansion of different states in IDA\* and different nodes in UTS can vary significantly. Thus, it is difficult to statically identify such tasks and decide *a priori* whether migration of the task in hand can offset the associated overheads to yield performance benefits.

In such applications, the runtime system may migrate any randomly selected tasks. Experimental evaluations show that the proposed scheduling algorithms do not degrade performance on such applications as well, which are not particularly suited to locality-aware scheduling.

#### 3.2 Migration of Locality-Flexible Tasks

This work investigates the merits of locality-aware task migration by implementing distributed work-dealing and work-stealing schedulers. Under work dealing, the runtime scheduler dynamically adjusts the mapping of tasks to nodes to alleviate any load imbalance. Under work stealing, an idle worker in a node steals tasks from other co-located or remote workers. Both of these schedulers employ the same policy for task migration. A locality-flexible task may be migrated to an idle or an underloaded node only if the locality-flexible task's designated place is not idle or underloaded. These schedulers complement the existing work-stealing scheduler in X10 that operates only within shared-memory nodes.

#### 3.2.1 Work Dealing

The work-dealing scheduler maps all *locality-sensitive* tasks to their designated places. The scheduler must decide if task migration is both necessary and beneficial only for *locality-flexible* tasks.

A common approach to make these decisions is to compare the number of tasks assigned, the number of tasks pending, or the expected completion times of the tasks in different places. Such an approach entails several runtime explorations and computations across all places. This work relies on a simple heuristic that a place must be *underloaded* if any worker in the place fails to successfully steal work after n consecutive attempts. In the prototype implementation, n is the number of workers per node. The idea is to exploit the principle that if an idle worker fails to retrieve work from its co-located workers in n attempts, then it is most likely that most of the workers in the node are either idle, and thus also searching for surplus work, or do not have any extra work to be stolen. Thus, it would be beneficial, in terms of load distribution, to map a dynamically spawned *locality-flexible* task to this node. By uniquely learning from the stealing operations to initiate task migrations to underloaded nodes, this work prevents expensive book-keeping operations.

Migrating a task to a remote node by starving workers in the task's designated place is counter-productive – it incurs the overhead of task migration and that of unnecessary work stealing within a place. Therefore, the scheduler maps a *locality-flexible* task <code>async(p)</code> to the task's designated place <code>p</code> if <code>p</code> is underloaded. Only if <code>p</code> is not underloaded, the scheduler proceeds to identify an underloaded node in the cluster. Using this strategy, the work-dealing algorithm prioritizes the utilization of cores over the utilization of nodes.

#### Control-Logic for Work-Dealing

Algorithm 1 describes the control logic for work dealing. The work-dealing scheduler checks the boolean variable initiateWD – initially set to false – to determine if there is any load imbalance in the system. An idle worker in a place sets initiateWD to true if it fails to steal successfully in n consecutive attempts. Multiple workers in multiple nodes may be attempting to steal in their home places. The scheduler tracks all such underloaded or idle places using targetNode – a boolean array.

The scheduler scans the targetNode to find the first underloaded place, say q, in the cluster, and deals out work to that place. In preparation for sending a task to the chosen underloaded place q, the scheduler first sets targetNode(q.id) to false to indicate that the place will no longer be underloaded because it is about to

| Algorithm 1: Control logic for work dealing.                                                               |  |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| <b>Require:</b> A sequence of place-sensitive and place-flexible tasks                                     |  |  |  |  |  |  |  |  |  |

| $\langle \operatorname{async}_1(p), \operatorname{async}_2(p), \dots, \operatorname{async}_n(p), \rangle.$ |  |  |  |  |  |  |  |  |  |

| <b>Ensure:</b> Locality-aware mapping of tasks $\mathtt{async}_i(p)$ , and work dealing.                   |  |  |  |  |  |  |  |  |  |

| 1: for each place $\mathbf{p}_i$ in the Program do                                                         |  |  |  |  |  |  |  |  |  |

| 2: <b>if</b> local steal fails $n$ times consecutively <b>then</b>                                         |  |  |  |  |  |  |  |  |  |

| 3: atomic initiateWD $\leftarrow$ true                                                                     |  |  |  |  |  |  |  |  |  |

| 4: $atomic targetNode(i) \leftarrow true$                                                                  |  |  |  |  |  |  |  |  |  |

| 5: for each $async_i(p)$ in the Program do                                                                 |  |  |  |  |  |  |  |  |  |

| 6: <b>if</b> isPlaceFlexible(async <sub>i</sub> (p)) && !isTargetNode(p.id) && initiateWD                  |  |  |  |  |  |  |  |  |  |

| then                                                                                                       |  |  |  |  |  |  |  |  |  |

| 7: for id in targetNode $\setminus$ targetNode(p.id) do                                                    |  |  |  |  |  |  |  |  |  |

| 8: if (atomic targetNode(id)) then                                                                         |  |  |  |  |  |  |  |  |  |

| 9: $atomic targetNode(id) \leftarrow false$                                                                |  |  |  |  |  |  |  |  |  |

| 10: $initiateWD \leftarrow targetNode.reduce(Or)$                                                          |  |  |  |  |  |  |  |  |  |

| 11: create closure using body of $\operatorname{async}_i(p)$ activity                                      |  |  |  |  |  |  |  |  |  |

| 12: prepare closure for remote execution                                                                   |  |  |  |  |  |  |  |  |  |

| 13: create an async to run the closure at place(id); break                                                 |  |  |  |  |  |  |  |  |  |

| 14: else                                                                                                   |  |  |  |  |  |  |  |  |  |

| 15: perform locality-guided mapping of $async_i(p)$                                                        |  |  |  |  |  |  |  |  |  |

receive a task for execution. To decide whether work dealing needs to be employed on subsequently arriving  $\mathtt{async}_i(p)$  tasks, the  $\mathtt{targetNode}$  array is scanned to see if there are other places searching for surplus work and the  $\mathtt{initiateWD}$  variable is set accordingly. Then, using the  $\mathtt{async}_i(p)$ 's body, a closure is created. The closure is marked for remote execution and finally an  $\mathtt{async}$  activity is created at the chosen place q to run the closure. A worker in the idle or the underloaded place performs the book keepings to minimize interruptions on the operation of busy places.

#### 3.2.2 Work Stealing

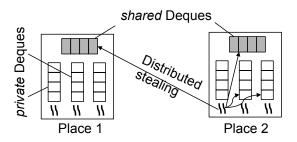

Under distributed work-stealing, local and remote workers may attempt to retrieve tasks from deques at the same time. Frequent steal requests from remote nodes may interfere with the operation of local workers in a node, thereby, significantly degrading the performance of the local workers. Thus, the key to scaling distributed work-stealing implementations is to use data structures that minimize the contention among local and remote workers. This work maintains separate deques for localityflexible and locality-sensitive tasks, and permits remote workers to steal only from the deques of locality-flexible tasks. Using multiple deques or specialized deques to reduce contention is a standard practice in scheduling [2, 3, 54]. The proposed distributed work-stealing algorithm maintains a *shared* deque and per-worker *private* deques in each place, as shown in Figure 3.2.

Tasks that bear affinity to a place are mapped to its *private* deque, while locality-flexible tasks are mapped to the *shared* deque. Under this scheme, each worker can operate on its private deque without interruptions from remote workers. The

Figure 3.2: Private deques offer a place-local view of locality-sensitive tasks and a shared deque offers a global view of locality-flexible tasks.

last-in-first-out access policy of a worker's private deque leads the local worker to execute the most recently created task and thus, offers a higher chance of exploiting cache locality. The shared deque, in contrast, is manipulated in a first-in-first-out manner to ensure that any steal operation, whether local or remote, receives the oldest task in the deque. Older tasks potentially contain the largest amount of work in the task graph leading thieves to remain busy for a longer period of time and reducing the overhead of frequent steals.

#### Control-Logic for Distributed Work-Stealing

Algorithm 2 shows the control-logic for distributed work-stealing. Load imbalances within a place are managed by X10's intra-place work-stealing scheduler. The algorithm first attempts to steal from other co-located workers, then from the local shared deque, and finally from the remote shared deque. A worker attempts distributed work-stealing only when: i) all the other co-located workers are either busy executing their own activity and do not posses surplus work to be stolen, or are themselves attempting to steal work; and, ii) the local shared deque is empty. The algorithm checks the boolean variable *active* determine whether there are any running activities in a place. The variable is set to true when a worker starts processing work from its deque. An idle node has the variable set to false. The algorithm checks the number of *spare* workers and the total number of workers (*i.e.*, *size*) in a node to determine if the node is underloaded.

Under distributed work-stealing, the thief — worker attempting a steal operation — holds a lock on the remote shared deque, retrieves an activity, creates a closure using the stolen activity, marks this closure for remote execution, and creates a new **async** activity at its home place to execute the closure. If the thief's attempt to steal from a remote worker fails, the thief first probes the network to see if any remote task has spawned tasks at its home place before continuing to explore other places. This approach eliminates unnecessary steal operations and also prevents polluting other place's caches. The thief continues this process until it finds work or until it has explored all available places.

| Algorithm 2: Async mapping & distributed work stealing                                                              |

|---------------------------------------------------------------------------------------------------------------------|

| <b>Require:</b> A sequence of locality-sensitive and locality-flexible tasks                                        |

| $\langle \texttt{async}_1(\texttt{p}), \texttt{async}_2(\texttt{p}), \dots, \texttt{async}_n(\texttt{p}), \rangle.$ |

| <b>Ensure:</b> A mapping of tasks $\mathtt{async}_i(p)$ to private or shared deques, task                           |

| execution strategy and distributed work stealing.                                                                   |

| 1: for each $async_i(p)$ in the Program do                                                                          |

| 2: <b>if</b> $lisPlaceFlexible(async_i(p))$ then                                                                    |

| 3: map $\operatorname{async}_i(p)$ to a private deque of place p                                                    |

| 4: else if !isActive(p)    spares>0    size(p) <max_threads td="" then<=""></max_threads>                           |

| 5: map $\operatorname{async}_i(p)$ to a private deque of place p                                                    |

| 6: <b>else</b>                                                                                                      |

| 7: map $\operatorname{async}_i(p)$ to the shared deque of place p                                                   |

| // Control logic for local and distributed work-stealing policies                                                   |

| 8: activity $\leftarrow$ poll the private deque                                                                     |

| 9: while !activity and !terminated do                                                                               |

| 10: activity $\leftarrow$ probe the network for incoming tasks                                                      |

| 11: <b>if</b> lactivity <b>then</b>                                                                                 |

| 12: activity $\leftarrow$ steal from co-located workers                                                             |

| 13: if !activity then                                                                                               |

| 14: activity $\leftarrow$ steal from the shared deque in its place                                                  |

| 15: if !activity then                                                                                               |

| 16: remoteVisits++                                                                                                  |

| 17: activity $\leftarrow$ steal from remote place's shared deque                                                    |

| 18: $p_{visited}.add(remotePlaceVisited)$                                                                           |

| // Distributed Work-stealing                                                                                        |

| 19: for $p_j$ in places $\langle p_{visited} \wedge p_i \mathbf{do} \rangle$                                        |

| 20: activity $\leftarrow$ atomically poll from the shared deque of $p_j$                                            |

| 21: if lactivity then                                                                                               |

| 22: create <b>closure</b> using the body of activity                                                                |

| 23: annotate activity to prepare it for remote execution                                                            |

| 24: async at $(p_j)$ closure                                                                                        |

| 25: <b>else</b>                                                                                                     |

| 26: break                                                                                                           |

#### 3.3 Experimental Evaluation

This section describes the experimental setup and discusses the main findings from the performance evaluation.

#### 3.3.1 Experimental Setup

*Platform:* Our performance measurements use a blade server with 16 nodes, each featuring two 2 GHz Quad-Core AMD Opteron processors, with 8 GB RAM, 64KB L1 cache, 512KB L2 cache, 2MB L3 cache, and 20 GB of swap space, running CentOS GNU/Linux version 6.0.

Compiler and Runtime: The x10c++ compiler version 2.2 is used for measurements and the command-line arguments -0 -N0\_CHECKS are passed to the compiler to enable optimizations and disable array bounds, null pointer, and place checking. The nodes in the cluster are connected by an InfiniBand network with a bandwidth of 10 Gbit/s and use the MVAPICH2 library for communication. The experimental runs set X10\_NTHREADS=8 to create eight worker threads per place and vary the number of places from 1 to 16 so that the number of threads is the same as the total number of cores available.

Applications: The experimental evaluation uses applications with unstructured data and irregular parallelism because they present significant opportunities for load balancing. These include the following applications from the Cowichan suite [59, 76]: i) Quicksort sorts an array of 100M elements using quick-sort; ii) Turing ring solves a set of coupled differential equations modelling system dynamics using 1M bodies; iii) k-Means implements a k-means clustering algorithm resulting in four clusters and using 1000 iterations; and iv) n-Body simulates the forces acting on a system of 220K bodies using the Barnes-Hut algorithm. The evaluation also uses the following applications from the Lonestar suite [44], that we ported from the Galois framework to the X10 language for distributed-memory systems: v) Agglomerative clustering performs clustering of 2M points by building a hierarchical tree in a bottom-up manner; vi) Delaunay mesh generation (DMG) deals with 2D Delaunay triangular mesh generation using 80,000 points; and vii) Delaunay mesh refiner (DMR) refines a Delaunay mesh of 550K triangles such that no angle in the mesh is less than 30°.

*Methodology:* Each application is run 10 times to account for variances, such as work-stealing in the runtime, and scheduling policies in the operating system. The performance charts do not show the 95% confidence intervals because they are small.

#### 3.3.2 Results and Discussion

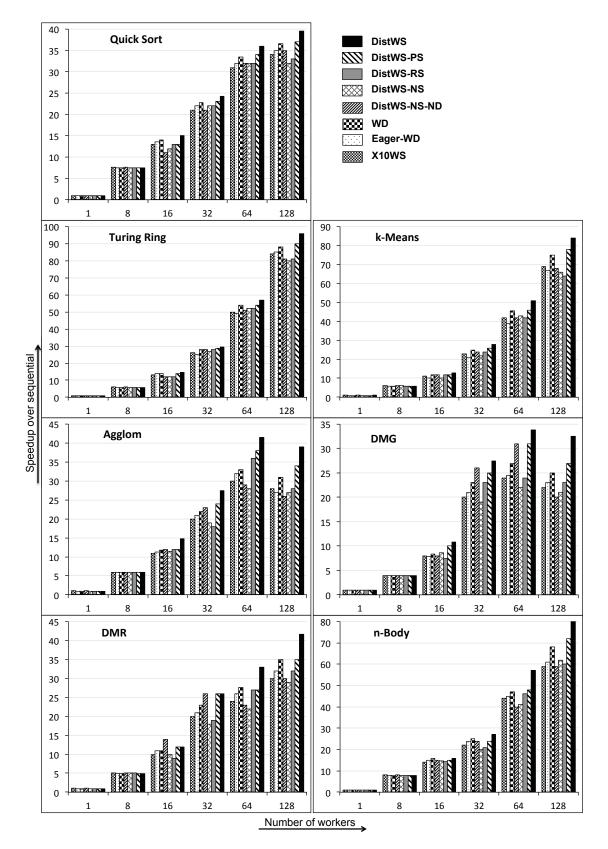

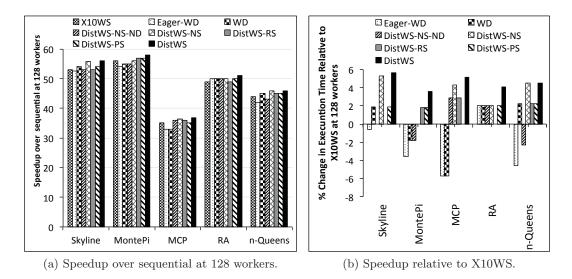

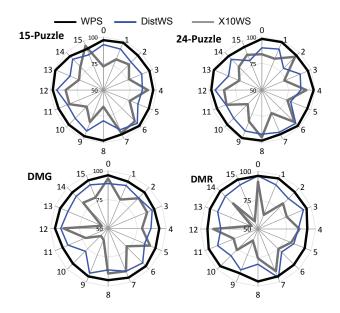

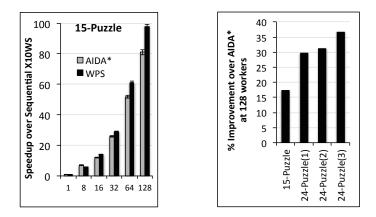

The evaluation compares the performance of eight different schedulers:

- i) X10WS is X10's existing intra-node work-stealing scheduler.

- ii) WD combines X10WS with the distributed work-dealing scheduler.

- iii) Eager-WD proactively maps each *locality-flexible* task in a load-balance-aware manner rather than waiting until the occurrence of a load-imbalance.

- iv) DistWS combines X10WS with the distributed work-stealing scheduler.