#### Hardware-Efficient Logarithmic Floating-Point Multipliers for Error-Tolerant Applications

by

Zijing Niu

A thesis submitted in partial fulfillment of the requirements for the degree of

Master of Science

$\mathrm{in}$

Integrated Circuits and Systems

Department of Electrical and Computer Engineering University of Alberta

© Zijing Niu, 2023

# Abstract

The deployment of computation-intensive applications, such as digital signal processing (DSP) and machine-learning (ML), on resource-constrained applications is spurring research that aims to increase the power efficiency of the arithmetic circuits that perform a huge amount of computation. Approximate computing is one of the emerging strategies to reach this objective. Neural networks (NNs) involve extensive multiply-and-accumulate computations, especially in the training process, where iterative computations incur significant energy consumption. DSP applications, such as image processing, also demands intensive arithmetic computations. In this research project, we focus on the design of hardware-efficient floating-point (FP) multipliers for the energy-efficient implementation of error-tolerant computation-intensive applications using approximate computing techniques.

As an alternative to the conventional FP representation, the logarithmic representation of FP numbers has been considered for the acceleration of NNs. We show that the FP representation is naturally suited for the binary logarithm of numbers and, thus, logarithmic arithmetic. In this thesis, two logarithmic approximation methods are proposed to generate double-sided error distributions that mitigate the accumulative effect of errors introduced in both the logarithm conversion and the anti-logarithm conversion. Hardware-efficient logarithmic FP multipliers are then proposed by using simple operators, such as adders and multiplexers, to replace complex conventional FP multipliers. The radix-4 logarithm is considered to further reduce the hardware complexity. The proposed multipliers provide superior trade-offs between accuracy and hardware, with up to 30.8% higher accuracy than a recent logarithmic FP design or up to  $68 \times$  less energy than the conventional FP multiplier. Using the proposed FP logarithmic multipliers in JPEG image compression achieves higher image quality than the recent multiplier design with up to 4.7 dB larger peak signal noise ratio. For training in benchmark NN applications, including a 922-neuron model for the MNIST dataset, the proposed FP multipliers can slightly improve the classification accuracy while achieving  $4.2 \times$  less energy and  $2.2 \times$  smaller area than a state-of-the-art design.

## Preface

This dissertation presents original work in the field of approximate computing by Zijing Niu.

The review of approximate multipliers in Chapter 2 was partially published as T. Zhang, Z. Niu and J. Han, "A Brief Review of Logarithmic Multiplier Designs," IEEE 23rd Latin American Test Symposium (LATS), 2022, pp. 1-4. T. Zhang and I collaboratively reviewed literature and drafted the article.

One of the logarithmic multiplier designs, presented in Chapter 3 to Chapter 6, was published in GLSVLSI'21, Proceedings of the 31st IEEE/ACM Great Lakes Symposium on VLSI, 2021, as "A Logarithmic Floating-Point Multiplier for the Efficient Training of Neural Networks." Z. Niu, H. Jiang, M. Ansari, B. Cockburn, L. Liu, and J. Han. I devised the logarithmic multiplier, carried out the simulations and circuit synthesis, and composed the article. I also presented the article at the conference. Dr. H. Jiang provided an original idea of improving the logarithmic multiplier designs and revised the manuscript. Dr. J. Han supervised this work and revised the manuscript together with Dr. B. Cockburn, Dr. M. Ansari and Dr. L. Liu. The other logarithmic multiplier designs, presented in Chapter 3 to Chapter 6, are presented in a manuscript in preparation for submission. I devised the logarithmic multiplier designs, performed the error analysis and circuit synthesis, implemented error-tolerant applications, including neural networks and JPEG compression, using the proposed designs and completed the manuscript. T. Zhang provided many technical suggestions for improving the design and manuscript. H. Jiang provided the MATLAB code for JPEG compression and useful suggestions for the simulation of neural network applications. Dr. J. Han and Dr. B. Cockburn provided valuable suggestions to improve the structure and the technical content of the manuscript.

# Acknowledgements

Words cannot express my deepest gratitude to my supervisor Dr. Jie Han for his generous guidance and unlimited support throughout my graduate study. Thanks for providing insights and professional advice for solving research problems, offering invaluable advice to my personal development, and always being there when I needed support. I could not have undertaken this journey without Dr. Jie Han.

I greatly appreciate my collaborator Dr. Bruce Cockburn for his valuable suggestions on my research and manuscript writing. Thanks for his words of encouragement; it means a lot to me. I would also like to thank Dr. Honglan Jiang for her generous support and feedback on my publications. I learned so much from her work and the discussions with her.

I am grateful to all my colleagues in the research group and friends for their friendship and help. Many thanks to Tingting Zhang, Chengcheng Tang, Bailiang Liu, and Qichao Tao. Special thanks to Tingting Zhang, for her patience, late-night feedback sessions and moral support during my graduate study. Thanks to Zeyu Sun, Xiang Li, and Yuxiang Wang. Our friendships have added a lot to my life.

Most importantly, thanks to my beloved family for their unconditional love, understanding and financial support. My greatest thanks to my partner, Zhitao Nie, for his consistent love, company and encouragement. Their belief in me has kept my spirits and motivation high during this journey.

Lastly, I would like to thank my lovely cat, bubu, for all the entertainment and emotional support.

# **Table of Contents**

| 1        | Introduction |                                                                  |                                                          | 1  |

|----------|--------------|------------------------------------------------------------------|----------------------------------------------------------|----|

|          | 1.1          | Motiv                                                            | ation                                                    | 1  |

|          | 1.2          | Thesis Contributions                                             |                                                          |    |

|          | 1.3          | Thesis                                                           | s Outline                                                | 3  |

| <b>2</b> | Bac          | kgrou                                                            | nd                                                       | 4  |

|          | 2.1          | Theor                                                            | y of Logarithm Approximation                             | 4  |

|          | 2.2          | Review of Approximate Multipliers                                |                                                          | 5  |

|          |              | 2.2.1                                                            | Approximate Logarithmic Multipliers (LMs)                | 5  |

|          |              | 2.2.2                                                            | Approximate Floating-Point Multipliers                   | 6  |

|          | 2.3          | Error-                                                           | Tolerant Applications                                    | 7  |

|          |              | 2.3.1                                                            | JPEG Compression                                         | 7  |

|          |              | 2.3.2                                                            | Neural Networks                                          | 8  |

| 3        | Rep          | oresent                                                          | tation, Formulation and Approximation for Multiplication | 11 |

|          | 3.1          | FP Re                                                            | epresentation and Multiplication                         | 11 |

|          |              | 3.1.1                                                            | IEEE 754 FP Representation                               | 11 |

|          |              | 3.1.2                                                            | Floating-Point Multiplication                            | 12 |

|          |              | 3.1.3                                                            | Logarithmic Floating-Point Multiplication                | 12 |

|          | 3.2          | Logarithmic Approximation and Mathematical Formulations for Mul- |                                                          |    |

|          |              | tiplication                                                      |                                                          |    |

|          |              | 3.2.1                                                            | Logarithmic Multiplication 1                             | 13 |

|          |                         | 3.2.2                       | Logarithmic Multiplication 2                                   | 20 |  |

|----------|-------------------------|-----------------------------|----------------------------------------------------------------|----|--|

|          | 3.3                     | Theore                      | etical Error Analysis                                          | 25 |  |

| 4        | Circ                    | cuit De                     | esigns of Floating-Point Logarithmic Multipliers               | 30 |  |

|          | 4.1                     | A Gen                       | eric Circuit Architecture                                      | 30 |  |

|          | 4.2                     | FP Logarithmic Multiplier-1 |                                                                |    |  |

|          |                         | 4.2.1                       | Logarithm approximation and addition of approximate logarithms | 31 |  |

|          |                         | 4.2.2                       | Anti-logarithm approximation and value adjustment              | 34 |  |

|          |                         | 4.2.3                       | Addition of exponents and value adjustment                     | 34 |  |

|          | 4.3                     | FP Lo                       | garithmic Multiplier-2                                         | 35 |  |

|          |                         | 4.3.1                       | Logarithm approximation and addition of approximate logarithms | 35 |  |

|          |                         | 4.3.2                       | Anti-logarithm approximation and value adjustment              | 35 |  |

|          |                         | 4.3.3                       | Addition of exponents and value adjustment                     | 37 |  |

|          | 4.4                     | Design                      | s using the Radix-4 Logarithm                                  | 37 |  |

|          | 4.5                     | Optim                       | ization for Reduced Bit-Width in the Mantissa                  | 38 |  |

| <b>5</b> | Per                     | forman                      | ce Evaluation                                                  | 41 |  |

|          | 5.1                     | Accuracy Evaluation         |                                                                |    |  |

|          |                         | 5.1.1                       | Error Assessment                                               | 41 |  |

|          |                         | 5.1.2                       | The Relation between FP Precisions and Error Behavior          | 42 |  |

|          | 5.2                     | Hardw                       | are Evaluation                                                 | 49 |  |

| 6        | Application Evaluations |                             |                                                                |    |  |

|          | 6.1                     | JPEG                        | Compression                                                    | 51 |  |

|          |                         | 6.1.1                       | Experimental Setup                                             | 51 |  |

|          |                         | 6.1.2                       | Evaluation Results                                             | 52 |  |

|          | 6.2                     | Neural                      | Network Applications                                           | 53 |  |

|          |                         | 6.2.1                       | Experimental Setup                                             | 53 |  |

|          |                         | 6.2.2                       | Evaluation Results                                             | 56 |  |

7 Conclusions 64 Bibliography 66

# List of Tables

| 5.1 | Error Metrics for the Multipliers                                   | 43 |

|-----|---------------------------------------------------------------------|----|

| 5.2 | Circuit Measurements of the FP Multipliers                          | 50 |

| 6.1 | JPEG compression using FP multipliers for the four precisions       | 54 |

| 6.2 | PSNR (dB) for JPEG Compression using FP LMs with Different Pre-     |    |

|     | cisions                                                             | 55 |

| 6.3 | Average classification accuracy of three datasets with LMs for four |    |

|     | precision levels                                                    | 62 |

| 6.4 | Circuit Assessment of the Artificial Neuron                         | 63 |

# List of Figures

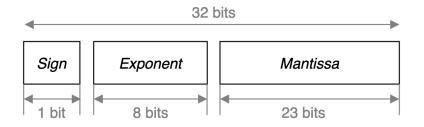

| 3.1 | The IEEE-754 single-precision format.                                                                                                                                   | 11 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

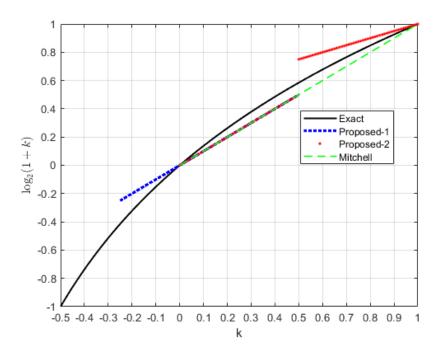

| 3.2 | Approximations of $\log_2(1+k)$                                                                                                                                         | 15 |

| 3.3 | Approximations of $2^l$                                                                                                                                                 | 15 |

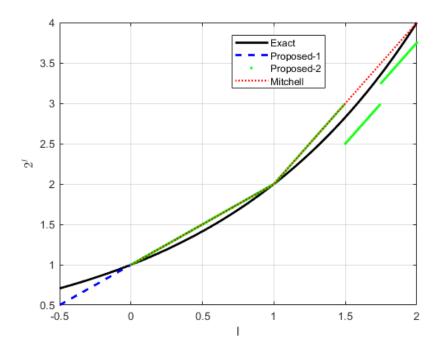

| 3.4 | $\varepsilon_1(k_i) + \varepsilon_1(k_j)$ , $\varepsilon_2(l)$ , and $\varepsilon_{tot}$ with respect to $\alpha(k_i) + \alpha(k_j)$ under the                          |    |

|     | three situations for the proposed approximation method-1                                                                                                                | 18 |

| 3.5 | Overall approximation error of the logarithm and anti-logarithm con-                                                                                                    |    |

|     | versions for the proposed approximation method-1. $\ldots$                                                                                                              | 19 |

| 3.6 | $\varepsilon_1(k_i) + \varepsilon_1(k_j), \ \varepsilon_2(l), \ \text{and} \ \varepsilon_{tot} \ \text{for} \ 1.5 \le \alpha(k_i) + \alpha(k_j) < 2. \ \ldots \ \ldots$ | 23 |

| 3.7 | Overall accumulated errors of the logarithm and anti-logarithm con-                                                                                                     |    |

|     | versions for the proposed approximation method-2                                                                                                                        | 24 |

| 3.8 | The contour maps of the theoretical error (error = exact - approximate)                                                                                                 |    |

|     | with respect to $x_A$ and $x_B$ for the multiplication-1 algorithm                                                                                                      | 28 |

| 3.9 | The contour maps of the theoretical error (error $=$ exact - approximate)                                                                                               |    |

|     | with respect to $x_A$ and $x_B$ for the multiplication-2 algorithm                                                                                                      | 29 |

| 4.1 | The generic circuit architecture for proposed designs                                                                                                                   | 32 |

| 4.2 | The circuit design of the first proposed floating-point logarithmic mul-                                                                                                |    |

|     | tiplier, FPLM-1.                                                                                                                                                        | 33 |

| 4.3 | The circuit design of the second proposed floating-point logarithmic                                                                                                    |    |

|     | multiplier, FPLM-2.                                                                                                                                                     | 36 |

| 4.4 | The simplified multiplier designs for the FP8 format. $\ldots$ $\ldots$ $\ldots$                                                                                        | 40 |

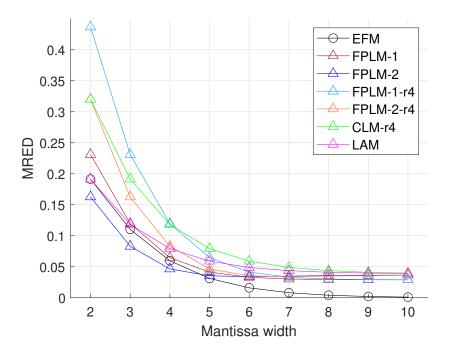

| 5.1 | MREDs of the multipliers as a function of the mantissa width                                                                                                            | 46 |

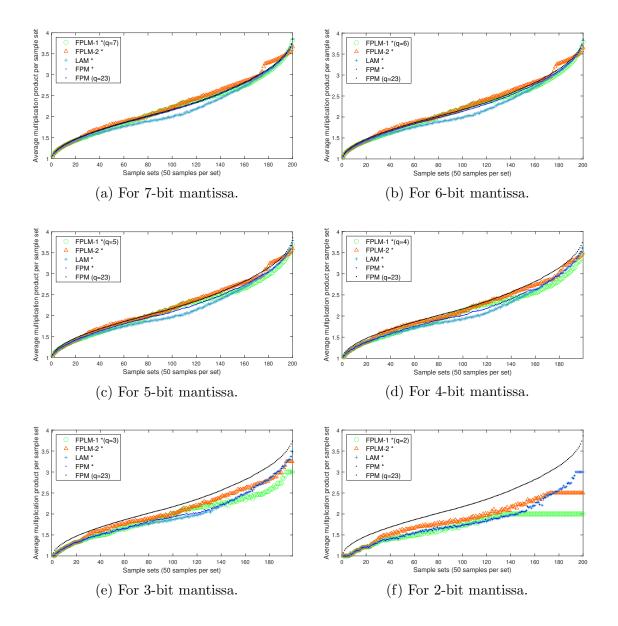

| 5.2 | Average product of each sample set (50 samples per set) for FPLM-1,     |    |

|-----|-------------------------------------------------------------------------|----|

|     | FPLM-2, LAM [3] and FPM with reduced mantissa width (from 7-            |    |

|     | bit to 2-bit) compared to the single-precision FPM (mantissa width of   |    |

|     | 23-bit)                                                                 | 47 |

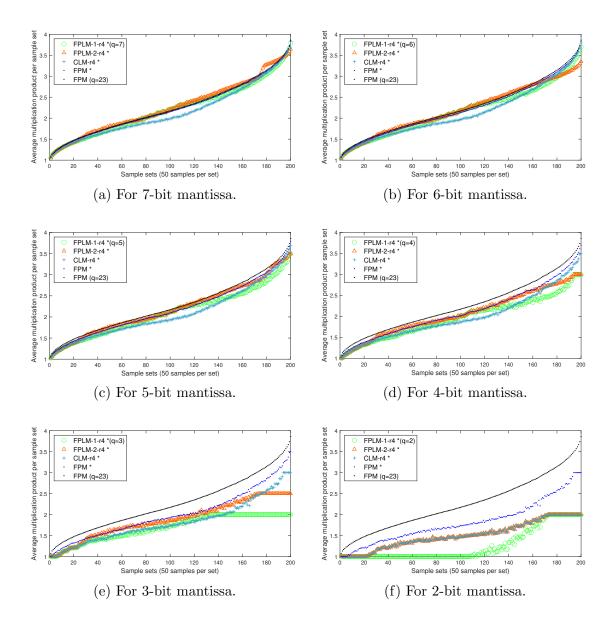

| 5.3 | Average product of each sample set (50 samples per set) for FPLM-1-     |    |

|     | r4, FPLM-2-r4, CLM-r4 and FPM with reduced mantissa width (from         |    |

|     | 7-bit to 2-bit) compared to the single-precision FPM (mantissa width    |    |

|     | of 23-bit)                                                              | 48 |

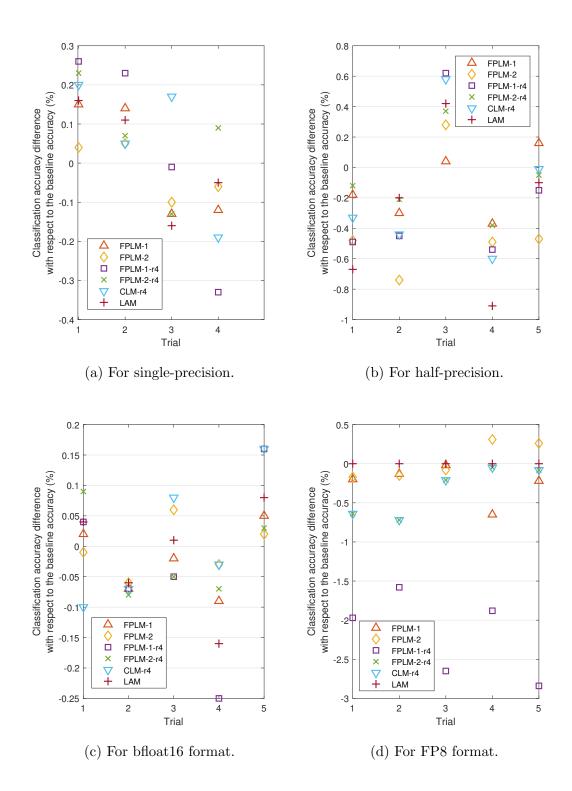

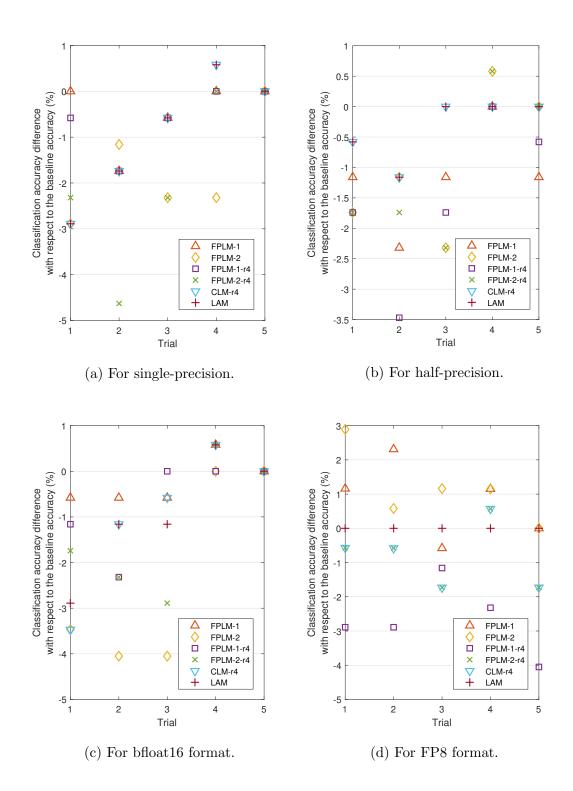

| 6.1 | Comparison of the classification accuracy of the MNIST dataset with     |    |

| 0.1 | - v                                                                     |    |

|     | LMs for four precision levels: a negative percentage means a decrease   |    |

|     | and a positive percentage means an increase in the accuracy with re-    |    |

|     | spect to using accurate multipliers.                                    | 59 |

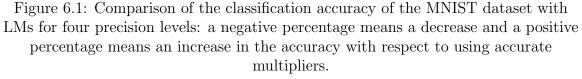

| 6.2 | Comparison of the classification accuracy of the HARS dataset with      |    |

|     | LMs for four precision levels: a negative percentage means a decrease   |    |

|     | and a positive percentage means an increase in the accuracy with re-    |    |

|     | spect to using accurate multipliers                                     | 60 |

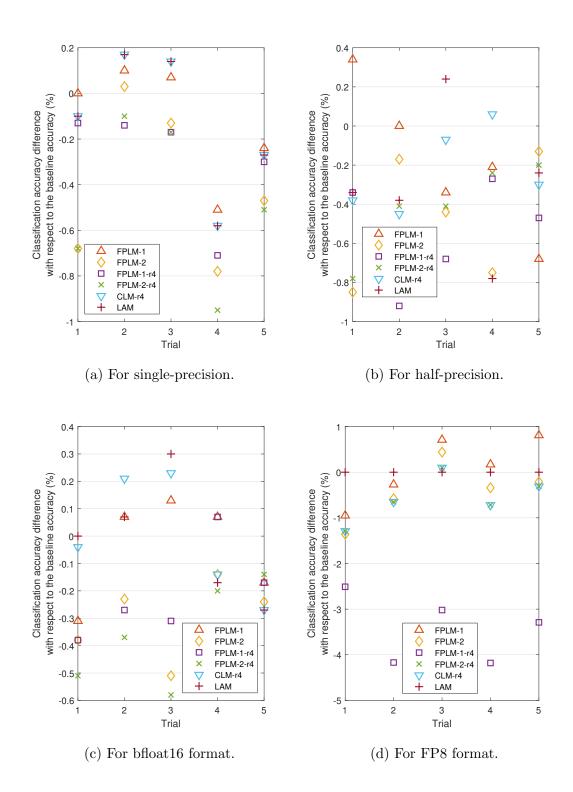

| 6.3 | Comparison of the classification accuracy of the Fourclass dataset with |    |

|     | LMs for four precision levels: a negative percentage means a decrease   |    |

|     | and a positive percentage means an increase in the accuracy with re-    |    |

|     | spect to using accurate multipliers                                     | 61 |

|     |                                                                         |    |

# List of Abbreviations

- AC Approximate Computing.

- AE Average Error.

**AMBE** Approximate Modified Booth Encoding in [1].

Bfloat16 Brain FP.

**CFPU** Configurable Floating-point Unit in [2].

**CMOS** Metal–oxide Semiconductor.

**DCT** Discrete Cosine Transform.

**DSP** Digital Signal Processing.

FP Floating-Point.

**FPM** Floating-point Multiplier.

**IDCT** Inverse Discrete Cosine Transform.

- **ILM** Iterative Logarithmic Multiplier.

- **JPEG** Joint Photographic Experts Group.

- KNN K-nearest Neighbor.

LAM Logarithmic Approximate Floating-point Multiplier in [3].

- **LM** Logarithmic Multiplier.

- LOA Lower-part-Or Adder in [4].

MAA3 Approximate Mirror Adder in [5].

MAC Multiply-ACcumulate.

ML Machine Learning.

MLP Multi-layer Perceptron.

**MRED** Mean Relative Error Distance.

**NN** Neural Network.

**NOD** Nearest-one Detector in [6].

**PSNR** Peak Signal Noise Ratio.

R4L Radix-4 Logarithm.

**ReLU** Rectified Linear Unit.

# Chapter 1 Introduction

### 1.1 Motivation

Due to further scaling of complementary metal–oxide semiconductor (CMOS) technology, power density has significantly increased in integrated circuits. The substantial increase in energy becomes a limiting factor for computation-intensive applications, such as machine learning (ML) and digital signal processing (DSP), in resource-constrained devices [7][8]. The computations in many important recent applications involves massive multiply-accumulate (MAC) operations, which requires a significant amount of energy. This challenge motivates the development of more efficient arithmetic circuit implementations for emerging computing systems.

Many computation-intensive applications, such as image processing and neural networks (NNs), that produce results for human perception, can successfully tolerate a degree of computational error [9]. Approximate computing (AC) has emerged as a promising strategy to improve the energy efficiency in such systems [10]. In particular, AC has extensively been exploited in hardware implementations, including approximate arithmetic circuit designs, voltage over-scaling and precision scaling techniques [11], [12].

Floating-point (FP) arithmetic is often favored in applications that require sufficient relative accuracy over a wide dynamic range. Moreover, since FP MAC circuits, especially the multipliers therein, dominate the power dissipation and circuit area, efficient FP multiplier design has been of interest [1]–[3], [13]–[15]. Nevertheless, FP multipliers are relatively underexplored compared to their fixed-point counterparts and only a few of them have been applied to applications, such as image processing and, particularly, the training process of NNs. Bit width reduction of the FP representation for the training of NNs increase efficiency [16][17]. However, it can cause a significant deterioration on accuracy. Therefore, designs of approximate FP multipliers are promising to further improve the hardware performance for error-tolerant applications.

As an alternative to the conventional FP representation, logarithmic representations of FP numbers have been considered for the acceleration of NNs. For example, Lognet shows that logarithmic computation can enable more accurate encoding of weights and activations that results in higher classification accuracies at low resolutions [18]. A state-of-the-art 4-bit training strategy for deep NNs was developed for the logarithmic radix-4 representation [19]. Hence, efficient FP logarithmic multipliers (LMs) have become promising for NN training. Significant progress has been made in exploiting reduced-precision integers for inference, while 8-bit FP numbers [20] and logarithmic 4-bit FP numbers [19] have shown their effectiveness in the training of deep NNs.

### **1.2** Thesis Contributions

In this research project, we propose five energy-efficient FP LMs for error-tolerant, computation-intensive applications. Two novel approximation methods are described for the logarithm and anti-logarithm conversions that generate double-sided error distributions. The multiplier designs consist of simple operators, such as adders and multiplexers, which lead to lower power consumption and area cost compared to the conventional FP multipliers. Finally, the application-level performance of the proposed FP multipliers is evaluated for an image processing application and several benchmark NNs. It was also found that the classification accuracy can be slightly

improved in some cases with a significant reduction in energy consumption.

The novel contributions in this work are summarized as follows:

- Two novel approximation methods that generate double-sided error distributions in logarithm and anti-logarithm conversions to minimize the accumulation error.

- Five FP LMs are designed with circuit optimizations. Especially, a radix-4 logarithm (R4L) is developed for further reducing the hardware complexity.

- A detailed and comprehensive error evaluation is presented for four different FP precision formats. In particular, the relation between the FP precision format and the error behavior of the multipliers is analyzed.

- The proposed designs are evaluated in the JPEG compression and the training process of NNs to improve the hardware efficiency.

## 1.3 Thesis Outline

The remainder of this thesis is organized as follows. In Chapter 2, the background and the related work are reviewed. Chapter 3 introduces the proposed logarithmic approximation methods and logarithmic multiplications. A detailed error analysis for the approximation error and the proposed logarithmic multiplications are also presented. Circuit designs of five proposed FP multipliers and the radix-4 logarithm hardware reduction approach are illustrated in Chapter 4. Their performance in accuracy and hardware are also shown. Chapter 5 presents case studies for errortolerant applications. Finally, conclusions are provided in Chapter 6.

# Chapter 2 Background

In this chapter, the theory that underlies logarithm approximation, various approximate multipliers and the background on the error-tolerant applications are introduced.

## 2.1 Theory of Logarithm Approximation

Let Z be a number in the binary representation  $Z = 2^e(1+k)$ , where  $k \ (0 \le k < 1)$ denotes the fractional part and e is the exponent. Mitchell first proposed a simple method for a logarithmic conversion, given by [21]:

$$\log_2 Z \cong e + k. \tag{2.1}$$

If  $\log_2(1+k)$  is approximated by l, then Mitchell's anti-logarithm approximation can be expressed as:

$$2^l \cong l+1, \tag{2.2}$$

where  $0 \leq l < 1$ .

Mitchell's approximation offers both high speed and low hardware cost. However, it always underestimates the true logarithm, which cause negative errors to accumulate in MAC operations. To produce a double-sided error distribution, a nearest-one logarithmic approximation finds the nearest power of two for Z [6]. When  $Z - 2^e < 2^{e+1} - Z$ , it uses the same logarithm as Mitchell's method; otherwise, Z is given by  $Z = 2^{e+1}(1-y)$ , where  $0 \le y < 0.25$ , and thus the logarithm is approximated as:

$$\log_2 Z \cong e + 1 - y. \tag{2.3}$$

## 2.2 Review of Approximate Multipliers

#### 2.2.1 Approximate Logarithmic Multipliers (LMs)

Mitchell's approximation has been the basis for many proposed LMs. Operand decomposition improves the accuracy of Mitchell's approximation by dividing the two inputs into four inputs to reduce the number of '1's in the inputs [22]. An improved operand decomposition algorithm further reduces the energy consumption in LMs [23]. The iterative LM (ILM) improves the accuracy through a pipelined implementation with an error correction circuit that leads to iterative calculations of compensation terms [24]. A truncated ILM further reduces the hardware complexity [25]. A low-cost two-stage ILM compensates for errors in the addition of approximate logarithms [26].

To further improve the hardware efficiency, Mitchell's algorithm has been combined with other approximation techniques and optimized implementations of components. A customizable signed LM utilizes logarithmic approximation and truncation of operands, in which the one's complement representation is adopted to imprecisely handle negative numbers [27]. A cost-efficient two-stage logarithmic design uses a truncated LM in an iterative structure [26]. In both the non-iterative and iterative LMs, approximate adders are used to add the mantissas to reduce energy and improve accuracy [28]. A set-one adder (SOA) sets the lower significant bits as '1's to compensate the accumulated errors in sums generated in Mitchell's LM. The lower significant sum bits are computed using OR gates in the lower-part-or adder (LOA) and are set as one of the inputs in the approximate mirror adder (MAA3) [4] [5]. A two-stage LM employs different trimming strategies in the least significant parts of the input operands and the mantissas of the trimmed operands, which leads to lower energy and area cost [29]. A dynamic range LM relies on a truncation scheme to dynamically compensate for the accumulated errors generated by Mitchell's approximation [30].

Unlike Mitchell's approximation-based LMs, an improved LM uses the nearest-one logarithmic approximation method to produce double-sided error distributions [6]. A nearest-one detector (NOD) was proposed to first detect the nearest power of two and then produce the approximate logarithm.

#### 2.2.2 Approximate Floating-Point Multipliers

Truncation and voltage over-scaling techniques are commonly used for approximate FP multipliers [31]–[35]. A configurable approximate FP multiplier utilizes the K-nearest neighbor (kNN) algorithm to determine the truncation bits of a given input that can minimize energy and area [13]. Using Mitchell's approximation, a logarithmic approximate FP multiplier (LAM) improves the energy efficiency of NN training [3]. Moreover, configurable FP multipliers have been studied to provide different levels of accuracy in real-time [2] [14]. In [2], a configurable floating-point unit (CFPU) avoids multiplication by discarding one mantissa or adding and shifting two mantissas. The multiplication is also replaced with addition in a runtime configurable FP multiplier, using an accuracy tuning method [14]. However, neither of these two configurable FP multipliers completely eliminates multiplication since exact multiplication is still required when the error rate exceeds a pre-determined value.

Approximate fixed-point multipliers are required for the mantissa multiplication. For example, an approximate modified Booth encoding (AMBE) algorithm generates the partial products and then uses an inexact 4-2 compressor to optimize the mantissa multiplier [1]. This design also adopts bit truncation in the partial products to generate variable accuracy. Three approximate FP units are developed by proposing an approximate speculative multiplier and using gate-level pruning with an approximate speculative adder [15].

## 2.3 Error-Tolerant Applications

This section presents a brief background for the error-tolerant applications that involve intensive computations and discusses the usage of the hardware-efficient floatingpoint multipliers in these applications.

### 2.3.1 JPEG Compression

Joint Photographic Experts Group (JPEG) is a worldwide standard for the compression of digital images. The JPEG lossy compression algorithm uses the discrete cosine transform (DCT) for the encoding and decoding processes [36]. The DCT operation converts each image pixel from the spatial domain into the frequency domain. The high-frequency information is then discarded by using a quantization matrix. The image quality can be user-defined by setting a compression quality factor, which ranges from 1 to 100.

In the JPEG compression, an input image is first partitioned into blocks of  $8 \times 8$  pixels for the DCT coding. Let the pixel of the input image be i[x, y], an  $8 \times 8$  DCT coefficient matrix, denoted by I[p, q], for each  $8 \times 8$  pixel block is obtained by [37]:

$$\boldsymbol{I}[\boldsymbol{p}, \boldsymbol{q}] = \frac{C[\boldsymbol{p}]C[\boldsymbol{q}]}{4} \sum_{x=0}^{7} \sum_{y=0}^{7} i[x, y] \cos \frac{(2x+1)p\pi}{16} \cos \frac{(2y+1)q\pi}{16}$$

(2.4)

where  $0 \le p, q \le 7$ , and C[p] (or C[q]) is expressed as:

$$C[p] = \begin{cases} \frac{1}{\sqrt{2}}, & p = 0, \\ 1, & 1 \le p \le 7. \end{cases}$$

(2.5)

Then, the quantization is done by multiplying each DCT coefficient matrix, I[p, q], with an quantization matrix that is determined by the compression quality factor (Q[p, q]). Thus, the quantized coefficient matrix is given by:

$$I_{qt}[p,q] = round(\frac{I[p,q]}{Q[p,q]}).$$

(2.6)

By computing the de-quantization and the inverse discrete cosine transform (IDCT):

$$I_{dqt}[p,q] = I_{qt}[p,q] \times Q[p,q], \qquad (2.7)$$

the input image is reconstructed as:

$$j[x,y] = \sum_{p=0}^{7} \sum_{q=0}^{7} \frac{C[p]C[q]}{4} \boldsymbol{I_{dqt}}[\boldsymbol{p,q}] \cos\frac{(2x+1)p\pi}{16} \cos\frac{(2y+1)q\pi}{16}$$

(2.8)

where  $0 \le x, y \le 7$ . Finally, the reconstructed input image is obtained when the above operations are applied to all of the image blocks.

The JPEG compression algorithm involves considerable multiplications with real numbers, which leads to the use of approximate floating-point arithmetic that provides acceptable quality loss. Although fixed-point arithmetic can be used in the encoding and decoding processes, additional effort and time are required for the implementation and the wider range of floating-point representation provides better quality image recovery. Therefore, approximate floating-point multipliers can be beneficial for improving the hardware efficiency of the JPEG compression algorithm.

#### 2.3.2 Neural Networks

NNs are computational models that possess attractive characteristics of the biological NNs of the brain [38]. NNs perform tasks based on the machine learning algorithm that is able to learn from data. One of the most common tasks is classification, by which the input data is decided to belong to one among several possible categories. To solve the task, NNs process the data by artificial neurons and update the weights and biases through the training process consisting of feed-forward propagation and back propagation [39]. In the feed-forward process, the state of neurons in NNs is computed based on the output of neurons in the previous layer and is propagated to the following layer for further computation. As the basic unit of NNs, each neuron computes the sum of multiplication products of the inputs and their corresponding weights for the current layer. The sum is added with a bias and then passed to the activation function, which introduces non-linearity to the learning process. The basic computation for a neuron in the forward propagation can be expressed as:

$$a_k^l = \sigma(\sum_{i=1}^n w_{ik}^l x_i^{l-1} + b_k^l)$$

(2.9)

where  $a_k^l$  denotes the output value of the k-th neuron in the l-th layer,  $w_{ik}^l$  indicates the weight that connects the *i*-th neurons of the (l-1)-th layer, denoted by  $x_i^{l-1}$ , with the k-th neuron in the l-th layer, and  $b_k^l$  represents the bias value for the k-th neuron in the l-th layer. The sum is performed over the n neurons in the (l-1)-th layer.  $\sigma()$  indicates the activation function that maps the sum obtained in the range from -1 to 1 or from 0 to 1 [39]. Particularly, for the input layer,  $x_i^0$  represents the input data.

The outputs of neurons in the output layer are inspected by comparing with the target outputs. A loss function, denoted by L, is used to evaluate the training loss in the results of the feed-forward propagation. Since the training process aims to generate the weights and biases that are capable of performing the classification, the loss value needs to be minimized through the back-propagation. The gradient descent algorithm is usually adopted to minimize the loss function by scaling a small change in the weights and biases that lead to reduction in the loss value. The derivatives of L with respect to each weight and bias, i.e.,  $\frac{\partial L}{\partial w}$  and  $\frac{\partial L}{\partial b}$ , are computed first. For the k-th neuron in the l-th layer, the gradient of its output, denoted by  $\delta_k^l$ , is essential for computing  $\frac{\partial L}{\partial w}$  and  $\frac{\partial L}{\partial b}$ , given by:

$$\delta_k^l = \frac{\partial L}{\partial z_k^l} = \frac{\partial L}{\partial a_k^l} \sigma'(z_k^l) \tag{2.10}$$

where  $z_k^l = \sum_{i=1}^n w_{ik}^l x_i^{l-1} + b_k^l$ .  $\delta_k^l$  is expressed differently for the output layer and the hidden layers.  $\frac{\partial L}{\partial a_k^l}$  is computed directly with respect to the loss function for the output layer; however, when the *l*-th layer is a hidden layer,  $\frac{\partial L}{\partial a_k^l}$  is computed using the gradients in the next following layers, e.g., the (l + 1)-th layer. Thus,  $\delta_k^l$  for a hidden layer is expressed as:

$$\delta_k^l = (\sum_{k=1}^m w_{kj}^{l+1} \sigma_j^{l+1}) \sigma(z_k^l), \qquad (2.11)$$

where  $w_{kj}^{l+1}$  is the weight that connects the k-th neurons in the l-th layer with the *j*-th neuron in the (l + 1)-th layer. The sum is performed in the *m* neurons in the (l + 1)-th layer. Thus,  $\delta_k$  is computed recursively for each hidden layer in a backward direction. Therefore, the gradients of a weight and a bias,  $w_{ik}^l$  and  $b_k^l$ , are given by:

$$\frac{\partial L}{\partial w_{ik}^l} = \delta_k^l a_i^{l-1},\tag{2.12}$$

$$\frac{\partial L}{\partial b_k^l} = \delta_k^l. \tag{2.13}$$

The computation shown above is for a single input sample. Depending on different gradient descent optimization methods, such as the mini-batch gradient descent [40], the stochastic gradient descent [41], among others, the weights and biases are updated using a learning rate  $(\eta)$  and their gradients obtained from the u input samples. Let  $W'_v$  and  $B'_v$  denote the gradients of the weights and biases for a single input sample in a NN model, the weights and biases are updated by:

$$W \to W - \frac{\eta}{u} \sum_{v=1}^{u} W'_{v}, \qquad (2.14)$$

$$B \to B - \frac{\eta}{u} \sum_{v=1}^{u} B'_{v},$$

(2.15)

The training process requires a massive number of MAC computations in the iterative forward-propagation and back-propagation algorithms. These delicate computations, especially for the gradients, are performed by using the floating-point representation due to the wider range of numeric precision compared to the fixed-point representation. Therefore, the use of hardware-efficient floating-point arithmetic is advantageous for the training of NNs.

# Chapter 3

# Representation, Formulation and Approximation for Multiplication

## 3.1 FP Representation and Multiplication

#### 3.1.1 IEEE 754 FP Representation

The IEEE 754 standard defines the most commonly used formats for FP numbers. This format contains a 1-bit sign S, a w-bit exponent E and a q-bit mantissa M [42]. Fig. 3.1 shows the IEEE 754 representation of a single-precision FP number.

Figure 3.1: The IEEE-754 single-precision format.

In this format, a number N can be expressed in a base-2 scientific notation as follows:

$$N = (-1)^{S} \cdot 2^{E-bias} \cdot (1+x), \tag{3.1}$$

where S is either 0 for a positive number or 1 for a negative number. To ensure unsigned integers in the exponent field, a bias  $(2^{(w-1)} - 1)$ , such as 127 for the singleprecision, is added to the actual exponent value. E-bias denotes the actual exponent value of N. With the hidden '1', x is the fractional part of the FP number, and hence  $0 \le x < 1$ .

#### 3.1.2 Floating-Point Multiplication

In the IEEE 754 format, the FP multiplication involves three processes, including an XOR operation for the sign bits, the addition of the exponents, and the multiplication of the mantissa bits. Note that X is used to denote the actual mantissa, 1 + x, in the following formulation. Consider  $P = A \times B$ , which is computed as follows:

$$S_P = S_A \oplus S_B, \tag{3.2}$$

$$X_{AB} = (1 + x_A) \times (1 + x_B), \tag{3.3}$$

$$E_P = \begin{cases} E_A + E_B - bias, & X_{AB} < 2, \\ E_A + E_B - bias + 1, & otherwise, \end{cases}$$

(3.4)

$$X_P = \begin{cases} X_{AB}, & X_{AB} < 2, \\ X_{AB}/2, & otherwise, \end{cases}$$

(3.5)

where the sign bit, exponent and mantissa of A, B and P are respectively denoted with the corresponding subscripts. The exponent and mantissa of product P relate to the comparison of the obtained mantissa  $X_{AB}$  with 2. Note that (3.2) is valid for the sign computation of the proposed design, so it will not be discussed hereafter.

#### 3.1.3 Logarithmic Floating-Point Multiplication

For  $P = A \times B$  in the logarithm domain, the binary logarithmic multiplication converts the multiplication in (3.3) to an addition operation.

Assume that the logarithm, i.e.,  $\log_2(1 + x)$ , is approximated by a term denoted by  $\alpha(x)$ , then  $\log_2(X_{AB})$  is expressed as:

$$\log_2(X_{AB}) = \log_2(1+x_A) + \log_2(1+x_B) \cong \alpha(x_A) + \alpha(x_B).$$

(3.6)

Assume the anti-logarithm for  $2^{(\alpha(x_A)+\alpha(x_B))}$  is approximated by a term denoted by  $\beta(\alpha(x_A) + \alpha(x_B))$ , then  $X_{AB}$  is expressed as:

$$X_{AB} \cong 2^{(\alpha(x_A) + \alpha(x_B))} \cong \beta(\alpha(x_A) + \alpha(x_B)).$$

(3.7)

Finally,  $E_P$  and  $X_P$  are obtained as in (3.4) and (3.5). Note that  $\alpha$ () and  $\beta$ () are used for ease of presentation.

## 3.2 Logarithmic Approximation and Mathematical Formulations for Multiplication

Since Mitchell's approximation method computes underestimated products that lead to error accumulation in the MAC output, two novel approximation methods that produce a double-sided error distribution are proposed.

# 3.2.1 Logarithmic Multiplication 1

## Logarithmic FP Representation

The proposed approximation method-1 is based on the conversion of a logarithmic FP representation that differs from the IEEE 754 format. An FP number N is first converted into the format using its nearest power of two as per (2.3) and the corresponding mantissa. Since the IEEE 754 FP format provides the largest power of two smaller than N, by comparing the fraction x in (3.1) with 0.5, the nearest power of two can be determined for N.

If  $x \ge 0.5$ , N is closer to  $2^{E-bias+1}$  than  $2^{E-bias}$  (or equally away for the equal sign). The exponent E is incremented by 1 and, accordingly, the mantissa becomes  $\frac{1+x}{2}$ . In contrast, the exponent and mantissa of N remain the same as in (3.1) when x < 0.5. Let the converted exponent of N be denoted by E' and the converted mantissa by X'. Then E' and X' are given by:

$$E' = \begin{cases} E, & x < 0.5, \\ E+1, & x \ge 0.5, \end{cases}$$

(3.8)

$$X' = 1 + x' = \begin{cases} 1 + x, & x < 0.5, \\ \frac{1 + x}{2}, & x \ge 0.5, \end{cases}$$

(3.9)

where  $0.75 \le X' < 1.5$ .

#### Logarithm and Anti-logarithm Approximation

To better introduce the approximation method and its usage in multiplication, different notations are used. Consider the logarithm of 1 + k, i.e.,  $\log_2(1 + k)$  and the anti-logarithm of l, i.e.,  $2^l$ .

Due to the conversion in representation as per (3.9), the logarithm is applied to X'. Thus the range of 1 + k is [0.75, 1.5) and the logarithm approximation method-1 is applied over the domain  $-0.25 \le k < 0.5$ . Since l is obtained as the sum of the two approximate logarithms, its range is [-0.5, 1). Therefore, the anti-logarithm approximation method-1, as described in (2.2), is applied over the region of  $-0.5 \le l < 1$ .

The logarithm approximation method-1 of the function  $\log_2(1 + k)$  is shown in Fig. 3.2, where it is compared with Mitchell's method and the exact function. Note that method-1 computes the same underestimated results as Mitchell's method when both input operands are closer to  $2^{E-bias}$ . However, the input operands closer to  $2^{E-bias+1}$  are converted to overestimated logarithm values. As shown in Fig. 3.3, the anti-logarithm approximation method-1 produces the same overestimated results as Mitchell's method when l is in the range of [0, 1), whereas it underestimates the results when l is negative. As a result, the proposed approximation method-1 can compute either underestimated or overestimated results depending on the input operands.

#### **Approximation Error Analysis**

Denote the error introduced in the logarithm approximation by  $\varepsilon_1(k)$ . Then  $\varepsilon_1(k)$  for the proposed logarithm approximation method-1 is expressed as:

$$\varepsilon_1(k) = \log_2(1+k) - k,$$

(3.10)

where  $-0.25 \leq k < 0.5$ . When  $-0.25 \leq k < 0$ , the approximate logarithm, i.e.,  $\alpha(k) = k$ , is in the range of  $-0.25 \leq k < 0$  (recall that  $\alpha(k)$  denote the approximate result for computing the logarithm of k using a logarithm approximation), thus  $\varepsilon_1(k)$

Figure 3.2: Approximations of  $\log_2(1+k)$ .

Figure 3.3: Approximations of  $2^l$ .

is in the range of [-0.1650, -0.0044), where the negative error indicates an overestimated result. When  $0 \le k < 0.5$ ,  $0 \le \alpha(k) < 0.5$ ,  $\varepsilon_1(k)$  is within the range of [0, 0.0860), where the positive error indicates an underestimated result.

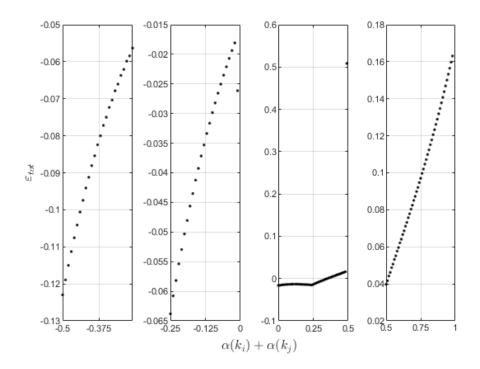

When adding the approximate logarithms of  $k_i$  and  $k_j$ , i.e.,  $\alpha(k_i)$  and  $\alpha(k_j)$ , the accumulated errors can be reduced due to the double-sided error distribution for  $\varepsilon_1(k)$ . Consider  $\varepsilon_1(k_i)$  and  $\varepsilon_1(k_j)$  to be the logarithm approximation errors for  $k_i$  and  $k_j$ , respectively. There are three scenarios when adding  $\alpha(k_i)$  and  $\alpha(k_j)$ , depending on the ranges of  $k_i$  and  $k_j$ :

- If  $-0.25 \leq k_i, k_j < 0, -0.5 \leq \alpha(k_i) + \alpha(k_j) < 0$ , then negative errors are accumulated, resulting in  $-0.3300 \leq \varepsilon_1(k_i) + \varepsilon_1(k_j) < -0.0088$ .

- If  $0 \le k_i, k_j < 0.5, 0 \le \alpha(k_i) + \alpha(k_j) < 1$ , then  $0 \le \varepsilon_1(k_i) + \varepsilon_1(k_j) < 0.1720$  due to the accumulated positive errors.

- If  $-0.25 \le k_i(k_j) < 0$  and  $0 \le k_j(k_i) < 0.5$ , then  $-0.25 \le \alpha(k_i) + \alpha(k_j) < 0.5$ , and the range of  $\varepsilon_1(k_i) + \varepsilon_1(k_j)$  is reduced to [-0.1650, 0.0816).

Let  $\varepsilon_2(l)$  denote the error introduced in the anti-logarithm approximation. Since  $l = \alpha(k_i) + \alpha(k_j)$  according to (3.7), we have  $-0.5 \leq l < 1$ . Then  $\varepsilon_2(l)$  for the proposed method-1 is given by:

$$\varepsilon_2(l) = 2^l - (l+1). \tag{3.11}$$

Positive errors, i.e.,  $0.0030 \le \varepsilon_2(l) < 0.2071$ , are generated when  $-0.5 \le l < 0$ , whereas non-positive errors are produced when  $0 \le l < 1$  since  $-0.0860 \le \varepsilon_2(l) < 0$ .

Errors introduced in the logarithm conversion and the anti-logarithm conversion are accumulated, contributing to the overall approximation error, denoted by  $\varepsilon_{tot}$ .  $\varepsilon_{tot}$  is computed as:

$$\varepsilon_{tot} = \varepsilon_1(k_i) + \varepsilon_1(k_j) + \varepsilon_2(l), \qquad (3.12)$$

where  $l = \alpha(k_i) + \alpha(k_j)$ .

The sum of the two approximate logarithms,  $\alpha(k_i) + \alpha(k_j)$ , is involved in the two conversion processes, as it outputs from the logarithm conversion and is propagated as the input to the anti-logarithm conversion (l), according to (3.6) and (3.7). Therefore,  $\varepsilon_{tot}$  is analyzed with respect to  $\alpha(k_i) + \alpha(k_j)$  to show the overall accumulation effect. For the proposed approximation method-1, depending on the range of  $\alpha(k_i) + \alpha(k_j)$ ,  $\varepsilon_{tot}$  can be analyzed for the following three scenarios:

- When  $-0.5 \le \alpha(k_i) + \alpha(k_j) < 0, -0.3300 \le \varepsilon_1(k_i) + \varepsilon_1(k_j) < -0.0088, 0.0030 \le \varepsilon_2(l) < 0.2071.$

- When  $0 \le \alpha(k_i) + \alpha(k_j) < 1, \ 0 \le \varepsilon_1(k_i) + \varepsilon_1(k_j) < 0.1720, \ -0.0860 \le \varepsilon_2(l) < 0.$

- When  $-0.25 \leq \alpha(k_i) + \alpha(k_j) < 0.5, -0.1650 \leq \varepsilon_1(k_i) + \varepsilon_1(k_j) < 0.0816, -0.0855 \leq \varepsilon_2(l) < 0.0908.$

For all the three scenarios shown above,  $\varepsilon_1(k_i) + \varepsilon_1(k_j)$ ,  $\varepsilon_2(l)$ , and  $\varepsilon_{tot}$  are plotted in Fig. 3.4 with respect to  $\alpha(k_i) + \alpha(k_j)$ . Note that  $k_i$  and  $k_j$  are sampled with a step size of 0.01. As shown in Fig. 3.4, the proposed approximation method-1 always produces errors with opposite signs in the two conversions, which largely reduces the accumulation effect. A value of  $\alpha(k_i) + \alpha(k_j)$  can lead to multiple values of  $\varepsilon_1(k_i) + \varepsilon_1(k_j)$  since multiple combinations of  $\alpha(k_i)$  and  $\alpha(k_j)$  can lead to the same sum. Fig. 3.5 shows the overall approximation error with respect to the four sub-regions that divide the range of [-0.5, 1). The  $\varepsilon_{tot}$  under the first and third scenarios and under the second and third scenarios are averaged, respectively, for  $-0.25 \leq \alpha(k_i) + \alpha(k_j) < 0$  and for  $0 \leq \alpha(k_i) + \alpha(k_j) < 0.5$ . As shown in Fig. 3.5, the overall approximation error is small, especially when  $\alpha(k_i) + \alpha(k_j)$  is in the range of [0, 0.5), due to the offset of errors with opposite signs in the two conversions. The approximation method-1 produces double-sided error distribution since  $\varepsilon_{tot}$  can be positive or negative.

Figure 3.4:  $\varepsilon_1(k_i) + \varepsilon_1(k_j)$ ,  $\varepsilon_2(l)$ , and  $\varepsilon_{tot}$  with respect to  $\alpha(k_i) + \alpha(k_j)$  under the three situations for the proposed approximation method-1.

Figure 3.5: Overall approximation error of the logarithm and anti-logarithm conversions for the proposed approximation method-1.

#### Mathematical Formulations

For the logarithmic N using the logarithmic FP representation, the exponent is given as (3.8) and the logarithm is approximated as follows:

$$\log_2(X') = \log_2(1+x') \cong \begin{cases} x, & x < 0.5, \\ \frac{1+x}{2} - 1, & x \ge 0.5. \end{cases}$$

(3.13)

For  $P = A \times B$  in the logarithm domain, the exponent is still computed by addition, whereas the multiplication for the mantissa is converted to addition. Let  $X'_{AB} = X'_A \times X'_B = (1 + x'_A) \times (1 + x'_B)$ , and hence the logarithm of  $X'_{AB}$  is given by:

$$\log_2(X'_{AB}) = \log_2(1 + x'_A) + \log_2(1 + x'_B) \cong \widehat{X}_A + \widehat{X}_B, \qquad (3.14)$$

where  $\widehat{X}_A$  and  $\widehat{X}_B$  denote the approximate logarithms obtained by (3.13).

Using the anti-logarithm approximation method-1,  $X'_{AB}$  is obtained as:

$$X'_{AB} \cong 2^{\hat{X}_A + \hat{X}_B} \cong 1 + \hat{X}_A + \hat{X}_B.$$

(3.15)

According to (3.13), we obtain  $-0.5 \leq \hat{X}_A + \hat{X}_B < 1$ , and thus,  $0.5 \leq X'_{AB} < 2$ . When  $X'_{AB} < 1$  (or  $\hat{X}_A + \hat{X}_B < 0$ ),  $X'_{AB}$  cannot be directly represented as the mantissa for the product P. In this case,  $X'_{AB}$  is multiplied by 2 and, accordingly, the exponent is reduced by 1.

Finally, the proposed logarithmic FP multiplication-1 is given by:

$$E_{P} = \begin{cases} E'_{A} + E'_{B} - bias, & \widehat{X}_{A} + \widehat{X}_{B} \ge 0, \\ E'_{A} + E'_{B} - bias - 1, & otherwise, \end{cases}$$

(3.16)

$$X_P = \begin{cases} 1 + \widehat{X}_A + \widehat{X}_B, & \widehat{X}_A + \widehat{X}_B \ge 0, \\ (1 + \widehat{X}_A + \widehat{X}_B) \times 2, & otherwise. \end{cases}$$

(3.17)

Note that  $E'_A$  and  $E'_B$  are the converted exponents, and  $\widehat{X}_A$  and  $\widehat{X}_B$  are the approximate logarithms given in the converted mantissas, for A and B, respectively.

#### 3.2.2 Logarithmic Multiplication 2

#### Logarithm and Anti-logarithm Approximation

Consider a given number N, when  $x \ge 0.5$ ,  $\log_2 N = (E+1) + (\frac{1+x}{2} - 1)$  according to (3.13). By cancelling out the '+1' and '-1', we obtain  $\log_2 N = E + \frac{1+x}{2}$ , which leads to the logarithm approximation method-2 given by (3.18). Note that the conversions for the original exponent and the mantissa in (3.8) and (3.9) are avoided.

$$\log_2(1+k) \cong \begin{cases} k, & 0 \le k < 0.5, \\ \frac{(1+k)}{2}, & 0.5 \le k < 1, \end{cases}$$

(3.18)

where the range of the approximate logarithm is [0, 1). Thus, the range of l is [0, 2)(l is the sum of the two approximate logarithms). Consider using Mitchell's antilogarithm method, as shown in Fig. 3.3, when  $1.5 \leq l < 2$ , larger approximate results will be produced in both the logarithm and anti-logarithm processes, which will lead to large error accumulation. Therefore, we propose to reduce the anti-logarithm value by subtracting certain values to ensure positive errors. The subtracted value is selected from our experiments for computing the overall accumulative error with various subtracted values. This process is shown in the following approximation error analysis. 0.5 and 0.25 are used for the range of [1.5, 1.75) and [1.75, 2), respectively. The anti-logarithm approximation used in this method is given by:

$$2^{l} \cong \begin{cases} l+1, & l<1, \\ 2 \times l, & 1 \le l < 1.5, \\ 2 \times l - 0.5, & 1.5 \le l < 1.75, \\ 2 \times l - 0.25, & 1.75 \le l < 2, \end{cases}$$

(3.19)

The logarithm approximation method-2 is shown in Fig. 3.2. When the mantissas of both input operands are smaller than 0.5, method-2 computes the same underestimated logarithm approximation as Mitchell's method; otherwise, it computes overestimated results. As shown in Fig. 3.3, the same overestimated anti-logarithm approximation as Mitchell's method is produced when  $0 \le l < 1.5$ , whereas underestimated anti-logarithm approximations are generated when  $1.5 \le l < 2$ .

#### **Approximation Error Analysis**

$\varepsilon_1(k)$  for the proposed logarithm approximation method-2 is expressed as:

$$\varepsilon_1(k) = \begin{cases} \log_2(1+k) - k, & 0 \le k < 0.5, \\ \log_2(1+k) - \frac{(1+k)}{2}, & 0.5 \le k < 1, \end{cases}$$

(3.20)

where  $0 \le k < 1$ . When  $0 \le k \in < 0.5$ , the approximate logarithm, i.e.,  $\alpha(k) = k$ , is in the range of [0, 0.5),  $\varepsilon_1(k)$  is in the range of [0, 0.0860), where the positive errors indicate overestimated results. When  $0.5 \le k < 1$ , the approximate logarithm, i.e.,  $\alpha(k) = \frac{(1+k)}{2}$ , is in the range of [0.75, 1),  $\varepsilon_1(k)$  is within the range of [-0.1650, -0.0022), where the negative errors indicate underestimated results.

Similar to the proposed method-1, the accumulation effect can be reduced when adding the approximate logarithms for  $k_i$  and  $k_j$ , i.e.,  $\alpha(k_i)$  and  $\alpha(k_j)$ , due to the double-sided error distribution. There are three scenarios when adding  $\alpha(k_i)$  and  $\alpha(k_j)$  depending on the ranges of  $k_i$  and  $k_j$ :

• If  $0 \le k_i, k_j < 0.5, 0 \le \alpha(k_i) + \alpha(k_j) < 1$ , positive errors are accumulated, resulting in  $0 \le \varepsilon_1(k_i) + \varepsilon_1(k_j) < 0.1720$ .

- If  $0.5 \le k_i, k_j < 1, 1.5 \le \alpha(k_i) + \alpha(k_j) < 2, -0.3300 \le \varepsilon_1(k_i) + \varepsilon_1(k_j) < -0.0044$ due to the accumulated negative errors.

- If  $0 \le k_i(k_j) < 0.5$  and  $0.5 \le k_j(k_i) < 1$ ,  $0.75 \le \alpha(k_i) + \alpha(k_j) < 1.5$ , the range of  $\varepsilon_1(k_i) + \varepsilon_1(k_j)$  is reduced to [-0.1650, 0.0838).

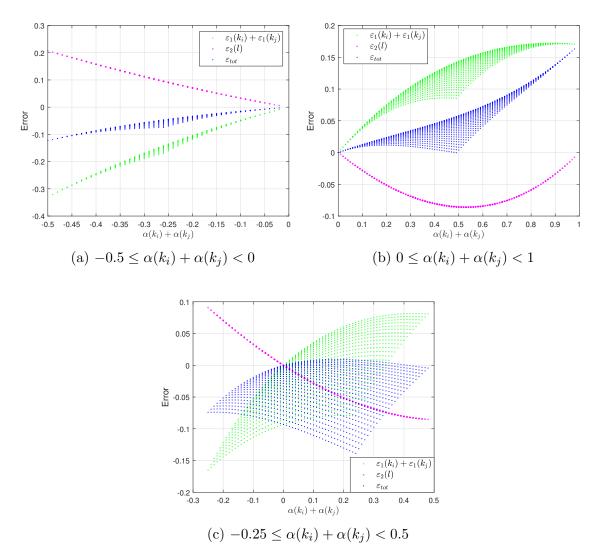

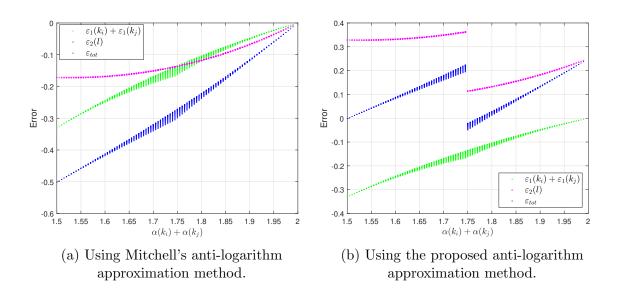

Using Mitchell's anti-logarithm approximation method, negative errors are generated both when  $0 \leq l < 1$  and  $1 \leq l < 2$  with  $-0.0860 \leq \varepsilon_2(l) < 0$  and  $-0.1721 \leq \varepsilon_2(l) < 0$ , respectively. While analyzing  $\varepsilon_{tot}$  as per (3.12), we observed that, when  $1.5 \leq \alpha(k_i) + \alpha(k_j) < 2$ , the negative errors are accumulated in the two conversions due to  $-0.3300 \leq \varepsilon_1(k_i) + \varepsilon_1(k_j) < -0.0044$  and  $-0.1721 \leq \varepsilon_2(l) < -0.0076$ . As shown in Fig. 3.6(a),  $\varepsilon_{tot}$  is plotted when  $1.5 \leq \alpha(k_i) + \alpha(k_j) < 2$ , which indicates the accumulation of negative errors leads to large  $\varepsilon_{tot}$ . Therefore, to reduce the accumulation effect for the range of [1.5, 2), we propose to reduce the approximate anti-logarithm value by simply subtracting certain values from it, which ensures generating positive errors, i.e.,  $\varepsilon_2(l) > 0$ . Denote the subtracted value by  $\delta$ , the antilogarithm approximation for the range of [1.5, 2) is expressed as  $2 \times l - \delta$  and  $\varepsilon_2(l)$  is computed as:

$$\varepsilon_2(l) = 2^l - (2 \times l - \delta), \tag{3.21}$$

where  $1.5 \leq l < 2$ .

The value of  $\delta$  is selected to reduce the error accumulation effect as much as possible while introducing a small hardware overhead. As shown in Fig. 3.6a, the absolute value of  $\varepsilon_1(k_i) + \varepsilon_1(k_j)$  decreases with  $\alpha(k_i) + \alpha(k_j)$  in the range of [1.5, 2), indicating that  $\delta$  should be decreasing with  $\alpha(k_i) + \alpha(k_j)$  to produce the positive  $\varepsilon_2(l)$ that can offset errors of the negative  $\varepsilon_1(k_i) + \varepsilon_1(k_j)$  as much as possible. A trade-off is assessed when determining  $\delta$ . Using different  $\delta$  with excessively small intervals in the range of [1.5, 2) can substantially increase the hardware overhead, whereas subtracting one single value in the range of [1.5, 2) can be ineffectual or aggravate the error accumulation. We consider to use  $\delta$  for the two sub-regions of [1.5, 2) divided

by 1.75. By computing  $\varepsilon_{tot}$  with various values of  $\delta$ ,  $\delta$  is determined to be 0.5 and 0.25 for the range of [1.5, 1.75) and [1.75, 2), respectively. Therefore, the proposed anti-logarithm approximation is given by (3.19).

Figure 3.6:  $\varepsilon_1(k_i) + \varepsilon_1(k_j)$ ,  $\varepsilon_2(l)$ , and  $\varepsilon_{tot}$  for  $1.5 \le \alpha(k_i) + \alpha(k_j) < 2$ .

$\varepsilon_2(l)$  for the proposed method-2 is given by:

$$\varepsilon_2(l) = \begin{cases} 2^l - (l+1), & 0 \le l < 1, \\ 2^l - l \times 2, & 1 \le l < 1.5, \\ 2^l - (2 \times l - 0.5), & 1.5 \le l < 1.75, \\ 2^l - (2 \times l - 0.25), & 1.75 \le l < 2, \end{cases}$$

(3.22)

where  $0 \leq l < 2$ . As shown in Fig. 3.6b, for  $1.5 \leq \alpha(k_i) + \alpha(k_j) < 2$ , positive  $\varepsilon_2(l)$  is produced to cancel out the negative  $\alpha(k_i) + \alpha(k_j)$ .  $\varepsilon_{tot}$  can then be analyzed for the following four scenarios:

- when  $0 \le \alpha(k_i) + \alpha(k_j) < 1, \ 0 \le \varepsilon_1(k_i) + \varepsilon_1(k_j) < 0.1720, \ -0.0860 \le \varepsilon_2(l) < 0.$

- when  $1.5 \le \alpha(k_i) + \alpha(k_j) < 1.75, -0.3300 \le \varepsilon_1(k_i) + \varepsilon_1(k_j) < -0.1418, 0.3278 \le \varepsilon_2(l) < 0.3603.$

- when  $1.75 \le \alpha(k_i) + \alpha(k_j) < 2, -0.135 \le \varepsilon_1(k_i) + \varepsilon_1(k_j) < -0.0044, 0.1135 \le \varepsilon_2(l) < 0.2423.$

• when  $0.75 \le \alpha(k_i) + \alpha(k_j) < 1.5, -0.1650 \le \varepsilon_1(k_i) + \varepsilon_1(k_j) < 0.0838, -0.1711 \le \varepsilon_2(l) < 0.$

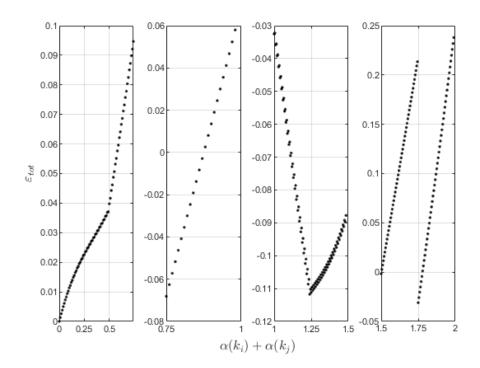

Negative errors are generated both when  $0 \le l < 1$  and  $1 \le l < 1.5$  with  $-0.0860 \le \varepsilon_2(l) < 0$  and  $-0.1721 \le \varepsilon_2(l) < 0$ , respectively. When  $1.5 \le l < 1.75$  and  $1.75 \le l < 2$ , positive errors are generated with  $0.3278 \le \varepsilon_2(l) < 0.3603$  and  $0.1135 \le \varepsilon_2(l) < 0.2423$ , respectively. The overall approximation error is shown in Fig. 3.7 with respect to four sub-regions that divide the range of [-0.5, 1). The  $\varepsilon_{tot}$  in the first and fourth scenarios are averaged for  $0.75 \le \alpha(k_i) + \alpha(k_j) < 1$ . As shown in Fig. 3.7, a double-sided error distribution is generated by the approximation method-2.

Figure 3.7: Overall accumulated errors of the logarithm and anti-logarithm conversions for the proposed approximation method-2.

#### Mathematical Formulations

Using the proposed logarithm approximation method-2, as per (3.18) and the antilogarithm approximation, as per (3.19),  $X_{AB}$  is obtained. When  $\hat{X}_A + \hat{X}_B \ge 1$ ,  $X_{AB}$ is divided by 2 to fit in the range of [1, 2) and, accordingly, a carry to  $E_A + E_B$  is added to ensure the correct result.

Finally, the logarithmic FP multiplication in the proposed multiplication-2 is given by:

$$E_P = \begin{cases} E_A + E_B - bias + 1, & \widehat{X}_A + \widehat{X}_B \ge 1\\ E_A + E_B - bias, & otherwise, \end{cases}$$

(3.23)

$$X_{P} = \begin{cases} 1 + \hat{X}_{A} + \hat{X}_{B}, & \hat{X}_{A} + \hat{X}_{B} < 1, \\ \hat{X}_{A} + \hat{X}_{B}, & 1 \le \hat{X}_{A} + \hat{X}_{B} < 1.5, \\ \hat{X}_{A} + \hat{X}_{B} - 0.25, & 1.5 \le \hat{X}_{A} + \hat{X}_{B} < 1.75, \\ \hat{X}_{A} + \hat{X}_{B} - 0.125, & 1.75 \le \hat{X}_{A} + \hat{X}_{B} < 2. \end{cases}$$

(3.24)

## **3.3** Theoretical Error Analysis

The two proposed FP logarithmic multiplication methods introduce approximation errors in both the logarithm conversion and anti-logarithm conversion. The error distance is analyzed with the exponent ignored for simplicity.

According to (3.2)-(3.5), the result of exact multiplication is given by  $P_{ex} = (1 + x_A) \times (1 + x_B) = 1 + x_A + x_B + x_A x_B$ . The products for the proposed multiplication-1 and multiplication-2 algorithms, denoted as  $P_{ap1}$  and  $P_{ap2}$ , are given by:

$$\begin{cases}

1 + x_A + x_B, & x_A, x_B < 0.5, \\

(3.25a)

\end{cases}$$

$$P_1 = \begin{cases} 1 + 2x_A + x_B, & x_A < 0.5, x_B \ge 0.5, \\ & (3.25b) \end{cases}$$

$$1 + x_A + 2x_B, \ x_A \ge 0.5, x_B < 0.5, \tag{3.25c}$$

$$\begin{cases} 2x_A + 2x_B, & x_A, x_B \ge 0.5, \end{cases}$$

(3.25d)

$$\begin{cases} 1 + x_A + x_B, & x_A, x_B < 0.5, \\ \frac{3 + 2x_A + x_B}{2} \text{ or } 1 + 2x_A + x_B, \end{cases}$$

(3.26a)

$$x_A < 0.5, x_B \ge 0.5,$$

(3.26b)

$$P_{2} = \begin{cases} \frac{3 + x_{A} + 2x_{B}}{2} \text{ or } 1 + x_{A} + 2x_{B}, \\ x_{A} \ge 0.5, x_{B} < 0.5, \\ 1.5 + x_{A} + x_{B} \text{ or } 1.75 + x_{A} + x_{B}, \\ x_{A}, x_{B} \ge 0.5. \end{cases}$$

(3.26d)

By comparing the equations under different conditions, the error,  $Err = P_{ex} - P_{ap}$ , can be derived as follows:

$$\begin{cases} x_A x_B, & x_A, x_B < 0.5, \end{cases}$$

(3.27a)

$$Err_1 = \begin{cases} x_A(x_B - 1), & x_A < 0.5, x_B \ge 0.5, \\ (3.27b) \end{cases}$$

$$x_B(x_A - 1), \quad x_A \ge 0.5, x_B < 0.5,$$

(3.27c)

$$((1 - x_A)(1 - x_B), \quad x_A, x_B \ge 0.5,$$

(3.27d)

$$\begin{cases} x_A x_B, & x_A, x_B < 0.5, \\ \frac{x_B + 2x_A x_B - 1}{2} \text{ or } x_A (x_B - 1), \end{cases}$$

(3.28a)

$$x_A < 0.5, x_B \ge 0.5,$$

(3.28b)

$$Err_{2} = \begin{cases} \frac{x_{A} + 2x_{A}x_{B} - 1}{2} \text{ or } x_{B}(x_{A} - 1), \\ x_{A} \ge 0.5, x_{B} < 0.5, \end{cases}$$

(3.28c)

$$x_A x_B - 0.5 \text{ or } x_A x_B - 0.75,$$

$x_A, x_B \ge 0.5.$  (3.28d)

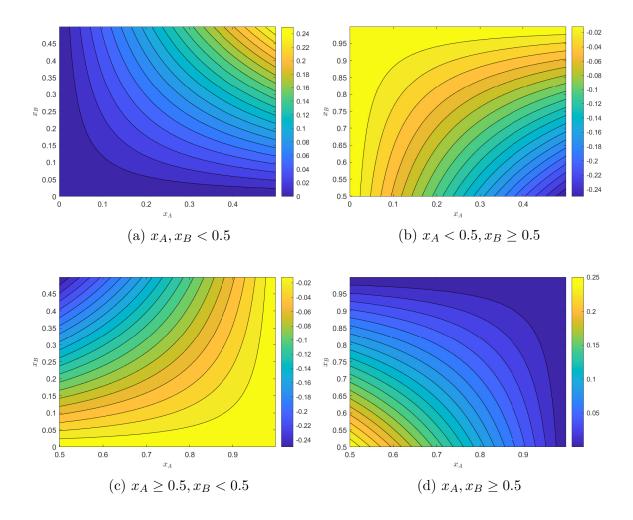

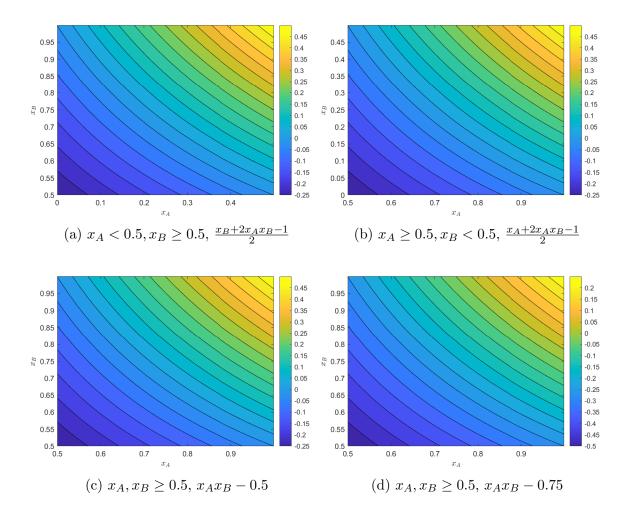

The contour maps of  $Err_1$  and  $Err_2$  are shown in Fig. 3.8 and Fig. 3.9, respectively. The largest positive  $Err_1$  is 0.25 when both  $x_A$  and  $x_B$  are 0.5, as shown in Fig. 3.8(d), while the negative  $Err_1$  that has the maximum absolute value is close to -0.25 when either one of  $x_A$  and  $x_B$  approaches 0.5 while the other one equals 0.5, as seen in Fig. 3.8(b) and Fig. 3.8(c).  $Err_1$  is larger than 0 when  $x_A, x_B < 0.5$  or  $x_A, x_B \ge 0.5$  and it is less than 0 under the other two conditions. The negative  $Err_2$  has the largest absolute value of -0.5 when both  $x_A$  and  $x_B$  are 0.5, while the largest positive  $Err_2$ is close to 0.5 when both  $x_A$  and  $x_B$  approach 1. Specifically, When  $x_A, x_B < 0.5$ ,  $Err_2$  is the same as  $Err_1$  as shown in Fig. 3.8(a). For each of the other three scenarios as shown in (3.28b)-(3.28d),  $Err_2$  is given by two expressions. Fig. 3.9(a) and Fig. 3.9(b) present the contour maps for the first equation of (3.28b) and (3.28c), respectively. In these two cases, the largest positive  $Err_2$  is very close to 0.5 when one of  $x_A$  and  $x_B$  approaches 0.5 and another one approaches 1; the negative  $Err_2$ with the maximum absolute value is -0.25 when one of  $x_A$  and  $x_B$  is 0 and the other is 0.5.  $Err_2$  is expressed by the second equations of (3.28b) and (3.28c), the same as the multiplication-1, as shown in Fig. 3.8(b) and Fig. 3.8(c). When  $x_A, x_B \ge 0.5$ , the contour maps for  $Err_2$  are presented in Fig. 3.9(c) and Fig. 3.9(d).

Therefore the maximum |Err| is 0.25 and 0.5 for the multiplication-1 and the multiplication-2, respectively. In comparison, the LAM [3] that uses Mitchell's approximation has the largest absolute error of 0.25 and always underestimates the product. However, the average errors for the multiplication-1 and the multiplication-2 can be reduced since the positive errors and negative errors tend to cancel each other in a sum of products.

Figure 3.8: The contour maps of the theoretical error (error = exact - approximate) with respect to  $x_A$  and  $x_B$  for the multiplication-1 algorithm.

Figure 3.9: The contour maps of the theoretical error (error = exact - approximate) with respect to  $x_A$  and  $x_B$  for the multiplication-2 algorithm.

## Chapter 4

## Circuit Designs of Floating-Point Logarithmic Multipliers

In this chapter, a generic circuit architecture is first introduced for the proposed FP LMs. The circuit design for these multipliers is then presented in detail. Lastly, the radix-4 logarithm (R4L) is considered to further reduce the hardware cost of the proposed designs.

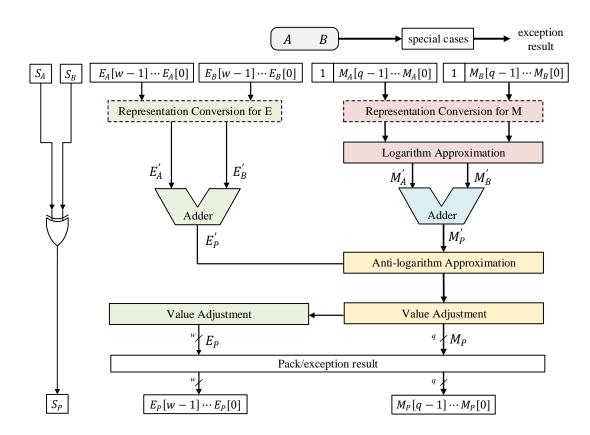

## 4.1 A Generic Circuit Architecture

Fig. 4.1 presents the generic circuit architecture for the proposed FP LMs according to their mathematical formulations. Taking advantage of the IEEE 754 FP format, the sign S, the exponent E, and the mantissa M of the FP number can be obtained directly. The w-bit E is given by  $E[w-1]E[w-2]\cdots E[0]$ . 1.M is used to denote the actual mantissa. Here, M contains q bits, e.g., 23 bits for single-precision, after the binary point and the hidden '1', and is given as  $M[q-1]M[q-2]\cdots M[1]M[0]$ . Note that 1.M represents 1 + x in (3.1).

The sign bit of the product,  $S_P$ , is obtained using an XOR gate with two input signs,  $S_A$  and  $S_B$ . For the multiplier that uses the approximation method-1, the exponents ( $E_A$  and  $E_B$ ) and the mantissas ( $1.M_A$  and  $1.M_B$ ) are converted into the nearest-one FP representation, whereas for the approximation method-2, the conversion is not required. The converted exponents or original exponents serve as the inputs of the adder, denoted by  $E'_A$  and  $E'_B$ , and the sum is denoted by  $E'_P$ . The converted mantissas are propagated to the logarithm approximation block to compute the approximate logarithms, denoted as  $M'_A$  and  $M'_B$ . Since the multiplication is replaced by the addition operation in the logarithm domain,  $M'_A$  and  $M'_B$  are added to obtain the sum, denoted by  $M'_P$ , which is then used in the anti-logarithm approximation block to compute its anti-logarithm. In the following adjustment block, the approximate anti-logarithm will be normalized to the range of [1, 2) if needed, and  $E'_P$  will be adjusted accordingly, resulting in  $E_P$  and  $M_P$ .  $E_P$  is added with the bias to comply with the IEEE standard and any exception (such as overflow, underflow, and "not a number") is reported. The two inputs are checked for exceptions at the beginning of the computation. Note that the rounding unit is not required in the inexact design since it is already inherently imprecise.

For the proposed multiplier designs, instead of being implemented directly according to the equations, the circuits are simplified to reduce the hardware complexity and latency. Specifically, some arithmetic operations are replaced with simpler operations. By merging multiple computations, the circuit blocks in the same color, as shown in Fig. 4.1, are integrated into a single block. In particular, the representation conversion blocks of the exponent and the mantissa are shown in dashed boxes since the conversion is not always required.

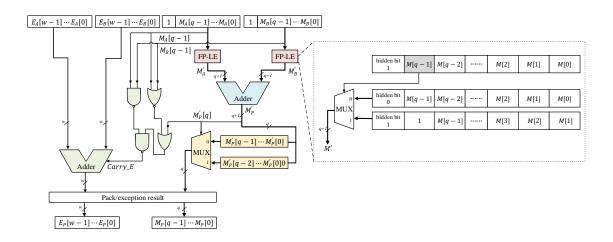

## 4.2 FP Logarithmic Multiplier-1

# 4.2.1 Logarithm approximation and addition of approximate logarithms

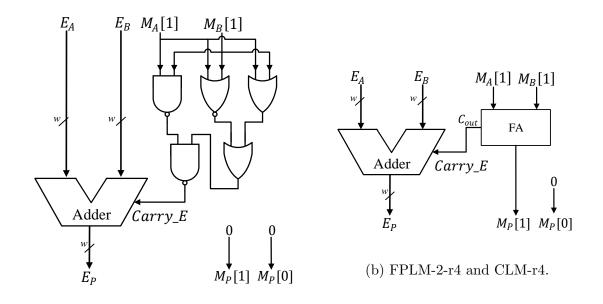

As shown in Fig. 4.2, for the two given mantissas,  $M_A$  and  $M_B$  are used as the inputs for the two FP logarithm estimators (FP-LEs), which compute the approximate logarithm of the mantissa. For FPLM-1, both the representation conversion and logarithm approximation for the mantissa are implemented by an FP-LE. Simple wire routing is used to implement the FP-LE, as shown in Fig. 4.2. The nearest power

Figure 4.1: The generic circuit architecture for proposed designs.

of two for each FP number can be determined by simply checking the leading bit of the explicit mantissa (without the hidden 1), M[q-1], and hence a 2-to-1 multiplexer is used to obtain the approximate logarithm, M'. According to (3.13), the left shifter for implementing the division by 2 is replaced by wire routing. Therefore, (1+x)/2 is implemented as  $0.1M[q-1]\cdots M[1]$ . When M[q-1] = 1, the approximate logarithm, (1+x)/2 - 1, is obtained as a negative number in 2's complement, i.e.,  $M' = 1.1M[q-1]\cdots M[1]$ ; otherwise, M' is  $0.M[q-1]\cdots M[0]$ . In the case of M[q-1] = 1, the LSB of M', M[0], is discarded to keep M' in q+1 bits.

$M^\prime_A$  and  $M^\prime_B$  are then summed using a q+1-bit adder.

Figure 4.2: The circuit design of the first proposed floating-point logarithmic multiplier, FPLM-1.

#### 4.2.2 Anti-logarithm approximation and value adjustment

The anti-logarithm approximation and value adjustment are implemented together using a multiplexer, as shown in Fig. 4.2. The q + 1-bit  $M'_P$  obtained from the adder is the input for this block. For FPLM-1, as per (3.17), since  $\hat{X}_A + \hat{X}_B$  can be negative in some cases, the MSB of  $M'_P$ , i.e.,  $M'_P[q]$  is the sign bit of  $M'_P$  in 2's complement. When  $\hat{X}_A + \hat{X}_B < 0$ ,  $M'_P[q] = 1$ ; otherwise,  $M'_P[q] = 0$ . Therefore,  $M'_P[q]$  is used as the selection signal for the multiplexer.  $1 + \hat{X}_A + \hat{X}_B$  is implemented as  $0.M'_P[q-1] \cdots M'_P[0]$  or  $1.M'_P[q-1] \cdots M'_P[0]$  when  $M'_P[q] = 1$  or  $M'_P[q] = 0$ , respectively. According to (3.17),  $-0.5 \leq \hat{X}_A + \hat{X}_B < 1$ , meaning that  $M'_P[q-1] = 1$ when  $M'_P[q] = 1$ . Therefore, in the case of  $M'_P[q] = 1$ ,  $1.M'_P[q-2] \cdots M'_P[0]0$  is obtained by performing the  $\times 2$  operation on  $0.M'_P[q-1] \cdots M'_P[0]$ .

### 4.2.3 Addition of exponents and value adjustment

The circuits for the exponent conversion, addition and value adjustment, shown as the green blocks in Fig. 4.1, are implemented together by integrating and simplifying multiple computations. For FPLM-1, according to (3.8), the exponents of the two operands are converted first, practically depending on  $M_A[q-1]$  and  $M_B[q-1]$ . Then the converted exponents are added subsequently to obtain  $E'_P$ , which is subtracted by 1 if  $M'_P[q] = 1$ , as per (3.16). The required circuits to implement these operations are simplified to one adder with a carry-in bit,  $Carry\_E$ , that is determined by the modified value of  $E_A$  and  $E_B$ . When  $M_A[q-1]M_B[q-1]$  are '00' or '11',  $M'_P[q]$  can only be '0' or '1', respectively; otherwise,  $M'_P[q]$  can be '0' or '1' in either case. According to (3.13) and (3.16), when both mantissa values are smaller than 0.5  $(M_A[q-1]M_B[q-1]$ 1] = 00),  $\hat{X}_A + \hat{X}_B \ge 0$   $(M'_P[q] = 0)$ , which means  $E'_A + E'_B$  is not modified; hence,  $Carry\_E = 0$ . When both mantissas are greater than or equal to 0.5  $(M_A[q-1]M_B[q-1]] = 11$ ,  $\hat{X}_A + \hat{X}_B < 0$   $(M'_P[q] = 1)$ , which means that  $E'_A + E'_B$  is subtracted by 1, i.e.,  $E_A + 1 + E_B + 1 - 1 = E_A + E_B + 1$ ; therefore,  $Carry\_E = 1$ .

Therefore, the  $Carry_E$  for FPLM-1 is obtained by using (4.1). As shown in Fig.

4.2, four logic gates are used to generate  $Carry\_E$ .

$$Carry_{-}E = \overline{\left(M'_{P}[q] + \overline{\left(M_{A}[q-1] + M_{B}[q-1]\right)}\right)}_{\overline{\left(M_{A}[q-1] \cdot M_{B}[q-1]\right)}}.$$

$$(4.1)$$

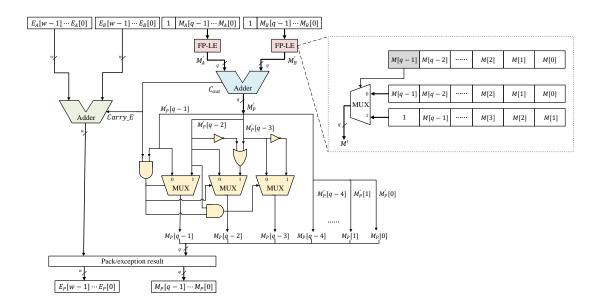

### 4.3 FP Logarithmic Multiplier-2

# 4.3.1 Logarithm approximation and addition of approximate logarithms

As shown in Fig. 4.3, for FPLM-2, the FP-LE implements the logarithm approximation for the mantissa without the conversion to the nearest-one FP representation. As per (3.18), (1 + x)/2 is implemented as  $0.1M[q - 1] \cdots M[1]$  when M[q - 1] =1, by performing the division by 2 operation with wire routing; x is obtained as  $0.M[q - 1] \cdots M[0]$  when M[q - 1] = 0. In both cases, the hidden bit is 0, which has no effect on the addition result. Thus, M' is obtained without the hidden bit and a q-bit adder is used for the addition of  $M'_A$  and  $M'_B$  with a carry-out signal,  $C_{out}$ , as shown in Fig. 4.3. In the case of M[q - 1] = 1, the LSB of M', M[0], is discarded to keep M' as q bits.

#### 4.3.2 Anti-logarithm approximation and value adjustment

According to (3.24),  $x'_A + x'_B$ , is obtained as  $C_{out}.M'_P[q-1]\cdots M'_P[0]$ . When  $x'_A + x'_B < 1$ , which means  $C_{out} = 0$ , the mantissa,  $1+x'_A+x'_B$ , is obtained as  $1.M'_P[q-1]\cdots M'_P[0]$ . When  $1 \le x'_A + x'_B < 1.5$ , meaning that  $C_{out}M'_P[q-1] = 10$ ,  $x'_A + x'_B$  is also obtained as  $1.M'_P[q-1]\cdots M'_P[0]$ . When  $1.5 \le x'_A + x'_B < 1.75$ ,  $C_{out}M'_P[q-1]M'_P[q-2] = 110$ ,  $x'_A + x'_B - 0.25$  is implemented by  $1.01M'_P[q-3]\cdots M'_P[0]$ . When  $1.75 \le x'_A + x'_B < 2$ ,  $C_{out}M'_P[q-1]M'_P[q-2] = 111$ ,  $x'_A + x'_B - 0.125$  is implemented by  $1.101M'_P[q-4]\cdots M'_P[0]$  or  $1.110M'_P[q-4]\cdots M'_P[0]$  if  $M'_P[q-3]$  is 0 or 1, respectively. Therefore,  $M_P[q-4]\cdots M_P[0]$  is obtained as  $M'_P[q-4]\cdots M'_P[0]$  and  $M_P[q-1]\cdots M_P[q-3]$  is determined by  $M'_P[q-1]\cdots M'_P[q-3]$  and  $C_{out}$ . The circuit for computing  $M_P$  is

Figure 4.3: The circuit design of the second proposed floating-point logarithmic multiplier, FPLM-2.

shown in Fig. 4.3.

#### 4.3.3 Addition of exponents and value adjustment

For FPLM-2, according to (3.23),  $E_A$  and  $E_B$  are summed and increased by 1 if  $C_{out} = 1$ . Therefore, as shown in Fig. 4.3,  $C_{out}$  is directly used to generate  $Carry_E$ .

## 4.4 Designs using the Radix-4 Logarithm

The radix-4 logarithm (R4L) was introduced to reduce the hardware complexity of the FP logarithm multipliers by exploiting the relation between the base 2 and base 4 logarithms. The base 2 logarithm of a given number N, is two times its base 4 logarithm, i.e.,  $\log_2 N = 2 \log_4 N$ . This indicates that the base 4 logarithm can be stored with a smaller bit-width than the base 2 logarithm in a hardware implementation. Therefore, we propose to convert the approximate logarithm of the mantissa to a radix-4 logarithm in an intermediate computation process to reduce the hardware cost of an FP LM. The radix-4 logarithm conversion is only used for the mantissa since applying to the exponent leads to large errors.

The R4L approach is specified in Algorithm 1. The approximate logarithms for the two mantissas, denoted by  $m_A$  and  $m_B$ , are obtained by applying the logarithm approximation to the mantissa that is concatenated with the hidden '1'. Note that the & operator indicates concatenation.  $m_A$  and  $m_B$  are converted to the radix-4 logarithm by simply discarding their LSB, resulting in  $m_A[q:1]$  and  $m_B[q:1]$ . The bit-width of the resulting approximate logarithm is reduced, which leads to a smaller hardware cost for the adder. Then the result, *sum*, is concatenated with '0' to ensure the correctness of the anti-logarithm approximation. When q is 1, the addition can be implemented with just an OR gate. The output,  $M_P$ , is obtained after normalizing the anti-logarithm result to make it lie in the range of [0, 1).

The R4L approach was applied to the proposed FPLM-1, FPLM-2, and the conventional logarithmic multiplier that uses Mitchell's approximation [21] to reduce their

Algorithm 1 A Radix-4 Logarithm (R4L) Approach

**Require:** Mantissas:  $M_A$  and  $M_B$ ; Bit-width of mantissa: q; Logarithm approximation method:  $\alpha()$ ; Anti-logarithm approximation method:  $\beta()$ ;

**Ensure:** Mantissa of the product:  $M_P$ .

```

\begin{array}{l} \mbox{if } q \geq 1 \ \mbox{then} \\ m_A \leftarrow \alpha(`1' \& M_A) \\ m_B \leftarrow \alpha(`1' \& M_B) \\ \mbox{if } q > 1 \ \mbox{then} \\ sum \leftarrow ADD(m_A[q:1], \ m_B[q:1]) \\ \mbox{else} \\ sum \leftarrow OR(m_A[1], \ m_B[1]) \\ \mbox{end if} \\ h \leftarrow \beta(sum \& `0') \\ M_P \leftarrow NORM(h) \\ \mbox{else} \\ M_P \leftarrow 0 \\ \mbox{end if} \end{array}

```

hardware complexity. The obtained multiplier designs are denoted as FPLM-1-r4, FPLM-2-r4, and CLM-r4.

## 4.5 Optimization for Reduced Bit-Width in the Mantissa

With a reduced mantissa bit-width, the circuit can be further optimized. Consider an FP number with the FP8 format, which has a 2-bit mantissa. Its mantissa can only represent four binary numbers, i.e., 00, 01, 10, and 11.