National Library of Canada

Bibliothèque nationale du Canada

Canadian Theses Service

Service des thèses canadiennes

Ottawa, Canada K1A 0N4

## NOTIÇE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Previously copyrighted materials (journal articles, published tests, etc.) are not filmed.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30.

## **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

Les documents qui font déjà l'objet d'un droit d'auteur (articles de revue, tests publiés, etc.) ne sont pas microfilmés.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30.

# The University of Alberta

# THE IMAGE COMPOSITION ARCHITECTURE: A HIGHLY PARALLEL GRAPHICS SYSTEM

bs

# Christopher David Shaw

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Master of Science

Department of Computing Science

Edmonton, Alberta Fall, 1988 Permission has been granted to the National Library of Canada to microfilm this thesis and to lend or sell copies of the film.

The author (copyright owner) has reserved other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without his/her written permission.

L'autorisation a été accordée à la Bibliothèque nationale du Canada de microfilmer cette thèse et de prêter ou de vendre des exemplaires du film.

L'auteur (titulaire du droit d'auteur) se réserve les autres droits de publication; ni la thèse ni de longs extraits de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation écrite.

# THE UNIVERSITY OF ALBERTA

## RELEASE FORM

NAME OF AUTHOR: Christopher David Shaw

TITLE OF THESIS: The Image Composition Architecture: A Highly Parallel Graphics System

DEGREE FOR WHICH THIS THESIS WAS PRESENTED: Master of Science

YEAR THIS DEGREE GRANTED: 1988

<

Permission is hereby granted to The University of Alberta Library to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly or scientific research purposes only.

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.

(Signed) .....

Permanent Address:

Box 18, Bristol Pond Estates

R.R. #3

Stouffville,

Ontario Canada

Dated: 1/109 30 1488

## THE UNIVERSITY OF ALBERTA

# FACULTY OF GRADUATE STUDIES AND RESEARCH

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies and Research, for acceptance, a thesis entitled The Image Composition Architecture: A Highly Parallel Graphics System submitted by Christopher David Shaw in partial fulfillment of the requirements for the degree of Master of Science.

Co-Supervisor

Co-Supervisor

Barry Gre

Xiasbo Li

Date 8/8/88

## **ABSTRACT**

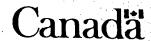

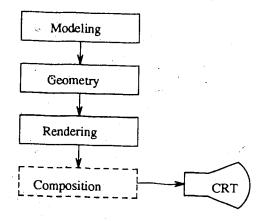

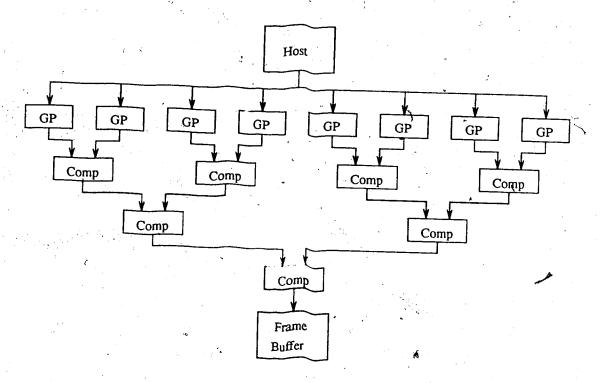

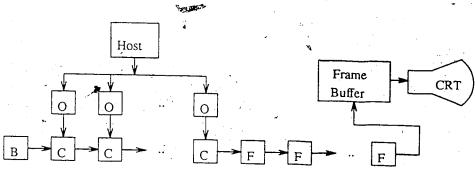

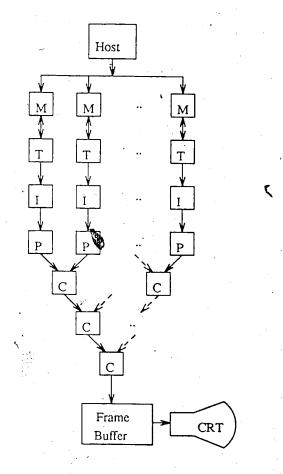

This thesis describes a new parallel architecture for performing high-speed raster graphics. A central host broadcasts graphical objects to a number of identical graphics processors. Each graphics processor produces a raster depicting its graphical object on a transparent black background, and passes the raster to a leaf of a tree of VLSI processors called *Compositors*. Each Compositor combines a pair of rasters, performing anti-aliased hidden surface removal, and passes the composed raster to the next level of the tree. The final raster appearing at the root of the tree shows all of the graphical objects that were distributed by the host in correct depth order. Each Compositor is a VLSI chip that performs raster composition of 512×512 pixel rasters at 14 frames per second.

The thesis first introduces the above architecture, with motivations for the need for high-speed graphics. A review of significant parallel graphics architectures of various classifications is presented. Published algorithms for performing the composition task are also reviewed, one of which is chosen for its anti-aliasing and linear time complexity properties. This algorithm, due to Duff, is then further simplified for hardware implementation with a view to minimizing the effects on its anti-aliasing property. High-level design of the dataflow and control parts of the VLSI chip are then presented.

## Acknowledgements

I would like to thank my supervisors, Jonathan Schaeffer and Mark Green, for their guidance, helpful criticism and support throughout this research. I would like to thank Gurminder Singh, who read first drafts of the thesis and served as the alpha test site for the document which you are about to enjoy.

I would also like to thank Scott Goodwin for ensuring that a high level of bogosity was maintained in our office at all times. Other members of the Canadian Institute for Advanced Bogosity Research (CIABR) are to be thanked for electing me as their Director. It is a profound honour I would soon forget if I didn't write it down somewhere.

## **Table of Contents**

دې

| Chapter                                                                                            | •                                       |      |

|----------------------------------------------------------------------------------------------------|-----------------------------------------|------|

| •                                                                                                  |                                         | Page |

| Chapter 1: Introduction  1.1. Motivation  1.2. Image Production                                    |                                         | 1    |

| 1.2. Image Production                                                                              |                                         | 1    |

| 1.2. Image Production                                                                              |                                         | 2    |

| 1.2.1. Modeling                                                                                    | •••••••                                 | 2    |

| 1.2.2. Geometric Transformations                                                                   |                                         | 3,   |

|                                                                                                    |                                         |      |

| - Barrier 1011 11111111111111111111111111111111                                                    |                                         | *.   |

| 1.4. The Proposed Architecture                                                                     | *************************************** | 4    |

| 1.5. Bandwidth Requirements                                                                        | *************************************** | 8    |

| 1.6. Implementation Technology                                                                     |                                         | 9    |

| 1.7. Contributions                                                                                 |                                         | 10   |

|                                                                                                    | •                                       | 11   |

| The analysis packground and Harriware                                                              |                                         | 12   |

| 2.1. Introduction                                                                                  | ,                                       | 12   |

| 2.2.1. Z-Buffer                                                                                    |                                         | 12   |

| 2.2.1. Z-Buffer                                                                                    | *************************************** | 12   |

| 2.2.2. A-Buffer                                                                                    |                                         | 14   |

| 2.2.3. Duff's Composition Algorithm                                                                |                                         | 16   |

| 2.3. Hardware Review                                                                               | ••••••                                  | . 18 |

| 2.3.1. Geometry Hardware                                                                           | ••••••                                  | 19   |

| 2.3.2. Réndering Hardware                                                                          | ·····                                   | 20   |

| 2.3.2.1. Special Memory Architectures                                                              | *************************************** | 20   |

| 2.3.2.2. Pixel-planes                                                                              |                                         | 21   |

| 2.3.2.3. Pixar Chap                                                                                | •••••                                   | 23   |

| 2.3.3. Full-Scale Parallel Graphics Systems                                                        | *******************************         | 24   |

|                                                                                                    |                                         | 24   |

| 2.3.3.2. Object-Based Systems                                                                      |                                         | 29   |

| 2.4. Summary Chapter 3: Reducing the Computational Level                                           |                                         | 32   |

|                                                                                                    |                                         | 35   |

| 3.2 Hardware Teeds Off.                                                                            | **************************              | 35   |

| 3.1. Purpose  3.2. Hardware Trade-Offs  3.3. Analysis of Duff's Algorithm                          |                                         | 35   |

| 3.3. Analysis of Duff's Algorithm  3.4. Duff's Algorithm For One Pixel  3.5. Determining & Cheaply | •••••                                   | 36   |

| 3.5. Determining & Charles                                                                         | • • • • • • • • • • • • • • • • • • • • | 38   |

| D CITOMPI I III III III III III III III III II                                                     |                                         | 39   |

| 3.5.1. Suggestion 1: Eliminate Previous Row of Z Entirely                                          | *************************************** | 40   |

| and the second                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.3.3. Suggestion 3: Estimating R Without Floating Point |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

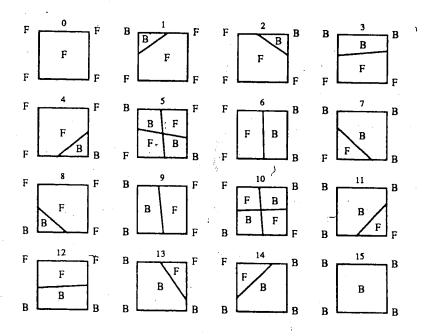

| 3.5.3.1. Five Schemes of Data Collection                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

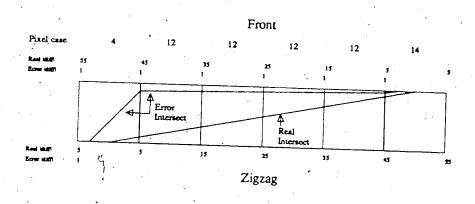

| 3.5.3.2. Linear Intersection Model                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

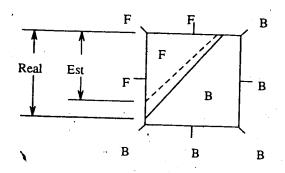

| 3.5.3.3. Linear Intersection With Center Bias Model      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.5.3.4. Contribution Model4.                            | <b>1.</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

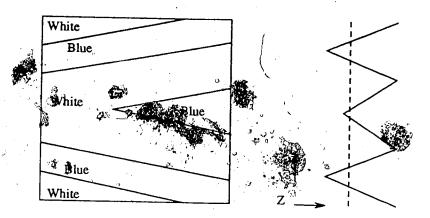

| 3.5.3.5. Statistical Model                               | Tig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.5.4. Stochastic Sampling                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.6. Conclusion                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| hapter 4: Experiments for Evaluating Approximations      | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.1. Test Images                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.2. Judgement of Composition Quality                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.3. Composition Candidates                              | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.3.1. Linear Intersection Model                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.3.2. Center Bias Model                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.3.3. Contribution Model                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Ranking the Results                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.5. Summary                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| hapter 5: High-Level Hardware Design                     | * · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.1. Scope                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.2. Data Representation                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.3. Chip Pinout                                         | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.4. Algorithm Review and Simplification                 | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

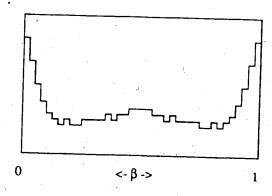

| 5.5. \( \beta \) Hardware Choices                        | et.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.5.1. The Chosen β Algorithm                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.5.2. B Hardware                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.5.2.1. Overflow                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

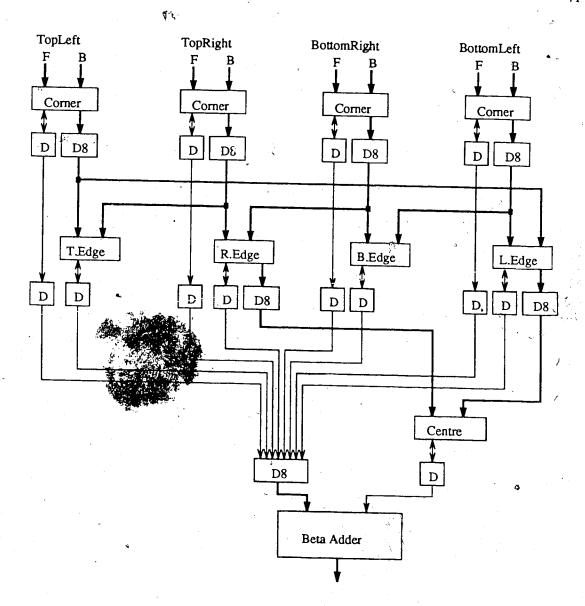

| 5.5.2.2. β Ad&er <sup>4</sup>                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.5.3. Overview of B Hardware and Simulations            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

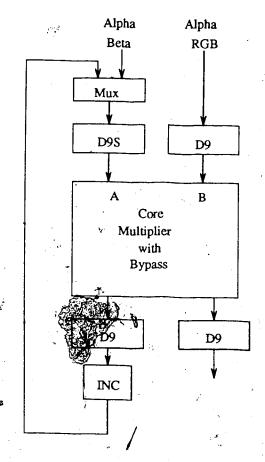

| o.6. The Multiplier                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

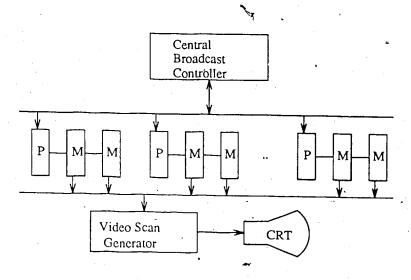

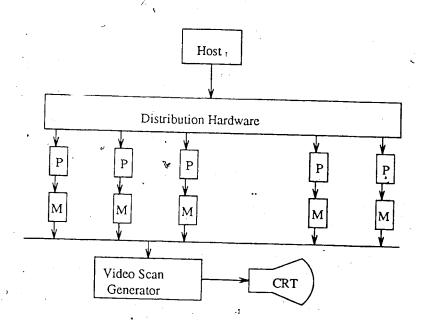

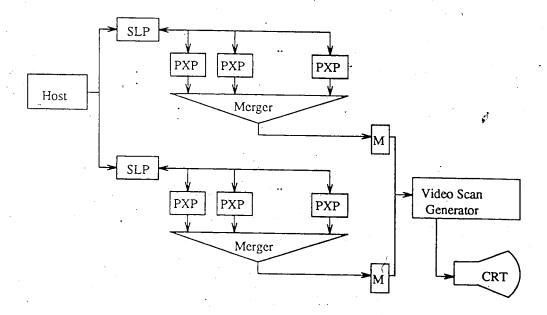

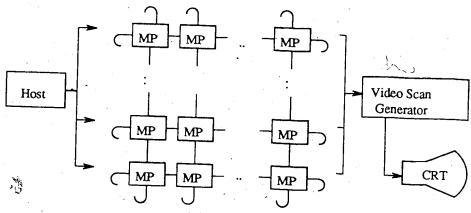

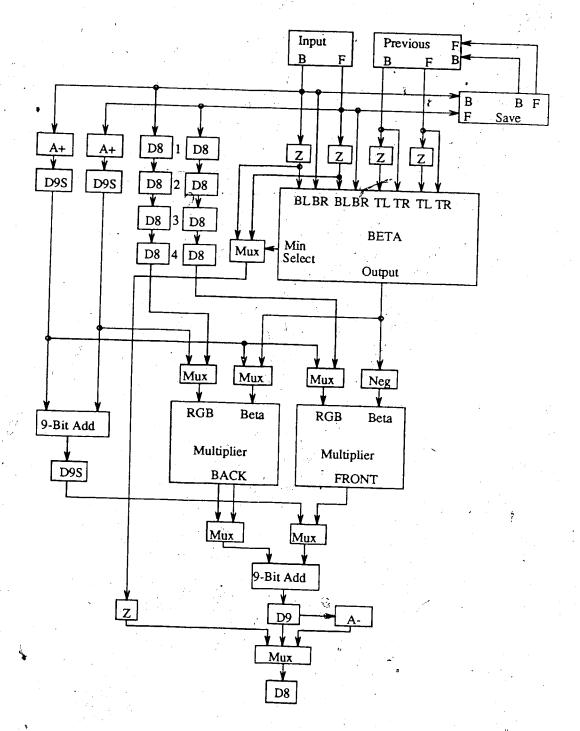

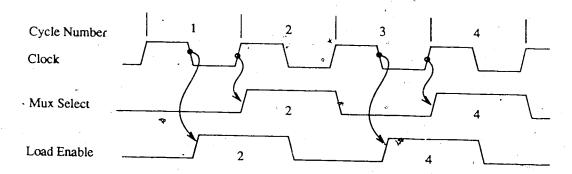

| O. /. Data Flow Circuitry                                | ••••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |