Acquisitions and Bibliographic Services Branch

395 Wethington Street Ottawa, Ontano K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Olfawa (Ontario) K1A 0N4

Stap for State Physics P

LANGE MAIN PROPERTY

### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à décirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

### **UNIVERSITY OF ALBERTA**

### OPTOELECTRONIC REFLEX SIGNAL PROCESSOR

BY

### **DOBBY LAM**

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of MATER OF SCIENCE.

### DEPARTMENT OF ELECTRICAL ENGINEERING

**EDMONTON, ALBERTA**

**SPRING 1994**

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Banger frage . Bartege egbigbe gering ge

Charles Aprilia interpretation

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence et non exclusive irrévocable **Bibliothèque** permettant la nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette disposition la des personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-612-11267-5

### UNIVERSITY OF ALBERTA

### RELEASE FORM

NAME OF AUTHOR: DOBBY LAM

TITLE OF THESIS: OPTOELECTRONIC REFLEX SIGNAL PROCESSOR

**DEGREE: MASTER OF SCIENCE**

YEAR THIS DEGREE GRANTED: 1994

Permission is hereby granted to THE UNIVERSITY OF ALBERTA LIBRARY to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly, or scientific purposes only.

The author reserves other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without the author's written permission.

PERMANENT ADDRESS: 119 TEMPLETON CIRCLE, N.E. CALGARY, ALBERTA CANADA, T1Y 3Z1

Date:January 24, 1994

### UNIVERSITY OF ALBERTA

## FACULTY OF GRADUATE STUDIES AND RESEARCH

The undersigned certify that they have read and recommend to the Faculty of Graduate Studies and Research for acceptance, a thesis entitled OPTOELECTRONIC REFLEX SIGNAL PROCESSOR submitted by DOBBY LAM in partial fulfillment of the requirements for the degree of MASTER OF SCIENCE.

Dr. R. I. MacDonald

Dr. J. McMullin

3 Koles

Dr. Z. (Roles

### VRSTD

This thesis describe the dose of a reconfigurable optoelectronic signal processor based on a 10 switch matrix and 10 replaceable optical fiber delay lines. The demonstrate various signal processing functions, such as switching and with the processor. This thesis concerns the demonstration of the basic mode overall concept. The processor consists of transmitter and receiver modules. The transmitter module with 10 optical transmitters was completed with a bandwidth up to 1.6 GHz. Two prototype receivers were built. With the completed portion of the system, various signal processing functions, such as FIR and IIR filtering and cascading switch network, were successfully demonstrated.

### **ACKNOWLEDGMENT**

I would like to thank my supervisor, Dr. R.I.MacDanold, for his trust in my ability and for his financial and intellectual support. In addition, I would like to thank Dr. Barrie Keyworth, Dr. Qing Liu, and David Clegg for their help in the design and assembling of the processor. I would also like to express my sincere thanks to Dr. Jan Conradi for his input on the final presentation. I am grateful to Wayne Fuche for his help with the construction of the processor. I would like to thank Rohit Sharma for his effort in carrying this project to its completion.

I would like to acknowledge the financial supports of both TRLabs and NSERC scholarships.

I would also like to thank the staffs and students of Telecommunications Research Laboratories (TRLabs) for their help, support, and comradeship. My special thanks are also due to Rob Tholl for his help in proof reading my thesis. Finally, I wish to extend my gratitude to the members of the examining committee for reviewing my work.

# TABLE OF CONTENTS

| 1.0   | INTRODUCTION                                                                | 1                  |

|-------|-----------------------------------------------------------------------------|--------------------|

| 1.1   | Background                                                                  | 1                  |

|       | 1.1.1 Discrete Time Signal Processing 1.1.2 Elemental Components for a DTSP |                    |

|       | 1.1.2 Elemental Components for a DTSP                                       | 1                  |

|       | 1.1.3 Finite Impulse Response (FIR) And Infinite Impulse Response (IIR)     | ٠.٠.٠              |

| 1.2   | Implementations of the DTSP                                                 | ,1                 |

| • • • | 1.2.1 Optical Delay Lines                                                   | 0                  |

|       | 1.2.2 Optical Discrete Time Signal Processor                                | /                  |

|       | 1.2.2 Optical Discrete Time Signal Processor                                | 8                  |

|       | 1.2.3 Optoelectronic Discrete Time Signal Processor.                        | 9                  |

|       | 1.2.3.1 Historical Perspective of Optoelectronic Signal Processing          | 10                 |

|       | 1.2.3.3 Optoelectronic Switch Matrix                                        | I.                 |

| 1.3   | Proposed Signal Processor Structure                                         | <b>I</b> •         |

| 1.4   | The organization of the thesis                                              | 10                 |

| 2.0   | STSTEM CONSIDERATIONS                                                       | 17                 |

| 2.1   | Cumponent Performance                                                       | 1.                 |

|       | 2.1.1 Metal-semiconductor-metal (MSM) photodiode array                      | . 17               |

|       | 2.1.1.1 Detector noise                                                      | 21                 |

|       | 2.1.2 Laser Diode                                                           | 7                  |

|       | 2.1.2.1 Laser noise                                                         | · •                |

|       | 2.1.3 Optical Components                                                    | ·· ວັ              |

|       | 2.1.3.1 Optical Noise                                                       | ۳ <u>ئى</u><br>د ر |

|       | 2.1.3.1 Optical Noise                                                       | <u></u> 44         |

|       | 2.1.4 Receiver Amplifier                                                    | 23                 |

| 2.2   | Applications under Consideration                                            | 2:                 |

| 2.2   | Applications under Consideration                                            | 2:                 |

|       | 2.2.1 Cascadable Switch Matrix                                              | 2:                 |

|       | 2.2.2 Reconfigurable Discrete Time Filter                                   | 27                 |

|       | 2.2.2.1 Sensitivity analysis of round-off error on system                   |                    |

|       | parameters.                                                                 | 2≀                 |

|       | 2.2.2.2 FIR Tap Weight Sensitivity                                          | 29                 |

|       | 2.2.2.3 IIR Tap Weight Sensitivity                                          | H                  |

|       | 2.2.2.4 Time delay sensitivity analysis                                     | 33                 |

|       | 2.2.2.5 Electrical Response Sensitivity Analysis                            | 35                 |

| 3.0   | TRANSMITTER MODULE                                                          | 38                 |

| 3.17  | ransmitter Card                                                             | . 38               |

|       | 3.1.1 Laser Support Circuitry                                               | 30                 |

|       | 3.1.1.1 Laser Power Regulation Circuit                                      | AI                 |

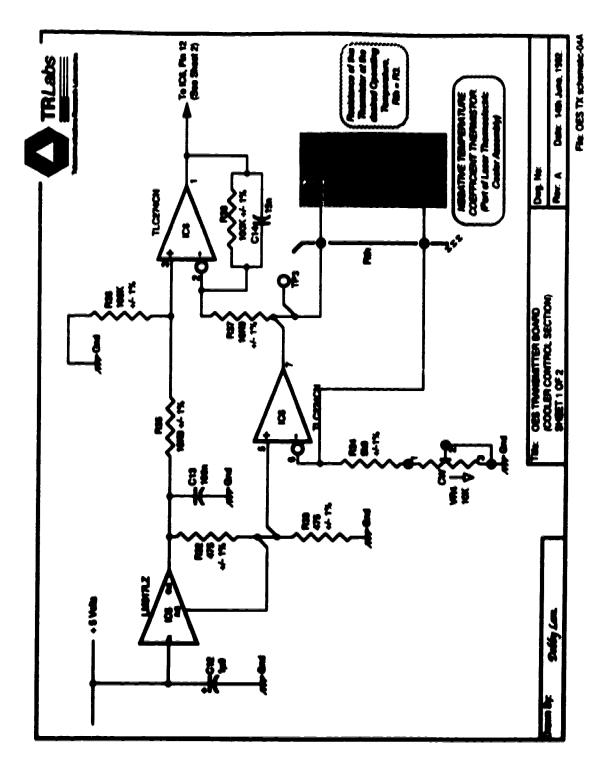

|       | 3.1.1.2 Thermal Regulation Circuit                                          | 41                 |

|       | 3.1.1.3 RF/Bias Insertion Circuit                                           | 47                 |

|       | 3.1.3 Optical Distribution And Optical Delay                                | . <b>7</b> /       |

| 40    | RECEIVER MODULE                                                             | . J.               |

| 7.0 ( | ADCEIVER MODULE                                                             | . 30               |

| 7.1 E | Receiver Module Organization                                                | . 20               |

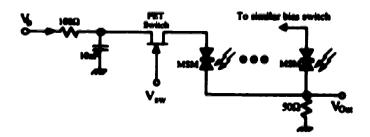

| 7.2 ( | rosspoint Biasing system                                                    | . 57               |

|       | 4.2.1 Requirements For The Programmable Voltage Sources                     | . 57               |

|       | 4.2.2 Programmable Voltage Sources                                          | . 57               |

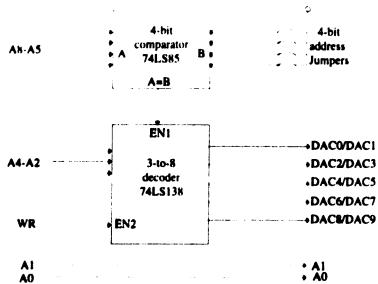

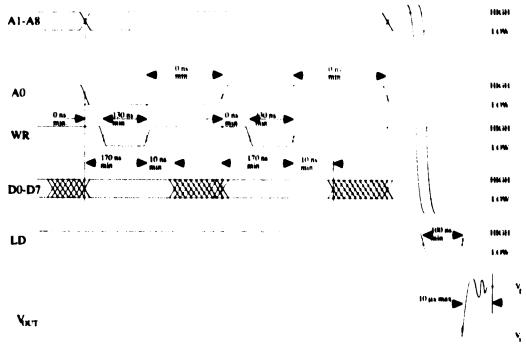

|       | 4.2.3 Address Decoder Circuit                                               | . 58               |

|       | 4.2.4 Interface Controller Card                                             | . 60               |

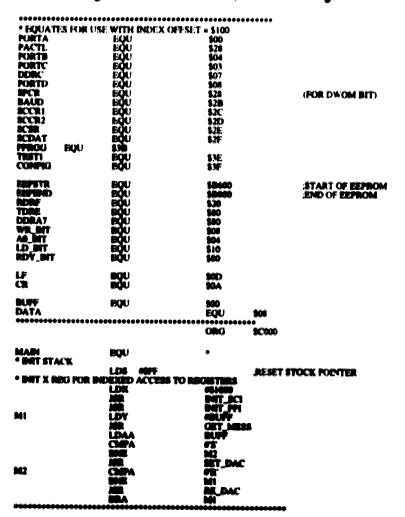

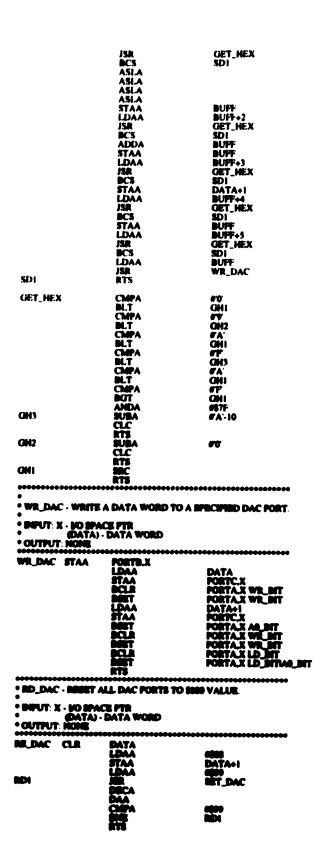

|       | 4.2.5 Control software                                                      | .61                |

|       | 4.2.6 DAC bias system performance                                           | .63                |

| 4.3 1 | Viscellaneous Optical Receiver Support Circuits                             | . 64               |

| 4.4 1 | Planned Optical Assembly Procedures                                         | .66                |

| 4.5 i | ASM optical Receiver                                                        | 69                 |

|       | 4.5.1 Original MSM Receiver Design                                          | . GO               |

| 4.5.2 Modified Receiver Design                                                      | 73   |

|-------------------------------------------------------------------------------------|------|

| 5.0 SYSTEM PERFORMANCE                                                              | 77   |

| 5.1 Crosspoint Characteristic                                                       | 77   |

| 5.1 Crosspoint Characteristic 5.2 Optoelectronic FIR filter (Direct Implementation) | 82   |

| 5.3 Optoelectronic IIR Filter                                                       | 88   |

| 5.4 Cascading Switches                                                              | 90   |

| 5.5 Optoelectronic FIR Filter (Reflex Implementation)                               | 92   |

| 6.0 SUMMARY                                                                         | 05   |

| 6.1 The Optoelectronic Signal Processor                                             | . 95 |

| 6.2 System Performance                                                              | 96   |

| 6.3 Future Research Directions                                                      | 97   |

|                                                                                     |      |

| APPENDIX A THE REQUIRED GAIN CALCULATION FOR THE MSM                                |      |

| OPTICAL RECEIVER AMPLIFIER                                                          | 102  |

| APPENDIX B                                                                          | 102  |

| IMPAIRMENTS OF MULTISTAGE OPTOELECTRONIC SWITCH                                     |      |

| NETWORKS                                                                            | 104  |

| NETWORKS                                                                            |      |

| VARIATIONS                                                                          | 109  |

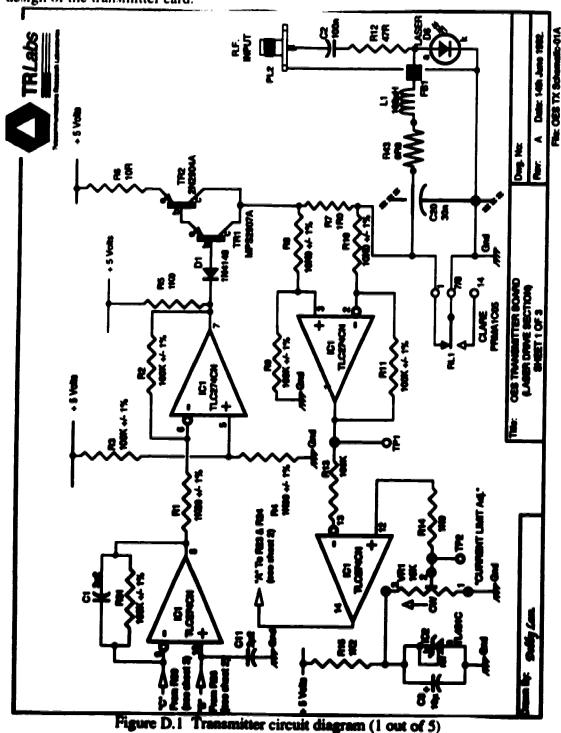

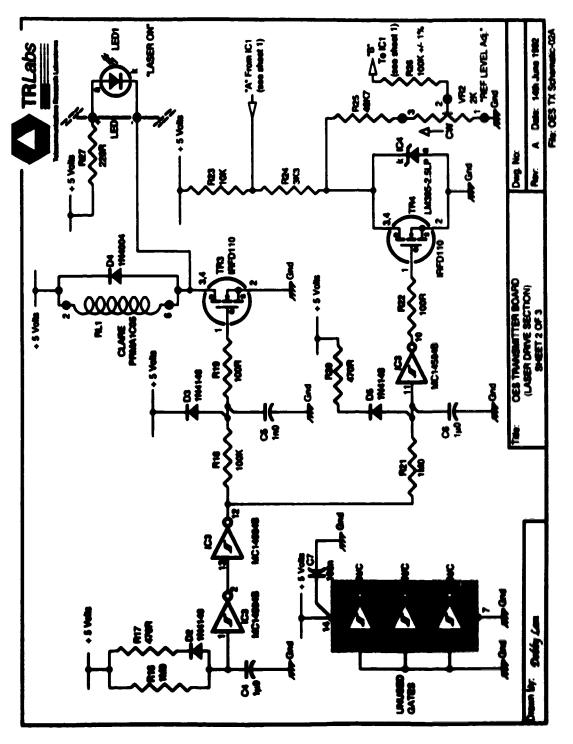

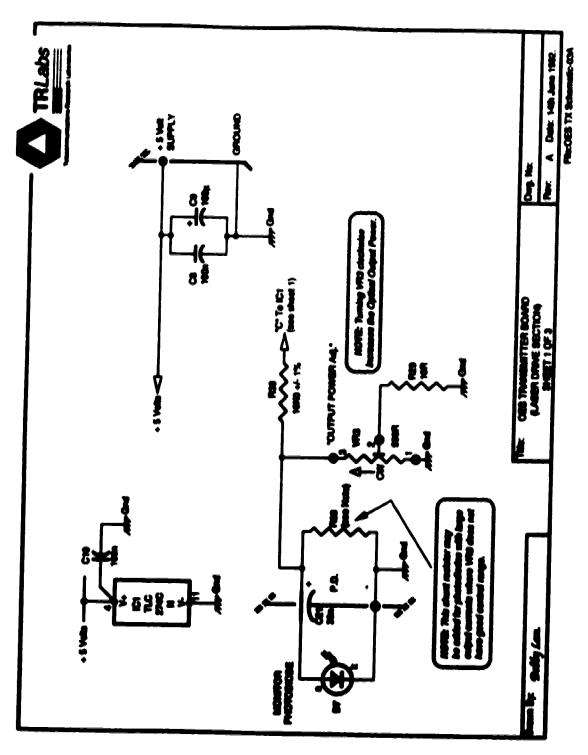

| VARIATIONSAPPENDIX D THE DETAIL TRANSMITTER CIRCUIT DIAGRAM                         | 120  |

| APPENDIX E LASER TRANSMITTER OPTICAL MEASUREMENT SETUP                              | 120  |

| AND RESULTS                                                                         | 128  |

| E.1 Frequency Response Measurement Setup                                            | 128  |

| E.2 SNK Measurement Setup                                                           | 129  |

| APPENDIX F THE MECHANICAL DRAWINGS AND THE ASSEMBLY                                 |      |

| DIAGRAM OF THE TRANSMITTER CARD                                                     | 130  |

| APPENDIX G THE CIRCUIT DIAGRAMS OF THE RECEIVER MODULE                              | 140  |

| APPENDIX H HC11 INTERNAL EEPROM PROGRAMMING PROCEDURES                              |      |

| & RELATED HC11 ASSEMBLE PROGRAM LISTINGS                                            | 149  |

| APPENDIX I THEORETICAL CALCULATION OF THE RESPONSIVITY OF                           |      |

| GaAs MSM PHOTODIODE                                                                 | 155  |

|                                                                                     |      |

|           | LIST OF TABLES                                                         |     |

|-----------|------------------------------------------------------------------------|-----|

| Table 3.1 | Measured optical power levels and losses of a typical transmitter card | .54 |

| Table I.1 | The material parameter for MSM responsivity calculation                | 50  |

| Table I.2 | The MSM responsivity with different finger spacing and interfaces      | 50  |

# LIST OF FIGURES

| Figure 1.1 Relationships between the time impulse and its frequency domain       |    |

|----------------------------------------------------------------------------------|----|

| responses                                                                        | 2  |

| Figure 1.2 Four basic components for a discrete time signal processor            | 3  |

| Figure 1.3 Two implementations of a FIR structure                                | 4  |

| Figure 1.4 First order averager and differentiator using a two tap FIR filter    | 5  |

| Figure 1.5 Two canonical forms of IIR filters                                    | 6  |

| Figure 1.6 A block diagram of a generalized optical signal processor             | 8  |

| Figure 1.7 (a) a schematic diagram and (b) a block diagram of an optoelectronic  |    |

| FIR filter                                                                       | 9  |

| Figure 1.8 The typical photoresponsivities of various photodetectors             | 10 |

| Figure 1.9 The optoelectronic switch using a PIN photodiode. The switching is    |    |

| achieved by completing the optoelectronic signal path using a photodiode bias    | 1  |

| Figure 1.10 A conceptual diagram of a 5x5 switched delay line signal processor   | 12 |

| Figure 1.11 A NxM switch matrix                                                  | 12 |

| Figure 1.12 a 5x5 optoelectronic switch matrix                                   | 13 |

| Figure 1.13 The proposed optoelectronic discrete time signal processor with a    |    |

| 10x10 matrix                                                                     | 15 |

| Figure 1.14 The organization of the proposed processor                           | 16 |

| Figure 2.1 A cross-section view of an MSM photodetector used in this project and |    |

| its circuit equivalent                                                           | 17 |

| Figure 2.2 A schematic diagram of the 1x4 MSM detector array                     | 18 |

| Figure 2.3 The frequency response of a 1µm MSM detector under different biasing  |    |

| conditions                                                                       | 19 |

| Figure 2.4 The DC response of 1 µm photodiode under different bias voltages and  |    |

| optical powers                                                                   | 20 |

| Figure 2.5 The AC response of a 1 µm MSM photodiode as a function of bias        | 21 |

| Figure 2.6 A 100x100 3 layer Clos network                                        | 26 |

| Figure 2.7 The proposed processor configured as a serial of Tx-Rx pairs          | 27 |

| Figure 2.8 The reflex optoelectronic signal processor with different filter      |    |

| configurations                                                                   | 28 |

| Figure 2.9 The response of 20 tap bandpass FIR filter with the 10 bit resolution | 30 |

| Figure 2.10 The 20 tap FIR filter simulation model. (a) A conceptual diagram of  |    |

| the filter. (b) A block diagram of the filter                                    | 33 |

| Figure 2.11 The effects of the delay variation on a bandness FIR filter          |    |

| Figure 2.12 The effects of the electrical responses on a reflex bandpass filter   | 7         |

|-----------------------------------------------------------------------------------|-----------|

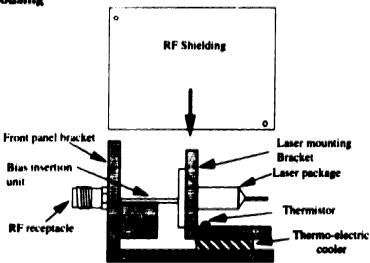

| Figure 3.1 Block diagram of the transmitter module                                | 8         |

| Figure 3.2 A picture of the optical backplane.                                    | <b>()</b> |

| Figure 3.3 A schematic diagram of the laser power regulator                       | ()        |

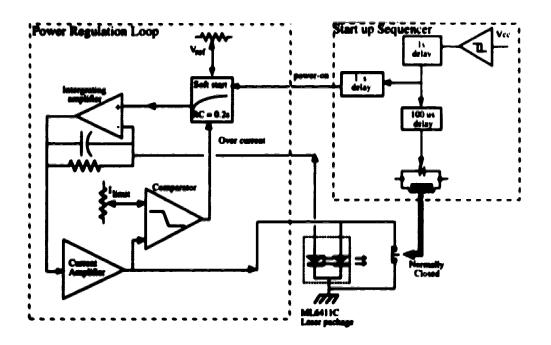

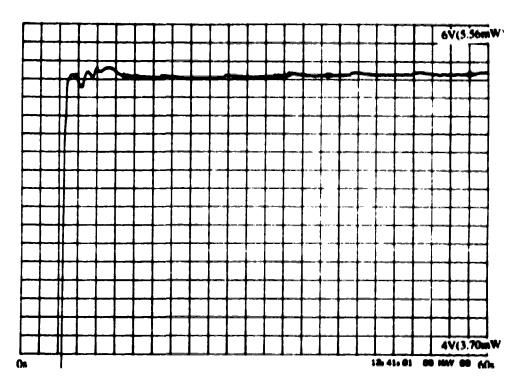

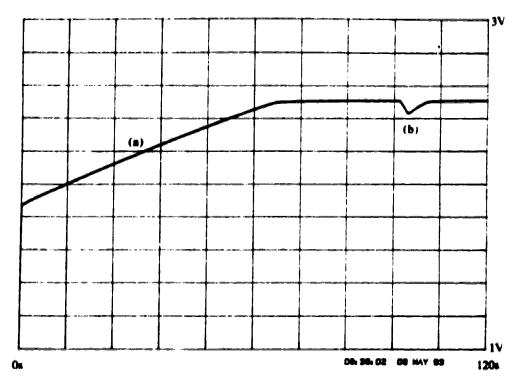

| Figure 3.4 The start-up sequence of the optical power regulation loop             | 3         |

| Figure 3.5 The initial transient of a transmitter card optical output             | 4         |

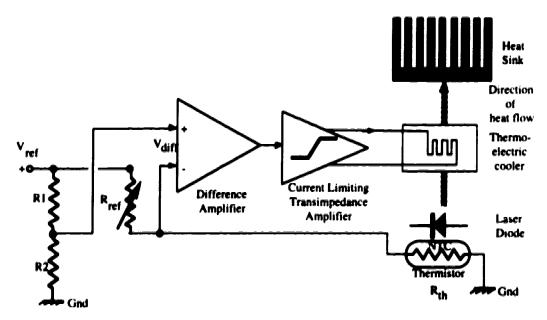

| Figure 3.6 A schematic diagram of the laser cooling circuit                       | 5         |

| Figure 3.7 The behavior of the laser temperature control loop                     | 7         |

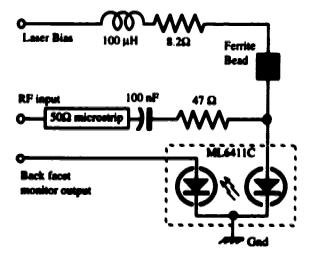

| Figure 3.8 Schematic of the bias insertion unit                                   | 7         |

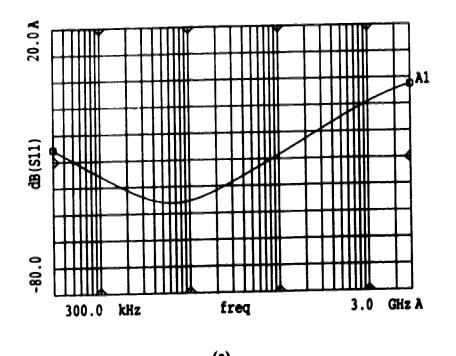

| Figure 3.9 The input characteristics of the RF/Lias insertion circuit             | ı)        |

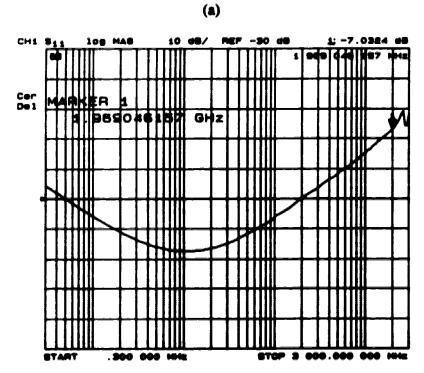

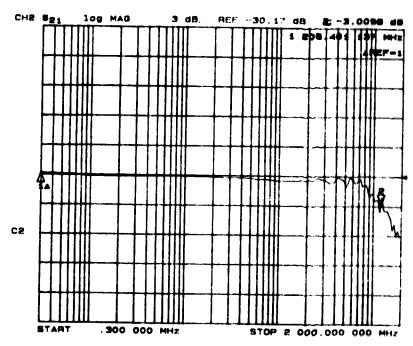

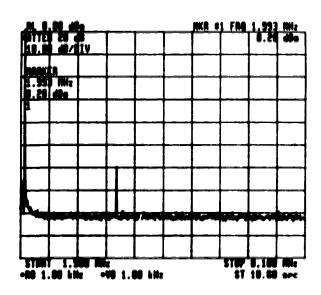

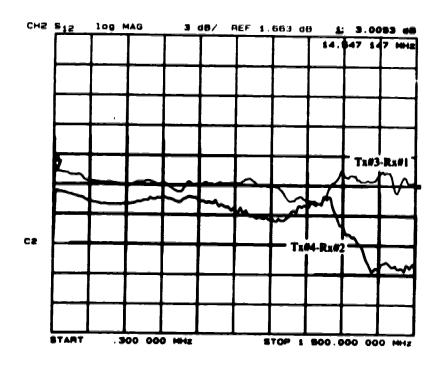

| Figure 3.10 The frequency response of Transmitter No.3                            | ()        |

| Figure 3.11 The effect of the back reflection from a improperly terminated FC     |           |

| connector                                                                         | I         |

| Figure 3.12 The linearity measurement of transmitter card No.2 with a 22 dB post- |           |

| amplifier                                                                         | 2         |

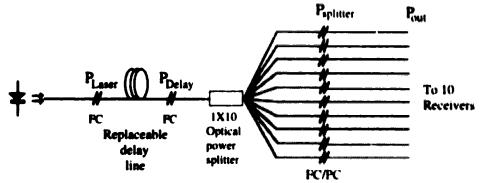

| Figure 3.14 The optical distribution of a transmission card                       | 4         |

| Figure 3.15 The low frequency fluctuation on the optical output of transmitter    |           |

| No.3                                                                              | 5         |

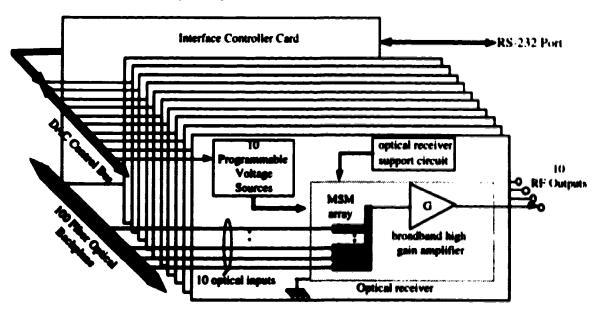

| Figure 4.1 A schematic of the receiver module                                     | 6         |

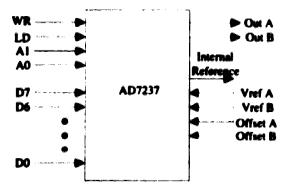

| Figure 4.2 A schematic diagram of AD7237 DAC configured in the stand-alone        |           |

| mode                                                                              | В         |

| Figure 4.3 A schematic diagram of the address decoder of a receiver card          | 9         |

| Figure 4.4 a timing diagram of the control bus for the biasing system             | D         |

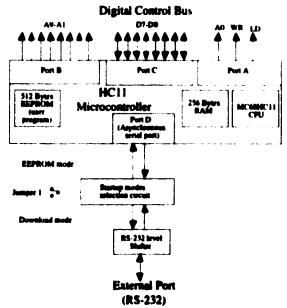

| Figure 4.5 A block diagram of the interface controller card                       | D         |

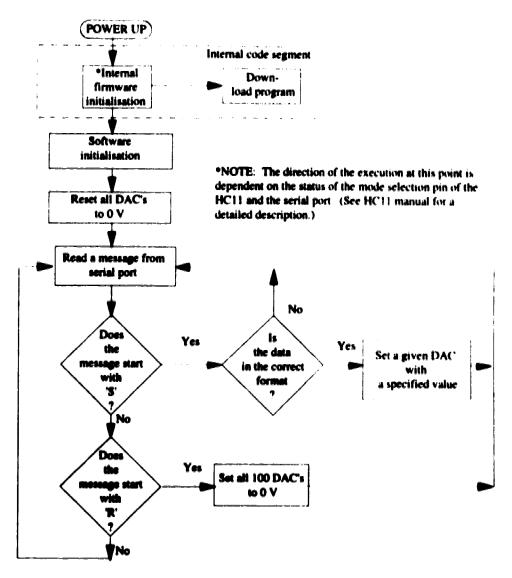

| Figure 4.6 An execution flow diagram of the HC11 control program for the biasing  |           |

| system                                                                            | 2         |

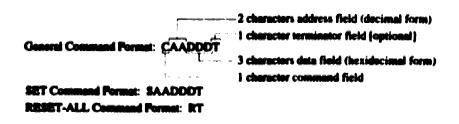

| Figure 4.7 The command format of the interface controller card                    | 2         |

| Figure 4.8 The switching transient measurements of the biasing circuit            | 3         |

| Figure 4.9 The DC photocurrent interference on a MSM photodiode array             | 5         |

| Figure 4.10 The behavior of the virtual ground circuit (a) under a DC current     |           |

| injection and (b) under a periodic injection                                      | 5         |

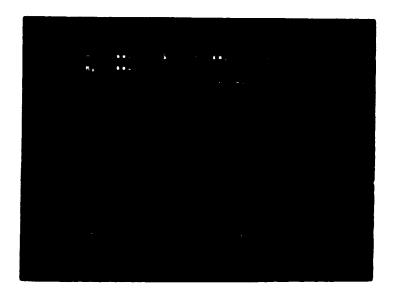

| Figure 4.11 The mask for the silicon alignment wafer with the modifications       |           |

| Figure 4.12 The front view of the alignment wafer                                 |           |

| Figure 4.13 The diagram of the laser assembly                                     |           |

| Figure 4.13 A picture of an assembled alignment wafer with optical outputs        |           |

| Pigure 4.14 A schematic diagram of the original MSM receiver                      |           |

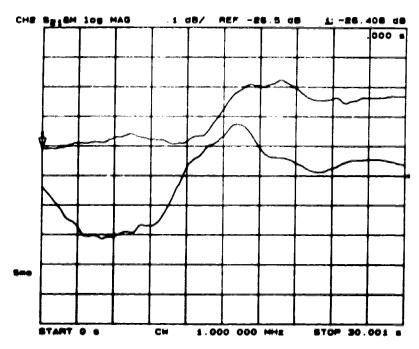

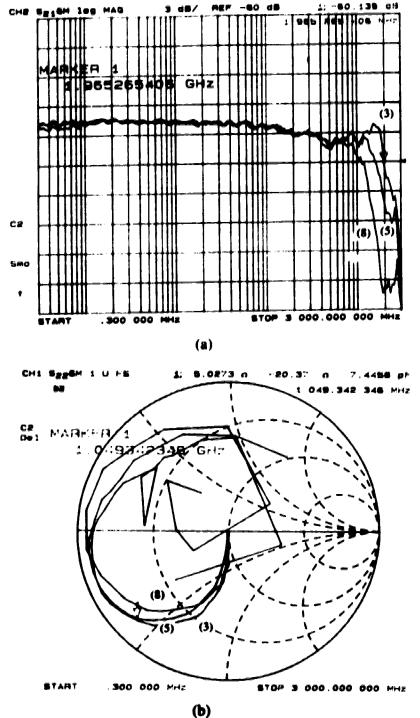

| Figure 4.15 Two typical frequency response of the original MSM receiver design    |

|-----------------------------------------------------------------------------------|

| with various problems70                                                           |

| Figure 4.16 The scatter parameters of the MSM photodiode array with various       |

| numbers of photodiodes71                                                          |

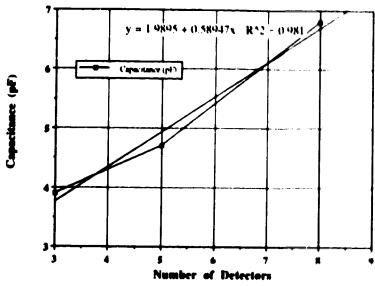

| Figure 4.17 The capacitance of 1 µm finger spacing MSM capacitance as a function  |

| of the number of photodiodes72                                                    |

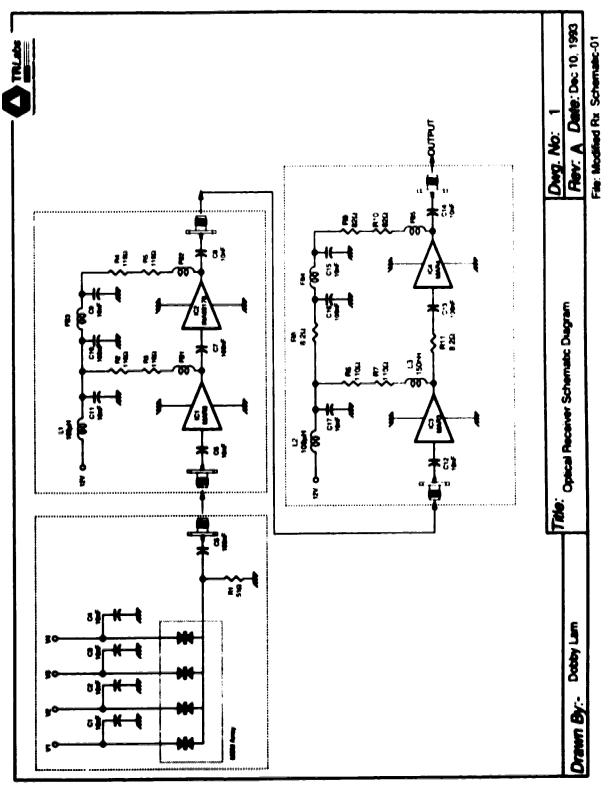

| Figure 4.18 A schematic diagram of the modified amplifier circuit74               |

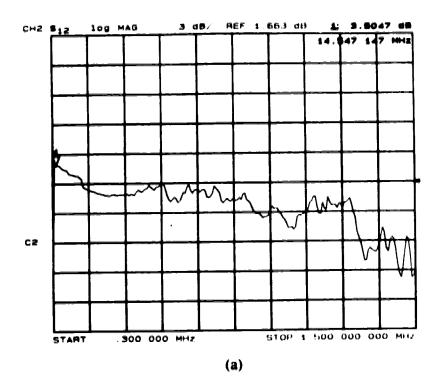

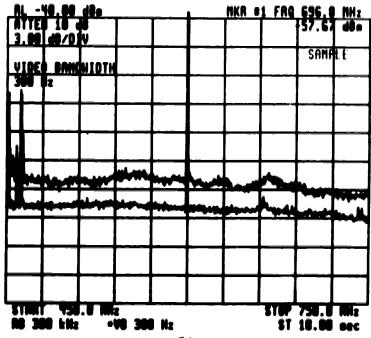

| Figure 4.19 The performances of the two modified amplifiers                       |

| Figure 4.20 The frequency response of the two optical links                       |

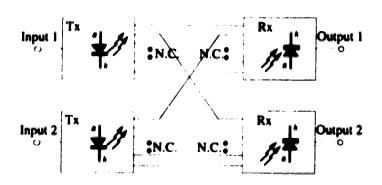

| Figure 5.1 The 2x2 switch matrix system used for testing the signal processing    |

| functions77                                                                       |

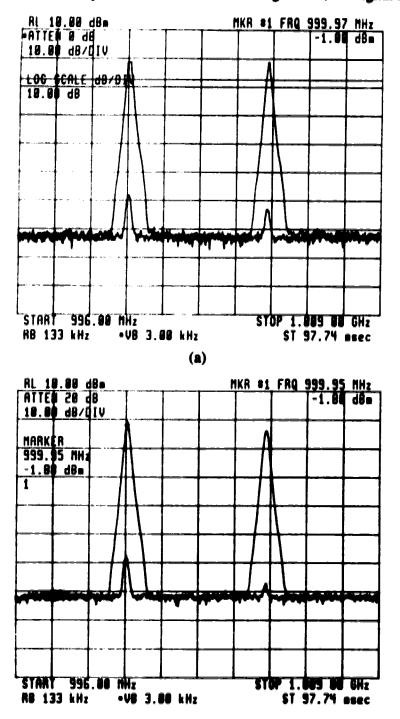

| Figure 5.2 The crosspoint isolation measurement with a HP-8753A network           |

| analyzer78                                                                        |

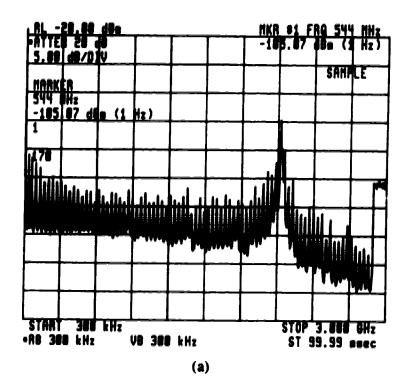

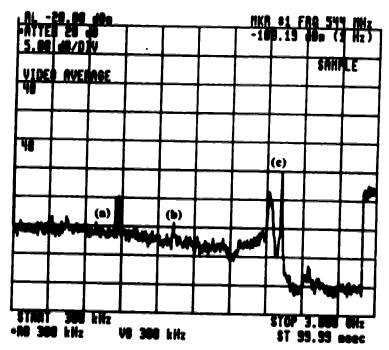

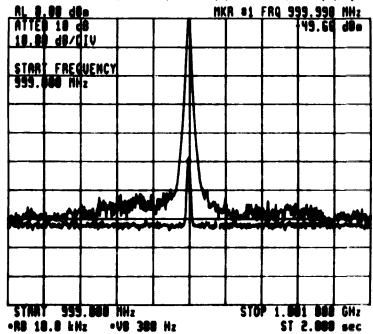

| Figure 5.3 The crosspoint isolation measurement with a HP-8642A signal            |

| generator and a HP-7100 spectrum analyzer                                         |

| Figure 5.4 The optical cross-talk measurements79                                  |

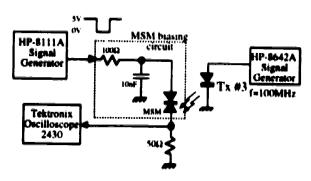

| Figure 5.5 The experimental setup for testing the switching characteristic of the |

| MSM biasing circuit80                                                             |

| Figure 5.6 Switching transients measurements                                      |

| Figure 5.7 High speed switching for MSM photodiode array with continuous          |

| bias82                                                                            |

| Figure 5.8 A block diagram of a 2-tap optoelectronic FIR filter using a direct    |

| implementation83                                                                  |

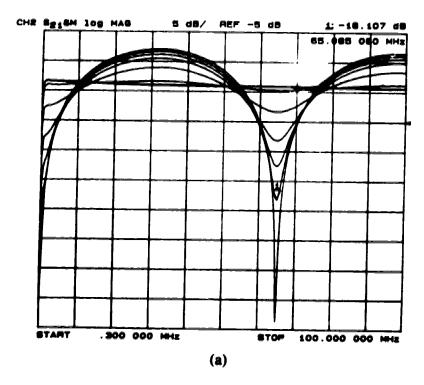

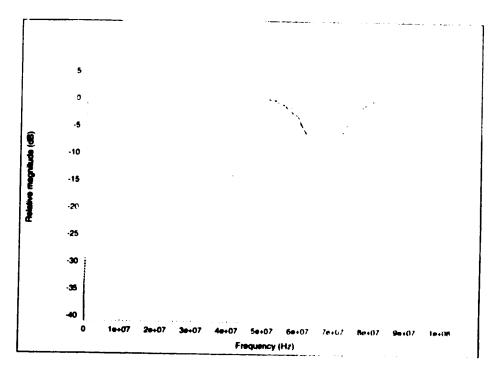

| Figure 5.9 The direct implementation FIR filter responses                         |

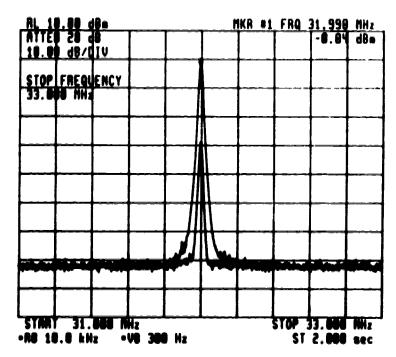

| Figure 5.10 The spectrum measurement of a 32 MHz under both high pass and         |

| low pass response of FIR filter in Figure 5.885                                   |

| Figure 5.11 The measured and predicted low pass response of the FIR filter        |

| response under different crosspoint bias                                          |

| Figure 5.12 A block diagram and a conceptual diagram of the IIR filter using the  |

| 2x2 test system                                                                   |

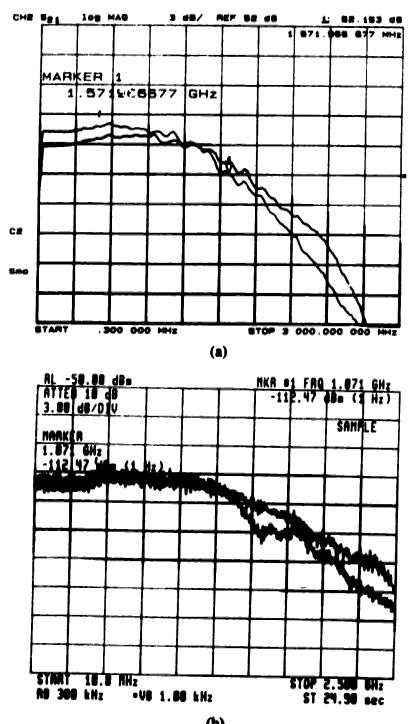

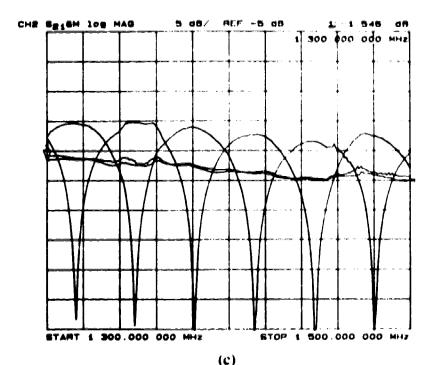

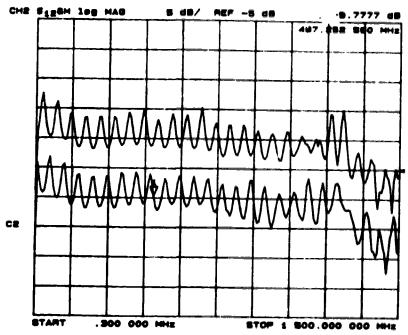

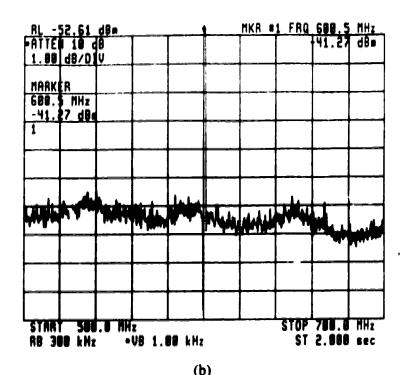

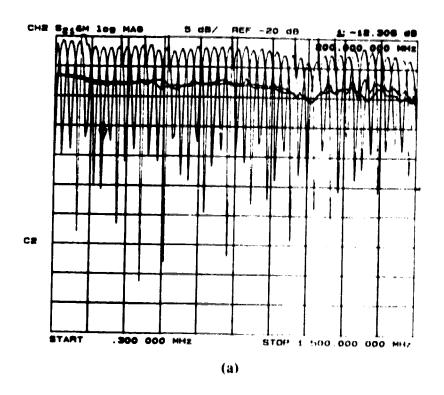

| Figure 5.13 The frequency response of the IIR filter over a 1.5 GHz. Note the     |

| low pass (lower) curve is offset by -10 dB                                        |

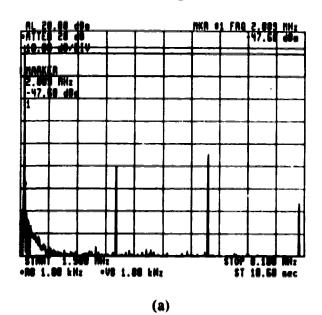

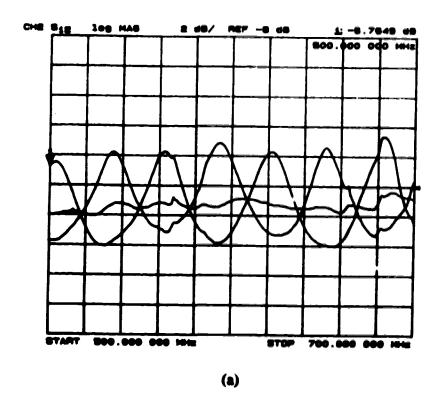

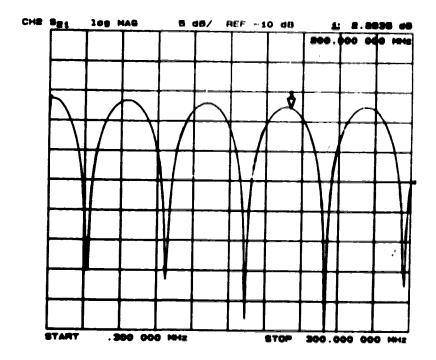

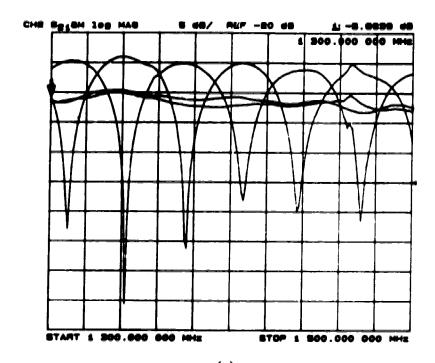

| Figure 5.14 (a) The frequency response and (b) noise floor measurement of the IIR |

| filter from 500 MHz to 700 MHz                                                    |

| Figure 5.15 The noise floor and the frequency response of the two cascading       |

| stages91                                                                          |

|                                                                                   |

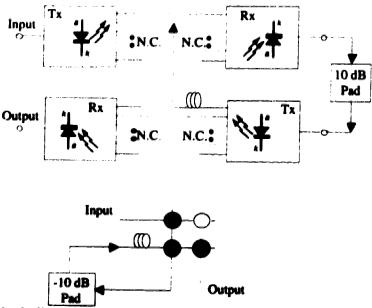

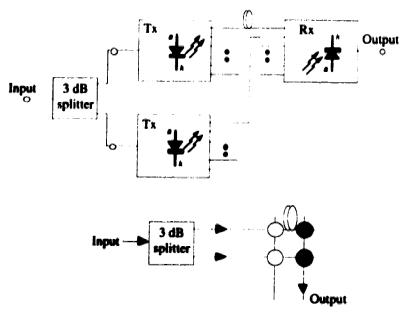

| Figure 5.16 A block diagram and a conceptual diagram of the reflex FIR filter        |     |

|--------------------------------------------------------------------------------------|-----|

| using the 2x2 test system                                                            | 92  |

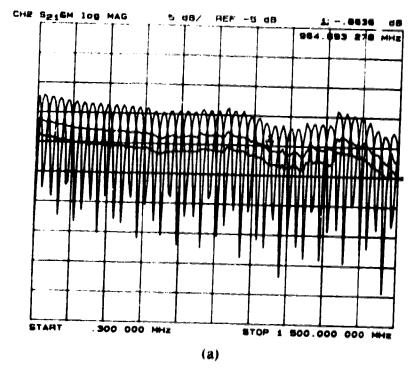

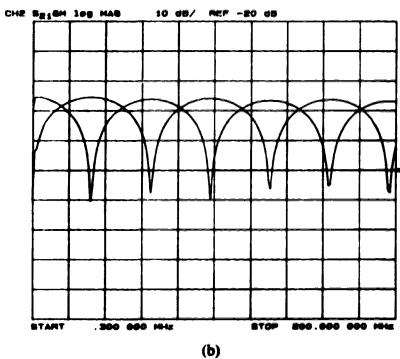

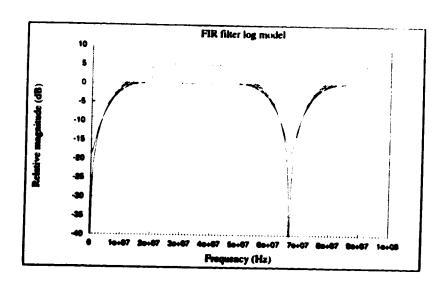

| Figure 5.17 The high pass, low pass, and all pass responses of the reflex FIR filter |     |

| (a) over 1.5 GHz, (b) from 300 kHz to 200 MHz, and (c) from 1300 MHz to 1500         |     |

| MHz                                                                                  | 94  |

| Figure A.1 The input circuit of the MSM receiver                                     | 102 |

| Figure B.1 Noise models of a single stage and cascading stages                       | 105 |

| Figure B.2 The SNR behaviors as a function of number cascading stages                | 106 |

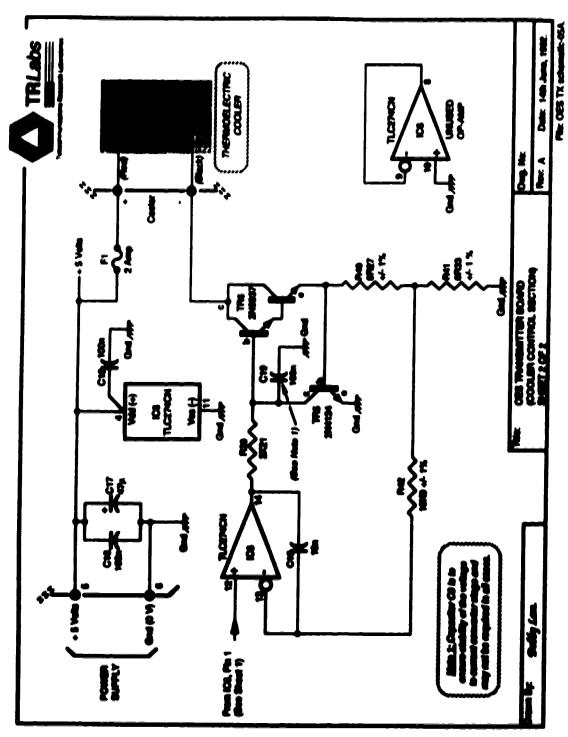

| Figure D.1 Transmitter circuit diagram                                               | 120 |

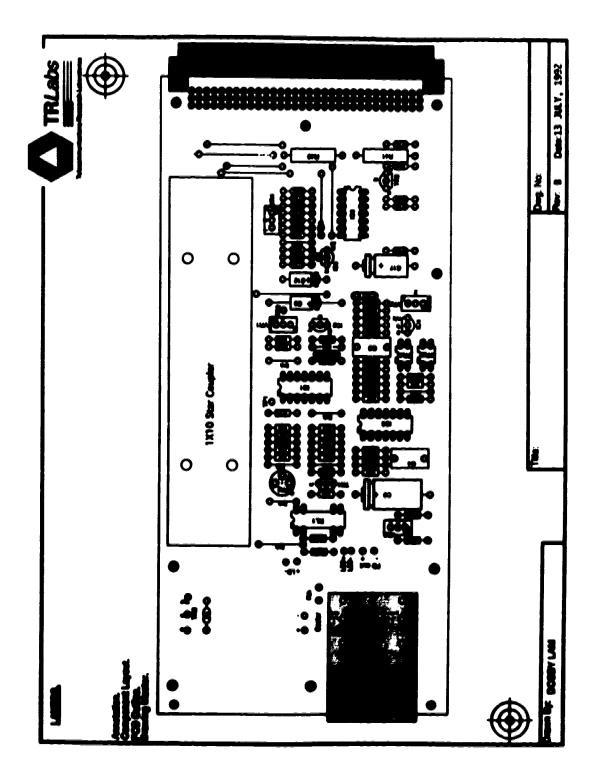

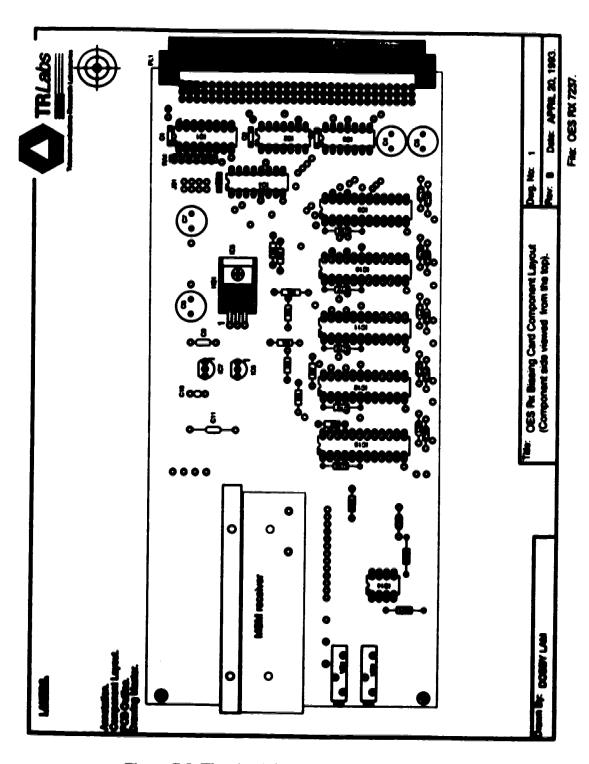

| Figure D.2 The layout digram of the transmitter card                                 | 125 |

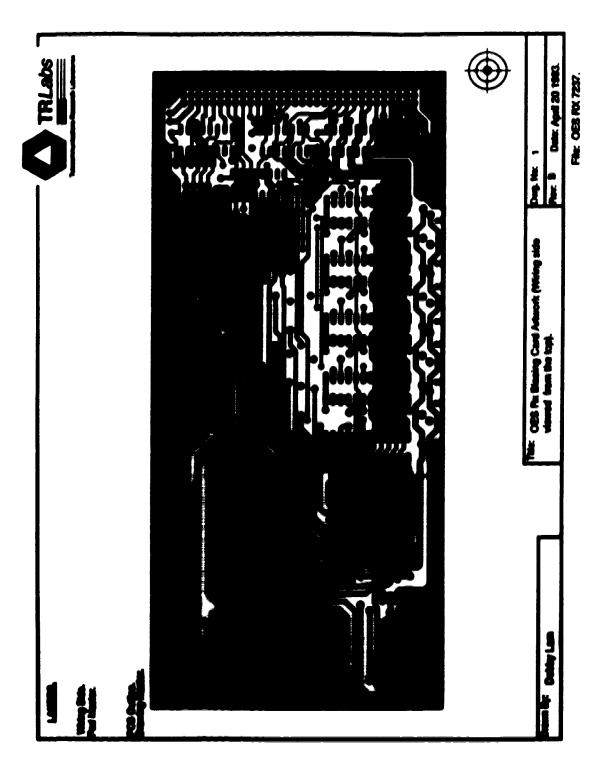

| Figure D.3 The printed circuit design for the transmitter card                       | 126 |

| Figure D.4 The layout diagram of the Bias/RF insertion unit                          | 127 |

| Figure D.5 The printed circuit board design of the Bias/RF insertion unit            | 127 |

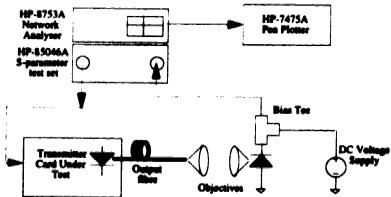

| Figure E.1 The frequency response test setup of the transmitter frequency response   | 128 |

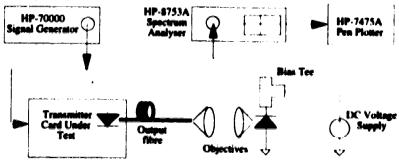

| Figure E.2 The noise floor test setup of the transmitter frequency response          | 129 |

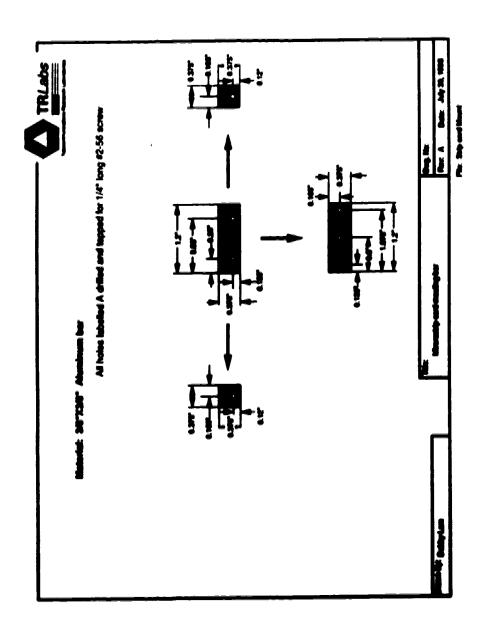

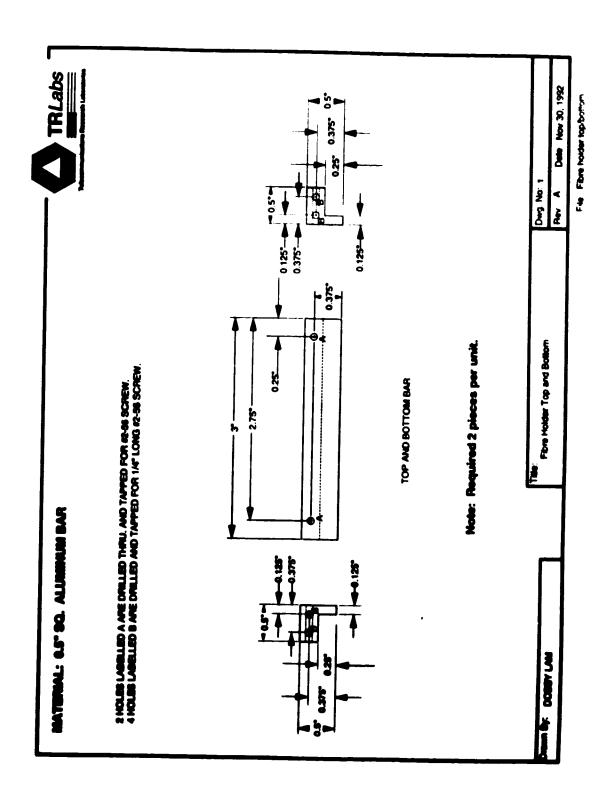

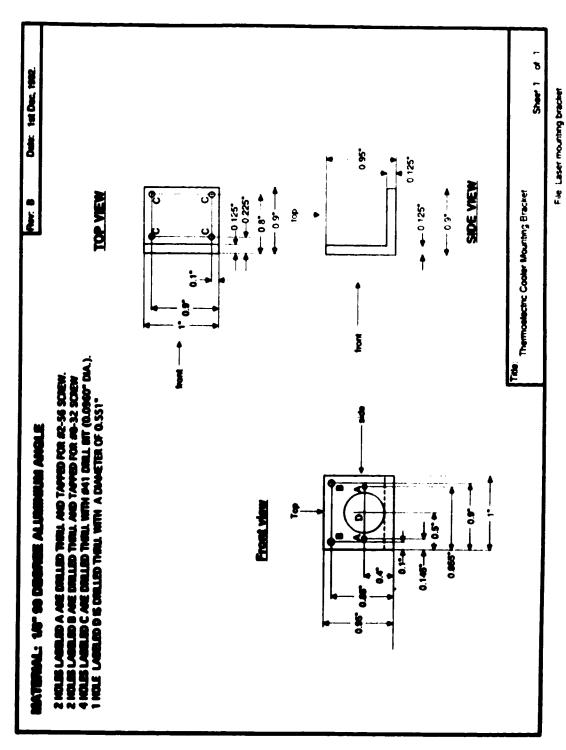

| Figure F.1 Microstrip card mounting bar design                                       | 130 |

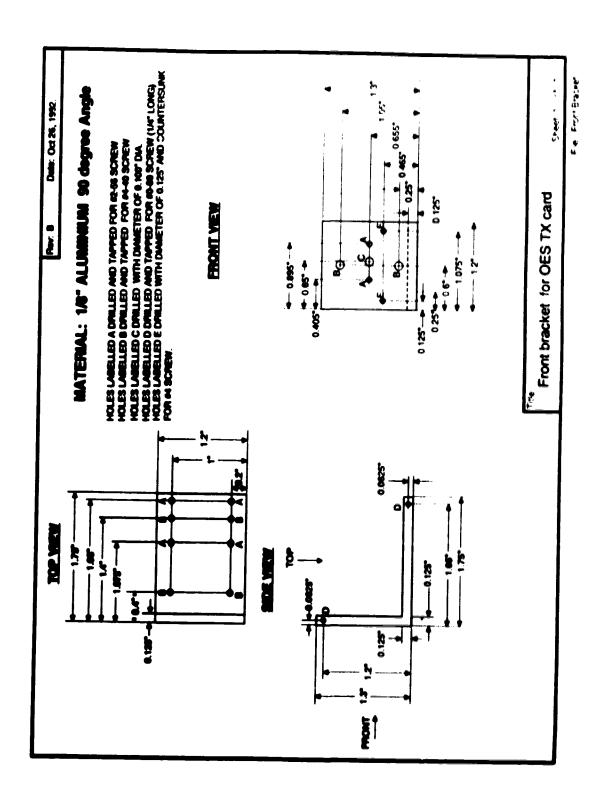

| Figure F.10 Laser mounting bracket design                                            | 139 |

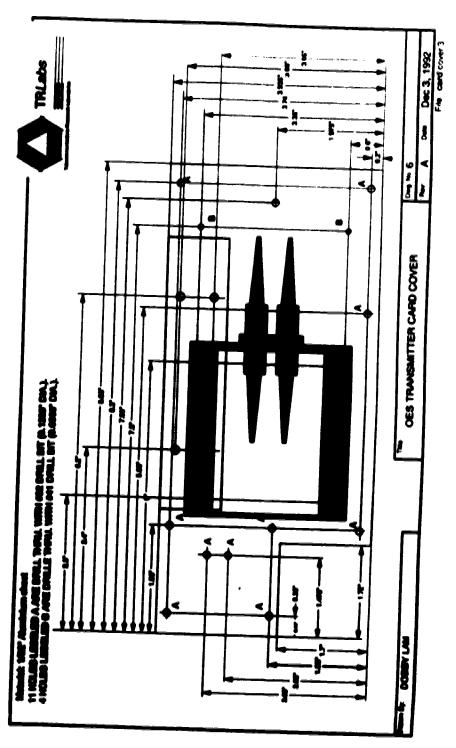

| Figure F.2 Transmitter card cover design                                             | 131 |

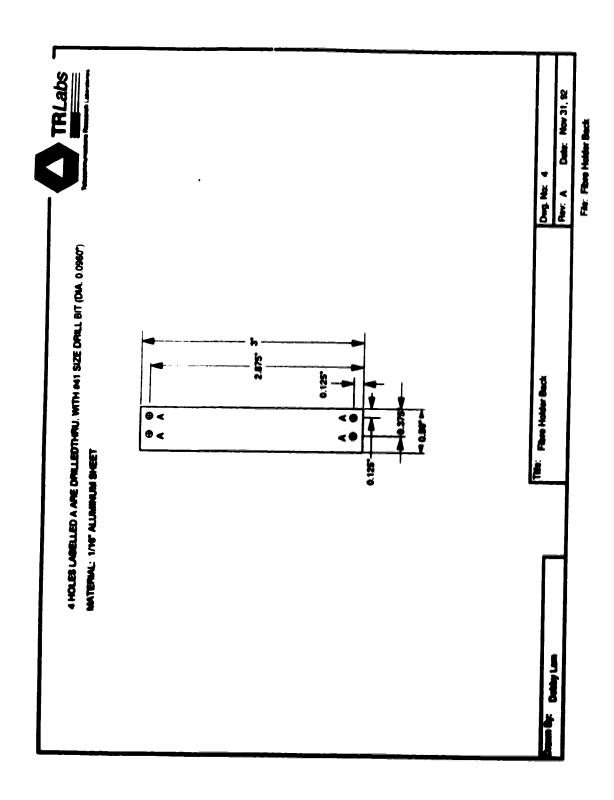

| Figure F.3 Fiber holder back design                                                  | 132 |

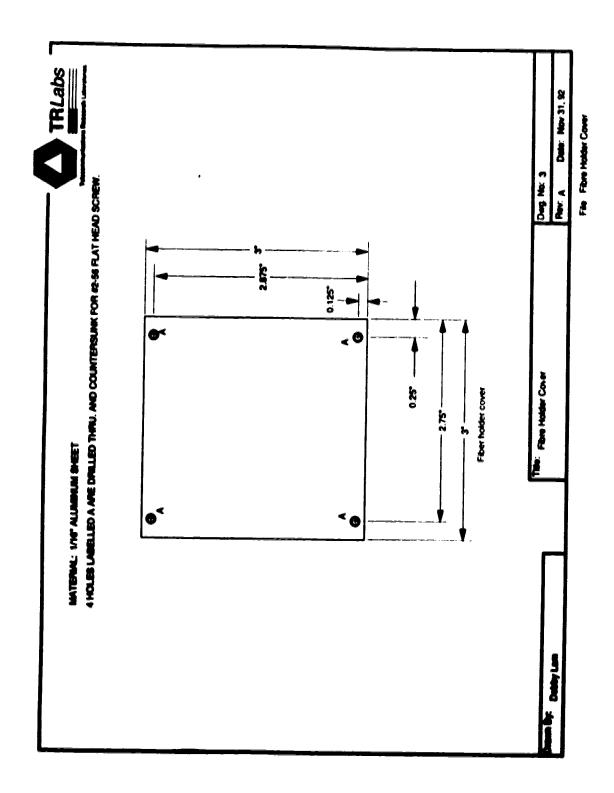

| Figure F.4 Fiber holder cover design                                                 | 133 |

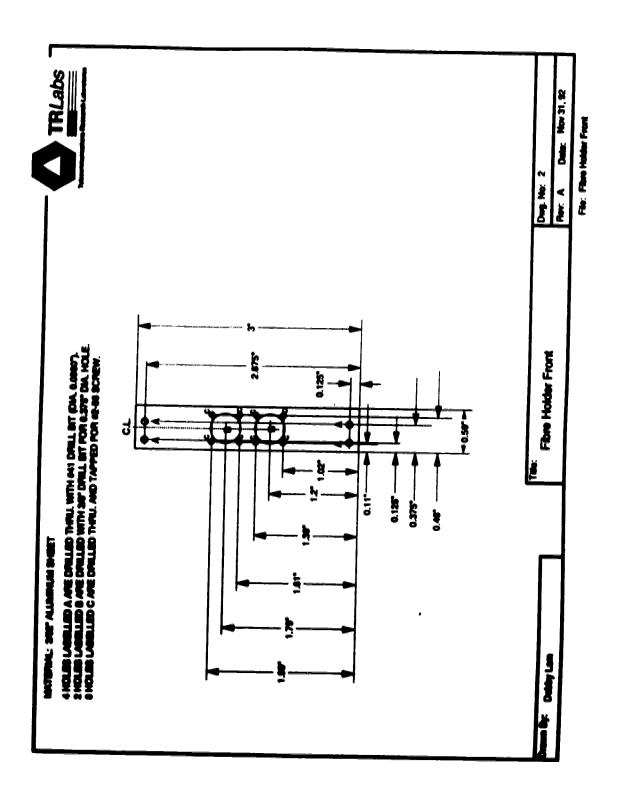

| Figure F.5 Fiber holder front design                                                 |     |

| Figure F.6 Fiber holder top/bottom design                                            | 135 |

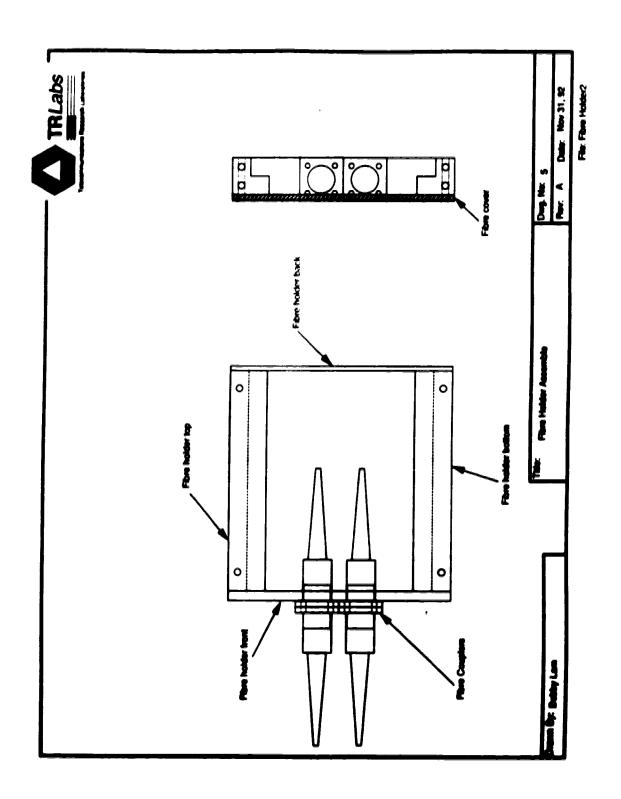

| Figure F.7 Fiber holder assembly diagram                                             | 136 |

| Figure F.8 Laser mount front bracket design                                          | 137 |

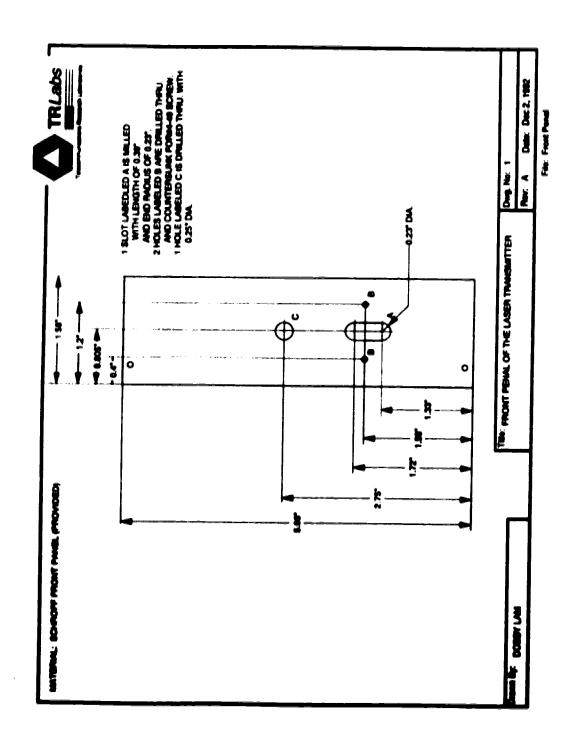

| Figure F.9 Transmitter front panel design                                            |     |

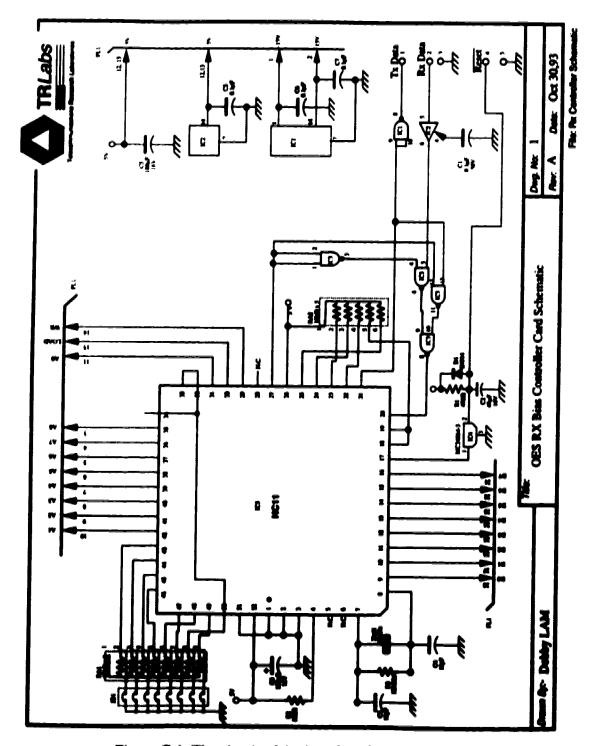

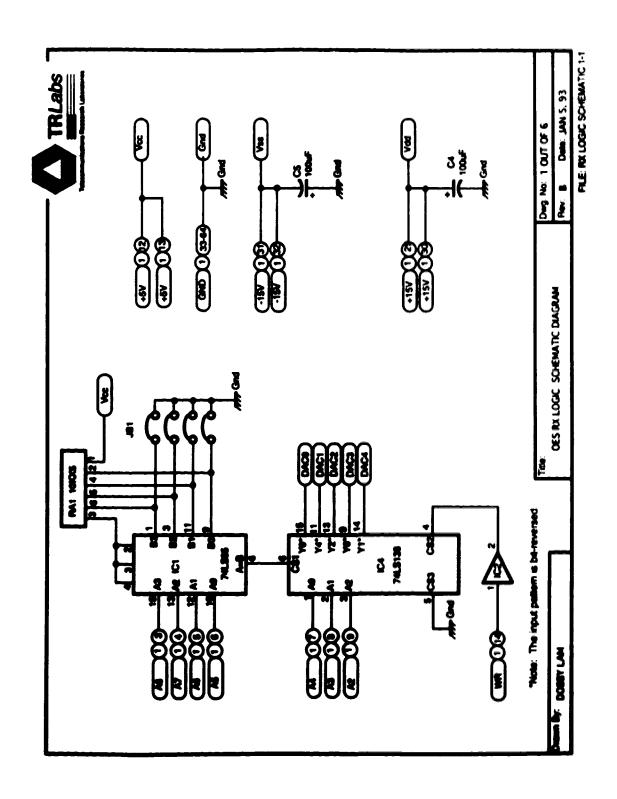

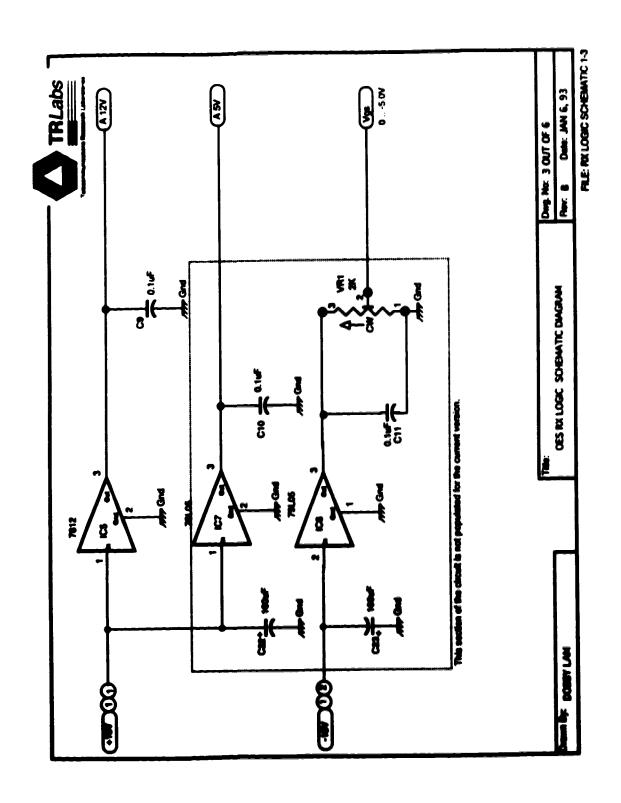

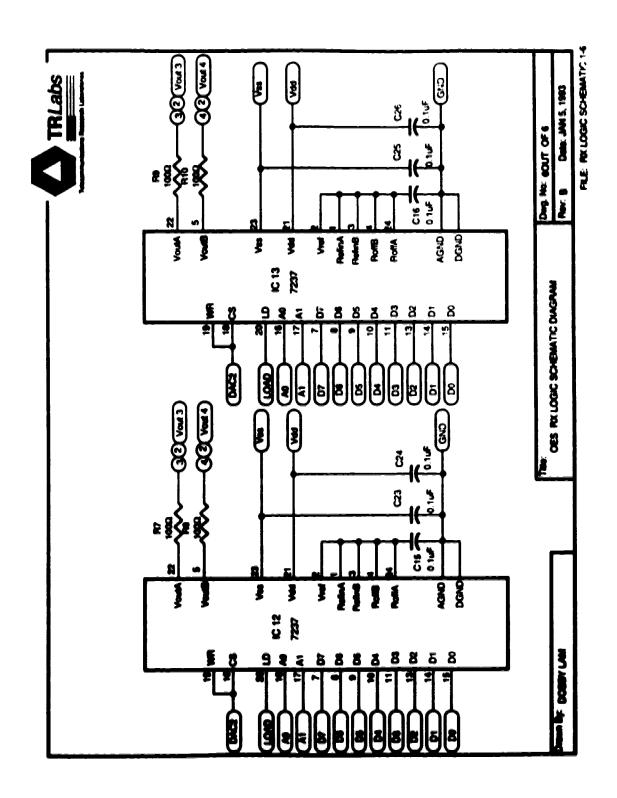

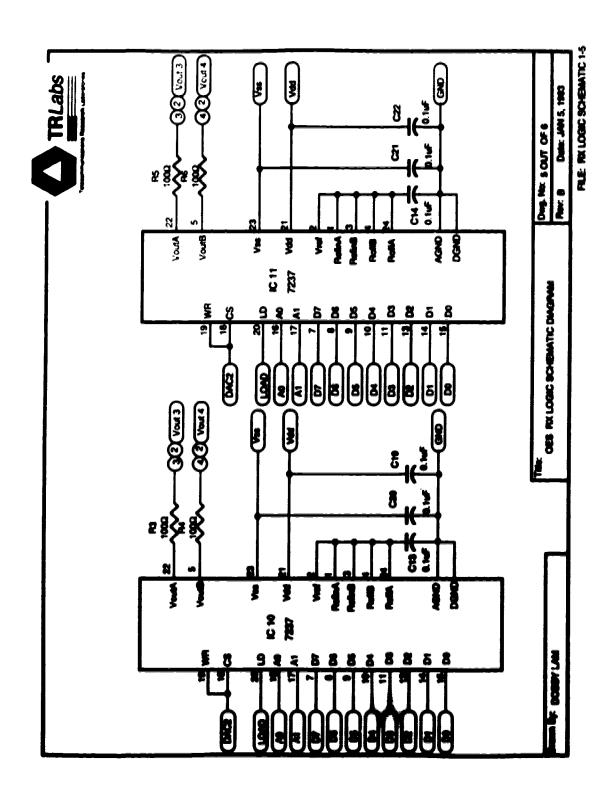

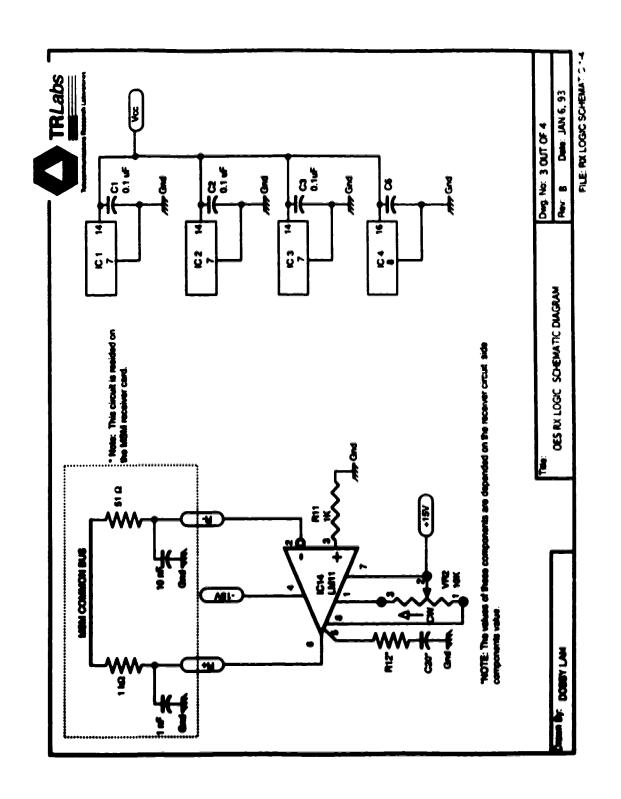

| Figure G.1 The circuit of the Interface Card                                         | 140 |

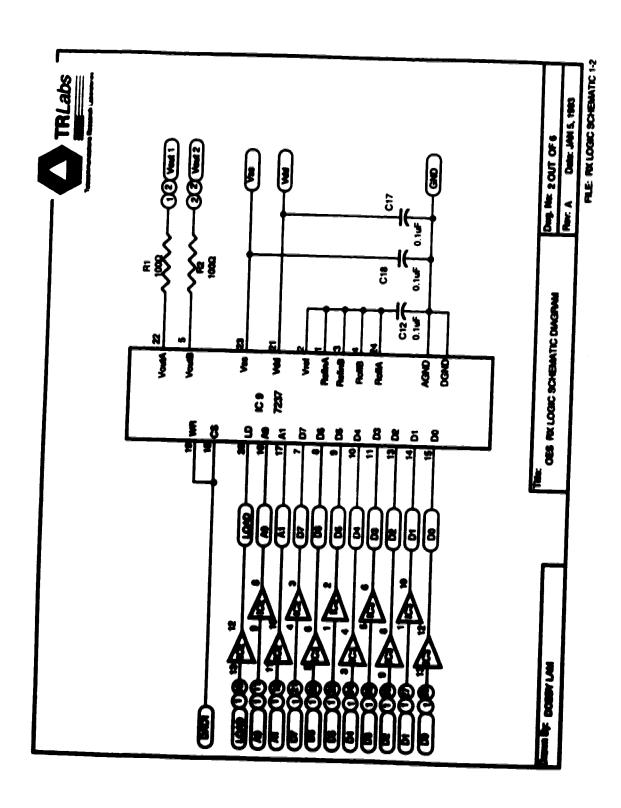

| Figure G.2 The circuit of the receiver card                                          | 141 |

| Figure G.3 The circuit layout of the receiver card                                   |     |

| Figure G.4 The circuit board masks of the receiver card                              |     |

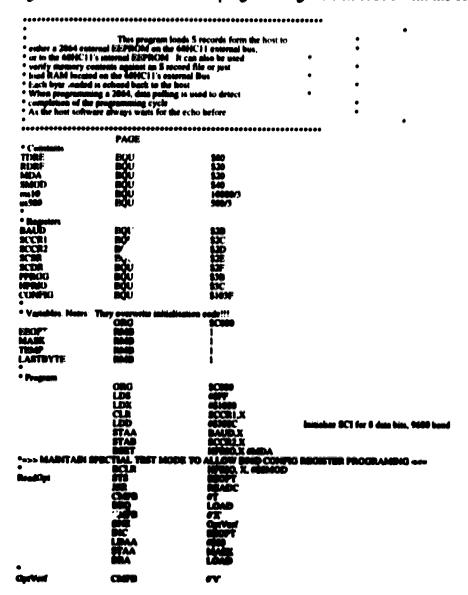

| Figure H.1 The connection for the EEPROM programming setup with HC11EVH              |     |

# LIST OF ABBREVIATIONS

| AC                     | Alternating current                       |

|------------------------|-------------------------------------------|

| ACT                    | Acoustic charge transport                 |

| APC                    | Angled physical contact                   |

| APD                    | Avalanche photodiode                      |

| BNR                    | Bell Northern Research                    |

| BW                     | Bandwidth                                 |

| CRC                    | Communications Research Council           |

| <b>CW</b>              | Continuous wave                           |

| DAC                    | Digital to analog converter               |

| DC                     | Direct current                            |

| DTSP                   | Discrete time signal processor            |

| EEPROM Electrical eras | able/programmable random access memory    |

| FC                     | Fiber connector                           |

| FET                    | Field effect transistor                   |

| FIR                    | finite impulse response                   |

| GaAs                   |                                           |

| <b>10</b>              | Input/output                              |

| IIR                    | infinite impulse response                 |

| MMIC                   | Monolithic microwave integrated circuit   |

| <b>MSM</b>             | metal-semiconductor-metal                 |

| O/E                    | Optoelectronic                            |

| OP-AMP                 | Operational amplifier                     |

| PC                     | physical contact                          |

| PIN                    | Positive-intrinsic-negative               |

| <b>RF</b>              | Radio frequency                           |

| <b>RIN</b>             | Relative intensity noise                  |

| <b>Rx</b>              |                                           |

| <b>SAW</b>             | Surface acoustic wave                     |

| SDLP                   | Switched delay line processor             |

| SNR                    | Signal to noise ratio                     |

| THD                    | Total harmonic distortion                 |

| TRLabs                 | l'elecommunications Research Laboratories |

| Tx                     | Treasmitter                               |

| UV                     |                                           |

# LIST OF SYMBOLS

| an             | FIR filter coefficients |

|----------------|-------------------------|

| b <sub>n</sub> | IIR filter coefficients |

| T <sub>5</sub> | Sampling time           |

| δ()            |                         |

| f              | Frequency               |

| i              | imaginary operator      |

| Po             |                         |

| ishot          | Shot noise current      |

| ith            | Thermal noise current   |

| Iph            | DC photocurrent         |

| ig-r           |                         |

| q,e            | Electronic charge       |

| 0              |                         |

| ζ)             |                         |

| fc             | 3 dB corner frequency   |

| 91             | • •                     |

| R              |                         |

| В              | •                       |

### 1.0 INTRODUCTION

Because of its low loss (<0.22 dB/km) and low dispersion (<17ps/nm/km), optical fiber has been widely recognized for its potential in delay line signal processing applications [1, 2, 3]. However, the high insertion loss of optical switches and the high cost of optical amplifiers restrict the implementation of a reconfigurable optical fiber delay line signal processor. Optoelectronic implementation of a switched delay line processor may be simpler and more practical. An optoelectronic ring resonator using a photoconductor receiver has been demonstrated [4], and a 16 tap transversal filter based on metal-semiconductor-metal (MSM) photodiode array has been exhibited with a programmable bandwidth of 500 MHz [5].

In this thesis, a novel signal processor, which combines optical fiber delay lines and an optoelectronic switch matrix, will be described. This processor is reconfigurable for testing different optoelectronic discrete time signal processing structures such as FIR and IIR in various signal processing applications such as adaptive filters; it can also serve as a switch matrix for broadband signal switching with a high isolation.

### 1.1 Background

### 1.1.1 Discrete Time Signal Processing

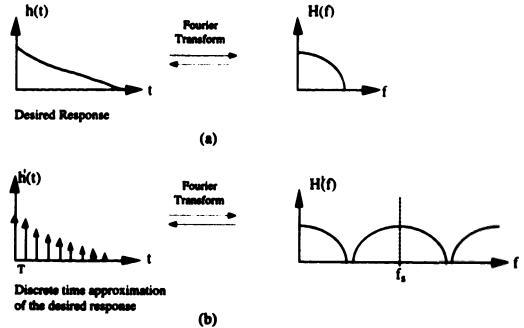

Discrete time signal processing approximates any arbitrary impulse response by using its discrete time equivalent. Since the impulse response is related to the frequency response by a Fourier transform, a desired frequency response can be approximated by its discretized time impulse response. Figure 1.1 depicts the relationship between the frequency domain representations of a continuous time impulse response and its discrete time equivalent. The discretization is achieved by sampling the continuous function at a regular interval,  $T_0$ . Note that the frequency domain representation of the discrete time response is a periodic version of the continuous time response. This periodicity is an artifact of the sampling process. The frequency domain period of the sampled response is  $I_0 = 1/T_0$  where  $T_0$  is the sampling interval.

When the bandwidth of the desired response is greater than half of the sampling frequency, the response periods can overlap each other and distort the desired response. This effect is called aliesing. To avoid the aliesing of the response, the sampling frequency, for must be at least twice the bandwidth of the continuous response.

Figure 1.1 Relationships between the time impulse and its frequency domain responses.

a) A continuous time function and its frequency response b) their discrete time equivalents.

The impulse response of a discrete time signal processor is described by

$$h(t) = \sum_{n=-\infty}^{\infty} a_n \delta(t - nT_s)$$

(1.1)

where h(t) is the impulse response of the processor,  $a_{\Omega}$  is the sampled value of the continuous impulse response, which is in general complex,  $\delta(t)$  is the impulse function, and  $T_{0}$  is the sampling interval. In theory, the sampling times can be arbitrary and not necessarily equispaced. However, arbitrary sampling times lead to a complicated filter design problem and a periodic sampling interval is normally used to simplify the analysis.

By Fourier transforming Eq.1.1, the transfer function of the series, H(f), is obtained as

$$H(f) = \sum_{n=-\infty}^{\infty} a_n e^{-j2\pi nT_n f}$$

(1.2)

which is a complex exponential series with the same coefficients,  $a_n$ . It is obvious that the discrete time series can synthesize any arbitrary periodic frequency response within the period  $2\pi/T_0$  by applying Pourier decomposition. An arbitrary periodic function, O(f), can be decomposed into a complex exponential series which is given by

$$G(f) = \sum_{n=-\infty}^{\infty} B_n e^{-j2\pi nT_n f}$$

(1.3)

where the coefficients, Bn, can be determined by

$$B_n = \int_{-\frac{1}{2T_i}}^{\frac{1}{2T_i}} G(f)e^{-j2 \operatorname{mi} T_i f} df$$

(1.4)

Comparing Eq.1.2 and 1.3 reveals that G(f) can be synthesized with a discrete time series in the form of Eq.1.1 by replacing  $a_n$  with  $B_n$ . The effects of periodicity in h'(f) can be removed by cascading a low pass filter with a cutoff frequency at half of the sampling frequency to remove the higher order periods. In many real systems, the bandlimited nature of the input signal renders an additional low-pass filter unnecessary.

It can be shown that a time impulse series with an even symmetry is transformed into a real frequency response and an odd series is transformed into an imaginary frequency response [6]. Any complex frequency response can be generated by combining the odd and even time series.

# 1.1.2 Elemental Components for a DTSP InT (a) Delay element (b) Summation element (c) Distribution element (d) Scaling element

Figure 1.2 Four basic components for a discrete time signal processor

To realize the DTSP structure described by Eq.1.1, we need to employ four basic elements: time-delay, multiplication, branching and summation [1]. Figure 1.2 illustrates these four functions and their block representations. In Figure 1.4(a), nT denotes that the signal is delayed by a multiple n of the incremental delay T. The scaling element (d) scales the output signal with coefficient, a<sub>n</sub>. The summing (b) and branching (c) elements perform the signal combining and distribution operations, respectively. By linking and arranging these four elements together, one can realize any transfer function described by Eq.1.1.

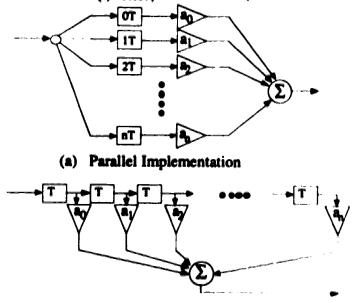

The series representation described by Eq.1.1 of the impulse response h'(t) can be synthesized with either the serial tapped delay line or the parallel pipe organ structure shown in Figure 1.3. The input signal is launched into a single delay line or a delay line array with outputs at multiple sampling intervals. Each tapped output is then scaled with a

coefficient and all are summed together to form an overall output signal. Each tapped output represents a term in the h(t) series,  $a_n \delta(t - nT)$ .

(b) Serial Implementation

Figure 1.3 Two implementations of a FIR structure

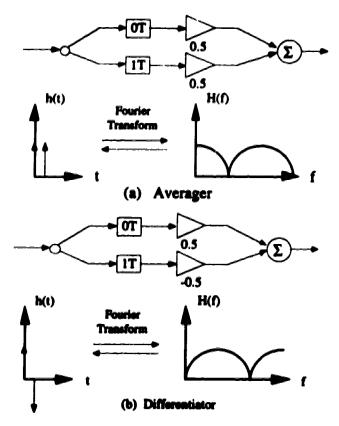

The versatility of the discrete time signal processor arises from the fact that different responses can be realized with the same structure using different coefficients. For example, Figure 1.4 shows a single delay structure filter configured as an averager (a low pass response) changed to a differentiator (a high pass response) by modifying the sign of one of the coefficients.

Figure 1.4 First order averager and differentiator using a two tap FIR filter.

# 1.1.3 Finite Impulse Response (FIR) And Infinite Impulse Response (IIR)

There are two basic categories of DTSP structures: finite impulse response (FIR) and infinite impulse response (IIR) filter structure. A FIR structure, a truncated implementation of Eq.1.1, is a feed-forward structure in which each tapped delay represents one term in Eq.1.1. The transfer function of an FIR filter structure is given by

$$H(f) = \sum_{i=1}^{M} a_i e^{-j2\pi i T_i f} \tag{1.5}$$

where M is the number of FIR stages. Figure 1.3.a and Figure 1.3.b show the two realizations of a FIR structure: serial tapped delay line and parallel pipe organ structures. The chief advantage of a FIR filter is its unconditional stability. The length of a FIR filter impulse sesponse is always finite; therefore, a FIR filter always satisfies the bounded-in-bounded-out (BIBO) stability criterion [7]. The FIR structure is widely used for adaptive applications, in which the filter coefficients might change over a wide range, to avoid oscillations.

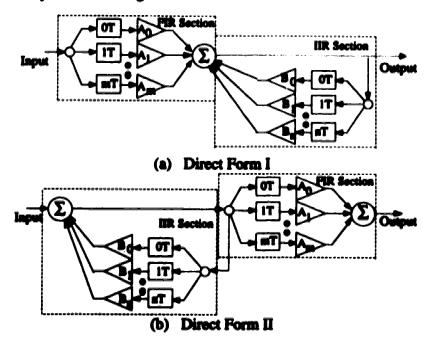

In an IIR filter, a portion of the signal is fed back into the input side of the structure. In general, an IIR filter consists a feed-forward (or FIR) section and a feedback (or IIR section) in series. Figure 1.5 shows two canonical forms of IIR filter. The response of an IIR filter is expressed in the form

$$H(f) = \frac{\sum_{n=0}^{H} a_n e^{-j2 \operatorname{mit}_i f}}{1 - \sum_{n=1}^{N} b_n e^{-j2 \operatorname{mit}_i f}}$$

(1.6)

where an and bn are the coefficients for the FIR and IIR sections, respectively [7].

Because of this feedback, an IIR filter can generate an infinite number of impulses instead of a fixed number of impulses. An IIR filter has greater efficiency than a similar FIR filter with the same number of stages; however, this feedback also causes an IIR filter to be potentially unstable with certain coefficient values. This unstability must be considered for any IIR filter design.

Figure 1.5 Two canonical forms of IIR filters

## 1.2 Implementations of the DTSP

Many different discrete time signal processor implementations are categorized by the delay medium used. In Ref.[8], the performances of various delay line technologies, such as charage coupled device (CCD), surface acoustic wave (SAW), acoustic charge transport (ACT), digital electronic, superconductive transmission line, and optical fiber delay lines, were compared in an extensive survey. In terms of the delay tap density,

CCD, SAW, and digital delay lines, which are all integrated circuit technology based devices, can provide hundreds of taps on one integrated device. Unfortunately, the bandwidths of these devices are relatively low. Only SAW and ACT delay lines can reach up to 100's of MHz. The superconductor delay line has the potential for large bandwidths (2-20 GHz) and potentially long delays due to its low loss. However, the difficulty in broadband coupling and the inherent cooling requirements prohibit any large scale realization of its broadband and low loss potentials. On the other hand, optical delay lines, both in optical fiber form or in an integrated form, can provide a bandwidth potentially up to THz's range and long delay times (10 µs's). The components for implementing broadband and long delay optical fiber delay are commercially available [9].

### 1.2.1 Optical Delay Lines

Two commonly used optical delay media are optical fiber delay lines and integrated optic delay lines. The optical fiber with its low loss (<0.22 dB/km for monomode fiber) and low dispersion (<1.7 ns/km/nm monomode fiber) is long recognized for its potential in delay line signal processing applications [1,2,9]. The optical loss of high quality monomode fiber commonly used today translates into an electrical loss less than 0.44 dB/km. Propagation delay through optical fiber is about 5  $\mu$ s/km. The high velocity of light in fiber (c ~  $2x10^6$  m/s in silica glass) relaxes the constraint on implementing high tap resolution which limits the bandwidth of slow wave delay media such as acoustic wave devices. The high carrier frequency of the optical wave reduces the difficulty in the design of broadband coupling structures which is a major difficulty for the broadband electromagnetic and acoustic delay line [10, 11].

The integrated optic waveguides in various forms, such as ridge, slab, or diffusion types, have a typical propagation losses of fractions of a dB/cm which is considerably higher than optical fiber [12,13,16]. On the other hand, using common lithographic processing, integrated optics offers short, precision time delay down to the picosecond range which is difficult to implement with optical fiber devices [13]. Furthermore, the potential for integrating optoelectronic and optical components, such as lessers and optical couplers, in the same substrate promises the possibility of a monolithic optical delay line signal processor [12, 13]. The high precision delay also allows the application of coherent optical techniques which could generate complex top coefficients directly by interfering two coherent optical signals [13]. The use of a broadband complex coefficient adds an extra degree of freedom in discrete time signal processor design such as the optoelectronic dispersion componentor described in Ref.[15]. However, the maximum time delay of the

integrated optic delay line device is limited by the size of a semiconductor wafer which is constrained to a few inches in diameter. A 1m (~ 5ns delay) long silica integrated delay line coil that occupied an entire 5 inch wafer with only 4 dB loss has been reported [16].

## 1.2.2 Optical Discrete Time Signal Processor

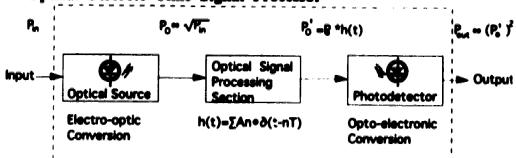

Figure 1.6 A block diagram of a generalized optical signal processor. Pin and Pout are the input and output electrical power level and Po and Po are intermediate optical power level inside the signal processor.

Figure 1.6 depicts a block diagram of a general optical discrete time signal processor. The input electrical signal is converted into optical form by means of a directly modulated laser diode, or alternatively, an unmodulated laser diode source with an external intensity modulator. The optical signal is then launched into an optical signal processing section where it is manipulated to produce the desired time impulse response function. Inside this optical signal processing section, the optical signal is split, delayed, weighted, routed, and combined to form the desired impulse response. At the output terminal, the optical signal is converted back into electrical output by a photodetector.

In an optical DTSP system, the optoelectronic conversion is confined to the two edges of the system and all the signal processing functions are implemented by optical means. A variety of novel optical techniques, such as microbend adjustable directional couplers [17], fiber V-groove adjustable couplers[18], integrated coherent adjustable couplers [13], and etched fiber reflectors [19], have been developed to implement optical discrete time signal processors. The high coupling loss of these optical devices requires an optical amplification step in order to maintain a reasonable signal to noise ratio. Recently, optical amplification as a weight setting technique and a new class of IIR fiber filter design based on this technique have been proposed[20,21]. The current cost of optical amplifiers, such as erbium doped fiber amplifiers, or semiconductor optical amplifiers, is relatively high (~\$20,000 for an erbium doped fiber amplifier currently [21]). The cost of the optical amplifier and the losses of adjustable couplers prohibit any large scale implementation of optical DTSP.

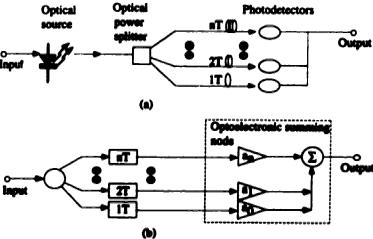

### 1.2.3 Optoelectronic Discrete Time Signal Processor

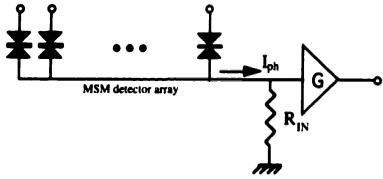

The major difference between an optoelectronic discrete time signal processor and an optical discrete time signal processor is the usage of optoelectronic conversion in the processing itself. In an optoelectronic DTSP, the optoelectronic conversion is applied to perform two signal processing functions: weighting and summation. Figure 1.7 shows a block diagram of an optoelectronic signal processor in a transversal (FIR) filter configuration. The input signal is converted into optical form by an optoelectronic process as discribed previously. Then the signal is distributed and delayed in an optical form. The scaling and the summing of the intermediate signals into the output signal are performed with an optoelectronic weight setting technique using a photodetector array with a common output bus.

Figure 1.7 (a) a schematic diagram and (b) a block diagram of an optoelectronic FIR filter

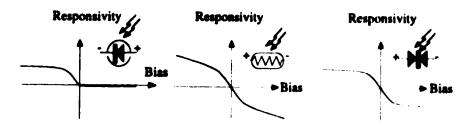

Optoelectronic weight setting modifies the output of a photodetector by electrically modulating its responsivity <sup>1</sup>. The responsivity of a photodetector, such as photodiode or photoconductor, is dependent on its biasing voltage. The biasing voltage controls the carrier transit time, and hence the ratio of transit time to carrier lifetime, that is the photoconductive gain (or attenuation in devices such as photodiodes that do not permit the carrier injection necessary for true photoconductive gain). For a given optical input, the output photocurrent can be scaled by controlling the bias voltage of the photodetector. Pigure 1.8 depicts the relationships between the bias voltage and the responsivities of three different types of photodetectors. A unijunction photodiode, such as an avalanche

<sup>&</sup>lt;sup>1</sup>The responsivity is defined as the ratio between the output photocurrent and the optical power incident on the photodetector.

photodiode (APD) or positive-intrinsic-negative (PIN) photodiode behaves asymmetrically under bipolar bias because of its n-p structure. On the other hand, the symmetric structure of a photoconductor or a double junction photodiode, such as a metal-semiconductor-metal (MSM) or Mott photodiode, generates an antisymmetric response under a bipolar bias.

Figure 1.8 The typical photoresponsivities of various photodetectors. A unijunction photodiode, a photoconductor, and a double junction photodiode.

An advantage of optoelectronic weight setting is that the output signals are in the form of photocurrent and can be easily summed together. This summation is accomplished by simply passing multiple intermediate current signals through a common load. A photodetector array with a common output node forms an optoelectronic weighted summing node [22]. By summing photocurrents instead of optical power, optoelectronic summation avoids the addition of temporally coherent signals or spatially coherent signals leading to interference noise. (Incoherent summation of optical signals is not possible. Only mixing can be accomplished.).

### 1.2.3.1 Historical Perspective of Optoelectronic Signal Processing

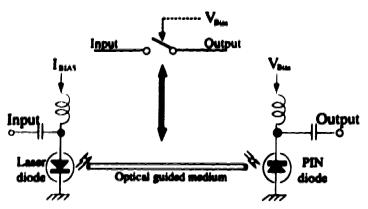

The first optoelectronic signal processing was used for switching high frequency signals. Optoelectronic switching in the form of optical gating, with a photoconductor used as an optically controlled switch, was first proposed and demostrated by Auston in 1975 [23]. Optoelectronic weight setting by means of photodetector bias which electrically controls the photodetector responsivity was first demonstrated as a form of switching by MacDonald and Hara in 1978 [22]. Their paper described an optoelectronic switch with an isolation up to 80 dB at a bandwidth of 100 MHz using a PIN photodiode. Figure 1.9 shows the optoelectronic switch described by MacDonald and Hara; the signal switching is accomplished by biasing the photodiode in two states which are formed by applying forward or reverse bias to the PIN photodiode. Subsequently, other devices such heterojunction photodiodes [24], APD [25], and photoconductors [26] had been demonstrated for optoelectronic switching in this sense.

Figure 1.9 The optoelectronic switch using a PIN photodiode. The switching is achieved by completing the optoelectronic signal path using a photodiode bias.

The use of an optoelectronic matrix as a variable delay line was proposed and demonstrated in 1984 [4], using the reflex configuration that is the subject of this thesis. The use of this reflex configuration to perform analog/digital conversion was proposed in 1986 [27], using an optoelectronic continuous weight setting process. Optoelectronic weight setting for signal processing was first demonstrated by Lee [28] in 1991 for an optoelectronic neural network application. An optoelectronic switch matrix with optical fibre delay line as a configurable signal processor was proposed in 1986 in a form of switched delay line signal processor (SDLP) [29]. The first demonstration of continuous weight setting for filtering was demonstrated in an optoelectronic transversal filter experiment [5]. In that experiment, a MSM photodiode array was used to realize a 16 tap transversal filter in a pipe organ (parallel) configuration with a 500 MHz programmable bandwidth.

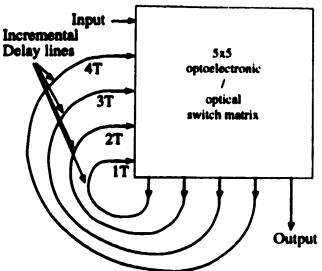

Up to the present, the experimental results on both optical and optoelectronic delay line signal processors have been based on a predefined configuration. In this thesis, we expand the transversal filter structure used by Swekia [8] into the reconfigurable delay line processor described by MacDonald [29]. MacDonald described a switched delay line signal processor which combines a switch matrix (optical or optoelectronic) with optical fiber delay lines. Figure 1.10 is a conceptual diagram of switched delay line signal processor. This processor can be configured to apply a variety of different signal processing operations such as filtering and code generation either by electronically routing the signal or physically modifying the optical connections.

Figure 1.10 A conceptual diagram of a 5x5 switched delay line signal processor

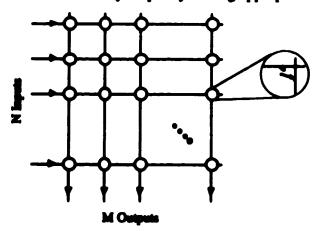

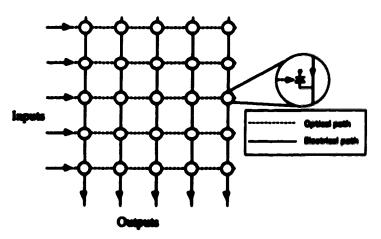

Figure 1.11 is shown an NxM switch matrix which consists of an N dimensional vector of inputs and an M dimensional vector of outputs. The inputs and the outputs are connected via a set of NxM crosspoints; each crosspoint being made up of a switch. Any input can be routed or distributed to any output by closing appropriate crosspoints.

Pigure 1.11 A NxM switch matrix

Two crucial requirements for implementing a switch matrix are low crosstalk among the channels and a high isolation between switching states because of the proximity of the input channels and the multiple shared inputs on each output. High isolation and low crosstalk are required to minimize the interference on any output from the unwanted input signals and from adjacent signal paths. These two requirements make optoelectronic switching a suitable technology for high frequency matrix switching. A major advantage of optoelectronic switching over its electrical counterpart is the potentially low crosstalk

between channels. By using a guided medium, such as optical fiber, to distribute the optical signal from the light source to the photodetector in conjunction with an electromagnetic shielding, the electromagnetic crosstalk can be reduced to practically zero. An optoelectronic crosspoint with 85 dB isolation has been demonstrated using a heterojunction photodiode [24].

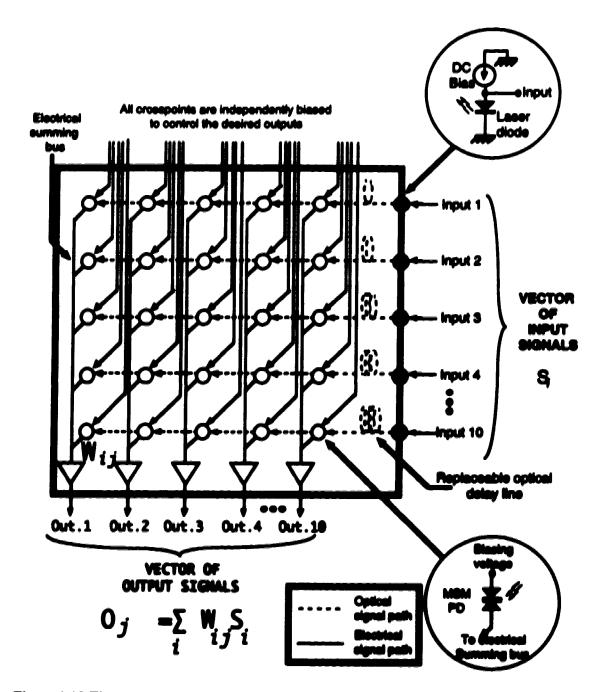

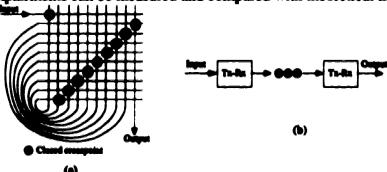

### 1.2.3.3 Optoelectronic Switch Matrix

In a typical optoelectronic switch matrix shown in Figure 1.12, the inputs are converted into an optical form and each optical signal is distributed into a row of optoelectronic crosspoints. Each crosspoint consists of a photodiode with a control bias. The crosspoint is "closed" or "opened" when the photodiode is sensitized or desensitized to the optical signal input by modulating the bias. The required bias control states are determined by the photodetector type used for the crosspoint. For example, for a PIN diode, forward and reverse biases are commonly used for the "opened" and "closed" states respectively. Each matrix output is formed by summing the photocurrent from a column of photodetectors.

Figure 1.12 a 5x5 optoelectronic switch matrix

A similar 10x10 optoelectronic switch matrix using a novel depletion channel photoconductor array has been demonstrated to have a continut ratio greater than 60 dB over a 1.8 GHz bandwidth. However, due to the intrinsic properties of depletion channel photoconductor, the crosspoint consistently failed after a short period of operation [30]. In this project, we replace the depletion channel photoconductor with a MSM photodiode which is physically a more stable device and has been demonstrated in many monolithic

optical receiver designs. The operation frequency of a single MSM photodiode has been reported up to the 375 GHz range [31].

The MSM photodiode proposed for this project was reported to have a lower isolation (typically 50 dB or less) than the depletion channel photoconductor [30]. The lower isolation of MSM photodiode is chiefly caused by an imbalance in the photovoltages of the two opposed junctions which can be caused by an imbalance either in barrier heights or in the illumination pattern [30]. This imbalance in photovoltage can be partially corrected by applying external bias. Furthermore, the crosspoint isolation can be enhanced by applying additional electronic techniques such as a transmission gate [32] in future integrated versions of the processor.

### 1.3 Proposed Signal Processor Structure

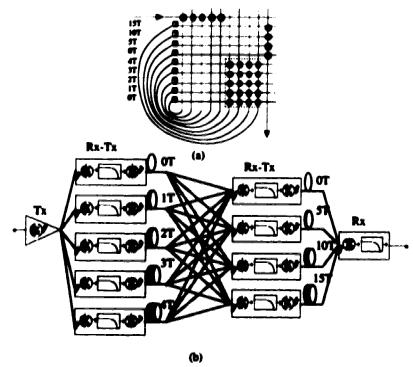

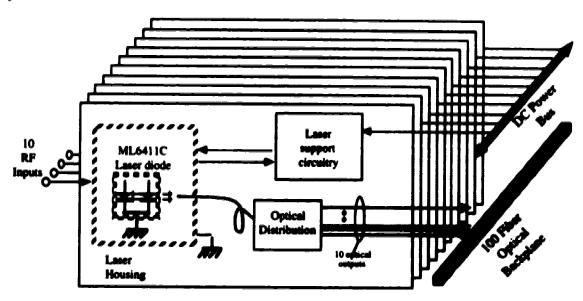

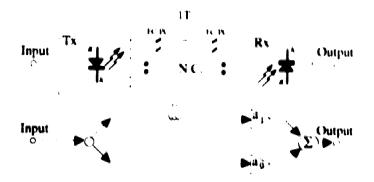

Figure 1.13 shows a conceptual diagram of the reflex optoelectronic signal processor proposed for this project. The processor is based on a non-blocking switch matrix configuration with input rows and output columns. Each input row is connected to a laser diode which converts the input electrical signal into an optical signal using intensity modulation. This optical signal is launched through an optical delay line and split among 10 fibers using a fiber power splitter. These 10 optical signals represent one input row inside the matrix. One output from each fiber splitter is gathered to form an optical bundle and one of these 10 bundles is fed to each of ten optical receivers. Each optical receiver thus represents an output column from the matrix. Inside the optical receiver, a MSM photodiode array with individual photodiode bias connections acts as a column of crosspoints and a common electrical output bus sums the photocurrents from the entire detector column. An electrical amplifier is then used to compensate for the optoelectronic conversion and optical power splitting losses.

Optoelectronic switching or optoelectronic weight setting is achieved by controlling the bias to each crosspoint. By changing the biasing pattern of the switch crosspoints, one can route, scale, and combine the signals through the switch. By connecting outputs back to inputs with appropriate time delays and by biasing the detectors with appropriate voltages, the switch can be configured to perform different signal processing functions.

Figure 1.13 The proposed optoelectronic discrete time signal processor based on a 10x10 matrix

The goals of this project were to construct the sellex optoelectronic signal processor based on a 10x10 optoelectronic switch matrix, to demonstrate the possibility of optoelectronic signal processing, and to study the signal degradation due to circulating the signals through the matrix.

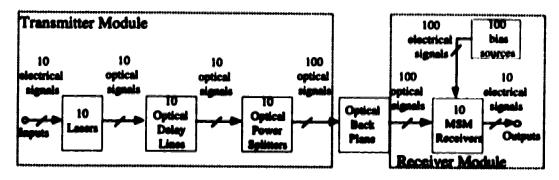

Figure 1.14 shows the organization of the proposed processor. The processor divides into two modules: transmitter module and receiver module. These two modules are linked with an optical backplane. The transmitter module represents the 10 input rows of the matrix; it converts the 10 electrical inputs into 100 delayed optical signals to illuminate 100 crosspoints. The receiver module represents the output columns of the matrix; it converts the optical signals back into 10 electrical outputs according the crosspoint biases. 100 programmable bias sources in the receiver module are used to generate 100 crosspoint biases.

Figure 1.14 The organization of the proposed processor

### 1.4 The organization of the thesis

In Chapter 2, the performance of the proposed system in various applications is estimated based on the available components and the configuration used. In Chapters 3 and 4, the detailed structures and performances of the switch modules are presented. In Chapter 5, the performance of the processor for different signal processing functions is investigated and results are presented. In Chapter 6, a summary of the completed portion of the processor is presented and future experimental directions are described.

### 2.0 SYSTEM CONSIDERATIONS

In this chapter the components of the reflex optoelectronic signal processor are described. The performance of the processor with available components is estimated and some requirements of the processor for various applications are examined and estimated.

### 2.1 Component Performance

The performance of the processor is determined by its components. Four major components which dictate the system performance are the photodetector array, receiver amplifier, laser diode, and fiber optic elements. In this section, we examine the characteristics of these components and their impacts on the system performance.

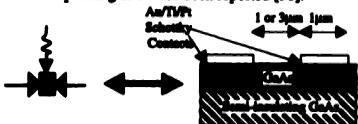

## 2.1.1 Metal-comiconductor-metal (MSM) photodiode array

The heart of the optoelectronic switch matrix is the crosspoint photodetector array which determines the isolation and the bandwidth of the crosspoints. The photodetector used in this project is a MSM photodiode array. Figure 2.1 shows a MSM photodiode which consists of a double Schottky contact structure on a thin epitaxial layer of intrinsic Gallium Arsenide (GaAs) grown on a semi-insulating GaAs substrate. The thin epitaxial active layer confines the photogenerated current to flow within the high electric field surface region which enhances the speed of the photodiode. The double Schottky contact of a MSM detector eliminates low frequency photoconductive gain, as seen in photoconductors, by blocking carrier re-injection [33]. The double Schottky barrier also reduces dark current which ranges from hundreds of nA to less than 1nA depending on the Schottky contact [34, 35]. A single MSM detector with a bandwidth of 375 GHz and a dark current of 300 nA operating at 8V has been reported [31].

Figure 2.1 A cross-section view of an MSM photodetector used in this project and its circuit equivalent

The symmetry of the MSM photodiode allows biasing with either polarity, making possible either positive or negative photocurrent from a single detector with one optical input. This bipolar sensitivity permits bipolar weight setting, which is required for some signal processing operations, such as differentiation and subtraction [36]. Other

optical/optoelectronic signal processors require either two separate, parallel weight setting subsystems for positive and negative weights [1,20,29] which causes an additional 3 dB optical loss, or a coherent optic system which requires a narrow linewidth and highly stable source, to generate bipolar weights [13].

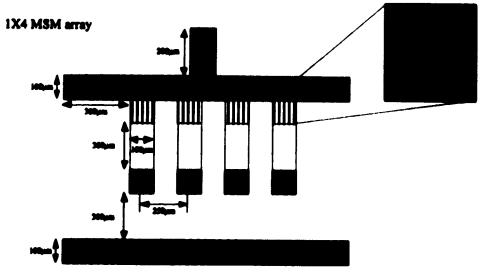

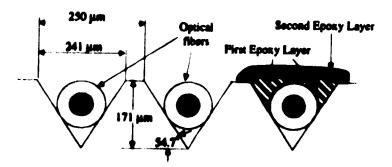

Figure 2.2 A schematic diagram of the 1x4 MSM detector array

Figure 2.2 shows a drawing of the MSM photodiode array used in this project. The detector was designed by Rohit Sharma of the Telecommunications Research Laboratories (TRLabs) and was fabricated by Bell Northern Research (BNR) in Ottawa, Canada [37]. The pitch of the detector array is 250 μm center to center, chosen to be compatible with the standard optical fiber ribbon cable. Photodiodes with two different finger spacings, 3μm and 1μm, and different sizes arrays (1x4, 1x8, and 1x12) were fabricated for different responsivities and bandwidths. The frequency responses of these detectors in parallel was confirmed to be above 1.6 GHz at TRLabs. This measurement was limited by the optical source bandwidth. The bandwidth of a single detector was measured to be 4.5 GHz at CRC [38], using a wideband optical source. The photodiode with 1μm finger spacing was selected for this project because it exhibited a higher bandwidth than the 3 μm spacing photodiode during the initial testing.

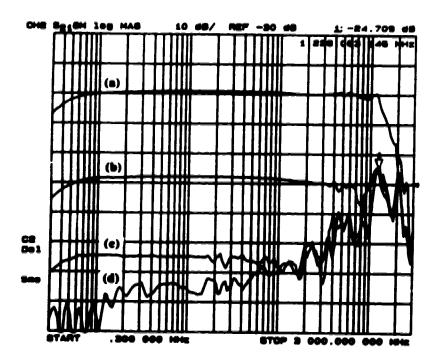

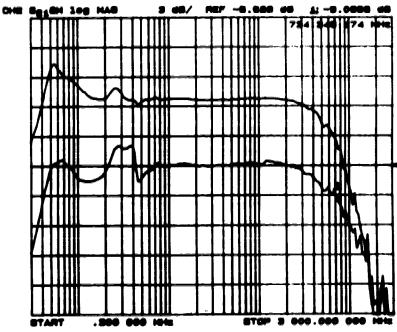

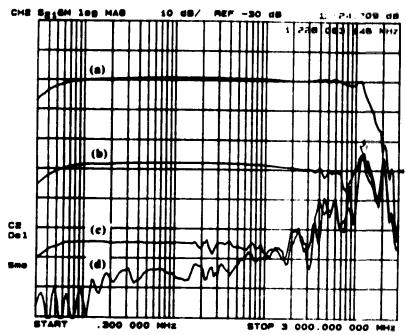

The relationship between the bias voltage and the frequency response of a 1 µm MSM detector is illustrated in Figure 2.3 which shows the isolation between ON state (5V bias) and three different OFF states. The three different OFF state conditions are open circuit bias, 0 V (short circuit) bias, and 12.7 mV bias<sup>2</sup>. Note that the highest isolation occurs when the OFF state is an open circuit, or when the photodiode is biased

<sup>&</sup>lt;sup>3</sup>This value varies from detector to detector.

slightly above zero voltage, rather than OV bias. The requirement for an offset voltage to achieve minimal sensitivity may be explained by an imbalance of the photovoltages of the two junctions. Under open circuit bias, the residual photocurrent is eliminated by the high series impedance of the open circuit and thus the output current is dominated by the noise floor of the measurement setup.

Figure 2.3 The frequency response of a 1 $\mu$ m MSM detector under different biasing conditions.  $P_o = 410 \,\mu$ W. The bias conditions are (a) 5V, (b) 0V, (c) 12.7mV, and (d) open circuit. The output is amplified with a 56 dB amplifier.

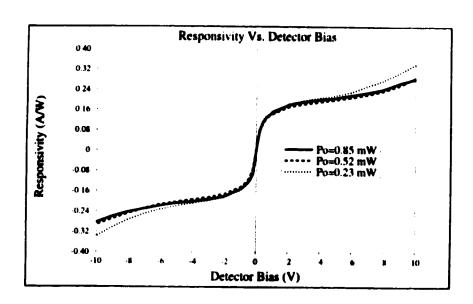

Figure 2.4 The DC response of 1 µm photodiode under different bias voltages and optical powers.

Figure 2.4 shows the DC response of a 1  $\mu$ m detector with different biasing voltages and optical powers [39]. When the detector is under a high bias, the dc responsivity of the detector is in excess of the theoretical<sup>3</sup> predicted value of 0.21 A/W. This apparently indicates a gain caused by high applied fields. Because Schottky barrier height can be lowered under an intense electric field [40], there may be carrier reinjection at high bias, permitting photoconductive gain.

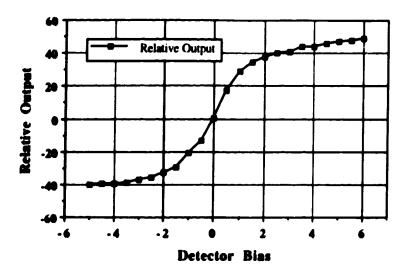

Figure 2.5 shows the relationship between the detector bias and the output signal recorded with a modulation frequency of 200 MHz. Note that this relationship is not exactly symmetric which might indicate an imbalance of the Schottky contacts or an imbalance in the DC photovoltage. This would also explain the offset bias required to extinguish the crosspoints. Saturation of the output signal was observed at a bias greater than 2 V.

<sup>&</sup>lt;sup>3</sup>See Appendix I for detailed responsivity calculations.

Figure 2.5 The AC response of a 1 μm MSM photodiode as a function of bias. f=200MHz. Po=410 μW.

#### 2.1.1.1 Detector noise

The detector noise is a major factor influencing system performance. There are three major noise mechanisms for the MSM photodiode: shot noise, thermal noise, and generation-recombination noise [41].

When a current flows across a potential barrier, the individual carriers cross the barrier independently and at random. This random process gives rise to shot noise. Assuming a constant noise distribution over frequency, the mean square shot noise current corresponding to a given DC current I is given by [42]

$$\langle i_{\text{that}}^2 \rangle = 2qIBW \tag{2.1}$$

where q is the electronic charge and BW is the bandwidth.

There are two current components in every photodetector: dark current and photocurrent. In a photodetector, the dark current is the current portion present when the detector is not illuminated. This current is due to leakage through the barrier or the device surface [41]. The exact value of this leakage is determined by the properties of the metal-semiconductor interface and the bias voltage level. The dark currents of different samples tested vary from microamperes (10-4 A) to not observable.

The photocurrent shot noise, also known as current noise, is the shot noise caused by the average signal current [41]. Based on a responsivity of 0.2 A/W and an incident optical power of 500  $\mu$ W, the DC photocurrent is expected to be on the order of 100  $\mu$ A which is significantly larger than the dark current; therefore, the photocurrent shot noise dominates the shot noise contribution. A study with similar MSM devices has shown that

the dark current can dominate the shot noise contribution under an extremely high bias voltage (~ 50 Volts) [34].

Based on an AC responsivity about 0.2 A/W and an average detector optical power of 500  $\mu$ W, the shot noise current density is calculated to be in the order of 6 pA/ $\sqrt{\text{Hz}}$ .

Thermal noise, also known as Johnson noise, is associated with the fluctuations of the thermal velocities of free charge carriers. The mean squared noise current is given by

$$\left\langle I_{\rm th}^2 \right\rangle = \frac{4kTBW}{R_{\rm co}} \tag{2.2}$$

where T is the absolute temperature of the device and  $R_{eq}$  is the equivalent resistance of the device. The high dynamic impedance of a MSM photodiode, which is commonly modeled with a gigaohm (G $\Omega$ ) resistor [43], diminishes the thermal noise term to an insignificant level. Based on a 100 M $\Omega$  equivalent resistance model, the thermal noise of a MSM diode is estimated at ~400 fA/ $\sqrt{Hz}$ .

The generation-recombination noise is due to the random fluctuations in the number of free charge carriers generated through traps. The processes of capture and of re-injection of charge carriers are accelerated with an increase in temperature and with the absorption of photons. Under illumination, the noise current spectral density due to recombination-generation process is given by [41]

$$\left\{i_{s-r}^{2}\right\} = \frac{4qI_{ph}|M(\omega)|^{2}}{M_{o}}$$

(2.3)

where  $I_{ph}$  is the average photocurrent,  $M_0$  is the DC photoconductive gain, and  $M(\omega)$  is the dynamic photoconductive gain. The dynamic photoconductive gain is expressed as

$$M(\omega) = \frac{t_n}{t_{max}} \circ \frac{1}{(1+jt_n\omega)} \tag{2.4}$$

and the DC photoconductive gain is expressed as

$$M_0 = \frac{t_n}{t_{max}} \tag{2.5}$$

so that Eq.(2.3) can be rewritten as

$$\left\{i_{e^{-r}}^{2}\right\} = \frac{4qI_{ph}M_{o}}{1+t^{2}\omega^{2}}$$

(2.6).

where  $t_n$  and  $t_{transit}$  are the mean life time and the transit time of the electron, respectively. Assuming that the bandwidth is low (BW<<1/th>

1/t<sub>n</sub>), the mean squared generation-recombination noise current can be written as

$$\left\langle i_{s-r}^{2}\right\rangle =4qI_{sh}M_{0}BW \tag{2.7}.$$

Under a low bias, the re-injection of charge carriers in a MSM photodiode is blocked by the double Schottky barrier and thus the photoconductive gain of a MSM diode approaches unity. The generation-recombination noise of an MSM approaches twice the photocurrent shot noise at low frequency ( $\omega <<1/t_n$ ).

Among the four noise contributions considered, the generation-recombination noise dominates the MSM photodiode array noise spectrum at the low frequency range ( $f < 2\pi/t_n$ ). The photocurrent shot noise dominates at a high frequency range. The magnitude of the detector noise is in the order of 8 pA/ $\sqrt{Hz}$  allowing a SNR of 50 dB with a 1GHz bandwidth assuming a 500 $\mu$ W incident optical power.

#### 2.1.2 Laser Diode

An optical source with a wavelength within the detector absorption spectrum is chosen to generate the optical carrier. The criteria for the optical source selection were studied thoroughly by M. Veilleux in his thesis [30]. He pointed out the requirements for the optical source are a high conversion efficiency to minimize the conversion loss, a high spatial coherence to maximize the coupling coefficient, and a high modulation bandwidth for broadband operation. A Mitsubishi ML6411C AlGaAs injection laser diode with a 50  $\mu$ m core multimode fiber pigtail was chosen for M. Veilleux's application. This laser diode has a nominal wavelength of 780 nm and a quantum efficiency of about 0.4 W/A with 20 mW peak power. The device was tested with a 2.0 GHz modulation bandwidth and has two optical emission peaks with an output power of 5 mW total.

A multimode fiber pigtail was chosen over a monomode fiber because of its potentially high coupling efficiency; however, the pigtailing process used by manufacturer has a 50% coupling loss. The external quantum efficiency of the 10 lasers after pigtailing is 0.2 W/A on average. In this project, ML6411C laser diodes were used for optical sources because of their compatibility with existing components.

## 2.1.2.1 Laser noise

The noise of a Fabry Perot laser diode originates from two sources: shot noise and relative intensity noise (RIN). The laser shot noise is caused by the junction current of the laser and the relative intensity noise is caused by the amplified spontaneous emission inside the gain medium [44]. The noise performance of the ML6411C is specified in terms of a dynamic range which includes the contributions of both laser shot and RIN

noises. The worst specified dynamic range values for ML6411C are 125 dB/Hz at 20kHz and 128 dB/Hz at 10 MHz [45]. These dynamic range values are functions of both optical power and optical feedback; these values are obtained under a strong radio frequency (RF) modulation  $(35\text{mA}_{\text{p-p}})$  with a low (<0.1%) optical feedback. In the proposed optical system, the laser is expected to be operating under a high modulation index to maximize the SNR performance and a 1x10 optical splitter serves as a 10 dB attenuator to attenuate the reflected light. The dynamic range of the laser is expected to be near the 125 - 128 dB/Hz range.

## 2.1.3 Optical Components

A Northern Telecom 50 µm core multimode optical fiber with a numerical aperture of 0.2 is used for the optical system because of its high coupling efficiency. The fiber loss at 850 nm wavelength is specified to be 2.4 dB/km. For the application proposed, the fiber length is expected to be few meters and thus the fiber loss is insignificant compared to other losses. The two major sources of insertion loss are optical splitters and optical connectors. The optical splitter is a 1x10 biconical-taper fiber splitter from Canstar Optics. From the manufacturer's data, the excess loss of the 1x10 multimode optical splitter is less than 3 dB for all 10 splitters [46]. Two types of optical connectors used for interconnecting components are fiber connector (PC) and physical contact fiber connector (PC/PC). The insertion losses for the fiber connectors are expected to be less than 0.5 dB/splice. The overall optical loss from the laser to the MSM photodiode is expected to be less than 15 dB.

#### 2.1.3.1 Optical Noise

When multimode fiber components are used, some other problems related to multimode propagation, such as modal dispersion and modal noise, must be considered. The modal dispersion limitation of multimode fiber (~500 MHz/km at 850nm) is insignificant because of the short fiber length of the proposed system. For a fiber length of few meters, the dispersion limited bandwidth is on the order of 100 GHz which is much greater than the electrical bandwidth.

Model noise, also known as speckle noise, is caused by the random interference of different modes which propagate at slightly different velocities. The model noise in this system arises primarily from the biconical splitter. If a mode selection process is present, when the distribution of power in the various modes changes, the power incident on the detector can change. The average power to variance ratio of a similar 1x8 biconical-taper splitter was reported at 28.5-33.0 dB with the input fiber under a constant vibration to

enhance the fluctuation level [47]. The modal noise is expected to be lower with no vibration. The SNR of the fiber system is expected to be about 30 dB.

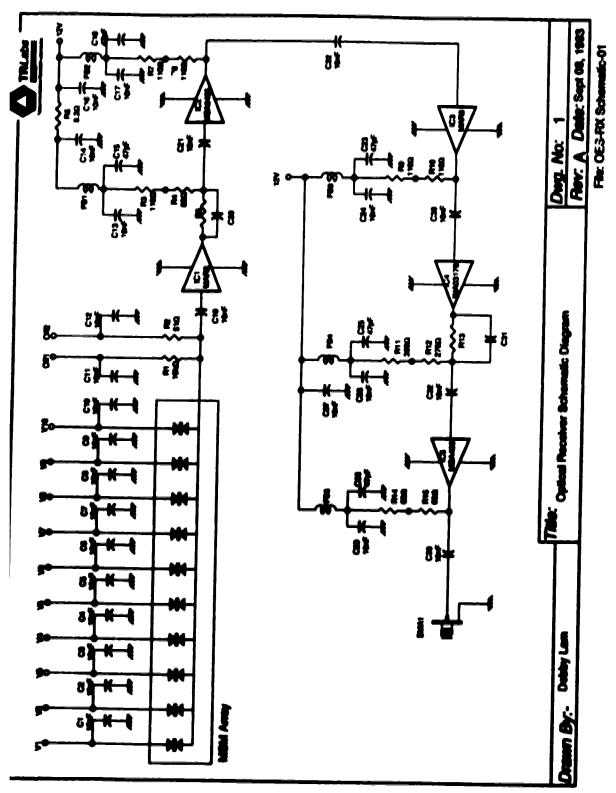

## 2.1.4 Receiver Amplifier

The required amplifier gain for compensating the total path loss from optoelectronic conversions and optical propagation losses is determined to be approximately 60 dB<sup>4</sup>. A low noise 50  $\Omega$  gain block amplifier design with a gain of approximately 60 dB was considered for this application. A prototype of the amplifier was built and measured to have a gain of 60 dB with an output noise floor range of -106 dBm/Hz and with a bandwidth of 1.5 GHz.

The dynamic range of the amplifier is determined by its maximum available output signal and its noise floor. The maximum output power of the receiver amplifier is limited by the maximum electrical input of the transmitter which corresponds to 10 dBm for a 100% modulation index. The maximum dynamic range of the receiver amplifier with the low noise  $50~\Omega$  amplifier design is estimated to be  $116~\mathrm{dB/Hz}$ .

## 2.1.5 Estimated System Performance

Based on the available components, the system parameters, such as the bandwidth, the dynamic range, and the isolation can be estimated. The dynamic range of the system is expected to be dominated by the amplifier thermal noise and is expected to be about 116 dB/Hz. The bandwidth of the system is limited by the receiver amplifier and is expected to be 1.5 GHz. The isolation of the crosspoints is determined by the MSM photodiode array which is expected to be about 40-50 dB over the 1.5 GHz bandwidth.

#### 2.2 Applications under Consideration

Based on the component performances described above, we can estimate the performance of the processor in different applications such as cascadable switch matrix and reconfigurable filter.

#### 2.2.1 Cascadable Switch Matrix

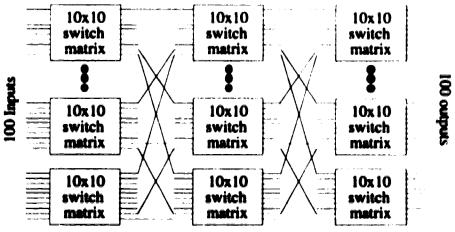

By cascading a number of switching matrices, one can realize a larger switching network with a smaller number of crosspoints than a single large matrix implementation. For example, a 3 level Clos network, shown in Figure 2.6, is one such non-blocking

<sup>&</sup>lt;sup>4</sup>see Appendix A for detailed calculations.

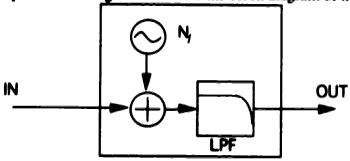

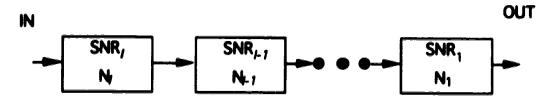

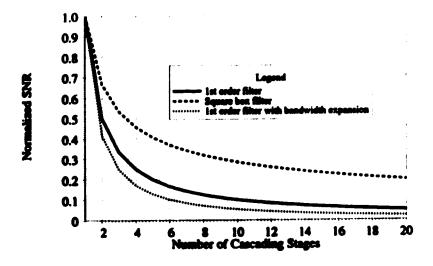

network. A direct 100x100 non-blocking switch matrix requires 10000 crosspoints; a 3 level Clos network can implement the same matrix with only 3000 cross points. The size of an optoelectronic switch matrix is limited by two factors: the cumulative capacitance of the detector array and the available optical power [36]. By subdividing large matrices into smaller matrices, one can reduce the cumulative capacitance on each detector array and the required optical power from each source and thus extend the size limit of a matrix [48]. However, this type of network requires multiple optoelectronic and electo-optic conversions through the switching matrices, and these multiple conversions can induce additional signal degradation from various sources, such as noise accumulation, bandwidth reduction, and crosspoint isolation.

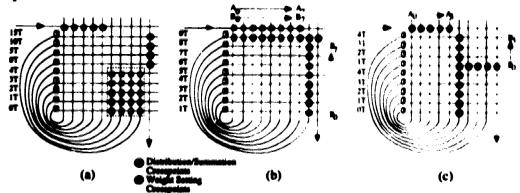

Figure 2.6 A 100x100 3 layer Clos network

In Appendix B, the effects of these impairments were studied. Based on a first order low pass model, the bandwidth of a multistage network decreases with a factor of

$$\frac{f_c}{\sqrt{N/2}-1}$$

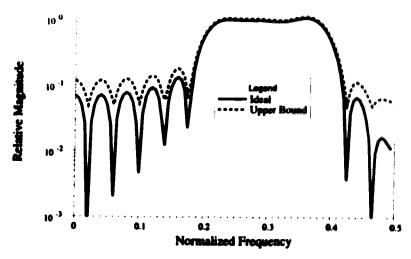

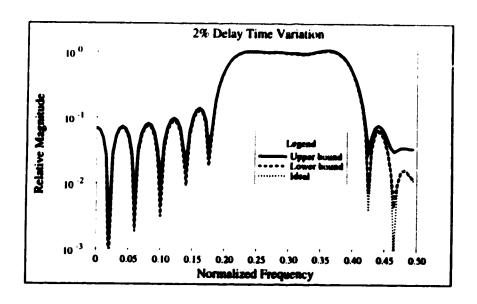

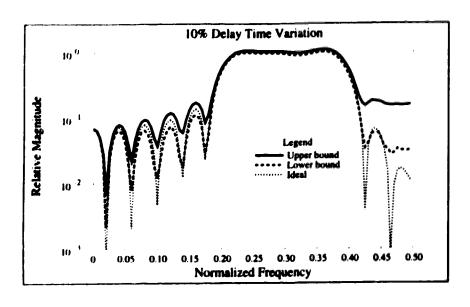

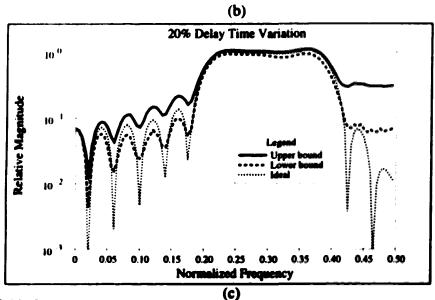

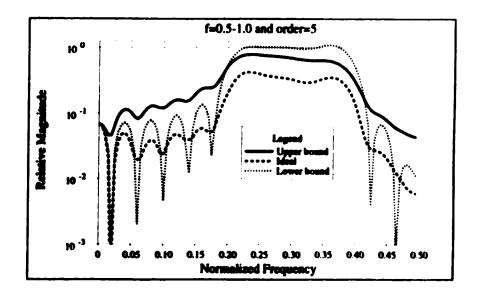

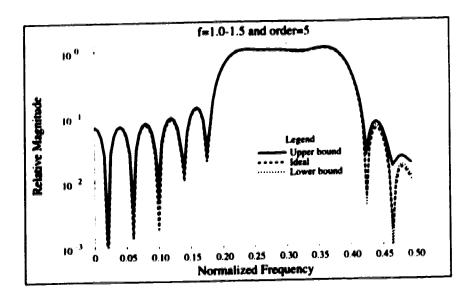

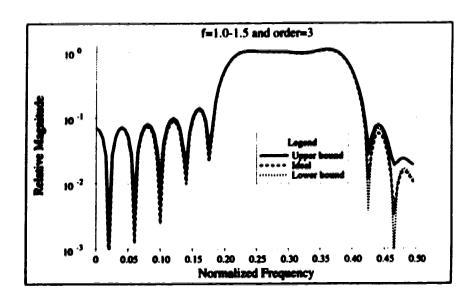

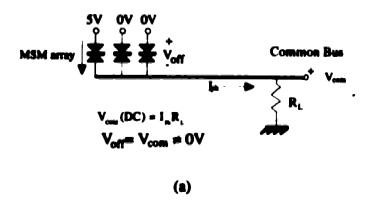

where N is the number of stages and  $f_c$  is the 3 dB frequency of each