#### **University of Alberta**

#### AREA AND POWER EFFICIENT ECHO CANCELLATION FOR HIGH-SPEED WIRE-LINE SYSTEMS

by

Saraswathi Sachidananda

$\bigcirc$

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of **Master of Science**.

Department of Electrical and Computer Engineering

Edmonton, Alberta Fall 2004

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

Library and Archives Canada

Published Heritage Branch

Patrimoine de l'édition

395 Wellington Street Ottawa ON K1A 0N4 Canada 395, rue Wellington Ottawa ON K1A 0N4 Canada

Bibliothèque et

Direction du

Archives Canada

Your file Votre référence ISBN: 0-612-95844-2 Our file Notre référence ISBN: 0-612-95844-2

The author has granted a nonexclusive license allowing the Library and Archives Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque et Archives Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou aturement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this thesis.

While these forms may be included in the document page count, their removal does not represent any loss of content from the thesis. Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de cette thèse.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

Dedicated to, My family

### Acknowledgements

I would like to sincerely thank all the people who made this thesis possible.

My utmost regards to my Supervisor, Dr. Stephen Bates for his valuable guidance, patient assistance and constant encouragement. I would like to thank my colleagues Pranavi Anand and Ram Swamy for their useful feedback and suggestions. I also express my gratitude to Amir Alimohammad and Kamlesh Raiter who helped me get familiar with some of the CAD tools. I am indebted to the Department of Electrical and Computer Engineering, University of Alberta for having provided me with Research and Teaching assistantships.

Lastly, I would like to extend my gratefulness to my family and friends for all their support and encouragement.

## **Table of Contents**

| 1 | Intr | oduction  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1  |

|---|------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 1.1  | Gigabit   | t Ethernet systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1  |

|   |      | 1.1.1     | Ethernet to Gigabit Ethernet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1  |

|   |      | 1.1.2     | Benefits of Gigabit Ethernet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2  |

|   |      | 1.1.3     | Achieving 1000 Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2  |

|   |      | 1.1.4     | Modulation scheme of 1000BASE-T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3  |

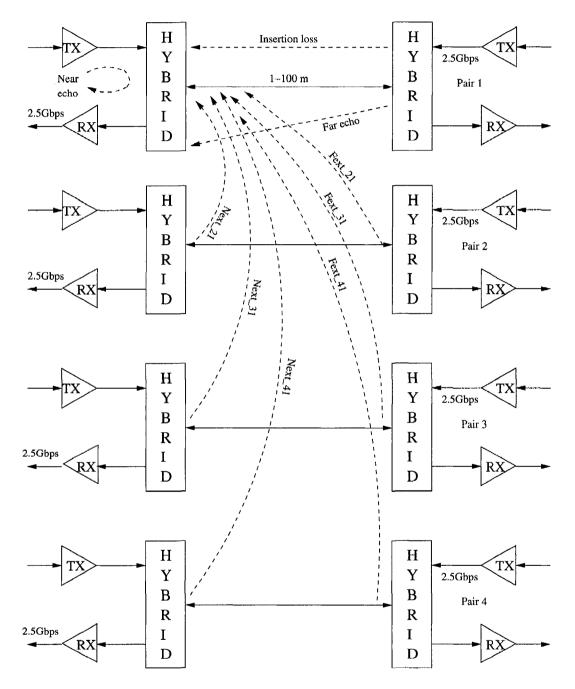

|   | 1.2  | Channe    | el impairments in the Gigabit Ethernet system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3  |

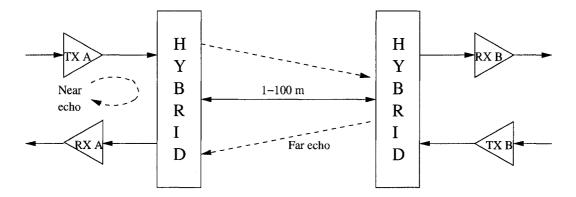

|   | 1.3  | The ech   | ho phenomenon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6  |

|   |      | 1.3.1     | Echo in the channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6  |

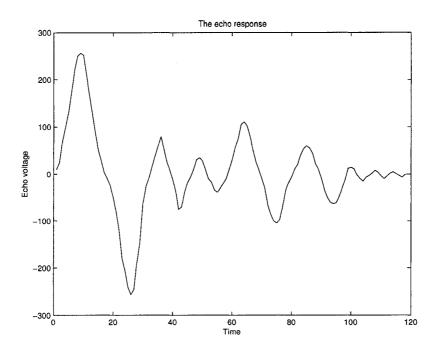

|   |      | 1.3.2     | The echo response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7  |

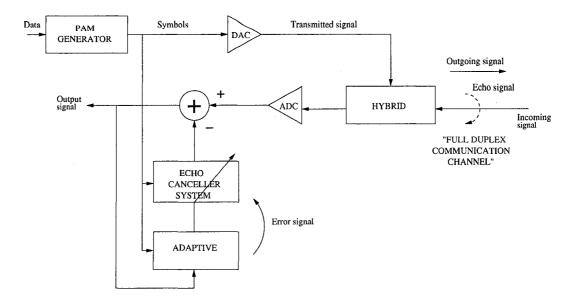

|   | 1.4  | Adaptiv   | ve echo cancellation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8  |

|   | 1.5  | Goals c   | of this thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10 |

| _ |      | _         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

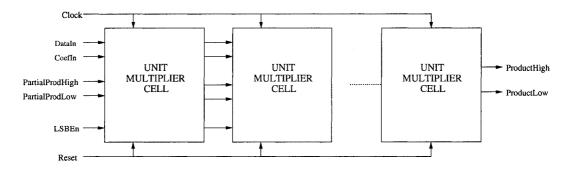

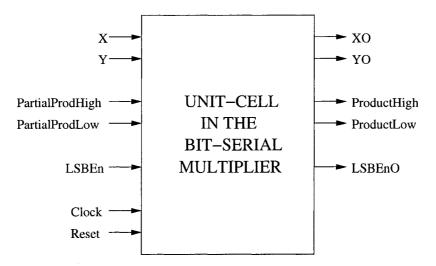

| 2 |      | hitectura |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11 |

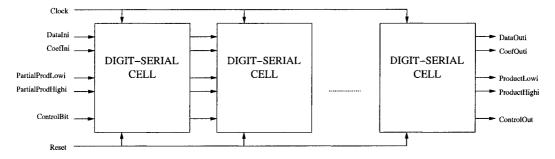

|   | 2.1  |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13 |

|   |      | 2.1.1     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13 |

|   |      | 2.1.2     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13 |

|   |      | 2.1.3     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16 |

|   |      | 2.1.4     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16 |

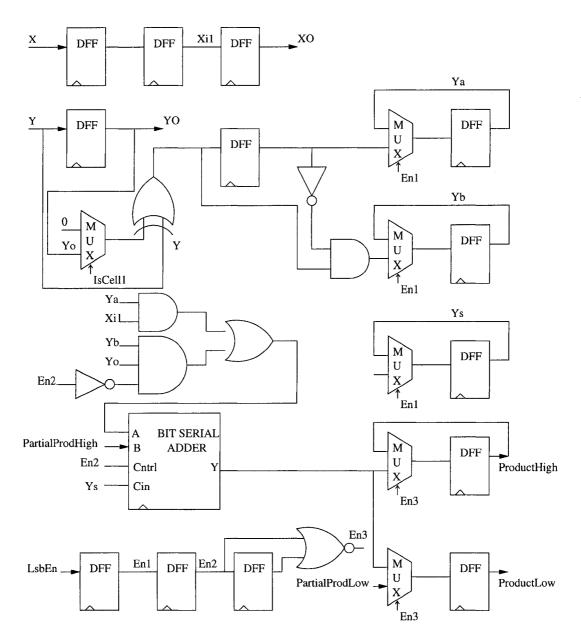

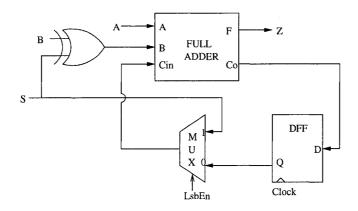

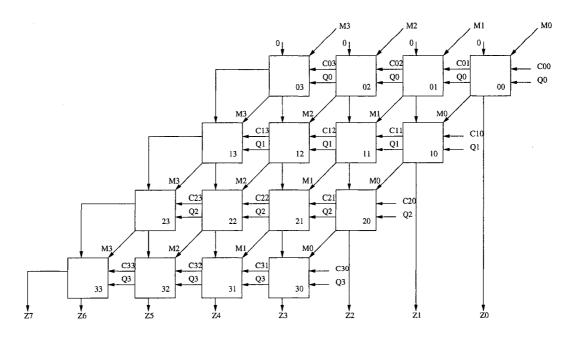

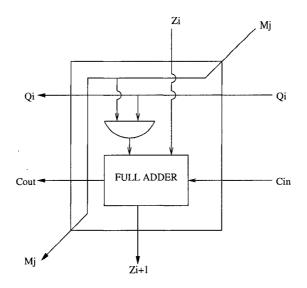

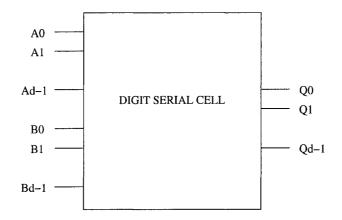

|   |      | 2.1.5     | Operation of the unit-cell in the Modified Booth bit-serial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|   |      |           | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20 |

|   |      | 2.1.6     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22 |

|   |      | 2.1.7     | Let the second s | 23 |

|   | 2.2  | Bit-para  | allel multiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23 |

|   |      | 2.2.1     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 23 |

|   |      | 2.2.2     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26 |

|   | 2.3  | FPGA i    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26 |

|   |      | 2.3.1     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26 |

|   |      | 2.3.2     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 27 |

|   | 2.4  | ASIC in   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28 |

|   |      | 2.4.1     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28 |

|   |      | 2.4.2     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29 |

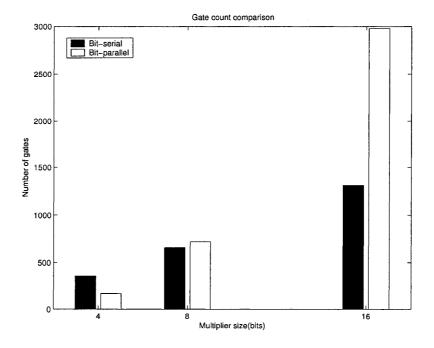

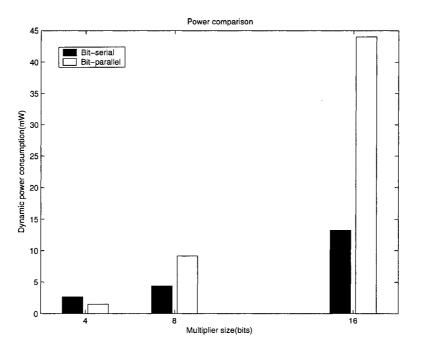

|   |      | 2.4.3     | Performance comparion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 30 |

|   | 2.5  | Conclusion                                                  | 32 |

|---|------|-------------------------------------------------------------|----|

| 3 | Desi | ign of the echo cancellation unit                           | 34 |

|   | 3.1  | Echo canceller system                                       | 35 |

|   |      | 3.1.1 The adaptive filter                                   | 35 |

|   |      | 3.1.2 Architecture mode of the filter                       | 35 |

|   |      | 3.1.3 Design goals                                          | 35 |

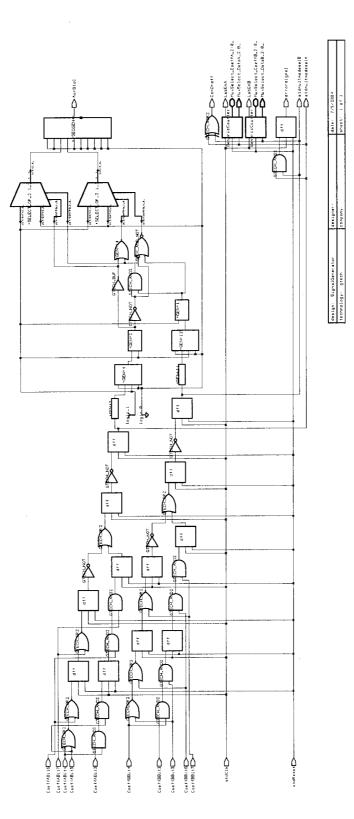

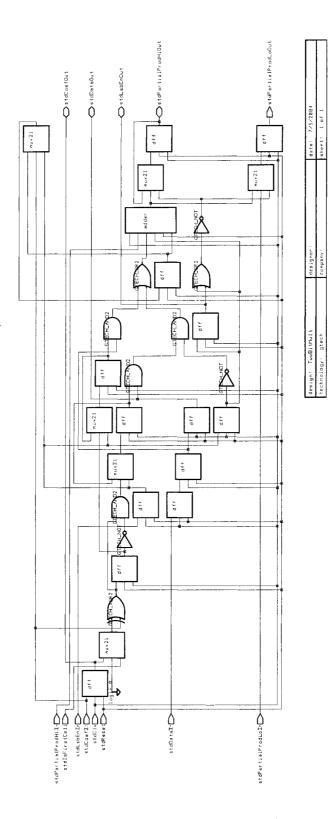

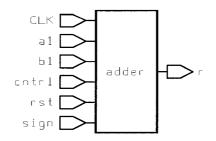

|   | 3.2  | Design of the bit-serial adaptive filter                    | 36 |

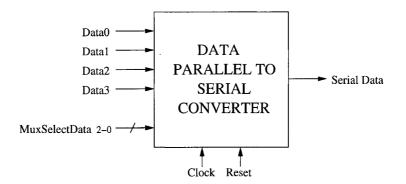

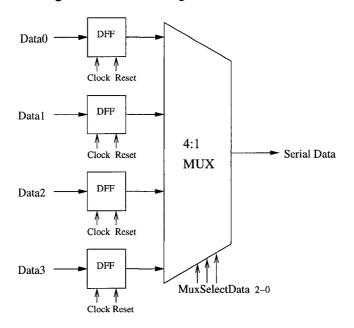

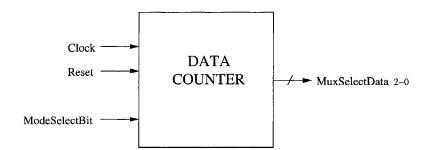

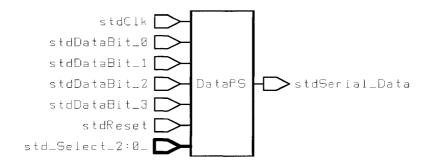

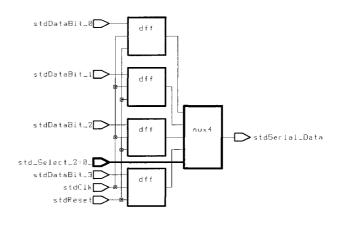

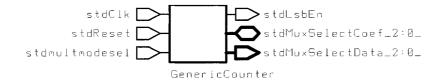

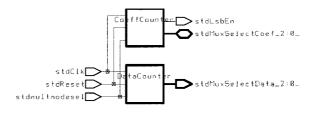

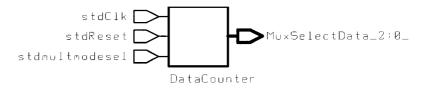

|   |      | 3.2.1 Parallel-to-serial converter for the data term        | 40 |

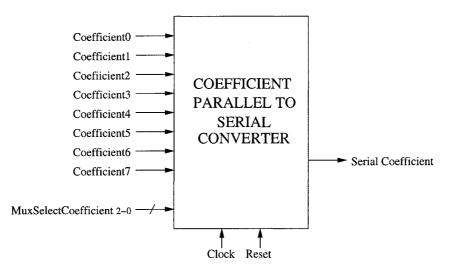

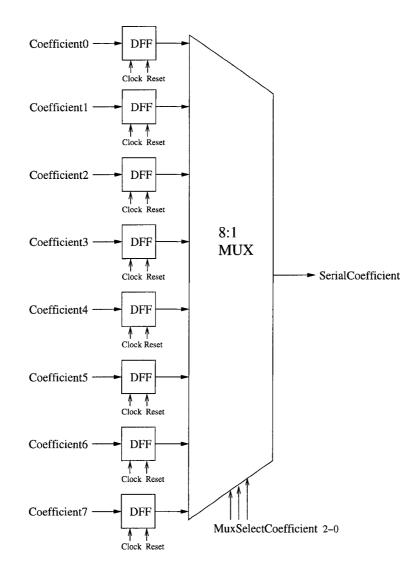

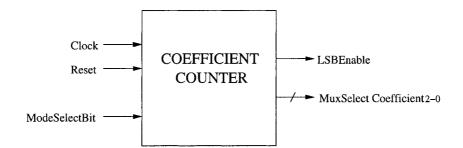

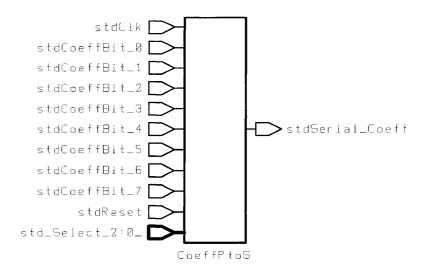

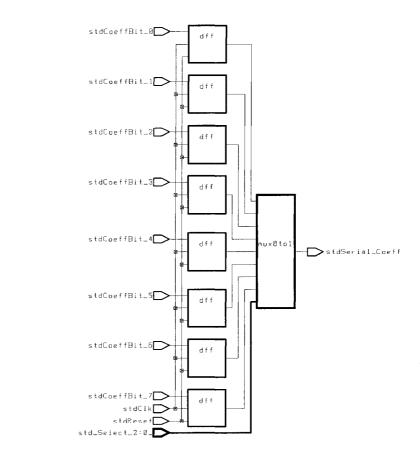

|   |      | 3.2.2 Parallel-to-serial converter for the coefficient term | 41 |

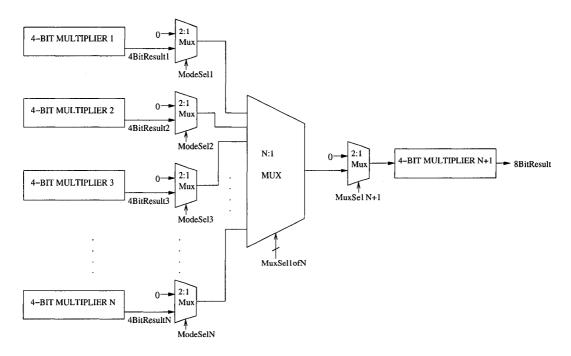

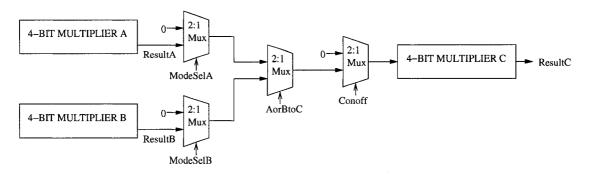

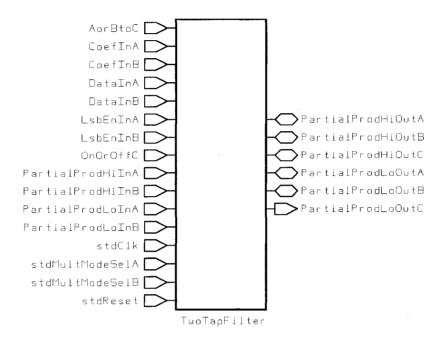

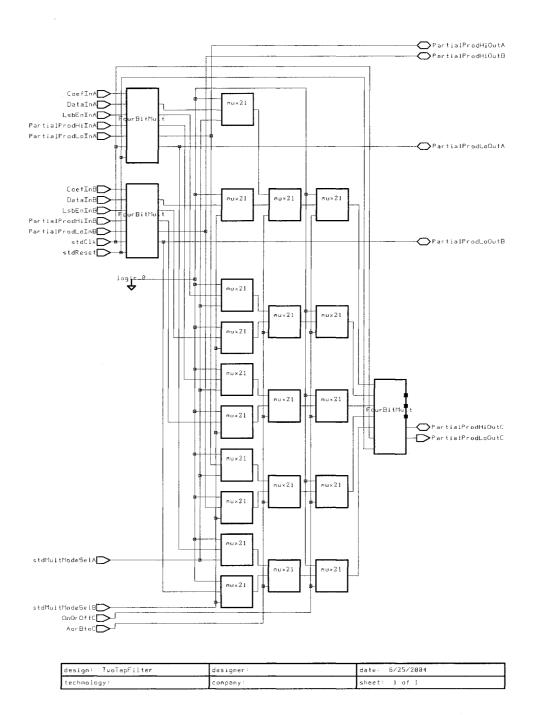

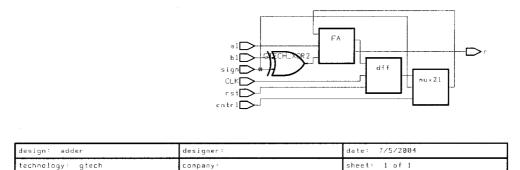

|   |      | 3.2.3 Filter component                                      | 42 |

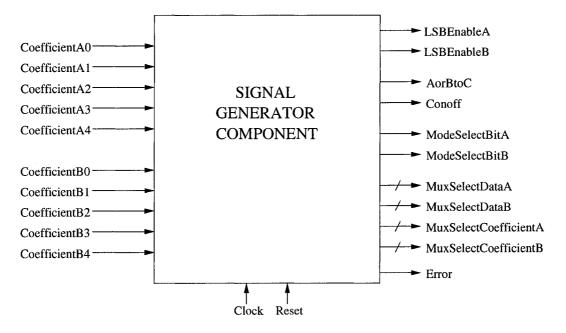

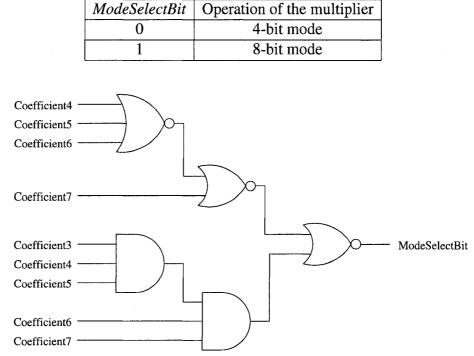

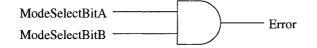

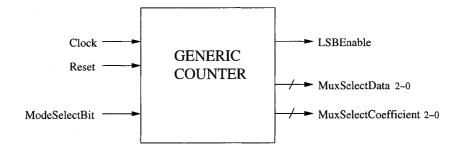

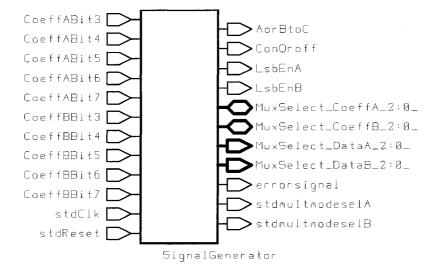

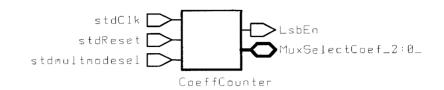

|   |      | 3.2.4 Signal generator component                            | 48 |

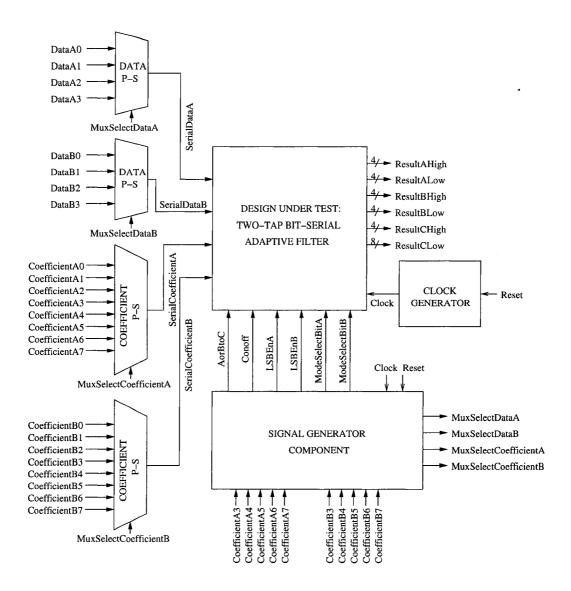

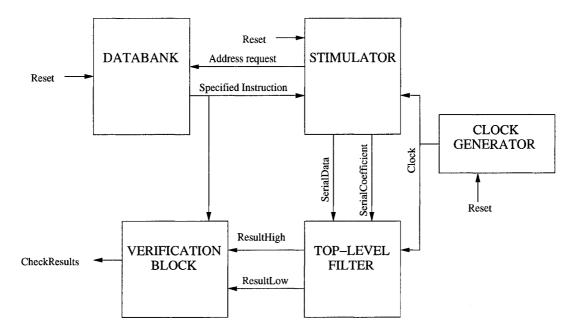

|   | 3.3  | Testing the design                                          | 54 |

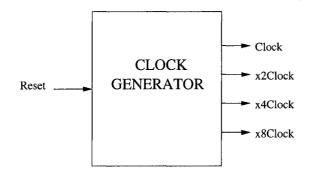

|   |      | 3.3.1 Clock generator                                       | 56 |

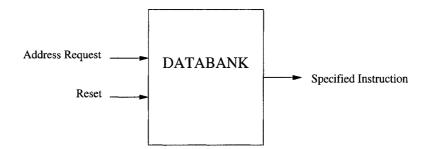

|   |      | 3.3.2 Databank                                              | 56 |

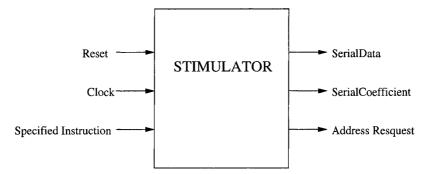

|   |      | 3.3.3 Stimulator                                            | 56 |

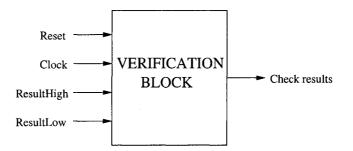

|   |      | 3.3.4 Verification block                                    | 57 |

|   |      | 3.3.5 Package                                               | 58 |

|   |      | 3.3.6 Use of <i>Matlab</i>                                  | 58 |

|   | 3.4  | Conclusion                                                  | 59 |

| 4 | FPG  | A implementation of the bit-serial adaptive filter          | 60 |

| • | 4.1  | Introduction to logic design                                | 61 |

|   |      | 4.1.1 Top-down design process                               | 61 |

|   |      | 4.1.2 The hierarchical approach                             | 61 |

|   |      | 4.1.3 Computer aided design                                 | 61 |

|   | 4.2  | Hardware description languages                              | 61 |

|   | 4.3  | Introduction to FPGA devices                                | 63 |

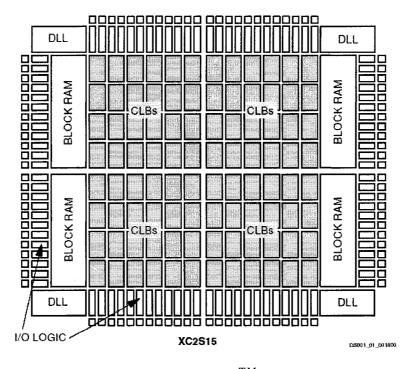

|   |      | 4.3.1 Introduction to the <i>Spartan</i> FPGA device family | 63 |

|   | 4.4  | FPGA implementation of the bit-serial filter                | 65 |

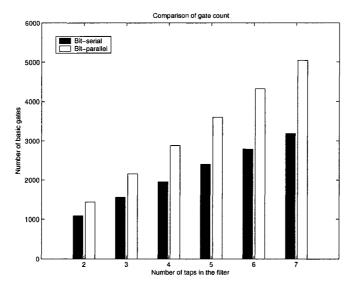

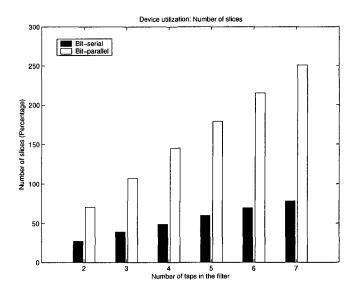

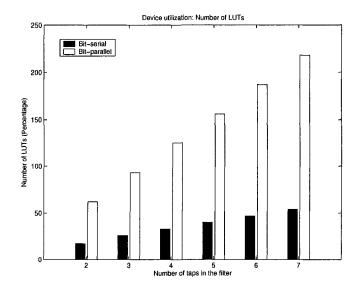

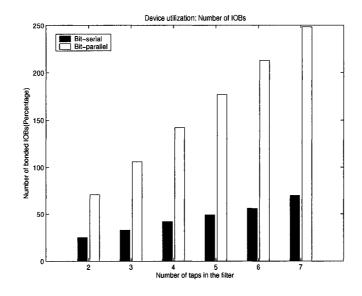

|   | 4.5  | Performance comparison of the serial and parallel filters   | 65 |

|   | 4.6  | Conclusion                                                  | 69 |

| 5 | Mar  | oping the filter to an ASIC                                 | 70 |

| 5 | 5.1  |                                                             | 71 |

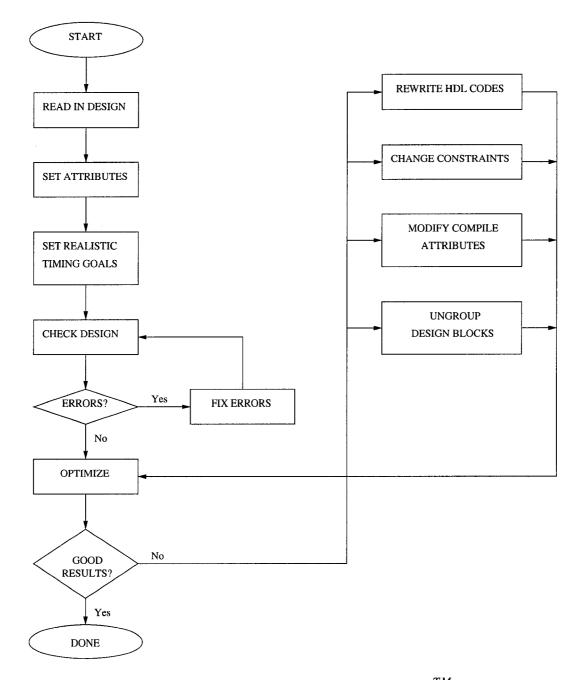

|   | 5.2  | The synthesis process                                       | 71 |

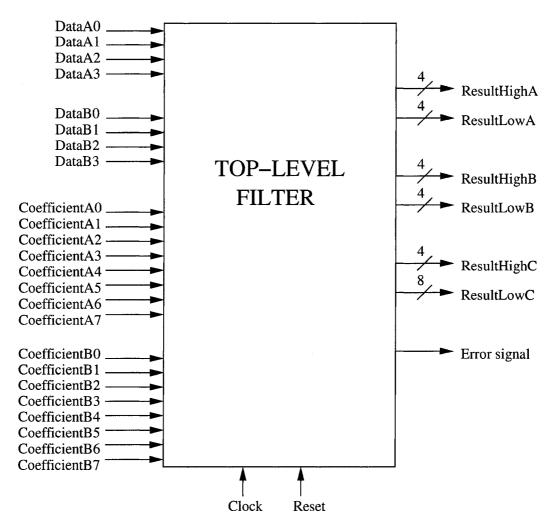

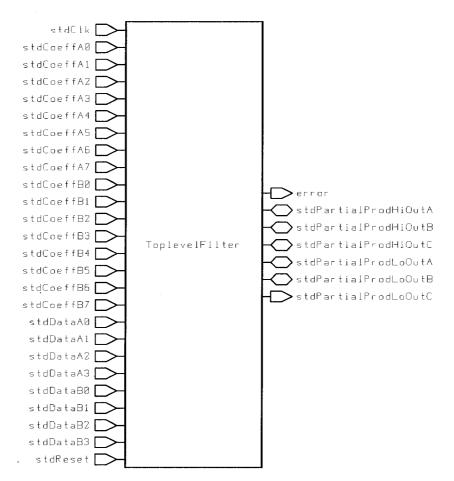

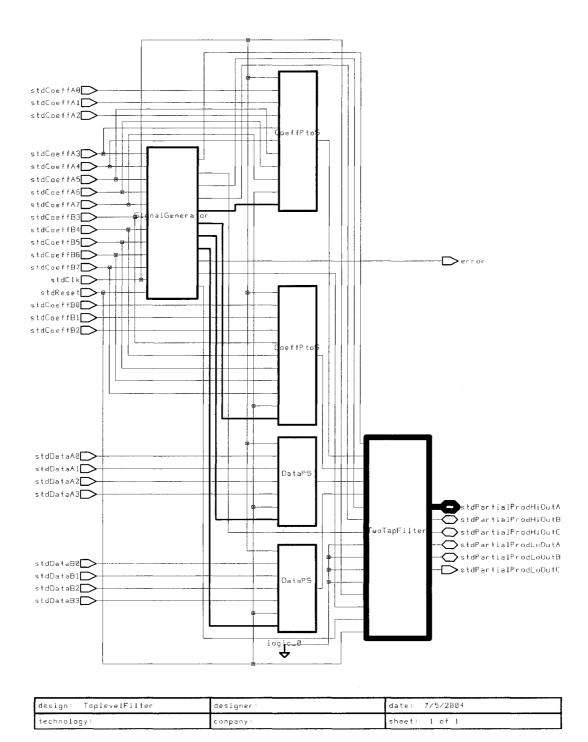

|   | 5.3  | Top-level filter                                            | 73 |

|   | 0,0  | 5.3.1 Critical path                                         | 74 |

|   |      | 5.3.2 Frequency of operation                                | 76 |

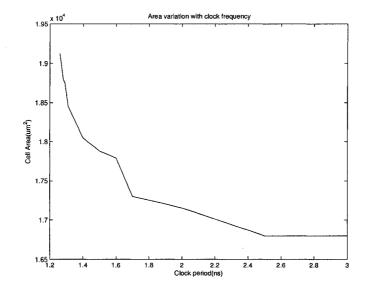

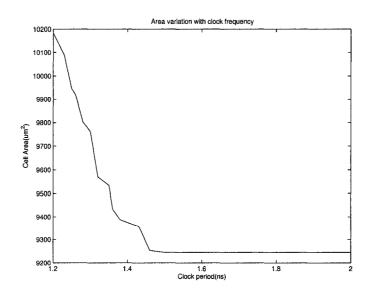

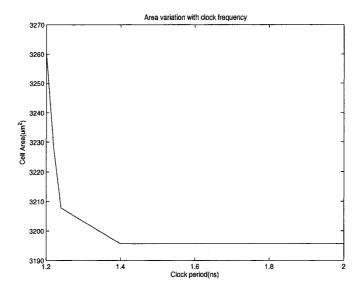

|   |      | 5.3.3 Area variation with frequency                         | 76 |

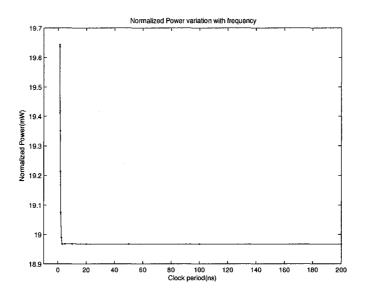

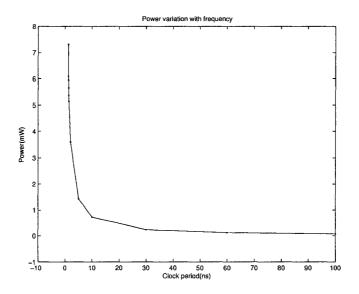

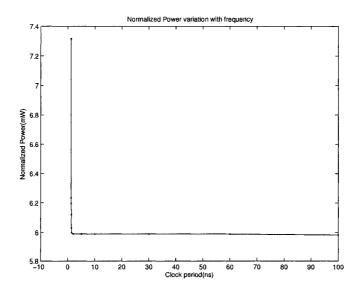

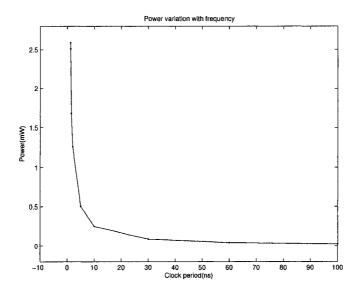

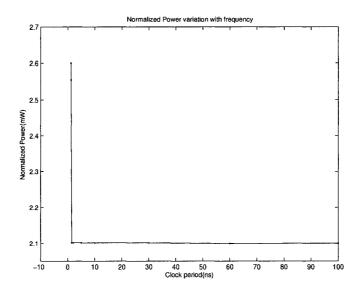

|   |      | 5.3.4 Power variation with frequency                        | 78 |

|   | 5.4  | Components of the top-level filter                          | 80 |

|   |      | 5.4.1 Parallel-to-serial converter for the data term        | 81 |

|   |      | 5.4.2 Parallel-to-serial converter for the coefficient term | 82 |

|   |      |                                                             |    |

|        |                                                                      | 5.4.3 Signal generator component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 84                                                       |

|--------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|        | 5.5                                                                  | Bit-serial adaptive filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 87                                                       |

|        |                                                                      | 5.5.1 Area variation with frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 90                                                       |

|        |                                                                      | 5.5.2 Power variation with frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 92                                                       |

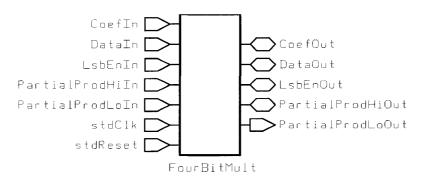

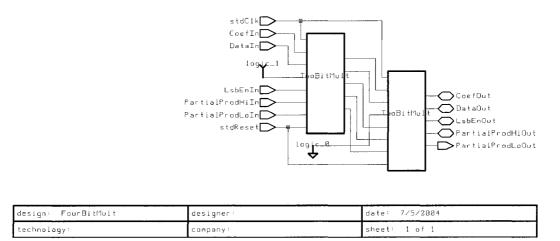

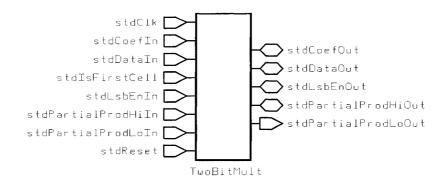

|        | 5.6                                                                  | Bit-serial multiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 94                                                       |