# University of Alberta

## Nanostructured Inductors for Millimetre-Wave Applications

by

# Aaron Gregory Seilis

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of

Master of Science

in

**Electromagnetics and Microwaves**

## Department of Electrical and Computer Engineering

©Aaron Gregory Seilis

### Fall 2013

#### Edmonton, Alberta

Permission is hereby granted to the University of Alberta Libraries to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly or scientific research purposes only. Where the thesis is converted to, or otherwise made available in digital form, the University of Alberta will advise potential users of the thesis of these terms.

The author reserves all other publication and other rights in association with the copyright in the thesis and, except as herein before provided, neither the thesis nor any substantial portion thereof may be printed or otherwise reproduced in any material form whatsoever without the author's prior written permission.

# Abstract

Modern integrated and system-on-chip electronics require high-quality on-chip passive components. Existing inductor designs for microwave and millimetre-wave applications are typically prohibitively large and have low quality factors, requiring circuit designers to avoid integrating them or to use less desirable alternatives. This research studied vertical on-chip inductor structures through electromagnetic simulations and measurements on two materials. Simulations demonstrated that magnetic anisotropic materials produce useful inductances and quality factors at microwave frequencies. Thin magnetic films deposited using glancing angle deposition were fabricated as inductors and measured up to 70 GHz, producing inductances as high as  $1 \text{ nH}/\mu\text{m}^2$ , which is significantly higher than other CMOS compatible technologies reported to date. The highest quality factor measured for the films was 3, with the measurements suggesting that the quality factor continues to increase at higher frequencies. Carbon nanotube inductors were also fabricated and measured, however, the contact resistance was found to be prohibitively high.

# **Table of Contents**

| Chapter 1: Introduction to Inductors at GHz Frequencies     | . 7 |

|-------------------------------------------------------------|-----|

| 1.1 Inductors and Circuits                                  | . 1 |

| 1.1.1 Introduction                                          | . 1 |

| 1.1.2 Ubiquitous computing and advanced communications      | . 1 |

| 1.1.3 What are inductors                                    | . 2 |

| 1.2 A brief overview of the proposed inductor technologies  | . 3 |

| Chapter 2: Inductance and Inductors                         | . 5 |

| 2.1 Introduction                                            | . 5 |

| 2.2 Inductance                                              | . 5 |

| 2.2.1 Introduction                                          | . 5 |

| 2.2.2 Maxwell's Equations                                   | . 5 |

| 2.2.3 Definition                                            | . 6 |

| 2.2.4 Inductance and energy                                 | . 7 |

| 2.2.5 Inductance in the frequency domain and Quality Factor | . 8 |

| 2.3 Magnetic materials                                      | 10  |

| 2.3.1 Magnetic polarization in response to an applied field | 10  |

| 2.3.2 Magnetism                                             | 11  |

| 2.4 Loop and Partial Inductance                             | 12  |

| 2.4.1 The inductance problem                                | 12  |

| 2.4.2 Partial inductance                                    | 12  |

| 2.4.3 Partial Inductance of a straight wire                 | 13  |

| 2.5 Existing Inductor Types                                 | 15  |

| 2.5.1 About                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| 2.5.2 Helical Coils                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                            |

| 2.5.3 Planar Inductors                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            |

| 2.5.4 Active Inductors                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            |

| 2.5.5 MEMS Inductors                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                            |

| 2.6 New materials for inductors                                                                                                                                                                                                                                                                                                                                                                                              |                                                                            |

| 2.6.1 Nanotechnology and inductors                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            |

| 2.6.2 Nanostructured thin films                                                                                                                                                                                                                                                                                                                                                                                              |                                                                            |

| 2.6.3 Carbon nanotubes                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            |

| Chapter 3: Nanostructured thin films as inductors                                                                                                                                                                                                                                                                                                                                                                            |                                                                            |

| 3.1 Nano-scale structures                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                            |

| 3.1.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            |

| 3.1.2 Nano-scale wires and helices                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            |

| 3.1.3 Simulation methodology                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                            |

| 3.1.4 Devices studied                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

| 3.1.4 Devices studied         3.2 Single Helix                                                                                                                                                                                                                                                                                                                                                                               |                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                            |

| 3.2 Single Helix                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                            |

| <ul><li>3.2 Single Helix</li><li>3.2.1 Helices as inductors</li></ul>                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

| <ul><li>3.2 Single Helix</li></ul>                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            |

| <ul> <li>3.2 Single Helix</li> <li>3.2.1 Helices as inductors</li> <li>3.2.2 Single helix electromagnetic simulations</li> <li>3.2.3 Inductor material effects</li> </ul>                                                                                                                                                                                                                                                    | 31<br>31<br>32<br>33<br>33<br>37                                           |

| <ul> <li>3.2 Single Helix</li></ul>                                                                                                                                                                                                                                                                                                                                                                                          | 31<br>31<br>32<br>33<br>33<br>37<br>41                                     |

| <ul> <li>3.2 Single Helix</li></ul>                                                                                                                                                                                                                                                                                                                                                                                          |                                                                            |

| <ul> <li>3.2 Single Helix</li></ul>                                                                                                                                                                                                                                                                                                                                                                                          | 31<br>31<br>32<br>33<br>33<br>37<br>41<br>41<br>41<br>43                   |

| <ul> <li>3.2 Single Helix</li> <li>3.2.1 Helices as inductors</li> <li>3.2.2 Single helix electromagnetic simulations</li> <li>3.2.3 Inductor material effects</li> <li>3.2.4 Comparison of helix structures</li> <li>3.3 Surrounding Medium</li> <li>3.3.1 Single helix in an effective medium</li> <li>3.3.2 Ideal magnetic material</li> </ul>                                                                            | 31<br>31<br>32<br>33<br>33<br>37<br>41<br>41<br>41<br>43<br>43             |

| <ul> <li>3.2 Single Helix</li> <li>3.2.1 Helices as inductors</li> <li>3.2.2 Single helix electromagnetic simulations</li> <li>3.2.3 Inductor material effects</li> <li>3.2.4 Comparison of helix structures</li> <li>3.3 Surrounding Medium</li> <li>3.3.1 Single helix in an effective medium</li> <li>3.3.2 Ideal magnetic material</li> <li>3.3.3 Finite conductivity material</li> </ul>                                | 31<br>31<br>32<br>33<br>33<br>37<br>41<br>41<br>41<br>43<br>46<br>48       |

| <ul> <li>3.2 Single Helix</li> <li>3.2.1 Helices as inductors</li> <li>3.2.2 Single helix electromagnetic simulations</li> <li>3.2.3 Inductor material effects</li> <li>3.2.4 Comparison of helix structures</li> <li>3.3 Surrounding Medium</li> <li>3.3.1 Single helix in an effective medium</li> <li>3.3.2 Ideal magnetic material</li> <li>3.3.3 Finite conductivity material</li> <li>3.4 Anisotropic Media</li> </ul> | 31<br>31<br>32<br>33<br>33<br>37<br>41<br>41<br>43<br>43<br>46<br>48<br>48 |

| 3.5.1 Scaling behaviour of nano inductor films                       | 52 |

|----------------------------------------------------------------------|----|

| 3.5.2 Fabrication defects in helix arrays                            | 59 |

| 3.6 Summary                                                          | 63 |

| 3.6.1 Nanostructured materials as inductors                          | 63 |

| Chapter 4: Magnetic Thin Film Inductors by Glancing Angle Deposition | 65 |

| 4.1 Introduction to GLAD Films                                       | 65 |

| 4.1.1 Introduction                                                   | 65 |

| 4.1.2 Glancing angle deposition                                      | 65 |

| 4.1.3 Fabrication                                                    | 66 |

| 4.2 Measurement techniques                                           | 67 |

| 4.2.1 Direct probing                                                 | 67 |

| 4.2.2 Anisotropic Conductivity                                       | 68 |

| 4.2.3 Capping technique                                              | 69 |

| 4.2.4 Destructive testing technique                                  | 71 |

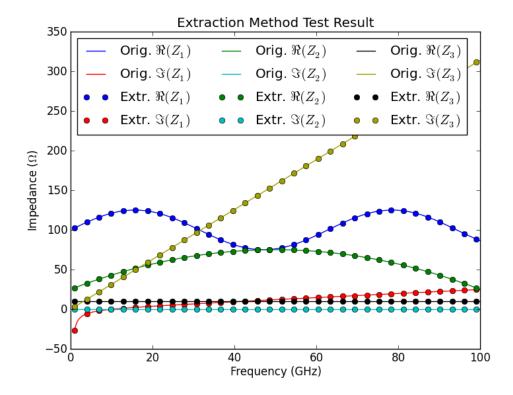

| 4.2.5 Film inductance extraction                                     | 73 |

| 4.2.6 Extraction of capping layer                                    | 73 |

| 4.2.7 HFSS simulation of test structure                              | 75 |

| 4.3 Extracted Results                                                | 76 |

| 4.3.1 Film simulation                                                | 76 |

| 4.4 Measured Power                                                   | 78 |

| 4.4.1 Measured Power                                                 | 78 |

| Chapter 5: Thin Film Inductors Utilizing Carbon Nanotubes            | 80 |

| 5.1 Introduction to Carbon Nanotubes                                 | 80 |

| 5.1.1 Introduction                                                   | 80 |

| 5.1.2 What are carbon nanotubes?                                     | 80 |

| 5.1.3 Quantum effects                                                | 80 |

| 5.1.4 Single walled carbon nanotube transmission line simulation     | 82 |

| 5.1.5 Planar inductors composed of carbon nanotubes                  | 87 |

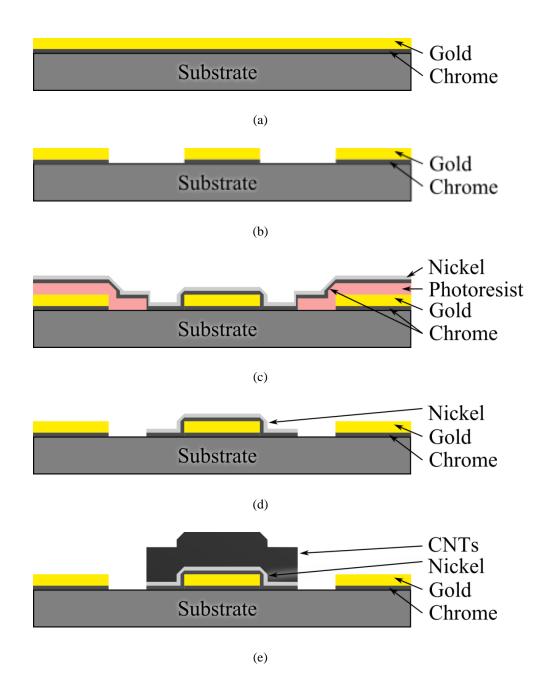

| 5.1.6 Fab      | rication of carbon nanotubes                    | 87  |

|----------------|-------------------------------------------------|-----|

| 5.2 Carbon 1   | nanotubes as inductors                          | 87  |

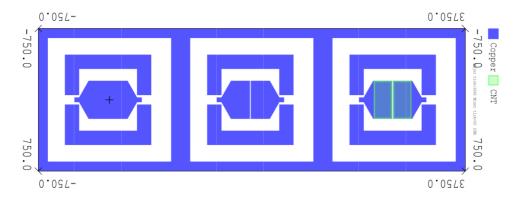

| 5.2.1 Test     | ting technique                                  | 87  |

| 5.2.2 Test     | t substrate design                              | 88  |

| 5.2.3 Test     | t Results                                       | 88  |

| 5.3 Summar     | у                                               |     |

| 5.3.1 Qua      | ntum Materials                                  |     |

| 5.3.2 Mea      | asurement Results                               |     |

| Chapter 6: Cor | nclusion                                        |     |

| 6.1 Thin film  | ns as Inductors                                 |     |

| 6.1.1 Sum      | ımary                                           |     |

| 6.2 Future W   | Vork                                            |     |

| 6.2.1 Nan      | ostructured thin films                          |     |

| 6.2.2 Carl     | bon nanotubes                                   |     |

| Appendix A     | : Carbon Nanotube Substrate Fabrication Process |     |

| Appendix B     | : Definition of a Helix                         | 101 |

| Appendix C     | : HFSS Simulation Details                       | 103 |

| Appendix D     | : Microwave.py                                  |     |

| References     |                                                 | 106 |

# **List of Tables**

| Table 1: Comparison of performance of existing inductor devices.    | . 21 |

|---------------------------------------------------------------------|------|

| Table 3.1: Physical parameters for the helices shown in Figure 3.2. | . 29 |

# **List of Figures**

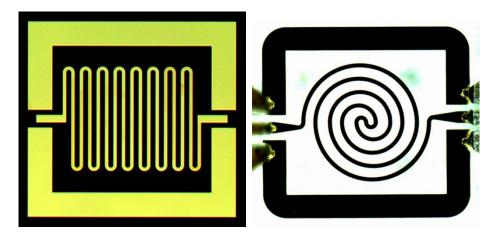

| Figure | 1.1: Planar inductors.   3                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -      | <ul><li>2.1: Inductor circuits. (a) Inductor model with a series resistance. Increasing the resistance in this model means that more power is lost in the resistor when compared to the inductor.</li><li>(b) Inductor model with a parallel resistance. Increasing the resistance means that more power is stored in the inductor when compared to the resistor</li></ul>                                         |

| Figure | 2.2: Self inductance of a single wire as a function of length. Multiple curves are shown which represent various wire widths as shown in equation 2.29                                                                                                                                                                                                                                                             |

|        | 2.3: Two-turn square-spiral planar inductor. Note that the inner turn is connected to the outer terminal by a set of vias and a wire on a second layer                                                                                                                                                                                                                                                             |

| Figure | 2.4: Two-turn meander inductor                                                                                                                                                                                                                                                                                                                                                                                     |

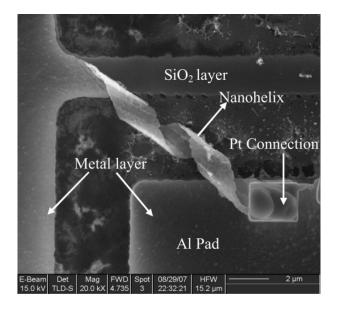

| -      | 2.5: Stressed thin-film inductor © 2008 IEEE, reproduced from [37]. The original figure text: SEM image of a suspended two-turn nanohelix aluminum inductor fabricated using FIB-SIT. The inductor with an air-core is 2 $\mu$ m higher [sic] above [the] silicon substrate and is isolated from the substrate through a silicon dioxide layer between the metal layer and the substrate. 21                       |

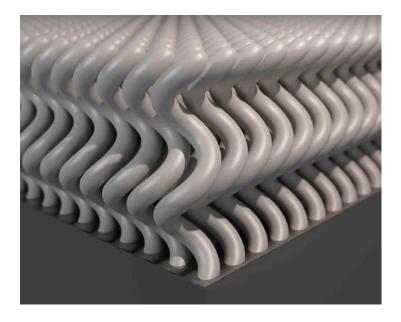

| Figure | 2.6: Conceptual diagram of the cross section of a helical GLAD film                                                                                                                                                                                                                                                                                                                                                |

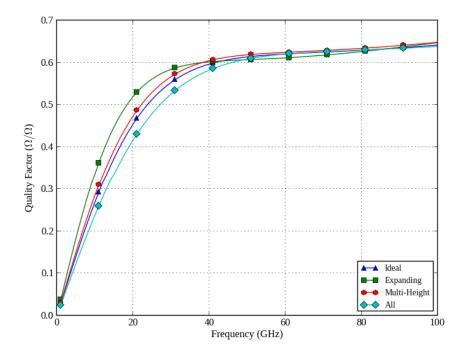

| Figure | 2.7: Set-up to perform glancing angle deposition with a sputtering system                                                                                                                                                                                                                                                                                                                                          |

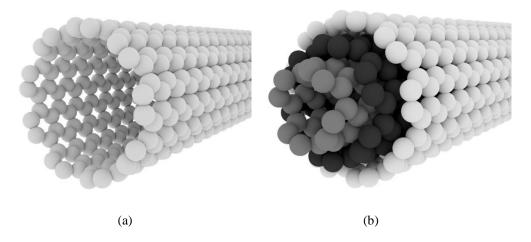

| -      | 2.8: The structure of a carbon nanotube (ends not shown). On the left (a) is a single-wall carbon nanotube that consists of a single tube of carbon atoms. On the right (b) is a multi-wall carbon nanotube which consists of concentric rings of carbon atoms. The spheres in the multi-wall carbon nanotube are all carbon and are shaded to show how each tube is positioned in relation to the other tubes. 25 |

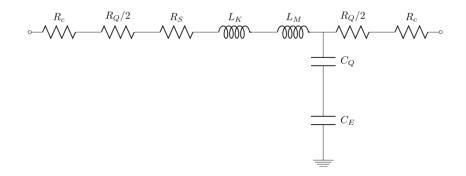

| -      | 2.9: Circuit model for a short, single-wall carbon nanotube [59]. $Rc$ is the contact resistance, $RQ$ is the quantum resistance, $RS$ is the scattering (ohmic-like) resistance, $LK$ is the kinetic inductance, $LM$ is the magnetic inductance, $CQ$ is the quantum capacitance, and $CE$ is the electrostatic capacitance of a CNT to ground                                                                   |

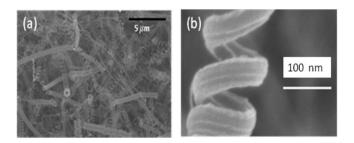

|        | 3.1: Image © IEEE 2010, reproduced from [69]. Original image caption: (a) SEM image for coiled CNWs [sic] with a (b) more detailed view. No preferred alignment was observed.                                                                                                                                                                                                                                      |

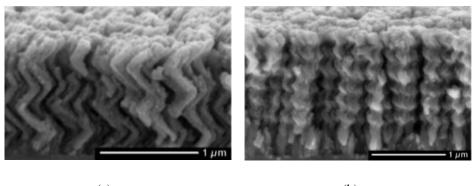

| •      | 3.2: Nano-scale helix structures fabricated using physical vapour deposition from [68]. Both (a) and (b) were modeled as part of this work. In this work, (a) is called a wide helix and (b) is called a narrow helix                                                                                                                                                                                              |

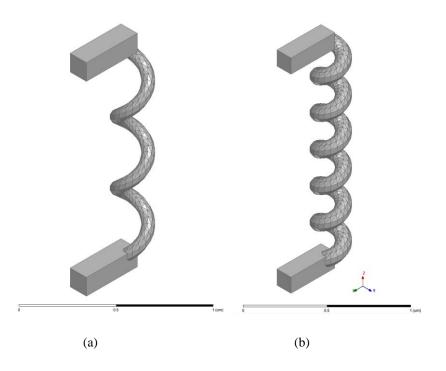

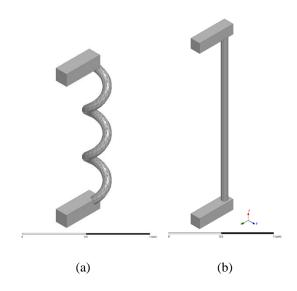

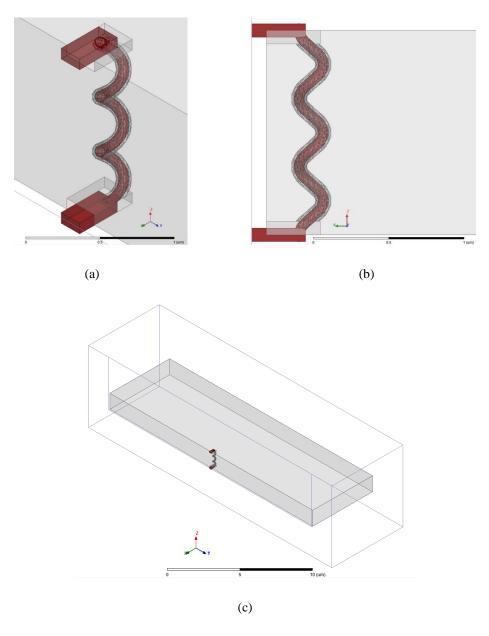

| C      | 3.3: Models of single helices in free space. (a) Model of an individual element from the film shown in Figure 3.2a. (b) Model of an individual element from the film shown in Figure 3.2b                                                                                                                                                                                                                          |

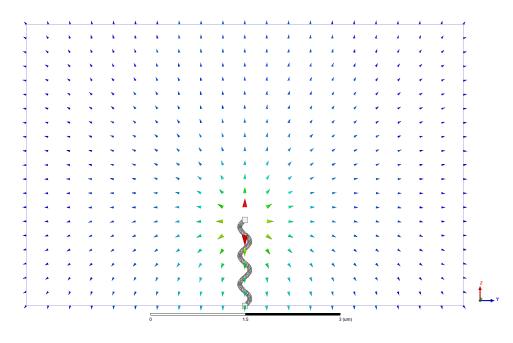

|        | 3.4: Wave port excitation in relation to the inductor model. The colored arrows show the electric field solution in the wave port plane                                                                                                                                                                                                                                                                            |

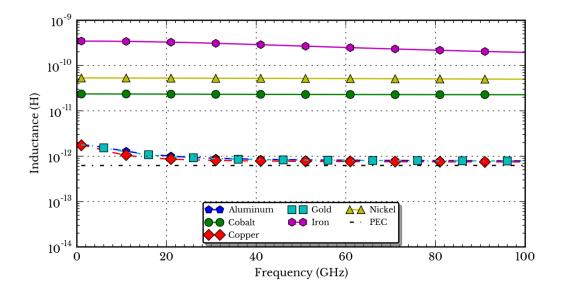

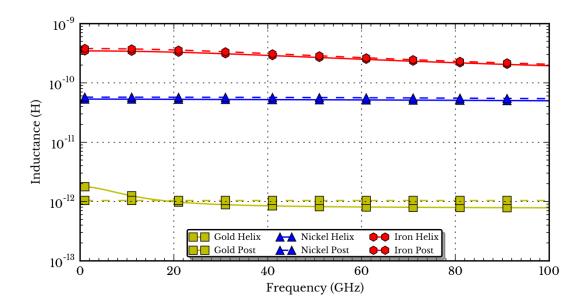

| Figure 3.5: Inductance of the single wire shown in Figure 3.3 in free space                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

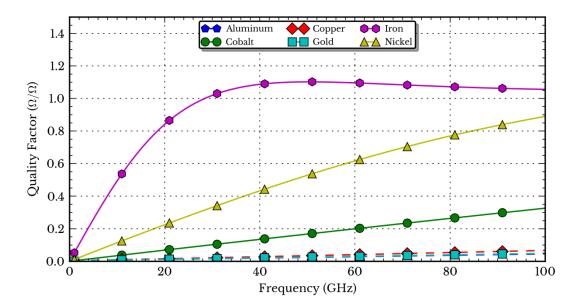

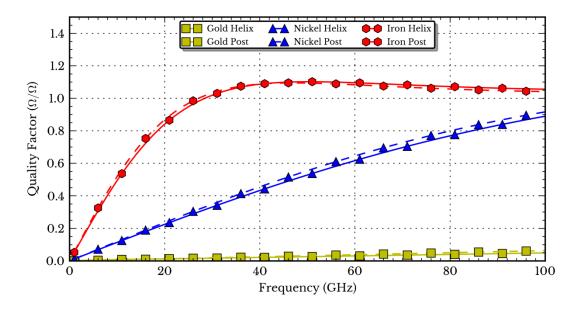

| Figure 3.6: Quality factor of a single wire shown in Figure 3.3 in free space                                                                                                                               |

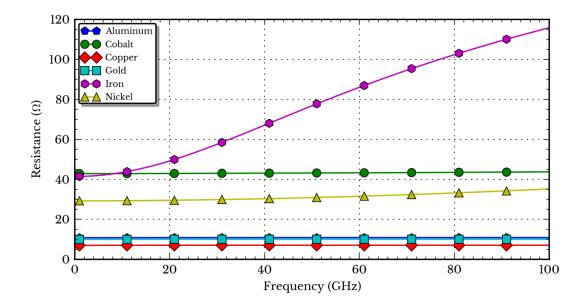

| Figure 3.7: Resistance of a single wire shown in Figure 3.3 in free space                                                                                                                                   |

| Figure 3.8: (a) Helix model shown in Figure 3.3a next to (b) its post inductor of equivalent length and wire width                                                                                          |

| Figure 3.9: Comparison of the inductance of the wide helix and the equivalent linear wire                                                                                                                   |

| Figure 3.10: Comparison of the quality factor of the wide helix and the equivalent wire                                                                                                                     |

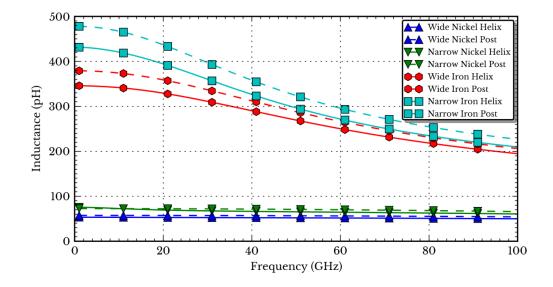

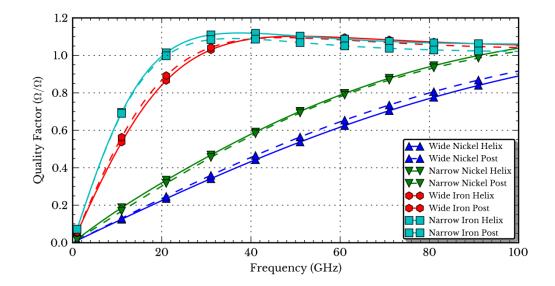

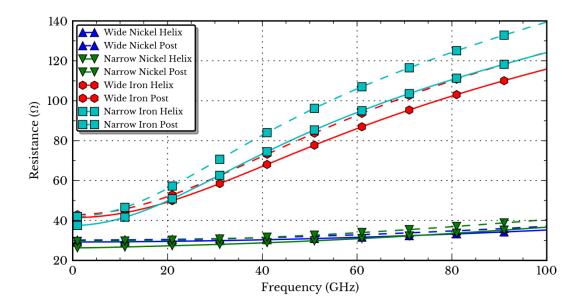

| Figure 3.11: Comparison of the inductance of the wide and narrow helix made of iron and nickel.<br>Also shown are the inductances of the equivalent post inductors for both the narrow and wide helix       |

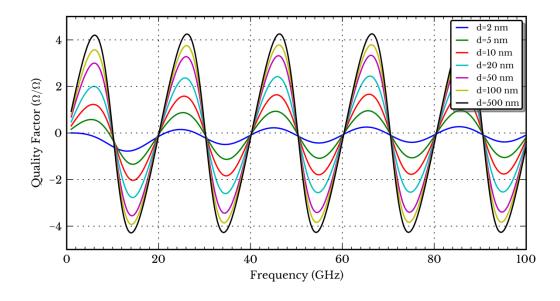

| Figure 3.12: Comparison of the quality factor of wide and narrow helices made of iron and nickel.<br>Also shown are the quality factors of the equivalent post inductors for both the narrow and wide helix |

| Figure 3.13: Comparison of the resistance of wide and narrow helices and the equivelent length of a straight wire                                                                                           |

| Figure 3.14: Model of a single inductor embedded in an effective medium                                                                                                                                     |

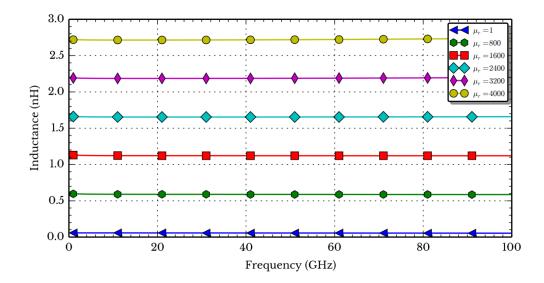

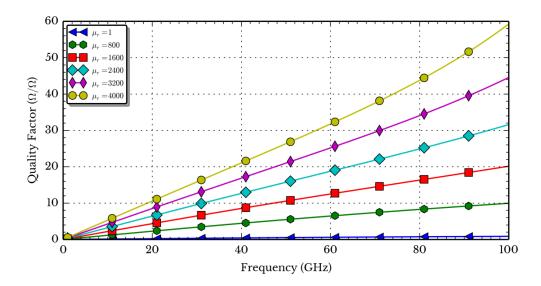

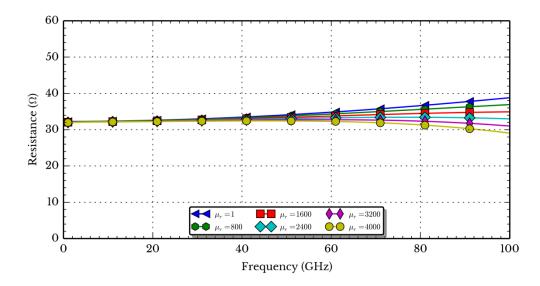

| Figure 3.15: Inductance of a single helix in an ideal magnetic material                                                                                                                                     |

| Figure 3.16: Quality factor of a single helix in an ideal magnetic material                                                                                                                                 |

| Figure 3.17: Resistance of a single helix in an ideal magnetic material                                                                                                                                     |

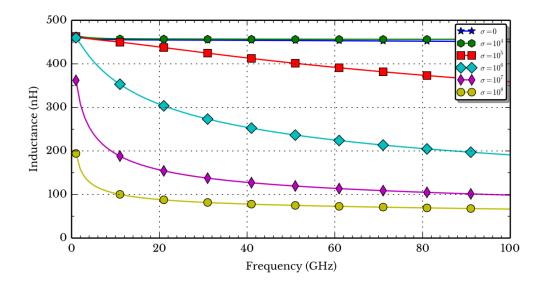

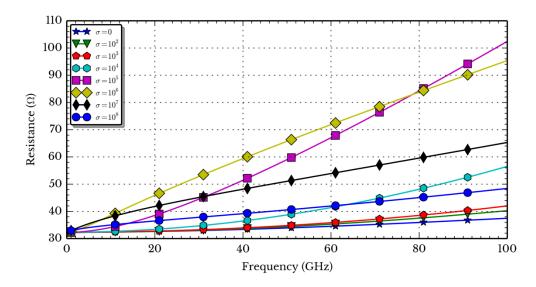

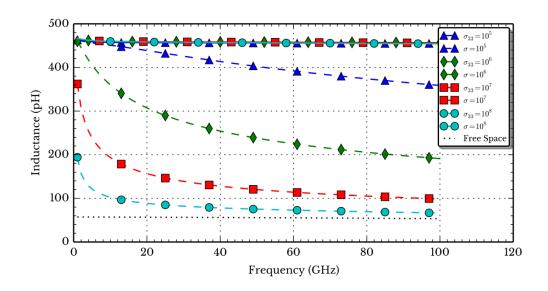

| Figure 3.18: Inductance of a single helix embedded in a conducting magnetic material ( $\mu r = 600$ )<br>47                                                                                                |

| Figure 3.19: Resistance of a single helix embedded in a conducting magnetic material ( $\mu r = 600$ )                                                                                                      |

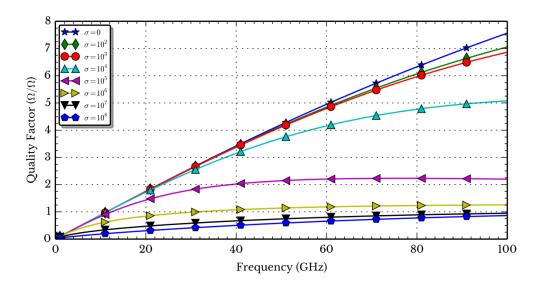

| Figure 3.20: Quality factor of a single helix embedded in a conducting magnetic material ( $\mu r = 600$ )                                                                                                  |

| Figure 3.21: Inductance of an anisotropic conductive film compared to the isotropic film                                                                                                                    |

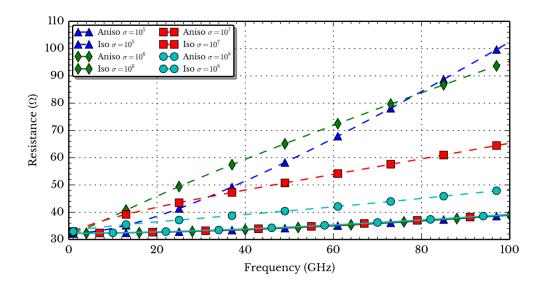

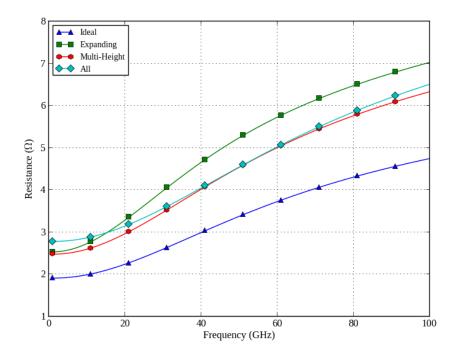

| Figure 3.22: Resistance of an anisotropic conductive film compared to the isotropic film                                                                                                                    |

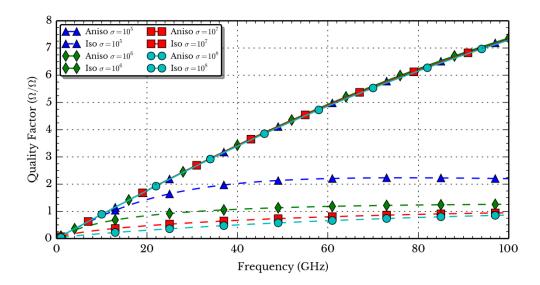

| Figure 3.23: Quality factor of an anisotropic conductive film compared to the isotropic film 51                                                                                                             |

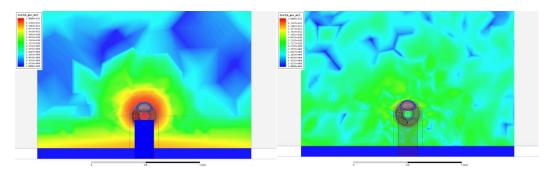

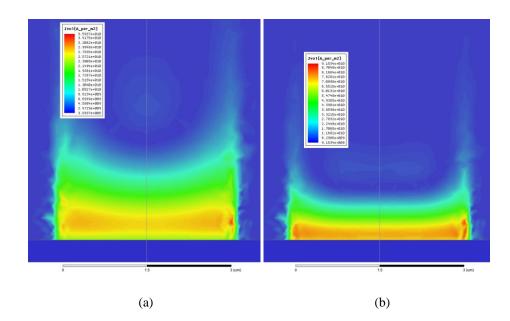

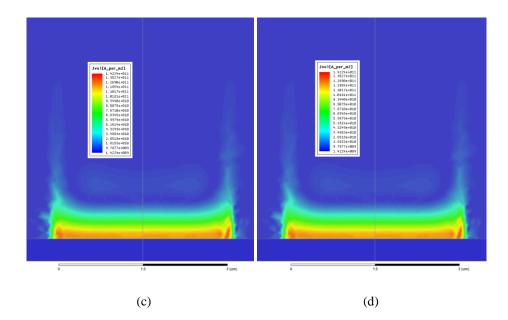

| Figure 3.24: Current distribution of the inductor embedded in (a) an isotropic film (b) an anisotropic film of the same conductivity at 70 GHz                                                              |

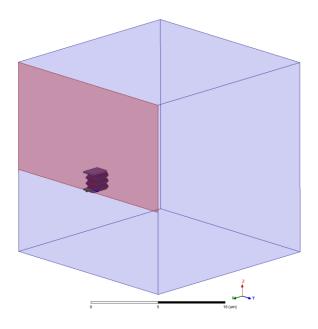

| Figure 3.25: Helix array simulation environment                                                                                                                                                             |

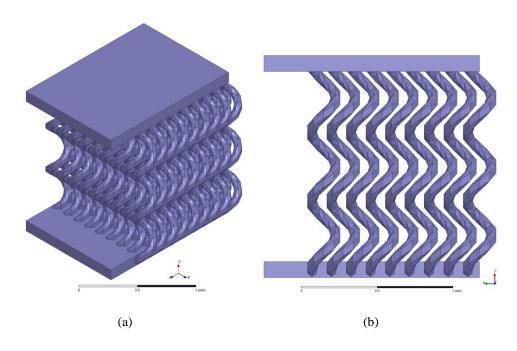

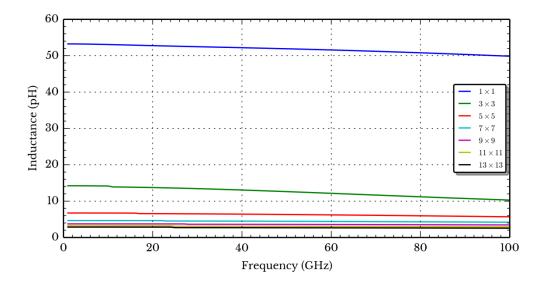

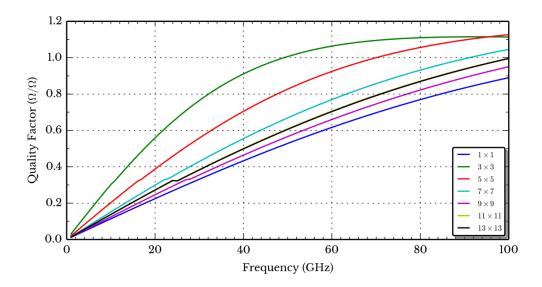

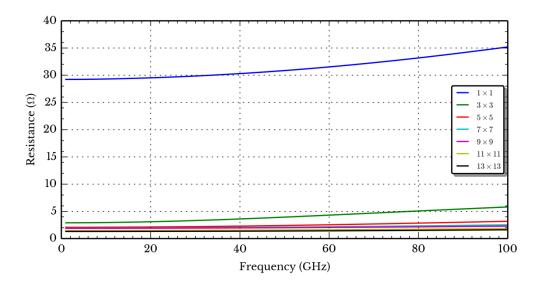

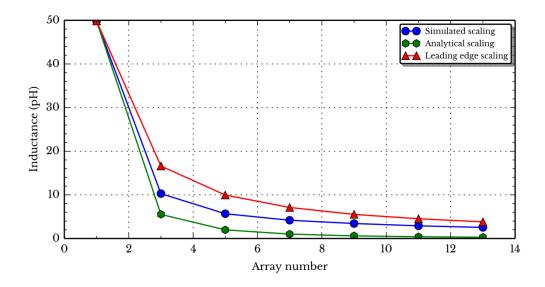

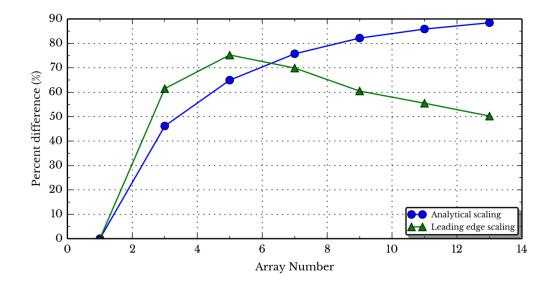

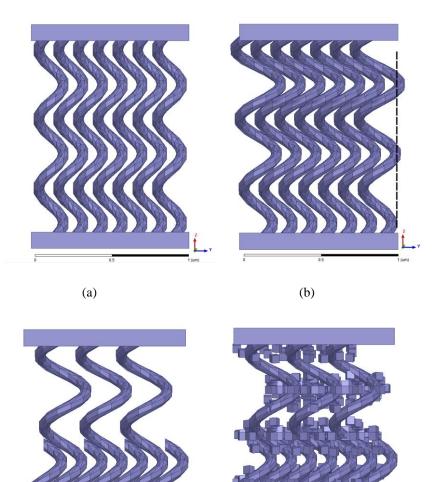

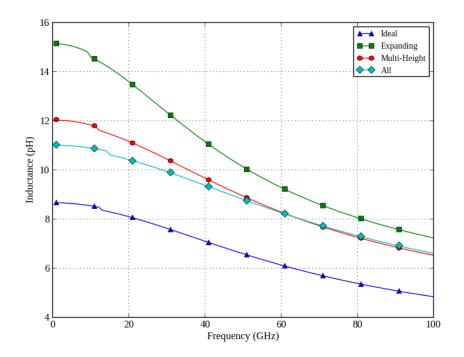

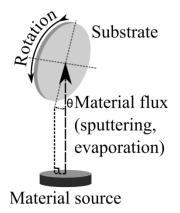

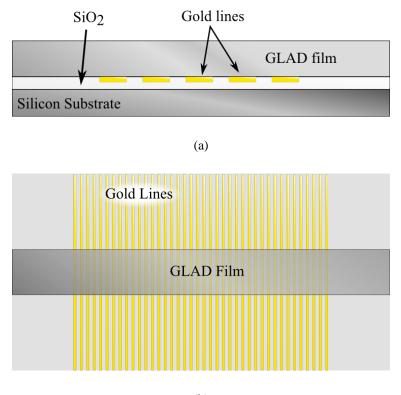

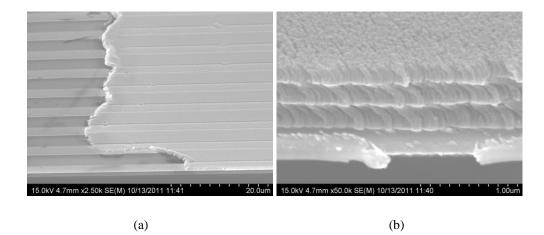

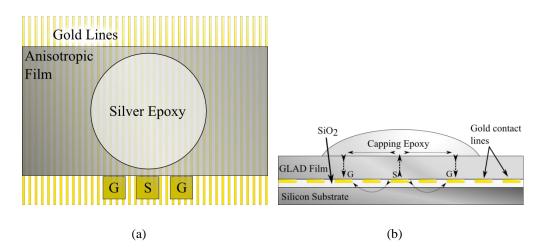

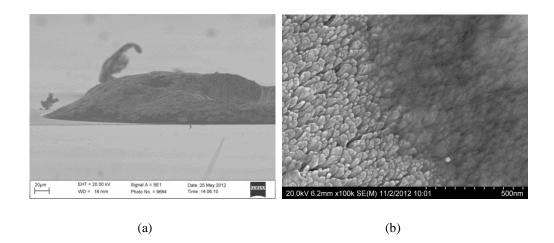

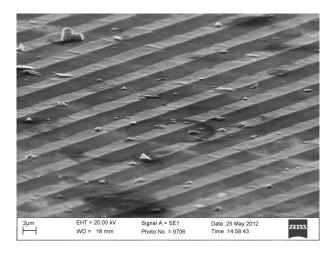

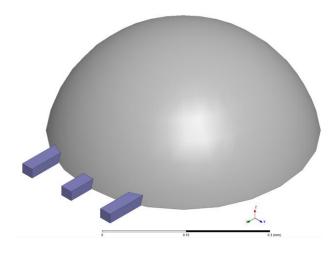

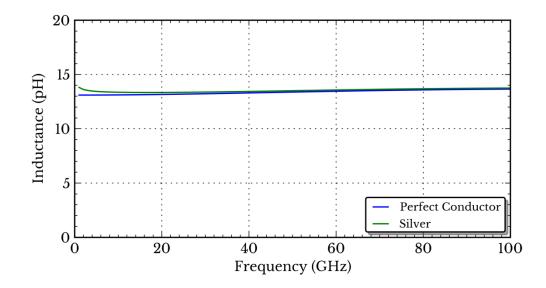

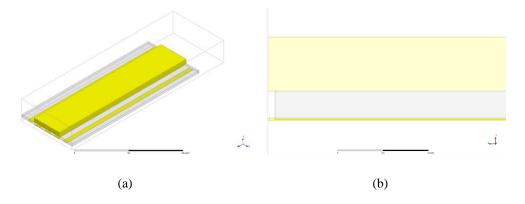

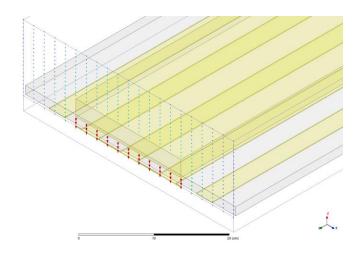

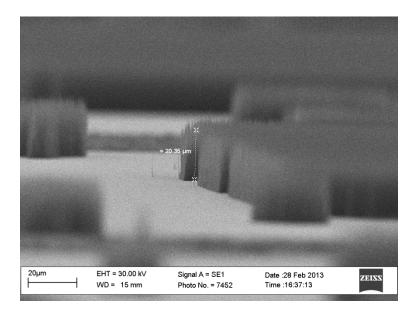

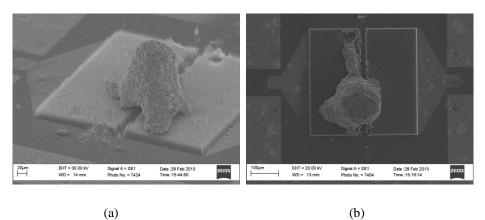

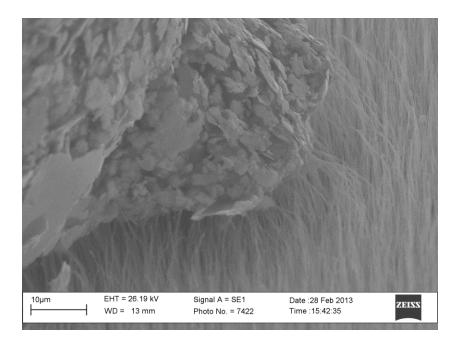

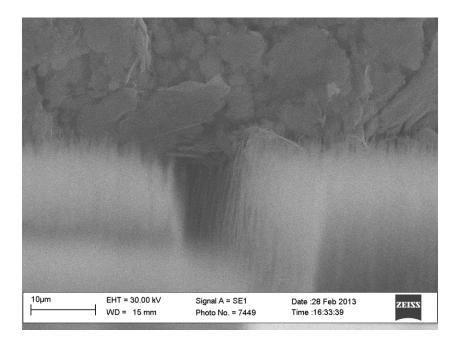

Figure 3.26: Detailed view of the  $9 \times 9$  helix array. (a) isometric view of the helix array showing the 2-dimensional square array. (b) side view of the helix array showing the top and bottom lines that connect to the port as well as the completely separated nature of the helices..... 53 Figure 3.30: Inductance scaling of helix arrays. The array number is the number of helices along each side of the square (eg. an array number of 5 means the simulation is a 5x5 array). The Figure 3.31: Top-down view of the current distribution of an anisotropic nickel film (reduced conductivity,  $\sigma = 105$ ) at (a) 10 GHz, (b) 30 GHz, (c) 50 GHz, (d) 70 GHz. The edge of the film is visible as the sudden transition from no current to high current at the bottom of the image. The incoming wave is travelling from the bottom of the image to the top. The skin depth is very small at high frequencies, including depths of less than  $1 \,\mu m$  for 50 and 70 GHz. The small skin depth means that fewer inductors are conducting in parallel, Figure 3.32: Percent difference between the analytical inductor scaling models and the simulated Figure 3.33: Helix width comparison. (a) An idealized helical film. (b) The same film but with a radius change of 50% between bottom and top. The radius change is emphasized by the vertical, dashed line. (c) Addition of helix termination defects to the model in (b). (d) Addition to random growth defects to the model in (c). The defects are modeled as arrays of cubes of material that are placed pseudo-randomly. This model includes all observed Figure 4.2: Test substrate layout for RF measurements of the GLAD film. (a) The cross section of the test substrate. The dimensions are not to scale: the oxide layer is approximately  $1 \, \mu m$ thick, the gold lines are **100 nm** thick, and the GLAD film is about **500 nm** thick. (b) The layout of the film on the substrate. The GLAD film covers the entire length in the long axis, but leaves the gold lines exposed in the short axis. Note that the dimensions are not to scale; the gold lines are closely spaced and approximately  $3 \mu m$  in width, compared to a width of about 7 mm (short axis) for the substrate and a length of about 20 mm (long axis). Figure 4.3: Fabricated nickel film. (a) A portion of the GLAD film with good uniformity. (b) A

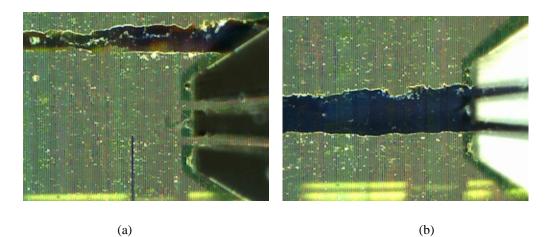

| Figure 4.5: SEM image of damage to the GLAD film due to direct contact with the RF probe 68                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.6: SEM image of a non-uniform section of GLAD film. The image clearly shows gaps in the film that are smaller than 2 microns (1 bar in the scale graph)                                                                                                                                                                         |

| Figure 4.7: Capping technique measurement layout. (a) Top-down view of the conductive capping material (labeled silver epoxy). The material is placed directly on top of the film. (b) Cross-section view of the capping layer. The dashed lines show the direction of current through the device. 70                                    |

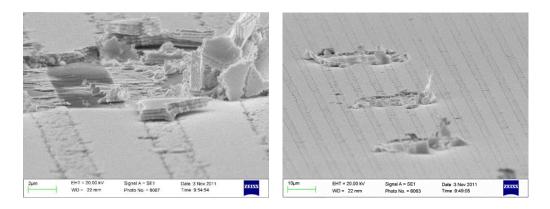

| Figure 4.8: SEM micrographs of the silver conductive epoxy capping layer. (a) Epoxy shown deposited on top of the film. (b) Interface between the epoxy and the film                                                                                                                                                                     |

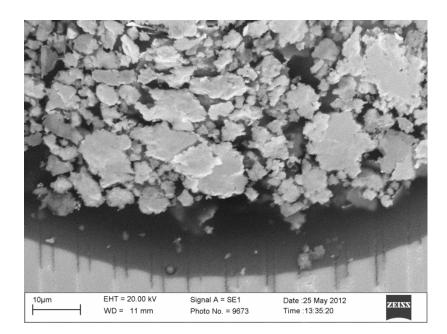

| Figure 4.9: Silver particles suspended in the epoxy material                                                                                                                                                                                                                                                                             |

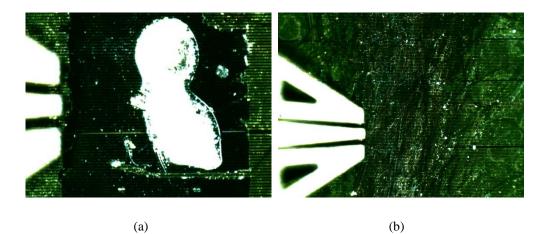

| Figure 4.10: Measurement setup with: (a) silver epoxy capping layer (white), gold (green) and anisotropic film (black) and (b) with the film removed                                                                                                                                                                                     |

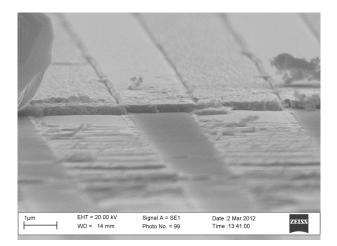

| Figure 4.11: SEM image of gold lines after the GLAD film was manually removed                                                                                                                                                                                                                                                            |

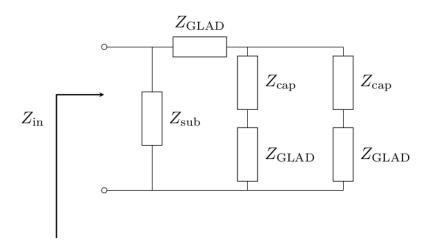

| Figure 4.12: Circuit model for extraction of the GLAD film                                                                                                                                                                                                                                                                               |

| Figure 4.13: Simulation model of the silver epoxy. The blue lines on the left are the GSG probe lines which end on the surface of the silver (grey)                                                                                                                                                                                      |

| Figure 4.14: Simulated inductance of the silver epoxy                                                                                                                                                                                                                                                                                    |

| Figure 4.15: One-port simulation model of the measured chip. (a) Full structure including boundary. (b) Side view of the port and layers                                                                                                                                                                                                 |

| Figure 4.16: One-port model with port field visible                                                                                                                                                                                                                                                                                      |

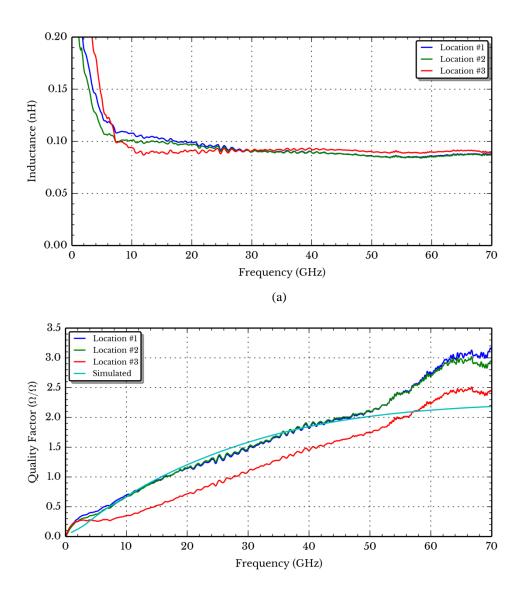

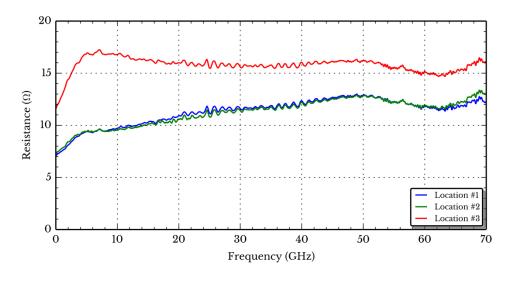

| Figure 4.17: Measured film inductance with return path results. (a) The inductance of a single return path. (b) The quality factor of a single return path. (c) The resistance of a single return path                                                                                                                                   |

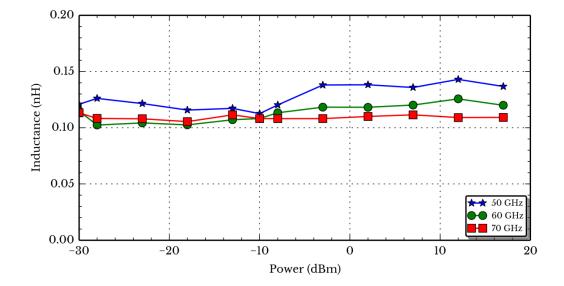

| Figure 4.18: Raw (unextracted) measured inductance at 50, 60, and 70 GHz over a range of powers from -23 dBm to 7 dBm                                                                                                                                                                                                                    |

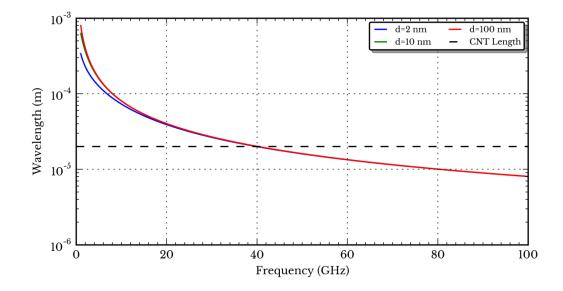

| Figure 5.1: Wavelength of a SWCNT of varying diameters and 20 um in length. As the frequency increases, the CNT length becomes close to the wavelength and the CNT length is equal to the wavelength around 40 GHz. This ultra-short wavelength for a CNT transmission line causes even short CNT devices to act as distributed elements |

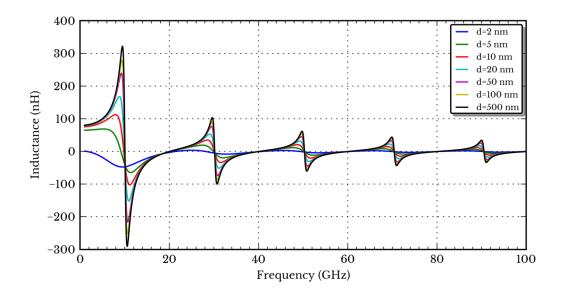

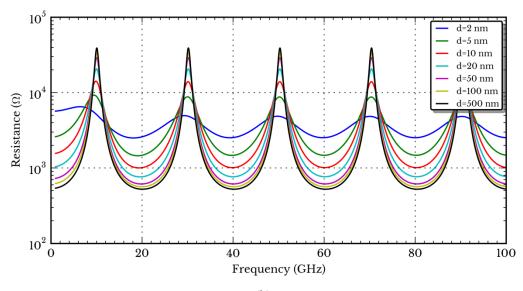

| Figure 5.2: Circuit performance of a SWCNT. In all cases the CNT length was 20 μm (a) The inductance of the SWCNT using a transmission line model for the CNT. (b) The resistance of the CNT using the transmission line model, and (c) the resulting quality factor for the CNT                                                         |

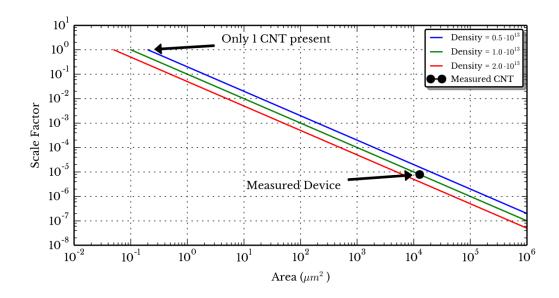

| Figure 5.3: Scaling behaviour of CNT bundles by area                                                                                                                                                                                                                                                                                     |

| Figure 5.5: CNT test structures (short, open, CNT)                                                                                                                                                                                                                                                                                       |

| Figure 5.6: Carbon nanotube growth on substrate                                                                                                                                                                                                                                           | ;9 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 5.7: Two-port CNT test device with silver epoxy cap9                                                                                                                                                                                                                               | 0  |

| Figure 5.8: CNT adhesion to silver epoxy9                                                                                                                                                                                                                                                 | 0  |

| Figure 5.9: Epoxy bridge over CNT gap. The integrity of the gap between the CNTs as well as the structure of the CNTs under the silver epoxy is clearly visible                                                                                                                           |    |

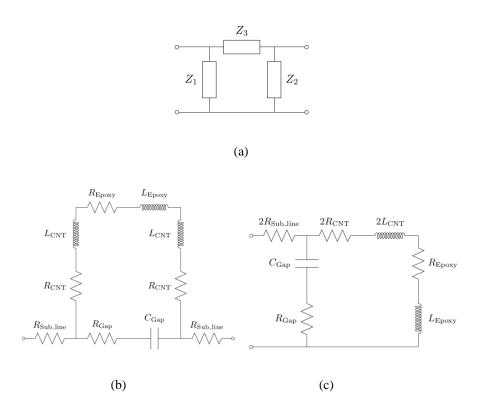

| Figure 5.10: Circuit extraction models. (a) The generic $\pi$ -model for a 2-port network. (b) A expanded model for <b>Z3</b> from (a), including the capacitance of the gap and the resistance of the gold connecting traces. (c) The same model as shown in (b), with duplicate element | of |

# List of Symbols and Abbreviations

| С            | Symbol for capacitance                            |

|--------------|---------------------------------------------------|

| CNT          | Carbon nanotube                                   |

| GLAD         | Glancing angle deposition                         |

| j            | Symbol for the imaginary number $(j = \sqrt{-1})$ |

| L            | Symbol for inductance                             |

| MMW          | Millimetre-wave                                   |

| MMWI         | Millimetre-wave inductor                          |

| MWCNT        | Multi-wall carbon nanotube                        |

| NSF          | Nano-structured film                              |

| Q            | Symbol for the quality factor                     |

| R            | Symbol for resistance                             |

| S-Parameters | Scattering parameters                             |

| SWCNT        | Single wall carbon nanotube                       |

| X            | Symbol for reactance                              |

| Z            | Symbol for impedance $(Z = R + jX)$               |

| Z-Parameters | Impedance Parameters                              |

### Chapter 1: Introduction to Inductors at GHz Frequencies

#### **1.1 Inductors and Circuits**

#### 1.1.1 Introduction

This thesis discusses the challenges involved in integrating inductors into modern radio-frequency integrated circuits (RFICs) and proposes new nanotechnology-based inductor designs for on-chip inductors.

This thesis begins with an overview of modern inductor designs in the first chapter. The subsequent chapters introduce vertically-aligned nanoscale structures for on-chip inductors, including simulations and fabricated device measurements.

#### 1.1.2 Ubiquitous computing and advanced communications

The last several decades have brought about great advances in semiconductor technology which has made portable electronic devices an indispensable part of our daily lives. Many advanced electronic circuits and systems are now inexpensively available to the general public in the form of laptops, tablets, smartphones, global positioning systems (GPS), heath monitoring devices, and many others. In addition to core computing, many of these portable electronic devices contain advanced radio technologies for communicating with other portable and stationary devices.

These advanced communicating devices require small and low-power transceivers to send and receive signals to base stations and each other [1]. Integrated transceivers are complex devices that are often built monolithically in a single chip. Transceivers, like any circuit, are constructed out of transistors, resistors, capacitors and inductors. Although transistors have been aggressively scaled down to nanometer sizes, passive components such as inductors and capacitors have not noticeably scaled [2]. The scaling behaviour for inductors is a significant problem in modern high-frequency electronic systems design because the area of a single spiral on-chip inductor is a thousand times larger than a transistor. This area inefficiency has motivated efforts to build circuits with a minimum number of inductors or to look for alternative technologies for implementing on-chip inductors. Moreover, the low quality factor of integrated inductors, due to metal and substrate losses, poses a significant challenge to overcome in the design of modern CMOS radio frequency integrated circuits [3].

This thesis will discuss the challenges associated with building modern integrated inductors, using modern inductor technologies, and it will propose new inductor technologies for radio-frequency applications.

#### 1.1.3 What are inductors

Inductors are one of the fundamental electronic components, along with resistors, capacitors and transistors. Inductors are useful in a wide variety of applications, ranging from power system transformers to microwave filters. Large scale, discrete inductors are typically made by wrapping coils of wire around a core material such that the magnetic field from each of the wires adds in a constructive manner to create a large magnetic field in the core material. Due to the creation of the magnetic field, inductors resist changes in currents flowing through the device.

While discrete inductors are relatively simple to build, the field of integrated electronics is based on planar fabrication technology involving the deposition and patterning of layers of materials. These layers are deposited on to the chip and patterned in an iterative process until they have been built up into functioning device. This planar fabrication technology limits the devices created to a primarily 2-dimensioal structure. Vertical connections between layers are possible; however, it is necessary that any device fabricated on-chip have only 2 principle dimensions. In other words, all devices on a modern chip should be planar.

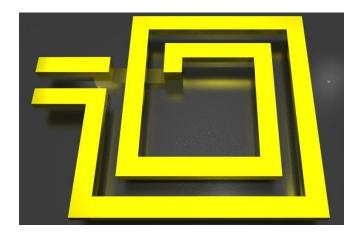

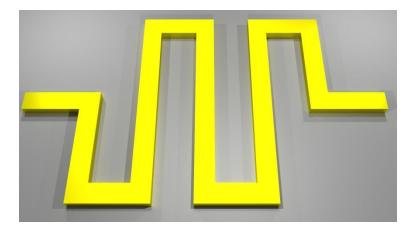

Unfortunately, solenoid structures are intrinsically 3-dimensional and do not translate well into planar structures. To avoid the use of 3D structures, a number of 2-dimensional designs have been developed and are currently used in commercial devices, such as the designs shown in Figure 1.1. These 2D structures mainly consist of spiral inductors (shown in Figure 1.1b), but they have many drawbacks compared to 3-dimensional des[4]igns. For example, planar inductors suffer from large parasitic coupling to the substrate, inducing losses and limiting their maximum operation frequency in addition to occupying significantly larger areas than their 3D counterparts of the same inductance. A typical area for a 1 nH on-chip inductor is approximately  $10^4 \,\mu\text{m}^2$  (when implemented as a square-spiral), which is huge compared to a typical transistor area of only few tens of  $\mu\text{m}^2$  [5][6][7].

(a) Planar meander inductor

(b) Planar circular-spiral inductor

#### Figure 1.1: Planar inductors.

Integrated electrical component sizes are continuously being reduced for increased circuit density, lower power consumption, and increased speed. Recently, inductor designs have not been able to scale as fast as other components. For low frequency and discrete devices, solenoid structures are known to produce high quality inductors with useful inductance values. These structures are used extensively in large discrete devices, such as transformers and electric motors. However, for high frequency integrated devices it is impractical to have large discrete components due to high costs and exact manufacturing requirements. For this reason there is a high demand for small inductor designs that can be integrated on-chip with other electronic components, such as digital CMOS chips.

#### **1.2** A brief overview of the proposed inductor technologies

This thesis will introduce the use of nano-structured materials for millimetre-wave (mm-wave) inductor applications. This research into new materials and structures for mm-wave inductors will attempt to bridge the size and quality gap between inductors and other integrated chip components. The finite element simulations of the proposed inductor devices will be presented as well as measured results from fabricated samples. The resulting inductor technologies show promise, with high inductance and acceptable quality factors in the mm-wave frequency range.

The two nanostructured materials that will be presented are carbon nanotubes (CNTs) deposited with PECVD and nanowire films fabricated by glancing angle deposition (GLAD).

Nanostructured thin films are constructed using fabrication processes that produce wafer-scale arrays of nanoscale structures through techniques such as GLAD. The GLAD technique is based

on physical vapour deposition, which makes it very versatile in the types of materials that can be deposited. This thesis will introduce the use of anisotropic magnetic structures as a building block for integrated RF inductors. These inductors have inductance density when compared to traditional inductor designs and quality factors which are suitable for commercial applications.

Both CNTs and GLAD films are promising alternatives to modern integrated inductor technologies. This thesis will introduce the background necessary to evaluate inductor technologies and explore new materials for advancing the state of modern integrated inductors.

Chapter 2 introduces on theory necessary to evaluate inductor parameters and provides background information about the current state of inductor technologies. Chapter 3 presents the electromagnetic (EM) simulation results for new inductor designs using the proposed material technologies. Chapter 4 presents the measured results for the nanostructured thin film devices and compares these results with the simulation results from chapter 3. Chapter 5 presents the measured results for carbon-nanotube array-based inductors. Finally, chapter 6 concludes this dissertation by summarizing the research work and suggesting directions for our future research.

# Chapter 2: Inductance and Inductors

#### 2.1 Introduction

This chapter will introduce the concepts behind modern inductors, including the mathematics and theory of inductors. Once the basic concepts have been covered, a survey of the various types of modern inductors will be presented as well as some new technologies that promise improved performance over existing technologies.

#### 2.2 Inductance

#### 2.2.1 Introduction

Inductance is the name given to the physical phenomenon of the creation of an electric field in response to a changing current in a circuit. This phenomenon is an electromagnetic property which is described by Maxwell's equations and that relates changes in magnetic fields to electric fields. Devices that are built to exhibit inductance are called inductors. Inductors are used in many kinds of circuits including filters, resonators, biasing circuits, transformers, and regulators. When the inductance effect is undesired, it is called a parasitic effect and it is often modeled in circuits as extra circuit elements called parasitic elements, typically limiting the performance of a circuit.

Inductance is a frequency-dependent effect, often becoming more important at higher frequencies as the impedance of inductors increases with frequency. This makes inductors especially important in radio-frequency (RF) circuits both because of its uses in RF circuits (eg. filters, biasing, resonators) and its undesired effects. Inductors are especially useful in conjunction with capacitors; together they form resonators which can be used as building blocks for filters, switches, and matching circuits [8]. However, inductors can also be used on their own as RF chokes (open-circuits), transformers, and as RF biasing elements (eg. inductively degenerated biasing).

#### 2.2.2 Maxwell's Equations

Inductance, like all electromagnetic phenomenon, is governed by a set of equations called Maxwell's Equations. Maxwell's equations are the foundation of classical electrodynamics and govern all electromagnetic phenomena [9]. Maxwell's equations can be written as in equations 2.1-2.4 [9].

n

$$\nabla \cdot \mathbf{E} = \frac{\rho}{\varepsilon_0}$$

2.1

$$\nabla \cdot \mathbf{B} = 0 \tag{2.2}$$

$$\nabla \times \mathbf{E} = -\frac{\partial \mathbf{B}}{\partial t}$$

2.3

5

$$\nabla \times \mathbf{B} = \mu_0 \mathbf{J} + \mu_0 \varepsilon_0 \frac{\partial \mathbf{E}}{\partial t}$$

2.4

Maxwell's equations describe the two vector fields in classical electrodynamics and their interactions with each other, as well as a quantity called charge. The two vector fields are called the electric field (denoted **E**) and the magnetic field (denoted **B**), with charge ( $\rho$ ) and current (**J**) acting as the physical sources for those fields [9]. However, current is just the movement of charge, making charge the source of all electric and magnetic fields.

Inductance is a derived quantity of Maxwell's equations; the derivation is shown in the next section (section 2.2.3).

#### 2.2.3 Definition

At the beginning of this chapter, inductance was introduced with its definition; that it is the creation of an electric field in response to a change in current. None of Maxwell's equations directly relate a change in current and an induced electric field; however, equation 2.4 relates a current to a magnetic field and equation 2.3 states that a change in a magnetic field produces an electric field. In the quasi-static case, the second term  $(\frac{\mu\epsilon\partial E}{\partial t})$  **B** causes an electric field [9]. This can be assumed to be equal to Obecause the magnetic field produced by a change in **E** is small compared to the field produced by **J**. In this case, if **J** is known, then **B** is also known from equation 2.4. One key point to note from equation 2.4 is that **B** is proportional to **J**, therefore a change in **J** means a proportional change in **B**.With this knowledge, we can note that equation 2.3 directly relates an electric field with a changing magnetic field. However, in this form to solve for the generated electric field, the calculation of a curl is required. To simplify this equation, the curl theorem can be applied and both sides of the equation can be integrated over an area as shown in equation 2.5.

$$\int (\nabla \times \mathbf{E}) \cdot d\mathbf{a} = -\int \frac{\partial \mathbf{B}}{\partial t} \cdot d\mathbf{a}$$

2.5

Then the curl theorem can be applied to the left side [9]:

$$\int (\nabla \times \mathbf{E}) \cdot d\mathbf{a} = \oint \mathbf{E} \cdot d\mathbf{l}$$

2.6

Next, the derivative with respect to time can be taken outside the integral on the right side of equation 2.5. Finally, the integral is just the total magnetic flux through the area a, which is denoted by  $\phi$  in equation 2.7.

$$-\int \frac{\partial \mathbf{B}}{\partial t} \cdot d\mathbf{a} = -\frac{\partial}{\partial t} \int \mathbf{B} \cdot d\mathbf{a} = -\frac{d}{dt} (\Phi)$$

2.7

6

One important relation to note from equation 2.7 is that it is just the time derivative of the definition of magnetic flux, shown in equation 2.8.

$$\Phi = \int \mathbf{B} \cdot d\mathbf{a}$$

2.8

Then the curl theorem can be applied to the left side to change the area integral into a line integral, as shown in equation 2.6 [9].

$$\int (\nabla \times \mathbf{E}) \cdot d\mathbf{a} = \oint \mathbf{E} \cdot d\mathbf{l} = -V$$

2.9

Where  $\mathbf{l}$  is the circumferential loop around the area  $\boldsymbol{a}$ . The right hand side of equation 2.6 is just the definition of the negative of the voltage around the loop, *V*.

Finally, substituting the relations from equations 2.7 and 2.6 into equation 2.5 gives equation 2.10.

$$-V = -\frac{d\Phi}{dt}$$

2.10

Equation 2.10 is not useful for circuit designers because it requires the explicit calculation of the total magnetic flux through a loop and its change with respect to time, which is generally hard. To simplify the calculation, it is useful to note that  $\Phi$  is proportional to **B** and in the quasi-static case, **B** is proportional to a current *I* [9]. This constant of proportionality is called the inductance and it is given the symbol *L* and has the unit of henries (H), as shown in equation 2.11 [9].

$$\Phi = LI \qquad 2.11$$

Substituting equation 2.11 into equation 2.10 yields equation 2.12, which is very useful in circuit analysis.

$$V = L \frac{dI}{dt}$$

2.12

Equation 2.12 is a very useful equation because it relates inductance to quantities that are easily measured: voltage, current and time. Unlike equation 2.3, all the quantities in equation 2.12 are scalar quantities that don't require vector analysis or calculus to compute. Equation 2.12 says that the inductance of a device can be determined by changing the current running through a device and measuring the voltage produced by the changing current. The voltage produced is always opposing the change in current [9].

#### 2.2.4 Inductance and energy

As magnetic fields store energy, it is possible to use inductance as a convenient way to calculate the magnetic energy stored in a circuit since inductance is the relation between current and a produced magnetic field. The energy stored in the magnetic field of an inductor is given by equation 2.13, where W is the energy stored in the field, L is the inductance of the device, and I is the current through the device [9].

$$W = \frac{1}{2}LI^2 \tag{2.13}$$

Equation 2.13 provides physical insight into the physical operating principle of inductors: moving current stores energy in the form of a magnetic field. Applying an electric field (ie. a voltage) to a charge causes it to move, creating a current. The current stores energy in a magnetic field. Changing the current causes a change to the magnetic field which in turn creates an electric field. Therefore, energy is converted from magnetic energy into electric energy.

#### 2.2.5 Inductance in the frequency domain and Quality Factor

The primary figure of merit for an inductor is called the quality factor. Similar to capacitors, the quality factor is defined as the ratio of the energy stored in the device to the energy dissipated by the device (equation 2.14) [8][10].

$$Q = \omega \frac{\text{peak energy stored}}{\text{average energy dissipated}} = \frac{\omega(2E_{\rm M} - 2E_E)}{P_{av}}$$

2.14

The magnetic energy stored in the circuit can be expressed in terms of the inductance given in 2.13. The energy dissipated by the resistor is given by  $P = VI = I^2 R$ . The electric energy present in a capacitor is given by equation 2.15 [8].

$$E_E = \frac{1}{2}V^2C = \frac{1}{2}I^2\frac{1}{\omega^2C}$$

2.15

Combining equations 2.13, 2.14, 2.15 gives equation 2.16.

$$Q = \frac{\omega(2E_M - 2E_E)}{P_{av}} = \frac{\omega\left(2\frac{1}{2}LI^2 - 2\frac{1}{2}I^2\frac{1}{\omega^2 C}\right)}{I^2 R} = \frac{\omega L - \frac{1}{\omega C}}{R}$$

$$= \frac{\Im\{Z\}}{\Re\{Z\}}$$

2.16

Physically, the energy dissipated by the inductor is due to ohmic losses (heating), parasitic losses (coupling to the substrate) and radiation losses.

The most important result of the definition of the quality factor shown in equation 2.16 is that the quality factor is the tangent of the input impedance phasor of a 1-port device, given by equation 2.17 [11]. It is much easier to measure the impedance of a device than it is to measure the energy stored in the electric and magnetic fields. This equivalent definition of the quality factor is useful for determining the quality factor of an experimental device due to the ease of measuring the impedance of a device. The quality factor can be calculated from the S-parameters measured by vector network analyzers (VNA).

$$Q = \tan \theta = \frac{\Im\{Z\}}{\Re\{Z\}}$$

2.17

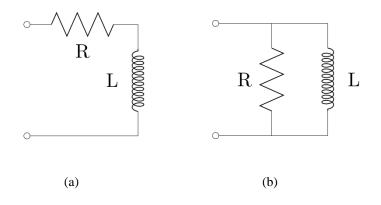

For the purposes circuit modeling, there are two elementary circuits which can simply describe a genetic inductor: an ideal inductor in series or in parallel with a resistor. The total energy dissipated in the inductor is modeled using the resistor and the inductive reactance is modeled with the ideal inductor, shown in Figure 2.1a. The result for a series resistance model for the quality factor is shown in equation 2.18.

$$Q = \frac{\Im\{Z\}}{\Re\{Z\}} = \frac{\omega L}{R}$$

2.18

If the inductor is modeled with a parallel resistance, as shown in Figure 2.1b, then the resulting quality factor can be calculated by equation 2.17; the result is given by equation 2.19. The resulting quality factor for the parallel circuit is the inverse of the quality factor in the series circuit. For a series circuit, the inductor is ideal if the resistance is equal to 0, however in the parallel circuit the inductor is ideal when the resistance is infinite.

$$Q = \left(\frac{\omega L R^2}{R^2 + \omega^2 L^2}\right) \left(\frac{R^2 + \omega^2 L^2}{\omega^2 L^2 R}\right) = \frac{R}{\omega L}$$

2.19

Figure 2.1: Inductor circuits. (a) Inductor model with a series resistance. Increasing the resistance in this model means that more power is lost in the resistor when compared to the inductor. (b) Inductor model with a parallel resistance. Increasing the resistance means that more power is stored in the inductor when compared to the resistor.

Equation 2.14 indicates that the quality factor of an inductor can be understood as a measure of how much energy is stored in the magnetic field compared to the energy lost through operation of

the inductor. An ideal inductor is one that has no real power loss, indicating a device that conserves energy in a circuit. In contrast, a purely restive element converts energy in a circuit to other kinds of energy (eg. mechanical, optical, radiation, heat, etc.). The lack of storage of energy in a resistor means that a resistor has a quality factor of 0.

For most applications of inductors, high quality factor inductors are essential for good system performance. The exception for high quality factors is wideband systems (resonators, impedance matching, etc.) which may require lower quality factors; however, due to the simplicity of building integrated resistive components it is simple to arbitrarily lower the quality factor of a high-quality inductor. A low quality factor means that the inductor exhibits a high resistance in proportion to its reactance, which can introduce noise into a high-frequency circuit [12].

#### 2.3 Magnetic materials

#### 2.3.1 Magnetic polarization in response to an applied field

The relations discussed so far have related the values of **E** and **B** or *V* and *I* directly with no discussion of the effect of materials on the magnetic field and the inductance. Similar to the electric polarizability materials, some materials also exhibit a magnetic polarizability in response to applied magnetic fields. This polarization is often denoted by **M** and it contributes directly to the total magnetic field **B** [9].

The magnetic field can therefore be broken up into two components, a component due to freeflowing current (denoted **H**) and a component due to bound atomic currents (**M**). These components are analogous to the electric **D** and **P**, however they tend to be more useful than **D** and **P** in practical scenarios [9]. Therefore, the total magnetic field is given by equation 2.20 [9].

$$\mathbf{B} = \mu_0 (\mathbf{H} + \mathbf{M})$$

2.20

It is quickly worth noting that authors sometimes refer to  $\mathbf{H}$  as the magnetic field due to its usefulness in solving equations with linear materials [8]; however, this usage is confusing and can lead to a number of incorrect conclusions [9].

A permanent magnet is a simple example of the differences between **B** and **H**. Permanent magnets have a well-understood **B**-field and the **H**-field outside of a permanent magnet is equivalent after scaling by  $\mu_0$  (**M** = 0 outside the magnet) [13]. However, inside the magnet there is a magnetic dipole **M**, which has a divergence on the surface of the magnet. Taking the divergence of equation 2.20 results in equation 2.21, indicating that the **H**-field has a discontinuity on the surface of a permanent magnet and that this can be viewed as a magnetic "charge" [13]. The implication of this charge is that the **H** field acts the same way as an electric field, with field lines going from north "charge" to south "charge". This behaviour results in an **H** field that is not only different from **B** inside a magnetic material, but is also in the direction opposing **B**.

$$\nabla \cdot \mathbf{H} = -\nabla \cdot \mathbf{M} = \rho_{magnetic} \qquad 2.21$$

In general, **M** is an independent property of a material; however, there is a class of materials called *linear materials* for which **M** is proportional to **H**, shown in equation 2.22. The constant of proportionality,  $\chi_m$ , is called the magnetic susceptibility [9]. Plugging equation 2.22 into equation 2.21 gives equation 2.23, where  $\mu$  is called the magnetic permeability and it is a material property [9]. Many magnetic materials are linear materials for small values of **H**.

$$\mathbf{M} = \chi_{\mathrm{m}} \mathbf{H}$$

2.22

$$\mathbf{B} = \mu_0 (1 + \chi_m) \mathbf{H} = \mu \mathbf{H}$$

2.23

#### 2.3.2 Magnetism

There are a wide variety of materials that respond differently to magnetic fields classified into several groups [14]; however, there are only two forms of magnetism that interact strongly with external applied magnetic fields: ferromagnetism and ferrimagnetism [15].

A ferromagnetic material is a material in which every atom in the lattice spontaneously aligns to have the same magnetic moment, which produces a strong external magnetic field [14][9]. However, despite this alignment of magnetic moments, ferromagnetic materials often do not spontaneously have macroscopic magnetic fields because the aligned atoms form groups [9]. These groups are called domains, which may have a moment in any direction and tend to cancel each other out in a bulk material [14]. Domains can be aligned by an external magnetic field, resulting in a relative permeability for the material which is typically much greater than 1 [9]. Typical examples of ferromagnetic materials include iron, nickel, steel, etc [15].

In contrast to ferromagnetic materials, ferrimagnetic materials tend to be high resistivity compound materials, called ferrites [8]. Ferrimagnetic materials consist of two types of lattice sites: sites that align to external magnetic fields and sites that anti-align to external magnetic fields [14]. The two different lattice sites typically have different magnitudes of their magnetic spin, which produces a net magnetic field [14]. Similar to ferromagnets, ferrimagnets can be aligned to form a macroscopic field by applying an external magnetic field [14]. Ferrimagnets are often used in microwave devices to produce anisotropic materials to make non-reciprocal devices [8].

Since both ferromagnetic materials and ferromagnetic materials have magnetic permeabilities that are greater than 1, they are suitable for use as magnetic cores in inductors [9].

### 2.4 Loop and Partial Inductance

#### 2.4.1 The inductance problem

Section 2.2.3 showed the definition of inductance and the derivation of inductance from Maxwell's equations; however, the arguments used all contained areas and loops, not single elements. This definition is useful for analyzing devices that contain easily identifiable loops, such as solenoids, however it is much more difficult to analyze more complex structures where the loop may not be easily identifiable or the loop may have multiple devices connected across it. One example of these kinds of complex structures include integrated circuits, which may have many signal and ground lines and often have devices connected between them.

#### 2.4.2 Partial inductance

The solution to the inductance problem is to use an alternate solution to magnetic flux: the magnetic vector potential, **A**. The magnetic flux of a loop can be written in terms of the magnetic vector potential as in equation 2.29 [9]. Whereas the magnetic flux is dependent on the magnetic field and the area of the enclosed loop, it is dependent only on the magnetic vector potential and the circumference of the loop.

$$\Phi = \int \mathbf{B} \cdot d\mathbf{a} = \oint \mathbf{A} \cdot d\mathbf{l}$$

2.24

This change from area to length is important because the magnetic flux can then be written by knowing only the path and the magnetic vector potential along the path and not the magnetic field over an area. This means that a specific portion of the magnetic flux can be attributed to a specific portion of the loop, which is not possible with the area integral [16]. Due to the properties of integrals, the loop integral can be expressed as a sum of its parts (equation 2.33).

$$\oint \mathbf{A} \cdot d\mathbf{l} = \int \mathbf{A} \cdot d\mathbf{l}_1 + \int \mathbf{A} \cdot d\mathbf{l}_2 + \dots = \sum_i \int \mathbf{A} \cdot d\mathbf{l}_i$$

2.25

Equation 2.25 states that the contour integral of A can be split into an arbitrary number of segments and the total integral is equal to the summation of the contribution of each segment. Using this equation, it is possible to express the total magnetic flux as the summation of partial fluxes from each segment [16].

$$\Phi = \Phi_1 + \Phi_2 + \cdots \qquad 2.26$$

Thus, the inductance of an arbitrary segment of conductor can be expressed as equation 2.26.

$$\Phi_{partial} = \int \mathbf{A} \cdot d\mathbf{l}_{partial}$$

2.27

Combining equation 2.24 with equation 2.27 gives the partial inductance of a current path (equation 2.28).

$$L_{partial} = \frac{\Phi_{partial}}{I} = \frac{\int \mathbf{A} \cdot d\mathbf{l}_{partial}}{I}$$

2.28

Equation 2.28 is extremely useful in practical applications of inductance calculations because it can be used to express inductances that would be cumbersome or computationally impossible to express using the magnetic field [16]. It can be used to calculate the self or mutual inductances of any set of conductors. Equation 2.28 forms the basis of numerous inductance extraction programs, such as FastHenry [17], [18] and FastMaxwell [19].

#### 2.4.3 Partial Inductance of a straight wire

Two important cases of the calculation of partial inductances are the self-inductance of a single wire and the mutual inductance of parallel wires. All current-carrying conductors have a self-inductance and a mutual inductance term between all other conductors in a system which must be added together to form the total inductance of a device.

Perhaps the most important partial inductance formula is the self-inductance of a straight wire (of circular cross section). The formula for the partial inductance of a single straight wire is given by equation 2.29 [16].

$$L_{wire} = \frac{\mu_0 l}{2\pi} \left[ \ln\left(\frac{l}{r} + \sqrt{\left(\frac{l}{r}\right)^2 + 1}\right) - \sqrt{1 + \left(\frac{r}{l}\right)^2} + \frac{r}{l} \right]$$

2.29

Where  $L_{wire}$  is the self-inductance,  $\mu_0$  is the permeability of free space, l is the length of the wire, r is the radius of the wire.

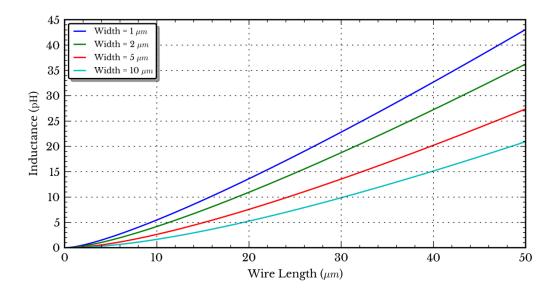

The inductance resulting from equation 2.29 is shown in Figure 2.2 for various realistic on-chip trace lengths and widths. The self-inductance of these wires are trivially small, however, the inductance increases as the trace width is reduced or the trace length is increased. In the case of a long wire, where  $l \gg r$ , then equation 2.29 is reduced to the simpler equation 2.30.

$$L_{wire} = \frac{\mu_0 l}{2\pi} \left[ \ln\left(\frac{2l}{r}\right) - 1 \right]$$

2.30

This equation clearly shows a strong dependence on the length of the wire and a weaker dependence on the radius of the wire. Overall equation 2.31 is approximately linear for each order of magnitude of the ratio l/r.

13

Figure 2.2: Self inductance of a single wire as a function of length. Multiple curves are shown which represent various wire widths as shown in equation 2.29.

The next most important case is two parallel wires, separated by a distance, d. For the same physical reasons as in equation 2.29, the equation is identical, but with  $r \rightarrow d + r_w$  where  $r_w$  is the radius of the wire [16]. The mutual inductance of two wires is then equal to the self-inductance of a single wire of a larger radius, equation 2.31.

$$M = \frac{\mu_0}{2\pi} l \left[ \ln \left( \frac{l}{d + r_w} + \sqrt{\left( \frac{l}{d + r_w} \right)^2 + 1} \right) - \sqrt{1 + \left( \frac{d + r_w}{l} \right)^2} + \frac{d + r_w}{l} \right]$$

$$(2.31)$$

Similarly to equation 2.29, equation 2.31 simplifies if the length of the wires is larger than the radius of the wires and the distance between them. In many cases, the wire radius is much smaller than the separation of the wires. In the case that two small wires are parallel for a long distance, the mutual inductance of the two wires is reduced to equation 2.32.

$$L_{wire} = \frac{\mu_0 l}{2\pi} \left[ \ln\left(\frac{2l}{d}\right) - 1 \right]$$

2.32

#### 2.5 Existing Inductor Types

#### 2.5.1 About

Due to their utility in analog systems, discrete inductors are core components of many electronic systems. Discrete inductors often take the form of wire wrapped in a helix or a toroid and are still widely used today in power systems, such as power transformers. However, to mass-manufacture RF components in an inexpensive fashion, it is necessary to integrate inductors into integrated circuits that can be manufactured in a monolithic fashion. This integration has proven to be difficult, due to the challenges of adapting inductor designs to planar technologies.

In an effort to mitigate the poor performance of modern on-chip inductor designs, various technologies are being developed and demonstrated by researchers: active inductors, microelectromechanical system (MEMS) inductors, and nano-technology-based inductors (nano-inductors).

#### 2.5.2 Helical Coils

In order to analyze the performance of on-chip inductors, it is helpful to understand the principles behind the discrete helical (or toroidal) coils that are used in low-frequency applications.

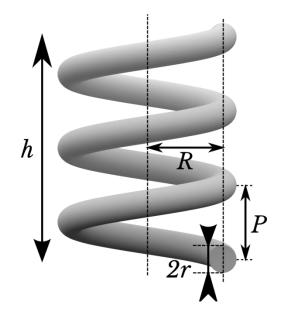

Helical coils (also called solenoids [20, p. 155]) are lengths of wire wrapped around a cylindrical object. Ideal helical coils are simple to analyze analytically and have the well-known result for inductance shown in equation 2.33, where *L* is the inductance of the coil,  $\mu$  is the permeability of the material inside the coil, *N* is the number of turns (i.e. number of times the wire wraps around the core material), *A* is the cross-sectional area of the coil and *l* is the length of the coil [9].

$$L = \frac{\mu N^2 A}{l}$$

2.33

Equation 2.33 is derived under the assumption that there is a single layer of wire wrapped around the core and that the spacing between the turns is small compared to both the radius of the helix as well as the length of the coil [9]. If these conditions are true, then the helix can be analyzed as a cylinder of current that produces a magnetic field inside the cylinder's radius and equation 2.33 is an exact result for the inductance. This well-known result can be used to design helical coils with a large inductance.

If the assumptions about the wire radius, packing and helix radius are not valid, then additional terms are added to equation 2.33. If the coil is a circular coil and it is short, then equation 2.33 must be multiplied by the Nagaoka constant [11].