Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Cntario) K1A 0N4

Your life Votre rélérence

Our file Notre référence

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

**AVIS**

If pages are missing, contact the university which granted the degree.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments. La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# University of Alberta

The High-Performance Distributed Queue Protocol for High Speed MANs.

by

#### Ashvanee Bissonauth

A thesis

submitted to the Faculty of Graduate Studies and Research

in partial fulfillment of the requirements for the degree

of Master of Science

Department of Computing Science

Edmonton, Alberta

Spring 1993

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file Votre référence

Our lile Notre référence

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive Bibliothèque la permettant nationale du Canada reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette à la disposition des personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

# UNIVERSITY OF ALBERTA

# RELEASE FORM

NAME OF AUTHOR: Ashvance Bissonauth

TITLE OF THESIS: The High-Performance Distributed Queue Protocol for

High Speed MANs.

DEGREE: Master of Science

YEAR THIS DEGREE GRANTED: 1993

Permission is hearby granted to the UNIVERSITY OF ALBERTA LIBRARY to reproduce single copies of this thesis and to lend or sell such copies for private, scolarly or scientific research purposes only.

The author reserves other publication rights, and neither the thesis nor extension extracts from it may be printed or otherwise reproduce without the author's written permission.

(Signed)

25 Avenue Des Rosiers,

Quatre-Bornes.

MAURITIUS.

Date: 19/03/93

## UNIVERSITY OF ALBERTA

## FACULTY OF GRADUATE STUDIES AND RESEARCH

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies and Research, for acceptance, a thesis entitled The High Performance Distributed Queue protocol for High-Speed Metropolitan Area Networks submitted by Ashvanee Bissonauth in partial fulfillment of the requirements for the degree of Master of Science.

Supervisor: Dr A. Kamal

External: Dr G.D. Cormack (Dept. of Elect. Eng.)

Examiner: Prof. U.M. Maydell

Chair: Dr L.Y. Yuan

Date: March 2/93.

#### **Dedication**

In recognition of the unconditional love and belief that my family have shown me over the past six years, I dedicate this thesis to them.

To my father, Oomahshankar.

whose dream it was that I should achieve an M.Sc. degree.

To my mother, Kamlaotee,

and grandmother, Chando,

whose emotional support comforted me.

And finally to my sisters,

Asvina and Aruna,

who have missed me, written to me and included me in their lives even though I was away.

I thank you all.

#### ABSTRACT

The IEEE 802.6 committee has adopted the DQDB as the standard metropolitan area network. Studies of this network have shown that the behavior of the DQDB medium access control is unpredictable in the sense that bandwidth may be distributed unfairly among nodes. This anomalous behavior is not only present under unipriority type of operation, but also between nodes operating at different priority levels. Remedial corrections to the MAC protocol have been proposed in the literature, in addition to alternative network protocols.

This thesis proposes a novel network protocol, the High-Performance Distributed Queue (HPDQ). The network is based on the double bus topology and is capable of operating at a rate of multi gigabits per second. The objectives behind the design of this protocol are to provide equitable access and reliable operation. Fluctuations in network activities should have negligible impact on the network operation by redistributing the bandwidth among the active nodes within the same priority level. The protocol also implements priority by allowing higher priority nodes to discriminate against lower priority ones in terms of bandwidth offering. The protocol should also subscribe to the class of network protocols offering integrated access and service of multiple services.

The principle of operation of HPDQ protocol is fundamentally differ-

ent from other protocols. It requires nodes to maintain essential information about activities downstream, such as the number of active nodes, and their aggregate bandwidth requirements. Additionally, the network nodes must be equipped with active taps, which allow the modification of data observed on the bus. Through the proper handling of this pair of information items by the protocol, the protocol is capable of satisfying the above objectives.

To demonstrate the validity of the above claims, a simulation study was undertaken to assess both the steady state performance and the transient behavior of the HPDQ. By analysing several important scenarios, it is shown that the results establish that the objectives of the protocol have been met.

#### Acknowledgments

I would like to express my gratitude to my supervisor Dr A. E. Kamal for his exemplary guidance in my research work, for devoting quality time into proof reading my thesis and for providing me with financial support. My thanks to the members of my examining committee for their comments and suggestions to improve the quality of my thesis.

The help that I have received from the staff of the Department of Computing Science should not be left unmentioned. I would like to thank the Department for their support without which the completion of this thesis might not have been possible.

My sincere thanks also go to my father who gave me the opportunity to study in Canada. His dedication in writing to me weekly for the past six years, his understanding and guidance have provided me with great moral and emotional support at times when I most needed them.

Lastly, I would like to thank my friends Aditya K. Ghose, Suryanil Ghosh, Ramesh S. Sankaranayana, Florence Lehmann and Audrey Smith for making life outside the university so pleasant. Their friendship is most appreciated. They will always have a very special place in my heart.

# Contents

| 1 | IN  | rrod   | UCTION                                      | 1  |

|---|-----|--------|---------------------------------------------|----|

|   | 1.1 | Comp   | outer Networks                              | 4  |

|   | 1.2 | Intro  | luction to MANs                             | 5  |

|   |     | 1.2.1  | Architecture of a MAN                       | 5  |

|   |     | 1.2.2  | Early proposals for a MAN standard          | 7  |

|   |     | 1.2.3  | Media Access Protocol for DQDB              | 9  |

|   | 1.3 | Proble | ems with the DQDB MAC protocol              | 15 |

|   |     | 1.3.1  | Heavy loading by an initial heavy user      | 15 |

|   |     | 1.3.2  | Heavy Loading Initiated by a group of users | 17 |

|   |     | 1.3.3  | Node Stopping Transmission                  | 18 |

|   |     | 1.3.4  | Unfair behavior in the priority mechanism   | 18 |

|   |     | 1.3.5  | Bandwidth Balancing Mechanism               | 21 |

|   | 1.4 | Other  | Proposals                                   | 23 |

|   |     | 1.4.1  | Distributed Queue Multiple Access (DQMA)    | 24 |

|   |     | 1.4.2  | Cyclic Reservation Multiple Access protocol    | 26 |

|---|-----|--------|------------------------------------------------|----|

|   |     | 1.4.3  | Cyclic Reservation Multiple Access II protocol | 28 |

|   |     | 1.4.4  | Fair Distributed Queue protocol                | 30 |

|   | 1.5 | Summ   | ary                                            | 32 |

|   | 1.6 | Thesis | Overview                                       | 33 |

|   | 1.7 | Thesis | Outline                                        | 34 |

| 2 | ME  | DIUM   | ACCESS PROTOCOL FOR HPDQ                       | 36 |

|   | 2.1 | Object | tives                                          | 36 |

|   | 2.2 | Descri | ption of HPDQ                                  | 37 |

|   | 2.3 | The E  | nhanced HPDQ Protocol                          | 44 |

|   | 2.4 | Netwo  | rk Aspects                                     | 50 |

|   |     | 2.4.1  | Performance issues                             | 50 |

|   |     | 2.4.2  | Implementation Cost and Complexity             | 52 |

|   | 2.5 | Summ   | ary                                            | 54 |

| 3 | PE  | RFOR   | MANCE ASPECTS                                  | 55 |

|   | 3.1 | Simula | ation of the Basic Protocol                    | 57 |

|   |     | 3.1.1  | Steady state analysis                          | 57 |

|   |     | 3.1.2  | Transient analysis                             | 60 |

|   | 3.2 | Simula | ation of the Enhanced Protocol                 | 66 |

|   |     | 3.2.1  | Transient analysis                             | 66 |

|   | 3.3 | SUMN   | MARY                                           | 67 |

| 4 | Pri                                     | ority Implementation                                           | 69  |

|---|-----------------------------------------|----------------------------------------------------------------|-----|

|   | 4.1                                     | Introduction and Background                                    | 69  |

|   | 4.2                                     | Priority Scheme for HPDQ                                       | 73  |

|   | 4.3                                     | The Buffering System                                           | 80  |

|   | 4.4                                     | Summary                                                        | 86  |

| 5 | Performance of the HPDQ priority scheme |                                                                |     |

|   | 5.1                                     | Nodes with different starting time and positions               | 89  |

|   | 5.2                                     | Nodes of the same priority level                               | 90  |

|   | 5.3                                     | Effect of distances on performance of nodes under heavy load . | 97  |

|   | 5.4                                     | SUMMARY                                                        | 100 |

| 6 | СО                                      | NCLUSIONS and DIRECTIONS for FUTURE                            |     |

|   | RE                                      | SEARCH                                                         | 103 |

# List of Figures

| 1.1 | MAN with access and transport subnetworks               | (          |

|-----|---------------------------------------------------------|------------|

| 1.2 | Networks interconnetion                                 | 10         |

| 1.3 | DQDB network configuration                              | 11         |

| 1.4 | DQDB Access Control Field Format                        | 13         |

| 1.5 | Transfer of segments                                    | 13         |

| 1.6 | Nodes of different priorities                           | 20         |

| 2.1 | HPDQ network configuration                              | 38         |

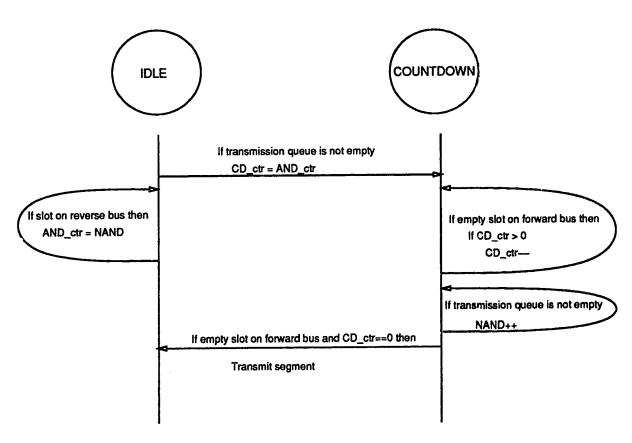

| 2.2 | Finite State Machine for Basic HPDQ protocol            | <b>3</b> 9 |

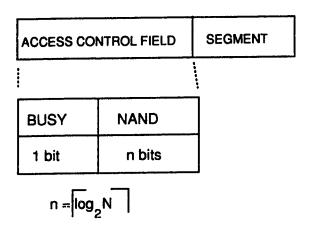

| 2.3 | Slot format for basic HPDQ                              | 40         |

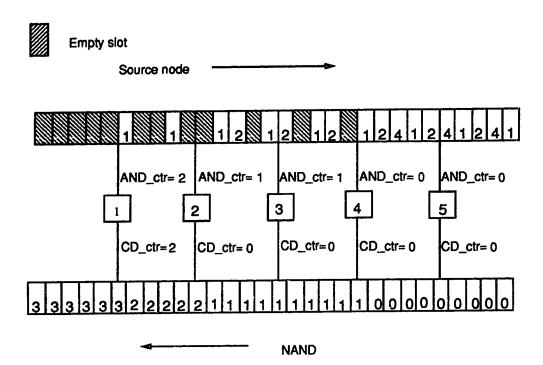

| 2.4 | Basic operation of HPDQ                                 | 42         |

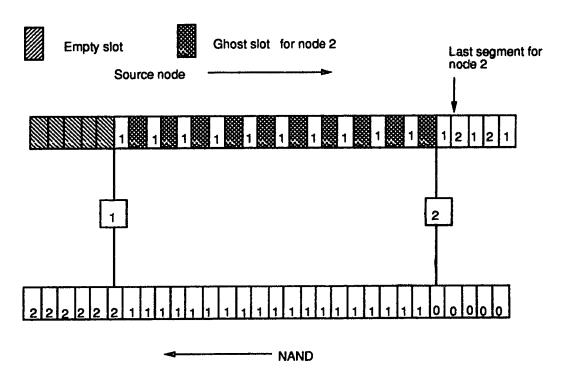

| 2.5 | Node 2 stops updating at completion of its transmission | 43         |

| 2.6 | Bandwidth loss due to stopping of transmission          | 45         |

| 2.7 | Slot format for enhanced HPDQ                           | 46         |

| 2.8 | Finite State Machine of Enhanced HPDQ protocol          | 47         |

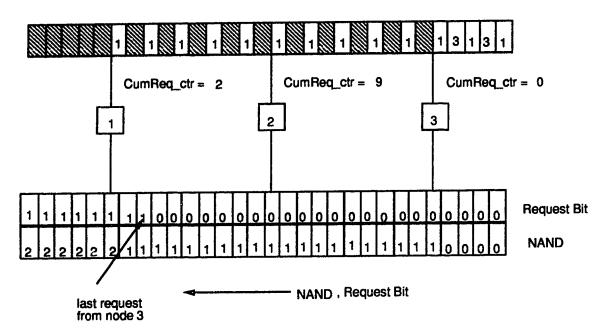

| 2.9 | Operation of the CumReq_ctr counters                    | 48         |

| 2.10 | Bandwidth distribution due to node stopping transmission     | 49 |

|------|--------------------------------------------------------------|----|

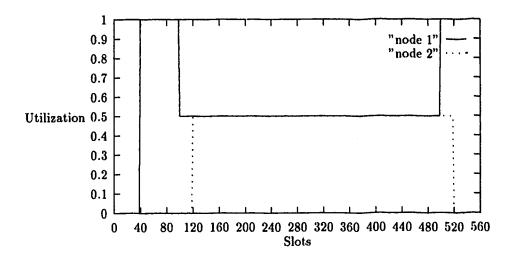

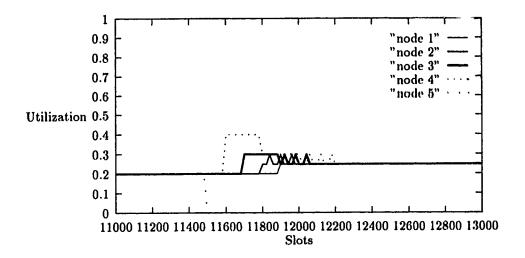

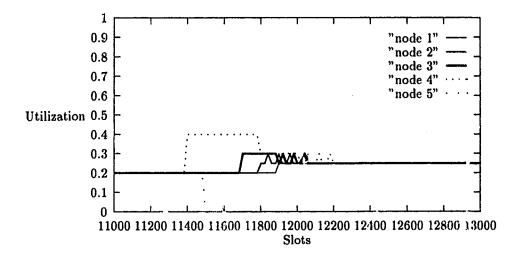

| 3.1  | Transient utilization of nodes starting from left to right   | 62 |

| 3.2  | Transient behavior of nodes at different distances from each |    |

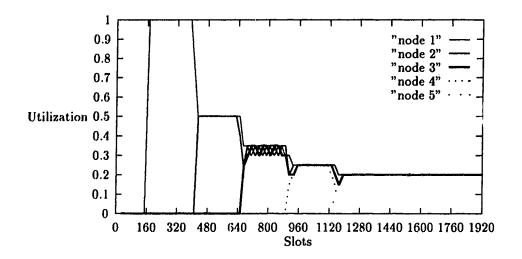

|      | other                                                        | 63 |

| 3.3  | Transient utilization of node 5 leaving the system           | 65 |

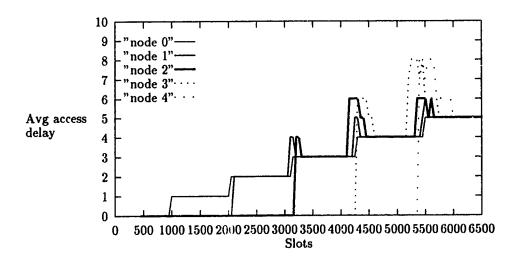

| 3.4  | Transient utilization of node 5 leaving the system (Enhanced |    |

|      | HPDQ)                                                        | 67 |

| 4.1  | Finite state machine for nodes' operation on the reverse bus | 75 |

| 4.2  | Finite state machine for nodes' operation on the forward bus | 76 |

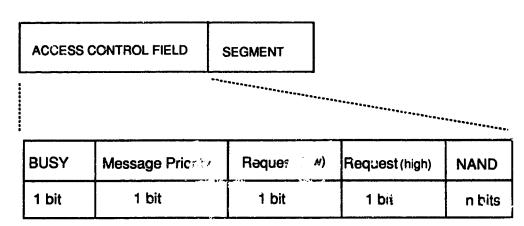

| 4.3  | IIPDQ Access Control Field format                            | 77 |

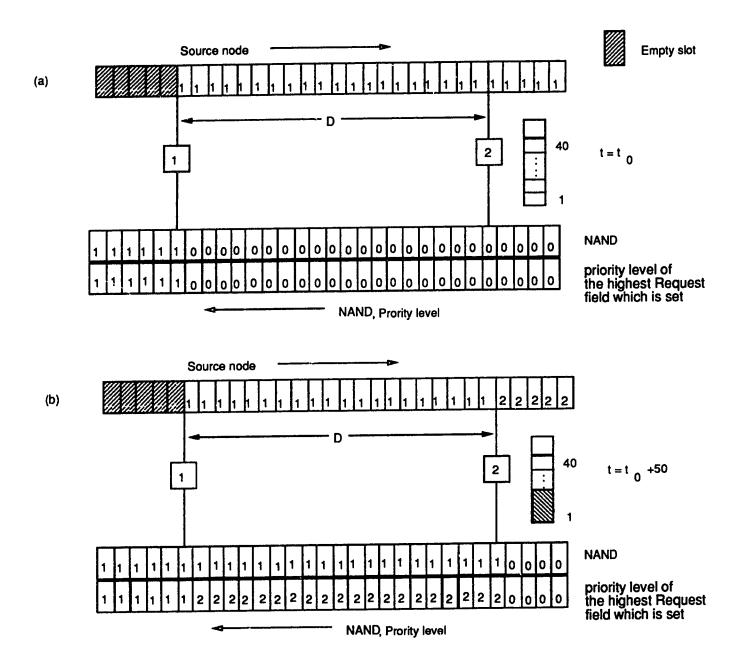

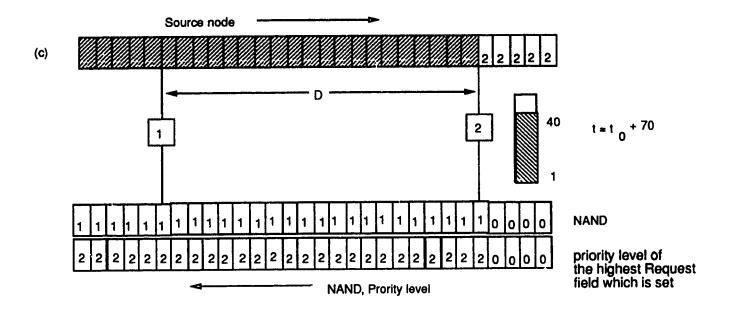

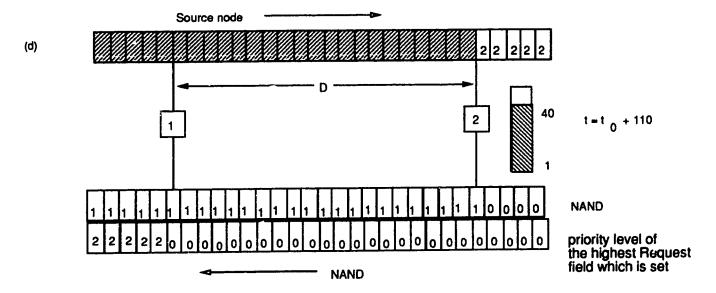

| 4.4  | High priority node leaving the system                        | 85 |

|      |                                                              |    |

# List of Tables

| 3.1      | Maximum bus length for throughput fairness                       | 58         |

|----------|------------------------------------------------------------------|------------|

| 3.2      | Node utilization.                                                | 58         |

| 3.3      | Access Delay                                                     | 59         |

| 3.4      | Utilization for different initial heavy users                    | 60         |

| 3.5      | Summary of system                                                | 62         |

| 3.6      | Utilization at 660                                               | 62         |

| 3.7      | Utilization at 680                                               | 62         |

| 3.8      | Summary of system                                                | 63         |

| 4.1      | Summary of $\alpha$                                              | <b>7</b> 9 |

| 4.2      | Summary of AND_ctrs update                                       | 79         |

| 5.1      | Average utilization and average access delay for various speeds. | 90         |

| 5.2      | Utilization for scenario 1                                       | 92         |

| <b>5</b> | Average access delay for HPDO under scenario 1                   | 93         |

| 5.4  | DQDB with priority and without Bandwidth Balancing Mech-           |

|------|--------------------------------------------------------------------|

|      | anism                                                              |

| 5.5  | DQDB protocol with Global priority scheme                          |

| 5.6  | Utilization for HPDQ under scenario 2 95                           |

| 5.7  | Transfer time for HPDQ under scenario 2 96                         |

| 5.8  | Internode distances of network of 5 nodes                          |

| 5.9  | Performance results for nodes at different internode distances. 98 |

| 5.10 | DQDB: Throughput distribution for different priority config-       |

|      | urations (seven users, balancing ratio 8/9) 100                    |

| 5.11 | HPDQ: Throughput distribution for different priority config-       |

|      | urations                                                           |

# Chapter 1

# INTRODUCTION

Since the beginning of time, man has been pushing back the barriers of reality. We have migrated from the stone age, through the machine age into the information age. Indeed, the twentieth century is about gathering, processing and distributing information. The unprecedented growth of the computer industry is a definite manifestation of a new era.

During the first couple of decades of this computer age, computers were of a centralized nature. They were accessible to a small privileged portion of the world population. Today, besides becoming more accessible, computers are getting more decentralized. The decentralization is closely linked to the merging of computers and communications. This bonding has permanently influenced the way the computer system is organized and has led to the merger between the communication and the computer industries

creating what has become known as the computer network.

In general terms a computer network can be defined as an interconnection of a collection of autonomous computers [18] and its purpose is to share resources, provide a higher reliability and extend the scale of cost effectiveness.

In the early days of computers, the computer industry had to advertise for the services that computers are able to provide as people were unaware of its potential. Today, the computer industry has overwhelmed people who are willing to pay for the many services that it provides [1]. These services can be integrated together and an International Committee has been set up to look into this integration. The CCITT (Consultive Committee for International Telephony and Telegraph) has been developing and standardizing the ISDN (Integrated Services Digital Network) since mid 1970's [5, 21, 1] which has eventually evolved into BISDN (Broadband Integrated Services Digital Network) [21, 6, 1]. The following (incomplete) list depicts the services that BISDN would provide to the different applications in the future:

#### Communication of data, text, graphics.

- Data transfer (burst, stream)

- Document transfer

- document filing and retrieval

#### Person to person video communications.

- Video telephony (including showing documents etc)

- Video conference

- Broadband message handling

#### Access to video information.

- Broadband videotex

- Video on demand

#### Broadcast of programs and data.

- Common TV

- Pay TV (pay per channel, pay per view)

- High-definition television (HDTV)

- Cabletext

In order to be able to provide this impressive list of services in a cost effective manner, a unified data transport service must support all these applications. Among other alternatives, a new multiplexing scheme known as Asynchronous Transfer Mode(ATM) [16, 3, 20], has been adopted as the transport mechanism BISDN. ATM can be thought of as a multiplexing and switching techniques confined to layer 1 and basic functions of layer 2 of the OSI model. ATM is based on the use of fixed length packets, 53 octets called cells. Out of these, 48 octets are used for data, while 5 octets are used as a header. One of the main features of ATM is its use of highly simplified protocols, which is useful in high speed network.

# 1.1 Computer Networks

From a geographical-coverage viewpoint, computer networks can be classified into three main classes, namely Local Area Networks(LAN), Wide Area Networks(WAN) and the more recent Metropolitan Area Networks(MAN). A LAN is a communication network that provides interconnection of a variety of devices such as computers, terminals and peripherals within a limited geographical area(e.g. LAN can be used to connect several machines on different floors in a building). LANs are based on a shared medium that runs at a sufficiently high speed to accommodate needs of many users at once. LANs differ from the other networks in that they span shorter distances, typically a few kilometers, have high data rates, low error rates, simpler routing, are owned and used by a single organization and have lower communication costs [4]. At the other end of the spectrum, we have the WAN which spans several hundred kilometers. For WANs the RS-232 interface has served as a fixed point through which the great bulk of data transmission has passed in the past two decades. WANs have lower data rates, more complex routing mechanisms and are not necessarily used by the central body that owns it. LANs and WANs shall not be discussed any further as the rest of this thesis is concerned with MANs.

### 1.2 Introduction to MANs

Metropolitan Area Networks inherit characteristics from LANs and WANs. MAN started as an extension of LAN, but its size and scope dictate that it be operated by a central body. In essence, a MAN is a large LAN with access protocols less sensitive to network size than those used by LANs. As MAN will serve more users, interconnect both LANs and large computers, it must provide higher bandwidth. With high data rates, it will be capable of supporting data, voice and video communication services.

In this section the MAN architecture shall be described followed by a review of some of the earlier proposals for a MAN standard. Thereafter, the current standard for metropolitan area networks shall be discussed and end with more recent proposals for medium access protocols for MANs.

#### 1.2.1 Architecture of a MAN

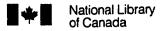

MAN installation can be either public or private [14]. The private MAN is analogous to the dedicated line; it is leased to a single company to connect a number of sites in a metropolitan area. Large organizations can afford a dedicated line but this is not justifiable for small ones. A public MAN is divided into two parts: an access network and a transport network, as shown in Figure 1.1., [14]. The access network terminates at the customers' premises

Figure 1.1: MAN with access and transport subnetworks

and is bridged to the transport network at the Medium Access Control level. The transport network is therefore invisible to the customer's equipment. The bridge must recognize present addresses on the transport network and selectively pass the data on to the access network. Similarly, outgoing data are transferred to the transport network. The access network can be another segment of the MAN network, or can be an IEEE 802 LAN (such as covered by standard IEEE 802.3 which applies to the ETHERNET system) that internally serves the building's occupants. Because of the growing importance of MANs, the need for a standard for metropolitan area networks was recognized as early as 1981 by the IEEE's Project 802, the standardization body for LANs. The specific standard for MAN s is now designated IEEE 802.6. Several proposals to be covered have been considered for inclusion in a MAN standard over the last decade. Some of those proposals are reviewed next.

# 1.2.2 Early proposals for a MAN standard

Unless a standard interface between the network and the customer premises equipment exists, interconnection of different vendor equipment becomes impossible. MANs are therefore being standardized under Project 802.6 whose goal is to come up with a MAN standard that will provide a two-way interchange of digital bit streams using a shared medium between

nodes located within an area that is typically up to 50 kilometers in diameter. A standard should support services that require guaranteed bandwidth and constrained delay. The range of transmission rates should extend from 1 Mbps to the appropriate limits of the medium used.

The first proposals for MANs were based on time division multiplexing protocols, similar to those used by multiple ground stations to access a satellite channel. Unfortunately, this protocol's original growth or profitability expectation were never reached. Another proposal that was also based in a radio system which is already in production was brought in by Motorola but was rejected because its data rate fell below the Project 802 threshold of 1 Mbps. Yet, another proposal used the FDDI token ring protocol for data packets and superimposed a set of 64 kilobits/sec slots for isochronous traffic. The fixed 100 Mbps speed of FDDI was modified to match the speeds of the telephone industry's transmission hierarchy, ranging from 1.544 Mbps for T1 to approximately 155 Mbps which is the **T** channel of the SONET standard.

Telecom Australia submitted a competing proposal at the same time. The protocol that they put forward, called QPSX for Queued Packet for Synchronous Exchange, was unique. It is based on two unidirectional busses running in opposite directions. Writing to the bus is only possible in unused slots. Scheduling is done by sending reservations upstream when a station wants to transmit downstream. Each station has a pair of counters which forces stations to transmit under specific conditions only, as will be discussed

in the next section 1.2.3.

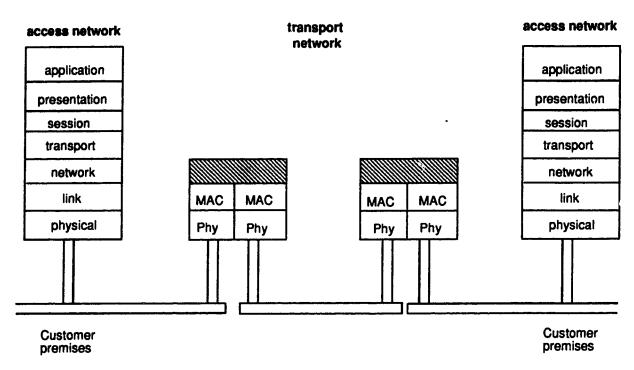

In November 1987, a consensus emerged within the IEEE Project 802 to use a modified version of QPSX, better known as the Distributed Queue Dual Bus(DQDB) as the medium access protocol to be used for standardizing MANs. A few years later, the IEEE 802.6 committee approved DQDB network as the standard Metropolitan Area Network. The media access protocol for DQDB will now be described in detail, followed by a discussion of some of its anomalous aspects of behavior. Figure 1.2 shows how the DQDB network fits in the communication system. In this example, it is shown that two 802.6 MANs can be connected by bridges. Gateways are used to connect 802.6 MAN to LAN or WAN.

#### 1.2.3 Media Access Protocol for DQDB

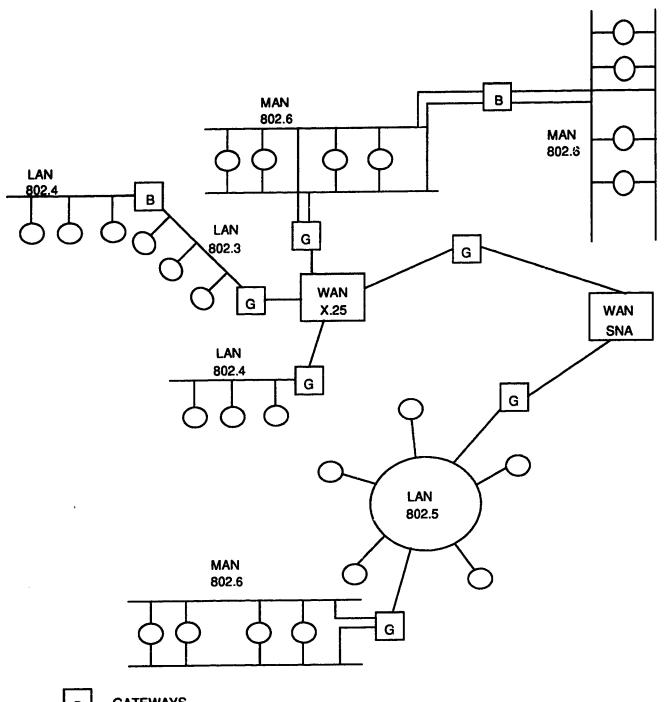

The network configuration of the DQDB protocol is shown in Figure 1.2. It consists of a pair of unidirectional busses serving opposite directions. Since the operation of the node is the same on both busses, only the operation of the node on one bus, bus A, shall be considered without loss of generality. Bus A shall be referred to as the forward bus, while bus B shall be called the reverse bus. The operation is slotted and at the head of each bus a special station referred to as the head end station is responsible for

**GATEWAYS**

BRIDGES

#### connection points

Figure 1.3: DQDB network configuration

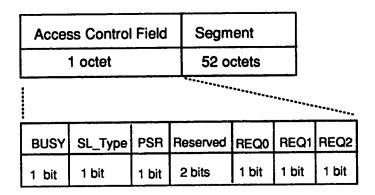

generating frames which are subdivided into fixed length slots. The duration of a frame is  $125~\mu s$  (sampling period used in digital telephony). A frame is subdivided into fixed length slots. The slot format is shown in Figure 1.4. The busy bit indicates whether a slot is used or unused. The SL\_Type bit indicates whether the slot is a Queued Arbitrated (used for asynchronous transmission) or Pre\_Arbitrated (used for isochronous transmission). The PSR bit indicates whether the segment in the previous slot may be cleared or not. A request bit is set to indicate that a station is requesting a slot on the other bus. Three such bits exist to implement three different priority levels. The slots can be used to transmit both synchronous and asynchronous traffic. The network controller (head station) reserves some slots of a frame

for synchronous use and allocates them to stations that have requested synchronous packets. Slots not reserved for synchronous circuits are available for packet switched communication. The access to the slots is determined according to the DQDB medium access protocol. In this section only Queued Arbitrated traffic is considered.

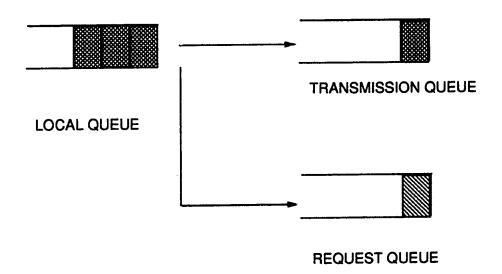

The unipriority DQDB medium access protocol is discussed first. On both busses, a node can send data to downstream nodes and receive data from upstream nodes, or vice versa. Therefore, nodes need to maintain information about their relative positions on the network. Existence of the two busses running in opposite directions allows nodes to send requests on one bus to inform the upstream stations on the other bus of their intention to send data on the latter. User data is segmented to fit into slots and are kept in a local queue. Segments are transmitted on a FIFO basis. The segment at the top of the local queue is moved to the transmission queue, once the latter is empty. At the same time a request is enqueued for transmission on the reverse bus. The transmission queue can hold only one segment, Figure 1.5.

In the DQDB protocol [3] a distributed queue is implemented by a pair of Request and CountDown counters foe each bus. When a node has a segment ready for transmission, it enqueues a self request for transmission on the reverse bus. The request is transmitted in the next empty request field on the reverse bus. A node also observes request bits on the reverse bus and

Figure 1.4: DQDB Access Control Field Format

Figure 1.5: Transfer of segments

increments the value of its Request Counter by 1 to keep track of the number of segments ready for transmission by downstream stations. This implements a distributed queue. To insert its own segment in the queue, a node transfers the content of its Request Counter to the CountDown counter, and resets the former to zero. An empty slot on the forward hus causes the CountDown Counter to be decremented by one until it reaches zero. At this point, the node is allowed to transmit its segment in the next available empty slot. After doing so, another segment from the local queue may be moved to the transmission queue and the whole process will be repeated. Under light load, the basic DQDB protocol behaves reasonably well and is fair to all nodes. Unfortunately problems emerge as the load becomes heavier [22, 27, 8].

According to the latest version of the standard, DQDB supports three priority levels [3]. This is achieved by placing three request bits in each slot and having a set of counters for each level of priority. The basic DQDB protocol is extended by letting a free slot decrease the counters of all three priority levels. At the same time, a passing request of priority *i* increments the request counter for that priority level, but increments all Request Counters of lower priorities for which no data is scheduled and all CountDown Counters for which data is scheduled. Just like in the basic protocol, under light load the priority mechanism works but is inefficient under heavy load [22, 27, 8, 12]. Thus, the priority mechanism fails to work properly. In the next section we shall elucidate on these problems and discuss some of the

- -

proposed solutions.

# 1.3 Problems with the DQDB MAC protocol

Under light load, the DQDB protocol behaves reasonably. Unfortunately, its behavior is not flattering at heavier loads. We shall define a network to be under heavy load if the number of segments queued up for transmission is enough to keep the entire bus busy. In the following section, we have chosen various scenarios to bring up the drawbacks of the DQDB protocol.

## 1.3.1 Heavy loading by an initial heavy user

In this section, heavy load nodes at different positions on the network with different starting times are discussed. These cases were investigated in references [22, 10, 27, 2, 7, 13]. As reported in those references, the initial heavy user is definitely the largest consumer of the bandwidth. This unfair behavior becomes more severe the closer the initial heavy user is to the headend. Besides, the faster the speed or the shorter the bus length, the higher the throughput of the initial heavy user node.

The reason for this unequal distribution of throughput is due to the

the initial node has flooded the forward bus with its segments and the reverse bus with its requests, the other nodes are forced to transmit in a certain pattern. Upstream stations from the initial heavy user record requests while transmitting their segments. When upstream station let empty slots pass by on the forward bus for downstream stations, upstream stations record more requests on the reverse bus from initial heavy user stations. Consequently, upstream stations transmissions are scheduled further apart after each of their transmissions. This process is repeated for some time and is subsequently partially suppressed by requests sent from nodes downstream from the initial heavy user. Eventually these two opposing forces stabilize the system and provide the initial heavy user with the largest share of throughput. The steady state throughput rate for two nodes can be described by the following equations [10]:

$$\gamma_1 = 2/(2 - D - C(\delta) + ((D - C(\delta) + 2)^2 + 4DC(\delta))^{1/2})$$

$$\gamma_2 = 1 - \gamma_1$$

$\gamma_1$  and  $\gamma_2$  are the nodal throughputs at nodes 1 and 2, respectively. D is the distance in slots between the two nodes.  $\delta$  represents the phase difference in the arrival times at the slots from the two nodes, measured in slot times. Note that if D=0 or  $\delta$ =0, the nodal throughput is evenly distributed

between the two nodes.

It has also been reported in [22] that the same kind of dominance, though to a lesser extent, prevails if there is a group of nodes at light load and a single heavy user bursting in.

## 1.3.2 Heavy Loading Initiated by a group of users

Next, we consider the case where nodes start quasi simultaneously (within a small time interval) such that a node starts before seeing either busy slots on the forward bus or requests on the reverse bus. In [22, 9, 26], it was reported that in such cases the end nodes hold the largest share of the bandwidth, more or less equally divided amongst them. Intermediate nodes, on the other hand, consume a significantly lower share of the bandwidth. This share increases with increasing speed.

[22, 9, 26] provides a detailed description of why the system behaves in this way. Suffice to say that the unfair behavior is an extension of the effect discussed in the previous section. Intermediate nodes are suppressed by both downstream and upstream stations. Requests from downstream stations forces intermediate nodes to increment their Request counters. On the other hand, segments from upstream stations prevent intermediate nodes from transmitting segments. Therefore, segments transmission from intermediate nodes are delayed further and their throughputs fall below those of

nodes at the ends of the network.

## 1.3.3 Node Stopping Transmission

In this last case, we shall report the effects of a dominating heavy user stopping transmission. This case was studied and results reported in [22] and it was found that the bandwidth released is equally divided between the two adjacent nodes. The adjacent nodes acquire a considerably greater bandwidth share than the other active nodes. It is plausible to infer that they shared the released bandwidth by the stopping node. The other nodes do not seem to benefit considerably from that node's completion of transmission. Reference [22] provides a detailed explanation of how the bandwidth redistribution happens. The redistribution is attained by the dynamic relation that builds up between the bandwidth released by the node stopping transmission and the adjacent nodes' requests.

## 1.3.4 Unfair behavior in the priority mechanism

The unfairness problem associated with the DQDB network is persistent even when dealing with priorities [22, 11, 3, 19, 17]. Upstream nodes of lower priority can grab more bandwidth than downstream higher priority nodes, under heavy load. Also, it might happen that changing to higher

priority inadvertently causes low priority initial heavy user to get even more bandwidth. Next, we shall demonstrate these cases.

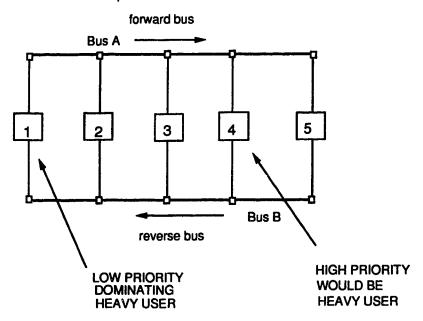

Consider the case where we have a 150 km network of 5 nodes that are evenly spaced. Assume that we have node 1 as a low priority dominating heavy user. Furthermore, let us assume that node 4 is the high priority would be heavy user, Figure 1.6. Despite node 4 being a higher priority user, it cannot attain its fair share of the bandwidth. Since the bus is already flooded with segments from node 1 when node 4 starts, node 4 is inhibited from transmitting which in turn inhibits requests from being issued on the reverse bus. The only time node 1 lets an empty slot go by is when it identifies a request of a higher priority. It increments its CountDown counter (rather than its Request counter) by one which enforces node 1 to let one slot pass by untouched. This clearly demonstrates that node 4's throughput is dependent on the round trip propagation delay between these two nodes.

In addition to the aforementioned problems, it may also happen that when a node changes its priority level form low to high, the node witnesses a decrease in its throughput. This phenomenon is called the inverse priority effect which is caused by the bunching effect [22]. Bunching effect usually happens when heavy users start quasi simultaneously and it so happens that the free slots on one bus and the requests on the reverse bus forms a special time relationship. This allows the low priority heavy user node closer to the high priority heavy user node to transmit more slots in a batch mode at the

#### - connection points

Figure 1.6: Nodes of different priorities

expense of the high priority node.

All the scenarios and investigations presented clearly show that the basic DQDB protocol is unfair under heavy load. Since bursty traffic is unpredictable, it is hard to anticipate the behavior of the node. The unfairness seems to become more profound as the network speed or the network size increases, because the throughput dominant nodes can exert a greater domination as there are more slots available to them or there are more slots they can take from the vulnerable nodes.

#### 1.3.5 Bandwidth Balancing Mechanism

In this procedure, a node is allowed to transmit only a fraction,  $\alpha$ , of the time before it artificially increments the Request counter by one for every M segments that it transmits. This M is referred to as the BWB modulus and its value influences the system behavior. The increment operation is achieved by using an additional counter called the trigger counter which keeps track of the number of segments transmitted. As reported in [10], this scheme does prevent throughput dominance by a single user when other users have heavy load traffic demands. However, a fraction of the bandwidth is lost due to passing extra empty slots downstream, which may not be necessarily used. The fraction of bandwidth loss is given by  $(1 - \alpha)/(1 + \alpha)$ , where  $0 \le \alpha < 1$ . A small value for  $\alpha$  means that more bandwidth will

be lost. On the other hand, a greater value of  $\alpha$  results in less bandwidth wastage, but at the same time slows down convergence to a fair bandwidth distribution among nodes. That is, as the bandwidth balancing modulus M or  $\alpha$  increases, the steady state nodal throughputs increase, but it takes longer to reach the steady state [13]. Reference [13] contains an example with 2 nodes separated by a distance D with  $\alpha = 0.9$  (the node will transmit 9 segments out of every 10 times that its CountDown Counter reaches zero). In that example, it takes 22D slots time for the throughput to reach the 90% steady state throughput. It was also reported that the convergence to a fair distribution of the bandwidth among nodes depends on  $\alpha$  only. The mechanism can still maintain unfair behavior owing to long transients needed to achieve balancing [21, 8, 21, 13]. However, the BWB mechanism provides a definite improvement over the basic DQDB protocol [10]. This is achieved at the expense of losing some bandwidth. In fact, wasting a small fraction of the bandwidth allows implicit coordination among the nodes. The BWB mechanism is in a way a rate control procedure.

Bandwidth balancing was originally proposed for single priority traffic. In [12] modifications to adapt the BWB mechanism to multi-priority traffic is discussed. The three modifications that are described in [12] are bandwidth balancing over nodes using local priority information, bandwidth balancing over parcels using local priority information and finally bandwidth balancing over parcels using global priority information. In this case local information means that nodes will transmit segments of priority  $\mathbf{P}$  using a modulus  $M_{\mathbf{p}}$  based on the traffic load of that priority level, whereas in global information, nodes will transmit segments of priority  $\mathbf{P}$  using a modulus of  $\mathbf{M}$ . Among these, bandwidth balancing over parcels using global priority information is the most effective and it will be the only scheme presented here. Unfortunately, Global priority information does have more communication and computation overhead than the others. In this scheme, every node can determine the bus utilization due to traffic of each priority level. Each parcel is forced to limit its throughput to some multiple  $\mathbf{M}$  of the spare bus capacity not used by parcels of equal or greater priority. A node with less demand can have all the bandwidth they desire. The IEEE 802.6 committee has not yet adopted any scheme for multi- priority operation and this issue is therefore still an open area of research.

### 1.4 Other Proposals

In this section, new proposals based on DQDB for media access protocols for Metropolitan Area Networks will be discussed. As it is not possible to review all proposals, since there are too many of them, a sample of the more prominent and relevant ones are included in this section. All these new protocols have one basic set of objectives. They would like to achieve:

- full bandwidth utilization,

- fairness among nodes,

- minimum possible access delay, and

- efficient priority implementation.

#### 1.4.1 Distributed Queue Multiple Access (DQMA)

Distributed Queue Multiple Access (DQMA) protocol is a generalization of the DQDB protocol. In the DQDB protocol, a node can enqueue at most one request in one slot, whereas in DQMA, a node can enqueue several requests in the same slot. In order to do so, DQMA has an access control field of two bytes out of which eight bits are for requests. Therefore, a node can transmit up to 255 requests. When a node has a packet to transmit, it has to send requests on one bus and segments on the opposite bus. Requests can be sent only if the request field of a slot is empty, otherwise the request transmission is delayed until such a slot is found. After sending a request, a node will enqueue the *local request* in its request queue. This queue also holds external requests. which are enqueued if the node identifies a slot with a nonzero request field. The request queue is served on a FIFO basis. If an external request is at the top of the queue, then every time an empty slot passes by, the external request is decremented by one until it reaches zero.

On the other hand, if the *local request* is at the top of the queue, the node uses all empty slots to transmit its segments. It also decrements the *local request* by one for every segment that it transmits. When the request at the top of the queue reaches zero, the request is deleted. Since the average number of requests per slot is greater than one, some constraints are necessary to keep the request bounded. This is achieved by having an access window that monitors the number of request transmissions. In DQMA, although nodes send multiple requests in a single slot, there is still no guarantee that the segments will be transmitted in contiguous slots. In order to obtain contiguous transmission, DQMA has a request delay equalization scheme [28]. In short, every external or local request which is read in is delayed by at least one round trip propagation delay with the headend before they are moved to the request queue. This enables nodes to make contiguous transmissions.

As reported in [28], this protocol enables the system to achieve fairness in throughput distribution even at high speeds and large distances. Reservation of multiple consecutive slots is a new concept introduced by this kind of network and makes segment labelling unnecessary. It also facilitates reassembly significantly as segments from the same node are received consecutively. To provide contiguous slots, it was necessary for nodes to have consistent view of the state of the network. This was achieved at the cost of introducing a delay before *local request* and *external request* before they can be moved to the request queue. Since the delay has to be at least one round trip

propagation delay, this means that the minimum access delay for a segment would have to be at least one round trip propagation delay too. For some types of data traffic, e.g., voice and video, such a delay could be detrimed to the applications. DQMA can be extended to enable segments for immediate access. However, that will leave the system with no guarantee of transmitting slots consecutively.

## 1.4.2 Cyclic Reservation Multiple Access protocol

Cyclic Reservation Multiple Access (CRMA) is yet another scheme for a metropolitan area network based on slotted unidirectional bus structure. The bus can be either a dual or a folded one. The 2 bytes access control field contains a 13 bit access command subfield. Out of the remaining three bits two are unused and one is used to indicate the status (busy/free) of the slot. There are two main access commands: reserve and start. The reserve command contains cycle number and cycle length as its arguments. The headend generates periodically reserve commands by setting the cycle length to zero. In this scheme a node can reserve multiple slots. This is attained by increasing the cycle length by the number of segments a node intends to send. A node also keeps track of the cycles it has requested to transmit by placing such cycle numbers in its local queues. It is to be noted that a re-

serve command is not considered successful until confirmed by the headend. In order to provide fair access to all nodes, a limit is imposed on the number of slots a node can reserve in a cycle [28, 15]. When the headend receives the reserve command back, it adds the cycle length to a global reservation queue which is served according to a FIFO discipline. The headend station serves every reservation by issuing a start command containing a cycle number, which indicates the start of such a cycle, followed by as many empty slots as requested by the stations for transmission in that cycle. When active nodes observe a start command, they check the local queue for a matching cycle number. If it is a matching one, segments are sent consecutively. Otherwise, transmission is delayed until a start with a matching cycle number is observed. In order to monitor the total number of slots in the cycles queued at the headend, including the slots in the outgoing cycle which have not left the headend, a back pressure mechanism is employed [28, 15]. As explained in [28, 15], if the cycle length in the global queue exceeds the round trip propagation delay in slots, the generation of reserve commands is inhibited. Furthermore, all reserve commands which have been issued but which have not yet returned are cancelled. The reserve generation is resumed when the number of reserved slots drops below the threshold.

In order to implement p priorities, the CRMA access protocol, both at the headend and nodes, must be replicated p times. These protocols run in parallel. An access command has precedence over another if it belongs to

a higher priority. Also, a cycle can preempt any other cycle of lower priority.

CRMA, just like DQMA, provides throughput fairness even at high speed and large distances. In addition, it also allows transmissions of contiguous segments. This slot contiguity property facilitates packet reassembly. When a folded bus is used, then DQMA has a lower access delay than CRMA. This is because CRMA has a reserve command to travel to the folded end of the bus, back to the headend. Then slots must be issued by the headend to the node. Recall that for DQMA, the requests are transmitted on the reverse bus immediately. Therefore, in the case of DQMA with synchronous mechanism for contiguous segments transmission, the minimum access delay is equal to the round trip delay between the node and the headend. In any case, the DQDB medium access protocol seems to have a better immediate access delay than either DQMA or CRMA.

## 1.4.3 Cyclic Reservation Multiple Access II protocol

Cyclic Reservation Multiple Access II (CRMA II) [23, 24] is based on the experience gained from a 1 Gbits/s implementation of CRMA [28, 15]. Slots are accessed through two distinct mechanisms:(1) immediate access of gratis slots and (2) access of previously reserved slots. In both cases, the busy/free flag needs to be free for a slot to be accessible. The gratis access

mechanism, which is simply based on inspecting the busy/free decisions gives fast access and fully exploits spatial reuse of slots. The principle of reservation is as follows. A special node known as the scheduling node issues a reserve command by transmitting a start/end delimiter pair back-to-back. Nodes that wants to send a request do so by inserting a slot in the passing reserve command, thereby increasing its length. The network latency is also enlarged by switching a delay register into the data path. Upon return of the reserve command, the scheduler copies the request entries into its memory while the command passes for a second round trip to eliminate the request of the additional network latency. Nodes successively remove their entries. The scheduler analyzes the requests made by the nodes and sends out a confirmation command. This command contains a threshold value. A node cannot transmit more than that threshold value in slots. Immediately after sending the confirm command, the scheduler starts to mark all passing gratis slots as reserved until the number of such reserved slots corresponds to the number of confirmed requests. Subsequently, the reserve command is issued to collect the request entries for the next cycle.

The priority implementation of CRMA II is analogous to what has been described for CRMA. Just like CRMA, CRMA II provides throughput fairness even at higher speeds and longer distances [28, 15]. Since slots are being transmitted contiguously, the reassembly at the receiving end is easier while the segments labelling at the transmitting end is less complex.

However, adding buffers does increase the complexity of the network. Nodes have to send the requests with the reserve command, followed by removing the request from the confirm command, and only after receiving the start command that nodes are allowed to transmit. Obviously, all this adds considerably to the access delay.

#### 1.4.4 Fair Distributed Queue protocol

The Fair Distributed Queue (FDQ) [25] is a more recent medium access protocol for MANs. FDQ is a slotted system based on the unidirectional bus topology. Slots of fixed duration are generated by a headend station. In this section the terms outbound and inbound channels are analogous to a forward and reverse bus with a folded end connecting the busses. In FDQ, each node has the capability of reading from both the outbound and the inbound channels and writing to the outbound channel only. A slot header contains a busy/free bit, and active (A) bit, and an Inactive (I) bit which are all initialized to a value of zero when the slots are generated. When a slot is written by the node, the busy bit is set to one. When a node becomes active it sets the next unset (A) bit, and after it has completed transmission it sets the next unset (I) bit. These bits enable upstream stations to deduce the status of downstream stations. The (A) and (I) bits can only be set

when the slot is in the inbound channel. Nodes keep track of the number of active nodes downstream by an Active Downstream node (AD) counter that operates even when the node has no packets to transmits. The AD counter is incremented by one for every (A) bit detected on the reverse bus while it is decremented by one for every (I) bit observed by the node. When a node becomes active, it sets the first unset (A) bit it encounters to one. At the same time, the contents of its AD counter is transferred to a second counter which is known as the Count Down (CD) counter. The CD counter is decremented by one for every free slot passing by the node on the forward bus. When CD counter reaches zero, a segment from the node can be transmitted in the first free slot. When a node becomes idle, it sets the first free I bit observed on the reverse bus to one.

Priority implementation in FDQ is an extension of the basic protocol. The counters are replicated for each priority level. In addition, there is a different active and inactive bit for each level of priority. The access mechanism is the same with preference given to segments of a higher priority. If a node has an AD counter of higher priority level with a non zero value, it refrains from transmitting and waits for AD counters of higher priority to drop to zero.

It is reported in [25] that this new protocol achieves throughput efficiency independent of the bus length, the transmission speeds and the number of nodes. FDQ allocates equal bandwidth under heavy load to all active users in a time period less than or equal to the round trip propagation delay without wasting bandwidth. The priority mechanism is effective as the bandwidth is shared fairly among nodes of same priority level. However, there is a delay involved between a high priority message at the top of the local queue and the time it gets transmitted. In the worst case, this delay could be as long as the round trip propagation delay. Bearing this in mind, the delay is still dependent on the size of the network. Another drawback of this protocol is that there is slot wastage with FDQ due to the time it takes for the (I) bit to propagate upstream.

#### 1.5 Summary

Before discussing the main objective of the thesis, we recapitulate the current technological situation. BISDN wants to provide a means by which data from diverse services can be transported in a unified way. The committee in charge has decided that ATM shall be the multiplexing technique. Besides, the IEEE 802.6 has adopted the DQDB protocol as the medium access protocol for MANs. Studies have revealed that DQDB possesses several inherent problems. Unfairness was manifested for unipriority as well as multipriority traffic. To partially overcome these problems, the IEEE 802.6 committee adopted the BWB mechanism to deal with the unfairness problem. The cost was to sacrifice some bandwidth to help coordination among

nodes. Unfortunately, new problems popped up as the balancing convergence is severely influenced by the speed and size of the network. As the network speed and size increase, it takes longer for the network to converge to the anticipated breakdown of bandwidth. The BWB mechanism is therefore ineffective if the convergence takes so long that the condition it intends to remedy disappears before the operation converges to its final steady state. To fulfill the requirements of BISDN, it is vital to have a protocol that is reliable and fair to all the nodes independent of the time the transmission started. More importantly, since BISDN provides services that are delay sensitive, it requires a protocol that can implement a reliable priority mechanism. Unfortunately, the current standard does not fulfill such objectives. The other newer protocols (DQMA, CRMA, CRMA II, FDQ) that were discussed provide solutions to several of the problems encountered by the DQDB protocol. Unfortunately, they have just stopped short of satisfying the entire objective list.

## 1.6 Thesis Overview

The purpose of this thesis is to propose a new protocol, the High Performance Distributed Queue, (HPDQ). Just like DQDB and the newer protocols, HPDQ is implemented on a slotted unidirectional bus system. This bus topology has been chosen since high speed transmission require optic fibers

as it supports transmission of several Gbits/sec. This bus topology also complies with ATM specifications of bus systems. The principles of operation of HPDQ are fundamentally different from the other protocols proposed. The primary goals of HPDQ is to achieve full bandwidth utilization and to be fair to all the nodes, independent of the bus length, transmission speeds, number of nodes and starting time of transmissions. In implementing priority, HPDQ aims at providing a reliable service in addition of being robust, i.e. HPDQ intends to provide minimum insertion delay for higher priority nodes. It shall also be shown that in the worst case, redistribution is achieved in a round trip propagation delay. The hardware implementation of the switch is a bit more complex as the switch requires some buffering capabilities. However, this is not a severe disadvantage as most implementations of high speed bus networks use such a switch, e.g., DQDB, DQMA, and CRMA I and II.

#### 1.7 Thesis Outline

In Chapter 2, the basic version of the new protocol High Performance Distributed Queue is described together with an enhanced version. In Chapter 3 performance of the basic and enhanced protocols is studied through simulation. In Chapter 4 the priority implementation on HPDQ is considered. Simulation of the priority implementation of HPDQ is reported

in Chapter 5. Chapter 6 concludes the thesis with a summary, remarks and directions for future research.

# Chapter 2

# MEDIUM ACCESS PROTOCOL FOR HPDQ

### 2.1 Objectives

Despite the efforts made in designing and implementing efficient network protocols for operation in the metropolitan environment, it is unfortunate that none of those protocols is problem free. Such problems can be either technological, economical, behavioral or performance related. To solve those problems, further research efforts is needed in this area.

This thesis extends yet another effort whose goal is to design a network protocol that is efficient, cost effective, and above all problem free, by proposing a new protocol: The High Performance Distributed Queue (HPDQ). This protocol is defined on a dual unidirectional slotted bus system with active taps. Slots are generated at equal intervals by the end nodes. The HPDQ protocol has been designed while bearing in mind the problems that were encountered by previous protocols defined on a similar bus topology. The protocol reduces and in fact eliminates most of those problems.

To be efficient, a protocol must make use of the total bus capacity. In order to prevent any node or group of nodes to take control of the network, a protocol must provide fairness among nodes. These are two of the objectives of the HPDQ protocol. In addition, the HPDQ protocol intends to provide the minimum access delay to segments. Since minimizing bandwidth wastage is another important issue considered in numerous protocols, the HPDQ protocol made that issue an additional goal. Next we describe how the HPDQ protocol attains these goals.

#### 2.2 Description of HPDQ

In this section the basic HPDQ protocol for unipriority operation is described and will be extended later to multipriority. Although this protocol suffers from a certain deficiency that will be remedied by the enhanced version, it is described in order to explain the principle of operation.

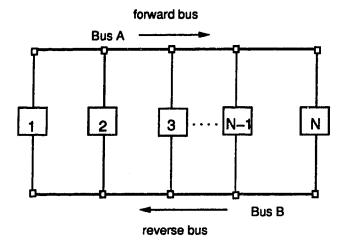

Since HPDQ operates on two unidirectional busses serving two oppo-

#### - Active Switch

Figure 2.1: HPDQ network configuration.

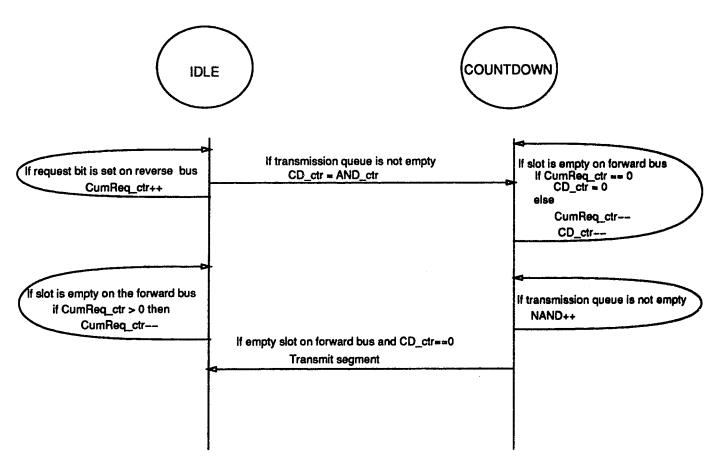

site directions and, since protocols for both busses are identical, the protocol for bus A only will be described. Bus A will be referred to as the forward bus while bus B will be called the reverse bus. The nodes are tapped onto the busses through active switches, see Figure 2.1. Through such switches, nodes can buffer slots and modify them with a minimum delay and then release them back onto the bus. Just like several other protocols defined on this bus topology, the HPDQ protocol is implemented through the use of counters. A node will have two basic counters: the number of Active Nodes Downstream counter, AND\_ctr and the Count Down counter, CD\_ctr. The finite state machine of the basic protocol is shown in Figure 2.2. The AND\_ctr keeps track of the number of nodes that are active downstream. It is to be noted that the AND\_ctr is not essential for the operation of this

Figure 2.2: Finite State Machine for Basic HPDQ protocol.

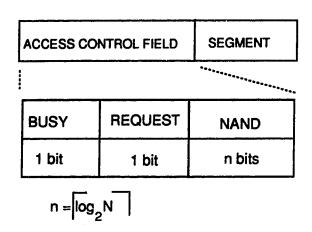

Figure 2.3: Slot format for basic HPDQ.

protocol and its sole purpose is for ease of understanding of the protocol. In fact the AND\_ctr is numerically equal to the value in the NAND field which shall be described later. The  $CD\_ctr$  holds the number of unused slots that the node should let go before consuming one. If the  $CD\_ctr$  is equal to zero and the transmission queue is not empty, the node transmits in the next empty slot. Then, the  $CD\_ctr$  is used in a manner similar to that in the DQDB protocol. This protocol relies on the reverse bus to provide information about the status of the nodes downstream. In order to do so, the slots need a field which will enable the upstream nodes to know the number of active stations downstream. We shall refer to this field as the NAND (Number of Active Nodes Downstream) field and the slot format is given in Figure 2.3. When a station has segments to transmit, it will increment the value of the NAND field of the next slot on the reverse bus by one. This can be

implemented with a single bit delay per node. The NAND field is updated as long as the transmission queue is not empty. Since the value contained in the received NAND indicates the number of active nodes downstream, its value is copied to the  $AND\_ctr$ . The minimum length of the NAND field is  $\lceil log_2(N) \rceil$  bits, where N is the number of stations on the bus. Since a typical MAN nowadays can contain up to 1000 stations, it shall be assumed that N is 1000. Therefore, a NAND field of 10 bits will suffice for a MAN.

In this protocol, nodes copy the  $AND\_ctrs$  to the  $CD\_ctrs$  everytime the  $CD\_ctr$  reaches zero. Therefore,  $CD\_ctrs$  hold the number of slots required by downstream stations. The  $CD\_ctr$  is decremented by one for every empty slot that a node observes on the forward bus. When the  $CD\_ctr$  is equal to zero, the node transmits its segments into the next empty slot. The  $CD\_ctr$  is then reinitialized to the new  $AND\_ctr$  value.

To illustrate the operation of the HPDQ protocol, consider the following example where there are 5 nodes out of which only nodes 1, 2 and 4 are active. The internode distance is 5 slots. Figure 2.4 shows a snap shot of the contents of the NAND fields, the *AND\_ctrs* and the *CD\_ctrs* of the five nodes. Notice that the value of the *CD\_ctrs* of nodes 3 and 5 are zero. However, since they are not active, they will not transmit. Nodes 1 and 3 will transmit segments after letting two empty slots and one empty slot go by, respectively. Since the AND\_ctr of node 4 is zero, it will transmit in every empty slot.

Figure 2.4: Basic operation of HPDQ

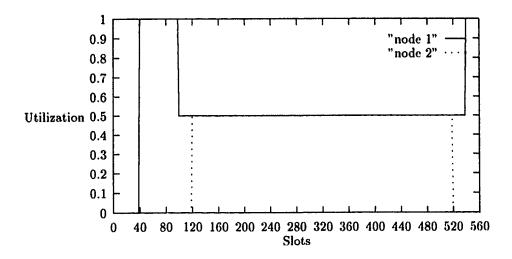

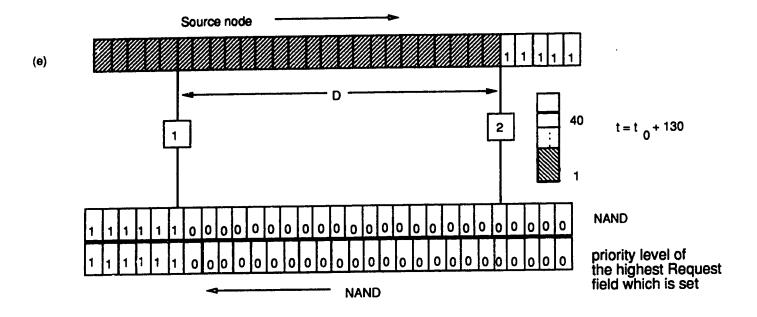

The protocol as it stands might attain 100% channel utilization when a group of stations are active for a long time. Unfortunately, HPDQ cannot maintain this level of utilization when stations start switching between the active and inactive states frequently. This is due to the effect of propagation delay. To illustrate this problem, the transient behvior of 2 nodes that are 20 slots apart is studied. The network configuration is shown in Figure 2.5.

Upon completion of its transmission, node 2 stops updating the NAND field on the reverse bus. This means that the next 20 slots that node 1 will read in, will have a value of 1 in the NAND field. Node 1 will therefore

Figure 2.5: Node 2 stops updating at completion of its transmission

assume that node 2 still requires empty slots to complete its transmission. This is clearly an erroneous interpretation. Hence, node 1 will release ghost slots which will not be consumed by node 2. Therefore, bandwidth is lost which leads to a transient wastage of the bandwidth when utilization drops below the 100% level while some nodes are still active. The transient behavior of the node in this example is shown in Figure 2.6. Note that time is measured in slots. Node 2 terminates its transmission at 520. Node 1 acknowledges that at 540 by consuming all the empty slots, thus reaching a utilization of 1.0. In the transient period between 520 and 540, node 1 was allowed a maximum utilization of only 0.5 although the other 50% of the bandwidth was wasted. It should be pointed out that, in general, bandwidth is wasted only when the most active downstream station completes its transmission.

Due to this, a modification to the original HPDQ protocol to overcome the above mentioned problem will be introduced next.

#### 2.3 The Enhanced HPDQ Protocol

As has been illustrated in Section 2.2, the completion of transmission by the most downstream active node results in a possible loss of bandwidth due to the effect of the propagation delay. This can be reduced, if not elimi-

Figure 2.6: Bandwidth loss due to stopping of transmission.

nated through the use of a special counter.

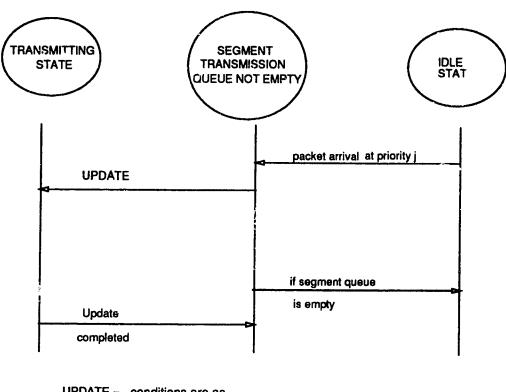

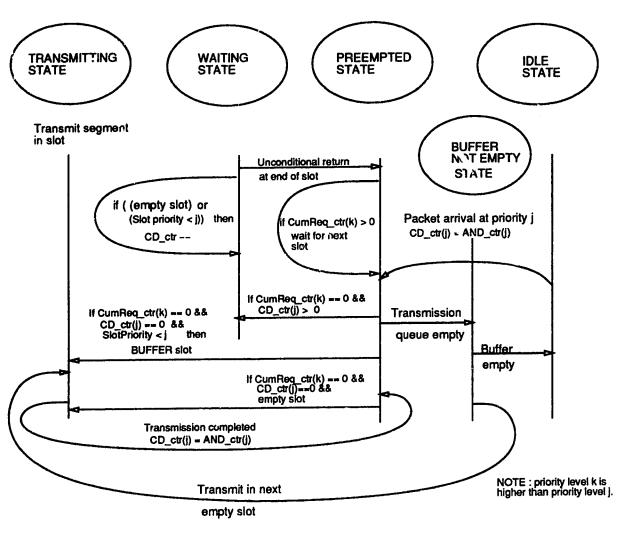

To implement the enhanced version of the HPDQ protocol, each node needs to have an additional counter, the Cumulative Request counter (CumReq\_ctr) and each slot should contain an additional field, namely the Request bit field shown in Figure 2.7. The CumReq\_ctr keeps track of the number of requests needed by downstream stations. The Request bit field differs from the NAND field in that, the former conveys requests from active stations whereas the NAND field indicates the number of nodes that are active downstream. The Request bit is set as it passes through an active node with pending requests, on a per segment basis. If the incoming Request field is already set then the node has to wait for the next available Request

Figure 2.7: Slot format for enhanced HPDQ.

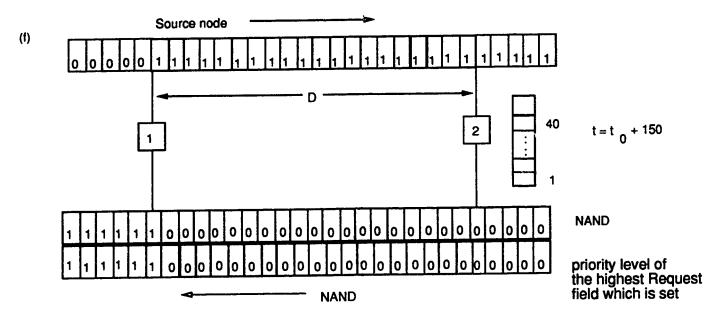

field. When a node has sent all its requests, it stops setting the Request field. However, it updates the NAND field as long as the segment transmission is incomplete. The finite state machine is shown in Figure 2.8. The CumReq\_ctr is decremented by one for every empty slot that the node lets go by on the forward bus. It is incremented by one for any requests arriving on the reverse bus. In fact, as long as CumReq\_ctr is greater than zero, the node will pass a number of empty slots that is equivalent to the value of the NAND field for every segment that the node transmits. When the CumReq\_ctr of a node reaches zero, the CD\_ctr is set to zero and that node will consume all empty slots on the forward bus regardless of the value of the NAND field. A value of zero in the CumReq\_ctr implies that stations downstream have completed all transmissions. As active nodes with a CumReq\_ctr of zero will consume all empty slots, this means that no bandwidth is lost.

Figure 2.8: Finite State Machine of Enhanced HPDQ protocol.

Figure 2.9: Operation of the CumReq\_ctr counters.

Figure 2.9 illustrates the outcome of this approach. The 3 nodes numbered 1 to 3 are 10 slots apart. Only nodes 1 and 3 are active. Node 1 has its CumReq\_ctr with a value of 2 in it, whereas node 3 has a 0 in its CumReq\_ctr. At the next slot time, node 1 will pass an empty slot downstream. Meanwhile, it will read the request from node 3 on the reverse bus. Since its CD\_ctr will be equal to zero at this instant, it will transmit in the next free slot. At the end of this transmission the CumReq\_ctr would have

Figure 2.10: Bandwidth distribution due to node stopping transmission.

been updated to a value of 3. The CumReq\_ctr of node 1 will not increase any more since there are no more requests from node 3 on the reverse bus. For the following six slots, node 1 will use every other slot and let an empty slot propagate downstream to node 3. Afterwards it will consume all free slots on the forward bus.

In order to understand the gain brought about by the introduction of the Cumulative Request counter, let us examine the scenario as described in Figure 2.5 but with the new set of rules.

Node 2 updates the Request field on the reverse bus for every segment that it has to transmit. The CumReq\_ctr of node 1 is incremented by one for every Request field that node 2 has modified. For every empty to 1, as the MAND and is 1, and decrements the value of the CumReq\_ctr by 1. Since CumReq\_ctr keeps track of the exact number of slots that the downstream node require, there is no need to let any more empty slots pass by once the CumReq\_ctr value reaches zero. Consequently, node 1 will consume all incoming slots. This enables the system to reduce, if not eliminate all sources of bandwidth wastage. The transient utilization shown in from Figure 2.8 clearly illustrates the performance gain that the enhanced HPDQ protocol provides. The total transient utilization stays at 100% and there are no more ghost slots.

#### 2.4 Network Aspects

In this section we shall discuss the performance and implementation aspects of this new protocol. This will be done in order to gain an insight into the protocol. Therefore, no comparison to other networks will be made.

#### 2.4.1 Performance issues

In order to investigate the effects of the HPDQ protocol on performance, let us consider an HPDQ network with N nodes. For the sake of this

analysis, assume that all active nodes have a load that is much greater than one. In other words, the transmission queue is never empty. Let  $N^*$  be the number of active nodes, where  $N^* \leq N$  and let X be one of the  $N^*$  active nodes. Let us further assume that there are  $N_1$  active stations upstream from X and  $N_2$  active stations downstream from X, such that  $N_1 + N_2 = N^* - 1$ . Once the system has stabilized, node X consumes one slot out of every  $N^*$  slots. Therefore an active node, X, will acquire  $1/N^*$  of the available bandwidth and an average insertion delay of  $N^* - 1$  slots, for  $N^* > 0$ .

Under the above conditions, the bus utilization reaches 100%. This is because when the system is active and stable, every slot on the bus is a dedicated slot. The bus utilization is independent of the actual number of active stations. It depends only on the load that the nodes offer to the system, and will reach 100% if there are enough segments queued up.

This new protocol is virtually insensitive to nodes leaving and entering the system and to their relative positions. At two different time instants,  $t_i$  and  $t_{i+n}$ , the system can have 2 different sets of  $N^*$  active nodes. Several stations of the first group of active nodes may have terminated their transmissions and have been replaced by another group of new nodes that become active. When this happens and the system has stabilized, the average bus utilization and average access delay of individual nodes remain the same. This is because the delay is based on the number of active nodes, regardless of the location of these nodes on the bus. As shown earlier, if we have  $N^*$

active nodes with an infinite number of segments queued up for transmission, nodes will still transmit in no more than one slot out of every  $N^*$  slots that go by, such that the throughput is  $1/N^*$ .

The fluctuation in the number of active stations does not affect the average bus utilization as long as there are enough segments to keep the bus busy. However, the average access delay is highly dependent on the number of active stations. A drop in the number of active stations enables the remaining nodes to transmit segments more frequently and consequently reduces the average access time. Similarly, if the number of stations increases the average access time will increase too since every node will have to let more slots go by before consuming one.

#### 2.4.2 Implementation Cost and Complexity

The implementation cost and complexity are very important issues to consider if we want to implement a protocol. The HPDQ protocol was designed by giving special considerations to such issues. The performance gains can be regarded as satisfactory. The enhanced HPDQ protocol will be the only one considered here since it has all the qualities of the basic HPDQ protocol together with some additional attractive features.

#### Counters

In this protocol, for each bus, a node has one Active Number of Downstream nodes counter, AND\_ctr, a CountDown counter, CD\_ctr and a Cumulative Requests Counter, CumReq-ctr. All of these can be implemented in software. Certainly, it will be faster if implemented by dedicated hardware. The size of the AND and CD counters has to be at least as large as the number of nodes that a Metropolitan Area Network can support. CumReq\_ctr should be large enough to hold requests coming from downstream stations and its size will be dictated by the number of segments that downstream stations intend to send. In order to prevent the CumReq\_ctr from overflowing, a mechanism that inhibits nodes from transmitting excessive requests is welcome. A back pressure mechanism is a reasonable choice. The headend could monitor the number of requests sent by the nodes. It will keep track of the number of request it receives and if they exceed a certain threshold value, the headend issues a special stop command demanding stations to stop request transmission until further notice. When the number of requests has drop below the threshold value, a special resume command could be issued to notify stations to resume request transmissions. These commands could be represented by an additional bit in the Access Control Field.

#### **Switches**

As the HPDQ protocol makes use of active switches, we should add the cost of these to the implementation cost. The cost of implementing counters is considerably less than that of the switches. The special function which is performed by switches is the modification of the content of the NAND fields. Updating of the NAND field can be done on a bit by bit basis.

#### 2.5 Summary

In this chapter, a new protocol HPDQ (High Performance Distributed Queue) defined on dual unidirectional bus topology, has been described. It provides good performance results and overcomes the problems that other protocols defined on similar bus topologies encountered. The basic protocol has been discussed which was later modified to the enhanced version. The main difference between the basic and the enhanced version is that when the most active downstream node leaves the system, the bandwidth wastage is reduced to a minimum in the enhanced version.

# Chapter 3

# PERFORMANCE ASPECTS

In this chapter the performance of the basic and enhanced versions of the HPDQ protocol is studied. The average bus utilization and the average access delay to the bus will be our performance measures. With the average bus utilization we can get a better understanding of how the bandwidth is divided among rodes under various conditions. Similarly, the average access delay to the bus enables us to analyze the average length of time a node has to wait before completing transmission of a segment under various conditions.

A simulation model for the HPDQ protocol was considered more ap propriate than a theoretical model. The main reason being the complexity of a theoretical model and its analysis. The performance results contained herein are based on simulations of several scenarios. First, we discuss the steady state analysis of the basic protocol, followed by the transient analysis. It is to be noted that under steady state and heavy load, either version of the protocol will yield the same results. Therefore steady state analysis of the enhanced version of HPDQ shall not be considered. However, the transient behavior of nodes leaving the system shall be analyzed for both versions.

In order to test the goals of our basic and enhanced protocol, a simulator that models the behavior of both protocols was implemented in software. The simulator was designed in such a way that it is flexible and the relevant parameters could be modified easily. Such parameters are: the number of nodes on the bus, the internode distance, the time at which transmission should start and stop, the packet arrival process per node, the distribution of packet lengths, the slot duration, the message and slot overhead and lastly the phase difference in slot generation on both busses. In order to be able to compare the HPDQ to the protocols proposed in the literature, we have chosen our message arrival process to follow a Poisson arrival. The start and stop time of transmissions were controlled whenever the transient behavior of the nodes was of interest.

#### 3.1 Simulation of the Basic Protocol

#### 3.1.1 Steady state analysis