### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

## University of Alberta

| DESIGN | AND | REALIZATION | OF A | NOVEL         | CLASS | OF  | HIGHLY | STABLE  | HIGH- | RESOLUTION |

|--------|-----|-------------|------|---------------|-------|-----|--------|---------|-------|------------|

|        |     | OVERSAMPL   | ED Σ | $-\Delta A/D$ | Conv  | ERT | ER CON | FIGURAT | IONS  |            |

by

Neil A. Fraser

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of **Master of Science**.

Department of Electrical and Computer Engineering

Edmonton, Alberta Fall 2001

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our ille Notre référence

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-69522-0

### University of Alberta

### Library Release Form

Name of Author: Neil A. Fraser

Title of Thesis: Design and Realization of a Novel Class of Highly Stable High-Resolution Over-

sampled  $\Sigma$ - $\Delta$  A/D Converter Configurations

Degree: Master of Science

Year this Degree Granted: 2001

Permission is hereby granted to the University of Alberta Library to reproduce single copies of this thesis and to lend or sell such copies for private, scholarly or scientific research purposes only.

The author reserves all other publication and other rights in association with the copyright in the thesis, and except as hereinbefore provided, neither the thesis nor any substantial portion thereof may be printed or otherwise reproduced in any material form whatever without the author's prior written permission.

Neil A. Fraser

**CEB 238**

University of Alberta

Edmonton, AB

Canada, T6G 2G7

Date: June 13,2001

### University of Alberta

### Faculty of Graduate Studies and Research

The undersigned certify that they have read, and recommend to the Faculty of Graduate Studies and Research for acceptance, a thesis entitled **Design and Realization of a Novel Class of Highly Stable High-Resolution Oversampled**  $\Sigma$ - $\Delta$  **A/D Converter Configurations** submitted by Neil A. Fraser in partial fulfillment of the requirements for the degree of **Master of Science**.

Dr. B. Nowrouzian (Supervisor)

Dr. I. Filanovsky

Dr. L. K. Stewart

Date: June 12, 2001

I dedicate this thesis to my parents Robert and Donna Fraser and to my sister Alison Fraser

## **Abstract**

This thesis is concerned with the design and realization of higher-order high-resolution oversampled  $\Sigma$ - $\Delta$  analog-to-digital (A/D) converter configurations. The design and realization of a set of hitherto feedforward and multiple-feedback  $\Sigma$ - $\Delta$  A/D converters is first reviewed. This is followed by an investigation of the achievable signal-to-quantization-noise ratio, dynamic range, and stability of the corresponding switched-capacitor (SC) hardware implementation for this set of  $\Sigma$ - $\Delta$  A/D converter configurations. A novel statistical approach for the estimation of the maximum DC input signal level for stable A/D converter operation is then presented. The hitherto  $\Sigma$ - $\Delta$  A/D converters are usually based on, a) complementary signal and noise transfer functions, and/or b) unit-circle noise transfer function zeros. This thesis is further concerned with the development of novel  $\Sigma$ - $\Delta$  A/D converters having, instead, magnitude-squared or magnitude complementary signal and noise transfer functions. The proposed A/D converters exhibit resolution and dynamic range properties similar to those of the existing feedforward and multiple-feedback  $\Sigma$ - $\Delta$  A/D converters, but offer increased stability performance in the presence of capacitor mismatches in the corresponding SC hardware implementations. In addition, the SC hardware implementation of the resulting A/D converters leads to a capacitance spread which is comparable to that of hitherto  $\Sigma$ - $\Delta$  A/D converters.

## Acknowledgements

The author would like to thank Dr. Nowrouzian for his countless hours of advice, guidance, and encouragement that he provided during the past two years.

The author would further like to thank Nortel Networks, Gennum Corporation, Micronet, and NSERC for their financial support.

Most importantly, the author would like to thank his mother and father, Donna and Robert Fraser and his sister Alison Fraser for their years of encouragement and support.

## **Contents**

| 1 | Int | oduction                                                                                    | 1  |

|---|-----|---------------------------------------------------------------------------------------------|----|

|   | 1.1 | A/D Conversion                                                                              | ;  |

|   | 1.2 | Nyquist-rate A/D Converters                                                                 | 4  |

|   |     | 1.2.1 Successive Approximation A/D Converters                                               | •  |

|   |     | 1.2.2 Flash A/D Converters                                                                  | 7  |

|   | 1.3 | Oversampled A/D Converters                                                                  | 8  |

|   |     | 1.3.1 Oversampled Δ-Modulators                                                              | ç  |

|   | 1.4 | Σ-Δ A/D Converters                                                                          | 10 |

|   |     | 1.4.1 First-Order Σ-Δ A/D Converter                                                         | 10 |

|   |     | 1.4.2 Motivation for $\Sigma$ - $\Delta$ A/D Converters                                     | 12 |

|   |     | 1.4.3 Disadvantages of Σ-Δ A/D Converters                                                   | 12 |

|   |     | 1.4.4 Higher-Order Σ-Δ A/D Converters                                                       | 13 |

|   |     | 1.4.5 Cascaded Σ-Δ A/D Converters                                                           | 14 |

|   |     | 1.4.6 Bandpass Σ-Δ A/D Conversion                                                           | 15 |

|   | 1.5 | Switched-Capacitor Hardware Implementation of Oversampled $\Sigma$ - $\Delta$ A/D Converter |    |

|   |     | Configurations                                                                              | 16 |

|   | 1.6 | Open Problems in Σ-Δ A/D Conversion                                                         | 17 |

|   |     | l.6.1 Design                                                                                | 17 |

|   |     | 1.6.2 Stability Prediction                                                                  | 17 |

|   | 1.7 | Overview of the Thesis                                                                      | 17 |

| 2 | Fee | forward and Multiple-feedback $\Sigma$ - $\Delta$ A/D Converter Configurations 1            | 18 |

|   | 2.1 | Introduction                                                                                | 19 |

|   | 2.2 | Five Widely Used Feedforward and Multiple-Feedback Σ-Δ A/D Converter Configu-               |    |

|   |     | rations                                                                                     | 21 |

|   |     | 2.2.1 Cascade-of-Integrators Σ-Δ A/D Converter Configuration                                | 21 |

|   |     | 2.2.2 Cascade-of-Resonators Σ-Δ A/D Converter Configuration                                 | 26 |

|   |     | 2.2.3 Cascade-of-Resonators/Integrators $\Sigma$ - $\Delta$ A/D Converter Configuration 3   | 30 |

|   |     | 2.2.4 Feedforward S-A A/D Converter Configuration                                           | 34 |

|   |      | 2.2.5 Multiple-Feedback $\Sigma$ - $\Delta$ A/D Converter Configuration                    | 37 |

|---|------|--------------------------------------------------------------------------------------------|----|

|   |      | 2.2.6 Concluding Remarks                                                                   | 41 |

| 3 | Des  | sign of Feedforward and Multiple-Feedback $\Sigma$ - $\Delta$ A/D Converter Configura      | -  |

|   | tion | ns                                                                                         | 44 |

|   | 3.1  | Introduction                                                                               | 44 |

|   | 3.2  | Design Procedure                                                                           | 45 |

|   |      | 3.2.1 System Design Specifications                                                         | 45 |

|   |      | 3.2.2 Approximation of Signal and Noise Transfer Functions                                 | 45 |

|   |      | 3.2.3 Realization of Signal and Noise Transfer Functions                                   | 47 |

|   | 3.3  | Hitherto Stability Estimation Technique                                                    | 48 |

|   | 3.4  | Application to the Design and Investigation of Feedforward and Multiple-Feedback           |    |

|   |      | Σ-Δ A/D Converter Configurations                                                           | 52 |

|   |      | 3.4.1 Investigation of the Effect of Capacitor Mismatches                                  | 59 |

|   | 3.5  | A Novel Statistical Approach for the Estimation of Stability in Feedforward and            |    |

|   |      | Multiple-Feedback Oversampled $\Sigma$ - $\Delta$ A/D Converter Configurations             | 64 |

|   | 3.6  | Demonstration of the Accuracy of the Proposed Statistical Approach                         | 66 |

|   | 3.7  | Concluding Remarks                                                                         | 69 |

| 4 | A N  | lovel Class of Highly Stable High-Resolution $\Sigma$ - $\Delta$ A/D Converters            | 70 |

|   | 4.1  | Introduction                                                                               | 70 |

|   | 4.2  | Magnitude-Squared Complementary and Magnitude Complementary Transfer Functions             | 71 |

|   | 4.3  | Proposed $\Sigma$ - $\Delta$ A/D Converter Configurations                                  | 74 |

|   |      | 4.3.1 Modified Cascade-of-Integrators $\Sigma$ - $\Delta$ A/D Converter Configuration      | 74 |

|   |      | 4.3.2 Modified Cascade-of-Resonators $\Sigma$ - $\Delta$ A/D Converter Configuration       | 76 |

|   |      | 4.3.3 Modified Cascade-of-Resonators/Integrators Σ-Δ A/D Converter Configuration           | 81 |

|   |      | 4.3.4 Modified Feedforward $\Sigma$ - $\Delta$ A/D Converter Configuration                 | 82 |

|   |      | 4.3.5 Modified Multiple-Feedback $\Sigma$ - $\Delta$ A/D Converter Configuration           | 87 |

|   | 4.4  | Design Procedure                                                                           | 88 |

|   |      | 4.4.1 Design of Magnitude-squared Complementary $\Sigma$ - $\Delta$ A/D Converters         | 90 |

|   |      | 4.4.2 Design of Magnitude Complementary $\Sigma$ - $\Delta$ A/D Converters                 | 90 |

|   | 4.5  | Advantages of the Proposed $\Sigma\text{-}\Delta$ A/D Converters                           | 91 |

|   | 4.6  | Concluding Remarks                                                                         | 91 |

| 5 | Desi | ign, Investigation, and Analysis of the Proposed $\Sigma$ - $\Delta$ A/D Converter Config- |    |

|   | urat | ions                                                                                       | 92 |

|   | 5.1  | Design and Simulation of the MCOI, MCOR, and MCRI $\Sigma$ - $\Delta$ A/D Converter Con-   |    |

|   |      |                                                                                            |    |

|   | <b>5.2</b> | Design and Simulation of the MFF and MMF $\Sigma$ - $\Delta$ A/D Converter Configurations .         | 98  |

|---|------------|-----------------------------------------------------------------------------------------------------|-----|

|   | 5.3        | Comparison of the Modified $\Sigma$ - $\Delta$ A/D Converters to the Hitherto A/D Converters .      | 104 |

|   | 5.4        | Concluding Remarks                                                                                  | 106 |

| 6 | Co         | nclusion                                                                                            | 107 |

|   | 6.1        | Original Contributions                                                                              | 108 |

|   |            | 6.1.1 Chapter 2                                                                                     | 108 |

|   |            | 6.1.2 Chapter 3                                                                                     | 108 |

|   |            | 6.1.3 Chapter 4                                                                                     | 109 |

|   |            | 6.1.4 Chapter 5                                                                                     | 109 |

|   | 6.2        | Future Work                                                                                         | 109 |

| A | Apj        | pendix                                                                                              | 113 |

|   | <b>A.1</b> | Important Properties of Hermite Polynomials                                                         | 113 |

|   | <b>A.2</b> | Derivation of k Using Gram-Charlier Series                                                          | 114 |

|   | A.3        | Derivation of $m_y$ Using Gram-Charlier Series                                                      | 115 |

| В | Apı        | pendix                                                                                              | 116 |

|   | B.1        | Calculation of Minimum Oversampling Ratio                                                           | 116 |

|   | <b>B.2</b> | Estimation of Quantizer Input Signal Distribution for First-Order $\Sigma$ - $\Delta$ A/D Converter |     |

|   |            | Configuration                                                                                       | 116 |

|   | B.3        | Estimation of Quantizer Input Signal Distribution for 2-nd Order $\Sigma$ - $\Delta$ A/D Converter  |     |

|   |            | Configuration                                                                                       | 117 |

## List of Figures

| 1.1  | Typical Digital Signal Processing System                                                           | 2  |

|------|----------------------------------------------------------------------------------------------------|----|

| 1.2  | Generalized A/D Converter                                                                          | :  |

| 1.3  | One-Bit Quantizer                                                                                  | 3  |

| 1.4  | Four-Bit Quantizer                                                                                 | 4  |

| 1.5  | Frequency Spectrum of Input Signal                                                                 | 5  |

| 1.6  | Anti-Aliasing Filter Requirement for Nyquist-Rate A/D Converters                                   | 5  |

| 1.7  | Successive Approximation Search Path                                                               | 6  |

| 1.8  | Flash A/D Generalized Architecture                                                                 | 7  |

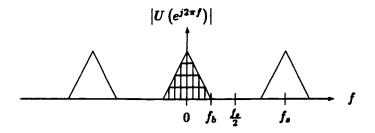

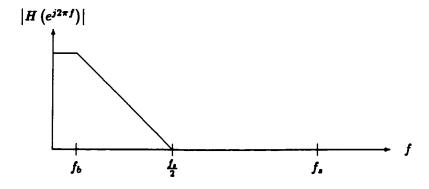

| 1.9  | Frequency Spectrum of Input Signal                                                                 | 8  |

| 1.10 | Anti-Aliasing Filter Requirement for Oversampled A/D Converter                                     | 8  |

| 1.11 | Generic Δ-Modulator                                                                                | 9  |

| 1.12 | Generic Σ-Δ A/D Converter Configuration                                                            | 10 |

| 1.13 | Single-loop $\Sigma$ - $\Delta$ A/D Converter Configuration                                        | 10 |

| 1.14 | Signal and Noise Transfer Function for Single-Loop $\Sigma$ - $\Delta$ A/D Converter Configuration | 11 |

| 1.15 | Theoretical SQNR versus Input Signal Amplitude                                                     | 12 |

| 1.16 | Generic Σ-Δ A/D Converter Configuration                                                            | 13 |

| 1.17 | A Second-order $\Sigma$ - $\Delta$ A/D Converter                                                   | 13 |

| 1.18 | Cascaded $\Sigma$ - $\Delta$ A/D Converter Configuration                                           | 14 |

| 1.19 | First-Order $\Sigma$ - $\Delta$ A/D Converter SC Hardware Implementation                           | 16 |

| 2.1  | Generic $\Sigma$ - $\Delta$ A/D Converter Configuration                                            | 19 |

| 2.2  | Generic Linear $\Sigma$ - $\Delta$ A/D Converter Configuration                                     | 19 |

| 2.3  | Cascade-of-Integrators $\Sigma$ - $\Delta$ A/D Converter Configuration                             | 21 |

| 2.4  | Basic SC Hardware Implementation Building Blocks                                                   | 24 |

| 2.5  | Identification of the Primary Elements in a 2-nd Order COI A/D Converter                           | 24 |

| 2.6  | Corresponding SC Hardware Implementation of a 2-nd Order COI $\Sigma$ - $\Delta$ A/D Con-          |    |

|      | verter                                                                                             | 25 |

| 2.7  | Cascade-of-Integrators SC Hardware Implementation                                                  | 27 |

| 2.8  | Cascade-of-Resonators $\Sigma$ - $\Delta$ A/D Converter Configuration                              | 28 |

| 9 A  | Creards of Passentons CC Handress Incolerantation                                                  | 91 |

| 2.10 | Cascade-of-Resonators/Integrators $\Sigma$ - $\Delta$ A/D Converter Configuration          | 32        |

|------|--------------------------------------------------------------------------------------------|-----------|

| 2.11 | Cascade-of-Resonators/Integrators SC Hardware Implementation                               | 35        |

| 2.12 | Feedforward $\Sigma$ - $\Delta$ A/D Converter Configuration                                | 36        |

| 2.13 | Feedforward SC Hardware Implementation                                                     | 38        |

| 2.14 | Multiple-Feedback $\Sigma$ - $\Delta$ A/D Converter Configuration                          | 39        |

| 2.15 | Multiple-Feedback SC Hardware Implementation                                               | 42        |

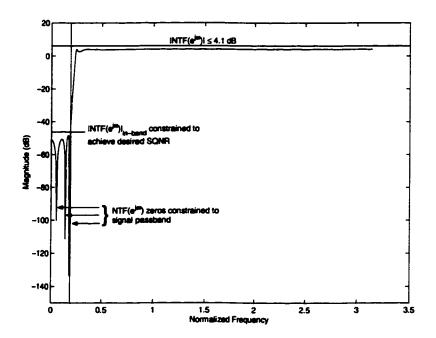

| 3.1  | Illustration of Noise Transfer Function Constraints                                        | 47        |

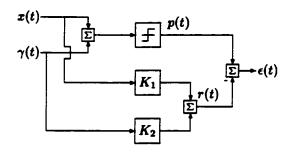

| 3.2  | Describing Function Method                                                                 | 48        |

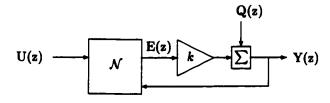

| 3.3  | Linearized Σ-Δ A/D Converter                                                               | 49        |

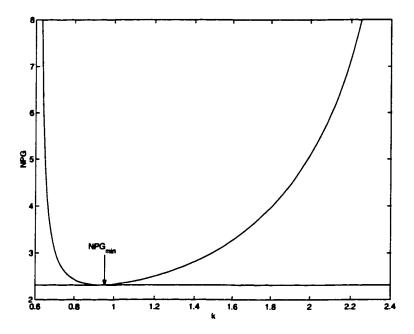

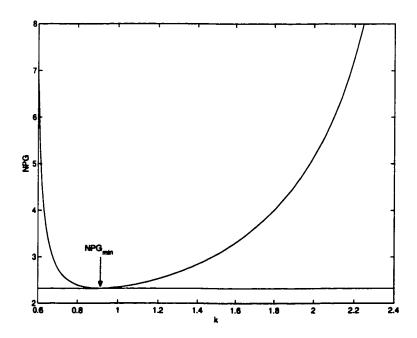

| 3.4  | Noise Power Gain versus k                                                                  | 50        |

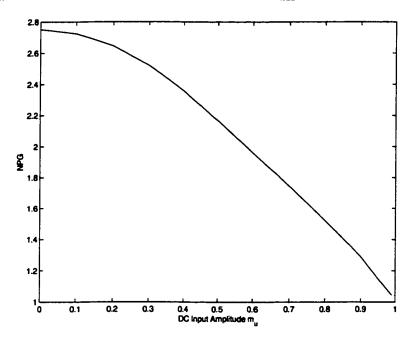

| 3.5  | NPG versus mu Curve                                                                        | 52        |

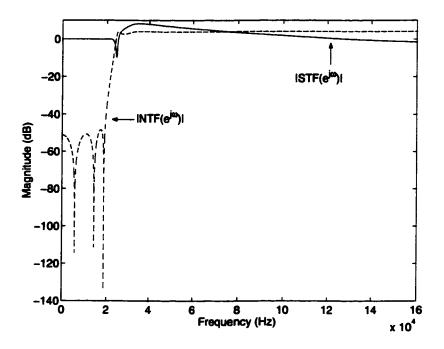

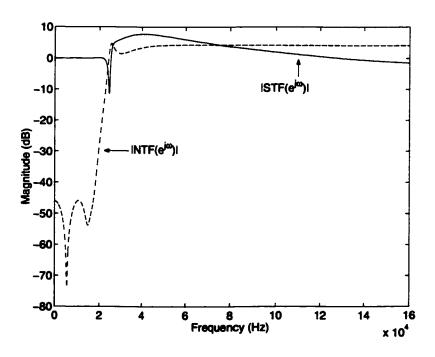

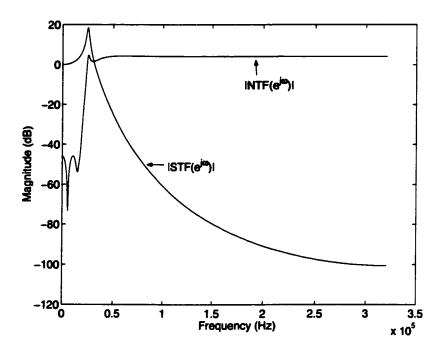

| 3.6  | COI, COR, CRI $NTF(z)$ and $STF(z)$                                                        | 55        |

| 3.7  | FF $NTF(z)$ and $STF(z)$                                                                   | 55        |

| 3.8  | MF $NTF(z)$ and $STF(z)$                                                                   | 56        |

| 3.9  | Noise Power Gain versus $k$ for FF and MF $\Sigma$ - $\Delta$ A/D Converters               | 57        |

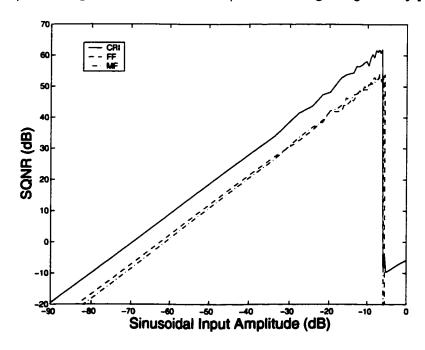

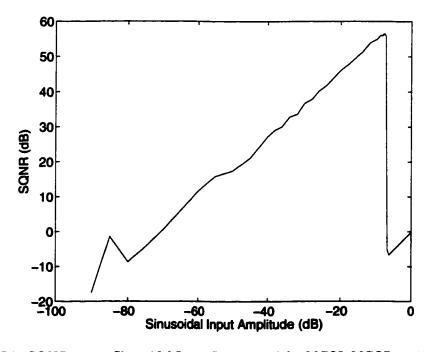

|      | SQNR versus Sinusoidal Input Signal Level                                                  | 58        |

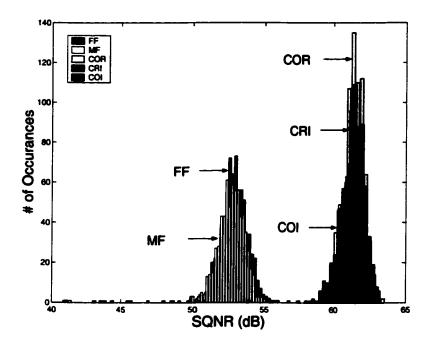

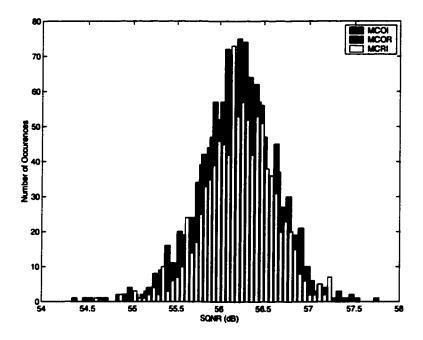

|      | Monte-Carlo Simulation Results                                                             | 63        |

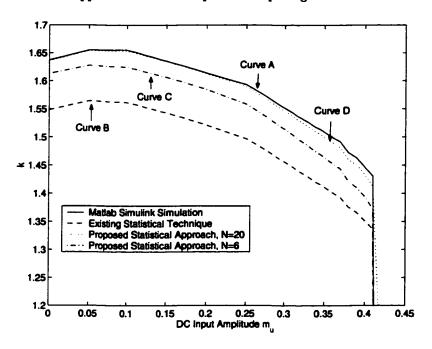

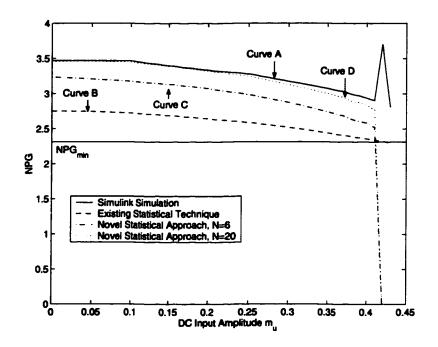

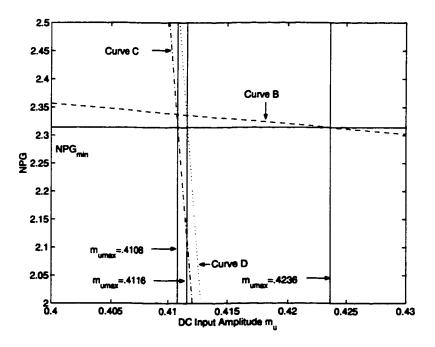

|      | Comparison of $k$ versus $m_u$ Curves                                                      | 67        |

|      | Comparison of NPG versus $m_u$ Curves                                                      | 68        |

|      | Detailed Comparison of NPG versus $m_u$ Curves                                             | 68        |

| 0.11 | Detailed Comparison of 141 G versus my Ourves                                              | •         |

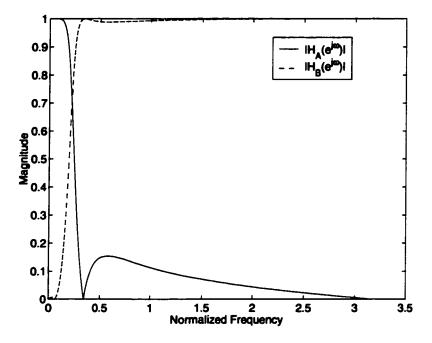

| 4.1  | Magnitude-Frequency Plot of $H_A(z)$ and $H_B(z)$                                          | <b>73</b> |

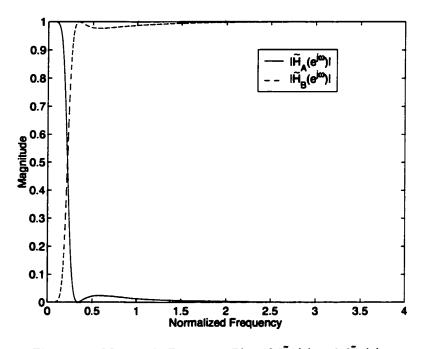

| 4.2  | Magnitude-Frequency Plot of $\tilde{H_A}(z)$ and $\tilde{H_B}(z)$                          | 73        |

| 4.3  | Modified Cascade-of-Integrators $\Sigma$ - $\Delta$ A/D Converter Configuration            | 74        |

| 4.4  | Equivalent SC system                                                                       | <b>76</b> |

| 4.5  | Modified Cascade-of-Integrators SC Hardware Implementation                                 | 77        |

| 4.6  | Modified Cascade-of-Resonators $\Sigma$ - $\Delta$ A/D Converter Configuration             | 78        |

| 4.7  | Modified Cascade-of-Resonators SC Hardware Implementation                                  | 80        |

| 4.8  | Modified Cascade-of-Resonators/Integrators $\Sigma$ - $\Delta$ A/D Converter Configuration | 81        |

| 4.9  | Modified Cascade-of-Resonators/Integrators SC Hardware Implementation                      | 83        |

| 4.10 | Modified Feedforward $\Sigma$ - $\Delta$ A/D Converter Configuration                       | 84        |

| 4.11 | Modified Feedforward SC Hardware Implementation                                            | 86        |

| 4.12 | Modified Multiple-Feedback $\Sigma$ - $\Delta$ A/D Converter Configuration                 | 87        |

| 4.13 | Modified Multiple-Feedback SC Hardware Implementation                                      | 89        |

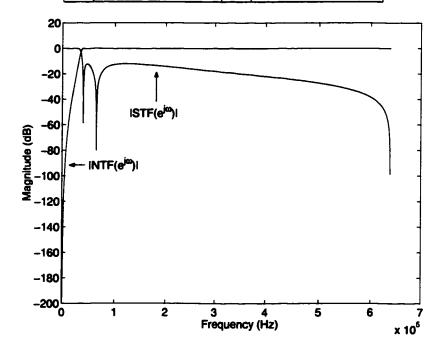

| 5.1  | Magnitude-Frequency Plot of $NTF(z)$ and $STF(z)$ for the MCOI, MCOR, and MCRI             |           |

|      | $\Sigma$ - $\Delta$ A/D Converters                                                         | 95        |

| 5.2        | SQNR versus Sinusoidal Input Signal Level for MCOI, MCOR, and MCRI                             | 95  |

|------------|------------------------------------------------------------------------------------------------|-----|

| 5.3        | MCOI, MCOR, and MCRI $\Sigma$ - $\Delta$ A/D Converters Monte-Carlo Simulation Results .       | 98  |

| 5.4        | Magnitude-Frequency Plot of $NTF(z)$ and $STF(z)$ for MFF and MMF $\Sigma$ - $\Delta$ A/D      |     |

|            | Converter Configurations                                                                       | 100 |

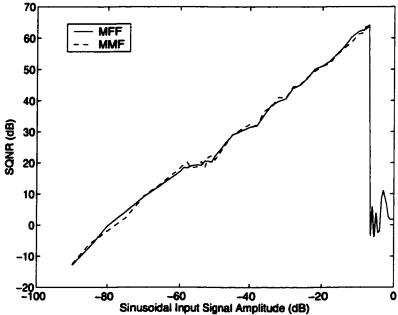

| 5.5        | $SQNR$ versus Sinusoidal Input Signal Level for MFF and MMF $\Sigma$ - $\Delta$ A/D Converters | 101 |

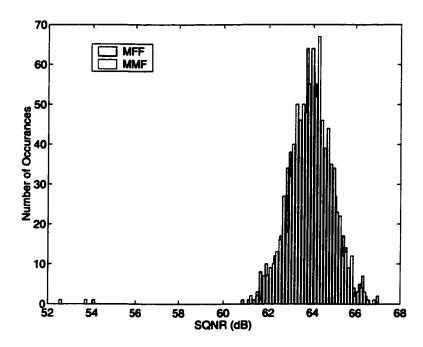

| 5.6        | MFF and MMF $\Sigma$ - $\Delta$ A/D Converters Monte-Carlo Simulation Results                  | 103 |

| B.1        | Decomposed First-Order $\Sigma$ - $\Delta$ A/D Converter Configuration                         | 117 |

| <b>B.2</b> | Estimated First-Order $\Sigma$ - $\Delta$ A/D Converter Quantizer Input Signal Distribution    | 118 |

| <b>B.3</b> | Actual First-Order $\Sigma$ - $\Delta$ A/D Converter Quantizer Input Signal Distribution       | 118 |

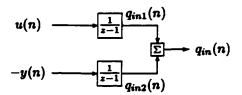

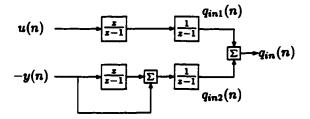

| <b>B.4</b> | Decomposed 2-nd Order $\Sigma$ - $\Delta$ A/D Converter Configuration                          | 118 |

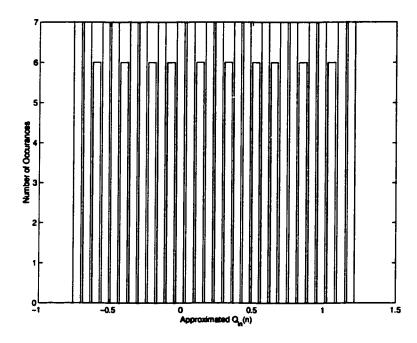

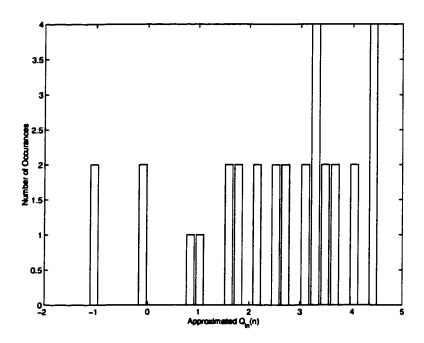

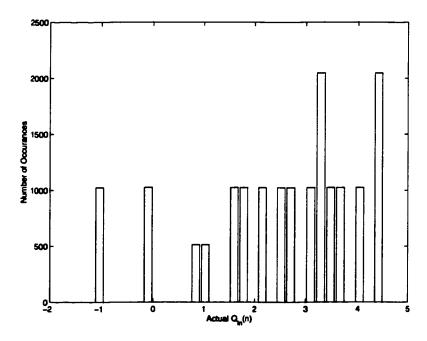

| B.5        | Estimated 2-nd Order $\Sigma$ - $\Delta$ A/D Converter Quantizer Input Signal Distribution     | 120 |

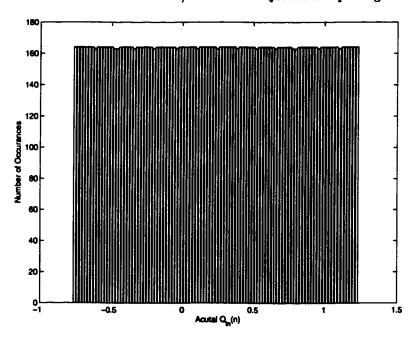

| <b>B.6</b> | Actual 2-nd Order Σ-Δ A/D Converter Quantizer Input Signal Distribution                        | 120 |

## **List of Tables**

| 1.1  | Quantizer Output Signal Levels                                      | 4  |

|------|---------------------------------------------------------------------|----|

| 2.1  | Cascade-of-Integrator Nominal Capacitor Values                      | 26 |

| 2.2  | Cascade-of-Resonators Nominal Capacitor Values                      | 32 |

| 2.3  | Cascade-of-Resonators-Integrator Nominal Capacitor Values           | 34 |

| 2.4  | Feedforward Nominal Capacitor Values                                | 37 |

| 2.5  | Multiple-Feedback Nominal Capacitor Values                          | 41 |

| 3.1  | System Design Specifications                                        | 45 |

| 3.2  | Lowpass $\Sigma$ - $\Delta$ A/D Converter Design Specifications     | 53 |

| 3.3  | COI, COR, CRI Noise and Signal Transfer Function Coefficients       | 53 |

| 3.4  | FF Noise and Signal Transfer Function Coefficients                  | 54 |

| 3.5  | MF Noise and Signal Transfer Function Coefficients                  | 54 |

| 3.6  | Cascade-of-Integrators Nominal Multiplier Coefficients              | 54 |

| 3.7  | Cascade-of-Resonators/Integrators Nominal Multiplier Coefficients   | 56 |

| 3.8  | Cascade-of-Resonators Nominal Multiplier Coefficients               | 56 |

| 3.9  | Feedforward Nominal Multiplier Coefficients                         | 57 |

| 3.10 | Multiple-Feedback Nominal Multiplier Coefficients                   | 57 |

| 3.11 | Maximum Stable DC Input Signal Amplitude $m_{umax}$                 | 58 |

| 3.12 | COI Σ-Δ A/D Converter Scaled Capacitor Values                       | 59 |

| 3.13 | CRI Σ-Δ A/D Converter Scaled Capacitor Values                       | 60 |

| 3.14 | COR Σ-Δ A/D Converter Scaled Capacitor Values                       | 61 |

| 3.15 | FF Σ-Δ A/D Converter Scaled Capacitor Values                        | 61 |

| 3.16 | MF Σ-Δ A/D Converter Scaled Capacitor Values                        | 62 |

| 3.17 | Comparison of Capacitance Spread and Total Capacitance              | 62 |

| 3.18 | Monte-Carlo Simulation Results                                      | 63 |

| 3.19 | Percentage of Unstable Samples                                      | 64 |

| 4.1  | Modified Cascade-of-Integrators Nominal Capacitor Values            | 78 |

| 4.2  | Modified Cascade-of-Resonators Nominal Capacitor Values             | 81 |

| 4.3  | Modified Cascade-of-Resonators/Integrators Nominal Capacitor Values | 84 |

| 4.4        | Modified Feedforward Nominal Capacitor Values                                                 | 87  |

|------------|-----------------------------------------------------------------------------------------------|-----|

| 4.5        | Modified Multiple-Feedback Nominal Capacitor Values                                           | 90  |

| 5.1        | $\Sigma$ - $\Delta$ A/D Converter Design Specifications                                       | 93  |

| 5.2        | MCOI, MCOR and MCRI $\Sigma$ - $\Delta$ A/D Converter Noise and Signal Transfer Function      |     |

|            | Coefficients                                                                                  | 93  |

| 5.3        | MCOI $\Sigma$ - $\Delta$ A/D Converter Nominal Multiplier Values                              | 94  |

| 5.4        | MCOR $\Sigma$ - $\Delta$ A/D Converter Nominal Multiplier Values                              | 94  |

| 5.5        | MCRI $\Sigma$ - $\Delta$ A/D Converter Nominal Multiplier Values                              | 94  |

| 5.6        | MCOI Σ-Δ A/D Converter Scaled Capacitor Values                                                | 96  |

| 5.7        | MCOR Σ-Δ A/D Converter Scaled Capacitor Values                                                | 96  |

| 5.8        | MCRI Σ-Δ A/D Converter Scaled Capacitor Values                                                | 97  |

| 5.9        | Monte-Carlo Simulation Results                                                                | 98  |

| 5.10       | Percentage of Unstable Samples                                                                | 99  |

| 5.11       | MFF and MMF $\Sigma$ - $\Delta$ A/D Converter Design Specifications                           | 99  |

| 5.12       | MFF and MMF $\Sigma$ - $\Delta$ A/D Converter Noise and Signal Transfer Function Coefficients | 100 |

| 5.13       | MFF Σ-Δ A/D Converter Nominal Multiplier Values                                               | 100 |

| 5.14       | MMF $\Sigma$ - $\Delta$ A/D Converter Nominal Multiplier Values                               | 101 |

| 5.15       | MFF Σ-Δ A/D Converter Scaled Capacitor Values                                                 | 102 |

| 5.16       | MMF $\Sigma$ - $\Delta$ A/D Converter Scaled Capacitor Values                                 | 102 |

| 5.17       | Monte-Carlo Simulation Results                                                                | 104 |

| 5.18       | Percentage of Unstable Samples                                                                | 104 |

| 5.19       | Comparison of $\Sigma$ - $\Delta$ A/D Converter Configurations                                | 105 |

| D 1        | Actual and Estimated First Order F. A. A./D. Conventor Overtion Insut Signal Ma               |     |

| D.1        | Actual and Estimated First-Order $\Sigma$ - $\Delta$ A/D Converter Quantizer Input Signal Mo- | 110 |

| DΛ         | ments                                                                                         | 119 |

| <b>B.2</b> | Actual and Estimated 2-nd Order $\Sigma$ - $\Delta$ A/D Converter Quantizer Input Signal Mo-  |     |

|            | ments                                                                                         | 191 |

## Chapter 1

## Introduction

In its most general sense, a signal is used to convey information. One can distinguish between two classes of signals. The signals within the first class have a value defined at all times and are referred to as continuous-time signals. An example of such a signal is the reading from a thermometer which can be taken at any time. The signals within the second class have values defined only at specified time instances and are referred to as discrete-time signals. A typical example of this type of signal is a graph of daily precipitation as functions of time.

One can further characterize continuous-time and discrete-time signals in terms of their range of values. If a signal can take on any value within a specified range, it is referred to as a continuous-amplitude (non-quantized) signal. On the other hand, if the signal can take on only a finite number of values from a specified range, it is referred to as a discrete-amplitude (quantized) signal. An example of a continuous-amplitude signal is the reading taken from a mercury thermometer. If the temperature reading was taken from a thermometer with a digital display, then this would be a discrete-amplitude signal.

Two important types of signals exist, namely, analog signals and digital signals. An analog signal is a signal which is both continuous in time and amplitude, whereas a digital signal is a signal which is both discrete in time and amplitude. The images, sounds, and smells that we perceive everyday are examples of analog signals. An example of a digital signal is a photograph taken with a digital camera as the photograph is stored in memory inside the camera.

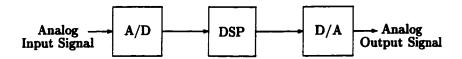

With the invention of transistors and eventually the modern-day digital computers (digital signal processors (DSP)), digital signals are found in a wide variety of applications. Given that all perceived signals are analog signals and that they are to be processed digitally (using a digital signal processor), some type of conversion between the two types of signals is required. The process of converting an analog signal to a digital signal is referred to as analog-to-digital (A/D) conversion. The digital output of such a system is then processed by a DSP and may then be converted to an analog signal through the reverse process called digital-to-analog (D/A) conversion. Figure 1.1 shows a simple block diagram of a typical digital signal processing system.

Figure 1.1: Typical Digital Signal Processing System

One can distinguish between two types of A/D converters<sup>1</sup>, namely, Nyquist-rate and oversampled A/D converters. Nyquist-rate converters are used in high-speed applications, such as video and radar signal processing, as they convert the minimum possible number of analog input signal samples to their corresponding digital counterparts. However, the precision of the analog components constituent in the hardware implementation of the Nyquist-rate A/D converters limits the resolution (i.e. the number of bits) in the digital output signal samples. Further difficulties are encountered with the anti-aliasing filter as it must realize a sharp transition band to bandlimit the input signal spectrum. Oversampled converters, on the other hand, find application in lower speed applications such as digital hearing aids, as they convert a larger number of analog input signal samples to their corresponding digital representations. As a result of taking more input signal samples, the anti-aliasing filter can be realized in a straightforward fashion. Moreover, oversampled A/D converters can achieve high-resolution by using even low tolerance analog components, making them easier to implement than their Nyquist-rate counterpart.

The present thesis is concerned with a practical representative type of oversampled A/D converters, namely, the  $\Sigma$ - $\Delta$  A/D converters. Section 1.1 introduces the process of sampling and quantization. Section 1.2 is concerned with Nyquist-rate A/D converters while Section 1.3 is concerned with oversampled A/D converters. Section 1.4 introduces the basic concepts of oversampled  $\Sigma$ - $\Delta$  A/D converters. The hardware implementation of  $\Sigma$ - $\Delta$  A/D converters is then considered in Section 1.5. Section 1.6 is concerned with a discussion of some existing problems associated with  $\Sigma$ - $\Delta$  A/D converters. Finally, an overview of this thesis is presented in Section 1.7.

## 1.1 A/D Conversion

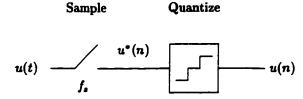

All A/D converters must convert a continuous-time continuous-amplitude (analog) signal to a discrete-time discrete-amplitude (digital) signal. The first task may be accomplished through a process called sampling, while the second task may be accomplished through a process called quantization. The general process is shown in Fig. 1.2, where an analog input signal u(t) is first sampled by a switch which opens and closes at the sampling frequency  $f_s$  to produce a discrete-time continuous-amplitude signal  $u^*(n)$ . The signal  $u^*(n)$  is then quantized to produce the digital signal u(n).

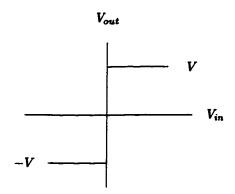

The function of the quantizer is to map a signal defined over a continuous range of amplitudes to a signal defined over a discrete set of amplitudes. The simplest quantizer is the one-bit quantizer

<sup>&</sup>lt;sup>1</sup>The same considerations apply to the corresponding D/A converters.

Figure 1.2: Generalized A/D Converter

Figure 1.3: One-Bit Quantizer

shown in Fig. 1.3, having only two output levels V and -V corresponding to the digital output '1' and '0', respectively. When the quantizer input signal is less than zero, the quantizer generates an output -V, and when the quantizer input signal is greater than or equal to zero, the quantizer generates an output V.

The quantizer is characterized by the number of output bits N and the quantization step size  $\Delta$ . The number of bits N produced by the quantizer determines the number of quantizer levels Q in accordance with

$$Q = 2^N. (1.1)$$

The quantization step size  $\Delta$  is in turn determined by the maximum output (input) signal amplitude V and the number of quantization levels Q in accordance with

$$\Delta = \frac{2V}{Q-1}. (1.2)$$

By replacing Q in Eqn. 1.2 from Eqn. 1.1, one obtains

$$\Delta = \frac{2V}{2^N - 1} \approx \frac{2V}{2^N} \quad for \quad N \gg 1. \tag{1.3}$$

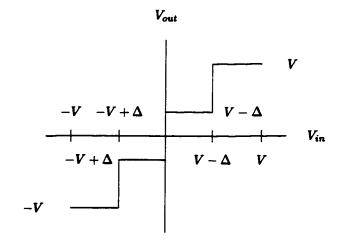

The process of quantization may be most easily described by example.

Example: A quantizer which produces a two-bit (N=2) output has four output levels Q  $(Q=2^2,$  c.f. Eqn. 1.1) corresponding to the quantizer shown in Fig. 1.4, where the quantizer step size  $\Delta$  can

Table 1.1: Quantizer Output Signal Levels

| $v(n_1)$                       | Output Level  | Output Code |

|--------------------------------|---------------|-------------|

| $-V \leq v(n_1) < -V + \Delta$ | -V            | 00          |

| $-V+\Delta \leq v(n_1)<0$      | $-V + \Delta$ | 01          |

| $0 \leq v(n_1) < V - \Delta$   | $V - \Delta$  | 10          |

| $V - \Delta \leq v(n_1) < V$   | <b>V</b>      | 11          |

Figure 1.4: Four-Bit Quantizer

be determined from Eqn. 1.3 as

$$\Delta = \frac{2V}{2^2 - 1} \tag{1.4}$$

$$=\frac{2V}{3}. (1.5)$$

Consider the quantizer input signal v(n) at sample time  $n_1$ . The corresponding output of the quantizer may be determined from Table 1.1.

As far as the sampling process is concerned, one may distinguish between two classes of A/D converters, namely Nyquist-rate A/D converters and oversampled A/D converters.

## 1.2 Nyquist-rate A/D Converters

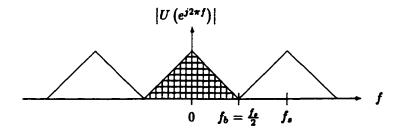

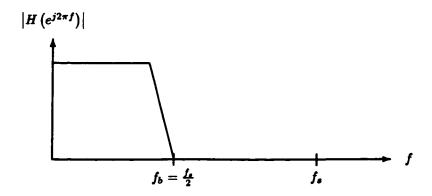

Nyquist-rate A/D converters sample the analog input signal at the Nyquist-rate  $f_s = 2f_b$ , where  $f_b$  is the highest frequency component of the input signal (Oppenheim et. al., [1]). If the input signal is not bandlimited to  $f_b$ , an anti-aliasing filter must be used before the sampling process takes place (to prevent aliasing). Figure 1.5 shows the spectrum of the sampled input signal. A typical frequency response of the anti-aliasing filter is shown in Fig. 1.6. Notice that the response of the anti-aliasing filter must have a very narrow transition band to ensure that the filtered signal is not

Figure 1.5: Frequency Spectrum of Input Signal

Figure 1.6: Anti-Aliasing Filter Requirement for Nyquist-Rate A/D Converters

magnitude distorted and does not contain any frequency components above  $\frac{L}{2}$ . The necessity of a narrow transition band makes the anti-aliasing filter difficult to realize.

Due to the nonlinear nature of the quantizer, any system employing a quantizer becomes complicated to analyse. Since the quantizer is introducing an error into the system, one may regard it as an additive white noise source, characterized by a quantization noise signal e(n), with equal probability of lying anywhere in the range  $\pm \frac{\Delta}{2}$ . As a result of this characterization, one may determine the quantization noise power to be (Candy et. al., [2])

$$\sigma_{es}^2 = \frac{\Delta^2}{12}.\tag{1.6}$$

An important performance measure of any A/D converter is the signal-to-quantization-noise ratio (SQNR). It is most generally defined as the ratio between the signal power  $\sigma_u^2$  and the quantization noise power  $\sigma_{es}^2$  as

$$SQNR = \frac{\sigma_u^2}{\sigma_{cs}^2}. (1.7)$$

By substituting Eqn. 1.3 into Eqn. 1.6, one may find the quantization noise power  $\sigma_{es}^2$  as

$$\sigma_{es}^2 = \frac{V^2}{3(2^{2N})}. (1.8)$$

By substituting Eqn. 1.8 into Eqn. 1.7, one is led to the well known result

$$SQNR_{dB} = 10log_{10}\frac{\sigma_u^2}{V^2} + 6.02N + 4.77. \tag{1.9}$$

Figure 1.7: Successive Approximation Search Path

It is easily noticed from the above equation that each additional bit of quantization increases the SQNR by 6 dB.

Example: Consider a standard compact disc which requires a sampling frequency of 44.1 kHz (to sample the 20 kHz bandlimited input signal) and 96 dB of SQNR. Using the largest sinusoidal input signal possible (with an amplitude of V and the power  $\frac{V^2}{2}$ ) and solving for N in Eqn. 1.9, one finds that a 16-bit quantizer is required (i.e. N=16).

Nyquist-rate A/D converters can fall into one of two broad categories, namely serial and parallel (J. M. Demler [3]). Typical examples of serial converters include successive approximation, bit-serial pipelined, and algorithmic A/D converters. The most popular type of Nyquist-rate A/D converter is a parallel converter known as a flash A/D converter. The basic operation of the successive approximation and flash A/D converters will be discussed in the following two subsections.

## 1.2.1 Successive Approximation A/D Converters

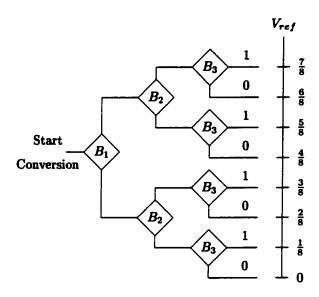

The most widely used type of Nyquist-rate A/D converter is the successive approximation converter (J. M. Demler, [3]). After each clock period, one bit of the digital word is resolved with the most-significant-bit first. This type of conversion is best described as a tree-type search as shown in Fig. 1.7 (J. M. Demler, [3]). In this example, at the start of the conversion cycle, the input voltage level  $V_{in}$  is compared to half the reference voltage  $V_{ref}$ . If  $V_{in}$  is greater than half of  $V_{ref}$ , then  $B_1$  is set to 1 and the search continues up the tree. Otherwise,  $B_1$  is set to 0 and the search continues down the tree. In this way, if  $B_1$  was set to one, then in the next iteration the input voltage level  $V_{in}$  is compared to three quarters of the reference voltage  $V_{ref}$  to determine  $B_2$ . A N-bit result requires N comparisons of this nature.

Figure 1.8: Flash A/D Generalized Architecture

## 1.2.2 Flash A/D Converters

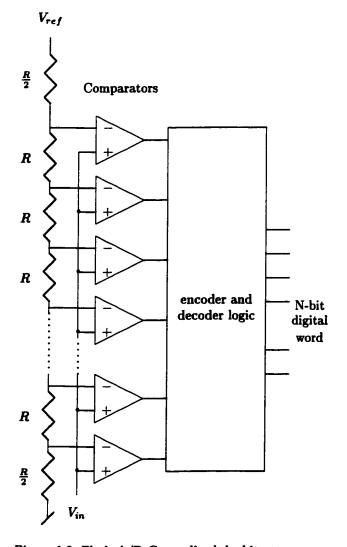

The flash A/D converter outputs a digital word every clock period, making it the fastest A/D converter (J. M. Demler, [3]). The basic flash A/D converter configuration is as shown in Fig. 1.8. For a N-bit output word,  $(2^N - 1)$  comparators are required making this type of A/D converter very expensive in terms of hardware. Every additional bit of resolution that is added doubles the amount of circuitry required, thus increasing power consumption (J. M. Demler, [3]). The resistor string is responsible for generating each quantizer voltage level from the reference voltage  $V_{ref}$ . Each comparator compares the input voltage  $V_{in}$  level to the corresponding quantizer voltage level. If the input voltage  $V_{in}$  is less than the quantizer voltage level, the comparator outputs the voltage level corresponding to the digital bit 0. Otherwise, the comparator outputs the voltage corresponding to the digital bit 1. The input to the encoder and decoder logic is a  $(2^N - 1)$  bit thermometer code which is then coded into N-bits.

Figure 1.9: Frequency Spectrum of Input Signal

Figure 1.10: Anti-Aliasing Filter Requirement for Oversampled A/D Converter

## 1.3 Oversampled A/D Converters

Oversampled A/D converters sample the input signal at a rate higher than the Nyquist-rate. The degree to which the input signal is oversampled is referred to as the oversampling ratio (OSR) defined in accordance with

$$OSR = \frac{f_s}{2f_b}. (1.10)$$

The spectrum of the sampled input signal in oversampled A/D converters is shown in Fig. 1.9. Notice that to ensure the analog input signal is bandlimited to  $f_b$ , an anti-aliasing filter with a frequency response as shown in Fig. 1.10 is required. One may notice from the figure that the transition band of the anti-aliasing filter can be significantly relaxed as compared to that of Fig. 1.6 for the Nyquistrate A/D converter. In the remainder of this thesis, it is assumed that the analog input signals to all A/D converters have been filtered by an appropriate anti-aliasing filter to avoid undesirable aliasing effects.

The noise power  $\sigma_{es}^2$  in the case of Nyquist A/D converters was given by Eqn. 1.6. In the case of oversampled A/D converters, the noise power  $\sigma_{es}^2$  is given by (Candy et. al., [2])

$$\sigma_{es}^2 = \frac{\Delta^2}{12 \times OSR}.\tag{1.11}$$

By substituting for  $\Delta$  from Eqn. 1.3 into Eqn. 1.11, and, in turn, by substituting the result into the expression for SQNR from Eqn. 1.7, one gets

$$SQNR_{dB} = 10log_{10}\frac{\sigma_u^2}{V^2} + 6.02N + 10log_{10}OSR + 4.7712.$$

(1.12)

Figure 1.11: Generic Δ-Modulator

This result implies that the noise power is inversely proportional to the sampling frequency f<sub>s</sub>. Consequently, a doubling of the sampling frequency leads to a 3 dB increase in SQNR.

Example: Consider a standard 20 kHz audio signal. In order to achieve 96 dB of SQNR, Eqn. 1.12 implies that a N=12-bit quantizer employing an oversampling ratio of OSR=160 is required (assuming a sinusoidal signal with amplitude V and with the power  $\frac{V^2}{2}$ ).

Two widely used types of oversampled A/D converters exist, namely, a)  $\Delta$ -modulators, and b)  $\Sigma$ - $\Delta$  A/D converters.

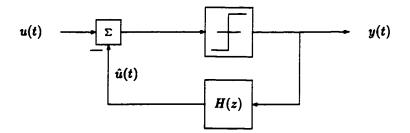

#### Oversampled $\Delta$ -Modulators 1.3.1

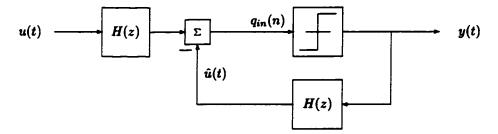

A widely used oversampled A/D converter is known as a  $\Delta$ -modulator. A simple block diagram of a  $\Delta$ -modulator is shown in Fig. 1.11 (B. P. Lathi et. al., [4]). In this configuration, the quantizer is in the feedforward path while the integrator is in the feedback path. The difference between the input signal u(t) and feedback signal  $\hat{u}(t)$  is quantized. The signal  $\hat{u}(t)$  tries to follow the input signal.  $\Delta$ -modulation suffers from a condition known as slope overload. In this condition, the input signal u(t) changes too fast for the feedback signal  $\hat{u}(t)$  to follow it. The maximum change that  $\hat{u}(t)$  can track is given by  $f_s\Delta$ , where  $f_s$  is the sampling frequency and  $\Delta$  is the quantizer step size. As an example consider a sinusoidal input signal

$$u(t) = A\cos\omega t. \tag{1.13}$$

Then, the maximum slope of the input signal u(t) may be determined as

$$\frac{du(t)}{dt} = -A\omega \sin(\omega t),\tag{1.14}$$

$$\frac{du(t)}{dt} = -A\omega \sin(\omega t), \qquad (1.14)$$

$$\left| \frac{du(t)}{dt} \right| = A\omega. \qquad (1.15)$$

In order to avoid the slope overload condition, it is required that

$$A\omega < f_{\bullet}\Delta. \tag{1.16}$$

The next section is concerned with oversampled  $\Sigma$ - $\Delta$  A/D converters, the main theme of the present thesis.

## 1.4 $\Sigma$ - $\Delta$ A/D Converters

## 1.4.1 First-Order $\Sigma$ - $\Delta$ A/D Converter

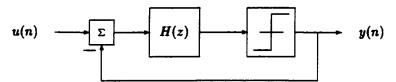

The general configuration of an oversampled  $\Sigma$ - $\Delta$  A/D converter contains a loop filter H(z) and a one-bit quantizer embedded in a feedback loop as shown in Fig. 1.12, where u(n) represents the

Figure 1.12: Generic  $\Sigma$ - $\Delta$  A/D Converter Configuration

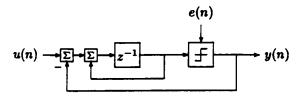

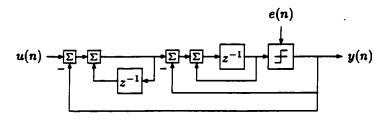

input signal and y(n) represents the corresponding output signal. In its simplest form, H(z) is an integrator as indicated in Fig. 1.13. By inspection of this  $\Sigma$ - $\Delta$  A/D converter one may obtain an expression for the output signal y(n) in terms of the input signal u(n) and quantizer noise signal e(n) (defined in Section 1.2) (Candy et. al., [2]) as

$$y(n) = u(n-1) + e(n) - e(n-1). (1.17)$$

Through the application of the z-transform, one may obtain the expression

$$Y(z) = z^{-1}U(z) + E(z)(1 - z^{-1})$$

(1.18)

where Y(z) represents the z-transformed output signal, U(z) represents the z-transformed input signal, and E(z) represents the z-transformed quantization noise.

Let us define the signal transfer function as

$$STF(z) \equiv \frac{Y(z)}{U(z)},$$

(1.19)

and the noise transfer function as

$$NTF(z) \equiv \frac{Y(z)}{E(z)}. (1.20)$$

Then, from Eqn. 1.18 it follows that

$$STF(z) = z^{-1},$$

(1.21)

Figure 1.13: Single-loop  $\Sigma$ - $\Delta$  A/D Converter Configuration

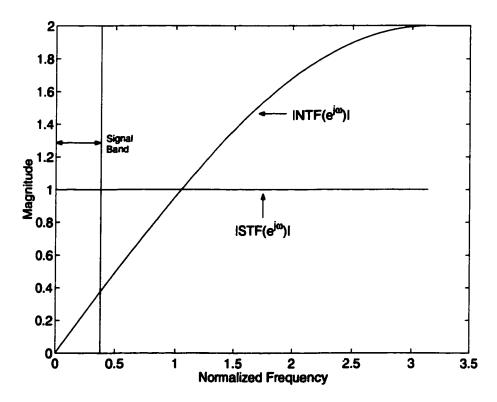

Figure 1.14: Signal and Noise Transfer Function for Single-Loop Σ-Δ A/D Converter Configuration

and

$$NTF(z) = 1 - z^{-1}. (1.22)$$

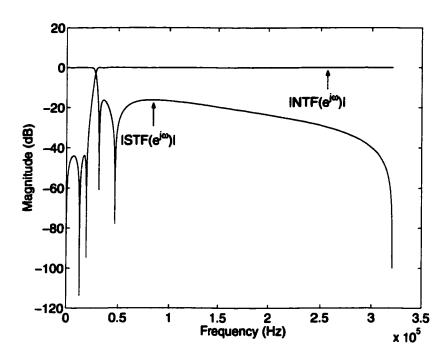

This A/D converter is referred to as a first-order  $\Sigma$ - $\Delta$  A/D converter as the maximum power of  $z^{-1}$  in the noise transfer function is 1. A magnitude-frequency plot of STF(z) and NTF(z) is shown in Fig. 1.14. As is evident from Fig. 1.14, the noise gain is very small at low frequencies (in the signal band) and becomes larger at higher frequencies. For this reason,  $\Sigma$ - $\Delta$  A/D converters are known as noise shaping converters, meaning that the noise is shaped away from the signal band. Furthermore, since the noise has a highpass characteristic, this converter is known as a lowpass  $\Sigma$ - $\Delta$  A/D converter. As explained in the previous section, the quantizer may be replaced by a uniformly distributed additive white noise source e(n). An analysis of the first-order  $\Sigma$ - $\Delta$  A/D converter reveals that the quantization noise is given by (Candy et. al., [2])

$$\sigma_{es}^2 = \frac{\Delta^2 \pi^2}{12 3} (2 \frac{f_b}{f_s})^3. \tag{1.23}$$

Substituting the definition of OSR given by Eqn. 1.10 into the definition of SQNR given by Eqn. 1.7 results in

$$SQNR_{dB} = 10log_{10}\frac{\sigma_{u}^{2}}{V^{2}} + 30log_{10}OSR - 0.4.$$

(1.24)

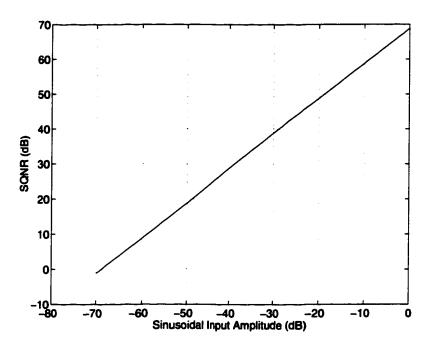

Figure 1.15: Theoretical SQNR versus Input Signal Amplitude

From the above equation, each doubling of the oversampling ratio improves the SQNR by 9 dB.

A plot of Eqn. 1.24 is shown in Fig. 1.15 for OSR = 256. As evident from Fig. 1.15 the peak-SQNR (PSQNR) of 68.8 dB is achieved with an input amplitude of 1. It is expedient at this time to define the dynamic range (DR) as the negative of the input amplitude where 0 dB SQNR is achieved (Norsworthy et. al., [5]). In this case a DR of 68.8 dB is observed.

Example: Consider a standard 20 kHz audio signal. If a SQNR of 96 dB is to be achieved, Eqn. 1.24 implies a sampling frequency of 81.92 MHz is required (assuming a sinusoidal signal of amplitude V and the power  $\frac{V^2}{2}$ ).

## 1.4.2 Motivation for $\Sigma$ - $\Delta$ A/D Converters

The main motivation behind employing  $\Sigma$ - $\Delta$  A/D converters is the ability to obtain high SQNRs by using a very simple (coarse) one-bit quantizer. Furthermore, the A/D converter may be implemented using high tolerance analog components, implying that they are not sensitive to noise and interference.

## 1.4.3 Disadvantages of $\Sigma$ - $\Delta$ A/D Converters

From the generic  $\Sigma$ - $\Delta$  A/D converter shown in Fig. 1.12, it is possible to rearrange the loop filter H(z) and produce the equivalent model shown in Fig. 1.16. Notice that the  $\Delta$ -modulator is exactly the same as the  $\Sigma$ - $\Delta$  A/D converter with the exception that the input signal u(t) is filtered by H(z) before the summing block.

Given that  $\Sigma$ - $\Delta$  A/D converters are based on  $\Delta$ -modulators, a similar phenomenon to slope

Figure 1.16: Generic  $\Sigma$ - $\Delta$  A/D Converter Configuration

Figure 1.17: A Second-order  $\Sigma$ - $\Delta$  A/D Converter

overload is observed, namely, instability. In (Borsodi, [6]), the quantizer is said to be overloaded when

$$|q_{in}(n)| > Q\frac{\Delta}{2}, \tag{1.25}$$

where  $q_{in}(n)$  represents the input signal to the quantizer. As a result it was shown in (Borsodi, [6]) that in the case of a first-order  $\Sigma$ - $\Delta$  A/D converter, the maximum input amplitude  $A_1$  is defined in accordance with

$$A_1 \le (Q-1)\frac{\Delta}{2}.\tag{1.26}$$

When this relationship is not satisfied, the  $\Sigma$ - $\Delta$  A/D converter exhibits unstable operation. In higher-order  $\Sigma$ - $\Delta$  A/D converters, no analytic solution of the maximum input signal exists and must be discovered through extensive simulations. Therefore, the design of stable higher-order  $\Sigma$ - $\Delta$  A/D converters is usually done through a trial-and-error process by experienced designers.

## 1.4.4 Higher-Order $\Sigma$ - $\Delta$ A/D Converters

The motivation to employ higher-order  $\Sigma$ - $\Delta$  A/D converters is to obtain an improvement in the noise attenuation in the signal band without increasing the sampling frequency. As a result of this improved noise attenuation, the SQNR is increased as compared to the first-order  $\Sigma$ - $\Delta$  A/D converter. The simplest case of a higher-order converter is the second-order  $\Sigma$ - $\Delta$  A/D converter shown in Fig. 1.17.

The output of this type of  $\Sigma$ - $\Delta$  A/D converter can be determined to be (Candy et. al., [2])

$$y(n) = u(n-1) + (e(n) - 2e(n-1) + e(n-2)). \tag{1.27}$$

Figure 1.18: Cascaded  $\Sigma$ - $\Delta$  A/D Converter Configuration

A further analysis of this A/D converter reveals that the quantization noise power is given by (Candy et. al., [2])

$$\sigma_{es}^2 = \frac{\Delta^2 \pi^4}{12} \frac{f_b^5}{5 f_s}.$$

(1.28)

By employing a one-bit quantizer, the following expression is obtained for SQNR

$$SQNR_{dB} = 10log_{10}\frac{\sigma_u^2}{V_2} + 1.82 + 50log_{10}OSR.$$

(1.29)

This result implies that the SQNR is increased by 15 dB for every doubling of the oversampling ratio (OSR).

Example: Consider a standard 20 kHz audio signal. If a SQNR of 96 dB is to be achieved, Eqn. 1.29 implies that a sampling frequency of only 3.52 MHz is required (assuming a sinusoidal signal of amplitude V and the power  $\frac{V^2}{2}$ ).

## 1.4.5 Cascaded $\Sigma$ - $\Delta$ A/D Converters

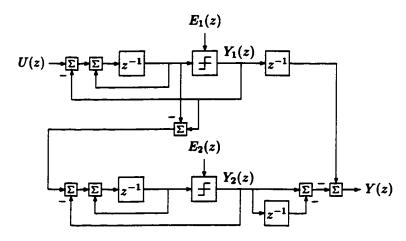

A very widely used form of  $\Sigma$ - $\Delta$  A/D converters is the cascaded configuration shown in Fig. 1.18 (Aziz et. al., [7]). In this configuration, the quantization error from the first converter is the input to the second converter. The output signal from each converter is then summed in an attempt to cancel the noise from the first converter. A simple analysis of the configuration leads to the following expressions for the two quantizer output signals  $Y_1(z)$  and  $Y_2(z)$

$$Y_1(z) = U(z)z^{-1} + E_1(z)(1-z^{-1}), (1.30)$$

$$Y_2(z) = E_1(z)z^{-1} + E_2(z)(1-z^{-1}). (1.31)$$

The overall output of the system is given by

$$Y(z) = Y_1(z)z^{-1} - Y_2(z)(1 - z^{-1})$$

(1.32)

$$=U(z)z^{-2}-E_2(z)(1-z^{-1})^2. (1.33)$$

Notice from Eqn. 1.33 that the noise term  $E_1(z)$  has been eliminated. In this way, the noise in the output signal Y(z) has been reduced without resorting to higher order structures where stability may be a problem. However, this type of configuration is highly susceptible to component mismatches (Aziz et. al., [7]).

## 1.4.6 Bandpass $\Sigma$ - $\Delta$ A/D Conversion

Thus far, only lowpass  $\Sigma$ - $\Delta$  A/D converters have been discussed. In particular, the noise transfer function has had a highpass magnitude-frequency characteristic while the signal transfer function has had a lowpass magnitude-frequency characteristic. Another type of converter is known as a bandpass  $\Sigma$ - $\Delta$  A/D converter, as first introduced in (Schreier et. al., [8]). This type of converter features a bandstop noise transfer function and a bandpass signal transfer function. Such converters find applications in AM digital radios or receivers for digital cellular mobile radios (Aziz et. al., [7]).

Recall that in the case of lowpass  $\Sigma$ - $\Delta$  A/D converters, the oversampling ratio is a function of both the sampling frequency  $f_s$  and the bandlimiting frequency  $f_b$  of the input signal. In order to have a large oversampling ratio with a high bandlimiting frequency  $f_b$ , the sampling frequency  $f_s$  must also be large.

Example: Assume OSR = 64 and  $f_b = 400$  kHz. In accordance with the definition of OSR from Eqn. 1.10, a sampling frequency of  $f_s = 51.2$  MHz must be employed.

In the case where the input signal does not have frequency content in the region 0 to  $f_a$  ( $f_a \ll f_b$ ), noise may be shaped into this region. The oversampling ratio is then defined as

$$OSR' = \frac{f_s}{2(f_b - f_a)}. ag{1.34}$$

In this way, the oversampling ratio is a function of the sampling frequency  $f_a$  and the signal bandwidth  $f_b - f_a$  (as opposed to the bandlimiting frequency  $f_b$  only). As a result, if the bandlimiting frequency  $f_b$  is large, as long as  $f_a \gg 0$ , the sampling frequency does not need to be excessively large.

Example: Assume OSR = 64,  $f_b = 400$  kHz, and  $f_a = 300$  kHz. In accordance with the definition of OSR' from Eqn. 1.34, a sampling frequency of  $f_a = 12.8MHz$  must be employed.

In the case of lowpass A/D converters, the noise was attenuated at frequencies in the range 0 to  $f_b$ . This was done by placing the zeros of the noise transfer function in this frequency range. In the case of bandpass A/D converters, on the other hand, the signal occupies a frequency range  $f_a$  to  $f_b$ , where  $f_a < f_b$ . In this way, the noise may occupy the frequencies from 0 to  $f_a$  and from  $f_b$  to  $f_a/2$ . To facilitate this characteristic, the zeros of the noise transfer function must be moved to the frequency region  $f_a$  to  $f_b$ .

Feedforward and multiple-feedback  $\Sigma$ - $\Delta$  A/D converters are a class of converters which are capable of realizing bandpass signal transfer functions and bandstop noise transfer functions. Typical examples include the cascade-of-integrators, the cascade-of-resonators, and their combination, namely the cascade-of-resonators/integrators (see Section 3.2).

Figure 1.19: First-Order  $\Sigma$ - $\Delta$  A/D Converter SC Hardware Implementation

## 1.5 Switched-Capacitor Hardware Implementation of Oversampled $\Sigma$ - $\Delta$ A/D Converter Configurations

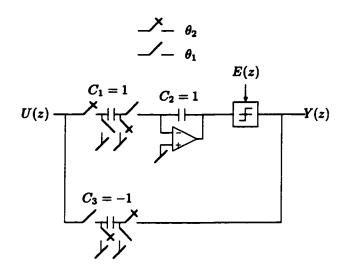

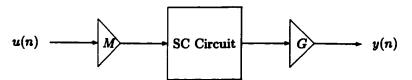

For the most part,  $\Sigma$ - $\Delta$  A/D converters are implemented using switched-capacitor (SC) circuits (Candy et. al., [2]). Such circuits are widely used in digital signal processing and are relatively cheap to manufacture as compared to continuous-time implementations. Furthermore, SC circuit hardware implementations are advantageous for low-power low-voltage applications (Shahriar et. al., [9]).

Consider the SC hardware implementation of the first-order  $\Sigma$ - $\Delta$  A/D converter shown in Fig. 1.19. An analysis of this circuit reveals that

$$\frac{Y(z)}{U(z)} = \frac{\frac{C_1}{C_2}}{z - 1 - \frac{C_3}{C_2}},\tag{1.35}$$

$$\frac{Y(z)}{E(z)} = \frac{z - 1}{z - 1 - \frac{C_3}{C_2}}. (1.36)$$

When  $C_1 = 1$ ,  $C_2 = 1$ , and  $C_3 = -1$ , the signal and noise transfer functions are equivalent to those previously determined for the first-order  $\Sigma$ - $\Delta$  A/D converter. However, during the manufacturing process, these capacitors may differ from their nominal values by up to 0.5% (Schreier et. al., [10]). As a result, different signal and noise transfer functions are realized which may affect the achievable SQNR and dynamic range performance of the A/D converter. In fact, the effect of capacitor tolerances may even result in unstable A/D converter operation.

## 1.6 Open Problems in $\Sigma$ - $\Delta$ A/D Conversion

### 1.6.1 Design

The design of  $\Sigma$ - $\Delta$  A/D converters is heavily based on a trial-and-error process. After a signal and noise transfer function have been obtained (by approximation), extensive simulations are required to ensure that the A/D converter provides adequate SQNR and DR performance. In addition, Monte-Carlo analysis is required to determine the effect of capacitor mismatches in a corresponding SC hardware implementation on the achievable SQNR, DR, and stability performance of the resulting A/D converter. Several attempts have been made to address the problem of achieving a desired SQNR and DR performance level. These attempts rely on extensive simulations to determine a set of guidelines relating the oversampling ratio and the order of the converter to the achievable SQNR. The most notable set of guidelines was made by (Kuo et. al., [11]). Other attempts by (Lee, [12]) and (W. M. Snelgrove et. al., [13]) amount to limiting the out-of-band noise transfer function gain so as to achieve high stability. However, the design of high-resolution, high-dynamic range oversampled  $\Sigma$ - $\Delta$  A/D converters having low sensitivity to capacitor mismatches in a corresponding SC hardware implementation still remains an open problem.

## 1.6.2 Stability Prediction

As mentioned in the previous subsection, the successful design of  $\Sigma$ - $\Delta$  A/D converters is heavily dependent on extensive simulations to determine the achievable SQNR and dynamic range. The problem of predicting dynamic range has also been studied in the hitherto literature, the most notable was the statistical estimation technique by (Ardalan et. al., [14]). This technique provides an estimation of the maximum DC input signal to the A/D converter. However, this technique is suitable for  $\Sigma$ - $\Delta$  A/D converters having Gaussian distributed quantizer input signals. Extending this technique to arbitrarily distributed quantizer input signals still remains an open problem.

## 1.7 Overview of the Thesis

Chapter 2 is concerned with the characterization of five practical feedforward and multiple-feedback  $\Sigma$ - $\Delta$  A/D converter configurations. These configurations are characterized in terms of two important features, namely, a) the location of their noise transfer function zeros with respect to the unit-circle in the complex z-plane, and b) the relationship between their constituent signal and noise transfer functions.

Chapter 3 presents a design procedure for feedforward and multiple-feedback  $\Sigma$ - $\Delta$  A/D converter configurations. This design procedure is based on a set of high-level system design specifications and proceeds in a step-by-step manner. Each of the five feedforward and multiple-feedback A/D converters are then designed and simulated to determine, a) the effect of the noise transfer function zeros on the achievable SQNR and dynamic range (DR), and b) the effect of capacitor mismatch on

the SQNR and DR in a corresponding SC hardware implementation using Monte-Carlo analysis. To estimate the maximum DC input signal level, a hitherto statistical technique is employed. This statistical technique is based on several assumptions, the most restricting of which is that the quantizer input signal is Gaussian distributed. A novel statistical approach is then presented which generalizes the hitherto technique to the case of arbitrary quantizer input signal distributions. Design examples are presented to demonstrate and compare the hitherto and proposed statistical techniques.

Chapter 4 is concerned with the design and realization of a novel class of  $\Sigma$ - $\Delta$  A/D converters based on magnitude-squared or magnitude complementary signal and noise transfer functions. These novel  $\Sigma$ - $\Delta$  A/D converter configurations are obtained by modifying the existing configurations.

Chapter 5 is concerned with an investigation of the proposed class of  $\Sigma$ - $\Delta$  A/D converters. It is demonstrated that the A/D converters in this class exhibit a high degree of stability in the presence of capacitor mismatches in their corresponding SC hardware implementation when compared to the existing converters. It will further be demonstrated that the achievable SQNR and DR remain very similar to that achieved by the feedforward and multiple feedback converters.

Chapter 6 presents the final conclusions of this thesis and presents some research topics suitable for future work.

## Chapter 2

# Feedforward and Multiple-feedback $\Sigma$ - $\Delta$ A/D Converter Configurations

## 2.1 Introduction

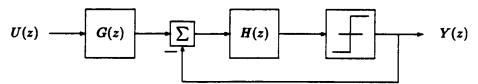

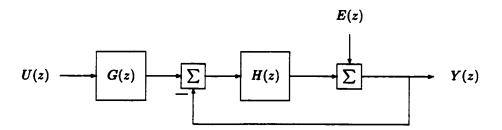

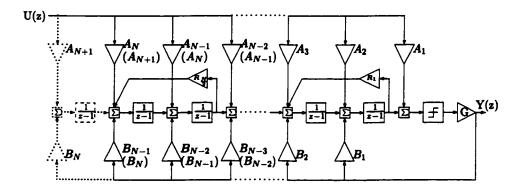

A generic  $\Sigma$ - $\Delta$  A/D converter is shown in Fig. 2.1, where U(z) represents the z-transformed input signal, and where Y(z) represents the z-transformed output signal. In design situations, the

Figure 2.1: Generic  $\Sigma$ - $\Delta$  A/D Converter Configuration

Figure 2.2: Generic Linear  $\Sigma$ - $\Delta$  A/D Converter Configuration

constituent quantizer is usually replaced by a uniformly distributed additive white noise source (Candy et. al., [2]) as shown in Fig. 2.2, where E(z) represents the (z-transformed) quantization noise. Then, the A/D converter may be characterized by the signal transfer function STF(z) and the noise transfer function NTF(z) in accordance with

$$STF(z) = \frac{G(z)H(z)}{1 - H(z)} \equiv G(z)\frac{S(z)}{D(z)},$$

(2.1)

$$NTF(z) = \frac{1}{1 - H(z)} \equiv \frac{N(z)}{D(z)}.$$

(2.2)

From the definition of NTF(z) given in Eqn. 2.2, one may express H(z) in accordance with

$$H(z) = \frac{N(z) - D(z)}{N(z)}.$$

(2.3)

By substituting this expression for H(z) into Eqn. 2.1, one gets

$$STF(z) = \frac{G(z)\left(N(z) - D(z)\right)}{D(z)}. (2.4)$$

If G(z) is assumed to be a polynomial in z, then one may note from Eqns. 2.4 and 2.2 that the signal and noise transfer functions share a common denominator. Furthermore, if G(z) = 1 then, the numerator of the signal transfer function may be formed in accordance with,

$$S(z) = N(z) - D(z). \tag{2.5}$$

A relationship between the signal and noise transfer functions may then be formed in accordance with

$$NTF(z) - STF(z) = 1. (2.6)$$

When a given signal and noise transfer function satisfy Eqn. 2.6, they are said to be complementary transfer functions. One of the main practical advantages of such a pair of transfer functions is that by deriving the noise transfer function (or the signal transfer function) the signal transfer function (or the noise transfer function) can be easily obtained from Eqn. 2.6, thus eliminating the need to derive both transfer functions.

It is expedient to recast the polynomial D(z) in the form

$$D(z) = \mathcal{Z}^T \mathcal{D},\tag{2.7}$$

and the polynomials N(z) and S(z) in the forms

$$N(z) = \mathcal{Z}^T \mathcal{N},\tag{2.8}$$

$$S(z) = \mathcal{Z}^T \mathcal{S},\tag{2.9}$$

where  $\mathcal{Z}^T = [z^0, z^{-1}, z^{-2}, \dots, z^{-N}]$ , where  $\mathcal{D}$ ,  $\mathcal{N}$ , and  $\mathcal{S}$  are column vectors of length (N+1) whose entries depend on the system parameters of the  $\Sigma$ - $\Delta$  A/D converter, and where N is the order of the A/D converter. In this way, by invoking Eqns. 2.7, 2.8, and 2.9 in Eqn. 2.5, one obtains

$$\mathcal{D} = \mathcal{N} - \mathcal{S}.\tag{2.10}$$

In addition to the relationship between the signal and noise transfer functions, the position of the noise transfer function zeros is also of particular practical interest. The zeros of the noise transfer function NTF(z) are directly related to the poles of the loop transfer function H(z). For maximum noise attenuation, the zeros of the noise transfer function must be located directly on the unit circle.

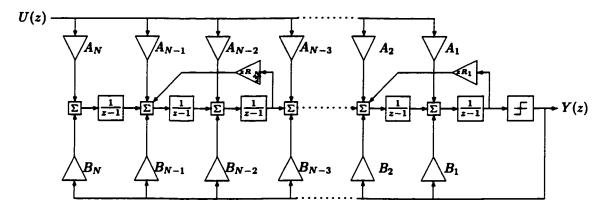

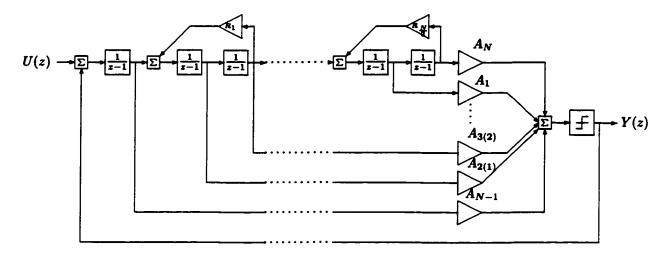

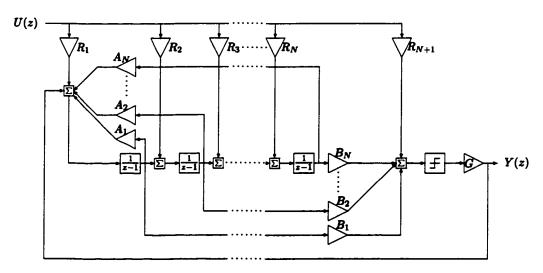

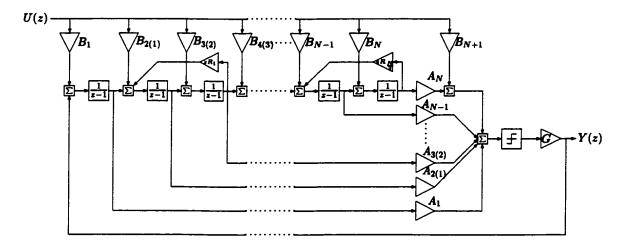

Figure 2.3: Cascade-of-Integrators  $\Sigma$ - $\Delta$  A/D Converter Configuration

This chapter is concerned with characterization and practical realization of five widely used feedforward and multiple-feedback  $\Sigma$ - $\Delta$  A/D converter configurations. In particular, Section 2.2 introduces these  $\Sigma$ - $\Delta$  A/D converter configurations, and characterizes them in terms of the complementarity of their signal and noise transfer functions and in terms of the location of their noise transfer function zeros. It will be shown that three cases exist with respect to the complementarity of the signal and noise transfer functions and that three different cases exist with respect to the location of the noise transfer function zeros. In addition, a technique is presented to determine the parameters of each  $\Sigma$ - $\Delta$  A/D converter configuration starting from given signal and/or noise transfer functions. Finally, a simple method is described for obtaining the corresponding SC hardware implementation associated with each  $\Sigma$ - $\Delta$  A/D converter configuration.

## 2.2 Five Widely Used Feedforward and Multiple-Feedback $\Sigma$ - $\Delta$ A/D Converter Configurations

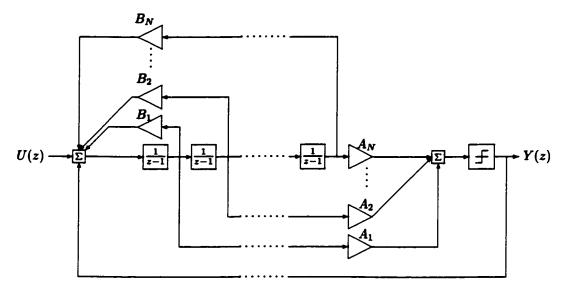

### 2.2.1 Cascade-of-Integrators $\Sigma$ - $\Delta$ A/D Converter Configuration

The cascade-of-integrators (COI)  $\Sigma$ - $\Delta$  A/D converter configuration, developed in (Lee et. al., [15]) and shown in Fig. 2.3, features both feedforward and feedback signal paths. In order to determine the contribution of the multiplier coefficients  $A_{1-N}$  and  $B_{1-N}$  on the signal and noise transfer functions, a detailed analysis of the COI  $\Sigma$ - $\Delta$  A/D converter configuration can be undertaken. The results of this analysis show that the numerator of the signal transfer function is given by

$$S(z) = \sum_{i=1}^{N} A_i (z-1)^{N-i}, \qquad (2.11)$$

the numerator of the noise transfer function is given by

$$N(z) = (z-1)^{N} - \sum_{i=1}^{N} B_{i}(z-1)^{N-i}, \qquad (2.12)$$

and the denominator of the signal and noise transfer functions is given by

$$D(z) = N(z) - S(z). (2.13)$$

Evidently, the COI  $\Sigma$ - $\Delta$  A/D converter configuration guarantees the complementarity of the signal and noise transfer functions (c.f. Eqns. 2.13 and 2.5). Furthermore, the multiplier coefficients  $B_{1-N}$  determine the location of the noise transfer function zeros and the multiplier coefficients  $A_{1-N}$  determine the location of the signal transfer function zeros (c.f. Eqns. 2.12 and 2.11, respectively).

To realize a given signal or noise transfer function, one must determine the corresponding A and B multiplier values. It can be shown that these multiplier values are given in accordance with

$$\mathcal{A}^T = \mathcal{C}_{1COI}^{-1} \mathcal{S} \tag{2.14}$$

$$\mathcal{B}^T = \mathcal{C}_{2COI}^{-1} \mathcal{N}, \tag{2.15}$$

where  $\mathcal{A} = [0, A_1, A_2, \dots, A_N]$ , where  $\mathcal{B} = [1, B_1, B_2, \dots, B_N]$ , and where  $\mathcal{C}_{1COI}$  and  $\mathcal{C}_{2COI}$  are  $(N+1) \times (N+1)$  matrices. Moreover, the matrices  $\mathcal{C}_{1COI}$  and  $\mathcal{C}_{2COI}$  may be determined as described in the following.

First, let us form the polynomials  $L_i(z) = (1 - z^{-1})^i$  for  $i = 1, 2, \dots, N$ . Then, by recasting these polynomials in the form  $L_i(z) = \mathcal{Z}^T \mathcal{L}_i$ , one obtains the column vectors  $\mathcal{L}_i$  of length (i + 1). It can be shown that the matrices  $\mathcal{C}_{1COI}$  and  $\mathcal{C}_{2COI}$  have the forms

$$C_{1COI} = \begin{bmatrix} 0 & 0 & 0 & \cdots & 0 & 0 \\ 0 & \mathcal{L}_{N-1} & 0 & \cdots & 0 & 0 \\ 0 & & \mathcal{L}_{N-2} & \ddots & 0 & 0 \\ \vdots & & & \ddots & \vdots & \vdots \\ 0 & & & \mathcal{L}_{1} & 0 \\ 0 & & & & \mathcal{L}_{0} \end{bmatrix}$$

$$(2.16)$$

$$C_{2COI} = \begin{bmatrix} \mathcal{L}_{N} & 0 & 0 & \cdots & 0 \\ -\mathcal{L}_{N-1} & 0 & \cdots & 0 \\ & -\mathcal{L}_{N-2} & \ddots & 0 \\ & & \ddots & \vdots \\ & & -\mathcal{L}_{0} \end{bmatrix}$$

(2.17)

The salient features of these matrices are, a) they are lower triangular, reducing the computational cost required for their inversion, and b) they are independent of the multiplier coefficients A and B.

As an example, by considering the case of N = 4, one has

$$C_{1COI} = \begin{bmatrix} 0 & 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 & 0 \\ 0 & -3 & 1 & 0 & 0 \\ 0 & 3 & -2 & 1 & 0 \\ 0 & -1 & 1 & -1 & 1 \end{bmatrix}$$

(2.18)

and

$$C_{2COI} = \begin{vmatrix} 1 & 0 & 0 & 0 & 0 \\ -4 & -1 & 0 & 0 & 0 \\ 6 & 3 & -1 & 0 & 0 \\ -4 & -3 & 2 & -1 & 0 \\ 1 & 1 & -1 & 1 & -1 \end{vmatrix}.$$

(2.19)

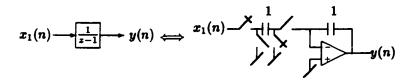

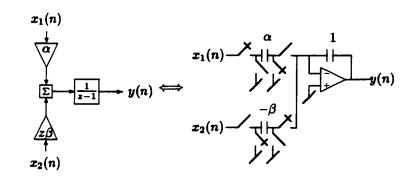

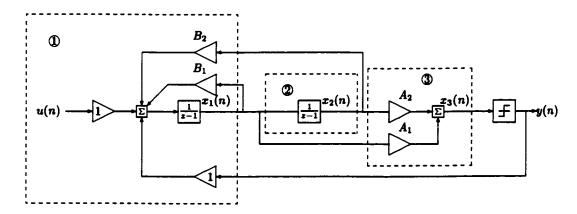

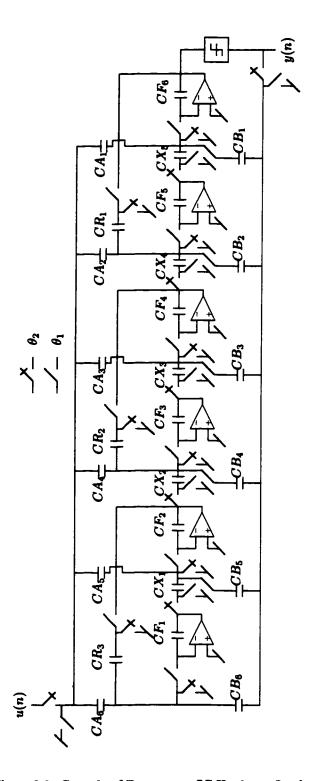

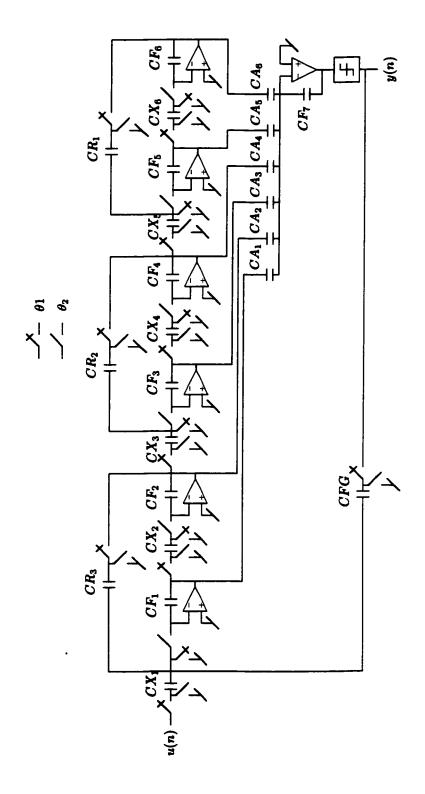

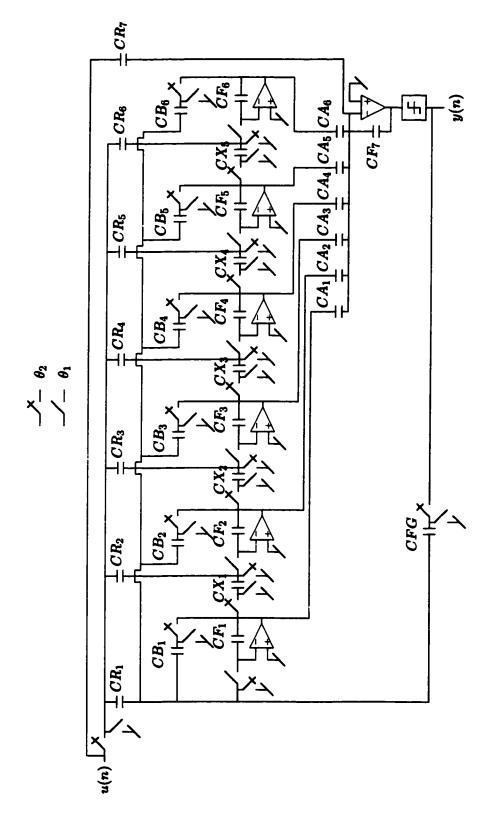

The COI Σ-Δ A/D converter configuration must be replaced to its corresponding SC hardware implementation for practical realization. By inspection of the COI A/D converter configuration, one may note that the configuration is composed of three primary elements, namely, a) an integrator, b) a multiple weighted input adder, and c) a combined adder (with multiple weighted inputs ¹) and an integrator. The corresponding SC hardware implementation of each of these elements is shown in Fig. 2.4. As an example consider the 2-nd order COI A/D converter configuration shown in Fig. 2.5, where the each primary element has been enclosed in a dashed box. Then, by replacing the primary elements by their corresponding SC hardware implementations as shown in Fig. 2.4, one obtains the overall SC hardware implementation of the second-order COI A/D converter configuration as shown in Fig. 2.6, where the dashed boxes enclose the corresponding SC hardware primary elements.

<sup>&</sup>lt;sup>1</sup>Later in this chapter it will be shown that some inputs to the adder are weighted by a constant and a unit-advance term z.

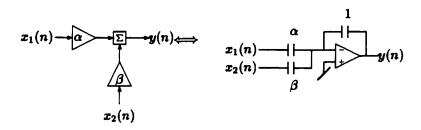

Figure 2.4: Basic SC Hardware Implementation Building Blocks

Figure 2.5: Identification of the Primary Elements in a 2-nd Order COI A/D Converter

Figure 2.6: Corresponding SC Hardware Implementation of a 2-nd Order COI  $\Sigma$ - $\Delta$  A/D Converter

Table 2.1: Cascade-of-Integrator Nominal Capacitor Values

| Capacitor       | Value | Capacitor       | Value | Capacitor  | Value | Capacitor       | Value |

|-----------------|-------|-----------------|-------|------------|-------|-----------------|-------|

| $CB_1$          | $B_1$ | $CA_1$          | $A_1$ | $CX_1$     | 1     | $CF_1$          | 1     |

| CB <sub>2</sub> | $B_2$ | CA <sub>2</sub> | $A_2$ | CX2        | 1     | CF <sub>2</sub> | 1     |

| :               | :     | :               | :     |            | :     | :               | :     |

| $CB_N$          | $B_N$ | $CA_N$          | $A_N$ | $CX_{N+1}$ | 1     | $CF_{N+1}$      | 1     |

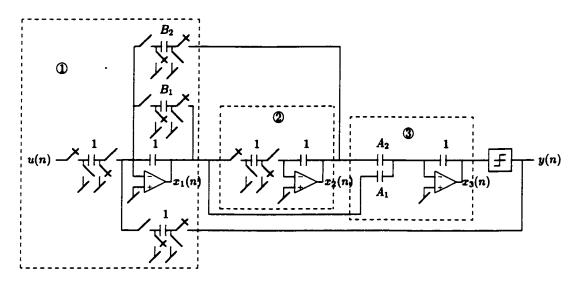

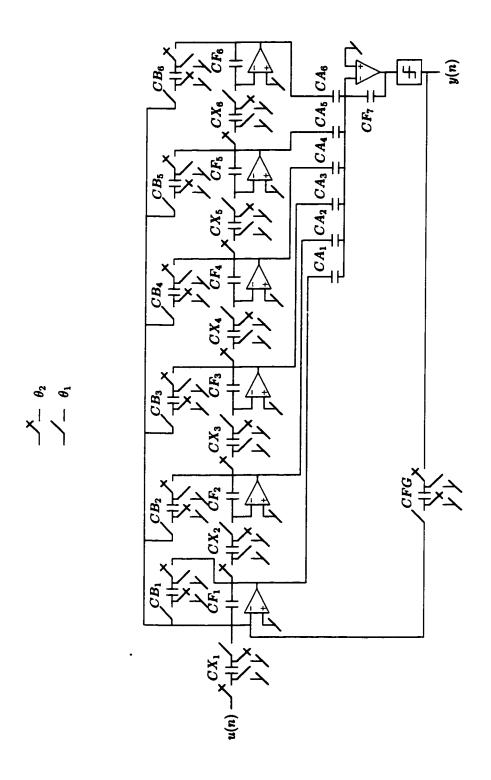

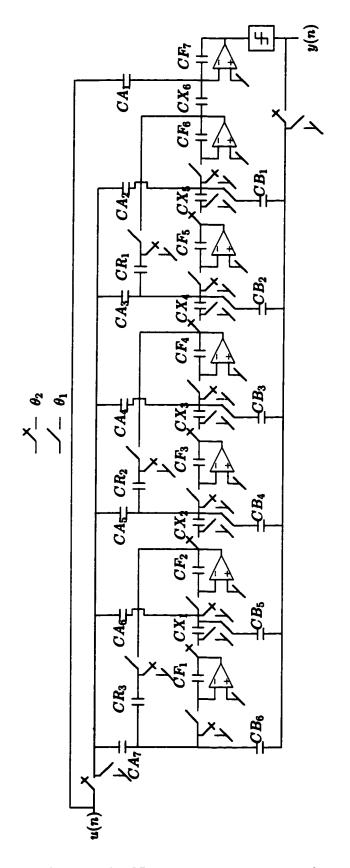

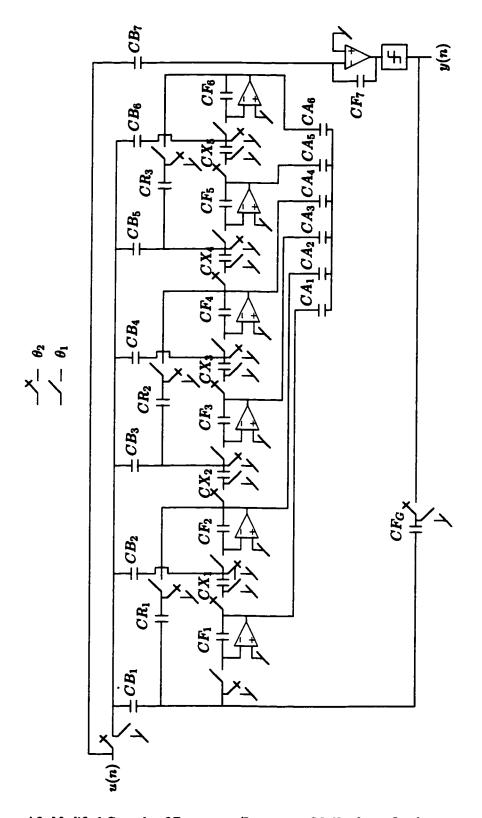

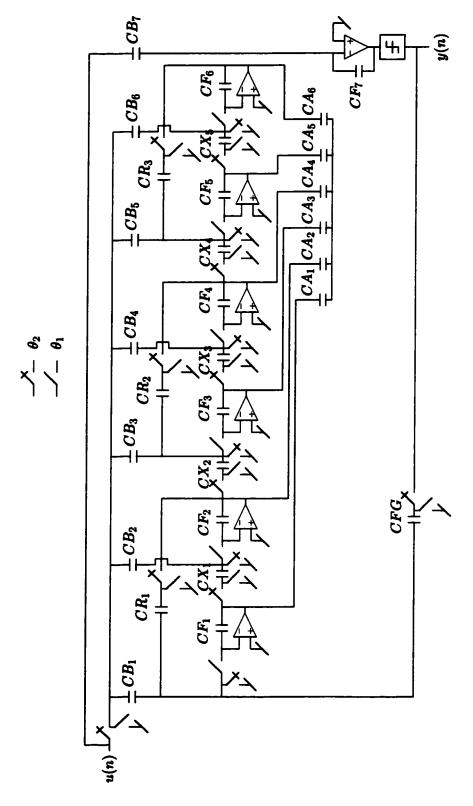

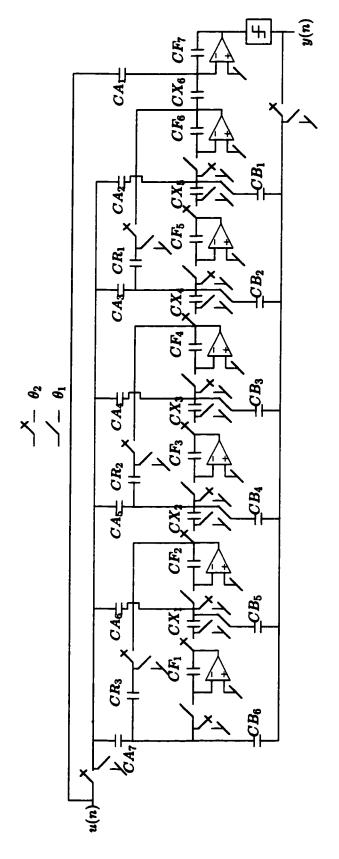

Applying the building blocks in Fig. 2.4 to a 6-th order COI A/D converter, one arrives at the SC hardware implementation shown in Fig. 2.7 where the nominal capacitor values are given in Table 2.1  $^2$ . In this way, (N+1) operational amplifiers are required for the implementation of an N-th order COI  $\Sigma$ - $\Delta$  A/D converter.

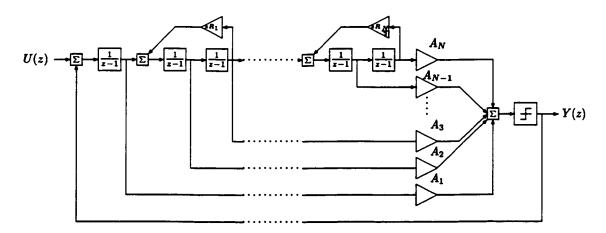

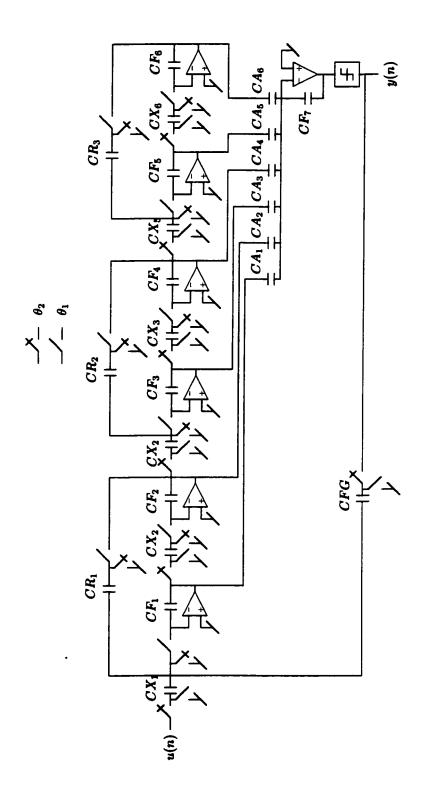

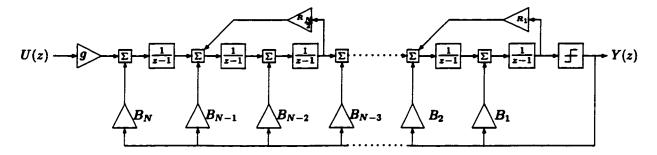

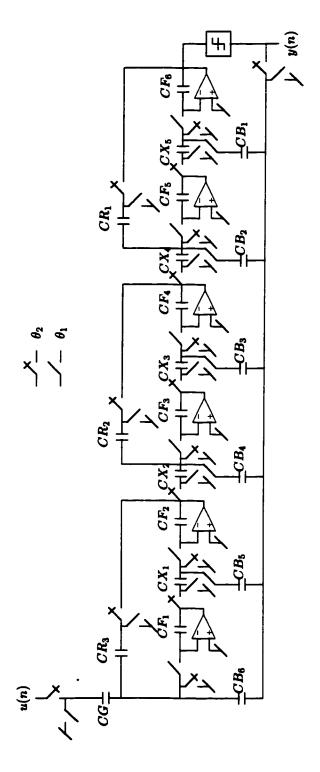

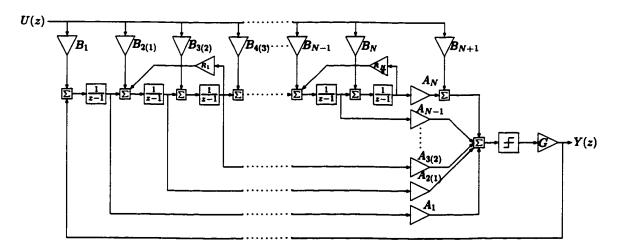

### 2.2.2 Cascade-of-Resonators $\Sigma$ - $\Delta$ A/D Converter Configuration

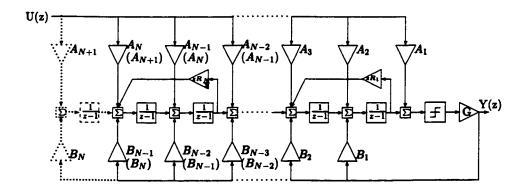

The cascade-of-resonators (COR)  $\Sigma$ - $\Delta$  A/D converter configuration shown in Fig. 2.8 first appeared in (Adams et. al., [16]), where it was used as a lowpass  $\Sigma$ - $\Delta$  A/D converter. This type of configuration is commonly referred to as an inverted configuration (due to the nature of the feedback path) and offers the advantage of no additional summing element (op-amp) which exists in the non-inverted COI  $\Sigma$ - $\Delta$  A/D converter <sup>3</sup>. This configuration was later successively employed for the realization of bandpass  $\Sigma$ - $\Delta$  A/D converters in (R. Schreier et. al., [10]) and subsequently in (W. M. Snelgrove et. al., [13]).

The COR  $\Sigma$ - $\Delta$  A/D converter configuration automatically places the zeros of NTF(z) on the unit-circle in accordance with (Botteron et. al., [17])

$$N(z) = \prod_{k=1}^{\frac{N}{2}} \left[ 1 - (2 + R_k)z^{-1} + z^{-2} \right], \qquad (2.20)$$

for even orders N and

$$N(z) = (1 - z^{-1}) \prod_{k=1}^{\left\lfloor \frac{N}{2} \right\rfloor} (1 - (2 + R_k)z^{-1} + z^{-2})$$

(2.21)

for odd orders N. Evidently, the zeros of NTF(z) depend on the values of multiplier coefficients  $R_k$  (for  $k = 1, 2, ..., \lfloor \frac{N}{2} \rfloor$ ) only.

Further analysis of the COR  $\Sigma$ - $\Delta$  A/D converter configuration leads to the expressions for S(z)

<sup>&</sup>lt;sup>2</sup>In the practical realisation of the SC hardware implementation, the capacitor values are scaled and will not directly correspond to the multiplier coefficients to be discussed in Chapter 3.

<sup>&</sup>lt;sup>3</sup>This summing element also appears in the non-inverted CRI and FF Σ-Δ A/D configurations to be discussed later

Figure 2.7: Cascade-of-Integrators SC Hardware Implementation

Figure 2.8: Cascade-of-Resonators  $\Sigma$ - $\Delta$  A/D Converter Configuration

and D(z) as

$$S(z) = \sum_{i=1}^{\frac{N}{2}} (A_{2i-1}z + (-A_{2i-1} + A_{2i}))$$