Enhancement-mode Polar Sourced Gallium Nitride MOSFET

by

Kyle M. Bothe

A thesis submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in

Solid State Electronics

Department of Electrical and Computer Engineering University of Alberta

© Kyle M. Bothe, 2015

### Abstract

All commercially fabricated Gallium Nitride (GaN) based power transistors to date have been heterojunction field effect transistors (HFET). The major down fall of this design architecture is the inability to produce an inherently true normally-off device. The more traditional metal-oxide-semiconductor field effect transistor (MOSFET) design has the potential for power efficiency and enhancement-mode device operation. GaN has been touted as the next promising semiconductor for use in high frequency and high power applications. Various potential applications range from low frequency switching solid state transformers to inverters beyond 10 GHz frequency. These devices require high current densities, large breakdown voltages and the ability to operate in high temperature environments. Modern HFET technology has higher off-state leakage current caused from the minimum carrier density under the channel being larger than a conventional depleted GaN MOSFET. This behavior is crucial for high power applications as the off-state power consumption has become one of the essential design parameters. To date, the limiting factors of producing a GaN MOSFET are the fabrication issues associated to essential components within the MOSFET architecture; a high quality gate dielectric and a large concentration of electrons along the source and drain.

Over the past decade, gate dielectrics grown on GaN have been extensively studied to obtain low interface defects, low leakage current and high channel mobility. Numerous fabrication methods have been attempted to produce an interface worthy for a device; however, the quality of the dielectrics on GaN have been insufficient to compete against an HFET design. The surface passivation of the semiconductor interface states has been studied and considered one of the most significant fabrication processes in a GaN MOSFET. Through a novel low temperature plasma-enhanced atomic layer deposition (PEALD) pretreatment, we have demonstrated interface traps densities below  $10^{11} cm^{-2} eV^{-1}$ , with corresponding dielectric capacitance densities greater than 2  $\mu F/cm^2$  for  $ZrO_2$  and  $HfO_2$  films. For the first time a dielectric on GaN has produced a high capacitance density (> 5x), whilst maintaining a high quality interface which significantly reduced the interface trap density (< 10x). This low temperature deposition technique has the ability to be applied to any current GaN technology for MOS applications.

GaN MOSFETs with a  $ZrO_2$  gate dielectric were fabricated on GaN-on-sapphire templates for the purpose of potential power switching applications. The GaN MOSFET design demonstrated enhancement-mode behavior without the complexity of high temperature fabrication and complex etching. The devices incorporated a unique selective deposition technique of ultra-thin PEALD AlN and  $ZrO_2$  films. This novel fabrication technique was one of the first reported low temperature processed unintentionally doped enhancement-mode GaN MOSFET with a peak current density of 50  $\mu A/mm$ , a peak transconductance of 40  $\mu S/mm$ , an intrinsic transconductance of 0.73 mS/mm and a channel electron mobility excess of 300  $cm^2/Vs$ . The advantage of the MOSFET architecture was depicted through the engineering capabilities of the threshold voltage of the device.

As power electronic systems desire improved internal power components for next generation circuit designs, the GaN MOSFET has shown great potential over the GaN HFET based on optimized simulations and the demonstration of high quality materials. This work has characterized novel low temperature PEALD gate dielectrics with improved properties on GaN for the potential of improved GaN MOSFET characteristics. Novel ultra-thin PEALD AlN films produced high electron densities along the source and drain regions through low temperature deposition. With the incorporation of these films and conventional commercial fabrication techniques the GaN MOSFET will have a distinct impact on power electronics.

### Acknowledgements

I would like to thank everyone who made this project possible. Without the support of many individuals I would not be writing this dissertation. First, I would like to thank Dr. Douglas Barlage as my academic advisor. His in-depth understanding of solid-state electronics provided great insight and assistance to this project.

This project would not have been possible without the support from Dr. Kenneth C. Cadien and his group members Dr. Amir Afshar  $(ZrO_2 \text{ and } HfO_2)$ , Pouyan Motamedi (AlN) and Triratna Muneshwar  $(ZrN_x)$ . The Cadien Nanofabrication Group provided some of the worlds best ultra-thin films for solid-state electronics. I would like to thank them for their countless hours of deposition, advice and material expertise.

I am proud to have had Alex Ma, Kevin Voon, Gem Shoute, Zohaib Hameed, Mourad Benlami, Brett Carnio, Mei Shen and Peter von Hauff as my colleagues through out my studies. Everyone was willing to collaborate, encourage and even criticize when needed. I wish them the best throughout their studies.

I am deeply thankful to my friends and family for all of the love and support. Finally to my wife Jennifer, without your encouragement and support this would not have been possible. Thank you.

### Preface

I, Kyle M. Bothe, am the principal contributor to all seven chapters in this thesis. In the thesis, Chapter 2 is based on the journal publication no. 4 and the conference publication no. 1 and no. 3. The work published in journal publication no. 1, no. 3 and no. 5 is described in Chapter 4. The basis of Chapter 5 included results published in journal publication no. 6 and conference publication no. 4 and no. 5. Finally, Chapter 6 is based on work included in the U.S. Provisional Patent no. 2 and conference publication no. 6. The work resulting in journal publication no. 7 and U.S. Provisional Patent no. 1 were not a part of the thesis.

Peter A. von Hauff had assisted me with the fabrication and characterization of the high- $\kappa$  dielectrics MOSCAPS discussed in Chapter 4 section 4.3 and 4.4.

Amir Afshar had provided the deposition of the optimized high- $\kappa$  rare earth metal oxides mentioned in Chapter 4, Chapter 5 and Chapter 6. Amir also assisted with the post fabricated annealing discussed in Chapter 5 section 5.4.1 and Chapter 6 section 6.3.1.

Kevin J. Voon had assisted me with the characterization and measurements of the AlN in Chapter 5 section 5.4 and ZrN Chapter 5 section 5.5.

Pouyan Motamedi had provided the deposition of the optimized PEALD AlN films mentioned in Chapter 5 and Chapter 6.

Triratna Muneshwar had provided the deposition of the optimized PEALD ZrN films mentioned in Chapter 5.

Alex M. Ma provided assistance with the fabrication of the GaN MOSFETs and the method for low-temperature lift-off of PEALD gate oxides.

Below is the list of published and submitted referred journals and conference papers that are resulted from my Ph.D. work.

#### Publications

#### **Journal Publications**

- Kyle M. Bothe, Peter A. von Hauff, Amir Afshar, Ali Foroughi-Abari, Kenneth C. Cadien and Douglas W. Barlage, "Capacitance Modeling and Characterization of Planar MOSCAP Devices for Wideband-gap Semiconductors with High-κ Dielectrics", IEEE Transactions on Electron Devices 59(10) 2662-2666 (2012)

- Alex M. Ma, Manisha Gupta, Fatema Rezwana Chowdhury, Mei Shen, Kyle M. Bothe, Karthik Shankar, Ying Tsui, and Douglas W. Barlage, "Zinc Oxide Thin Film Transistors with Schottky Source Barriers", Solid-State Electronics 76 104-108 (2012)

- Peter A. von Hauff, Amir Afshar, Ali Foroughi-Abari, Kyle M. Bothe, Kenneth C. Cadien and Douglas W. Barlage, "ZrO<sub>2</sub> on GaN Metal Oxide Semiconductor with Low Hysteresis via Atomic Layer Deposition" Applied Physics Letters 102, 251601 (2013)

- Kyle M. Bothe and Douglas W. Barlage, "Underlying Design Advantages for GaN MOSFETs Compared with GaN HFETs for Power Applications", Journal of Computational Electronics 13(1) 217-223 (2013)

- 5. Kyle M. Bothe, Peter A. von Hauff, Amir Afshar, Ali Foroughi-Abari, Kenneth C. Cadien and Douglas W. Barlage, "Electrical Comparison of HfO<sub>2</sub> and ZrO<sub>2</sub> Gate Dielectrics on GaN" IEEE Transaction on Electron Devices 60(12) 4119-4124 (2013)

- 6. Kevin J. Voon, Kyle M. Bothe, Pouyan Motamedi, Kenneth C. Cadien and Douglas W. Barlage, "Polarization Charge Properties of Low-Temperature Atomic Layer Deposition of AlN on GaN" Journal of Physics D: Applied Physics 47 345104 (2014)

- 7. Mourad Benlamri, Kyle M. Bothe, Alex M. Ma, Gem Shoute, Amir Afshar, Himani Sharma, Arash Mohammadpour, Manish Gupta, Kenneth C. Cadien, Ying Tsui, Karthik Shankar, and Douglas W. Barlage, "High-Mobility Solution-Processed Zinc Oxide Thin Films on Silicon Nitride" Physics Status Solidi: RRL (8) 871-875 (2014)

#### **U.S** Patent Applications

Alex M. Ma, Manish Gupta, Kyle M. Bothe, Amir Afshar, Kenneth C. Cadien, Douglas W. Barlage, "Buried Source Schottky Barrier Thin Film Transistor And Method of Manufacture" U.S Provisional Patent Application No.61/913,601  Kyle M. Bothe, Alex M. Ma, Kevin J. Voon, Amir Afshar, Triratna Muneshwar, Pouyan Motamedi, Kenneth C. Cadien, Douglas W. Barlage, "Polar Source Gallium Nitride MOSFET Structure and Method of Fabrication" U.S Provisional Patent Application No. 61/967,239

### **Conference Proceedings**

- Kyle M. Bothe, Mark Johnson, Douglas W. Barlage, "TCAD Modeling and Simulation of a Field Plated GaN MOSFET for High Voltage Applications", CS MANTECH Conference, Palm Springs (2011)

- Peter A. von Hauff, Kyle M. Bothe, Amir Afshar, Ali Foroughi-Abari, Kenneth C. Cadien and Douglas W. Barlage, "High Mobility (210cm2/Vs), High Capacitance (7.2uF/cm2) ZrO<sub>2</sub> on GaN Metal Oxide Semiconductor" CS MANTECH Conference, Boston (2012)

- 3. Kyle M. Bothe, Peter A. von Hauff, Amir Afshar, Ali Foroughi-Abari, Kenneth C. Cadien and Douglas W. Barlage, "GaN MOSFET: Projections for High Power High Frequency Applications" International Conference on Simulation in Semiconductor Processes and Devices, Denver (2012)

- Kevin J. Voon, Kyle M. Bothe, Pouyan Motamedi, Kenneth C. Cadien and Douglas W. Barlage, "Engineered Tunneling Contacts with Low-Temperature Atomic Layer Deposition of AlN on GaN", CS MANTECH Conference, Denver (2014)

- Kyle M. Bothe, Alex M. Ma, Kevin J. Voon, Amir Afshar, Pouyan Motamedi, Kenneth C. Cadien, Douglas W. Barlage, "Selective Deposition of Low Temperature AlN Ohmic Contacts for GaN Devices" CS MANTECH Conference, Denver (2014)

- Kyle M. Bothe, Alex M. Ma, Amir Afshar, Pouyan Motamedi, Kenneth C. Cadien, Douglas W. Barlage, "Impact of Post Fabrication Annealing PEALD ZrO<sub>2</sub> for GaN MOSFETs" CS MANTECH Conference, Scottsdale (2015)

### In Preparation

Kyle M. Bothe, Alex M. Ma, Kevin J. Voon, Amir Afshar, Triratna Muneshwar, Pouyan Motamedi, Kenneth C. Cadien, Douglas W. Barlage, "Reliability of Ultrathin PEALD Nitride Based Films in GaN FETs"  Kevin J. Voon, Kyle M. Bothe, Triratna Muneshwar, Kenneth C. Cadien, Douglas W. Barlage, "Polarization Charge Properties of Low-Temperature Atomic Layer Deposition of Semiconductor"

# Contents

| 1        | Intr | roduction                          | 1  |

|----------|------|------------------------------------|----|

|          | 1.1  | Motivation                         | 1  |

|          | 1.2  | Figure of Merits                   | 3  |

|          | 1.3  | Gallium Nitride Transistors        | 6  |

|          | 1.4  | Synopsis of Thesis                 | 10 |

| <b>2</b> | Dev  | vice Design and Simulation         | 12 |

|          | 2.1  | Introduction                       | 12 |

|          | 2.2  | Device Optimization                | 13 |

|          | 2.3  | Device Comparison                  | 19 |

|          | 2.4  | Summary                            | 24 |

| 3        | Fab  | rication Techniques                | 26 |

|          | 3.1  | Introduction                       | 26 |

|          | 3.2  | Gate Dielectrics for GaN           | 28 |

|          | 3.3  | Source/Drain Carriers              | 29 |

|          | 3.4  | GaN Metalization                   | 31 |

|          | 3.5  | GaN Substrates                     | 32 |

|          | 3.6  | Device Isolation                   | 33 |

|          | 3.7  | Summary                            | 34 |

| 4        | Gat  | e Dielectric Characterization      | 35 |

|          | 4.1  | Introduction                       | 35 |

|          | 4.2  | Dielectric Fabrication             | 36 |

|          | 4.3  | Current-Voltage Measurements       | 37 |

|          |      | 4.3.1 Frenkel-Poole Conduction     | 37 |

|          |      | 4.3.2 Quantum Mechanical Tunneling | 39 |

|          | 4.4  | Capacitance-Voltage Measurements   | 42 |

|          | 4.5  | Summary                            | 49 |

| <b>5</b> | Sou    | rce and Drain Characterization             | 50  |

|----------|--------|--------------------------------------------|-----|

|          | 5.1    | Introduction                               | 50  |

|          | 5.2    | Nitride Film Fabrication                   | 52  |

|          | 5.3    | Characterization Methods                   | 53  |

|          | 5.4    | Aluminum Nitride                           | 54  |

|          |        | 5.4.1 Current-Voltage Characterization     | 55  |

|          |        | 5.4.2 Capacitance-Voltage Characterization | 58  |

|          |        | 5.4.3 AlN Thickness Dependence             | 62  |

|          |        | 5.4.4 AlN Summary                          | 63  |

|          | 5.5    | Zirconium Nitride                          | 65  |

|          |        | 5.5.1 $ZrN_x$ on Silicon                   | 65  |

|          |        | 5.5.2 $ZrN_x$ on GaN                       | 69  |

|          |        | 5.5.3 $ZrN_x$ Summary                      | 75  |

|          | 5.6    | AlN and $ZrN_x$ Comparison                 | 75  |

|          | 5.7    | Nitride Reliability                        | 77  |

|          | 5.8    | Summary                                    | 81  |

| 6        | Gal    | N MOSFET Fabrication and Characterization  | 82  |

|          | 6.1    | Introduction                               | 82  |

|          | 6.2    | Device Fabrication                         | 82  |

|          | 6.3    | Device Characterization                    | 86  |

|          |        | 6.3.1 GaN MOSFET Operation                 | 87  |

|          |        | 6.3.2 Breakdown Voltage Characterization   | 103 |

|          | 6.4    | Summary                                    | 111 |

| 7        | Sun    | nmary and Conclusions                      | 113 |

|          | 7.1    | Directions for Future Work                 | 116 |

| Bi       | ibliog | graphy                                     | 117 |

# List of Figures

| 1.1 | The various markets and applications for GaN based devices. The inherent            |    |

|-----|-------------------------------------------------------------------------------------|----|

|     | material properties of GaN are starting to replace incumbent technologies           |    |

|     | unable to advance electronic components required for new applications [3].          | 2  |

| 1.2 | A visual comparison of peak operation capabilities for Si, GaAs and GaN             |    |

|     | based on temperature and power applications. GaN has the ability to replace         |    |

|     | all silicon power devices based on the ability to operate $200^{\circ}C$ higher and |    |

|     | with stand electric fields larger than 300 $V/\mu m$                                | 5  |

| 1.3 | The three most common GaN device architectures under investigation for              |    |

|     | power applications are the (a) HFET, (b) MOS-HFET and (c) MOSFET                    | 6  |

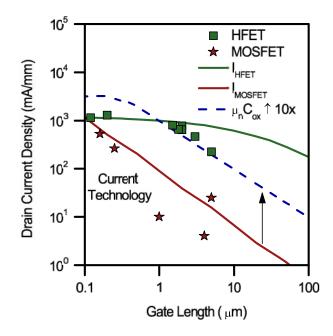

| 1.4 | Peak current density with respect to gate length for the GaN HFET, MOS-             |    |

|     | HFET and MOSFET.                                                                    | 8  |

| 1.5 | HFET and MOSFET peak current density with respect to gate length based              |    |

|     | on GaN properties. Improving the channel mobility and capacitance density           |    |

|     | of current GaN MOSFET technology has the potential to surpass HFET                  |    |

|     | characteristics below 2 $\mu m$ gate lengths                                        | 9  |

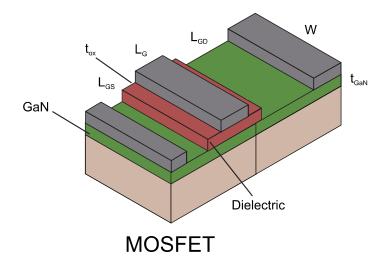

| 2.1 | The GaN MOSFET design and dimensions to be optimized for improved                   |    |

|     | device characteristics. The device architecture was optimized before field          |    |

|     | plates were included which were used to improve the breakdown voltage               | 13 |

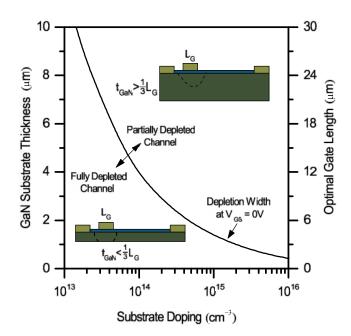

| 2.2 | The maximum substrate thickness of the GaN and equivalent minimum gate              |    |

|     | length were determined based on the depletion width determined from the             |    |

|     | substrate doping concentration. Any combination of thickness and substrate          |    |

|     | doping that remains below the curve will produce a fully depleted channel.          | 14 |

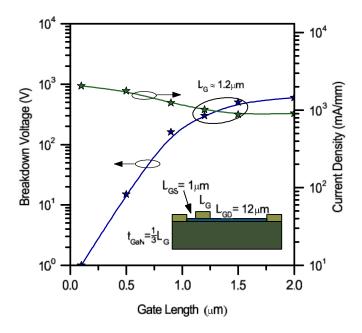

| 2.3 | The simulated device breakdown voltage and peak current density based on            |    |

|     | gate length. Through optimization of the gate length the power rating was           |    |

|     | largest at a gate dimension of $1.2\mu m$                                           | 15 |

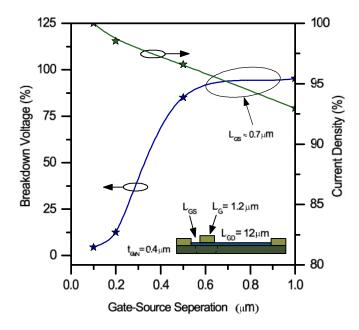

| 2.4 | The gate-source length dependence on breakdown voltage and current density          |    |

|     | for the GaN MOSFET. The gate-source separation was optimized to a peak              |    |

|     | power rating of $0.7\mu m.$                                                         | 16 |

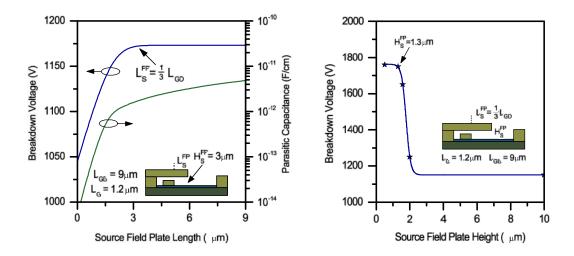

| 2.5 | Optimization of the source field plate based on length and height                   | 17 |

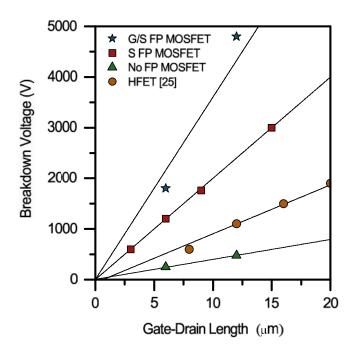

| 2.6 | The improved breakdown voltage with respect to drift region of the GaN              |    |

|     | MOSFET with field plates compared to current HFET technology                        | 18 |

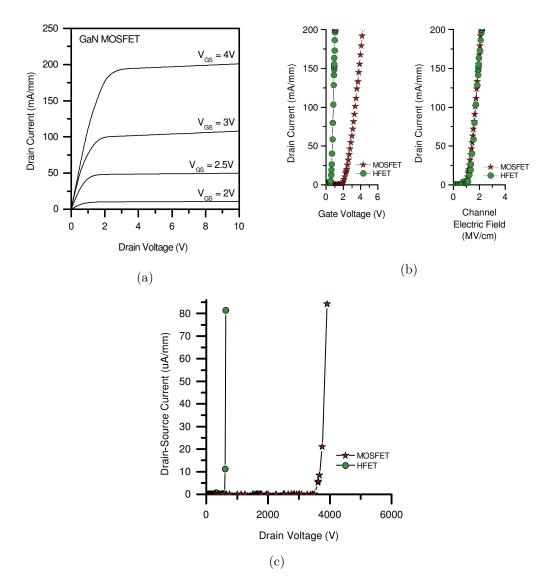

| 2.7  | (a) Simulated GaN MOSFET family of curves. (b) Voltage and electric field                                                                                                                                                                                                                                                                                                                                                 |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | <ul><li>dependence transfer characteristics for the simulate MOSFET and HFET.</li><li>(c) Breakdown voltage of the simulated HFET (600 V) and MOSFET (3500</li></ul>                                                                                                                                                                                                                                                      |     |

|      | V) with similar sized dimensions                                                                                                                                                                                                                                                                                                                                                                                          | 20  |

| 2.8  | The effective electron channel mobility was extracted from the simulated                                                                                                                                                                                                                                                                                                                                                  | 20  |

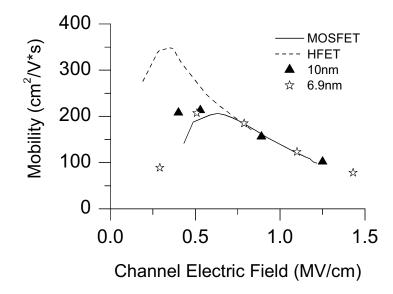

| 2.0  | family of curves for the GaN MOSFET and GaN HFET                                                                                                                                                                                                                                                                                                                                                                          | 21  |

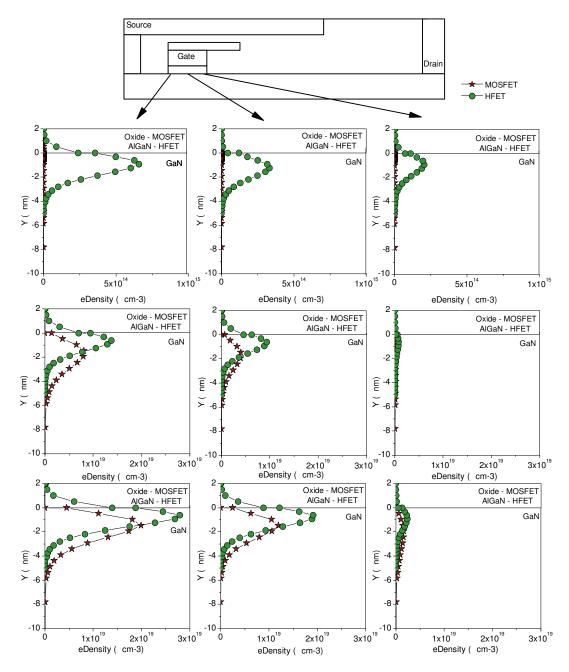

| 2.9  | The electron density during various modes of operation under the gate of the MOSFET and HFET. The electron distribution in the channel was examined near the source edge, middle and drain edge. (Top) The device is off, i.e. $V_{GS}$                                                                                                                                                                                   |     |

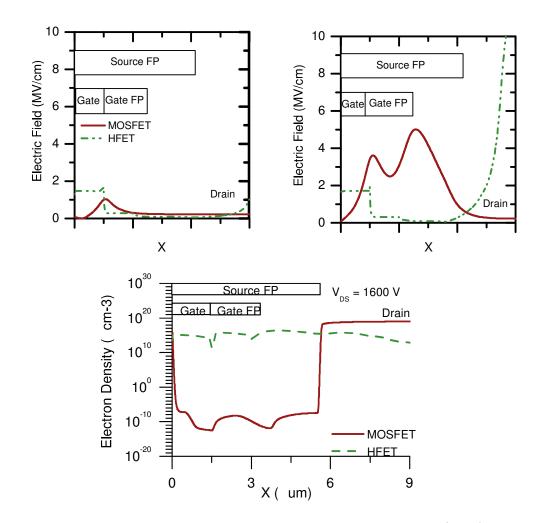

| 2.10 | < $V_t$ , (Middle) $I_{DS} = 40 \ mA/mm$ , (Bottom) $I_{DS} = 175 \ mA/mm$ The electric field under the gate and drain region when ( <i>Left</i> ) $V_{DS}=100V$ and ( <i>Right</i> ) $V_{DS}=1600V$ . ( <i>Bottom</i> ) The electron density for both devices under the gate and drift region at $V_{DS}=1600V$ . The MOSFET suppressed the electric field and maintain a large superstantian of corrient under the sets | 22  |

|      | the electric field and maintain a low concentration of carriers under the gate<br>whereas the HFET was unable to control the channel depletion                                                                                                                                                                                                                                                                            | 23  |

|      | whereas the HTET was unable to control the channel depletion                                                                                                                                                                                                                                                                                                                                                              | 20  |

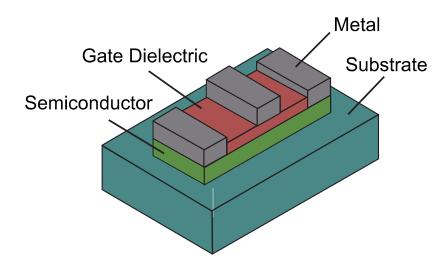

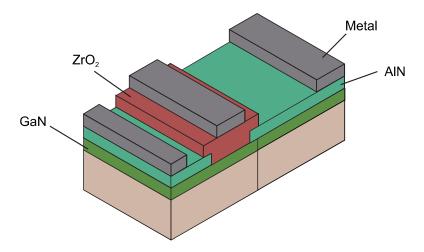

| 3.1  | Important regions and materials of the GaN MOSFET which require novel                                                                                                                                                                                                                                                                                                                                                     |     |

|      | fabrication techniques for improved device performance                                                                                                                                                                                                                                                                                                                                                                    | 27  |

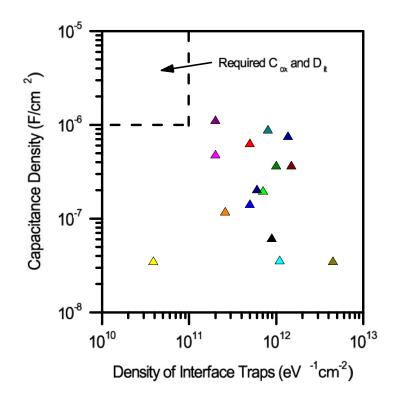

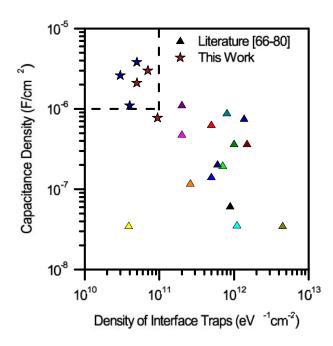

| 3.2  | Density of interface traps and capacitance density of dielectric on GaN. These                                                                                                                                                                                                                                                                                                                                            |     |

|      | techniques were unable to obtain the high charge control and low interface                                                                                                                                                                                                                                                                                                                                                |     |

|      | traps required for a MOSFET.                                                                                                                                                                                                                                                                                                                                                                                              | 28  |

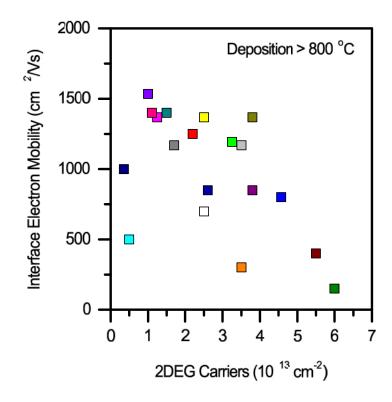

| 3.3  | Polarized 2DEG carriers and corresponding sheet mobility for AlN and Al-                                                                                                                                                                                                                                                                                                                                                  | 20  |

| 9.4  | GaN films.                                                                                                                                                                                                                                                                                                                                                                                                                | 30  |

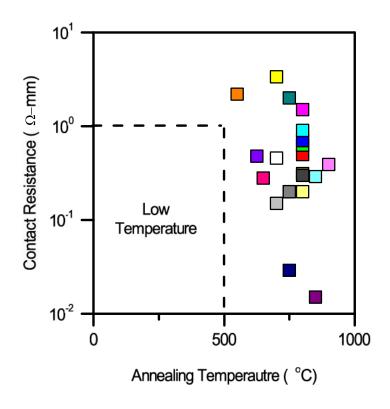

| 3.4  | Contact resistance with respect to annealing temperatures to produce ohmic contacts on GaN. The current techniques require high annealing temperatures                                                                                                                                                                                                                                                                    |     |

|      | and complex metal stacks.                                                                                                                                                                                                                                                                                                                                                                                                 | 31  |

| 3.5  | Schematic of GaN MOSFET with mesa etching to reduce the leakage current                                                                                                                                                                                                                                                                                                                                                   | 01  |

|      | through the unused bulk GaN.                                                                                                                                                                                                                                                                                                                                                                                              | 33  |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

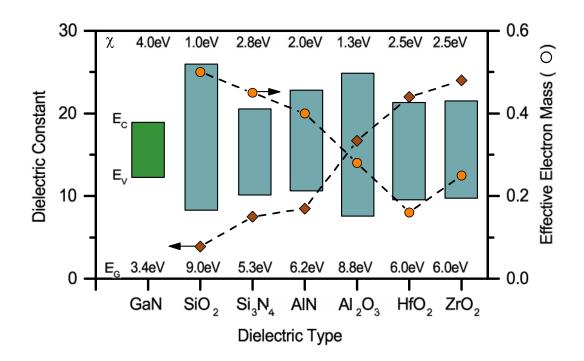

| 4.1  | Dielectric constant and effective electron mass for potential gate dielectrics                                                                                                                                                                                                                                                                                                                                            |     |

|      | for GaN based devices. The corresponding band diagram and conduction                                                                                                                                                                                                                                                                                                                                                      | 9.0 |

| 4.9  | band offset can be inferred for each material                                                                                                                                                                                                                                                                                                                                                                             | 36  |

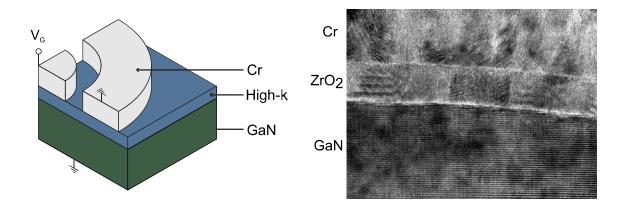

| 4.2  | (Left) Schematic of the MOSCAP used to evaluate the dielectric/GaN in-<br>terface. $(Right)$ TEM image of the high-k dielectric film grown on GaN via                                                                                                                                                                                                                                                                     |     |

|      | PEALD                                                                                                                                                                                                                                                                                                                                                                                                                     | 37  |

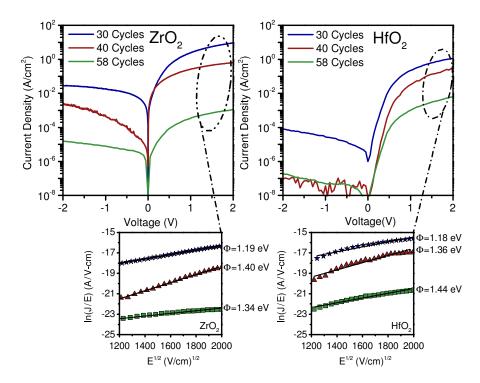

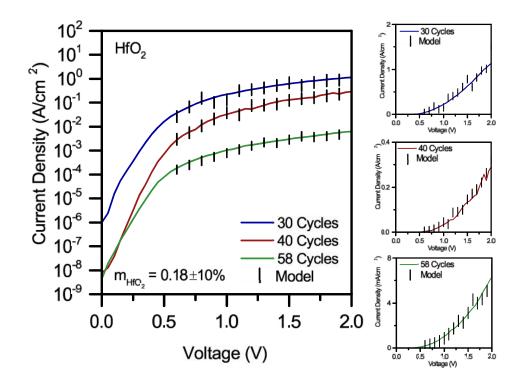

| 4.3  | Measured current densities with respect to voltage for all film samples. The                                                                                                                                                                                                                                                                                                                                              | 51  |

|      | results were converted into F-P plots to obtain the conduction band offset                                                                                                                                                                                                                                                                                                                                                |     |

|      | between the dielectric and GaN.                                                                                                                                                                                                                                                                                                                                                                                           | 38  |

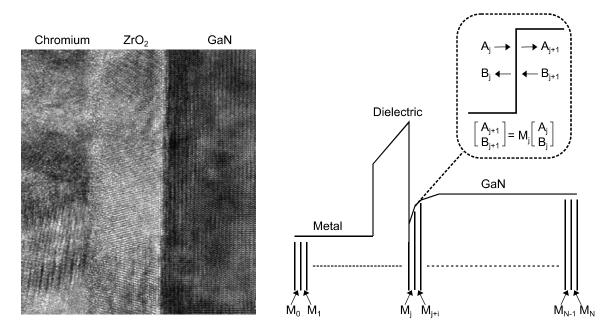

| 4.4  | (Left) Cross section image of the MOSCAP. $(Right)$ The illustration of                     |    |

|------|---------------------------------------------------------------------------------------------|----|

|      | the conduction band used to determine the electron tunneling through the                    |    |

|      | dielectric from the transfer matrix method.                                                 | 40 |

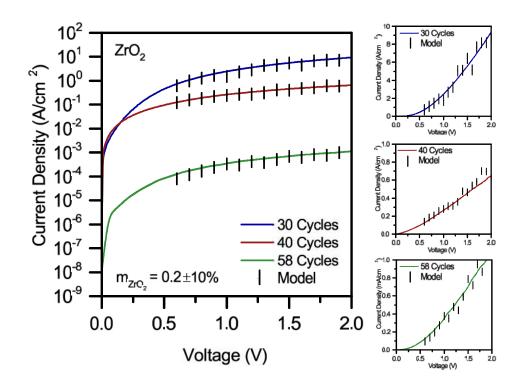

| 4.5  | The modeled quantum mechanical tunneling current was used to confirm the                    |    |

|      | measured conduction mechanisms and to extract the effective electron mass                   |    |

|      | of the $ZrO_2$ films. The model (with error bars) was matched to the measured               |    |

|      | results by creating the band structure for a given voltage and adjusting the                |    |

|      | effective mass of the dielectric. The effective electron mass of the $ZrO_2$ films          |    |

|      | was determined as $m_{ZrO_2} = 0.2.$                                                        | 41 |

| 4.6  | The modeled quantum mechanical tunneling current was used to confirm                        |    |

|      | the measured conduction mechanisms and to extract the effective electron                    |    |

|      | mass of the the $HfO_2$ films. The model (with error bars) was matched to                   |    |

|      | the measured results by creating the band structure for a given voltage and                 |    |

|      | adjusting the effective mass of the dielectric. The effective electron mass of              |    |

|      | the $HfO_2$ films was determined as $m_{HfO_2} = 0.18.$                                     | 42 |

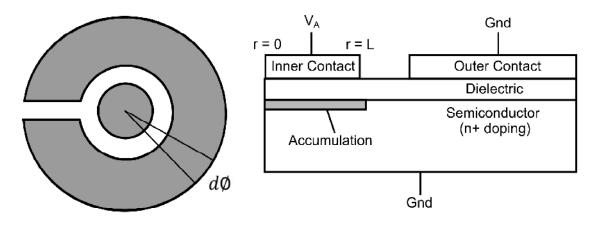

| 4.7  | (Left) An illustration of the modeled planar MOSCAP. (Right) The radial                     |    |

|      | cross section of the modeled planar MOSCAP.                                                 | 43 |

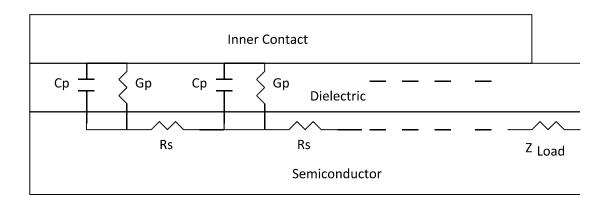

| 4.8  | Equivalent lumped circuit model under the inner contact for the planar                      |    |

|      | MOSCAP.                                                                                     | 44 |

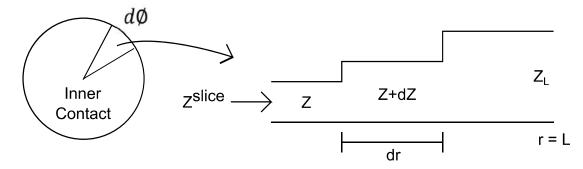

| 4.9  | A small slice of the inner contact $(\partial \phi)$ visually converted into the equivalent |    |

|      | triangular tapered transmission line.                                                       | 44 |

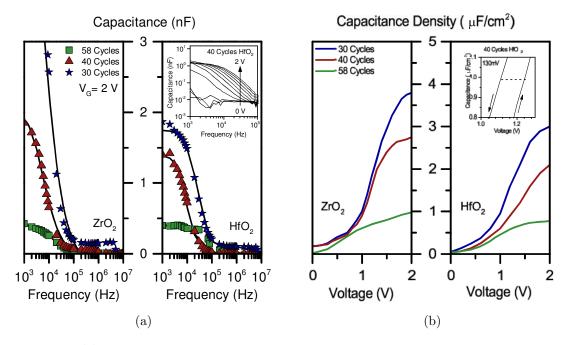

| 4.10 | (a) Capacitance-frequency measurements used to characterize the films through               |    |

|      | a planar MOSCAP model. (Inset) Voltage dependence of 40 cycles $HfO_2$                      |    |

|      | C-f plots (b) The extracted capacitance density of the MOSCAP obtained                      |    |

|      | from the C-f measurements. (Inset) Hysteresis of the 40 cycles C-V at 10 kHz.               | 46 |

| 4.11 | Density of interface traps along the dielectric/GaN surface obtained from                   |    |

|      | $G_p - \omega$ and hysteresis measurements for (a) $HfO_2$ and (b) $ZrO_2$                  | 47 |

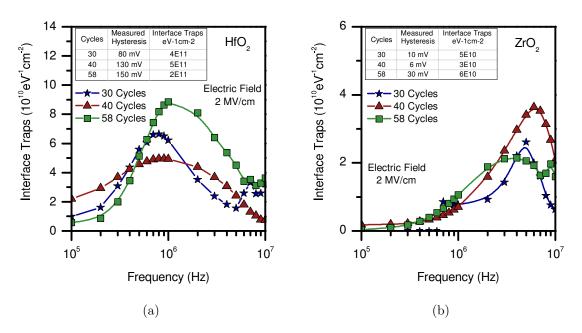

| 4.12 | The dielectric properties of the low temperature PEALD $HfO_2$ (red stars)                  |    |

|      | and $ZrO_2$ (blue stars) films compared to literature (triangles). The ultra-               |    |

|      | thin films were able improve the capacitance density and interface traps by                 |    |

|      | a factor of 30                                                                              | 48 |

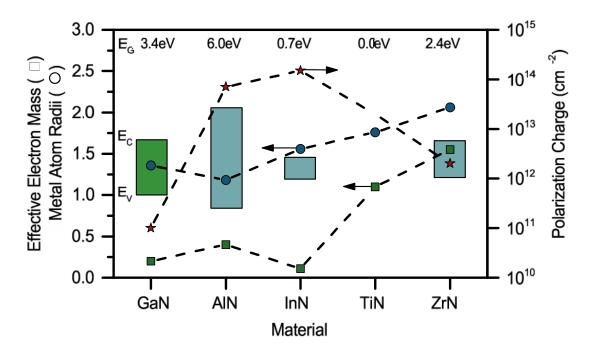

| 5.1  | The proposed nitride based films for the source/drain regions compared three                |    |

| 0.1  | electrical properties imperative to produce low ohmic contacts, high carrier                |    |

|      | densities and a reliable device; the effective electron mass, metal atomic radii            |    |

|      | and polarization charge were compared between the nitride films. AlN has                    |    |

|      | the potential to form the largest 2DEG along the interface, while ensuring                  |    |

|      | the current would flow through the GaN                                                      | 51 |

|      |                                                                                             | 91 |

| 5.2 | The film thickness for AlN and $ZrN_x$ with respect to PEALD cycle were<br>obtained from in-situ ellipsometry; courtesy of Pouyan Motamedi (AlN) and<br>Triratna Muneshwar $(ZrN_x)$ .                                                                                                                                                                                                                                                                                                       | 52       |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

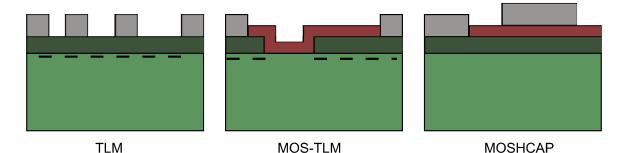

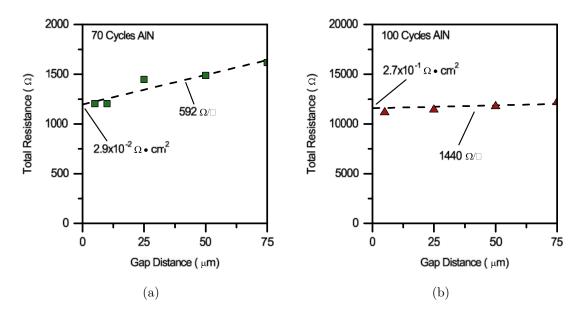

| 5.3 | Schematic of the test structures to evaluate the AlN and $ZrN_x$ films. The TLM structures were used to evaluate the contact and sheet resistance pro-<br>duced by the 2DEG along the GaN interface. The MOS-TLM included a<br>non-polarized region to extract the contact and sheet resistance of the nitride<br>film, in addition to confirming the GaN sheet resistance. The advantage of<br>the MOSHCAP was to extract the 2DEG through capacitance-voltage mea-<br>surements.           | 53       |

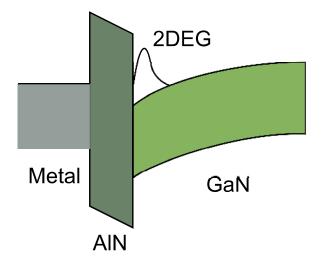

| 5.4 | The band structure of the AlN/GaN with the induced 2DEG carriers formed along the interface.                                                                                                                                                                                                                                                                                                                                                                                                 | 55       |

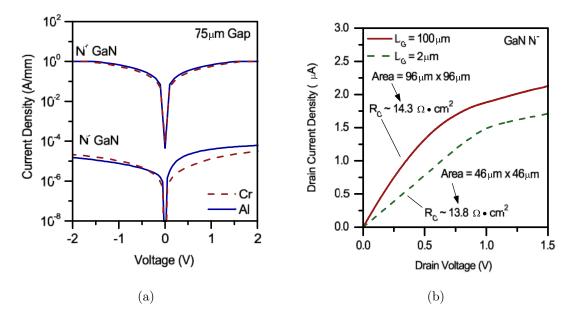

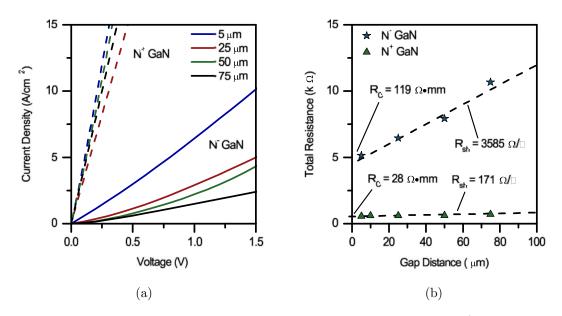

| 5.5 | (a) The I-V measurements from the 75 $\mu m$ gap TLM followed the trend<br>as the doping of the GaN was reduced. In addition, the Al metal contact<br>produced higher current densities than the Cr counter part for both cases<br>of GaN templates. (b) The Cr MOS-TLM results on N <sup>-</sup> GaN confirmed<br>the contact resistance from two devices with different contact areas. The<br>extracted contact resistivity between the different dimension devices was less<br>then $5\%$ | EG       |

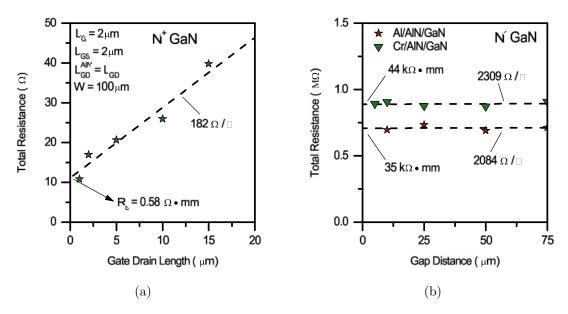

| 5.6 | than 5%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 56<br>57 |

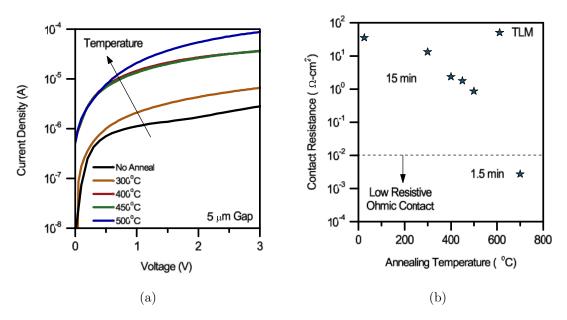

| 5.7 | (a) As the TLM structures were annealed the current density of the 5 $\mu m$<br>TLM gap increased. (b) The improved conduction was strongly dependent<br>on the reduced contact resistance with respect to annealing temperature.<br>Annealing the device at 700°C was found to produce a low ohmic contact<br>$(5x10^{-3} \ \Omega \cdot cm^2) \ \ldots \ $                                                         | 58       |

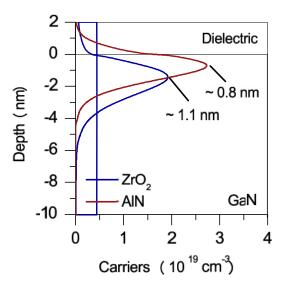

| 5.8 | The simulated accumulation thickness for the AlN/GaN and $ZrO_2$ /GaN to<br>extract the dielectric constant of the films. The effective mass of the films<br>determined the location of the peak centroid and the amount of carriers<br>within the dielectric film. AlN allowed 4x the amount of carriers into the<br>film compared to the $ZrO_2$ film.                                                                                                                                     | 59       |

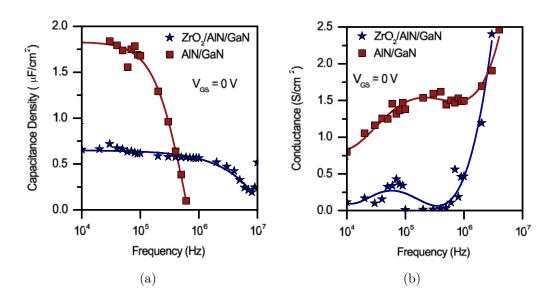

| 5.9 | The (a) capacitance and (b) conductance frequency dispersion based on the MOSCAP with and without a gate dielectric $(ZrO_2)$ under one of the metal contacts. By including the gate dielectric, the leakage conductance was reduced which provided less frequency dispersion than the AlN metal films.                                                                                                                                                                                      | 60       |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| 5.10 | The reverse C-V gate bias of the MOSHCAPs used to extract the 2DEG for               |    |

|------|--------------------------------------------------------------------------------------|----|

|      | both GaN templates. The area between the C-V measurement and the the-                |    |

|      | oretical depletion capacitance for GaN was the polarization interface charge.        |    |

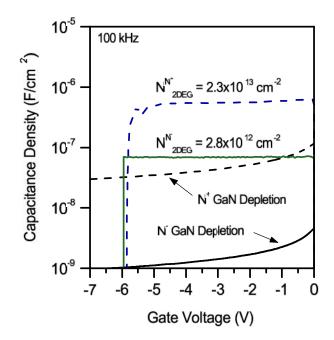

|      | The $N^+$ GaN (blue) produced a 2DEG roughly 10x larger than the $N^-$ GaN           |    |

|      | (green)                                                                              | 61 |

| 5.11 | The extracted contact and sheet resistance from the 5.7 nm and 7.9 nm                |    |

|      | AlN/GaN films                                                                        | 62 |

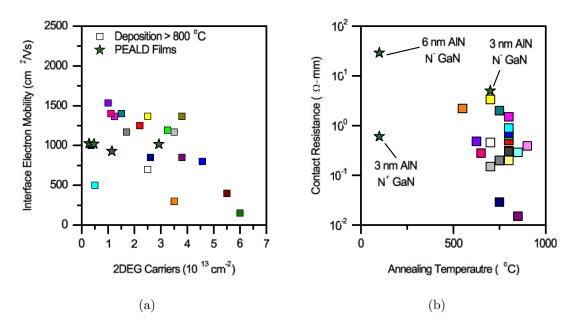

| 5.12 | (a) The comparison between carrier density to channel mobility of AlN films          |    |

|      | on GaN. The low temperature films produced equivalent 2DEG charge and                |    |

|      | carrier mobility as conventional high temperature deposition techniques. (b)         |    |

|      | The contact resistance of the doped GaN tunneling contact produced similar           |    |

|      | values to high temperature annealed metal contacts on GaN                            | 64 |

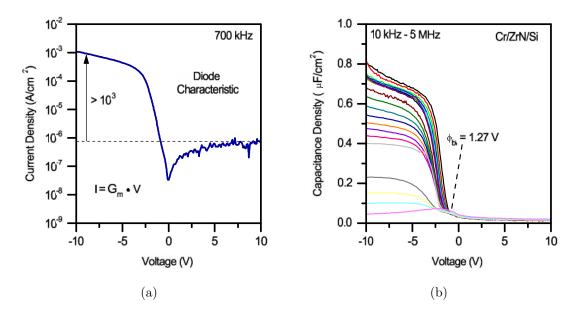

| 5.13 | (a) The measured I-V of the $ZrN_x/Si$ junction, courtesy of Kevin Voon.             | -  |

| 0.20 | (b) The frequency dependent C-V measurements of the $ZrN_x/Si$ , courtesy            |    |

|      | of Kevin Voon. The rectifying current density confirmed that a Schottky              |    |

|      | contact or pn-junction was formed. The extract built-in potential ( $\phi_{bi} =$    |    |

|      | 1.27 eV) of the material system confirmed a p-n junction was formed at the           |    |

|      | $ZrN_x$ /Si interface.                                                               | 66 |

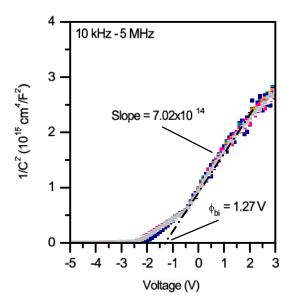

| 5.14 | Inverse squared capacitance of the measured test structure which was used            |    |

| 0    | to extract the electrical properties of the $ZrN_x$ film. The built-in potential     |    |

|      | was obtained from the x-axis intercept and the silicon doping concentration          |    |

|      | of was extracted from the slope                                                      | 67 |

| 5.15 | The expected band diagrams for $ZrN_x$ on different background doped GaN             |    |

|      | templates based on the extracted electrical parameters obtained from the             |    |

|      | silicon measurements.                                                                | 69 |

| 5.16 | (a) The current-voltage results of the $N^-$ (Solid) and $N^+$ (Dashed) GaN          |    |

|      | templates. (b) The total resistance with respect to TLM distance used to             |    |

|      | extract the contact resistance and sheet resistance of the $ZrN_x$ /GaN interface.   | 70 |

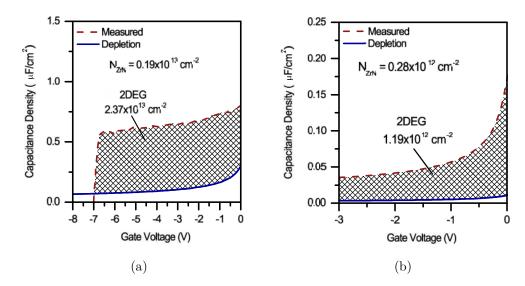

| 5.17 | Reverse bias C-V measurements of the $ZrO_2/ZrN_x$ /GaN MOSHCAPs ex-                 |    |

|      | tracted the 2DEG along the GaN interface for (a) $N^+$ and (b) $N^-$ GaN             |    |

|      | templates. The plots included the theoretical 2DEG expected from $ZrN_x$             |    |

|      | modulation doping $(N_{ZrN})$ . The additional charge in the reverse bias con-       |    |

|      | firmed that $ZrN_x$ had polarization properties                                      | 72 |

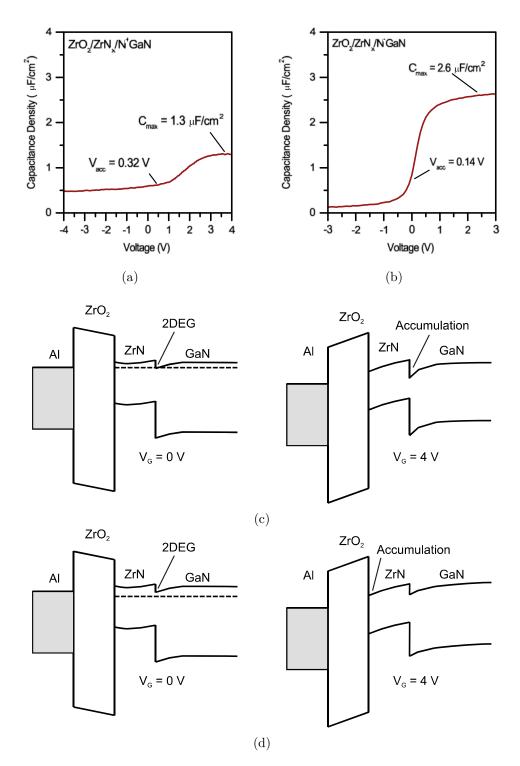

| 5.18 | Low frequency C-V to obtain the dielectric characteristics of $ZrN_x$ on (a)         |    |

|      | $N^+$ GaN and (b) $N^-$ GaN. (c) The band diagram at zero bias and strong            |    |

|      | accumulation regime on N <sup>+</sup> GaN were both along the $ZrN_x/GaN$ interface. |    |

|      | (d) The accumulation of the electrons for the $N^-$ GaN template occurred            |    |

|      | along the $Zr0_2/ZrN_x$ interface.                                                   | 73 |

|      |                                                                                      | -  |

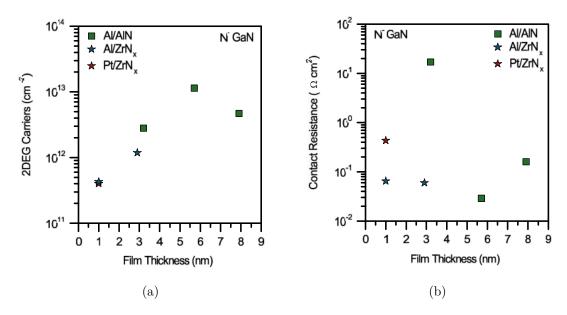

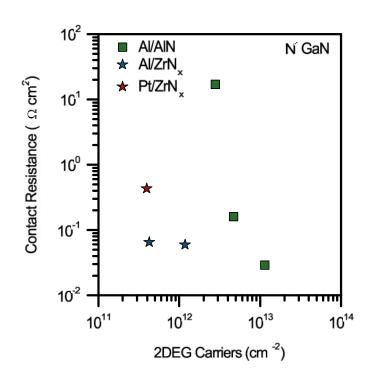

| 5.19 | (a) 2DEG carriers density and (b) Contract resistance based on the film thickness of AlN and $ZrN_x$ | 75 |

|------|------------------------------------------------------------------------------------------------------|----|

| 5.20 | Contact resistance of the nitride films compared to the 2DEG formed along                            |    |

|      | the GaN interface.                                                                                   | 76 |

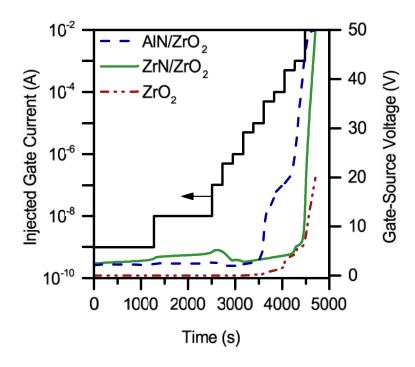

| 5.21 | Measured gate voltage based on injected gate current for different MOS GaN                           |    |

|      | devices. The voltage increased as the materials in the device failed due to                          |    |

|      | defects produced within the films                                                                    | 77 |

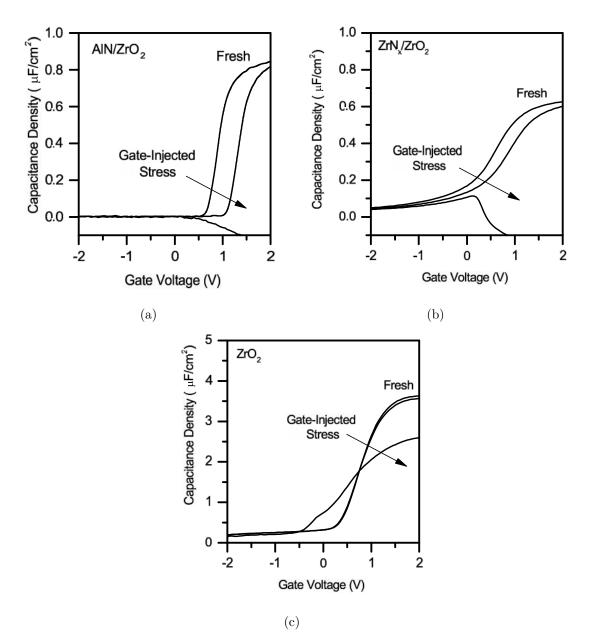

| 5.22 | Capacitance-voltage measurements (100 kHz) for (a) $AlN/ZrO_2$ (b) $ZrN_x/ZrO_2$                     |    |

|      | and (c) $ZrO_2$ were shifted as breakdown occurred due to electron induced                           | -  |

|      | defects within the films.                                                                            | 78 |

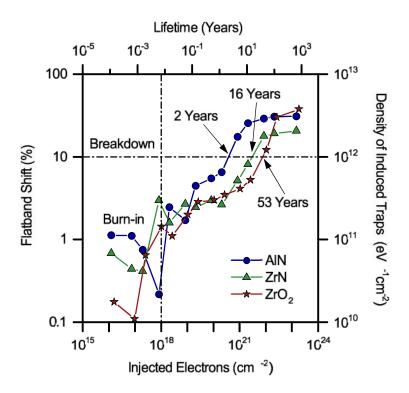

| 5.23 | Flat-band voltage shift and the associated traps within the film caused from                         |    |

|      | electrons injected through the gate. Lifetime of the devices based on worst                          |    |

|      | case scenario of 10 $\mu A/mm$ gate leakage. The lifetime ratio remains constant                     |    |

|      | regardless of the leakage current; i.e. The AlN film degraded 8x faster than                         |    |

|      | the $ZrN_x$ film.                                                                                    | 79 |

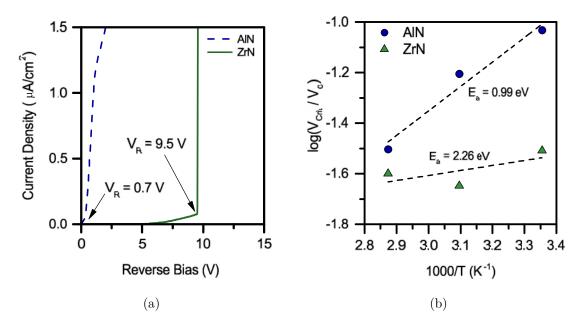

| 5.24 | (a) Reverse breakdown characteristics of the AlN and $ZrN_x$ films to extract                        |    |

|      | the materials critical electric field at $25^{\circ}C$ . (b) The materials reverse break-            |    |

|      | down based on temperature. Based on the temperature dependence, the                                  |    |

|      | $ZrN_x$ was more stable compared to the AlN                                                          | 80 |

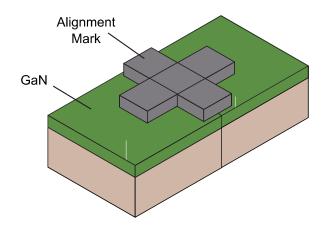

| 6.1  | Alignment marks were placed on the GaN template to align future layers.                              | 83 |

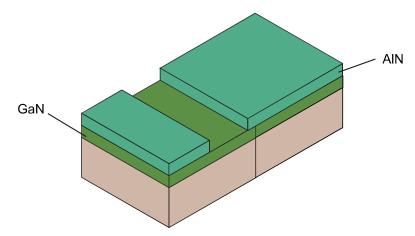

| 6.2  | The negative photoresist lift-off technique defined the source and drain re-                         |    |

|      | gions where the ultra-thin ALN films was deposited. The gate region was                              |    |

|      | protected with photoresist to ensure volatile Al atoms did not disturb the                           |    |

|      | GaN interface.                                                                                       | 84 |

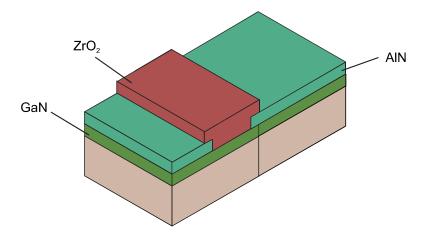

| 6.3  | The regions for the $ZrO_2$ gate dielectric were defined with same negative                          |    |

|      | photoresist process that defined the source and drain regions. The $ZrO_2$                           |    |

|      | overlapped the ALN along the source and drain to ensure the gate metal                               |    |

|      | would not come into contact with AlN.                                                                | 85 |

| 6.4  | The source, drain and gate contacts were all deposited at the same time to                           |    |

|      | reduce the fabrication steps of the device                                                           | 86 |

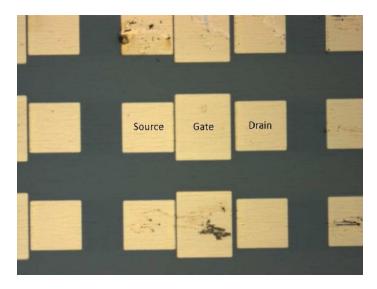

| 6.5  | Confocal image of the $100 \mu m \ge 100 \mu m$ FatFETs used to evaluate the quality                 |    |

|      | of the GaN MOSFET fabricated with the ultra-thin PEALD films. The gate                               |    |

|      | was extended 10 $\mu m$ beyond the width of the source and drain to reduce the                       |    |

|      | substrate leakage current.                                                                           | 87 |

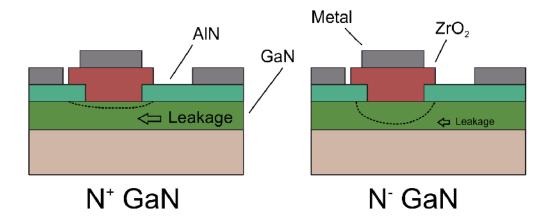

| 6.6  | A representation of the leakage current under the channel based dependence                           |    |

|      | on the depletion width (dashed region). The lower doped GaN produced a                               |    |

|      | larger depleted channel which was expected to create a lower leakage current.                        | 88 |

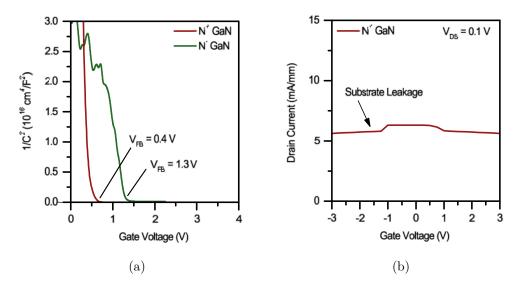

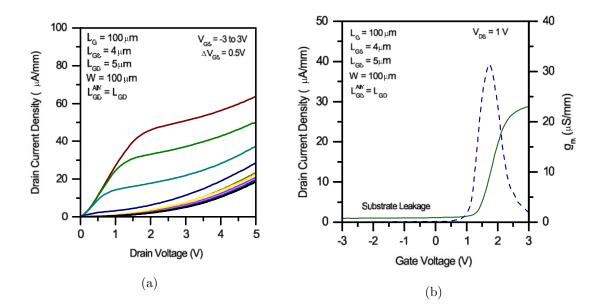

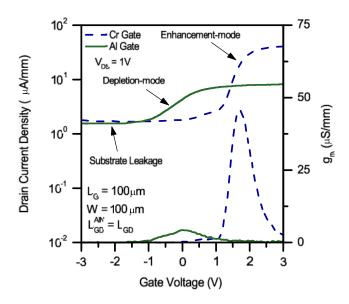

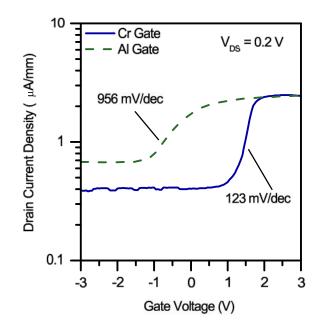

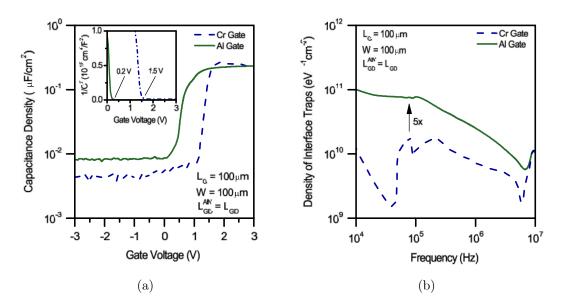

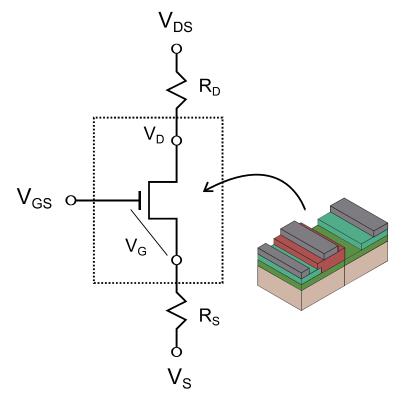

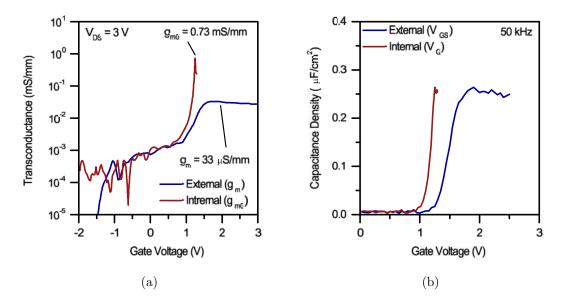

(a) The inverse squared capacitance with respect to gate voltage for the  $N^+$ 6.7GaN (red) and  $N^-$  GaN (green). The x-axis intercept was used to extract the accumulation voltage of the channel MOS. (b) The drain current (red) at  $V_{DS} = 0.1$  V for  $N^+$  GaN with respect to gate voltage. . . . . . . . . 88 (a) The family of curves for the  $N^-$  GaN MOSFET. The drain saturation 6.8 voltage of the MOSFET was consistent with conventional MOSFET models where  $V_{D_{sat}} = V_{GS} - V_t$ . (b) The drain current (green solid) and transconductance (blue dashed) at  $V_{DS} = 1$  V for  $N^-$  GaN with respect to gate voltage. The device demonstrated enhancement-mode operation, with a turn-on volt-89 6.9 The transfer and transconductance characteristics of the GaN MOSFET had a strong dependence with the work function of the gate metal. When the gate metal was exchanged from Al ( $\Psi_{Al} = 4.2 \ eV$ ) to Cr ( $\Psi_{Cr} = 4.7 \ eV$ ) the MOS-FET characteristics shifted from normally-on  $(V_t = -0.25 V)$  to normally-off  $(V_t = 1.3 V)$ . The enhancement-mode MOSFET improved current density (2x) and transconductance (5x) over the Al gate device.  $\ldots$ 91 6.10 The sub-threshold slopes of the GaN MOSFETs were extracted from the low transverse electric field transfer characteristics for the Al (Green) and Cr (Blue) gate metals. The enhancement-mode GaN MOSFET produced a 92sharper sub-threshold slope compared to the depletion-mode transistor. . . 6.11 (a) The gate-source capacitance of the oxide was obtain at low frequency (50) kHz) to determine the peak capacitance density and extract the flat band voltage of the MOS stack, shown in the inset. During reverse gate bias, the Cr metal was capable of depleting more charge from under the gate compared to the Al gate stack. (b) The density of interface traps were obtained from the conductance frequency spectrum. The  $Al/ZrO_2$  gate stack degraded the interface, which produced a 5x more traps compared to the Cr metal. . . . 936.12 The internal voltage drops are dependent on the external voltage biases and parasitic resistances along the source and drain interconnects. The MOSFET only experienced the internal bias for the drain  $(V_D)$  and gate  $(V_G)$  based on 956.13 (a) The external and internal transconductance of the 100  $\mu m \ge 100 \mu m$ GaN MOSFET at  $V_D = 3$  V. The peak intrinsic transconductance was 0.73 mS/mm. (b) The capacitance-voltage based on the external and internal 96

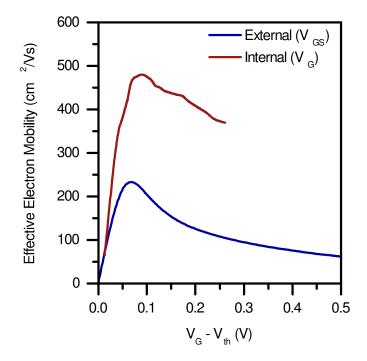

| 6.14 | The effective electron mobility of the FatFET obtained at low drain bias.                                                                                             |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | The mobility based on the external gate biases was determined to have a                                                                                               |     |

|      | peak mobility of 230 $cm^2/Vs$ Conversely, the peak electron mobility of the                                                                                          |     |

|      | GaN MOSFET without parasitic resistance has the potential to reach 480                                                                                                |     |

|      | $cm^2/Vs$                                                                                                                                                             | 98  |

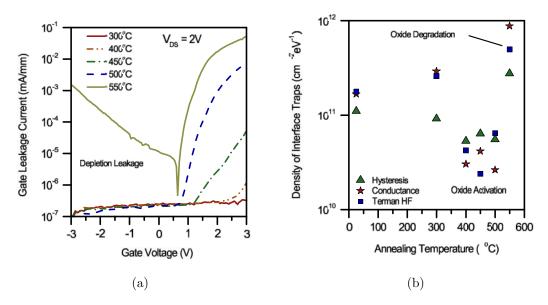

| 6 15 | (a) The gate leakage current of the FatFET as the gate voltage was swept                                                                                              | 00  |

| 0.10 | from reverse to forward bias. Higher annealing temperatures increased the                                                                                             |     |

|      | conduction leakage through the dielectric. (b) The extracted density of inter-                                                                                        |     |

|      | face traps based on annealing temperature. The gate oxide was electrically                                                                                            |     |

|      | activated between $400^{\circ}C$ and $500^{\circ}C$ before the gate dielectric was critically                                                                         |     |

|      | degraded                                                                                                                                                              | 99  |

| 6 16 | 0                                                                                                                                                                     | 99  |

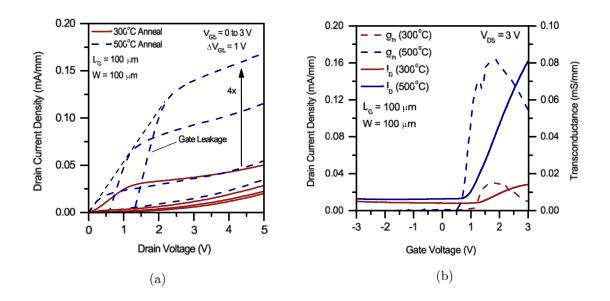

| 0.10 | (a) The FatFET family of curves after the device was annealed at $300^{\circ}C$ (red)                                                                                 |     |

|      | and $500^{\circ}C$ (blue). The drain current was improved by a factor a 4x over the                                                                                   |     |

|      | low temperature annealed device. (b) The transfer characteristics after the $1 + 2000 G$ (c $1$ ) $- 1 = 5000 G$ (1 $1 - 2$ ). The transfer characteristics after the |     |

|      | device was annealed at $300^{\circ}C$ (red) and $500^{\circ}C$ (blue). The transconduc-                                                                               |     |

|      | tance quadrupled over the original fabricated device due to the reduce series                                                                                         | 100 |

|      | resistances.                                                                                                                                                          | 100 |

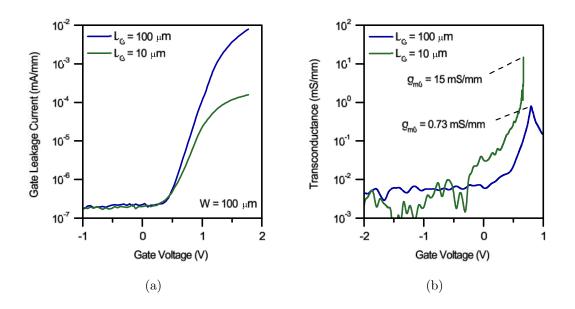

| 6.17 | (a) The leakage current through the gate dielectric with respect to gate volt-                                                                                        |     |

|      | age. The leakage current was reduced by a factor of 100 as the gate length                                                                                            |     |

|      | was reduced from 100 $\mu m$ to 10 $\mu m$ . (b) The GaN MOSFETs extracted                                                                                            |     |

|      | intrinsic transconductance were compared based on gate length. The 10 $\mu m$                                                                                         |     |

|      | channel increased the intrinsic transconductance to $15 mS/mm$ over the 100                                                                                           |     |

|      | $\mu m$ GaN MOSFET channel                                                                                                                                            | 102 |

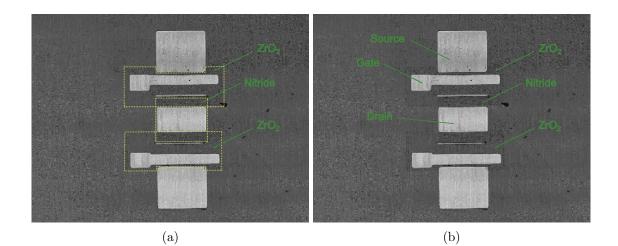

| 6.18 | A confocal image of the GaN MOSFET used to measure the breakdown                                                                                                      |     |

|      | voltage. (a) The dashed lines are where the transparent films were patterned                                                                                          |     |

|      | and deposited. (b) The source and gate contacts were grounded while the                                                                                               |     |

|      | drain voltage was increased. The confocal image allowed for the transparent                                                                                           |     |

|      | $ZrO_2$ and ZrN films to be imaged. The AlN optical properties were identical                                                                                         |     |

|      | to GaN making imaging nearly impossible.                                                                                                                              | 103 |

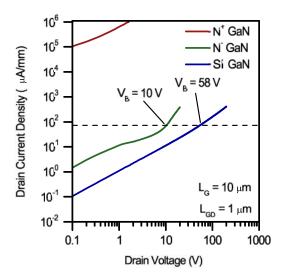

| 6.19 | The substrate leakage current with respect to GaN background doing as a                                                                                               |     |

|      | function of drain voltage. The semi-insulating GaN was capable of preventing                                                                                          |     |

|      | the substrate leakage current beyond 50 V                                                                                                                             | 104 |

| 6.20 | The GaN MOS-HFET and MOSFET transistor architectures were compared                                                                                                    |     |

|      | for the potential maximum drain voltage before the leakage current becomes                                                                                            |     |

|      | 80 $\mu A/mm$ . The significant variation between transistors was the ultra-thin                                                                                      |     |

|      | AlN film under the gate metal                                                                                                                                         | 105 |

|      |                                                                                                                                                                       |     |

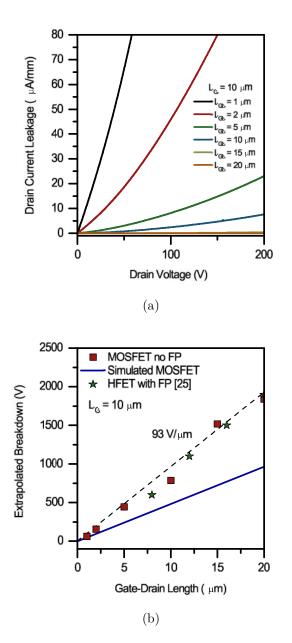

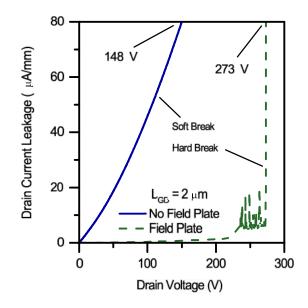

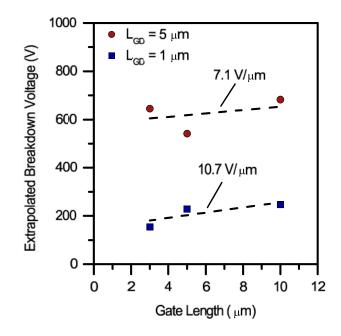

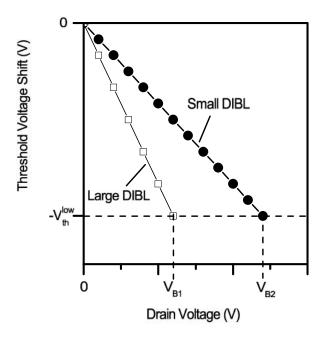

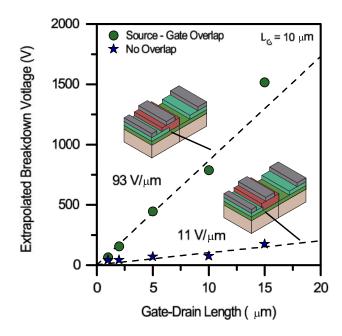

6.21 (a) The measured drain leakage current during the off-state of the GaN MOSFET. As the gate-drain length was increase, the device was capable of improving the maximum drain voltage. (b) The extrapolated breakdown voltage trend for the GaN MOSFET (red square) with respect to the drift region. The breakdown voltage of the leading GaN HFET device (green star) and the simulated GaN MOSFET (blue) were included. . . . . . . . . . 1066.22 The measured drain off-state leakage current for a 10  $\mu m$  gate GaN MOSFET with (solid green) and without (dashed blue) a floating field plate. The floating field plate increased the average critical electric field along the drain from 0.74 MV/cm to 1.4 MV/cm. 1086.23 The gate length extrapolated maximum drain voltage of GaN MOSFET architectures with different drift regions;  $L_{GD} = 1 \ \mu m$  (squares)  $L_{GD} = 5 \ \mu m$ 109(circles). 6.24 The breakdown of the device can be considered when the shift of the threshold voltage reached the low drain threshold voltage  $(V_{th}^{low})$ . This is where the 1106.25 The extrapolated breakdown voltage based on the substrate leakage current was examined as the AlN on the source-gate edge was removed from under the gate metal. A source-gate overlap of 100 nm ensured the breakdown voltage was close to 100 V/um. Removing the source carriers from under the

### gate prevented the transistor from withstanding larger drain voltages. . . . 111

# List of Tables

| 1.1 | Material Properties of Semiconductors for Electronic Devices                    | 2   |

|-----|---------------------------------------------------------------------------------|-----|

| 1.2 | Figure of Merits based on Material Properties for Power Electronic Devices      | 5   |

| 1.3 | GaN Device Characteristics for Different Design Architectures                   | 7   |

| 2.1 | Optimized GaN MOSFET and HFET Dimensions                                        | 19  |

| 3.1 | Gate Dielectrics for GaN Applications                                           | 29  |

| 3.2 | Contact Resistance for GaN based Devices                                        | 32  |

| 4.1 | Extracted Dielectric Properties on GaN                                          | 48  |

| 5.1 | Extracted Contact and Sheet Resistance Properties of AlN on GaN templates       | 57  |

| 5.2 | AlN Dielectric Constant Extracted from Peak Capacitance Density                 | 59  |

| 5.3 | Extracted Sheet and Contact Resistance                                          | 63  |

| 5.4 | ZrN Dielectric Constant Extracted from Peak Capacitance Density                 | 67  |

| 5.5 | Extracted Electronic Properties of $ZrN_x$                                      | 68  |

| 5.6 | $ZrN_x$ 2DEG Properties                                                         | 74  |

| 5.7 | $ZrN_x$ Contact Resistance Properties                                           | 74  |

| 6.1 | The Extracted Density of Interface Traps                                        | 94  |

| 7.1 | Low Temperature PEALD Gate Dielectrics on GaN                                   | 113 |

| 7.2 | Ultra-thin Low Temperature PEALD Al<br>N Films on GaN Templates $\ \ . \ . \ .$ | 114 |

| 7.3 | GaN MOSFET Device Characteristics                                               | 114 |

| 7.4 | GaN MOSFET Breakdown Voltage Characteristics                                    | 115 |

# Chapter 1

## Introduction

### 1.1 Motivation

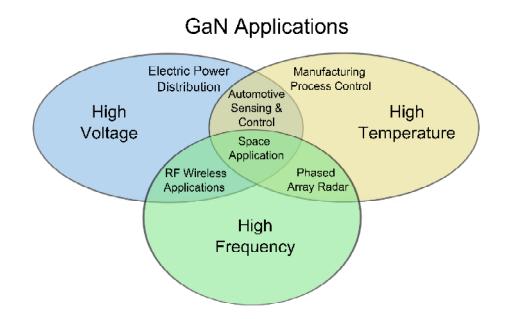

The perpetual strive to advance electronic systems has become a repetitive occurrence between improving device characteristics and optimizing the design of the system. A power systems overall electronic performance such as power handling, efficiency, size, and reliability are strongly dependent on the enhancements made to individual semiconductor devices. Many power electronic systems require the transistors to operate under extreme temperatures and large power modes of operation [1]. Until now, silicon (Si) has been the dominating semiconductor substrate in power electronics because of the prior knowledge and processing techniques acquired from complementary-metal-oxide-semiconductor (CMOS) technology. However, current silicon based technology has been unable to maintain next generation specifications due to the physical properties that limit the device performance [2]. This is not due to the design of the silicon transistors; rather, the electrical properties of a narrow band-gap has started to reach its limits in the power electronics industry. Conversely, gallium nitride (GaN) has gained significant interest over many researched semiconductors because of the preferential material properties ideal for a wide range of electronic applications [3], shown in Figure 1.1. The next generation power market for GaN devices has been estimated to be \$300 million by 2015 with a growth rate over 30% per year [4]. A conservative growth rate, predicts that GaN based devices should reach approximately 5% of the \$40 billion power market by 2020.

Gallium nitride has unique semiconductor properties, such that a combination of bandgap, critical electric field, and electron saturation velocity has the potential to advance the

Figure 1.1: The various markets and applications for GaN based devices. The inherent material properties of GaN are starting to replace incumbent technologies unable to advance electronic components required for new applications [3].

transistors switching frequency, operating temperature and blocking voltage (off-state drain voltage) [5]. The material properties of well-known semiconductors, [6–10], commonly used to fabricate microelectronic devices were compiled and tabulated below in Table 1.1. The band-gap,  $E_G$ , intrinsic carrier concentration,  $n_i$ , dielectric constant,  $\epsilon_r$ , electron mobility,  $\mu_n$ , critical electric field,  $E_C$ , electron saturation velocity,  $\nu_s$ , and thermal conductivity,  $\Phi_k$ were considered the most important electronic properties of semiconductors. The wider band gap semiconductors, GaN and SiC, inherently produce lower intrinsic carrier concentrations which were beneficial for lower junction leakage at higher operating temperatures. Furthermore, wide band gap semiconductors have demonstrated larger critical electric fields compared to small band gap semiconductors such as Si and GaAs. The semiconductors with

Table 1.1: Material Properties of Semiconductors for Electronic Devices

| Material            | Si                       | GaAs                    | 4H-SiC                 | GaN                       |

|---------------------|--------------------------|-------------------------|------------------------|---------------------------|

| $E_G (eV)$          | 1.12                     | 1.42                    | 2.6                    | 3.37                      |

| $n_i \ (cm^{-3})$   | $1.5 \mathrm{x} 10^{10}$ | $2.1 \mathrm{x} 10^{6}$ | $8.2 \text{x} 10^{-9}$ | $1.9 \mathrm{x} 10^{-10}$ |

| $\epsilon_r$        | 11.8                     | 10.8                    | 9.6                    | 9.7                       |

| $\mu_n \ (cm^2/Vs)$ | 1350                     | 8500                    | 700                    | 900                       |

| $E_C (MV/cm)$       | 0.3                      | 0.4                     | 3                      | 5                         |

| $\nu_s \ (cm/s)$    | $1.3 \mathrm{x} 10^{7}$  | $1.2 x 10^{7}$          | $0.8 x 10^{7}$         | $3.0 \mathrm{x} 10^{7}$   |

| $\Phi_k (W/cmK)$    | 1.3                      | 0.6                     | 4.5                    | 1.3                       |

higher critical electric fields will achieve the desired power rating within a smaller drift region; i.e. smaller device dimensions. Thus, the specific on-resistance of the devices will be lower for GaN and SiC compared to Si or GaAs [11]. In addition, the reduced switching losses and improved temperature handling will further permit higher switching frequencies and reduce the size and weight of many passive components within the circuit.

### **1.2** Figure of Merits

The main device characteristics used to evaluate power devices are breakdown voltage,  $V_{BV}$ , on-resistance,  $r_{on}$ , peak current density,  $I_{max}$ , substrate leakage,  $I_{off}$ , and material reliability. These electrical characteristics are all dependent on the material properties of the semiconductor. Figure of merits (FOM) were generated from similar systems relative to material properties to compare the potential transistor improvements between various semiconductors with respect to silicon. The relationship between basic material properties of the semiconductor and common device characteristics for transistors were used to create Johnson's figure of merit (JFOM), Baligas figure of merit (BFOM), Baliga's high frequency figure of merit (BHFFOM), Keyes figure of merit (KFOM) and the combined figure of merit (CFOM).

Johnson's figure of merit was formulated to compare the switching capabilities of semiconductors based on the potential cut-off frequency of an equivalent dimensioned device [12]. The trade off between cut-off frequency,  $f_T$ , and maximum applied voltage,  $V_m$ , were shown to be equivalent to the critical electric field and saturation velocity of the semiconductor shown in (1.1). The *JFOM* suggested that wider band gap materials would improve the switching characteristics over narrow band gap semiconductors (i.e. Si) which inherently have low critical electric fields.

$$JFOM = V_m f_T = \frac{E_C \nu_s}{2\pi} \tag{1.1}$$

Similarly, Baliga's (BFOM) comparison for power devices (1.2) was originated from the relationship of the transistors on-resistance and channel depletion width [13]. By applying the comparison of the breakdown voltage,  $V_B$  with respect to the specific on-resistance,  $r_{on}$ , of the drift region, the BFOM, compared the dielectric constant, carrier mobility and critical electric field of semiconductors for power devices. Like the JFOM, the BFOMstrongly suggested wide band gap materials were required to improve and advance the device characteristics over silicon based power devices. The evaluation of semiconductors for high frequency and high power applications (1.3) known as Baliga's high frequency figure of merit (BHFFOM) was created from the material properties which effected the on-resistance,  $r_{on}$ , and input capacitance,  $C_{in}$ , of the device [11]. The on-resistance was dependent on the critical electric field, mobility and dielectric constant and the input capacitance was based on the semiconductors dielectric constant and depletion width. Again, this comparison suggested that wide band gap materials were capable of withstanding large electric fields, while maintaining larger channel mobilities will be successful.

$$BFOM = \frac{V_B^2}{r_{on}} = \epsilon_r \mu_n E_C^3 \tag{1.2}$$

$$BHFFOM = \frac{1}{r_{on}C_{in}} = \mu_n E_C^2 \tag{1.3}$$

Devices that operate in high temperature applications are most effected by the degradation of carrier mobility and background doping concentration [14–16]. These effects were known to reduce the on-off ratio of the device, through reduced current density and increased leakage current. To account for thermal degradation of various semiconductors, the Keyes figure of merit (KFOM) for thermal management in integrated circuits, (1.4), was dictated by the thermal conductivity, saturation velocity and dielectric constant of the material. This figure of merit was originally used to compare the impact of high density circuitry in Si-based CMOS rather than high temperature environments in high power electronic applications. However, the results with respect to the materials of interest for thermal management were still applicable.

Lastly, the combined figure of merit (CFOM) evaluated the substrate quality for the potential in high temperature, high power and high frequency applications [17]. The *CFOM* (1.5) was created through the combination of *BHFFOM* and *KFOM*. A semiconductor with the capability of high frequency and high power applications must also have the potential to manage self heating from the device switching. For example, if a device operated at  $300^{\circ}C$  the intrinsic substrate background doping for a narrow band-gap (Si) and a wide band-gap (GaN) are  $6\times10^{14}$  cm<sup>-3</sup> and  $1\times10^3$  cm<sup>-3</sup> respectively. The small band gap material depletion width would significantly shrink due to the increased background doping leading to a higher leakage current.

$$KFOM = \frac{\Phi_k \nu_s}{\epsilon_r} \tag{1.4}$$

$$CFOM = \Phi_k \epsilon_r \mu_n \nu_s E_C^2 \tag{1.5}$$

The previously discussed figure of merits were tabulated and normalize to silicon in Table 1.2. Based on the physical properties of the semiconductors, GaN has the potential for a broad range of power applications compared to the other materials discussed. In addition,

| Material | Si | GaAs     | 4H-SiC   | GaN       |

|----------|----|----------|----------|-----------|

| JFOM     | 1  | 2        | 38       | 1479      |

| BFOM     | 1  | 16       | 531      | 1206      |

| BHFFOM   | 1  | 11       | 64       | 87        |

| CFOM     | 1  | 11       | 33       | 164       |

| KFOM     | 1  | 0.3      | 2.5      | 4.3       |

| Overall  | 1  | $10^{3}$ | $10^{8}$ | $10^{11}$ |

Table 1.2: Figure of Merits based on Material Properties for Power Electronic Devices

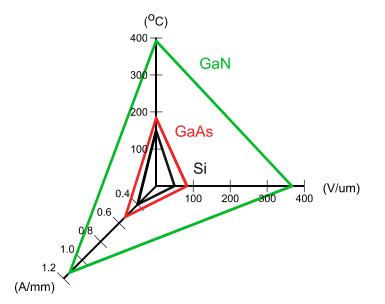

silicon carbide was also ranked well for the potential use in power devices. However, many fundamental issues of the material limited the advancement of this semiconductor over GaN for power devices. The most detrimental properties were the crystal orientation, mobility and band gap defects [18, 19]. In addition, the total consideration of all the figures of merits strongly suggested that GaN has the best possibility for next generation high power, high frequency and high temperature applications portrayed in Figure 1.2. Each material shown was only capable of operating within the triangular region defined by temperature, breakdown voltage and current density. As depicted below, GaN has the largest possible range of device operation for transistor applications compared to Si and GaAs.

Figure 1.2: A visual comparison of peak operation capabilities for Si, GaAs and GaN based on temperature and power applications. GaN has the ability to replace all silicon power devices based on the ability to operate  $200^{\circ}C$  higher and withstand electric fields larger than  $300 V/\mu m$ .

### 1.3 Gallium Nitride Transistors

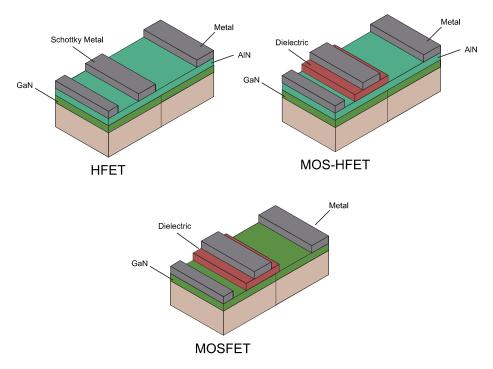

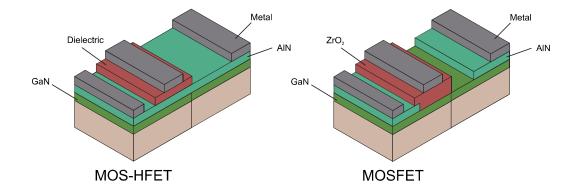

Over the last decade, GaN based devices have been regularly discussed in literature regarding the device characteristics and reliability for high frequency and high power applications [20–41]. The three main design architecture for GaN field effect transistors, shown in Figure 1.3, are the heterojunction field effect transistor (HFET), metal oxide semiconductor heterojunction field effect transistor (MOS-HFET) and the metal oxide semiconductor field effect transistor (MOSFET). The devices look similar in shape and metalization design; however, the gate film stacks along the channel are significantly different for each transistor. The HFET and MOS-HFET both have a 2-dimension electron gas (2DEG) formed along the AlGaN/GaN or AlN/GaN polarized interface [42]. The major difference is the HFET uses a Schottky metal at the gate, whereas the MOS-HFET has a gate dielectric. The Schottky gate has many issues, such as depletion-mode operation and higher gate leakage [43]; however, the HFET is currently capable of producing high current densities for a given gate length. The MOS-HFET has a similar architecture as the HFET, but the gate dielectric has been included to reduce the gate leakage current during operation [43]. Fluorine plasma pretreatments along the GaN channel surface was a common technique to shift the devices turn-on voltage positive. This pretreatment to the GaN adjusted the Fermi level under the channel, requiring a positive gate bias to form the 2DEG channel rather than a negative bias to turn the device off [44]. This has improved the sub-threshold

Figure 1.3: The three most common GaN device architectures under investigation for power applications are the (a) HFET, (b) MOS-HFET and (c) MOSFET.

leakage current; however, the performance of the device was degraded due to higher sheet resistance and lower channel mobility due to fluorine induced interface defects [45].

Lastly, the metal oxide semiconductor field effect transistor (MOSFET) architecture only has a dielectric along the gate [14, 15]. By removing the AlN or AlGaN film and the inherent 2DEG along the interface, the turn-on voltage of the device becomes strictly positive. This produced an enhancement-mode transistor where the device was normally-off at zero gate bias. Various gate dielectrics for GaN MOSFETs have been investigated to rectify issues that have reduced the capacitance density and channel field effect mobility. In-turn an improved dielectric and interface along the channel has the potential to advance the peak current density and cutoff frequency of the device.

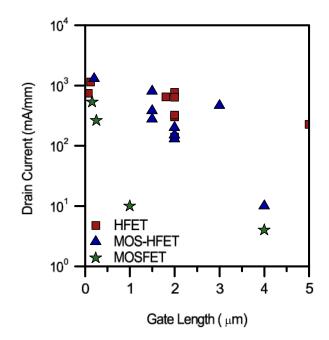

The majority of the scientific research has been aimed towards improving the off-state of the HFET design for high power applications. The following Table 1.3 highlights significant

|                                                                | T         | T         | TZ.   | Т        | ~       | I.       |                  |       |

|----------------------------------------------------------------|-----------|-----------|-------|----------|---------|----------|------------------|-------|

|                                                                | $L_G$     | $L_{GD}$  | $V_t$ | $I_{DS}$ | $g_m$   | $V_{BV}$ | $r_{on}$         | Ref.  |

|                                                                | $(\mu m)$ | $(\mu m)$ | (+/-) | (mA/mm)  | (mS/mm) | (V)      | $(m\Omega cm^2)$ | [2.0] |

| HFET                                                           | 4         | 3         | -     | 10       | 28      | 30*      | 6.6              | [20]  |

|                                                                | 1.5       | 10        | -     | 800      | 160     | 594*     | 3.3              | [21]  |

|                                                                | 2         | 4         | +     | 130      | 70      | 300      | 30               | [22]  |

|                                                                | 2         | 125       | -     | 150      | 50      | 8300*    | 186              | [23]  |

|                                                                | 2         | 7.5       | +     | 200      | 70      | 800      | 2.6              | [24]  |

|                                                                | 1.5       | 12        | +     | 275      | 150     | 1100     | 6.2              | [25]  |

|                                                                | 1.5       | 12        | +     | 380      | 246     | 1100*    | /                | [26]  |

|                                                                | 3         | 20        | -     | 463      | 102     | 1160     | 7.5              | [27]  |